# PSoC<sup>®</sup> 4: PSoC 4200M Family Datasheet

# Programmable System-on-Chip (PSoC®)

## **General Description**

PSoC<sup>®</sup> 4 is a scalable and reconfigurable platform architecture for a family of programmable embedded system controllers with an ARM<sup>®</sup> Cortex<sup>™</sup>-M0 CPU. It combines programmable and reconfigurable analog and digital blocks with flexible automatic routing. The PSoC 4200M product family, based on this platform architecture, is a combination of a microcontroller with digital programmable logic, programmable analog, programmable interconnect, high-performance analog-to-digital conversion, opamps with comparator mode, and standard communication and timing peripherals. The PSoC 4200M products will be fully compatible with members of the PSoC 4 platform for new applications and design needs. The programmable analog and digital subsystems allow flexibility and in-field tuning of the design.

#### **Features**

#### 32-bit MCU Subsystem

- 48 MHz ARM Cortex-M0 CPU with single-cycle multiply

- Up to 128 kB of flash with Read Accelerator

- Up to 16 kB of SRAM

- DMA engine

#### **Programmable Analog**

- Four opamps that operate in Deep Sleep mode at very low current levels

- All opamps have reconfigurable high current pin-drive, high-bandwidth internal drive, ADC input buffering, and Comparator modes with flexible connectivity allowing input connections to any pin

- Four current DACs (IDACs) for general-purpose or capacitive sensing applications on any pin

- Two low-power comparators that operate in Deep Sleep mode

- 12-bit SAR ADC with 1-Msps conversion rate

#### **Programmable Digital**

- Four programmable logic blocks, each with 8 Macrocells and an 8-bit data path (called universal digital blocks or UDBs)

- Cypress-provided peripheral component library, user-defined state machines, and Verilog input

#### Low Power 1.71 to 5.5 V Operation

- 20-nA Stop Mode with GPIO pin wakeup

- Hibernate and Deep Sleep modes allow wakeup-time versus power trade-offs

## Capacitive Sensing

- Cypress Capacitive Sigma-Delta (CSD) technique provides best-in-class SNR (>5:1) and water tolerance

- Cypress-supplied software component makes capacitive sensing design easy

- Automatic hardware tuning (SmartSense<sup>™</sup>)

#### Segment LCD Drive

- LCD drive supported on all pins (common or segment)

- Operates in Deep Sleep mode with 4 bits per pin memory

#### **Serial Communication**

- Four independent run-time reconfigurable serial communication blocks (SCBs) with reconfigurable I<sup>2</sup>C, SPI, or UART functionality

- Two independent CAN blocks for industrial and automotive networking

#### **Timing and Pulse-Width Modulation**

- Eight 16-bit timer/counter pulse-width modulator (TCPWM) blocks

- Center-aligned, Edge, and Pseudo-random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

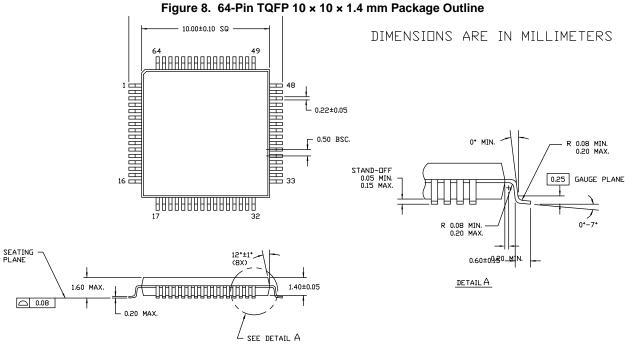

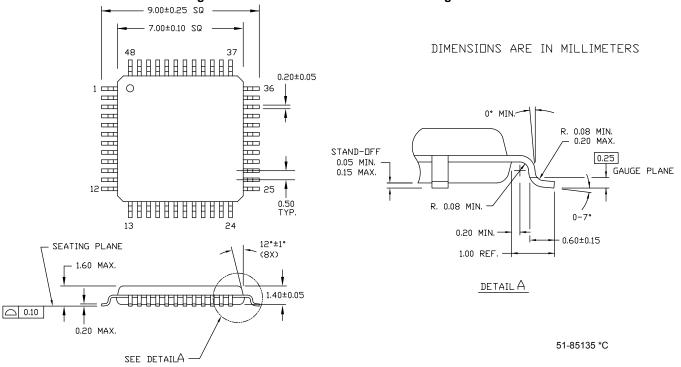

#### **Package Options**

- 68-pin QFN, 64-pin TQFP wide and narrow pitch, and 48-pin TQFP packages

- Up to 55 programmable GPIOs

- GPIO pins can be CapSense, LCD, analog, or digital

- Drive modes, strengths, and slew rates are programmable

#### **PSoC Creator Design Environment**

- Integrated Development Environment (IDE) provides schematic design entry and build (with analog and digital automatic routing)

- Applications Programming Interface (API component) for all fixed-function and programmable peripherals

#### Industry-Standard Tool Compatibility

After schematic entry, development can be done with ARM-based industry-standard development tools

**Cypress Semiconductor Corporation**Document Number: 001-93963 Rev. \*D

#### More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 4:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 4 are:

- □ AN79953: Getting Started With PSoC 4

- □ AN88619: PSoC 4 Hardware Design Considerations

- □ AN86439: Using PSoC 4 GPIO Pins

- □ AN57821: Mixed Signal Circuit Board Layout

- □ AN81623: Digital Design Best Practices

- □ AN73854: Introduction To Bootloaders

- □ AN89610: ARM Cortex Code Optimization

- Technical Reference Manual (TRM) is in two documents:

- □ Architecture TRM details each PSoC 4 functional block.

- □ Registers TRM describes each of the PSoC 4 registers.

- Development Kits:

- □ CY8CKIT-042, PSoC 4 Pioneer Kit, is an easy-to-use and inexpensive development platform. This kit includes connectors for Arduino™ compatible shields and Digilent® Pmod™ daughter cards.

- □ CY8CKIT-049 is a very low-cost prototyping platform. It is a low-cost alternative to sampling PSoC 4 devices.

- CY8CKIT-001 is a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

The MiniProg3 device provides an interface for flash programming and debug.

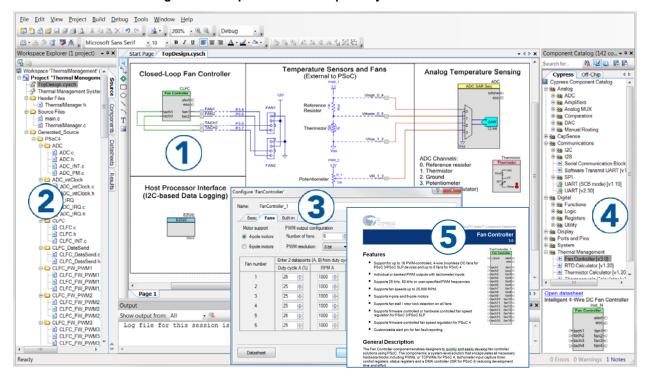

#### **PSoC Creator**

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- 1. Drag and drop component icons to build your hardware system design in the main design workspace

- Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

Figure 1. Multiple-Sensor Example Project in PSoC Creator

## **Contents**

| PSoC 4200M Block Diagram     | 4  |

|------------------------------|----|

| Functional Definition        | 5  |

| CPU and Memory Subsystem     | 5  |

| System Resources             | 5  |

| Analog Blocks                | 6  |

| Programmable Digital         | 7  |

| Fixed Function Digital       | 8  |

| GPIO                         | 9  |

| Special Function Peripherals | 9  |

| Pinouts                      | 10 |

| Power                        | 14 |

| Unregulated External Supply  | 14 |

| Regulated External Supply    | 14 |

| Development Support          |    |

| Documentation                | 15 |

| Online                       | 15 |

| Tools                        | 15 |

| Electrical Specifications    | 16 |

| Absolute Maximum Ratings     | 16 |

| Device Level Specifications  | 16 |

| Analog Peripherals                      | 20 |

|-----------------------------------------|----|

| Digital Peripherals                     | 25 |

|                                         |    |

| System Resources                        | 28 |

| Ordering Information                    | 32 |

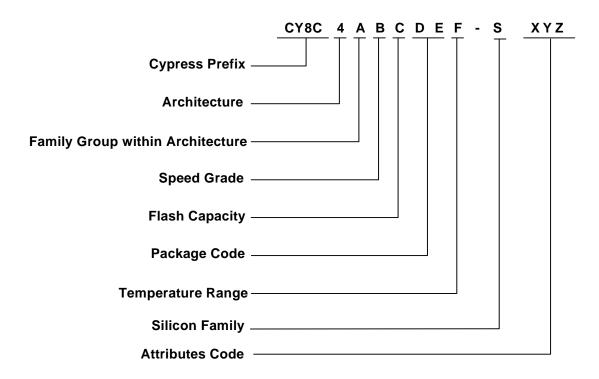

| Part Numbering Conventions              | 33 |

| Packaging                               | 34 |

| Acronyms                                | 37 |

| Document Conventions                    |    |

| Units of Measure                        | 39 |

| Revision History                        | 40 |

| Sales, Solutions, and Legal Information | 41 |

| Worldwide Sales and Design Support      | 41 |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             | 41 |

| Technical Support                       |    |

|                                         |    |

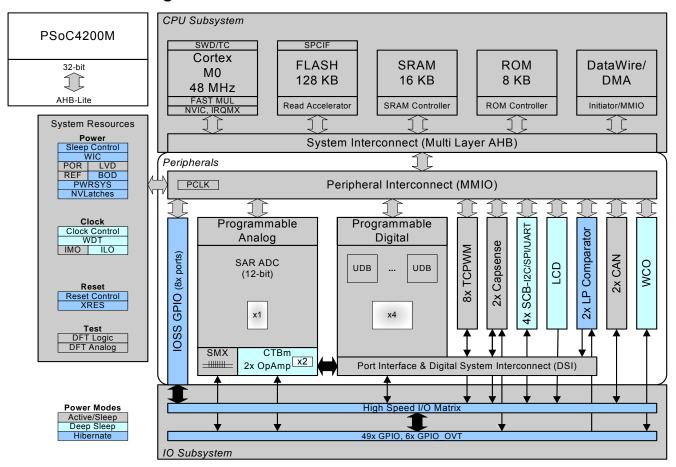

## **PSoC 4200M Block Diagram**

The PSoC 4200-M devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware.

The ARM Serial\_Wire Debug (SWD) interface supports all programming and debug features of the device.

Complete debug-on-chip functionality enables full-device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator Integrated Development Environment (IDE) provides fully integrated programming and debug support for PSoC 4200-M devices. The SWD interface is fully compatible with industry-standard third-party tools. The PSoC 4200-M family provides a level of security not possible with multi-chip application solutions or with microcontrollers. This is due to its ability to disable debug features, robust flash protection, and

because it allows customer-proprietary functionality to be implemented in on-chip programmable blocks.

The debug circuits are enabled by default and can only be disabled in firmware. If not enabled, the only way to re-enable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables debugging.

Additionally, all device interfaces can be permanently disabled (device security) for applications concerned about phishing attacks due to a maliciously reprogrammed device or attempts to defeat security by starting and interrupting flash programming sequences. Because all programming, debug, and test interfaces are disabled when maximum device security is enabled, PSoC 4200-M with device security enabled may not be returned for failure analysis. This is a trade-off the PSoC 4200-M allows the customer to make.

#### **Functional Definition**

#### CPU and Memory Subsystem

#### CPU

The Cortex-M0 CPU in the PSoC 4200-M is part of the 32-bit MCU subsystem, which is optimized for low-power operation with extensive clock gating. Most instructions are 16 bits in length and execute a subset of the Thumb-2 instruction set. The Cypress implementation includes a hardware multiplier that provides a 32-bit result in one cycle. It includes a nested vectored interrupt controller (NVIC) block with 32 interrupt inputs and also includes a Wakeup Interrupt Controller (WIC), which can wake the processor up from the Deep Sleep mode allowing power to be switched off to the main processor when the chip is in the Deep Sleep mode. The Cortex-M0 CPU provides a Non-Maskable Interrupt (NMI) input, which is made available to the user when it is not in use for system functions requested by the user

The CPU also includes a debug interface, the serial wire debug (SWD) interface, which is a 2-wire form of JTAG; the debug configuration used for PSoC 4200-M has four break-point (address) comparators and two watchpoint (data) comparators.

#### Flash

The PSoC 4200-M has a flash module with a flash accelerator, tightly coupled to the CPU to improve average access times from the flash block. The flash accelerator delivers 85% of single-cycle SRAM access performance on average. Part of the flash module can be used to emulate EEPROM operation if required.

#### **SRAM**

SRAM memory is retained during Hibernate.

#### SROM

A supervisory ROM that contains boot and configuration routines is provided.

#### DMA

A DMA engine, with eight channels, is provided that can do 32-bit transfers and has chainable ping-pong descriptors.

#### **System Resources**

#### Power System

The power system is described in detail in the section Power on page 14. It provides assurance that voltage levels are as required for each respective mode and either delay mode entry (on power-on reset (POR), for example) until voltage levels are as required for proper function or generate resets (brown-out detect (BOD)) or interrupts (low voltage detect (LVD)). The PSoC 4200M operates with a single external supply over the range of 1.71 to 5.5 V and has five different power modes, transitions between which are managed by the power system. The PSoC 4200M provides Sleep, Deep Sleep, Hibernate, and Stop low-power modes.

#### Clock System

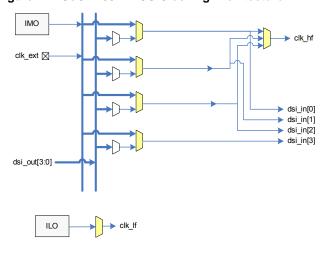

The PSoC 4200-M clock system is responsible for providing clocks to all subsystems that require clocks and for switching between different clock sources without glitching. In addition, the clock system ensures that no meta-stable conditions occur.

The clock system for the PSoC 4200-M consists of a Watch Crystal Oscillator (WCO) running at 32 kHz, the IMO (3 to 48 MHz) and the ILO (32-kHz nominal) internal oscillators, and provision for an external clock.

Figure 2. PSoC 4200M MCU Clocking Architecture

The clk\_hf signal can be divided down to generate synchronous clocks for the UDBs, and the analog and digital peripherals. There are a total of 16 clock dividers for the PSoC 4200-M, each with 16-bit divide capability; this allows 12 to be used for the fixed-function blocks and four for the UDBs. The analog clock leads the digital clocks to allow analog events to occur before digital clock-related noise is generated. The 16-bit capability allows a lot of flexibility in generating fine-grained frequency values and is fully supported in PSoC Creator.

#### IMO Clock Source

The IMO is the primary source of internal clocking in the PSoC 4200M. It is trimmed during testing to achieve the specified accuracy. Trim values are stored in nonvolatile memory. Trimming can also be done on the fly to allow in-field calibration. The IMO default frequency is 24 MHz and it can be adjusted between 3 to 48 MHz in steps of 1 MHz. IMO tolerance with Cypress-provided calibration settings is ±2%.

#### ILO Clock Source

The ILO is a very low power oscillator, nominally 32 kHz, which is primarily used to generate clocks for peripheral operation in Deep Sleep mode. ILO-driven counters can be calibrated to the IMO to improve accuracy. Cypress provides a software component, which does the calibration.

#### Crystal Oscillator

The PSoC 4200M clock subsystem also includes a low-frequency crystal oscillator (32-kHz WCO) that is available during the Deep Sleep mode and can be used for Real-Time Clock (RTC) and Watchdog Timer applications.

#### Watchdog Timer

A watchdog timer is implemented in the clock block running from the low-frequency clock; this allows watchdog operation during Deep Sleep and generates a watchdog reset or an interrupt if not serviced before the timeout occurs. The watchdog reset is recorded in the Reset Cause register.

#### Reset

The PSoC 4200M can be reset from a variety of sources including a software reset. Reset events are asynchronous and guarantee reversion to a known state. The reset cause is recorded in a register, which is sticky through reset and allows software to determine the cause of the reset. An XRES pin is reserved for external reset to avoid complications with configuration and multiple pin functions during power-on or reconfiguration.

#### Voltage Reference

The PSoC 4200M reference system generates all internally required references. A 1% voltage reference spec is provided for the 12-bit ADC. To allow better signal-to-noise ratios (SNR) and better absolute accuracy, it is possible to add an external bypass capacitor to the internal reference using a GPIO pin or to use an external reference for the SAR.

#### **Analog Blocks**

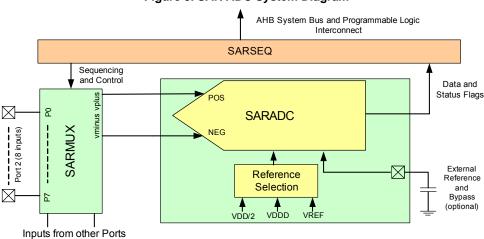

#### 12-bit SAR ADC

The 12-bit 1 MSample/second SAR ADC can operate at a maximum clock rate of 18 MHz and requires a minimum of 18 clocks at that frequency to do a 12-bit conversion.

The block functionality is augmented for the user by adding a reference buffer to it (trimmable to  $\pm 1\%$ ) and by providing the choice of three internal voltage references:  $V_{DD}$ ,  $V_{DD}/2$ , and

V<sub>REF</sub> (nominally 1.024 V) as well as an external reference through a GPIO pin. The Sample-and-Hold (S/H) aperture is programmable allowing the gain bandwidth requirements of the amplifier driving the SAR inputs, which determine its settling time, to be relaxed if required. The system performance will be 65 dB for true 12-bit precision if appropriate references are used and system noise levels permit. To improve performance in noisy conditions, it is possible to provide an external bypass (through a fixed pin location) for the internal reference amplifier.

The SAR is connected to a fixed set of pins through an 8-input sequencer (expandable to 16 inputs). The sequencer cycles through selected channels autonomously (sequencer scan) and does so with zero switching overhead (that is, the aggregate sampling bandwidth is equal to 1 Msps, whether it is for a single channel or distributed over several channels). The sequencer switching is effected through a state machine or through firmware-driven switching. A feature provided by the sequencer is buffering of each channel to reduce CPU interrupt service requirements. To accommodate signals with varying source impedance and frequency, it is possible to have different sample times programmable for each channel. In addition, the signal range specification through a pair of range registers (low and high range values) is implemented with a corresponding out-of-range interrupt if the digitized value exceeds the programmed range; this allows fast detection of out-of-range values without the necessity of having to wait for a sequencer scan to be completed and the CPU to read the values and check for out-of-range values in software.

The SAR is able to digitize the output of the on-board temperature sensor for calibration and other temperature-dependent functions. The SAR is not available in Deep Sleep and Hibernate modes as it requires a high-speed clock (up to 18 MHz). The SAR operating range is 1.71 to 5.5 V.

Figure 3. SAR ADC System Diagram

#### Analog Multiplex Bus

The PSoC 4200M has two concentric analog buses (Analog Mux Bus A and Analog Mux Bus B) that circumnavigate the periphery of the chip. These buses can transport analog signals from any pin to various analog blocks (including the opamps) and to the CapSense blocks allowing, for instance, the ADC to monitor any pin on the chip. These buses are independent and can also be split into three independent sections. This allows one section to be used for CapSense purposes, one for general analog signal processing, and the third for general-purpose digital peripherals and GPIO.

#### Four Opamps

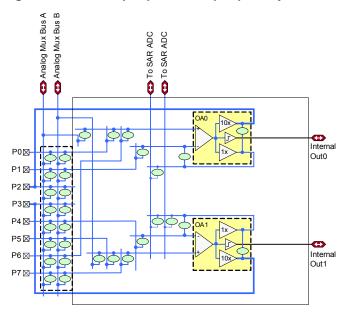

The PSoC 4200M has four opamps with comparator modes, which allow most common analog functions to be performed on-chip eliminating external components; PGAs, voltage buffers, filters, trans-impedance amplifiers, and other functions can be realized with external passives saving power, cost, and space. The on-chip opamps are designed with enough bandwidth to drive the Sample-and-Hold circuit of the ADC without requiring external buffering. The opamps can operate in the Deep Sleep mode at very low power levels. The following diagram shows one of two identical opamp pairs of the opamp subsystem.

Figure 4. Identical Opamp Pairs in Opamp Subsystem

The ovals in Figure 4 represent analog switches, which may be controlled via user firmware, the SAR sequencer, or user-defined programmable logic. The opamps (OA0 and OA1) are configurable via these switches to perform all standard opamp functions with appropriate feedback components.

The opamps (OA0 and OA1) are programmable and reconfigurable to provide standard opamp functionality via switchable feedback components, unity gain functionality for driving pins directly, or for internal use (such as buffering SAR ADC inputs as indicated in the diagram), or as true comparators.

The opamp inputs provide highly flexible connectivity and can connect directly to dedicated pins or, via the analog mux buses,

to any pin on the chip. Analog switch connectivity is controllable by user firmware as well as user-defined programmable digital state machines (implemented via UDBs).

The opamps operate in Deep Sleep mode at very low currents allowing analog circuits to remain operational during Deep Sleep.

#### Temperature Sensor

The PSoC 4200M has one on-chip temperature sensor. This consists of a diode, which is biased by a current source that can be disabled to save power. The temperature sensor is connected to the ADC, which digitizes the reading and produces a temperature value using Cypress-supplied software that includes calibration and linearization.

#### Low-power Comparators

The PSoC 4200M has a pair of low-power comparators, which can also operate in the Deep Sleep and Hibernate modes. This allows the analog system blocks to be disabled while retaining the ability to monitor external voltage levels during low-power modes. The comparator outputs are normally synchronized to avoid meta-stability unless operating in an asynchronous power mode (Hibernate) where the system wake-up circuit is activated by a comparator switch event.

#### **Programmable Digital**

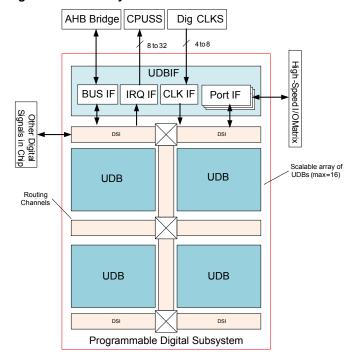

Universal Digital Blocks (UDBs) and Port Interfaces

The PSoC 4200M has four UDBs; the UDB array also provides a switched Digital System Interconnect (DSI) fabric that allows signals from peripherals and ports to be routed to and through the UDBs for communication and control. The UDB array is shown in the following figure.

Figure 5. UDB Array

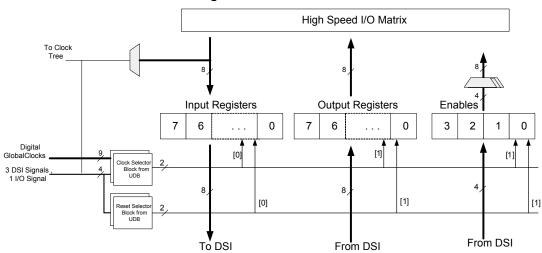

UDBs can be clocked from a clock divider block, from a port interface (required for peripherals such as SPI), and from the DSI network directly or after synchronization.

A port interface is defined, which acts as a register that can be clocked with the same source as the PLDs inside the UDB array. This allows faster operation because the inputs and outputs can be registered at the port interface close to the I/O pins and at the edge of the array. The port interface registers can be clocked by one of the I/Os from the same port. This allows interfaces such

as SPI to operate at higher clock speeds by eliminating the delay for the port input to be routed over DSI and used to register other inputs. The port interface is shown in Figure 6.

The UDBs can generate interrupts (one UDB at a time) to the interrupt controller. The UDBs retain the ability to connect to any pin on the chip through the DSI.

Figure 6. Port Interface

#### **Fixed Function Digital**

#### Timer/Counter/PWM (TCPWM) Block

The TCPWM block uses a16-bit counter with user-programmable period length. There is a Capture register to record the count value at the time of an event (which may be an I/O event), a period register which is used to either stop or auto-reload the counter when its count is equal to the period register, and compare registers to generate compare value signals, which are used as PWM duty cycle outputs. The block also provides true and complementary outputs with programmable offset between them to allow use as deadband programmable complementary PWM outputs. It also has a Kill input to force outputs to a predetermined state; for example, this is used in motor drive systems when an overcurrent state is indicated and the PWMs driving the FETs need to be shut off immediately with no time for software intervention. The PSoC 4200M has eight TCPWM blocks.

#### Serial Communication Blocks (SCB)

The PSoC 4200M has four SCBs, which can each implement an  $I^2$ C, UART, or SPI interface.

I<sup>2</sup>C Mode: The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multimaster arbitration). This block is capable of operating at speeds of up to 1 Mbps (Fast Mode Plus) and has flexible buffering options to reduce interrupt overhead and latency for the CPU. It also supports EzI<sup>2</sup>C that creates a mailbox address range in the memory of the PSoC 4200M and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in memory. In

addition, the block supports an 8-deep FIFO for receive and transmit which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read data on time. The FIFO mode is available in all channels and is very useful in the absence of DMA.

The I<sup>2</sup>C peripheral is compatible with the I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes.

UART Mode: This is a full-feature UART operating at up to 1 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO7816) protocols, all of which are minor variants of the basic UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows addressing of peripherals connected over common RX and TX lines. Common UART functions such as parity error, break detect, and frame error are supported. An 8-deep FIFO allows much greater CPU service latencies to be tolerated.

SPI Mode: The SPI mode supports full Motorola SPI, TI SSP (essentially adds a start pulse used to synchronize SPI Codecs), and National Microwire (half-duplex form of SPI). The SPI block can use the FIFO and also supports an EzSPI mode in which data interchange is reduced to reading and writing an array in memory.

#### CAN Blocks

There are two independent CAN 2.0B blocks, which are certified CAN conformant.

#### **GPIO**

The PSoC 4200M has 55 GPIOs in the 68-pin QFN package. The GPIO block implements the following:

- Eight drive strength modes including strong push-pull, resistive pull-up and pull-down, weak (resistive) pull-up and pull-down, open drain and open source, input only, and disabled

- Input threshold select (CMOS or LVTTL)

- Individual control of input and output disables

- Hold mode for latching previous state (used for retaining I/O state in Deep Sleep mode and Hibernate modes)

- Selectable slew rates for dV/dt related noise control to improve

The pins are organized in logical entities called ports, which are 8-bit in width. During power-on and reset, the blocks are forced to the disable state so as not to crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a high-speed I/O matrix is used to multiplex between various signals that may connect to an I/O pin. Pin locations for fixed-function peripherals are also fixed to reduce internal multiplexing complexity (these signals do not go through the DSI network). DSI signals are not affected by this and any pin may be routed to any UDB through the DSI network.

Data output and pin state registers store, respectively, the values to be driven on the pins and the states of the pins themselves.

Every I/O pin can generate an interrupt if so enabled and each I/O port has an interrupt request (IRQ) and interrupt service routine (ISR) vector associated with it (8 for PSoC 4200M).

The Pins of Port 6 (up to 6 depending on the package) are overvoltage tolerant (V<sub>IN</sub> can exceed V<sub>DD</sub>). The overvoltage cells will not sink more than 10  $\mu$ A when their inputs exceed  $V_{DDIO}$  in compliance with I<sup>2</sup>C specifications.

#### **Special Function Peripherals**

#### LCD Segment Drive

The PSoC 4200M has an LCD controller, which can drive up to four commons and up to 51 segments. Any pin can be either a common or a segment pin. It uses full digital methods to drive the LCD segments requiring no generation of internal LCD voltages. The two methods used are referred to as digital correlation and

Digital correlation pertains to modulating the frequency and levels of the common and segment signals to generate the highest RMS voltage across a segment to light it up or to keep the RMS signal zero. This method is good for STN displays but may result in reduced contrast with TN (cheaper) displays.

PWM pertains to driving the panel with PWM signals to effectively use the capacitance of the panel to provide the integration of the modulated pulse-width to generate the desired LCD voltage. This method results in higher power consumption but can result in better results when driving TN displays. LCD operation is supported during Deep Sleep refreshing a small display buffer (4 bits; 1 32-bit register per port).

#### CapSense

CapSense is supported on all pins in the PSoC 4200M through a CapSense Sigma-Delta (CSD) block that can be connected to any pin through an analog mux bus that any GPIO pin can be connected to via an Analog switch. CapSense functionality can thus be provided on any pin or group of pins in a system under software control. A component is provided for the CapSense block, which provides automatic hardware tuning (Cypress SmartSense<sup>™</sup>), to make it easy for the user.

Shield voltage can be driven on another Mux Bus to provide water tolerance capability. Water tolerance is provided by driving the shield electrode in phase with the sense electrode to keep the shield capacitance from attenuating the sensed input.

Each CSD block has two IDACs which can be used for general purposes if CapSense is not being used (both IDACs are available in that case) or if CapSense is used without water tolerance (one IDAC is available). The PSoC 4200M has two CSD blocks which can be used independently; one for CapSense and one providing two IDACs.

## **Pinouts**

The following is the pin list for the PSoC 4200M. This shows the power supply and port pins (for example, P0.0 is Pin 0 of Port 0).

|     | 68-QFN    |     | 64-TQFP   |     | 48-TQFP   |

|-----|-----------|-----|-----------|-----|-----------|

| Pin | Name      | Pin | Name      | Pin | Name      |

|     |           |     |           |     |           |

| 42  | P0.0      | 39  | P0.0      | 28  | P0.0      |

| 43  | P0.1      | 40  | P0.1      | 29  | P0.1      |

| 44  | P0.2      | 41  | P0.2      | 30  | P0.2      |

| 45  | P0.3      | 42  | P0.3      | 31  | P0.3      |

| 46  | P0.4      | 43  | P0.4      | 32  | P0.4      |

| 47  | P0.5      | 44  | P0.5      | 33  | P0.5      |

| 48  | P0.6      | 45  | P0.6      | 34  | P0.6      |

| 49  | P0.7      | 46  | P0.7      | 35  | P0.7      |

| 50  | XRES      | 47  | XRES      | 36  | XRES      |

| 51  | VCCD      | 48  | VCCD      | 37  | VCCD      |

| 52  | VSSD      | 49  | VSSD      | 38  | VSSD      |

| 53  | VDDD      | 50  | VDDD      | 39  | VDDD      |

| 54  | P5.0      | 51  | P5.0      |     |           |

| 55  | P5.1      | 52  | P5.1      |     |           |

| 56  | P5.2      | 53  | P5.2      |     |           |

| 57  | P5.3      | 54  | P5.3      |     |           |

| 58  | P5.4      |     |           |     |           |

| 59  | P5.5      | 55  | P5.5      |     |           |

| 60  | VDDA      | 56  | VDDA      | 40  | VDDA      |

| 61  | VSSA      | 57  | VSSA      | 41  | VSSA      |

| 62  | P1.0      | 58  | P1.0      | 42  | P1.0      |

| 63  | P1.1      | 59  | P1.1      | 43  | P1.1      |

| 64  | P1.2      | 60  | P1.2      | 44  | P1.2      |

| 65  | P1.3      | 61  | P1.3      | 45  | P1.3      |

| 66  | P1.4      | 62  | P1.4      | 46  | P1.4      |

| 67  | P1.5      | 63  | P1.5      | 47  | P1.5      |

| 68  | P1.6      | 64  | P1.6      | 48  | P1.6      |

| 1   | P1.7/VREF | 1   | P1.7/VREF | 1   | P1.7/VREF |

| 2   | P2.0      | 2   | P2.0      | 2   | P2.0      |

| 3   | P2.1      | 3   | P2.1      | 3   | P2.1      |

| 4   | P2.2      | 4   | P2.2      | 4   | P2.2      |

| 5   | P2.3      | 5   | P2.3      | 5   | P2.3      |

| 6   | P2.4      | 6   | P2.4      | 6   | P2.4      |

| 7   | P2.5      | 7   | P2.5      | 7   | P2.5      |

| 8   | P2.6      | 8   | P2.6      | 8   | P2.6      |

| 9   | P2.7      | 9   | P2.7      | 9   | P2.7      |

| 10  | VSSA      | 10  | VSSA      | 10  | VSSIO     |

| 11  | VDDA      | 11  | VDDA      |     |           |

|     | 68-QFN |     | 64-TQFP |     | 48-TQFP |

|-----|--------|-----|---------|-----|---------|

| Pin | Name   | Pin | Name    | Pin | Name    |

| 12  | P6.0   | 12  | P6.0    |     |         |

| 13  | P6.1   | 13  | P6.1    |     |         |

| 14  | P6.2   | 14  | P6.2    |     |         |

| 15  | P6.3   |     |         |     |         |

| 16  | P6.4   | 15  | P6.4    |     |         |

| 17  | P6.5   | 16  | P6.5    |     |         |

| 18  | VSSIO  | 17  | VSSIO   |     |         |

| 19  | P3.0   | 18  | P3.0    | 12  | P3.0    |

| 20  | P3.1   | 19  | P3.1    | 13  | P3.1    |

| 21  | P3.2   | 20  | P3.2    | 14  | P3.2    |

| 22  | P3.3   | 21  | P3.3    | 16  | P3.3    |

| 23  | P3.4   | 22  | P3.4    | 17  | P3.4    |

| 24  | P3.5   | 23  | P3.5    | 18  | P3.5    |

| 25  | P3.6   | 24  | P3.6    | 19  | P3.6    |

| 26  | P3.7   | 25  | P3.7    | 20  | P3.7    |

| 27  | VDDIO  | 26  | VDDIO   | 21  | VDDIO   |

| 28  | P4.0   | 27  | P4.0    | 22  | P4.0    |

| 29  | P4.1   | 28  | P4.1    | 23  | P4.1    |

| 30  | P4.2   | 29  | P4.2    | 24  | P4.2    |

| 31  | P4.3   | 30  | P4.3    | 25  | P4.3    |

| 32  | P4.4   | 31  | P4.4    |     |         |

| 33  | P4.5   | 32  | P4.5    |     |         |

| 34  | P4.6   | 33  | P4.6    |     |         |

| 35  | P4.7   |     |         |     |         |

| 39  | P7.0   | 37  | P7.0    | 26  | P7.0    |

| 40  | P7.1   | 38  | P7.1    | 27  | P7.1    |

| 41  | P7.2   |     |         |     |         |

The pins of Port 6 are overvoltage-tolerant. Pins 11 and 15 are No-connects in the 48-pin TQFP. All VSS pins must be tied together.

Each of the pins shown in the previous table can have multiple programmable functions as shown in the following table. Column headings refer to Analog and Alternate pin functions.:

| Port/Pin | Analog           | Alt. Function 1       | Alt. Function 2   | Alt. Function 3       | Alt. Function 4  | Alt. Function 5      |

|----------|------------------|-----------------------|-------------------|-----------------------|------------------|----------------------|

| P0.0     | lpcomp.in_p[0]   |                       |                   | can[1].can_rx:0       |                  | scb[0].spi_select1:0 |

| P0.1     | lpcomp.in_n[0]   |                       |                   | can[1].can_tx:0       |                  | scb[0].spi_select2:0 |

| P0.2     | lpcomp.in_p[1]   |                       |                   |                       |                  | scb[0].spi_select3:0 |

| P0.3     | lpcomp.in_n[1]   |                       |                   |                       |                  |                      |

| P0.4     | wco_in           |                       | scb[1].uart_rx:0  |                       | scb[1].i2c_scl:0 | scb[1].spi_mosi:1    |

| P0.5     | wco_out          |                       | scb[1].uart_tx:0  |                       | scb[1].i2c_sda:0 | scb[1].spi_miso:1    |

| P0.6     |                  | ext_clk:0             | scb[1].uart_cts:0 |                       |                  | scb[1].spi_clk:1     |

| P0.7     |                  |                       | scb[1].uart_rts:0 | can[1].can_tx_enb_n:0 | wakeup           | scb[1].spi_select0:1 |

| P5.0     | ctb1.oa0.inp     | tcpwm.line[4]:2       | scb[2].uart_rx:0  |                       | scb[2].i2c_scl:0 | scb[2].spi_mosi:0    |

| P5.1     | ctb1.oa0.inm     | tcpwm.line_compl[4]:2 | scb[2].uart_tx:0  |                       | scb[2].i2c_sda:0 | scb[2].spi_miso:0    |

| P5.2     | ctb1.oa0.out     | tcpwm.line[5]:2       | scb[2].uart_cts:0 |                       | lpcomp.comp[0]:1 | scb[2].spi_clk:0     |

| P5.3     | ctb1.oa1.out     | tcpwm.line_compl[5]:2 | scb[2].uart_rts:0 |                       | lpcomp.comp[1]:1 | scb[2].spi_select0:0 |

| P5.4     | ctb1.oa1.inm     | tcpwm.line[6]:2       |                   |                       |                  | scb[2].spi_select1:0 |

| P5.5     | ctb1.oa1.inp     | tcpwm.line_compl[6]:2 |                   |                       |                  | scb[2].spi_select2:0 |

| P5.6     | ctb1.oa0.inp_alt | tcpwm.line[7]:0       |                   |                       |                  | scb[2].spi_select3:0 |

| P5.7     | ctb1.oa1.inp_alt | tcpwm.line_compl[7]:0 |                   |                       |                  |                      |

| P1.0     | ctb0.oa0.inp     | tcpwm.line[2]:1       | scb[0].uart_rx:1  |                       | scb[0].i2c_scl:0 | scb[0].spi_mosi:1    |

| P1.1     | ctb0.oa0.inm     | tcpwm.line_compl[2]:1 | scb[0].uart_tx:1  |                       | scb[0].i2c_sda:0 | scb[0].spi_miso:1    |

| P1.2     | ctb0.oa0.out     | tcpwm.line[3]:1       | scb[0].uart_cts:1 |                       |                  | scb[0].spi_clk:1     |

| P1.3     | ctb0.oa1.out     | tcpwm.line_compl[3]:1 | scb[0].uart_rts:1 |                       |                  | scb[0].spi_select0:1 |

| P1.4     | ctb0.oa1.inm     | tcpwm.line[6]:1       |                   |                       |                  | scb[0].spi_select1:1 |

| P1.5     | ctb0.oa1.inp     | tcpwm.line_compl[6]:1 |                   |                       |                  | scb[0].spi_select2:1 |

| P1.6     | ctb0.oa0.inp_alt | tcpwm.line[7]:1       |                   |                       |                  | scb[0].spi_select3:1 |

| P1.7     | ctb0.oa1.inp_alt | tcpwm.line_compl[7]:1 |                   |                       |                  |                      |

| P2.0     | sarmux.0         | tcpwm.line[4]:1       |                   |                       | scb[1].i2c_scl:1 | scb[1].spi_mosi:2    |

| P2.1     | sarmux.1         | tcpwm.line_compl[4]:1 |                   |                       | scb[1].i2c_sda:1 | scb[1].spi_miso:2    |

| P2.2     | sarmux.2         | tcpwm.line[5]:1       |                   |                       |                  | scb[1].spi_clk:2     |

| P2.3     | sarmux.3         | tcpwm.line_compl[5]:1 |                   |                       |                  | scb[1].spi_select0:2 |

| P2.4     | sarmux.4         | tcpwm.line[0]:1       |                   |                       |                  | scb[1].spi_select1:1 |

| P2.5     | sarmux.5         | tcpwm.line_compl[0]:1 |                   |                       |                  | scb[1].spi_select2:1 |

| P2.6     | sarmux.6         | tcpwm.line[1]:1       |                   |                       |                  | scb[1].spi_select3:1 |

# PSoC® 4: PSoC 4200M Family Datasheet

| Port/Pin | Analog           | Alt. Function 1       | Alt. Function 2   | Alt. Function 3       | Alt. Function 4  | Alt. Function 5      |

|----------|------------------|-----------------------|-------------------|-----------------------|------------------|----------------------|

| P2.7     | sarmux.7         | tcpwm.line_compl[1]:1 |                   |                       |                  | scb[3].spi_select0:1 |

| P6.0     |                  | tcpwm.line[4]:0       | scb[3].uart_rx:0  | can[0].can_tx_enb_n:0 | scb[3].i2c_scl:0 | scb[3].spi_mosi:0    |

| P6.1     |                  | tcpwm.line_compl[4]:0 | scb[3].uart_tx:0  | can[0].can_rx:0       | scb[3].i2c_sda:0 | scb[3].spi_miso:0    |

| P6.2     |                  | tcpwm.line[5]:0       | scb[3].uart_cts:0 | can[0].can_tx:0       |                  | scb[3].spi_clk:0     |

| P6.3     |                  | tcpwm.line_compl[5]:0 | scb[3].uart_rts:0 |                       |                  | scb[3].spi_select0:0 |

| P6.4     |                  | tcpwm.line[6]:0       |                   |                       |                  | scb[3].spi_select1:0 |

| P6.5     |                  | tcpwm.line_compl[6]:0 |                   |                       |                  | scb[3].spi_select2:0 |

| P3.0     |                  | tcpwm.line[0]:0       | scb[1].uart_rx:1  |                       | scb[1].i2c_scl:2 | scb[1].spi_mosi:0    |

| P3.1     |                  | tcpwm.line_compl[0]:0 | scb[1].uart_tx:1  |                       | scb[1].i2c_sda:2 | scb[1].spi_miso:0    |

| P3.2     |                  | tcpwm.line[1]:0       | scb[1].uart_cts:1 |                       | swd_data         | scb[1].spi_clk:0     |

| P3.3     |                  | tcpwm.line_compl[1]:0 | scb[1].uart_rts:1 |                       | swd_clk          | scb[1].spi_select0:0 |

| P3.4     |                  | tcpwm.line[2]:0       |                   |                       |                  | scb[1].spi_select1:0 |

| P3.5     |                  | tcpwm.line_compl[2]:0 |                   |                       |                  | scb[1].spi_select2:0 |

| P3.6     |                  | tcpwm.line[3]:0       |                   |                       |                  | scb[1].spi_select3:0 |

| P3.7     |                  | tcpwm.line_compl[3]:0 |                   |                       |                  |                      |

| P4.0     |                  |                       | scb[0].uart_rx:0  | can[0].can_rx:1       | scb[0].i2c_scl:1 | scb[0].spi_mosi:0    |

| P4.1     |                  |                       | scb[0].uart_tx:0  | can[0].can_tx:1       | scb[0].i2c_sda:1 | scb[0].spi_miso:0    |

| P4.2     | csd[0].c_mod     |                       | scb[0].uart_cts:0 | can[0].can_tx_enb_n:1 | lpcomp.comp[0]:0 | scb[0].spi_clk:0     |

| P4.3     | csd[0].c_sh_tank |                       | scb[0].uart_rts:0 |                       | lpcomp.comp[1]:0 | scb[0].spi_select0:0 |

| P4.4     |                  |                       |                   | can[1].can_tx_enb_n:1 |                  | scb[0].spi_select1:2 |

| P4.5     |                  |                       |                   | can[1].can_rx:1       |                  | scb[0].spi_select2:2 |

| P4.6     |                  |                       |                   | can[1].can_tx:1       |                  | scb[0].spi_select3:2 |

| P4.7     |                  |                       |                   |                       |                  |                      |

| P7.0     |                  | tcpwm.line[0]:2       | scb[3].uart_rx:1  |                       | scb[3].i2c_scl:1 | scb[3].spi_mosi:1    |

| P7.1     |                  | tcpwm.line_compl[0]:2 | scb[3].uart_tx:1  |                       | scb[3].i2c_sda:1 | scb[3].spi_miso:1    |

| P7.2     |                  | tcpwm.line[1]:2       | scb[3].uart_cts:1 |                       |                  | scb[3].spi_clk:1     |

#### Descriptions of the power pin functions are as follows:

**VDDD**: Power supply for both analog and digital sections (where there is no  $V_{DDA}$  pin).

$\textbf{VDDA}\!:$  Analog  $V_{DD}$  pin where package pins allow; shorted to  $V_{DDD}$  otherwise.

VDDIO: I/O pin power domain.

VSSA: Analog ground pin where package pins allow; shorted to VSS otherwise

VSS: Ground pin.

**VCCD**: Regulated Digital supply (1.8 V ±5%).

Port Pins can all be used as LCD Commons, LCD Segment drivers, or CSD sense and shield pins can be connected to AMUXBUS A or B or can all be used as GPIO pins that can be driven by firmware or DSI signals.

#### **Power**

The supply voltage range is 1.71 to 5.5 V with all functions and circuits operating over that range.

The PSoC 4200M family allows two distinct modes of power supply operation: Unregulated External Supply and Regulated External Supply modes.

#### **Unregulated External Supply**

In this mode, the PSoC 4200M is powered by an External Power Supply that can be anywhere in the range of 1.8 to 5.5 V. This range is also designed for battery-powered operation, for instance, the chip can be powered from a battery system that starts at 3.5V and works down to 1.8 V. In this mode, the internal regulator of the PSoC 4200M supplies the internal logic and the VCCD output of the PSoC 4200M must be bypassed to ground via an external Capacitor (in the range of 1 to 1.6  $\mu F;\, X5R$  ceramic or better).

VDDA and VDDD must be shorted together on the PC board; the grounds, VSSA and VSS must also be shorted together. Bypass capacitors must be used from VDDD and VDDA to ground, typical practice for systems in this frequency range is to use a capacitor in the 1  $\mu F$  range in parallel with a smaller capacitor (0.1  $\mu F$ , for example). Note that these are simply rules of thumb and that, for critical applications, the PCB layout, lead inductance, and the Bypass capacitor parasitic should be simulated to design and obtain optimal bypassing.

| Power Supply            | Bypass Capacitors                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------|

| VDDD-VSS and VDDIO-VSS  | 0.1 μF ceramic at each pin plus bulk capacitor 1 to 10 μF.                                                |

| VDDA-VSSA               | 0.1 μF ceramic at pin. Additional 1 μF to 10 μF bulk capacitor                                            |

| VCCD-VSS                | 1 μF ceramic capacitor at the VCCD pin                                                                    |

| VREF-VSSA<br>(optional) | The internal bandgap may be bypassed with a 1 $\mu$ F to 10 $\mu$ F capacitor for better ADC performance. |

#### **Regulated External Supply**

In this mode, the PSoC 4200M is powered by an external power supply that must be within the range of 1.71 to 1.89 V (1.8  $\pm$ 5%); note that this range needs to include power supply ripple. In this mode, VCCD, VDDA, VDDIO, and VDDD pins are all shorted together and bypassed. The internal regulator is disabled in firmware.

# PSoC® 4: PSoC 4200M Family Datasheet

## **Development Support**

The PSoC 4200M family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit <a href="https://www.cypress.com/go/psoc4">www.cypress.com/go/psoc4</a> to find out more.

#### **Documentation**

A suite of documentation supports the PSoC 4200M family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes**: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

#### Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

#### Tools

With industry standard cores, programming, and debugging interfaces, the PSoC 4200M family is part of a development tool ecosystem. Visit us at <a href="https://www.cypress.com/go/psoccreator">www.cypress.com/go/psoccreator</a> for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## **Electrical Specifications**

## **Absolute Maximum Ratings**

Table 1. Absolute Maximum Ratings<sup>[1]</sup>

| Spec ID# | Parameter                    | Description                                                           | Min  | Тур | Max                      | Units | Details/<br>Conditions |

|----------|------------------------------|-----------------------------------------------------------------------|------|-----|--------------------------|-------|------------------------|

| SID1     | V <sub>DD_ABS</sub>          | Analog or digital supply relative to $V_{SS}$ ( $V_{SSD} = V_{SSA}$ ) | -0.5 | _   | 6                        | V     | Absolute maximum       |

| SID2     | V <sub>CCD_ABS</sub>         | Direct digital core voltage input relative to V <sub>SSD</sub>        | -0.5 | _   | 1.95                     | V     | Absolute maximum       |

| SID3     | V <sub>GPIO_ABS</sub>        | GPIO voltage; V <sub>DDD</sub> or V <sub>DDA</sub>                    | -0.5 | _   | V <sub>DD</sub> +0.<br>5 | V     | Absolute maximum       |

| SID4     | I <sub>GPIO_ABS</sub>        | Current per GPIO                                                      | -25  | _   | 25                       | mA    | Absolute maximum       |

| SID5     | I <sub>G-PIO_injection</sub> | GPIO injection current per pin                                        | -0.5 | _   | 0.5                      | mA    | Absolute maximum       |

| BID44    | ESD_HBM                      | Electrostatic discharge human body model                              | 2200 | _   | _                        | V     |                        |

| BID45    | ESD_CDM                      | Electrostatic discharge charged device model                          | 500  | -   | _                        | V     |                        |

| BID46    | LU                           | Pin current for latch-up                                              | -140 | _   | 140                      | mA    |                        |

#### **Device Level Specifications**

All specifications are valid for -40 °C  $\leq$  TA  $\leq$  85 °C and TJ  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

Table 2. DC Specifications

| Spec Id#   | Parameter         | Description                                                                         | Min  | Тур  | Max  | Units | Details / Conditions                      |

|------------|-------------------|-------------------------------------------------------------------------------------|------|------|------|-------|-------------------------------------------|

| SID53      | $V_{DDD}$         | Power supply input voltage (V <sub>DDA</sub> = V <sub>DDD</sub> = V <sub>DD</sub> ) | 1.8  | _    | 5.5  | V     | With regulator enabled                    |

| SID255     | $V_{DDD}$         | Power supply input voltage unregulated                                              | 1.71 | 1.8  | 1.89 | V     | Internally unregulated Supply             |

| SID54      | $V_{CCD}$         | Output voltage (for core logic)                                                     | _    | 1.8  | _    | V     |                                           |

| SID55      | C <sub>EFC</sub>  | External regulator voltage bypass                                                   | 1    | 1.3  | 1.6  | μF    | X5R ceramic or better                     |

| SID56      | C <sub>EXC</sub>  | Power supply decoupling capacitor                                                   | _    | 1    | -    | μF    | X5R ceramic or better                     |

| Active Mod | le                |                                                                                     |      | •    | •    |       |                                           |

| SID6       | I <sub>DD1</sub>  | Execute from flash; CPU at 6 MHz                                                    | _    | 2.2  | 2.8  | mA    |                                           |

| SID7       | I <sub>DD2</sub>  | Execute from flash; CPU at 12 MHz                                                   | _    | 3.7  | 4.2  | mA    |                                           |

| SID8       | I <sub>DD3</sub>  | Execute from flash; CPU at 24 MHz                                                   | _    | 6.7  | 7.2  | mA    |                                           |

| SID9       | I <sub>DD4</sub>  | Execute from flash; CPU at 48 MHz                                                   | _    | 13   | 13.8 | mA    |                                           |

| Sleep Mod  | e                 |                                                                                     |      |      |      |       |                                           |

| SID21      | I <sub>DD16</sub> | I <sup>2</sup> C wakeup, WDT, and comparators on. Regulator off.                    | _    | 1.75 | 2.1  | mA    | V <sub>DD</sub> = 1.71 to 1.89,<br>6 MHz  |

| SID22      | I <sub>DD17</sub> | I <sup>2</sup> C wakeup, WDT, and comparators on.                                   | _    | 1.7  | 2.1  | mA    | V <sub>DD</sub> = 1.8 to 5.5,<br>6 MHz    |

| SID23      | I <sub>DD18</sub> | I <sup>2</sup> C wakeup, WDT, and comparators on.<br>Regulator off.                 | _    | 2.35 | 2.8  | mA    | V <sub>DD</sub> = 1.71 to 1.89,<br>12 MHz |

#### Note

Document Number: 001-93963 Rev. \*D Page 16 of 41

Usage above the absolute maximum conditions listed in Table 1 may cause permanent damage to the device. Exposure to absolute maximum conditions for extended

periods of time may affect device reliability. The maximum storage temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature

Storage Life. When used below absolute maximum conditions but above normal operating conditions, the device may not operate to specification.

Table 2. DC Specifications

| Spec Id#    | Parameter          | Description                                        | Min | Тур  | Max  | Units | Details / Conditions                                        |

|-------------|--------------------|----------------------------------------------------|-----|------|------|-------|-------------------------------------------------------------|

| SID24       | I <sub>DD19</sub>  | I <sup>2</sup> C wakeup, WDT, and comparators on.  | -   | 2.25 | 2.8  | mA    | V <sub>DD</sub> = 1.8 to 5.5,<br>12 MHz                     |

| Deep Sleep  | Mode, -40 °C to    | + 60 °C                                            |     |      |      |       |                                                             |

| SID30       | I <sub>DD25</sub>  | I <sup>2</sup> C wakeup and WDT on. Regulator off. | _   | 1.55 | 20   | μA    | V <sub>DD</sub> = 1.71 to 1.89                              |

| SID31       | I <sub>DD26</sub>  | I <sup>2</sup> C wakeup and WDT on.                | _   | 1.35 | 15   | μΑ    | $V_{DD}$ = 1.8 to 3.6                                       |

| SID32       | I <sub>DD27</sub>  | I <sup>2</sup> C wakeup and WDT on.                | _   | 1.5  | 15   | μA    | V <sub>DD</sub> = 3.6 to 5.5                                |

| Deep Sleep  | Mode, +85 °C       |                                                    |     | •    | •    | •     |                                                             |

| SID33       | I <sub>DD28</sub>  | I <sup>2</sup> C wakeup and WDT on. Regulator off. | _   | _    | 60   | μA    | $V_{DD}$ = 1.71 to 1.89                                     |

| SID34       | I <sub>DD29</sub>  | I <sup>2</sup> C wakeup and WDT on.                | _   | _    | 45   | μΑ    | $V_{DD} = 1.8 \text{ to } 3.6$                              |

| SID35       | I <sub>DD30</sub>  | I <sup>2</sup> C wakeup and WDT on.                | _   | _    | 30   | μΑ    | V <sub>DD</sub> = 3.6 to 5.5                                |

| Hibernate I | Mode, -40 °C to +  | 60 °C                                              |     |      |      | ı     | 1                                                           |

| SID39       | I <sub>DD34</sub>  | Regulator off                                      | _   | 150  | 3000 | nA    | V <sub>DD</sub> = 1.71 to 1.89                              |

| SID40       | I <sub>DD35</sub>  |                                                    | _   | 150  | 1000 | nA    | $V_{DD} = 1.8 \text{ to } 3.6$                              |

| SID41       | I <sub>DD36</sub>  |                                                    | _   | 150  | 1100 | nA    | $V_{DD} = 3.6 \text{ to } 5.5$                              |

| Hibernate I | Mode, +85 °C       |                                                    |     |      |      | ı     | 1                                                           |

| SID42       | I <sub>DD37</sub>  | Regulator off.                                     | _   | _    | 4500 | nA    | V <sub>DD</sub> = 1.71 to 1.89                              |

| SID43       | I <sub>DD38</sub>  |                                                    | _   | _    | 3500 | nA    | $V_{DD} = 1.8 \text{ to } 3.6$                              |

| SID44       | I <sub>DD39</sub>  |                                                    | _   | _    | 3500 | nA    | V <sub>DD</sub> = 3.6 to 5.5                                |

| Stop Mode   |                    |                                                    |     |      |      | ı     | 1                                                           |

| SID304      | I <sub>DD43A</sub> | Stop Mode current;<br>V <sub>DD</sub> = 3.6 V      | _   | 35   | 85   | nA    | $T = -40 ^{\circ}\text{C} \text{ to } +60 ^{\circ}\text{C}$ |

| SID304A     | I <sub>DD43B</sub> | Stop Mode current;<br>V <sub>DD</sub> = 3.6 V      | _   | _    | 1450 | nA    | T = +85 °C                                                  |

| XRES curre  | ent                | ·                                                  |     |      |      | 1     | •                                                           |

| SID307      | I <sub>DD_XR</sub> | Supply current while XRES (Active Low) asserted    |     | 2    | 5    | mA    |                                                             |

Table 3. AC Specifications

| Spec ID# | Parameter               | Description                 | Min | Тур | Max | Units | Details/<br>Conditions                           |

|----------|-------------------------|-----------------------------|-----|-----|-----|-------|--------------------------------------------------|

| SID48    | F <sub>CPU</sub>        | CPU frequency               | DC  | _   | 48  | MHz   | $1.71 \leq V_{DD} \leq 5.5$                      |

| SID49    | T <sub>SLEEP</sub>      | Wakeup from sleep mode      | _   | 0   | _   | μs    | Guaranteed by characterization                   |

| SID50    | T <sub>DEEPSLEEP</sub>  | Wakeup from Deep Sleep mode | _   | _   | 25  | μs    | 24 MHz IMO.<br>Guaranteed by<br>characterization |

| SID51    | T <sub>HIBERNATE</sub>  | Wakeup from Hibernate mode  | _   | _   | 0.7 | ms    | Guaranteed by characterization                   |

| SID51A   | T <sub>STOP</sub>       | Wakeup from Stop mode       | _   | _   | 2   | ms    | Guaranteed by characterization                   |

| SID52    | T <sub>RESETWIDTH</sub> | External reset pulse width  | 1   | _   | _   | μs    | Guaranteed by characterization                   |

**GPIO**

Table 4. GPIO DC Specifications

| Spec ID# | Parameter                      | Description                                               | Min                       | Тур | Max                       | Units | Details/<br>Conditions                                                |

|----------|--------------------------------|-----------------------------------------------------------|---------------------------|-----|---------------------------|-------|-----------------------------------------------------------------------|

| SID57    | V <sub>IH</sub> <sup>[2]</sup> | Input voltage high threshold                              | 0.7 ×<br>V <sub>DDD</sub> | _   | -                         | V     | CMOS Input                                                            |

| SID57A   | IIHS                           | Input current when Pad > V <sub>DDIO</sub> for OVT inputs | _                         | _   | 10                        | μΑ    | Per I <sup>2</sup> C Spec                                             |

| SID58    | V <sub>IL</sub>                | Input voltage low threshold                               | _                         | _   | 0.3 ×<br>V <sub>DDD</sub> | V     | CMOS Input                                                            |

| SID241   | V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> < 2.7 V                     | 0.7×<br>V <sub>DDD</sub>  | _   | -                         | V     |                                                                       |

| SID242   | V <sub>IL</sub>                | LVTTL input, V <sub>DDD</sub> < 2.7 V                     | -                         | _   | 0.3 ×<br>V <sub>DDD</sub> | V     |                                                                       |

| SID243   | V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V                     | 2.0                       | _   | -                         | V     |                                                                       |

| SID244   | V <sub>IL</sub>                | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V                     | _                         | _   | 8.0                       | V     |                                                                       |

| SID59    | V <sub>OH</sub>                | Output voltage high level                                 | V <sub>DDD</sub><br>-0.6  | _   | _                         | V     | I <sub>OH</sub> =4 mA at 3 V<br>V <sub>DDD</sub>                      |

| SID60    | V <sub>OH</sub>                | Output voltage high level                                 | V <sub>DDD</sub><br>-0.5  | _   | _                         | V     | I <sub>OH</sub> = 1 mA at<br>1.8 V V <sub>DDD</sub>                   |

| SID61    | V <sub>OL</sub>                | Output voltage low level                                  | _                         | _   | 0.6                       | V     | I <sub>OL</sub> = 4 mA at<br>1.8 V V <sub>DDD</sub>                   |

| SID62    | V <sub>OL</sub>                | Output voltage low level                                  | -                         | _   | 0.6                       | V     | I <sub>OL</sub> = 8 mA at 3 V<br>V <sub>DDD</sub>                     |

| SID62A   | V <sub>OL</sub>                | Output voltage low level                                  | -                         | _   | 0.4                       | V     | I <sub>OL</sub> = 3 mA at 3 V<br>V <sub>DDD</sub>                     |

| SID63    | R <sub>PULLUP</sub>            | Pull-up resistor                                          | 3.5                       | 5.6 | 8.5                       | kΩ    |                                                                       |

| SID64    | R <sub>PULLDOWN</sub>          | Pull-down resistor                                        | 3.5                       | 5.6 | 8.5                       | kΩ    |                                                                       |

| SID65    | I <sub>IL</sub>                | Input leakage current (absolute value)                    | -                         | _   | 2                         | nA    | 25 °C, V <sub>DDD</sub> = 3.0 V.<br>Guaranteed by<br>Characterization |

| SID65A   | I <sub>IL_CTBM</sub>           | Input leakage current (absolute value) for CTBM pins      | -                         | _   | 4                         | nA    | Guaranteed by Characterization                                        |

| SID66    | C <sub>IN</sub>                | Input capacitance                                         | _                         | _   | 7                         | pF    |                                                                       |

Note

2. V<sub>IH</sub> must not exceed V<sub>DDD</sub> + 0.2 V.

Table 4. GPIO DC Specifications

| Spec ID# | Parameter             | Description                                              | Min                        | Тур | Max | Units | Details/<br>Conditions         |

|----------|-----------------------|----------------------------------------------------------|----------------------------|-----|-----|-------|--------------------------------|

| SID67    | V <sub>HYSTTL</sub>   | Input hysteresis LVTTL                                   | 25                         | 40  | _   | mV    | $V_{DDD} \ge 2.7 \text{ V}$    |

| SID68    | V <sub>HYSCMOS</sub>  | Input hysteresis CMOS                                    | 0.05 ×<br>V <sub>DDD</sub> | _   | _   | mV    |                                |

| SID69    | I <sub>DIODE</sub>    | Current through protection diode to V <sub>DD</sub> /Vss | _                          | _   | 100 | μA    | Guaranteed by characterization |

| SID69A   | I <sub>TOT_GPIO</sub> | Maximum Total Source or Sink Chip<br>Current             | -                          | _   | 200 | mA    | Guaranteed by characterization |

#### Table 5. GPIO AC Specifications

(Guaranteed by Characterization)[3]

| Spec ID# | Parameter            | Description                                                                    | Min | Тур | Max  | Units | Details/<br>Conditions                     |

|----------|----------------------|--------------------------------------------------------------------------------|-----|-----|------|-------|--------------------------------------------|

| SID70    | T <sub>RISEF</sub>   | Rise time in fast strong mode                                                  | 2   | _   | 12   | ns    | 3.3 V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID71    | T <sub>FALLF</sub>   | Fall time in fast strong mode                                                  | 2   | _   | 12   | ns    | 3.3 V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID72    | T <sub>RISES</sub>   | Rise time in slow strong mode                                                  | 10  | _   | 60   | ns    | 3.3 V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID73    | T <sub>FALLS</sub>   | Fall time in slow strong mode                                                  | 10  | _   | 60   | ns    | 3.3 V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID74    | F <sub>GPIOUT1</sub> | GPIO Fout;3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V. Fast strong mode.        | -   | -   | 33   | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID75    | F <sub>GPIOUT2</sub> | GPIO Fout;1.7 $V \le V_{DDD} \le 3.3 \text{ V. Fast}$ strong mode.             | -   | -   | 16.7 | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID76    | F <sub>GPIOUT3</sub> | GPIO Fout;3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V. Slow strong mode.        | -   | -   | 7    | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID245   | F <sub>GPIOUT4</sub> | GPIO Fout;1.7 V $\leq$ V <sub>DDD</sub> $\leq$ 3.3 V. Slow strong mode.        | -   | -   | 3.5  | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID246   | F <sub>GPIOIN</sub>  | GPIO input operating frequency;<br>1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V | -   | _   | 48   | MHz   | 90/10% V <sub>IO</sub>                     |

## XRES

## Table 6. XRES DC Specifications

| Spec ID# | Parameter            | Description                                                           | Min                       | Тур | Max                       | Units | Details/<br>Conditions         |

|----------|----------------------|-----------------------------------------------------------------------|---------------------------|-----|---------------------------|-------|--------------------------------|

| SID77    | V <sub>IH</sub>      | Input voltage high threshold                                          | 0.7 ×<br>V <sub>DDD</sub> | _   | -                         | V     | CMOS Input                     |

| SID78    | V <sub>IL</sub>      | Input voltage low threshold                                           | -                         | _   | 0.3 ×<br>V <sub>DDD</sub> | V     | CMOS Input                     |

| SID79    | R <sub>PULLUP</sub>  | Pull-up resistor                                                      | 3.5                       | 5.6 | 8.5                       | kΩ    |                                |

| SID80    | C <sub>IN</sub>      | Input capacitance                                                     | -                         | 3   | -                         | pF    |                                |

| SID81    | V <sub>HYSXRES</sub> | Input voltage hysteresis                                              | -                         | 100 | -                         | mV    | Guaranteed by characterization |

| SID82    | I <sub>DIODE</sub>   | Current through protection diode to V <sub>DDD</sub> /V <sub>SS</sub> | -                         | _   | 100                       | μA    | Guaranteed by characterization |

Document Number: 001-93963 Rev. \*D Page 19 of 41

Note

3. Simultaneous switching transitions on many fully-loaded GPIO pins may cause ground perturbations depending on several factors including PCB and decoupling capacitor design. For applications that are very sensitive to ground perturbations, the slower GPIO slew rate setting may be used.

Table 7. XRES AC Specifications

| Spec ID# | Parameter               | Description       | Min | Тур | Max | Units | Details/<br>Conditions         |

|----------|-------------------------|-------------------|-----|-----|-----|-------|--------------------------------|

| SID83    | T <sub>RESETWIDTH</sub> | Reset pulse width | 1   | 1   | 1   | μs    | Guaranteed by characterization |

## **Analog Peripherals**

Opamp

## **Table 8. Opamp Specifications**

(Guaranteed by Characterization)

| Spec ID# | Parameter                | Description                                    | Min   | Тур  | Max           | Units | Details/<br>Conditions                      |

|----------|--------------------------|------------------------------------------------|-------|------|---------------|-------|---------------------------------------------|

|          | I <sub>DD</sub>          | Opamp block current. No load.                  | _     | -    | -             | _     |                                             |

| SID269   | I <sub>DD_HI</sub>       | Power = high                                   | _     | 1100 | 1850          | μA    |                                             |

| SID270   | I <sub>DD_MED</sub>      | Power = medium                                 | _     | 550  | 950           | μA    |                                             |

| SID271   | I <sub>DD_LOW</sub>      | Power = low                                    | _     | 150  | 350           | μA    |                                             |

|          | GBW                      | Load = 20 pF, 0.1 mA. V <sub>DDA</sub> = 2.7 V | _     | -    | _             | _     |                                             |

| SID272   | GBW_HI                   | Power = high                                   | 6     | -    | _             | MHz   |                                             |

| SID273   | GBW_MED                  | Power = medium                                 | 4     | -    | _             | MHz   |                                             |

| SID274   | GBW_LO                   | Power = low                                    | _     | 1    | _             | MHz   |                                             |

|          | I <sub>OUT_MAX</sub>     | V <sub>DDA</sub> ≥ 2.7 V, 500 mV from rail     | _     | -    | _             | _     |                                             |

| SID275   | I <sub>OUT_MAX_HI</sub>  | Power = high                                   | 10    | -    | _             | mA    |                                             |

| SID276   | I <sub>OUT_MAX_MID</sub> | Power = medium                                 | 10    | -    | _             | mA    |                                             |

| SID277   | I <sub>OUT MAX LO</sub>  | Power = low                                    | _     | 5    | _             | mA    |                                             |

|          | I <sub>OUT</sub>         | V <sub>DDA</sub> = 1.71 V, 500 mV from rail    | _     | -    | _             | _     |                                             |

| SID278   | I <sub>OUT_MAX_HI</sub>  | Power = high                                   | 4     | -    | _             | mA    |                                             |

| SID279   | I <sub>OUT_MAX_MID</sub> | Power = medium                                 | 4     | -    | _             | mA    |                                             |

| SID280   | I <sub>OUT_MAX_LO</sub>  | Power = low                                    | _     | 2    | _             | mA    |                                             |

| SID281   | V <sub>IN</sub>          | Input voltage range                            | -0.05 | _    | VDDA<br>- 0.2 | V     | Charge-pump on, $V_{DDA} \ge 2.7 \text{ V}$ |

| SID282   | V <sub>CM</sub>          | Input common mode voltage                      | -0.05 | _    | VDDA<br>- 0.2 | V     | Charge-pump on, $V_{DDA} \ge 2.7 \text{ V}$ |

|          | V <sub>OUT</sub>         | $V_{DDA} \ge 2.7 \text{ V}$                    | _     | -    | _             |       |                                             |

| SID283   | V <sub>OUT_1</sub>       | Power = high, Iload=10 mA                      | 0.5   | _    | VDDA<br>- 0.5 | V     |                                             |

| SID284   | V <sub>OUT_2</sub>       | Power = high, Iload=1 mA                       | 0.2   | _    | VDDA<br>- 0.2 | V     |                                             |

| SID285   | V <sub>OUT_3</sub>       | Power = medium, Iload=1 mA                     | 0.2   | _    | VDDA<br>- 0.2 | V     |                                             |

| SID286   | V <sub>OUT_4</sub>       | Power = low, Iload=0.1mA                       | 0.2   | _    | VDDA<br>- 0.2 | V     |                                             |

| SID288   | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | 1     | ±0.5 | 1             | mV    | High mode                                   |

| SID288A  | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | -     | ±1   | _             | mV    | Medium mode                                 |

| SID288B  | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | _     | ±2   | _             | mV    | Low mode                                    |

| SID290   | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | -10   | ±3   | 10            | μV/C  | High mode                                   |

| SID290A  | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | _     | ±10  | _             | μV/C  | Medium mode                                 |

| SID290B  | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | _     | ±10  | _             | μV/C  | Low mode                                    |

**Table 8. Opamp Specifications**

(Guaranteed by Characterization) (continued)

| Spec ID#   | Parameter        | Description                                                                                                      | Min | Тур  | Max | Units   | Details/<br>Conditions                                        |

|------------|------------------|------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------|---------------------------------------------------------------|

| SID291     | CMRR             | DC Common mode rejection ratio.<br>High-power mode. Common Model<br>voltage range from 0.5 V to VDDA -<br>0.5 V. | 60  | 70   | _   | dB      | V <sub>DDD</sub> = 3.6 V                                      |

| SID292     | PSRR             | At 1 kHz, 100 mV ripple                                                                                          | 70  | 85   | _   | dB      | V <sub>DDD</sub> = 3.6 V                                      |

|            | Noise            |                                                                                                                  | _   | -    | _   | _       |                                                               |

| SID293     | V <sub>N1</sub>  | Input referred, 1 Hz - 1GHz, power = high                                                                        | _   | 94   | _   | μVrms   |                                                               |

| SID294     | V <sub>N2</sub>  | Input referred, 1 kHz, power = high                                                                              | _   | 72   | _   | nV/rtHz |                                                               |