# Multiple Supply Hot Swap Controller with I<sup>2</sup>C Compatible Monitoring

# **FEATURES**

- Allows Safe Insertion into Live CompactPCI<sup>™</sup> or PCI Express<sup>™</sup> Backplane

- 8-Bit ADC Monitors Current and Voltage

- I<sup>2</sup>C<sup>TM</sup>/SMBus Interface

- dl/dt Controlled Soft Start

- Simultaneous or Sequenced Turn-On

- ±20V Absolute Maximum Rating for ±12V Supplies

- No External Gate Capacitor Required

- Dual-Level Circuit Breaker and Current Limit

- Bus Precharge Output

- Power Good Input with Timeout

- Optional Latchoff or Autoretry After Faults

- Alerts Host After Faults

- Integrated LOCAL\_PCI\_RST# Logic

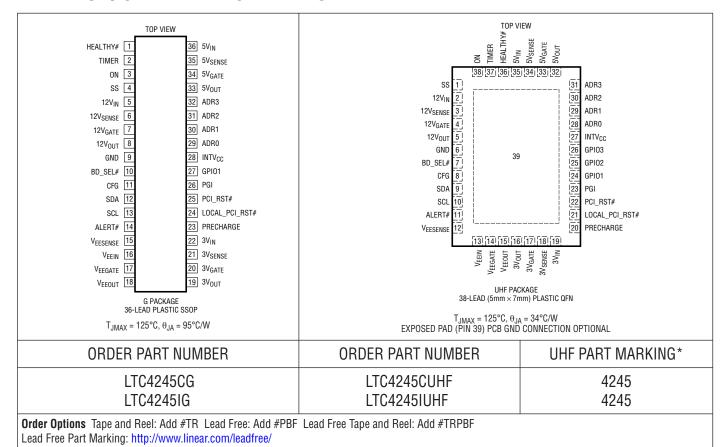

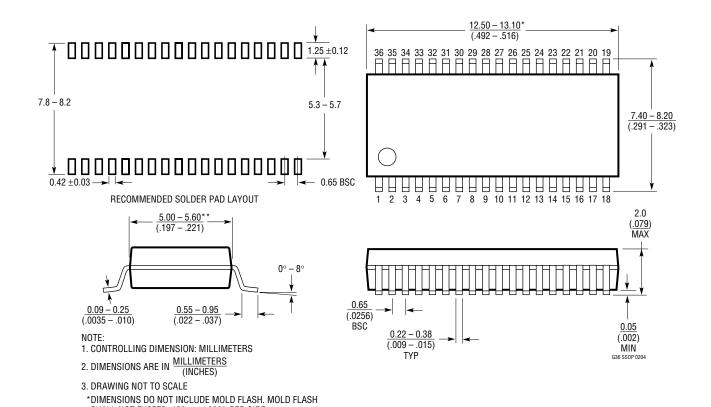

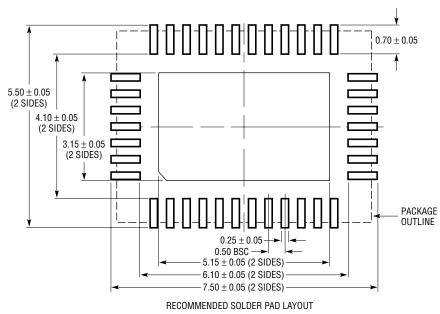

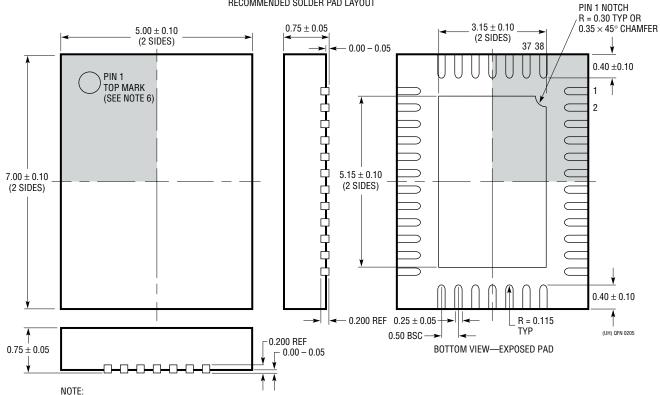

- 36-Pin SSOP and 38-Pin (5mm × 7mm) QFN Packages

# **APPLICATIONS**

- Live Board Insertion

- CompactPCI, CompactPCI Express, CompactTCA, PCI Express Systems

# DESCRIPTION

The LTC®4245 Hot Swap™ controller allows a board to be safely inserted and removed from a live backplane in multiple supply systems such as CompactPCI and PCI Express. Using four external N-channel pass transistors, the board supply voltages can be ramped up at an adjustable rate and in any desired sequence. An I<sup>2</sup>C interface and onboard ADC allow monitoring of board current, voltage and fault status for each supply.

The device features adjustable dl/dt controlled soft start and foldback limited inrush current. A dual-level timed circuit breaker and fast current limit protect each supply against overcurrent faults. A power good input with timeout allows a downstream supply monitor to disconnect the board supplies. The device can be configured to function without a –12V supply or with an extra 3.3V supply instead of a 5V supply.

The controller has additional features to interrupt the host when a fault has occurred, notify when output power is good, detect insertion of a load card and power-up in either the on or off state.

(T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

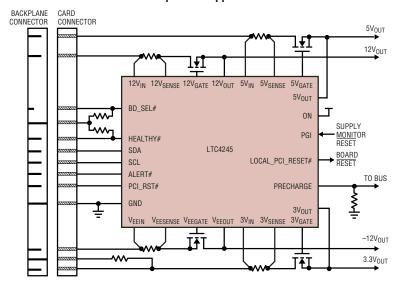

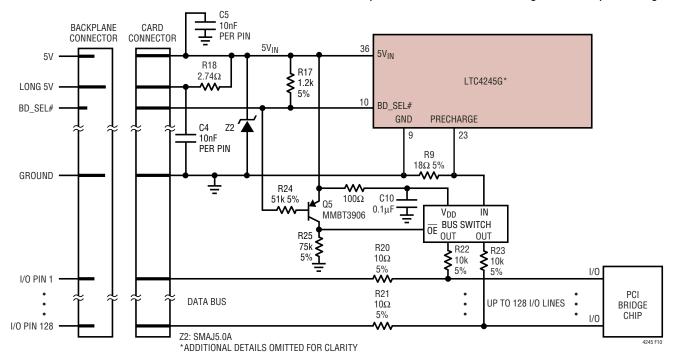

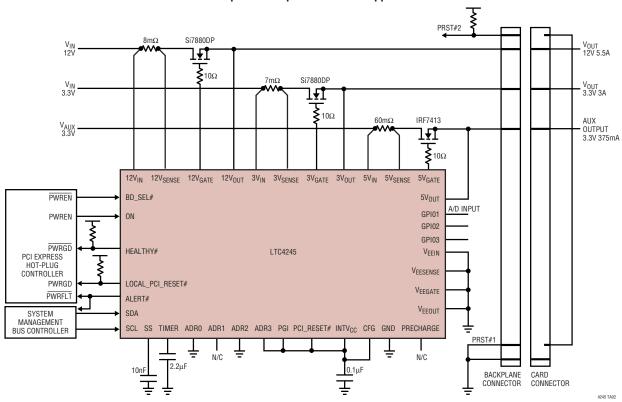

# TYPICAL APPLICATION

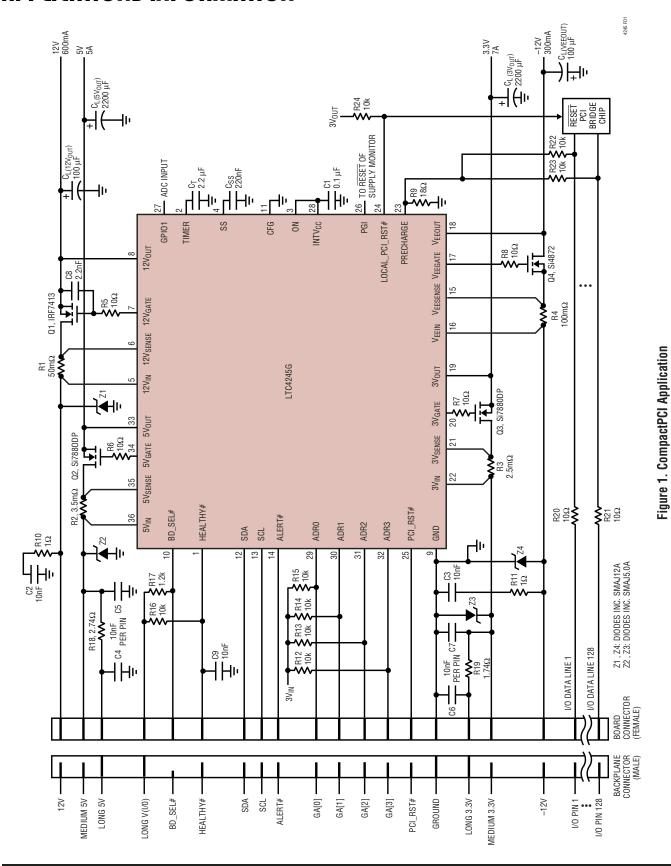

#### **CompactPCI Application**

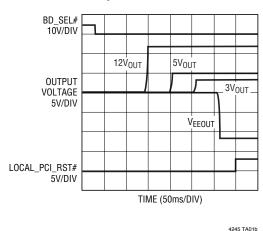

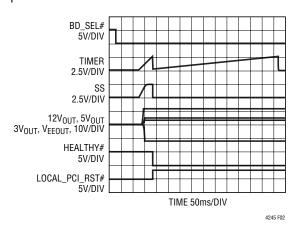

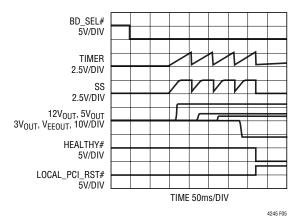

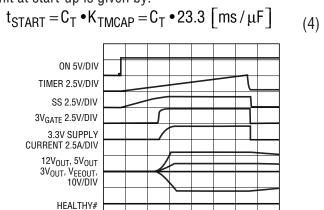

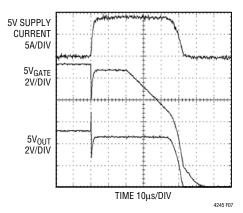

#### **Sequenced Turn-On Waveform**

# **ABSOLUTE MAXIMUM RATINGS**

| (Notes 1, 2)                                                      |

|-------------------------------------------------------------------|

| Supply Voltages                                                   |

| 12V <sub>IN</sub> –0.3V to 20V                                    |

| 5V <sub>IN</sub> , 3V <sub>IN</sub> –0.3V to 10V                  |

| V <sub>EEIN</sub> –20V to 0.3V                                    |

| INTV <sub>CC</sub> –0.3V to 6.5V                                  |

| Input Voltages                                                    |

| BD_SEL#, ON, PGI0.3V to 12V                                       |

| ADR0-3, CFG, SS, TIMER $-0.3V$ to INTV <sub>CC</sub> + $0.3V$     |

| PCI_RST#, SCL, SDA0.3V to 6.5V                                    |

| Output Voltages                                                   |

| ALERT#, GPIO1-3, HEALTHY#,                                        |

| LOCAL_PCI_RST# –0.3V to 6.5V                                      |

| Analog Voltages (n is 5V, 3V)                                     |

| 12V <sub>GATE</sub> –0.3V to 25V                                  |

| $n_{\text{GATE}}$ (Note 3)0.3V to 12V <sub>IN</sub> + 0.3V or 14V |

|                                                                   |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

TECHNOLOGY TECHNOLOGY

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>12VIN</sub> = 12V, V<sub>5VIN</sub> = 5V, V<sub>3VIN</sub> = 3.3V, V<sub>VEEIN</sub> = -12V, unless otherwise noted.

| SYMBOL                                       | PARAMETER                                                                                                            | CONDITIONS                                                                                                                                                                                                                                                         |   | MIN                                        | TYP                                            | MAX                                    | UNITS                            |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------|------------------------------------------------|----------------------------------------|----------------------------------|

| Supplies                                     |                                                                                                                      |                                                                                                                                                                                                                                                                    |   | 1                                          |                                                |                                        |                                  |

| I <sub>DD</sub>                              | Input Supply Current                                                                                                 | 12V <sub>IN</sub><br>5V <sub>IN</sub><br>3V <sub>IN</sub> , PRECHARGE Open<br>V <sub>EEIN</sub>                                                                                                                                                                    | • |                                            | 3<br>0.5<br>0.6<br>–0.5                        | 5<br>1<br>1<br>–1                      | mA<br>mA<br>mA<br>mA             |

| V <sub>UVL</sub>                             | Supply Undervoltage Lockout                                                                                          | $\begin{array}{l} 12V_{IN} \\ 5V_{IN}, V_{CFG} = 0V, \text{ Open} \\ 5V_{IN} \text{ When } V_{CFG} = V_{CC}, 3V_{IN} \\ V_{EEIN}, V_{CFG} = 0V \\ V_{CC} \text{ Falling} \end{array}$                                                                              | • | 10.2<br>4.25<br>2.7<br>–10.2<br>3.4        | 10.5<br>4.38<br>2.8<br>–10.5<br>3.8            | 10.8<br>4.5<br>2.9<br>–10.8<br>4.2     | V<br>V<br>V<br>V                 |

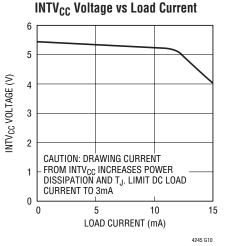

| V <sub>CC</sub>                              | Internal Regulator Voltage                                                                                           |                                                                                                                                                                                                                                                                    | • | 5                                          | 5.5                                            | 6                                      | V                                |

| Current Limit                                |                                                                                                                      |                                                                                                                                                                                                                                                                    |   |                                            |                                                |                                        |                                  |

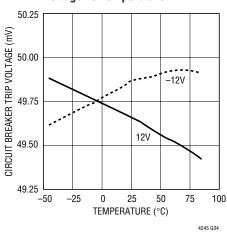

| ΔV <sub>SNS(CB)</sub>                        | Circuit Breaker Trip Sense Voltage (V12VIN - V12VSENSE) (V5VIN - V5VSENSE) (V3VIN - V3VSENSE) (VVEESENSE - VVEEIN)   | After Start-Up                                                                                                                                                                                                                                                     | • | 45<br>22.5<br>22.5<br>40                   | 50<br>25<br>25<br>50                           | 55<br>27.5<br>27.5<br>60               | mV<br>mV<br>mV                   |

| ΔV <sub>SNS(ACL)</sub>                       | Active Current Limit Sense Voltage (V12VIN - V12VSENSE) (V5VIN - V5VSENSE) (V3VIN - V3VSENSE) (VVEESENSE - VVEEIN)   | After Start-Up                                                                                                                                                                                                                                                     | • | 130<br>60<br>60<br>130                     | 150<br>75<br>75<br>150                         | 170<br>90<br>90<br>170                 | mV<br>mV<br>mV                   |

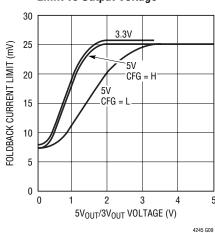

| $\Delta V_{SNS(FBL)}, \ \Delta V_{SNS(FBH)}$ | Foldback Current Limit Sense Voltage (V12VIN - V12VSENSE) (V5VIN - V5VSENSE) (V3VIN - V3VSENSE) (VVEESENSE - VVEEIN) | Start-Up, V <sub>TIMER</sub> = 0V<br>V <sub>12VOUT</sub> = 0V<br>V <sub>12VOUT</sub> = 12V<br>V <sub>5VOUT</sub> = 0V<br>V <sub>5VOUT</sub> = 5V<br>V <sub>3VOUT</sub> = 0V<br>V <sub>3VOUT</sub> = 3.3V<br>V <sub>VEEOUT</sub> = 0V<br>V <sub>VEEOUT</sub> = -12V | • | 10<br>40<br>4<br>22<br>4<br>22<br>11<br>40 | 15<br>50<br>7.5<br>25<br>7.5<br>25<br>16<br>50 | 20<br>60<br>11<br>29<br>11<br>29<br>21 | mV<br>mV<br>mV<br>mV<br>mV<br>mV |

| Gate Drive                                   |                                                                                                                      |                                                                                                                                                                                                                                                                    |   |                                            |                                                |                                        |                                  |

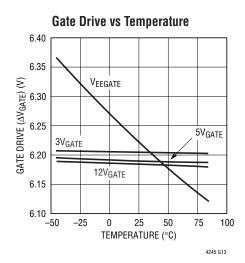

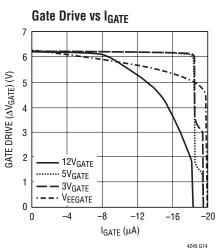

| $\Delta V_{GATE}$                            | Gate Drive                                                                                                           | Gate to Source                                                                                                                                                                                                                                                     | • | 5                                          | 6.2                                            | 7.5                                    | V                                |

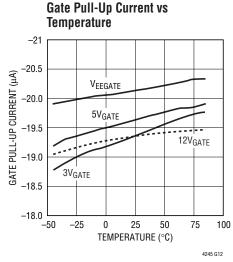

| I <sub>GATE(UP)</sub>                        | Gate Pull-Up Current                                                                                                 | Gate Drive On, $\Delta V_{GATE} = 0V$                                                                                                                                                                                                                              | • | -16                                        | -20                                            | -24                                    | μΑ                               |

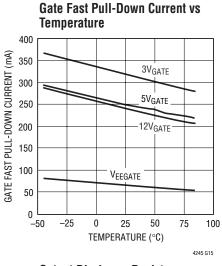

| I <sub>GATE(DN)</sub>                        | Gate Pull-Down Current<br>12V <sub>GATE</sub> , 5V <sub>GATE</sub> , 3V <sub>GATE</sub> ,<br>V <sub>EEGATE</sub>     | Gate Drive Off, $\Delta V_{GATE} = 5V$<br>$V_{OUT} = V_{IN}$<br>$V_{VEEGATE} = -7V$                                                                                                                                                                                | • | 0.9<br>1.7                                 | 1.3<br>3.5                                     | 1.7<br>5.3                             | mA<br>mA                         |

| I <sub>GATE(FST)</sub>                       | Gate Fast Pull-Down Current 12V <sub>GATE</sub> , 5V <sub>GATE</sub> 3V <sub>GATE</sub> V <sub>EEGATE</sub>          | Fast Turn Off, $\Delta V_{GATE} = 5V$<br>$V_{12VGATE} = 17V$ , $V_{5VGATE} = 10V$<br>$V_{3VGATE} = 8.3V$<br>$V_{VEEGATE} = -7V$                                                                                                                                    | • | 125<br>155<br>32                           | 250<br>310<br>65                               | 375<br>465<br>98                       | mA<br>mA<br>mA                   |

| Input/Output Pins                            |                                                                                                                      |                                                                                                                                                                                                                                                                    |   |                                            |                                                |                                        |                                  |

| V <sub>ON, BD_SEL#(TH)</sub>                 | ON, BD_SEL# Pin Threshold Voltage                                                                                    | V <sub>ON</sub> Rising, V <sub>BD_SEL#</sub> Rising                                                                                                                                                                                                                | • | 1.21                                       | 1.235                                          | 1.26                                   | V                                |

| $\Delta V_{ON, BD\_SEL\#(HYST)}$             | ON, BD_SEL# Pin Hysteresis                                                                                           |                                                                                                                                                                                                                                                                    | • | 70                                         | 120                                            | 170                                    | mV                               |

| I <sub>BD_SEL#(UP)</sub>                     | BD_SEL# Pull-Up Current                                                                                              | $V_{BD\_SEL\#} = 0V$                                                                                                                                                                                                                                               | • | <b>-</b> 7                                 | -10                                            | -16                                    | μА                               |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>12VIN</sub> = 12V, V<sub>5VIN</sub> = 5V, V<sub>3VIN</sub> = 3.3V, V<sub>VEEIN</sub> = -12V, unless otherwise noted.

| SYMBOL                  | PARAMETER                                                                                                           | CONDITIONS                                                                                                                                                                                           |   | MIN                         | TYP                          | MAX                          | UNITS                    |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------|------------------------------|------------------------------|--------------------------|

| V <sub>PB(TH)</sub>     | Power Bad Threshold Voltage                                                                                         | 12V <sub>OUT</sub><br>5V <sub>OUT</sub> , V <sub>CFG</sub> = 0V, Open<br>5V <sub>OUT</sub> When V <sub>CFG</sub> = V <sub>CC</sub> , 3V <sub>OUT</sub><br>V <sub>EEOUT</sub> , V <sub>CFG</sub> = 0V | • | 10.8<br>4.5<br>2.8<br>–10.8 | 11.1<br>4.63<br>2.9<br>–11.1 | 11.4<br>4.75<br>3.0<br>–11.4 | V<br>V<br>V              |

| V <sub>IN(TH)</sub>     | Logic Input Threshold                                                                                               | PGI, PCI_RST#, GPIOn<br>SDA, SCL                                                                                                                                                                     | • | 0.8<br>1.6                  | 1.0<br>1.8                   | 1.2<br>2.0                   | V                        |

| I <sub>IN</sub>         | Pin Input Current                                                                                                   | ON, PGI, PCI_RST#, V = 1.2V<br>SDA, SCL, ALERT#, GPIO <i>n</i> , HEALTHY#,<br>LOCAL_PCI_RST#, V = 6V                                                                                                 | • |                             | 0                            | ±1                           | μА                       |

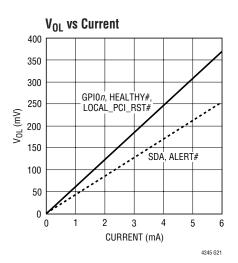

| V <sub>OL</sub>         | Output Low Voltage                                                                                                  | SDA, ALERT#, I = 5mA; GPIO <i>n</i> ,<br>HEALTHY#, LOCAL_PCI_RST#, I = 3mA                                                                                                                           | • |                             | 0.2                          | 0.4                          | V                        |

| $V_{TRI(H)}$            | ADR2, ADR3, CFG Input High Threshold                                                                                |                                                                                                                                                                                                      | • | V <sub>CC</sub> -0.8        | V <sub>CC</sub> -0.4         | V <sub>CC</sub> -0.2         | V                        |

| $\overline{V_{TRI(L)}}$ | ADR <i>n</i> , CFG Input Low Threshold                                                                              |                                                                                                                                                                                                      | • | 0.2                         | 0.4                          | 0.8                          | V                        |

| I <sub>TRI(IN,HL)</sub> | ADR2, ADR3, CFG High, Low Input<br>Current                                                                          | V = 0V, V <sub>CC</sub>                                                                                                                                                                              | • |                             |                              | ±80                          | μА                       |

| I <sub>TRI(IN,Z)</sub>  | ADR2, ADR3, CFG High Z Input Current                                                                                | $V = 0.8V, V_{CC} - 0.8V$                                                                                                                                                                            | • | ±10                         |                              |                              | μА                       |

| I <sub>ADR01(IN)</sub>  | ADR0, ADR1 Input Current                                                                                            | V <sub>ADR0</sub> , V <sub>ADR1</sub> = 0V, V <sub>CC</sub>                                                                                                                                          | • | -30                         |                              | 1                            | μΑ                       |

| I <sub>SENSE</sub>      | Sense Pin Input Current<br>12V <sub>SENSE</sub> , 5V <sub>SENSE</sub> , 3V <sub>SENSE</sub><br>V <sub>EESENSE</sub> | After Start-Up V <sub>SENSE</sub> = V <sub>IN</sub> V <sub>VEESENSE</sub> = -12V                                                                                                                     | • |                             | 0.3<br>-30                   | 1<br>-45                     | μ <b>Α</b><br>μ <b>Α</b> |

| I <sub>OUT(ON)</sub>    | OUT Pin Input Current                                                                                               | $egin{array}{lll} V_{12VOUT} = 12V, \ V_{ON} = 2V \\ V_{5VOUT} = 5V, \ V_{ON} = 2V \\ V_{3VOUT} = 3.3V, \ V_{ON} = 2V \\ V_{VEEOUT} = -12V, \ V_{ON} = 2V \\ \end{array}$                            | • |                             | 200<br>275<br>75<br>–200     | 280<br>390<br>105<br>–280    | μΑ<br>μΑ<br>μΑ<br>μΑ     |

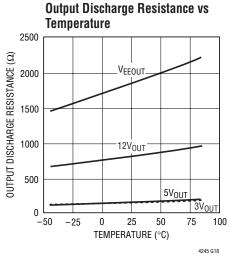

| R <sub>OUT(DIS)</sub>   | OUT Pin Discharge Resistance                                                                                        | $V_{12VOUT} = 6V, V_{ON} = 0V$<br>$V_{5VOUT} = 3V, V_{ON} = 0V$<br>$V_{3VOUT} = 2V, V_{ON} = 0V$<br>$V_{VEEOUT} = -6V, V_{ON} = 0V$                                                                  | • | 650<br>125<br>130<br>1300   | 1000<br>180<br>190<br>1800   | 1800<br>325<br>340<br>3200   | Ω<br>Ω<br>Ω              |

| I <sub>VEEOUT(UP)</sub> | V <sub>EEOUT</sub> Pull-Up Current                                                                                  | V <sub>VEEOUT</sub> = 0V                                                                                                                                                                             | • |                             | -36                          | -54                          | μΑ                       |

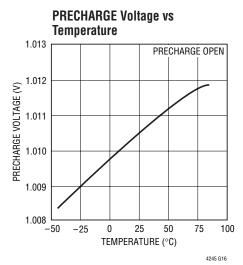

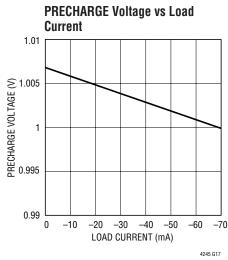

| $\overline{V_{PXG}}$    | PRECHARGE Voltage                                                                                                   | I <sub>PRECHARGE</sub> = Open, -70mA (Note 6)                                                                                                                                                        | • | 0.95                        | 1                            | 1.05                         | V                        |

| Timer, Soft-Star        | t                                                                                                                   |                                                                                                                                                                                                      |   |                             |                              |                              |                          |

| V <sub>TIMER(H)</sub>   | TIMER Pin High Threshold                                                                                            | V <sub>TIMER</sub> Rising                                                                                                                                                                            | • | 2.5                         | 2.56                         | 2.62                         | V                        |

| V <sub>TIMER(L)</sub>   | TIMER Pin Low Threshold                                                                                             | V <sub>TIMER</sub> Falling                                                                                                                                                                           | • | 0.1                         | 0.23                         | 0.4                          | V                        |

| I <sub>TIMER</sub>      | TIMER Pin Pull-Up Current                                                                                           | During Start-Up, V <sub>TIMER</sub> = 0V<br>During PGI Timeout, V <sub>TIMER</sub> = 0V<br>During Auto-Retry, V <sub>TIMER</sub> = 0V                                                                | • | -80<br>-8<br>-1.5           | -100<br>-10<br>-2            | -120<br>-12<br>-2.5          | μΑ<br>μΑ<br>μΑ           |

| K <sub>TMRATIO</sub>    | TIMER Pin Current Ratio                                                                                             | (ITIMER(RTRY)/ITIMER(START))                                                                                                                                                                         | • | 1.6                         | 2                            | 2.7                          | %                        |

| K <sub>TMCAP</sub>      | Start-Up Time per TIMER Capacitance                                                                                 | ((V <sub>TIMER(H)</sub> – V <sub>TIMER(L)</sub> )/I <sub>TIMER(START)</sub> )                                                                                                                        | • | 20                          | 23.3                         | 26                           | ms/μF                    |

| I <sub>SS</sub>         | SS Pin Pull-Up Current                                                                                              | Fast Ramp, V <sub>SS</sub> = 0V<br>Slow Ramp, V <sub>SS</sub> = 2V                                                                                                                                   | • | −16<br>−1.5                 | -20<br>-2                    | -24<br>-2.5                  | μ <b>Α</b><br>μ <b>Α</b> |

| R <sub>TS(DIS)</sub>    | TIMER, SS Discharge Resistance                                                                                      | V <sub>TIMER</sub> = 1.2V, V <sub>SS</sub> = 1.2V                                                                                                                                                    | • |                             | 225                          | 400                          | Ω                        |

| G <sub>SS</sub>         | Gain from SS Pin to Foldback Current Limit ( $\Delta V_{SNS(FB)}/\Delta V_{SS}$ )                                   | 12V <sub>IN</sub> , V <sub>EEIN</sub> 5V <sub>IN</sub> , 3V <sub>IN</sub>                                                                                                                            |   |                             | 46<br>23                     |                              | mV/V<br>mV/V             |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_{12VIN} = 12V$ , $V_{5VIN} = 5V$ , $V_{3VIN} = 3.3V$ , $V_{VEEIN} = -12V$ , unless otherwise noted.

| SYMBOL                         | PARAMETER                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS                                                                                                                                                                                                                                                                                                  |   | MIN                                                               | TYP                                                                    | MAX                                                              | UNITS                             |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------|

| ADC                            |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                             |   |                                                                   |                                                                        |                                                                  |                                   |

| RES                            | Resolution (No Missing Codes)                                                                                                                                                                                                                                                                                                                                                  | (Note 7)                                                                                                                                                                                                                                                                                                    | • | 8                                                                 |                                                                        |                                                                  | Bits                              |

| V <sub>FS</sub>                | Full-Scale Voltage (V <sub>FS</sub> = 255LSB) 12V <sub>IN</sub> , 12V <sub>OUT</sub> 12V <sub>IN</sub> - 12V <sub>SENSE</sub> , V <sub>EESENSE</sub> - V <sub>EEIN</sub> 5V <sub>IN</sub> , 5V <sub>OUT</sub> 5V <sub>IN</sub> - 5V <sub>SENSE</sub> , 3V <sub>IN</sub> - 3V <sub>SENSE</sub> 3V <sub>IN</sub> , 3V <sub>OUT</sub> V <sub>EEIN</sub> , V <sub>EEOUT</sub> GPIO | (Note 6)<br>V <sub>CFG</sub> = 0V, Open<br>V <sub>CFG</sub> = V <sub>CC</sub>                                                                                                                                                                                                                               | • | 13.744<br>62.47<br>5.5<br>3.75<br>31.24<br>3.75<br>-13.744<br>2.5 | 14.025<br>63.75<br>5.61<br>3.825<br>31.875<br>3.825<br>-14.025<br>2.55 | 14.306<br>65.03<br>5.72<br>3.9<br>32.51<br>3.9<br>-14.306<br>2.6 | V<br>mV<br>V<br>V<br>mV<br>V<br>V |

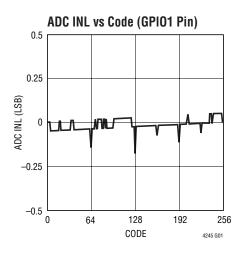

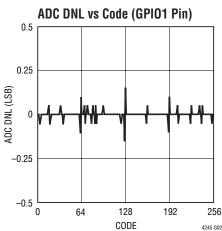

| INL                            | Integral Nonlinearity                                                                                                                                                                                                                                                                                                                                                          | ΔV <sub>SENSE</sub> (Note 8)<br>Other 9 Channels                                                                                                                                                                                                                                                            | • |                                                                   | ±0.5<br>±0.2                                                           | ±2<br>±1.25                                                      | LSB<br>LSB                        |

| OE                             | Offset Error                                                                                                                                                                                                                                                                                                                                                                   | ΔV <sub>SENSE</sub> (Note 6)<br>V <sub>EEIN</sub> , V <sub>EEOUT</sub><br>Other 7 Channels                                                                                                                                                                                                                  | • |                                                                   | ±0.5<br>±0.5<br>±0.3                                                   | ±1.5<br>±1.25<br>±1                                              | LSB<br>LSB<br>LSB                 |

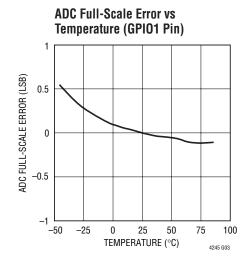

| FSE                            | Full-Scale Error                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                             | • |                                                                   |                                                                        | ±5                                                               | LSB                               |

| TUE                            | Total Unadjusted Error                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                             | • |                                                                   |                                                                        | ±5                                                               | LSB                               |

| t <sub>ADC</sub>               | Conversion Time                                                                                                                                                                                                                                                                                                                                                                | All 13 Channels Once<br>$\Delta V_{SENSE}$ , $V_{EEIN}$ , $V_{EEOUT}$<br>Other 7 Channels                                                                                                                                                                                                                   |   |                                                                   | 665<br>70<br>35                                                        |                                                                  | ms<br>ms<br>ms                    |

| Delays                         | ·                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             |   |                                                                   |                                                                        |                                                                  |                                   |

| $t_D$                          | Turn-On Delay                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             | • | 60                                                                | 100                                                                    | 150                                                              | ms                                |

| t <sub>PLH(GATE)</sub>         | Input High (ON) to Gates High Delay                                                                                                                                                                                                                                                                                                                                            | SS Open                                                                                                                                                                                                                                                                                                     | • |                                                                   | 15                                                                     | 30                                                               | μS                                |

| t <sub>PHL(GATE)</sub>         | Input High (BD_SEL#), Input Low (ON) to Gates Low Propagation Delay                                                                                                                                                                                                                                                                                                            | C <sub>GATE</sub> = 1pF                                                                                                                                                                                                                                                                                     | • |                                                                   | 0.3                                                                    | 1                                                                | μ\$                               |

| t <sub>PHL(UVL)</sub>          | Supply Low to Gates Low Delay                                                                                                                                                                                                                                                                                                                                                  | 12V <sub>IN</sub> , 5V <sub>IN</sub> , 3V <sub>IN</sub> , C <sub>GATE</sub> = 1pF<br>V <sub>EEIN</sub> , C <sub>VEEGATE</sub> = 1pF                                                                                                                                                                         | • | 2.1<br>3.3                                                        | 3.5<br>5.5                                                             | 4.9<br>7.7                                                       | μ\$<br>μ\$                        |

| t <sub>CB</sub>                | Circuit Breaker Filter Delay Time                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             | • | 16                                                                | 22                                                                     | 28                                                               | μS                                |

| t <sub>ACL</sub>               | Active Current Limit Delay                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{l} \Delta V_{12VSENSE} = 300 \text{mV}, \ C_{12VGATE} = 10 \text{nF} \\ \Delta V_{5VSENSE} = 150 \text{mV}, \ C_{5VGATE} = 10 \text{nF} \\ \Delta V_{3VSENSE} = 150 \text{mV}, \ C_{3VGATE} = 10 \text{nF} \\ \Delta V_{VEESENSE} = 300 \text{mV}, \ C_{VEEGATE} = 10 \text{nF} \end{array}$ | • |                                                                   | 0.9<br>0.85<br>0.7<br>2                                                | 2.3<br>2.1<br>1.8<br>5                                           | µՏ<br>µՏ<br>µՏ                    |

| t <sub>PHL(PGI)</sub>          | PGI Low to Gates Low                                                                                                                                                                                                                                                                                                                                                           | C <sub>GATE</sub> = 1pF                                                                                                                                                                                                                                                                                     | • | 12                                                                | 20                                                                     | 28                                                               | μS                                |

| t <sub>PHL(RST)</sub>          | Output Low to LOCAL_PCI_RST# Low                                                                                                                                                                                                                                                                                                                                               | 12V <sub>OUT</sub> , 5V <sub>OUT</sub> , 3V <sub>OUT</sub> , V <sub>PCI_RST#</sub> = 2V<br>V <sub>EEOUT</sub> , V <sub>PCI_RST#</sub> = 2V                                                                                                                                                                  | • | 9<br>10.2                                                         | 15<br>17                                                               | 21<br>23.8                                                       | μS<br>μS                          |

| t <sub>P(RST)</sub>            | PCI_RST# to LOCAL_PCI_RST# Delay                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                             | • |                                                                   | 60                                                                     | 200                                                              | ns                                |

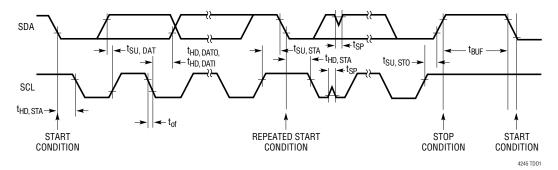

| I <sup>2</sup> C Interface Tin | ning (Note 7)                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             |   |                                                                   |                                                                        |                                                                  |                                   |

| f <sub>SCL(MAX)</sub>          | Maximum SCL Clock Frequency                                                                                                                                                                                                                                                                                                                                                    | Operates with $f_{SCL} \le f_{SCL(MAX)}$                                                                                                                                                                                                                                                                    |   | 400                                                               |                                                                        |                                                                  | kHz                               |

| t <sub>BUF(MIN)</sub>          | Min. Bus Free Time Between Stop/Start                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                             |   |                                                                   | 0.12                                                                   | 1.3                                                              | μS                                |

| t <sub>SU, STA(MIN)</sub>      | Minimum Repeated Start Set-Up Time                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                             |   |                                                                   | 10                                                                     | 600                                                              | ns                                |

| t <sub>HD</sub> , sta(MIN)     | Min. Hold Time After (Repeated) Start                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                             |   |                                                                   | 140                                                                    | 600                                                              | ns                                |

| t <sub>SU, STO(MIN)</sub>      | Minimum Stop Condition Set-Up Time                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                             |   |                                                                   | 10                                                                     | 600                                                              | ns                                |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{12VIN} = 12V$ , $V_{5VIN} = 5V$ , $V_{3VIN} = 3.3V$ , $V_{VEEIN} = -12V$ , unless otherwise noted.

| SYMBOL                     | PARAMETER                            | CONDITIONS | MIN                    | TYP  | MAX | UNITS |

|----------------------------|--------------------------------------|------------|------------------------|------|-----|-------|

| t <sub>SU, DAT(MIN)</sub>  | Minimum Data Set-Up Time Input       |            |                        | 0    | 100 | ns    |

| t <sub>HD, DATI(MIN)</sub> | Minimum Data Hold Time Input         |            |                        | -100 | 0   | ns    |

| t <sub>HD, DATO(MIN)</sub> | Minimum Data Hold Time Output        |            | 300                    | 500  | 900 | ns    |

| t <sub>SP(MAX)</sub>       | Maximum Suppressed Spike Pulse Width |            | 50                     | 110  | 250 | ns    |

| C <sub>X</sub>             | SCL, SDA Input Capacitance           |            |                        | 5    | 10  | pF    |

| t <sub>of</sub>            | Data Output Fall Time                | (Note 9)   | 20 + 0.1C <sub>b</sub> |      | 250 | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

Note 3: The  $5V_{GATE}$  and  $3V_{GATE}$  pins should not be driven beyond the lower of  $12V_{IN}$  + 0.3V and 14V.

**Note 4:** An internal clamp limits the GATE pins to a minimum of 5V above  $V_{OUT}$  ( $V_{EEIN}$  for  $V_{EEGATE}$ ). Driving this pin to voltages beyond the clamp may damage the device.

Note 5: The device pulls up the  $V_{\mbox{\scriptsize EEOUT}}$  pin to 0.6V when pin is in open state.

**Note 6:** UHF package specification limits are identical to G package limits and guaranteed by design and by correlation to wafer test measurements.

Note 7: Guaranteed by design and not subject to test.

**Note 8:** Integral Nonlinearity is defined as the deviation of a code from a precise analog input voltage. Maximum specifications are limited by the LSB step size and the single shot measurement. Typical specifications are measured from 1/4, 1/2, 3/4 areas of the quantization band.

Note 9: C<sub>b</sub> = total capacitance of one bus line in pF.

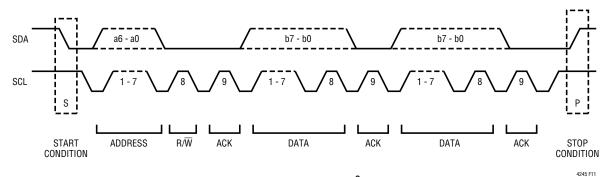

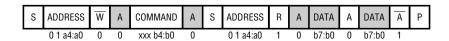

## TIMING DIAGRAM

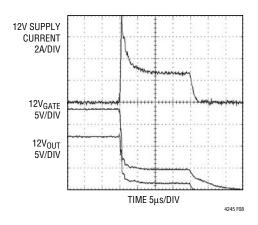

# TYPICAL PERFORMANCE CHARACTERISTICS

12V and -12V Circuit Breaker Trip Voltage vs Temperature

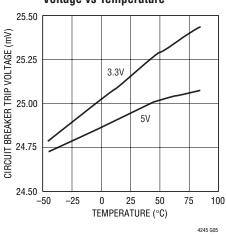

5V and 3.3V Circuit Breaker Trip Voltage vs Temperature

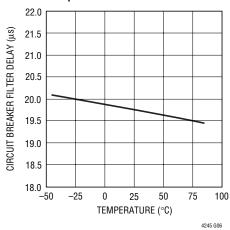

Circuit Breaker Filter Delay vs Temperature

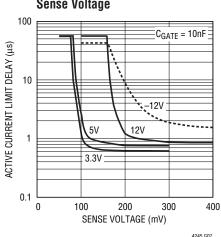

Active Current Limit Delay vs Sense Voltage

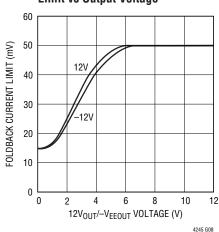

12V and -12V Foldback Current Limit vs Output Voltage

5V and 3.3V Foldback Current Limit vs Output Voltage

# TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

**12V**<sub>GATE</sub>: Gate Drive for 12V Supply External N-Channel MOSFET. An internal  $20\mu$ A current source charges the gate of the external N-channel MOSFET. An internal clamp limits the gate voltage to 6.2V above  $12V_{OUT}$ . During turn-off a 1.3mA pull-down current discharges  $12V_{GATE}$  to ground. During short-circuit a 250mA pull-down current between  $12V_{GATE}$  and  $12V_{OUT}$  is activated.

**12V**<sub>IN</sub>: 12V Supply, Current Sense and ADC Input. The internal low voltage supply  $V_{CC}$  is generated from  $12V_{IN}$ . An undervoltage lockout circuit, with 38mV hysteresis, prevents any external MOSFET from turning on when this pin is below 10.5V.

**12V**<sub>OUT</sub>: 12V Gate Drive Return; Foldback, ADC and Power Bad Input. Connect this pin to the source of the 12V supply external N-channel MOSFET switch for gate drive return. Power is considered bad if this pin drops below 11.1V. The comparator on this pin has a built-in hysteresis of 40mV. This pin is also an input to the ADC and the current limit foldback circuit. A  $1000\Omega$  active pull-down discharges  $12V_{OUT}$  to ground when the external MOSFET is turned off.

**12V**<sub>SENSE</sub>: 12V Supply Current Sense and ADC Input. Connect this pin to the output of the 12V current sense resistor. The current limit circuit controls the  $12V_{GATE}$  pin to limit the sense voltage between the  $12V_{IN}$  and  $12V_{SENSE}$  pins to 50mV or less during start-up and 150mV thereafter. During start-up a foldback feature reduces the current limit to 15mV as the  $12V_{OUT}$  pin approaches ground. A circuit breaker, enabled after start-up, trips when the sense voltage exceeds 50mV for  $22\mu s$ . To disable current limit, connect this pin to  $12V_{IN}$ .

$3V_{GATE}$ : Gate Drive for 3.3V Supply External N-Channel MOSFET. An internal  $20\mu$ A current source charges the gate of the external N-channel MOSFET. An internal clamp limits the gate voltage to 6.2V above  $3V_{OUT}$ . During turn-off a 1.3mA pull-down current discharges  $3V_{GATE}$  to ground. During short-circuit a 310mA pull-down current between  $3V_{GATE}$  and  $3V_{OLIT}$  is activated.

$3V_{IN}$ : 3.3V Supply, Current Sense and ADC Input. The 1V precharge circuit draws its power and reference voltage from  $3V_{IN}$ . An undervoltage lockout circuit, with 10mV hysteresis, prevents any external MOSFET from turning on when this pin is below 2.8V.

**3V<sub>OUT</sub>:** 3.3V Gate Drive Return; Foldback, ADC and Power Bad Input. Connect this pin to the source of the 3.3V supply external N-channel MOSFET switch for gate drive return. Power is considered bad if this pin drops below 2.9V. The comparator on this pin has a built-in hysteresis of 11mV. This pin is also an input to the ADC and the current limit foldback circuit. A 190 $\Omega$  active pull-down discharges  $3V_{OUT}$  to ground when the external MOSFET is turned off.

**3V<sub>SENSE</sub>**: 3.3V Supply Current Sense and ADC Input. Connect this pin to the output of the 3.3V current sense resistor. The current limit circuit controls the  $3V_{GATE}$  pin to limit the sense voltage between the  $3V_{IN}$  and  $3V_{SENSE}$  pins to 25mV or less during start-up and 75mV thereafter. During start-up a foldback feature reduces the current limit to 7.5mV as the  $3V_{OUT}$  pin approaches ground. A circuit breaker, enabled after start-up, trips when the sense voltage exceeds 25mV for  $22\mu s$ . To disable current limit, connect this pin to  $3V_{IN}$ .

**5V**<sub>GATE</sub>: Gate Drive for 5V Supply External N-Channel MOSFET. An internal 20μA current source charges the gate of the external N-channel MOSFET. An internal clamp limits the gate voltage to 6.2V above  $5V_{OUT}$ . During turn-off a 1.3mA pull-down current discharges  $5V_{GATE}$  to ground. During short-circuit a 250mA pull-down current between  $5V_{GATE}$  and  $5V_{OUT}$  is activated.

**5V**<sub>IN</sub>: 5V Supply, Current Sense and ADC Input. An undervoltage lockout circuit, with 16mV or 10mV of hysteresis, prevents any external MOSFET from turning on when this pin is below 4.38V or 2.8V depending on the state of the CFG pin.

## PIN FUNCTIONS

**5V<sub>OUT</sub>:** 5V Gate Drive Return; Foldback, ADC and Power Bad Input. Connect this pin to the source of the 5V supply external N-channel MOSFET switch for gate drive return. Power is considered bad if this pin drops below 4.63V or 2.9V depending on the CFG pin. The comparator on this pin has a built-in hysteresis of 17mV or 11mV. This pin is also an input to the ADC and the current limit foldback circuit. A  $180\Omega$  active pull-down discharges  $5V_{OUT}$  to ground when the external MOSFET is turned off.

**5V**<sub>SENSE</sub>: 5V Supply Current Sense and ADC Input. Connect this pin to the output of the 5V current sense resistor. The current limit circuit controls the  $5V_{GATE}$  pin to limit the sense voltage between the  $5V_{IN}$  and  $5V_{SENSE}$  pins to 25mV or less during start-up and 75mV thereafter. During start-up a foldback feature reduces the current limit to 7.5mV as the  $5V_{OUT}$  pin approaches ground. A circuit breaker, enabled after start-up, trips when the sense voltage exceeds 25mV for  $22\mu s$ . To disable current limit, connect this pin to  $5V_{IN}$ .

**ADR0 to ADR3:** Serial Bus Address Inputs. ADR0 and ADR1 are two-state inputs; ADR2 and ADR3 are three-state inputs. Tying these pins to ground, open or INTV<sub>CC</sub> configures one of 32 possible addresses. The addressing scheme is compatible with the CompactPCI geographic addressing for slot identification. See Table 5 in Applications Information.

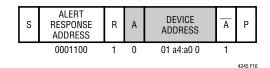

**ALERT#:** Fault Alert Output. Open-drain logic output that can be pulled to ground, when a fault occurs, to alert the host controller. A fault alert is enabled by the ALERT register. This device is compatible with SMBus alert protocol. See Applications Information. Tie to ground if unused.

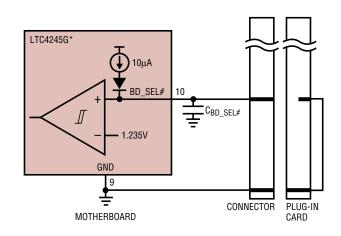

**BD\_SEL#:** Board Present Input. Ground this pin to enable the N-channel MOSFETs to turn on. When this pin is high, the MOSFETs are off. An internal  $10\mu$ A current source pulls up this pin to INTV<sub>CC</sub>. Transitions on this pin will be recorded in the FAULT2 register. A high-to-low transition activates the logic to read the state of the ON pin and clear faults. See Applications Information.

**CFG:** Supply Configuration Three-State Input. When this pin is grounded, all four supply inputs must satisfy their undervoltage lockout levels to allow the external MOSFETs

to turn on. Floating this pin disables  $V_{EE}$  undervoltage lockout and power bad functions, allowing other supplies to turn-on even when -12V supply is absent. Tying this pin to  $INTV_{CC}$  not only disables  $V_{EE}$ , but also converts the  $5V_{IN}$  undervoltage, power bad and ADC levels to 3.3V levels. This allows using an extra 3.3V supply instead of a 5V supply as in a PCI Express application.

**EXPOSED PAD (Pin 39, UHF Package):** Exposed Pad may be left open or connected to device ground.

**GND:** Device Ground.

GPI01 to GPI03 (GPI02, GPI03 on UHF package only): General Purpose Input/Output and ADC Input. Open-drain logic outputs and logic inputs. Any one of the three pins can be multiplexed to the GPIO channel of the internal ADC. GPI01 has a state change fault associated with it. The GPIO register (Table 13) contains status and control bits for these pins.

HEALTHY#: Board Power Status Output. This pin is pulled low by an open-drain output when all supply outputs are above their power bad thresholds and when all external N-channel MOSFETs are on. When any supply output falls below its power bad threshold voltage, this pin will go high after a 15µs deglitching time.

**INTV**<sub>CC</sub>: Internal Low Voltage Supply Decoupling Output. Connect a  $0.1\mu F$  capacitor from this pin to ground. When this pin falls below 3.8V, the internal registers are reset.

**LOCAL\_PCI\_RST#:** Reset Output. This pin is pulled low by an open-drain output whenever HEALTHY# is high or when the PCI\_RST# input is low. Tie to ground if unused.

**ON:** On Control Input. A rising edge turns on the external N-channel MOSFETs and a falling edge turns them off. This pin is also used to configure the state of the FET On control bits (and hence the external FETs) in the ON register. For example, if the ON pin is tied high, then one or all (depending on the Sequence control bit) FET On control bits will go high 100ms after power-up. Likewise if the ON pin is tied low then the part will remain off after power-up until the FET On control bits are set high using the I<sup>2</sup>C bus. If the Sequence control bit is set, taking ON pin high turns on the supplies in a 12V, 5V, 3.3V, -12V sequence. A high-to-low transition on this pin will clear faults.

LINEAR TECHNOLOGY

# PIN FUNCTIONS

**PCI\_RST#**: Reset Input. Pulling this pin low causes LO-CAL\_PCI\_RST# to pull low. When high, LOCAL\_PCI\_RST# is the logical inverse of HEALTHY#. Tie to INTV<sub>CC</sub> if unused.

**PGI:** Power Good Input. Tie this pin to the  $\overline{RESET}$  output of an external supply monitor or power good output of a DC/DC converter. When all supplies have been turned on, a timing cycle is started at the end of which the PGI pin is sampled. If it is low, all external MOSFETs are shut off. If the PGI Disable control bit C3 is not set, pulling this pin low for more than  $20\mu s$  during normal operation will also shut off all MOSFETs. Tie to INTV<sub>CC</sub> if unused.

**PRECHARGE:** Bus Precharge Output. This pin can source 70mA at 1V as soon as  $3V_{\text{IN}}$  is powered-up. Leave it open if unused.

**SCL:** Serial Bus Clock Input. Data at the SDA pin is shifted in or out on rising edges of SCL. This is a high impedance pin that is generally driven by an open-collector output from a master controller.

**SDA:** Serial Bus Data Input and Output. This is a high impedance input when address, command or data bits are shifted in. It is an open-drain output when sending data back to the master controller or acknowledging a write operation. An external pull-up resistor or current source is required.

**SS:** Soft-Start Input. Connect a capacitor between this pin and ground to set the rate of increase of current limit during start-up for dl/dt limited inrush current. When an external MOSFET is turned on, a  $20\mu\text{A}$  pull-up current charges the capacitor. The voltage ramp on the capacitor is converted into an internal current limit increasing linearly with time. Leave it open if dl/dt limited inrush is not required.

**TIMER:** Timer Input. A capacitor between this pin and ground sets the duration of the start-up, PGI and auto-retry timing cycles to be  $23.3 \text{ms/}\mu\text{F}$ ,  $233 \text{ms/}\mu\text{F}$  and  $1.17 \text{s/}\mu\text{F}$  respectively. A timing cycle consists of TIMER being charged to 2.56 V with an internal pull-up current source and then being reset by a switch to ground. The timing cycle ends when TIMER falls below 0.23 V. The start-up, PGI and auto-retry timing cycles use  $100 \mu\text{A}$ ,  $10 \mu\text{A}$  and  $2 \mu\text{A}$  pull-up current sources respectively.

**V**<sub>EEGATE</sub>: Gate Drive for -12V Supply External N-Channel MOSFET. An internal  $20\mu$ A current source charges the gate of the external N-channel MOSFET. An internal clamp limits the gate voltage to 6.2V above V<sub>EEIN</sub>. During turn-off, a 3.5mA pull-down current discharges V<sub>EEGATE</sub> to V<sub>EEIN</sub>. During short-circuit a 65mA pull-down current between V<sub>EEGATE</sub> and V<sub>EEIN</sub> is activated. If a -12V supply is not available, connect V<sub>EEGATE</sub> to ground and use the CFG pin appropriately.

**V**<sub>EEIN</sub>: -12V Supply, Current Sense and ADC Input. An undervoltage lockout circuit, with 38mV hysteresis, prevents any external MOSFET from turning on when this pin is above -10.5V. The V<sub>EEIN</sub> undervoltage lockout can be disabled by using the CFG pin. If a -12V supply is not available, connect V<sub>EEIN</sub> to ground and use the CFG pin appropriately.

**V**<sub>EEOUT</sub>: -12V Supply Foldback, ADC and Power Bad Input. Connect this pin to the drain of the -12V supply external N-channel MOSFET switch. Power is considered bad if this pin rises above -11.1V. The comparator on this pin has a built-in hysteresis of 54mV. The  $V_{EEOUT}$  power bad function can be disabled by using the CFG pin. This pin is also an input to the ADC and the current limit foldback circuit. A  $1800\Omega$  active pull-up discharges  $V_{EEOUT}$  to ground when the external MOSFET is turned off. If a -12V supply is not available, connect  $V_{EEOUT}$  to ground and use the CFG pin appropriately.

**V**<sub>EESENSE</sub>: -12V Supply Current Sense and ADC Input. Connect this pin to the output of the -12V current sense resistor. The current limit circuit controls the V<sub>EEGATE</sub> pin to limit the sense voltage between the V<sub>EESENSE</sub> and V<sub>EEIN</sub> pins to 50mV or less during start-up and 150mV thereafter. During start-up a foldback feature lowers the current limit to 16mV as the V<sub>EEOUT</sub> pin approaches ground. A circuit breaker, enabled after start-up, trips when the sense voltage exceeds 50mV for  $22\mu s$ . To disable current limit, connect this pin to V<sub>EEIN</sub>. If a -12V supply is not available, connect V<sub>EESENSE</sub> to ground and use the CFG pin appropriately.

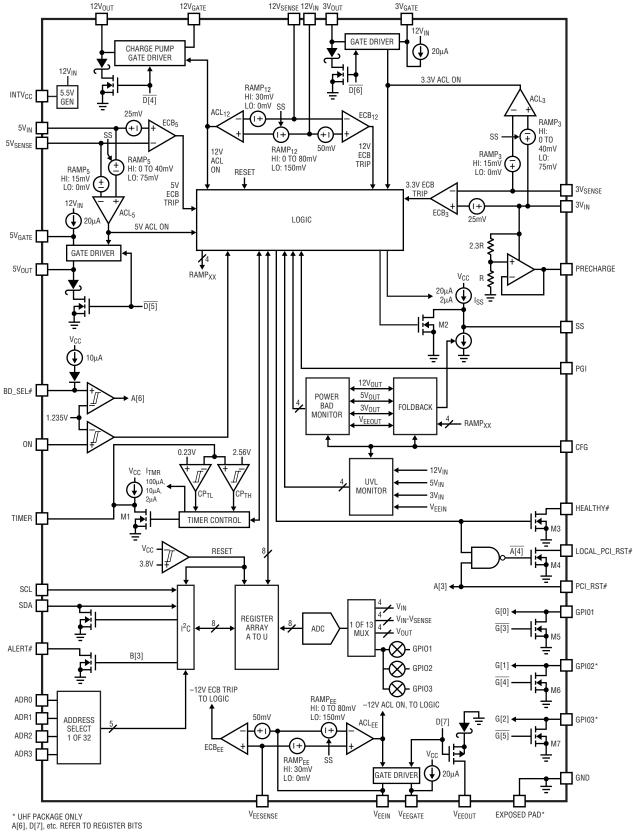

# **BLOCK DIAGRAM**

# **OPERATION**

#### Start-Up

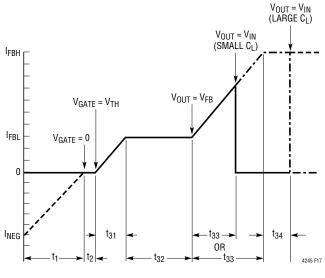

The LTC4245 is designed to turn a board's supply voltages on and off in a controlled manner, allowing the board to be safely inserted or removed from a live backplane slot. When a supply turn-on command is received, current sources start pulling up the TIMER and SS pins. The  $100\mu A I_{TMR}$ current and the external TIMER capacitor determine the time a supply can be in current limit during start-up. The gate of a supply's external N-channel MOSFET is servoed by an amplifer (ACL $_n$ ) so that the current, as indicated by the sense resistor voltage drop, never exceeds an internal current limit. This current limit rises at a rate determined by I<sub>SS</sub> and the capacitor at the SS pin. A foldback circuit determines the maximum value of the current limit and reduces it to 30% of the maximum when a supply's output is shorted to ground. When the TIMER pin crosses 2.56V it is reset to ground and the start-up timing cycle ends. If a supply is still in current limit all gates are turned off, an overcurrent fault is logged and the TIMER goes through a cool-down timing cycle using  $2\mu A$  for  $I_{TMR}$ . Otherwise, its circuit breaker (ECB<sub>n</sub>) is armed and the current limit is raised to 3 times the circuit breaker threshold. The SS pin is then reset by switch M2.

Any combination of the four supplies can be turned on together or one after another. Whenever a supply is ramping up, its output voltage will affect, through the foldback circuit, where the internal current limit ramp stops. The default configuration turns on all supplies together. If sequence control bit C6 (Table 9) is set, the supplies turn on in a 12V, 5V, 3.3V, -12V sequence. With this bit set, the end of a supply ramp-up triggers the start of the next one in the sequence. The  $I^2C$  interface allows independent on and off control for each supply through its On control bit. Turn-off is simultaneous under fault conditions and when using the ON or BD\_SEL# pins.

At the end of the last start-up timing cycle, HEALTHY# is pulled low by M3 if all supply outputs are above their power bad thresholds. LOCAL\_PCI\_RST# which was held low (M4), now follows PCI\_RST#. The TIMER pin goes through a PGI timeout cycle using  $10\mu$ A for I<sub>TMR</sub>. The PGI pin is sampled at the end of the cycle. If it is low, then all external MOSFETs are shut-off, a PGI fault is logged and TIMER goes through a cool-down cycle using  $2\mu$ A

for  $I_{TMR}$ . If PGI is high, the part enters the normal mode of operation.

#### **Normal Operation**

During normal operation, the gates of the MOSFETs are clamped about 6.2V above their sources. The 12V gate driver uses a charge pump, the 5V and 3.3V gate drive is derived from  $12V_{IN}$  and the -12V gate drive from  $INTV_{CC}$ . Each supply is continuously monitored for undervoltage, overcurrent and power bad conditions. Overcurrent monitoring consists of an electronic circuit breaker comparator (ECB<sub>n</sub>) and an active current limit circuit (ACL<sub>n</sub>) set at 3x the ECB threshold. Undervoltage and overcurrent faults cause all MOSFETs to be shut off. A power bad condition causes HEALTHY# to go high impedance and LOCAL\_PCI\_RST# to pull low, without shutting off the MOSFETs. If the PGI pin is not disabled (register bit C3 not set), then PGI pin going low will also shut off all MOSFETs.

#### **ADC**

Included in the LTC4245 is an 8-bit A/D converter. The converter has a 13-input multiplexer to select between input, output and current sense voltage of each supply, and the GPIO channel. The ADC can either cycle through all channels or measure a channel on-demand.

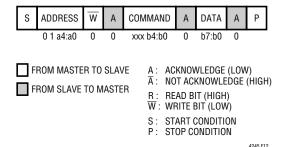

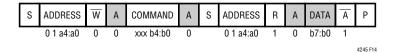

#### Serial Interface

An I<sup>2</sup>C interface is provided to read from or write to the status, control and A/D registers. It allows the host to poll the device and determine if faults have occurred. If the ALERT# line is used as an interrupt, the host can respond to a fault in real time. The LTC4245 I<sup>2</sup>C interface slave address is decoded using the ADR0 to ADR3 pins.

#### Configuration, GPIO and Precharge

The three-state CFG pin can be used to disable the  $V_{EE}$  undervoltage lockout, power bad and foldback functions. It can also convert the 5V undervoltage, power bad and ADC levels to 3.3V levels. The GPIO1 to GPIO3 pins can be used as general purpose inputs or outputs (M5 to M7). One of the pins can also be multiplexed to the GPIO channel of the ADC. A 1V reference voltage derived from  $3V_{IN}$  is provided at the PRECHARGE pin. This can be used to pre-charge I/O lines on the board so as not to corrupt the backplane bus.

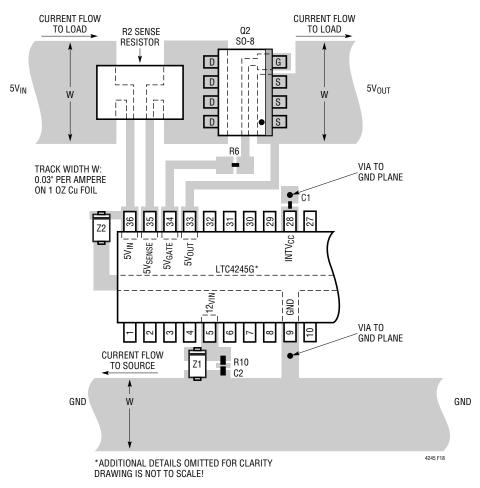

The typical LTC4245 application is in a high availability system where boards using multiple supplies are hot plugged. The device enables the system to periodically monitor board power consumption and fault status over the I<sup>2</sup>C interface. Boards in CompactPCI and PCI Express systems typically utilize three to four supplies. Figure 1 shows the LTC4245 being used in a CompactPCI application.

The following sections describe the turn on, turn off and fault response behavior of the LTC4245. The ADC and I<sup>2</sup>C interface are discussed next. External component selection is discussed in detail in the Design Example section.

#### **CPCI Connection Pin Sequence**

The staggered lengths of the CPCI male connector pins on the backplane ensures that all power supplies are physically connected to the LTC4245 before back-end power is allowed to ramp up (BD\_SEL# asserted low). The long pins, which include 5V, 3.3V, V(I/O) and GND, mate first. The short BD\_SEL# pin mates last. At least one long 3.3V power pin must be connected to the LTC4245 in order for the PRECHARGE pin voltage to be available before the CPCI bus pins mate.

The following is a typical hot plug sequence.

- 1. ESD clips make contact.

- 2. Long power and ground pins make contact and Early Power is established. The 1V precharge voltage becomes valid at this stage. Power is also applied to the pull-up resistors connected to the HEALTHY# and BD\_SEL# signals. LOCAL\_PCI\_RST# is held in reset. All power switches are held off at this stage of insertion.

- 3. Medium length pins make contact. The 12V and -12V connector pins make contact at this stage. The internal low voltage supply of the LTC4245 (INTV<sub>CC</sub>) powers up from the 12V supply. An internal  $10\mu$ A pull-up from INTV<sub>CC</sub> to BD\_SEL# turns on. Other connector pins that mate are HEALTHY#, PCI\_RST# and the bus I/O pins (which are precharged to 1V).

- 4. Short pins make contact. If the BD\_SEL# signal is grounded on the backplane, the plug-in board power-up cycle may begin immediately. If the ON pin

is tied high then turn-on is automatic, else the LTC4245 waits for a serial bus turn-on command. System backplanes that do not ground the BD\_SEL# signal will instead have circuitry that detects when BD\_SEL# makes contact with the plug-in board. The system logic can then control the power up process by pulling BD\_SEL# low. The precharge potential may be optionally disconnected from the CPCI bus signals at this stage.

#### Turn-On

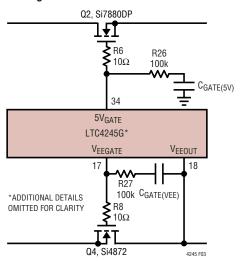

The back-end power planes are isolated from the input power planes by external N-channel pass transistors Q1 through Q4. Sense resistors R1 to R4 provide current fault detection. Resistors R5 to R8 prevent high frequency oscillations in MOSFETs Q1 to Q4 respectively.

The following conditions must be satisfied for a duration of 100ms before the external switches can be turned on.

- 1. All input supplies and the internally generated supply, INTV $_{CC}$ , must exceed their undervoltage lockout thresholds. The  $V_{EE}$  undervoltage lockout can be disabled by not tying the CFG pin low.

- 2. No undervoltage, overcurrent or PGI fault bits must be set unless the corresponding auto-retry is enabled. When  $12V_{IN}$  powers up for the first time,  $INTV_{CC}$  rises above its undervoltage threshold which generates a  $60\mu s$  to  $120\mu s$  internal power-on-reset pulse. During reset, the fault registers are cleared and the control bits are initialized. If  $INTV_{CC}$  is already up, then the  $I^2C$  interface can be used to clear the fault bits or set the auto-retry bits.

- 3. The BD SEL# pin must be pulled low.

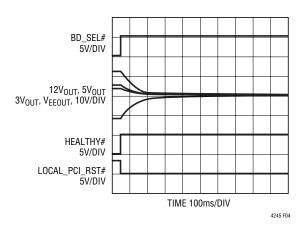

When these initial conditions are satisfied, the ON pin is checked. If it is high, the four FET On control bits (D0 to D3) are set either simultaneously (the default state) or in a 12V, 5V, 3.3V, -12V sequence (register bit C6 set). If ON is low, the external switches turn on when the ON pin is brought high or if a serial bus turn-on command is received. Figure 2 shows all supplies turning on after BD\_SEL# goes low.

When a switch is to be turned on, an internal 100µA current source is connected to the TIMER pin and a 20µA current to SS pin. The gate of each ramping supply's pass transistor is servoed by an internal amplifier, so the supply current never exceeds an internal current limit. This internal current limit starts off with a negative value, which makes the amplifier pull the gate low. The voltage ramp on the SS pin is converted to a current limit rising linearly with time. The amplifier releases the gate as the current limit crosses zero. An internal current source starts charging up the gate. When the gate voltage reaches the MOSFET threshold voltage, the switch begins to turn on. The amplifier once again starts modulating the gate pull-up current so that the sense resistor voltage drop follows the internally set current limit. The rate of rise of the inrush current is given by:

$$\frac{dI_{INRUSH}}{dt} = \frac{G_{SS}}{R_{SENSE}} \cdot \frac{dV_{SS}}{dt}$$

(1)

$$\frac{dV_{SS}}{dt} = \frac{I_{SS}}{C_{SS}} \tag{2}$$