# 16 Watt Digital Input Class-D Audio Amplifier with Speaker Sense Digital Output

# Description

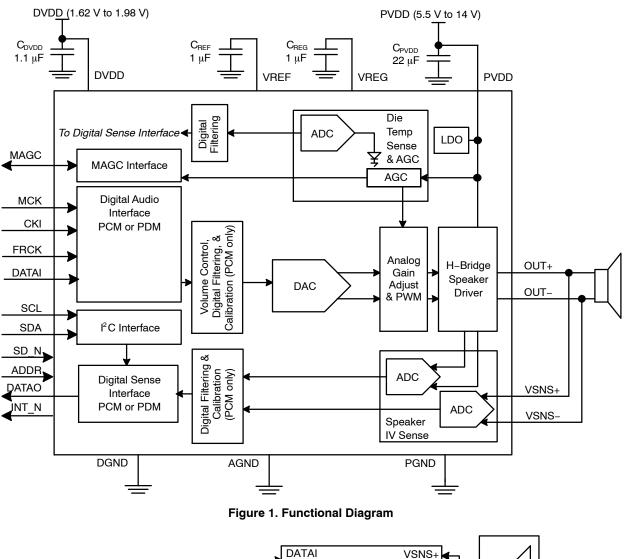

The ONA10IV is a digital input, mono Class–D audio amplifier with real time, integrated current and voltage sensing of the loudspeaker it's driving. This sense data is transmitted to the host through a separate digital output.

The ONA10IV can be directly connected to a 2-cell (2S) or 3-cell (3S) battery and offers a fast automatic gain control (AGC) for brownout protection that can react within 10  $\mu$ s.

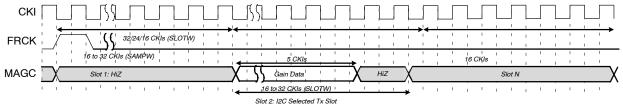

Up to eight devices can share the digital audio interfaces through I<sup>2</sup>C control. A separate bus (MAGC) is used to synchronize gain across multiple ONA10IV instantiations during a brownout protection event.

# **Key Features**

- Filter-less, Mono Class-D Amplifier

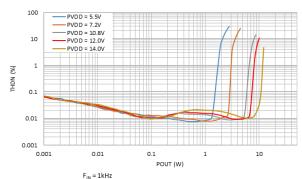

- 16 W into 4 Ω / 14 V Supply (1% THD+N)

- 13.8 W into 4 Ω / 12 V Supply (1% THD+N)

- $\bullet~500~\mu V$  "Click and Pop" Suppression

- 42 μV<sub>RMS</sub> Noise Floor (A–Weighted)

- No Boost Capacitors Required

- Speaker Voltage & Current Sense

- Up to 20 kHz Bandwidth

- 81 / 71 dBA Dynamic Range (Voltage / Current)

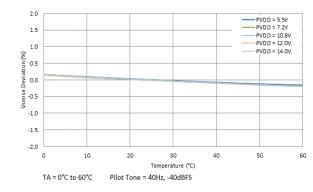

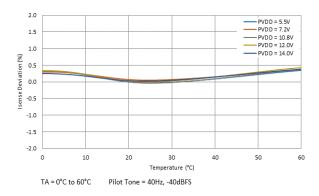

- ◆ 0.5% V/I Gain Error Variation

- Digital Audio / Sense Configurations

- 16 kHz to 96 kHz Audio Sampling Rates

- 16-, 24-, and 32-Bit I<sup>2</sup>S Data

- 16-, 24-, and 32-Bit TDM Data (up to 8 Slots)

- Selectable PCM or PDM Format

- I<sup>2</sup>C Fast Mode (up to 1 MHz) Control

- EMI Reduction Controls

- Over Current and Thermal Protection

- PVDD Power Supply: 5.5 V to 14 V

- DVDD Power Supply: 1.62 V to 1.98 V

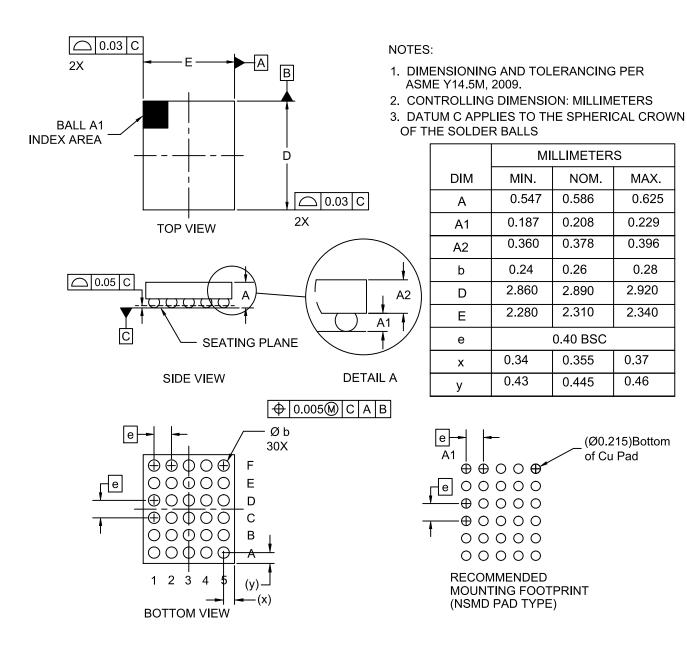

- 30-Bump WLCSP

- 2.31 mm x 2.89 mm, 0.4mm pitch

- This is a Pb–Free Device

# Applications

• Laptops, Smart Speakers, Portable Speakers, and Other IoT Devices

# **ON Semiconductor®**

www.onsemi.com

WLCSP30 CASE 567VB

# MARKING DIAGRAM

VD = Specific Device Code

- ZZ = Wafer Lot

- YW = Date Code

- A = Assembly Location

# **ORDERING INFORMATION**

| Device     | Package   | Shipping <sup>†</sup> |  |  |

|------------|-----------|-----------------------|--|--|

| NCA-       | WLCSP30   | 3000 Units /          |  |  |

| ONA10IVUCX | (Pb-Free) | Tape & Reel           |  |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# Capabilities

- *Filter-less Class D Amplifier:* Capable of operating off of direct 2-cell (2S) or 3-cell (3S) battery connection or a regulated supply from 5.5 V to 14 V.

- *Current and Voltage Speaker Sensing:* Able to sense up to 20 kHz with low gain error variation.

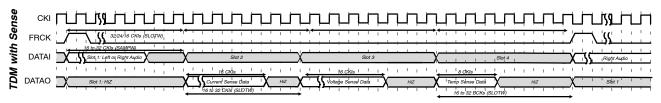

- *TDM / I2S Digital Audio Input:* Programmable interface that can support 16 kHz to 96 kHz sample rates with up to eight 16- to 32-bit input slots. Ability to select CKI active edge as well as FRCK polarity, delay, and pulse mode.

- *PDM Digital Audio Input/Output:* Ability to bypass embedded digital filters and drive/sense the speaker using pulse density modulation (PDM) interface.

- *TDM / I2S Digital Sense Path Output:* Can provide die temperature, current and voltage speaker sense data in up to 8 slots.

- *Volume Control:* Ability to adjust volume in 0.375 dB steps and automatically ramp on start up or shut down using 4 different rates.

- *Amplifier Gain:* Independently adjustable for PCM or PDM mode.

- *EMI Reduction Controls:* 4 selectable edge rates and 8 spread spectrum modes to accommodate EMI reduction per system needs.

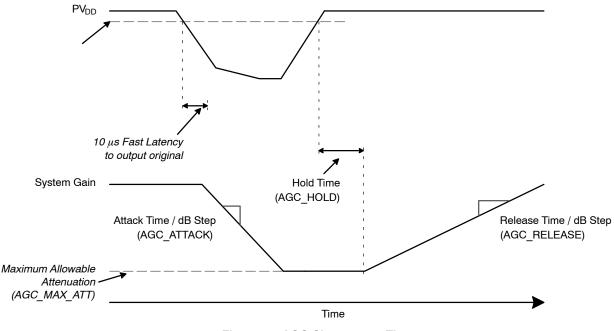

- *Brownout Protection:* Fast reaction of less than 10 µs with ability to customize attack threshold for a 2–cell or 3–cell battery. Maximum attenuation as well as attack, hold, and release timing programming available to adjust the dynamic response to a brownout event.

- *MAGC Synchronous Gain Adjustments:* Dedicated bus to synchronize multiple chip instantiations to within 0.5 dB.

- *Fatal Protections:* Includes output over-current, supply under-voltage, clock error, and chip over-temperature protections that are always on when the amplifier is active. The ONA10IV can recover from each fatal protection automatically without host intervention.

- *Interrupt Flags:* Indicate when a fatal protection, brownout protection, or thermal foldback is active.

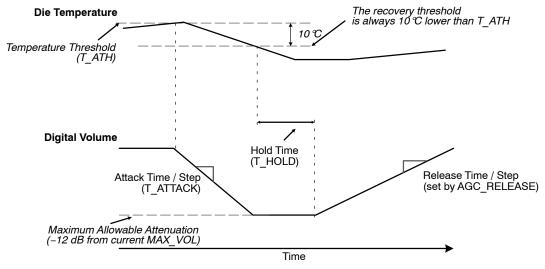

- *Thermal Foldback:* Ability to customize the chip's thermal response to elevated die temperature using four programmable thresholds. Attack, hold, and release timing customization also available.

- *Power Reduction Options:* Ability to disable features like IV sensing, brownout protection, and thermal foldback to reduce power consumption.

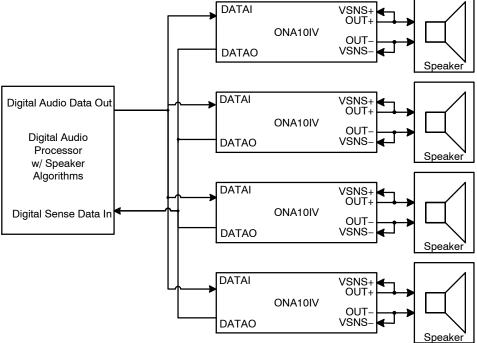

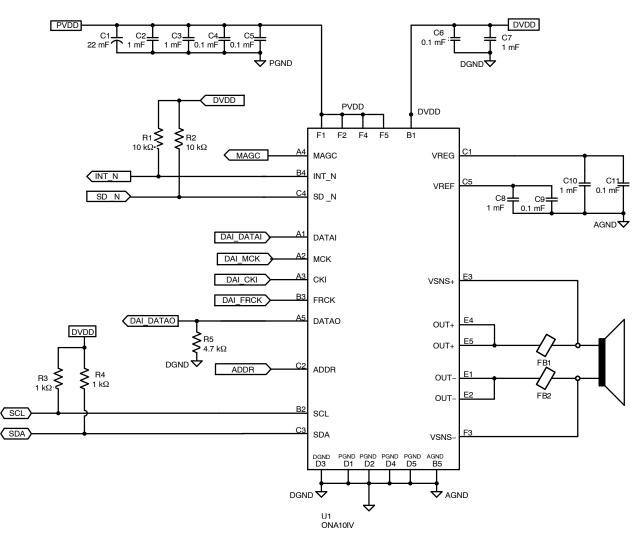

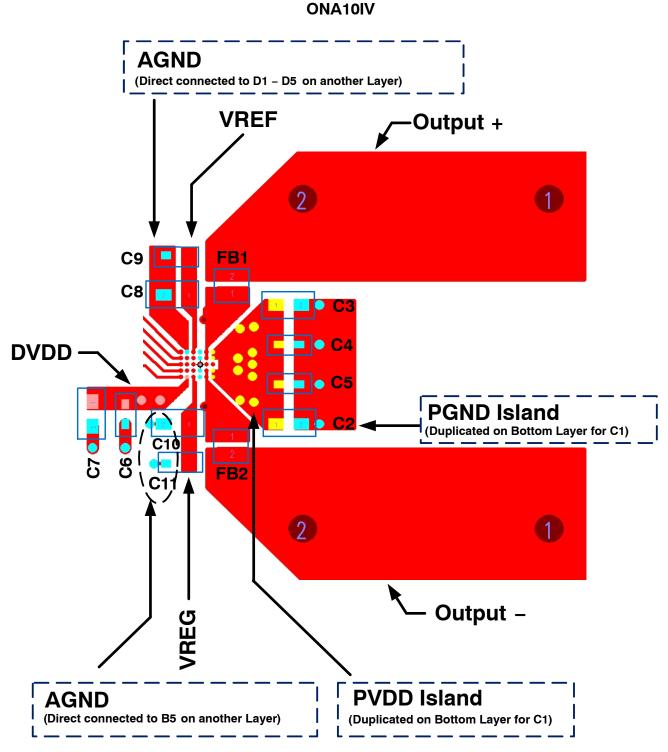

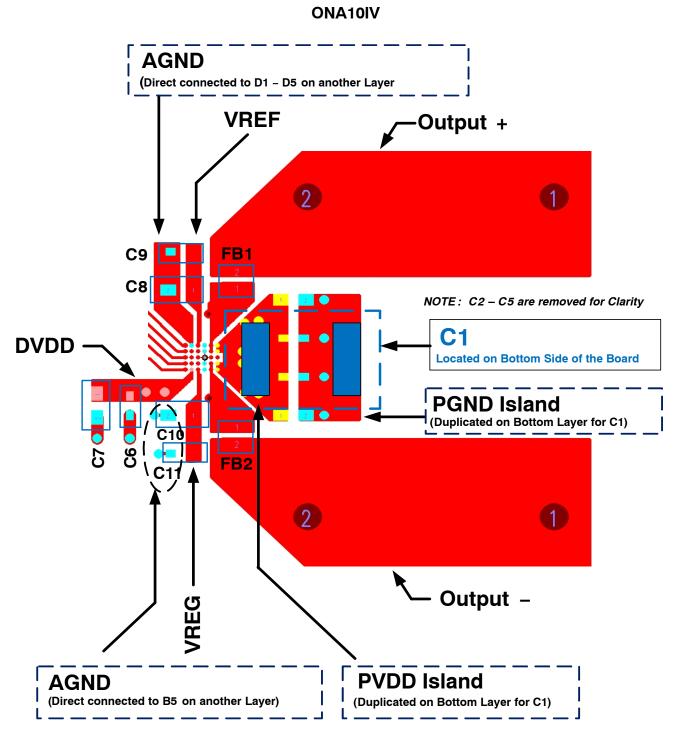

Figure 2. System Diagram

www.onsemi.com

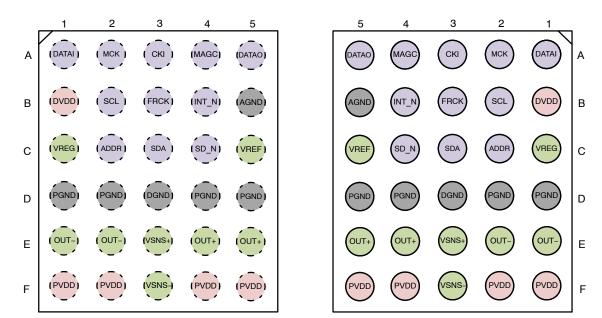

# **PIN CONFIGURATION**

Figure 3. Top Through View (Balls Down)

Figure 4. Bottom View (Balls Up)

#### **PIN DESCRIPTION**

| Pin No.        | Name  | Туре                  | Description                                                                                |

|----------------|-------|-----------------------|--------------------------------------------------------------------------------------------|

| A1             | DATAI | Data Input            | DAI – Serial Digital Audio Data (either I <sup>2</sup> S or PDM)                           |

| A2             | MCK   | Clock Input           | DAI – Master Clock                                                                         |

| A3             | CKI   | Clock Input           | DAI – Bit Clock (PCM Mode) / PDM Clock (PDM Mode) Input                                    |

| A4             | MAGC  | Control Bidirectional | Multi-speaker automatic gain control (MAGC) to synchronize multiple ONA10IV instantiations |

| A5             | DATAO | Data Output           | PDM or Serial PCM Speaker Sense Data Output                                                |

| B1             | DVDD  | Power                 | Digital Power Supply                                                                       |

| B2             | SCL   | Clock Input           | I <sup>2</sup> C – Clock Signal                                                            |

| B3             | FRCK  | Clock Input           | DAI – Frame Clock (PCM Mode)                                                               |

| B4             | INT_N | Control Output        | Interrupt Request Signal                                                                   |

| B5             | AGND  | Ground                | Analog Ground                                                                              |

| C1             | VREG  | Analog Output         | Internal LDO Regulator Output                                                              |

| C2             | ADDR  | Control Input         | Hardware selection of I <sup>2</sup> C address to allow multiple ONA10IV instantiations.   |

| C3             | SDA   | Data Bidirectional    | l <sup>2</sup> C – Data Signal                                                             |

| C4             | SD_N  | Control Input         | Shutdown (Active Low)                                                                      |

| C5             | VREF  | Analog Output         | Internally Generated Reference                                                             |

| D1, D2, D4, D5 | PGND  | Ground                | High Power Ground                                                                          |

| D3             | DGND  | Ground                | Digital Ground                                                                             |

| E1,E2          | OUT-  | Analog Output         | Inverting Class D Amplifier Output                                                         |

| E3             | VSNS+ | Analog Input          | Positive Analog Input for Voltage Sense                                                    |

| E4, E5         | OUT+  | Analog Output         | Non-inverting Class D Amplifier Output                                                     |

| F1,F2,F4,F5    | PVDD  | Power                 | Output Driver Power Supply                                                                 |

| F3             | VSNS- | Analog Input          | Negative Analog Input for Voltage Sense                                                    |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                                 |                                                      |                        | Мах                    | Unit |

|--------------------|-------------------------------------------|------------------------------------------------------|------------------------|------------------------|------|

| PV <sub>DD</sub>   | Voltage on PVDD Pin                       |                                                      | -0.3                   | 17.0                   | V    |

| DV <sub>DD</sub>   | Voltage on DVDD Pin                       | -0.3                                                 | 2.2                    | V                      |      |

| V <sub>OUT</sub>   | Voltage on OUT- and OUT+ Pins (Output Dis | -0.3                                                 | PV <sub>DD</sub> + 0.3 | V                      |      |

|                    | Voltage on INT_N, DATAO, and MAGC Pins    | -0.3                                                 | 6.0                    |                        |      |

| V <sub>IN</sub>    | Voltage on VSNS- and VSNS+ Pins           |                                                      | -0.3                   | PV <sub>DD</sub> + 0.3 |      |

| V <sub>CNTRL</sub> | Control Input Voltage                     | SCL, SDA, ADDR, CKI, DATAI,<br>MCK, FRCK, MAGC, SD_N | -0.3                   | 6.0                    | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

# THERMAL RATINGS

| Parameter                                                                                  |                                                                                                                                                   | Min                                                                                     | Тур                                                                                                                                                                                                         | Max                                                                                                                                                                                               | Unit                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Junction Temperature                                                                       |                                                                                                                                                   | -                                                                                       | -                                                                                                                                                                                                           | 150                                                                                                                                                                                               | °C                                                                                                                                                                                                                   |

| Storage Temperature Range                                                                  |                                                                                                                                                   | -65                                                                                     | -                                                                                                                                                                                                           | 150                                                                                                                                                                                               | °C                                                                                                                                                                                                                   |

| Lead Temperature (Soldering, 10 s)                                                         |                                                                                                                                                   | -                                                                                       | -                                                                                                                                                                                                           | 300                                                                                                                                                                                               | °C                                                                                                                                                                                                                   |

| Thermal Resistance, JEDEC Standard, Still Air 4-layer Board                                |                                                                                                                                                   | -                                                                                       | 55 (Note 1)                                                                                                                                                                                                 | -                                                                                                                                                                                                 | °C/W                                                                                                                                                                                                                 |

| 4-                                                                                         | -layer Board w/ vias                                                                                                                              | -                                                                                       | 33 (Note 2)                                                                                                                                                                                                 | -                                                                                                                                                                                                 |                                                                                                                                                                                                                      |

| Maximum continuous on-chip power dissipation ( $T_A = 25^{\circ}C$ ) for multi-layer board |                                                                                                                                                   |                                                                                         | 3.0                                                                                                                                                                                                         | -                                                                                                                                                                                                 | W                                                                                                                                                                                                                    |

|                                                                                            | Junction Temperature     Storage Temperature Range     Lead Temperature (Soldering, 10 s)     Thermal Resistance, JEDEC Standard, Still Air     4 | Junction Temperature<br>Storage Temperature Range<br>Lead Temperature (Soldering, 10 s) | Junction Temperature   -     Storage Temperature Range   -65     Lead Temperature (Soldering, 10 s)   -     Thermal Resistance, JEDEC Standard, Still Air   4-layer Board   -     4-layer Board w/ vias   - | Junction Temperature -   Storage Temperature Range -   Lead Temperature (Soldering, 10 s) -   Thermal Resistance, JEDEC Standard, Still Air 4-layer Board   4-layer Board w/ vias -   33 (Note 2) | Junction TemperatureImageImageImageStorage Temperature Range150Lead Temperature (Soldering, 10 s)55 (Note 1)Thermal Resistance, JEDEC Standard, Still Air4-layer Board-55 (Note 1)4-layer Board w/ vias-33 (Note 2)- |

More layers can provide a lower θ<sub>JA.</sub>

JEDEC standard board utilizes a via for each ball.

# **ESD PROTECTION**

| Symbol | Parameter                  | Condition                                | Min | Unit |

|--------|----------------------------|------------------------------------------|-----|------|

| ESD    | Human Body Model (HBM)     | ANSI/ESDA/ JEDEC JS-001-2012             | 2   | kV   |

|        | Charged Device Model (CDM) | According to "EIA/JESD22-C101 Level III" | 500 | V    |

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                | Parameter                                              | Min (Note 3) | Тур | Max  | Unit |

|-----------------------|--------------------------------------------------------|--------------|-----|------|------|

| T <sub>A</sub>        | Operating Temperature Range                            | -40          | -   | 85   | °C   |

| DV <sub>DD</sub>      | Digital Supply Voltage Range                           | 1.62         | -   | 1.98 | V    |

| PV <sub>DD</sub>      | Power Supply Voltage Range (2S- Battery Configuration) | 5.5          | -   | 9.0  | V    |

|                       | Power Supply Voltage Range (3S- Battery Configuration) | 7.5          | -   | 14.0 | V    |

| C <sub>REF</sub>      | Reference Capacitor                                    | 0.85         | -   | -    | μF   |

| C <sub>REG</sub>      | Regulator Capacitor                                    | 0.85         | -   | -    | μF   |

| C <sub>PVDD</sub>     | PV <sub>DD</sub> Capacitor (s)                         | 20           | -   | -    | μF   |

| C <sub>DVDD</sub>     | DV <sub>DD</sub> Capacitor (s)                         | 0.85         | -   | -    | μF   |

| R <sub>PD_DATAO</sub> | Pull down resistor; Only 1 required per DATAO bus      | -            | -   | 10   | kΩ   |

| ZL                    | Load Inductance                                        | -            | 10  | -    | μH   |

|                       | Load Resistance                                        | 4            | -   | -    | Ω    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.3. Minimum passive component values include temperature, tolerance, and aging.

| ELECTRICAL CHARACTERISTICS (PV <sub>DD</sub> = 12 V, DVDD = 1.8 V, f <sub>S</sub> = FRCK = 48 kHz, 24-bit digital audio data, Z <sub>L</sub> = ∞, T <sub>A</sub> = 25°C, |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD_N = H, Default I <sup>2</sup> C registers, and audio measurement bandwidth = 20 Hz to 20 kHz (AES17) unless otherwise noted)                                          |  |

| Symbol          | Parameter                               | Conditi                                                                                                                          | ons                                                                                                  | Min | Тур   | Max  | Unit                 |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-------|------|----------------------|

| SPEAKER D       | DRIVER PATH                             |                                                                                                                                  |                                                                                                      |     |       |      |                      |

| Po              | Maximum Continuous<br>Output Power      | THD+N $\leq$ 10%, f = 1 kHz                                                                                                      | $\begin{array}{l} Z_{L} = 4 \; \Omega + 10 \; \mu H \\ PV_{DD} = 12 \; V \end{array}$                | -   | 16.0  | -    | W                    |

|                 |                                         | THD+N $\leq$ 1%, f = 1 kHz                                                                                                       | $\begin{array}{l} Z_{L} = 4 \; \Omega + 10 \; \; \mu H \\ PV_{DD} = 12 \; V \end{array}$             | -   | 13.8  | -    |                      |

|                 |                                         |                                                                                                                                  | $\begin{array}{l} Z_L = 8 \ \Omega + 10 \ \mu H \\ PV_{DD} = 14 \ V \end{array}$                     | -   | 10.9  | -    |                      |

|                 |                                         |                                                                                                                                  | $\begin{array}{l} Z_L = 8 \ \Omega + 10 \ \mu H \\ PV_{DD} = 12 \ V \end{array}$                     | -   | 8.1   | -    |                      |

|                 |                                         |                                                                                                                                  | Z <sub>L</sub> = 8 Ω + 10 μH<br>PV <sub>DD</sub> = 10.8 V                                            | -   | 6.5   | -    |                      |

|                 |                                         |                                                                                                                                  | $Z_L$ = 8 Ω + 10 μH<br>PV <sub>DD</sub> = 7.2 V                                                      | -   | 2.9   | -    |                      |

| R <sub>ON</sub> | On Resistance of Output<br>Stage        | I <sub>O</sub> = 500 mA<br>High Side + Low Side Resis                                                                            | stance                                                                                               | -   | 435   | -    | mΩ                   |

| η               | Efficiency                              | f = 1 kHz, PV <sub>DD</sub> = 14 V                                                                                               | $\begin{array}{l} P_{OUT} = 14 \ W, \\ Z_L = 4 \ \Omega + 10 \ \ \muH \end{array}$                   | -   | 84    | -    | %                    |

|                 |                                         |                                                                                                                                  | $\begin{array}{l} P_{OUT} = = 10 \text{ W}, \\ Z_{L} = 8 \ \Omega + 10 \ \mu \mathrm{H} \end{array}$ | -   | 90    | -    |                      |

| PSRR            | PV <sub>DD</sub> Power Supply           |                                                                                                                                  |                                                                                                      | -   | 74    | -    | dB                   |

|                 | Rejection Ratio                         | f <sub>RIPPLE</sub> = 217 Hz, Square V<br>10 μs Rise/Fall Time<br>PV <sub>DD</sub> = 12 V w/ 200 mV Dr<br>Digitally Silent Input |                                                                                                      | -   | 74    | -    |                      |

|                 |                                         | f <sub>RIPPLE</sub> = 10 kHz, V <sub>RIPPLE</sub> =<br>Digitally Silent Input                                                    | = 200 mV <sub>PP</sub>                                                                               | -   | 74    | -    |                      |

|                 |                                         | f <sub>RIPPLE</sub> = 20 kHz, V <sub>RIPPLE</sub> =<br>Digitally Silent Input                                                    | = 200 mV <sub>PP</sub>                                                                               | -   | 70    | -    |                      |

| K <sub>CP</sub> | Click-And-Pop Level<br>(Note 10)        | Digitally Silent Input<br>Peak Output Voltage                                                                                    | Into Shutdown                                                                                        | -   | ±0.5  | -    | mV                   |

|                 |                                         | A-weighted, $T_A = 25^{\circ}C$<br>$Z_L = 4 \Omega + 10 \mu H$                                                                   | Out of Shutdown                                                                                      | -   | ±0.5  | -    |                      |

| V <sub>OS</sub> | Differential Output Offset<br>Voltage   | $T_A$ = 25°C, Digitally Silent In $Z_L$ =4 $\Omega$ + 10 $\mu$ H                                                                 | nput                                                                                                 | -   | ±0.5  | ±1.5 | mV                   |

| e <sub>N</sub>  | Output Noise                            | Digitally Silent Input,                                                                                                          | A-weighted                                                                                           | -   | 42    | -    | $\mu V_{\text{RMS}}$ |

|                 |                                         | 16 dB Gain<br>Z <sub>L</sub> = 4 Ω + 10  μH                                                                                      | Un-weighted                                                                                          | -   | 57    | -    | 1                    |

| DR              | Dynamic Range                           | 16 dB Gain, -60 dBFS Inpu<br>$Z_L = 4 \Omega + 10 \mu$ H, A-weigh<br>Relative to 1% THD+N Driv                                   | nted                                                                                                 | _   | 105   | -    | dB                   |

| THD+N           | Total Harmonic Distortion<br>Plus Noise | f = 1 kHz                                                                                                                        | $P_{OUT} = 4 W,$<br>$Z_L = 8 \Omega + 10 \mu H$                                                      | -   | 0.012 | -    | %                    |

|                 |                                         |                                                                                                                                  | P <sub>OUT</sub> = 8 W,<br>Z <sub>L</sub> = 4 Ω + 10 μH                                              | -   | 0.015 | -    |                      |

|                 |                                         | f = Up to 8 kHz                                                                                                                  | P <sub>OUT</sub> = 4 W,<br>Z <sub>L</sub> = 8 Ω + 10 μH                                              | -   | 0.080 | -    |                      |

|                 |                                         |                                                                                                                                  | $\begin{array}{l} P_{OUT} = 8 \ W, \\ Z_L = 4 \ \Omega + 10 \ \ \muH \end{array}$                    | -   | 0.090 | -    |                      |

| ELECTRICAL CHARACTERISTICS (PV <sub>DD</sub> = 12 V, DVDD = 1.8 V, f <sub>S</sub> = FRCK = 48 kHz, 24-bit digital audio data, Z <sub>L</sub> = ∞, T <sub>A</sub> = 25°C, |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD_N = H, Default I <sup>2</sup> C registers, and audio measurement bandwidth = 20 Hz to 20 kHz (AES17) unless otherwise noted) (continued)                              |  |

| Symbol             | Parameter                              | Conditions                                                                        | Min   | Тур   | Max  | Unit |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------------|-------|-------|------|------|

| SPEAKER D          | DRIVER PATH                            |                                                                                   |       |       |      |      |

| A <sub>V</sub>     | Amplifier Gain                         | Selected through AGC response or I <sup>2</sup> C                                 | 15.4  | 16.0  | 16.6 | dB   |

|                    |                                        | programming.<br>$Z_L = 8 \Omega + 10 \mu H \text{ or } Z_L = 4 \Omega + 10 \mu H$ | 11.4  | 12.0  | 12.6 |      |

|                    |                                        |                                                                                   | 8.3   | 9.0   | 9.6  |      |

|                    |                                        |                                                                                   | 5.2   | 6.0   | 6.7  |      |

|                    |                                        |                                                                                   | 2.1   | 3.0   | 3.9  |      |

| DAC <sub>MAP</sub> | P Typical DAC Mapping 0 dBFS PCM Input | -                                                                                 | 4.22  | -     | dBV  |      |

|                    |                                        | 0 dBFS PDM Input<br>85.35% Ones Density Maximum                                   | -9.68 | -0.13 | 7.23 |      |

#### DAC Digital Filter Characteristics (f<sub>s</sub> = 16, 22.05, 44.1, or 48kHz) (Note 5)

| f <sub>PB</sub> | Passband             | -0.1 dB Cutoff      | - | 0.43* f <sub>s</sub>  | - | Hz |

|-----------------|----------------------|---------------------|---|-----------------------|---|----|

|                 |                      | –3 dB Cutoff        | - | 0.504* f <sub>s</sub> | - | Hz |

|                 |                      | -6 dB Cutoff        | - | 0.524* f <sub>s</sub> | - | Hz |

| δ <sub>P</sub>  | Passband Ripple      |                     | - | 0.052                 | - | dB |

| f <sub>SB</sub> | Stopband             |                     | - | 0.62* f <sub>s</sub>  | - | Hz |

| α <sub>S</sub>  | Stopband Attenuation | f > f <sub>SB</sub> | - | 58                    | - | dB |

| tg              | Group Delay          |                     | - | 8.25                  | _ | S  |

# DAC Digital Filter Characteristics (f<sub>s</sub> = 32 or 96 kHz) (Note 5)

| f <sub>PB</sub> | Passband             | -0.1 dB Cutoff      | - | 0.43* f <sub>s</sub>  | - | Hz |

|-----------------|----------------------|---------------------|---|-----------------------|---|----|

|                 |                      | -3 dB Cutoff        | - | 0.485* f <sub>s</sub> | - | Hz |

|                 |                      | -6 dB Cutoff        | - | 0.494* f <sub>s</sub> | - | Hz |

| δ <sub>P</sub>  | Passband Ripple      |                     | - | 0.054                 | - | dB |

| f <sub>SB</sub> | Stopband             |                     | - | 0.54* f <sub>s</sub>  | - | Hz |

| α <sub>S</sub>  | Stopband Attenuation | f > f <sub>SB</sub> | - | 58                    | - | dB |

| tg              | Group Delay          |                     | - | 8.25                  | - | S  |

#### Driver References (Note 5)

| Γ | f <sub>SW(AMP)</sub> | Class-D Switching                  | MCK = 12.2880 MHz                                | -      | 646.7 | - | kHz |

|---|----------------------|------------------------------------|--------------------------------------------------|--------|-------|---|-----|

|   |                      | Frequency                          | MCK = 11.2986 MHz                                | _      | 519.2 | _ |     |

|   | $\alpha_{D}$         | Digital Volume Control<br>(Note 4) | Programmable in 0.375 dB steps from MUTE to 0 dB | -95.25 | -     | 0 | dB  |

# SPEAKER SENSE PATH

| $\Delta G_{ERRVI}$ | Gain Error Variation, Voltage<br>Over Current (Note 10) | $T_A = 0^{\circ}C$ to $60^{\circ}C$ , -40 dBFS Input at 40 Hz | - | ±0.50 | - | % | 1 |

|--------------------|---------------------------------------------------------|---------------------------------------------------------------|---|-------|---|---|---|

|--------------------|---------------------------------------------------------|---------------------------------------------------------------|---|-------|---|---|---|

#### **Current Sense**

| I <sub>IN</sub> | Current Sense Range |                                                                                           | -     | _  | 3.50 | A <sub>P</sub> |

|-----------------|---------------------|-------------------------------------------------------------------------------------------|-------|----|------|----------------|

| BWI             | Converter Bandwidth | HPF Enabled                                                                               | 0.014 | -  | 20   | kHz            |

| DRI             | Dynamic Range       | –60 dBFS Input<br>16 dB Gain, A-weighted<br>Relative to 1% THD+N Driver Path Output Power | _     | 71 | -    | dB             |

# Voltage Sense

| V <sub>IN</sub> | Voltage Sense Range |             | -     | - | 14 | VP  |

|-----------------|---------------------|-------------|-------|---|----|-----|

| $BW_{V}$        | Converter Bandwidth | HPF Enabled | 0.014 | - | 20 | kHz |

| ELECTRICAL CHARACTERISTICS (PV <sub>DD</sub> = 12 V, DVDD = 1.8 V, f <sub>S</sub> = FRCK = 48 kHz, 24-bit digital audio data, Z <sub>L</sub> = ∞, T <sub>A</sub> = 25°C, |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD_N = H, Default I <sup>2</sup> C registers, and audio measurement bandwidth = 20 Hz to 20 kHz (AES17) unless otherwise noted) (continued)                              |  |

|  | Symbol | Parameter | Conditions | Min | Тур | Max | Unit |  |

|--|--------|-----------|------------|-----|-----|-----|------|--|

|--|--------|-----------|------------|-----|-----|-----|------|--|

#### SPEAKER SENSE PATH

#### Voltage Sense

| DR <sub>V</sub> | Dynamic Range | -60 dBFS Input<br>16 dB Gain, A-weighted      | - | 81 | _ | dB  |

|-----------------|---------------|-----------------------------------------------|---|----|---|-----|

|                 |               | Relative to 1% THD+N Driver Path Output Power |   |    |   | l I |

# POWER SUPPLY

| V <sub>REG</sub>      | Regulator Voltage                                    | $I_{REG}$ = 100 $\mu$ A, Standby E                                                           | Bit Set                   | -   | 5.00 | -   | V  |

|-----------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------|-----|------|-----|----|

| I <sub>PVDD</sub>     | Supply Current, PV <sub>DD</sub>                     | Digital Silence                                                                              | PV <sub>DD</sub> = 14 V   | -   | 13.8 | -   | mA |

|                       |                                                      |                                                                                              | PV <sub>DD</sub> = 12 V   | -   | 13.5 | -   |    |

|                       |                                                      |                                                                                              | PV <sub>DD</sub> = 10.8 V | -   | 13.2 | -   | mA |

|                       |                                                      |                                                                                              | PV <sub>DD</sub> = 7.2 V  | -   | 12.6 | -   | mA |

| I <sub>DVDD</sub>     | Supply Current, DV <sub>DD</sub>                     | Digital Silence                                                                              |                           | -   | 1.5  | 2.0 | mA |

| I <sub>SB_PVDD</sub>  | Standby Current, PV <sub>DD</sub>                    | STBY bit set in I2C<br>register or CKI static<br>(Note 6) $PV_{DD} = 12 V$ $PV_{DD} = 7.2 V$ | PV <sub>DD</sub> = 12 V   | -   | 2.9  | -   | mA |

|                       |                                                      |                                                                                              | -                         | 2.9 | -    |     |    |

| I <sub>SB_DVDD</sub>  | Standby Current, DV <sub>DD</sub>                    | STBY bit set in I <sup>2</sup> C registe                                                     | er or CKI static (Note 6) | -   | 0.3  | -   | mA |

| I <sub>DRV_PVDD</sub> | Driver Path Only Supply<br>Current, PV <sub>DD</sub> | Digital Silence, IVSNS_PI                                                                    | D bit active.             | -   | 9.9  | -   | mA |

| I <sub>DRV_DVDD</sub> | Driver Path Only Supply<br>Current, DV <sub>DD</sub> | Digital Silence, IVSNS_PI                                                                    | D bit active.             | -   | 1.0  | -   | mA |

| I <sub>SD</sub>       | Shutdown Current                                     | SD_N = L                                                                                     | PV <sub>DD</sub> = 12 V   | -   | 2.0  | -   | μA |

|                       |                                                      |                                                                                              | DV <sub>DD</sub> = 1.8 V  | -   | 0.3  | 2.0 | 1  |

# **ENVIRONMENT SENSE & PROTECTION CHARACTERISTICS**

# **Chip Protection Thresholds**

| $V_{LMT}$        | Under-Voltage Limit, PV <sub>DD</sub> | Threshold          | 2.5 | -   | 4.5 | V  |

|------------------|---------------------------------------|--------------------|-----|-----|-----|----|

|                  |                                       | Hysteresis         | -   | 0.2 | -   |    |

|                  | Under-Voltage Limit, DV <sub>DD</sub> | Threshold          | 0.5 | -   | 1.5 |    |

|                  |                                       | Hysteresis         | -   | 0.5 | -   |    |

| I <sub>LMT</sub> | Output Current Limit                  | Shutdown Threshold | 3.6 | 5.0 | -   | А  |

| T <sub>LMT</sub> | Thermal Limit                         | Shutdown Threshold | -   | 145 | -   | °C |

|                  |                                       | Recovery Threshold | -   | 115 | -   |    |

# Automatic Gain Control (AGC) for Brownout Protection

| V <sub>ATH</sub> | Attack Threshold Range          | Programmable through I <sup>2</sup> C                | 2S Battery<br>Configuration<br>(48 mV Steps)              | 6.511 | -    | 7.999    | V     |

|------------------|---------------------------------|------------------------------------------------------|-----------------------------------------------------------|-------|------|----------|-------|

|                  |                                 |                                                      | 3S Battery<br>Configuration<br>(72 mV Steps)              | 9.763 | -    | 11.995   |       |

| ACCP             | Absolute Accuracy               | 2S Battery Configuration                             |                                                           | -     | ±70  | -        | mV    |

|                  |                                 | 3S Battery Configuration                             |                                                           | -     | ±104 | -        |       |

| t <sub>A</sub>   | Attack Time<br>(Gain Decrease)  | Programmable through I <sup>2</sup> C i              | Programmable through I <sup>2</sup> C in 35 $\mu$ s steps |       | -    | 530      | μs/dB |

| t <sub>H</sub>   | Hold Time                       | Programmable through I <sup>2</sup> C i              | Programmable through I <sup>2</sup> C in 35 ms steps      |       | -    | Infinite | ms    |

| t <sub>R</sub>   | Release Time<br>(Gain Increase) | Programmable through I <sup>2</sup> C in 70 ms steps |                                                           | 5     | -    | 1055     | ms/dB |

| <b>ELECTRICAL CHARACTERISTICS</b> (PV <sub>DD</sub> = 12 V, DVDD = 1.8 V, f <sub>S</sub> = FRCK = 48 kHz, 24-bit digital audio data, Z <sub>L</sub> = ∞, T <sub>A</sub> = 25°C, |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD_N = H, Default I <sup>2</sup> C registers, and audio measurement bandwidth = 20 Hz to 20 kHz (AES17) unless otherwise noted) (continued)                                     |

### **ENVIRONMENT SENSE & PROTECTION CHARACTERISTICS**

#### Automatic Gain Control (AGC) for Brownout Protection

| tL               | AGC Attenuation Latency             | Attack Time set to 5 $\mu s.$ Measured from PVDD to initial response on OUT $\pm$ | -  | -   | 10 | μs     |

|------------------|-------------------------------------|-----------------------------------------------------------------------------------|----|-----|----|--------|

| $\Delta_{AGC}$   | Maximum AGC Attenuation             | Gain setting is 16 dB or 12 dB (Note 7)                                           | -2 | -   | -9 | dB     |

| $\Delta_{AGC}$   | AGC Attenuation Step Size           |                                                                                   | -  | 0.5 | -  | dB     |

| t <sub>D2D</sub> | MAGC Device-to-Device<br>Latency    |                                                                                   | -  | 1   | _  | Sample |

| A <sub>D2D</sub> | MAGC Device-to-Device<br>Gain Delta |                                                                                   | -  | 0.5 | _  | dB     |

#### **Die Temperature Sense**

| ſ | $BW_T$          | Converter Bandwidth     | -   | 500 | -   | Sps |

|---|-----------------|-------------------------|-----|-----|-----|-----|

|   | T <sub>IN</sub> | Temperature Sense Range | -40 | -   | 150 | °C  |

DIGITAL INTERFACE (Includes SCL, SDA, CKI, FRCK, MCK, SD\_N, MAGC, ADDR, DATAI, DATAO, and INT\_N)

#### I/O Characteristics

| V <sub>IH</sub>              | Input High Voltage  |                                                              |                                           | 0.7 x<br>DV <sub>DD</sub> | _    | DV <sub>DD</sub>          | V  |

|------------------------------|---------------------|--------------------------------------------------------------|-------------------------------------------|---------------------------|------|---------------------------|----|

| $V_{\text{IL}}$              | Input Low Voltage   |                                                              |                                           | -0.5                      | -    | 0.3 x<br>DV <sub>DD</sub> | V  |

| V <sub>HYST</sub>            | Input Hysteresis    | SCL, SDA, and ADDR                                           |                                           | _                         | 0.20 | -                         | V  |

|                              |                     | All other inputs (Note 8)                                    |                                           | -                         | 0.40 | -                         |    |

| I <sub>IH</sub>              | Input High Leakage  | Input Voltage = V⊮ to D                                      | VDD                                       | -1                        | -    | 1                         | μA |

| Ι <sub>ΙL</sub>              | Input Low Leakage   | Input Voltage = Vi∟to D0                                     | GND                                       | -1                        | -    | 1                         | μA |

| I <sub>OFF</sub> Off Leakage |                     | DV <sub>DD</sub> = 0 V                                       | Any I/O from 0 V to<br>2.2 V              | -10                       | _    | 10                        | μA |

|                              |                     |                                                              | SCL, SDA, and AD-<br>DR from 0 V to 5.5 V | -10                       | _    | 10                        | μA |

| I <sub>OZ</sub>              | Disable Leakage     | DATAO & MAGC Pins, A<br>V <sub>IN</sub> on pin from 0 V to 2 |                                           | -5                        | _    | 5                         | μΑ |

| C <sub>IN</sub>              | Input Capacitance   |                                                              |                                           |                           | 5    | _                         | pF |

| V <sub>OH</sub>              | Output High Voltage | All Outputs; I <sub>OH</sub> = 4 mA                          |                                           | 1.2                       | _    | -                         | V  |

|                              |                     | For MAGC/DATAO, 50%                                          | 6 Drive; I <sub>OH</sub> = 2 mA           | 1.2                       | _    | -                         |    |

| V <sub>OL</sub>              | Output Low Voltage  | For MAGC/DATAO                                               | I <sub>OL</sub> = 4 mA                    | 0                         | -    | 0.2 x<br>DV <sub>DD</sub> | V  |

|                              |                     |                                                              | 50% Drive;<br>I <sub>OL</sub> = 2 mA      | 0                         | _    | 0.2 x<br>DV <sub>DD</sub> |    |

|                              |                     | For SDA, SCL, & INT_N                                        | l; l <sub>OL</sub> = 3 mA                 | 0                         | -    | 0.4                       |    |

| I <sub>OL</sub>              | Output Low Current  | For SDA, SCL, & INT_N                                        | I; V <sub>OL</sub> = 0.4 V                | 3                         | _    | -                         | mA |

#### Shutdown and Standby Timing

| t <sub>WU</sub> | Wake-Up Time | $D_N = L \rightarrow H$ to $I^2C$ Communication                                     | 10 | - | -    | μs |

|-----------------|--------------|-------------------------------------------------------------------------------------|----|---|------|----|

|                 |              | Shutdown condition removed (OUT+/- active) through I <sup>2</sup> C. MCK is present | -  | - | 17.0 | ms |

|                 |              | Standby condition removed (OUT+/– active) through I <sup>2</sup> C.                 | -  | - | 11.0 | ms |

| ELECTRICAL CHARACTERISTICS (PV <sub>DD</sub> = 12 V, DVDD = 1.8 V, f <sub>S</sub> = FRCK = 48 kHz, 24-bit digital audio data, Z <sub>L</sub> = ∞, T <sub>A</sub> = 25°C, |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD_N = H, Default I <sup>2</sup> C registers, and audio measurement bandwidth = 20 Hz to 20 kHz (AES17) unless otherwise noted) (continued)                              |  |

| Sy | mbol | Parameter | Conditions | Min | Тур | Max | Unit |  |

|----|------|-----------|------------|-----|-----|-----|------|--|

|----|------|-----------|------------|-----|-----|-----|------|--|

DIGITAL INTERFACE (Includes SCL, SDA, CKI, FRCK, MCK, SD\_N, MAGC, ADDR, DATAI, DATAO, and INT\_N)

#### Shutdown and Standby Timing

| t <sub>SD</sub> Shutdown/Standby Time Time required after volume ramp down. MCK must be present during this period. | 5.0 | 5.1 | - | ms |

|---------------------------------------------------------------------------------------------------------------------|-----|-----|---|----|

|---------------------------------------------------------------------------------------------------------------------|-----|-----|---|----|

#### Global Timing Requirements (Regardless of Mode or Interface)

| f <sub>FRCK</sub>     | FRCK Input Frequency<br>Range      |                                                            | 16 | -       | 96  | kHz |

|-----------------------|------------------------------------|------------------------------------------------------------|----|---------|-----|-----|

| f <sub>MCK</sub>      | MCK Input Frequency                | $f_S = 16, 24, 32, 48, \text{ or } 96 \text{ kHz}$         | -  | 12.2880 | -   | MHz |

|                       | Range                              | f <sub>S</sub> = 44.1 kHz                                  | -  | 11.2896 | -   |     |

| <sup>t</sup> jit, MCK | MCK Jitter                         | Allowable RMS jitter with minimal performance degradation. | -  | -       | 0.1 | ns  |

| t <sub>SETUP</sub>    | FRCK or DATAI to CKI<br>Setup Time |                                                            | 10 | -       | -   | ns  |

| t <sub>HOLD</sub>     | FRCK or DATAI to CKI Hold<br>Time  |                                                            | 0  | -       | -   | ns  |

#### PCM Mode – I<sup>2</sup>S

| f <sub>CKI</sub> | CKI Frequency Range | CKI must be 32, 48, and 64x of FRCK. | 0.512 | - | 6.144 | MHz |

|------------------|---------------------|--------------------------------------|-------|---|-------|-----|

|                  |                     |                                      |       |   |       |     |

#### PCM Mode – TDM (Used for DATAI & DATAO)

|      | Number of Slots Supported | 2     | 1 | 8      | Slots |

|------|---------------------------|-------|---|--------|-------|

| fcкi | CKI Frequency Range       | 0.512 | - | 12.288 | MHz   |

#### PDM Mode (Used for DATAI & DATAO)

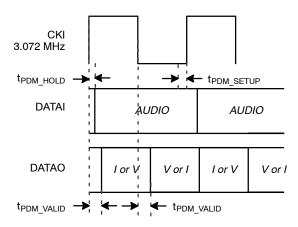

| f <sub>CKI</sub>       | Clock Frequency                                      |                           | -  | 3.072 | - | MHz |

|------------------------|------------------------------------------------------|---------------------------|----|-------|---|-----|

| t <sub>PDM_SETUP</sub> | DATAI to CKI Setup Time                              |                           | 10 | -     | _ | ns  |

| t <sub>PDM_HOLD</sub>  | DATAI to CKI Hold Time                               |                           | 0  | -     | - | ns  |

| <sup>t</sup> PDM_VALID | Time from CKI Transition to<br>DATAO Remaining Valid | C <sub>LOAD</sub> = 15 pF | -  | 17    | - | ns  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. This value is programmable through I<sup>2</sup>C.

5. These specs are intended as reference and are guaranteed by design.

6. CKI is static based upon it not meeting the criteria as outlined in the <u>Clock Requirements</u> section.

7. Absolute minimum gain setting is 3 dB.

8. Does not include MCK

9. In the recommended implementation, VDDEXT is DVDD.

10. Validated by characterization.

Figure 5. PDM Timing Parameters

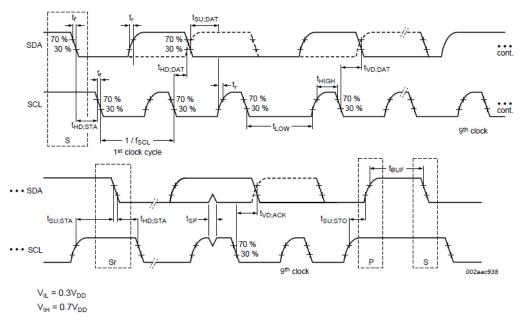

# FAST MODE I<sup>2</sup>C SPECIFICATION

|                     |                                                                        | Fast                                          | t Mode |      |

|---------------------|------------------------------------------------------------------------|-----------------------------------------------|--------|------|

| Symbol              | Parameter                                                              | Min                                           | Max    | Unit |

| f <sub>SCL</sub>    | SCL Clock Frequency                                                    | 0                                             | 1000   | kHz  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                                   | 0.26                                          | -      | μs   |

| t <sub>LOW</sub>    | Low Period of SCL Clock                                                | 0.5                                           | -      | μs   |

| t <sub>HIGH</sub>   | High Period of SCL Clock                                               | 0.26                                          | -      | μs   |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                               | 0.26                                          | -      | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time                                                         | 0                                             | -      | μs   |

| t <sub>SU;DAT</sub> | Data Set-up Time                                                       | 50                                            | -      | μs   |

| t <sub>r</sub>      | Rise Time of SDA and SCL Signals                                       | -                                             | 120    | ns   |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals                                       | 20* (V <sub>DDEXT</sub> /<br>5.5 V) (Note 11) | 120    | ns   |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                         | 0.26                                          | -      | μs   |

| t <sub>BUF</sub>    | Bus-Free Time between STOP and START Conditions                        | 0.5                                           | -      | μs   |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter      | 0                                             | 50     | ns   |

| Cb                  | Capacitive Load for each Bus Line                                      | -                                             | 550    | pF   |

| t <sub>VD-DAT</sub> | Data Valid Time for Data from SCL LOW to SDA HIGH or LOW Output        | 0                                             | 0.45   | μs   |

| t <sub>VD-ACK</sub> | Data Valid Time for acknowledge from SCL LOW to SDA HIGH or LOW Output | 0                                             | 0.45   | μs   |

| V <sub>nL</sub>     | Noise Margin at the LOW Level                                          | 0.1* V <sub>DDEXT</sub><br>(Note 11)          | -      | V    |

| $V_{nH}$            | Noise Margin at the HIGH Level                                         | 0.2* V <sub>DDEXT</sub><br>(Note 11)          | -      | V    |

In the recommended implementation, VDDEXT is DVDD.

Validated by characterization.

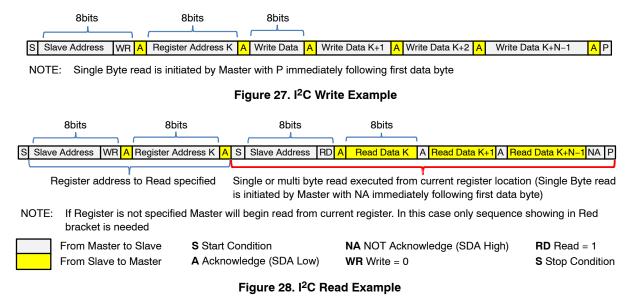

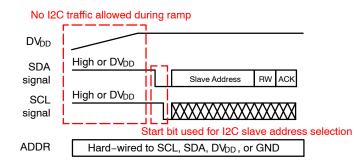

Figure 6. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

#### Table 1. I2C SLAVE ADDRESS

| Name          | Size (Bits) | Bit 7 | Bit 6                                                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------------|-------------|-------|--------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Slave Address | 8           |       | See Table 5 in <u>I<sup>2</sup>C Slave Address Selection</u> |       |       |       |       |       |       |  |

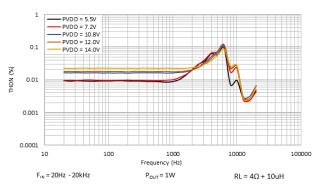

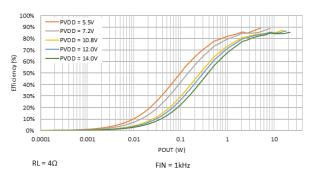

# **TYPICAL PERFORMANCE CHARACTERISTICS**

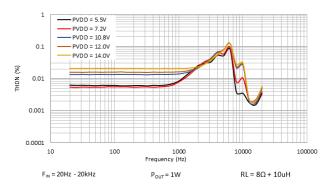

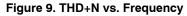

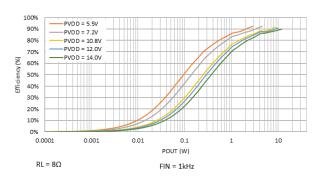

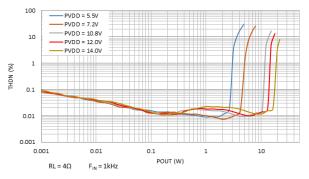

(Unless otherwise noted:  $Z_L = 8 \Omega + 10 \mu$ H, f = 1 kHz, Audio measurement bandwidth 20 Hz to 20 KHz (AES17), PV<sub>DD</sub> = 12 V, T<sub>A</sub> = 25°C, Typical external component values)

Figure 11. Efficiency vs. Output Power

Figure 8. THD+N vs. Output Power

Figure 10. THD+N vs. Frequency

Figure 12. Efficiency vs Output Power

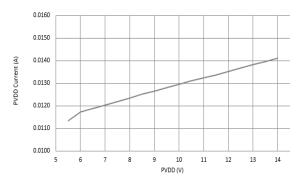

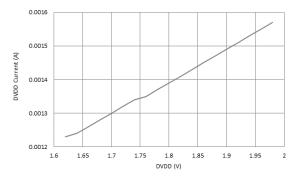

# **TYPICAL PERFORMANCE CHARACTERISTICS**

(Unless otherwise noted:  $Z_L = 8 \ \Omega + 10 \ \mu$ H, f = 1 kHz, Audio measurement bandwidth 20 Hz to 20 KHz (AES17),  $PV_{DD} = 12 \ V$ ,  $T_A = 25^{\circ}$ C, Typical external component values) (continued)

Figure 13. P<sub>VDD</sub> Idle Current vs. P<sub>VDD</sub>

4.5E-05

4.4E-05

4.3E-05

4.2E-05

4.1E-05

4.0E-05

3.9E-05

3.8E-05

3.7E-05

3.6E-05

5

6 7

Idle Channel Noise (A-Weighted) (V)

Figure 14. D<sub>VDD</sub> Idle Current vs. D<sub>VDD</sub>

Figure 15. Idle Channel Noise (A-Weighed) vs. PVDD

9

PVDD(V)

10 11

12

13

14

8

Figure 16. Vsense Gain Deviation vs. Temperature

Figure 17. Isense Gain Deviation vs. Temperature

# THEORY OF OPERATION

The ONA10IV is an audio endpoint, meaning that it includes the converters and amplifiers that translate the digital audio input into an analog audio output across the speaker and then senses that analog signal, amplifies, converts it to digital, and communicates what it senses to the host. This driver/sensor loop allows the host to optimize the audio speaker system.

While the theory of operation does not vary, there are multiple interface formats and device configurations that the ONA10IV can support. The remainder of this section describes the operating requirements and configurations. The list below summarizes the interface options available to the host:

Pulse Code Modulated (PCM)

- Formats: I<sup>2</sup>S, Left–Justified, and TDM

- Sampling (f<sub>FRCK</sub>): 16 kHz to 96 kHz

- Slot Width: 16-, 24, or 32 bits

- f<sub>CKI</sub>: 512 kHz to 6.144 (I<sup>2</sup>S)/12.288 MHz (TDM)

- f<sub>MCK</sub>: 12.288 MHz or 11.2896 MHz (can be phase asynchronous to CKI/FRCK)

- TDM configuration can be adjusted so long as:

- *f<sub>CKI</sub>* = # of slots \* slot width \* sampling frequency

- The digital formats are all clocked using MCK, CKI and FRCK. The digital input clocking is also applicable to the following interfaces:

- Digital Audio Input (DATAI Pin)

- Digital Sense Output (DATAO Pin)

- MAGC Bidirectional Bus (MAGC Pin)

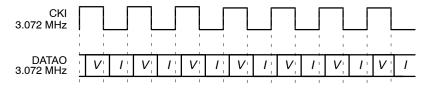

# Pulse Density Modulated (PDM)

- f<sub>CKI</sub>: 3.072 MHz

- f<sub>MCK</sub>: 12.288 MHz

- This modulation scheme is simpler and only clocked with CKI. The MAGC signal does not support PDM output and, if the MAGC feature is utilized, a FRCK is still required.

# **Power Supplies**

The ONA10IV uses two power supplies,  $DV_{DD}$  (1.8 V regulated supply) and  $PV_{DD}$ , (can be a regulated supply between 5.5 V to 14 V or a stacked cell battery (2S, 5.5 V to 9 V or 3S, 7.5 V to 13.5 V)) and generates a third,  $V_{REG}$  (5 V internally regulated supply).

# DV<sub>DD</sub> [1.62 V to 1.98 V]

$DV_{DD}$  is intended to match the I/O supply of the host such that no translators are required in the board design. It provides power to the digital interface and device controls. If  $DV_{DD}$  is 0 V, the chip cannot be communicated with, the I<sup>2</sup>C registers are in reset, the  $PV_{DD}$  supply current is below  $I_{SD}$  (max.), and the I/O leakage current is less than  $I_{OFF_DVDD}$  (max.).

# PV<sub>DD</sub> [5.50 V to 14.00 V]

$PV_{DD}$  provides a high voltage rail that supplies the H–Bridge of the amplifier to drive the speaker. It is also used to generate the  $V_{REG}$  supply.

If  $PV_{DD}$  is below  $V_{LIM}$  (shutdown) and not in shutdown, the chip enables only circuitry associated with detecting  $PV_{DD}$ .  $DV_{DD}$  supply current is  $I_{DVDD}$  (typ.), and the speaker interface pins (OUT+, OUT-, VSNS+, VSNS-) each have leakage less than  $I_{OFF}$  PVDD (max.).

# V<sub>REG</sub> [~5.00 V]

$V_{REG}$  is an internally generated supply that provides power to most of the analog circuitry. It is 0 V when the part is in shutdown (SD\_N or SD\_N bit low), PV<sub>DD</sub> is below  $V_{LIM}$  (shutdown), or DV<sub>DD</sub> is below  $V_{LIM}$  (shutdown).

# **POWER/ENABLE SEQUENCING**

The following power sequence is required on power-up:

- 1.  $PV_{DD}$  is the first power supply applied to the device. 2. With SD, N low and PV share  $V_{DD}$  (receiver)

- 2. With SD\_N low and  $PV_{DD}$  above  $V_{LIM}$  (recovery),  $DV_{DD}$  is applied with SCL and SDA always above  $V_{IH}$ .\*

- 3. Wait until  $DV_{DD}$  is above  $V_{LIM}$  (recovery).

- 4. Remove chip from a hard shutdown by driving the SD\_N pin high.

- 5. I<sup>2</sup>C communication is available after 10  $\mu$ s.

- 6. Remove chip from a soft shutdown by writing a 1 to the SD N bit in register 0x01: PWR CTRL.

- 7. With MCK applied any time prior to this point, wait  $t_{WU}$  before transmitting digital audio.

\*In the above sequence, SD\_N does not have to be an independent signal – it can be tied to  $DV_{DD}$ .

# Power States

The ONA10IV has three power states when  $DV_{DD}$  is present: SHUTDOWN, STANDBY, and ACTIVE. These are described below.

# SHUTDOWN Power State

("Hard":  $SD_N < V_{IL}$  or "Soft":  $SD_N$  bit is 0)

The SHUTDOWN power state provides the lowest possible supply current,  $I_{SD}$ . In shutdown, all non– $I^2C$  digital I/Os and the speaker interface pins are all below their  $I_{OZ}$  (max) specifications. SHUTDOWN can be accessed through a "soft" shutdown (SD\_N bit is 0) or a "hard" shutdown (SD N < V<sub>II</sub>).

In "Hard" shutdown, the I<sup>2</sup>C registers are reset and I<sup>2</sup>C is not operational. The minimum time for SD\_N to be low is indicated by "Soft" shutdown will not reset the registers and allow I<sup>2</sup>C communication, but will have slightly higher leakage current on D<sub>VDD</sub> (adds 5 – 10  $\mu$ A at higher temperatures).

# STANDBY Power State

A STANDBY power state can be entered through  $I^2C$  (from the PWR\_CTRL register), if CKI is not toggling, or after a timeout period from an AGC or error state. If STANDBY is entered into from a timeout period, the part

can recover by entering RESET or exiting the automatic mode that triggered the timeout period (i.e. – disable AGC\_TIMEOUT or ARCV setting). This mode is not as low-power as shutdown, but disables the DAC, mutes the amplifier, and disables all sense circuitry.

| Power State | Error State                   | Condition to Enter State                                                | Available Operation                          |  |  |

|-------------|-------------------------------|-------------------------------------------------------------------------|----------------------------------------------|--|--|

| RESET       | N/A                           | DVDD < V <sub>LIM</sub>                                                 | None                                         |  |  |

|             |                               | SD_N Input < V <sub>IL</sub>                                            |                                              |  |  |

|             |                               | Writing 1 to RST bit                                                    |                                              |  |  |

| SHUTDOWN    | N/A                           | SD_N Input < V <sub>IL</sub>                                            | I2C Communication when                       |  |  |

|             |                               | SD_N bit is 0                                                           | SD_N Input > V <sub>IH</sub>                 |  |  |

|             | Under-Voltage (VERR)          | PVDD < V <sub>LIM</sub><br>(Note, I <sub>PVDD</sub> > I <sub>SD</sub> ) |                                              |  |  |

| STANDBY     | N/A                           | STBY bit is 1                                                           | I2C Communication Only                       |  |  |

|             |                               | Exceeding ARVC attempts or<br>AGC_TIMEOUT Time                          |                                              |  |  |

| ACTIVE      | None                          | N/A                                                                     | All                                          |  |  |

|             | AGC Active                    | PVDD < BATT_ATH Register<br>Setting                                     | Speaker Drive Gain Limited by<br>AGC_MAX_ATT |  |  |

|             | Thermal Foldback Active       | $T_J \ge T_ATH$ Register Setting                                        | Maximum Volume Limited                       |  |  |

|             | Over-Temperature Error (TERR) | $T_J \geq T_{LIM}$                                                      | I2C Communication Only                       |  |  |

|             | Over-Current Error (IERR)     | I <sub>OUT±</sub> > I <sub>LIM</sub>                                    | I2C Communication Only                       |  |  |

The following sections describe operation in the "ACTIVE Power State"...

# DIGITAL AUDIO INPUT

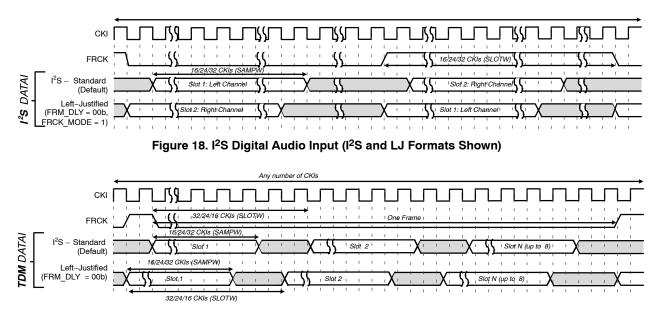

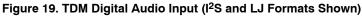

The digital audio input can be configured for a single-bit Pulse Density Modulation (PDM) stream or in a Pulse Code Modulation (PCM) format such as: I2S, Left Justified (LJ), or Time Divided Multiplexing (TDM). Examples of these digital audio formats are shown in the diagrams in Figure 18 (I2S) and Figure 19 (TDM).

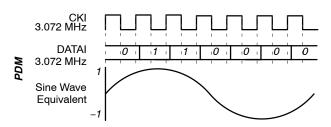

#### **PDM Digital Audio Operation**

In PDM mode, audio data on the DATAI pin is clocked in by CKI. Pulse Density Modulation (PDM) is a common output of ADCs and, in essence, is the audio signal oversampled by  $f_{CKI}$ . An example of this format is shown below:

Figure 20. PDM Digital Audio Input

The PDM data that is received on DATAI is mapped into the DAC. This mapping is configurable via I2C in the register under PDM\_DAC\_MAP. Additionally, a separate amplifier gain for PDM mode can be set in the same register under PDM\_AMP\_GAIN. When switching into PDM mode this value will be used rather than the PCM\_AMP\_GAIN setting. A time of  $t_{SW_MOD}$ , is required to switch between the PCM and PDM interfaces. It is expected that the host will manage any sequencing required between digital audio formats to avoid undesirable audible effects.

#### PCM Digital Audio Operation

Audio data on the DATAI pin is clocked in by CKI with the most significant bit appearing first. Audio samples are two's complement Pulse Code Modulation (PCM) and are 16 bits, 24 bits, or 32 bits in width as defined by the SAMPW register bits. SLOTW defines the number of CKI periods between each sample. For example, sample width may be 24 bits (SAMPW = 01b), while slot width may be 32 bits (SLOTW = 10b). After every 24 bit sample, there are an additional 8 bits (that are ignored by the DAC) before the next sample begins. Sample length must be equal to or less than slot width.

Sample rate,  $f_s$ , is equal to the FRCK frequency. In addition, one data "frame" is equal to one FRCK period.

PCM audio data is internally buffered and fed to the DAC at the end of the audio frame. This is done to keep separate amplifiers in phase with each other in multi–slot systems. The slot that the ONA10IV responds to can be selected using the A\_SLOT setting in the register.

#### I2S Digital Audio Interface

For I<sup>2</sup>S or left justified data (DAI = 00b), each frame contains 2 separate slots of audio – left channel and right channel. In each frame, the left channel is always transmitted first, and the right channel is always second. FRCK's duty cycle is always 50%.

Figure 18 shows the I<sup>2</sup>S digital audio interface with two different formats on DATAI: I<sup>2</sup>S (traditional) and left-justified. For "left justified", FRCK is high during left channel audio data and low during right slot audio data (FRCK\_MODE = 1). Audio samples are left justified so that the first data bit appears at the first CKI period after a FRCK edge (FRM\_DLY = 00b). Data is valid on the rising edges of CKI (BEDGE\_DAI = 1). If the audio sample width is 24 bits (SAMPW = 01b), but the data slot width is 32 bits (SLOTW = 10b) the 8 bits after the audio sample are ignored and one FRCK period is 64 CKI periods. The chip will respond to left or right channel audio data based on the A\_SLOT setting in the register.

For "I<sup>2</sup>S" formatted I<sup>2</sup>S digital audio, it is similar to left justified except that the frame is delayed by one CKI (FRM\_DLY = 01) and FRCK is low for left slot audio data and high for right slot audio data (FRM\_POL = 0). Note that the frame still begins with left channel audio data. If the frame were to begin with right channel audio data, left and right audio would be out of phase with each other by 1/2 fS. In this example, audio sample width is 16 bits wide (SAMPW = 00b) but the slot width is still 32 bits (SLOTW = 10b) and FRCK period is still 64 CKI periods. Only right channel audio data is used (A\_SLOT = 0000b).

#### TDM Digital Audio Interface

One TDM "frame" can contain 2, 4, or 8 separate slots of audio. In each frame, slot 1 is transmitted first; slot 2 is transmitted second, and so on. FRCK signals the beginning of a frame with a single pulse that is 1 CKI period wide. This can also be changed in  $I^2C$  through the FRCK\_MODE settings.

PCM audio data is internally buffered and fed to the DAC at the end of the audio frame. This is done to keep separate amplifiers in phase with each other in multi–slot systems. The data slot that the ONA10IV receives can be selected using the A\_SLOT register.

#### **Clock Requirements**

The ONA10IV requires a master clock that is 12.288 MHz or 11.2896 MHz (depending on if the sample rate is 44.1 kHz).

The bit (CKI) and frame (FRCK) clock need to match what has been programmed in the FS register (0x06) such that the following equation is valid:

$$f_{S} = f_{FRCK} = \frac{f_{CKI}}{N_{Channels} \cdot Slot_{Width}}$$

(eq. 1)

In addition, FRCK frequency must always be within recommended operating conditions. If FRCK fails to meet these criteria, a clock error is detected (CERR) and the class–D amplifier will shutdown (see Interrupts & Fault Recovery section).

# Volume Control

Volume can be ramped anytime the driving path is enabled or the volume setting changed. This minimizes pop if audio data is nonzero. If AVOLUP is set to 1 and the driving path is enabled, then the volume is ramped from mute up to MAX\_VOL in VOL\_RAMP. If the thermal fold back limit is reached before the volume reaches the MAX\_VOL setting, the startup ramp releases control of MAX\_VOL. If AVOLUP = 0, the volume is immediately set to MAX\_VOL upon enable.

If AVOLDN is set to 1 and the driving path is disabled, the volume is ramped from its present value down to mute in VOL\_RAMP. During the ramp, the detection of a thermal error is allowed to accelerate the downward ramp, but it is not allowed to increase the volume. If AVOLDN = 0, volume is immediately set to mute upon disable.

Further, if the maximum volume setting is changed, then the volume will also be ramped up or down as necessary.

Shutdown conditions caused by PVDD < VLIM or class–D amplifier over–current are immediate and unaffected by the VOL\_RAMP setting.

#### Interrupts & Fault Recovery

The ONA10IV contains multiple fault flags that will drive the INT\_N pin low when the status of the flag changes to alert the host and prevent a system failure. The flags are contained in the register and can be cleared by writing a "1" in the flagged bit. The following faults are detected and flagged:

- Under-Voltage Limit (VERR\_I)

- Over Output current Limit (IERR I)

- Over-Temperature Limit (TERR\_I)

- Absent or Insufficient Clocks (CERR I)

Additionally, there are interrupts to communicate that Automatic gain correction (AGC\_I) or thermal foldback(TFB I) is active.

Where the interrupt flag is sent to indicate a change in an error state, the error status register always shows the active status of the error.

If  $PV_{DD}$  falls below  $V_{LIM}$  (shutdown), the device goes into an under-voltage error state that is similar to shutdown. The device remains off until  $PV_{DD}$  rises above  $V_{LIM}$ (recovery). I<sup>2</sup>C registers are reset to default values.

If the output current of the class–D amplifier exceeds  $I_{LIM}$  (shutdown), OUT+ and OUT– are high impedance and the

IERR bit is set to 1. The I<sup>2</sup>C port remains active and I<sup>2</sup>C register values are preserved. If ARCV = 1, the class–D amplifier attempts to restart every 1 s until the fault condition is removed. If ARCV = 0, the class–D amplifier remains off until SD\_N or MRCV are toggled to successfully restart the amplifier without an over–current event.

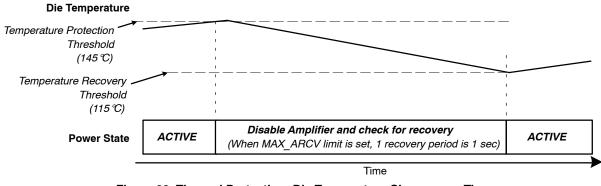

If the junction temperature meets or exceeds  $T_{LIM}$  (shutdown), OUT+ and OUT- are disabled, and the TERR bit is set to 1. The I<sup>2</sup>C port remains active and I<sup>2</sup>C register values are preserved. If ARCV = 1, the class–D amplifier will restart after the die temperature meets or falls below  $T_{LIM}$  (recovery). If the MAX\_ARCV is limited, then every 1 s period is counted as a recovery attempt. If ARCV = 0, the class–D amplifier remains off and the TERR status bit is set to 1 until SD\_N or MRCV are toggled to successfully restart the amplifier without an over–temperature event. See the "Thermal Foldback" section for more detail.

If a clock error is detected (see the <u>Clock Requirements</u> section), OUT+ and OUT– are high impedance, and the CERR bit is set to 1. The I<sup>2</sup>C port remains active and I<sup>2</sup>C register values are preserved. If ARCV = 1, the class–D amplifier will turn on when all clocks are valid. If ARCV = 0, the class–D amplifier will remain off until SD\_N or MRCV are toggled to successfully restart the amplifier without a clock error event.

During a CERR, the DATAO and MAGC buses will maintain their last driving state.

# Low EMI

The class–D amplifier's low EMI design allows the OUT+ and OUT– pins to be connected directly to a speaker without an output filter.

Edge Rate Control minimizes EMI generated by the high–current switching waveform of the Class–D amplifier output. One of the main contributors to EMI generated by Class–D amplifiers is the high–frequency energy produced by rapid (large dV/dt) transitions at the edges of the switching waveform. ERC suppresses the high–frequency component of the switching waveform by extending the rise and fall times of the output FET transitions at all power levels. Rise and fall rates are set to a default of 3.5 V/ns and can be reprogrammed through I<sup>2</sup>C.

Spread spectrum switching can also be adjusted through I<sup>2</sup>C.

# Thermal Foldback