# **Real-Time Clock (RTC)**

### **Features**

- ➤ Direct clock/calendar replacement for IBM<sup>®</sup> AT-compatible computers and other applications

- ➤ 2.7-5.5V operation (bq3285LC); 4.5-5.5V operation (bq3285EC)

- ➤ 242 bytes of general nonvolatile storage

- ➤ Dedicated 32.768kHz output pin

- ➤ System wake-up capability alarm interrupt output active in battery-backup mode

- ➤ Less than 0.5µA load under battery operation

- ➤ Selectable Intel or Motorola bus timing

- ➤ 24-pin plastic SOIC or SSOP

## **General Description**

The CMOS bq3285EC/LC is a low-power microprocessor peripheral providing a time-of-day clock and 100-year calendar with alarm features and battery operation. The architecture is based on the bq3285/7 RTC with added features: low-voltage operation, 32.768kHz output, and an extra 128 bytes of CMOS.

A 32.768kHz output is available for sustaining power-management activities. The bq3285EC 32kHz output is always on whenever  $V_{CC}$  is valid. For the bq3285LC, the output is on when the oscillator is turned on. In  $V_{CC}$  standby mode, the 32kHz is active, and the bq3285LC typically draws  $100\mu A$  while the bq3285EC typically draws  $300\mu A$ . Wake-up capability is provided by an alarm interrupt, which is active

in battery-backup mode. In battery backup mode, current drain is less than 500nA.

The bq3285EC/LC write-protects the clock, calendar, and storage registers during power failure. A backup battery then maintains data and operates the clock and calendar.

The bq3285EC/LC is a fully compatible real-time clock for IBM AT-compatible computers and other applications. The only external components are a 32.768kHz crystal and a backup battery.

The bq3285EC is intended for use in 5V systems. The bq3285LC is intended for use in 3V systems; the bq3285LC, however, may also operate at 5V and then go into a 3V power-down state, write-protecting as if in a 3V system.

## **Pin Connections**

#### МОТ ☐ 1 24 □ vcc Х1 Ц 23 □ 32k 2 X2 🗖 22 ☐ EXTRAM 3 AD<sub>0</sub> ☐ 21 RCL AD<sub>1</sub> d 5 20 ⊟ вс AD<sub>2</sub> ☐ 6 19 Ь int AD3 ☐ 7 18 □ RST AD4 ☐ 8 17 □ DS b∨ss AD<sub>5</sub> $\square$ 9 16 $\Box$ R/ $\overline{W}$ AD<sub>6</sub> □ 10 15 AD7 🗆 11 14 b as Vss ☐ b cs 24-Pin SSOP July 1996

### **Pin Names**

| AD <sub>0</sub> –AD <sub>7</sub> | Multiplexed address/<br>data input/output | 32K      | 32.768kHz output     |

|----------------------------------|-------------------------------------------|----------|----------------------|

|                                  | 1 1                                       | EXTRAM   | Extended RAM enable  |

| MOT                              | Bus type select input                     | RCL      | RAM clear input      |

| CS                               | Chip select input                         | ВС       | 3V backup cell input |

| AS                               | Address strobe input                      |          |                      |

| DS                               | Data strobe input                         | X1–X2    | Crystal inputs       |

| $R/\overline{W}$                 | Read/write input                          | $V_{CC}$ | Power supply         |

|                                  | •                                         | $V_{SS}$ | Ground               |

| INT                              | Interrupt request output                  |          |                      |

| RST                              | Reset input                               |          |                      |

|                                  |                                           |          |                      |

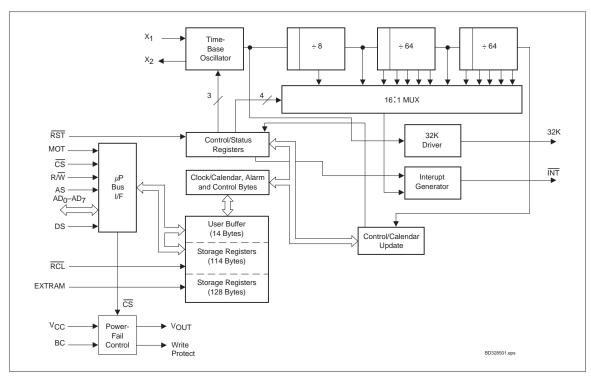

## **Block Diagram**

### **Pin Descriptions**

### MOT Bus type select input

MOT selects bus timing for either Motorola or Intel architecture. This pin should be tied to  $V_{\rm CC}$  for Motorola timing or to  $V_{\rm SS}$  for Intel timing (see Table 1). The setting should not be changed during system operation. MOT is internally pulled low by a 30K  $\Omega$  resistor.

Table 1. Bus Setup

| Bus<br>Type | MOT<br>Level    | DS<br>Equivalent                                    | R/W<br>Equivalent       | AS<br>Equivalent |

|-------------|-----------------|-----------------------------------------------------|-------------------------|------------------|

| Motorola    | V <sub>CC</sub> | DS, E, or $\Phi 2$                                  | R/W                     | AS               |

| Intel       | V <sub>SS</sub> | $\overline{\frac{RD}{MEMR}}$ , or $\overline{I/OR}$ | WR,<br>MEMW, or<br>I/OW | ALE              |

# AD<sub>0</sub>-AD<sub>7</sub> Multiplexed address/data input/output

The bq3285EC/LC bus cycle consists of two phases: the address phase and the data-transfer phase. The address phase precedes the data-transfer phase. During the address phase, an address placed on  $AD_0$ – $AD_7$  and EXTRAM is latched into the bq3285EC/LC on the falling edge of the AS signal. During the data-transfer phase of the bus cycle, the  $AD_0$ – $AD_7$  pins serve as a bidirectional data bus.

#### Address strobe input

AS serves to demultiplex the address/data bus. The falling edge of AS latches the address on AD0–AD7 and EXTRAM. This demultiplexing process is independent of the  $\overline{\text{CS}}$  signal. For DIP and SOIC packages with MOT = Vss, the AS input is provided a signal similar to ALE in an Intel-based system.

July 1996

AS

#### DS Data strobe input

When MOT =  $V_{CC}$ , DS controls data transfer during a bq3285EC/LC bus cycle. During a read cycle, the bq3285EC/LC drives the bus after the rising edge on DS. During a write cycle, the falling edge on DS is used to latch write data into the chip.

When MOT =  $V_{SS}$ , the DS input is provided a signal similar to  $\overline{RD}$ ,  $\overline{MEMR}$ , or  $\overline{I/OR}$  in an Intel-based system. The falling edge on DS is used to enable the outputs during a read cycle.

#### R/W Read/write input

When MOT =  $V_{CC}$ , the level on  $R/\overline{W}$  identifies the direction of data transfer. A high level on  $R/\overline{W}$  indicates a read bus cycle, whereas a low on this pin indicates a write bus cycle.

When  $MOT = V_{SS}$ ,  $R/\overline{W}$  is provided a signal similar to  $\overline{WR}$ ,  $\overline{MEMW}$ , or I/OW in an Intelbased system. The rising edge on  $R/\overline{W}$  latches data into the bq3285EC/LC.

#### **CS** Chip select input

$\overline{\text{CS}}$  should be driven low and held stable during the data-transfer phase of a bus cycle accessing the bq3285EC/LC.

### **INT** Interrupt request output

$\overline{INT}$  is an open-drain output. This allows alarm  $\overline{INT}$  to be valid in battery-backup mode. To use this feature, connect  $\overline{INT}$  through a resistor to a power supply other than  $V_{CC}.$   $\overline{INT}$  is asserted low when any event flag is set and the corresponding event enable bit is also set.  $\overline{INT}$  becomes high-impedance whenever register C is read (see the Control/Status Registers section).

#### 32K 32.768 kHz output

32K provides a buffered 32.768 kHz output. The frequency remains on and fixed at 32.768kHz as long as  $V_{\rm CC}$  is valid.

#### EXTRAM Extended RAM enable

Enables 128 bytes of additional nonvolatile SRAM. It is connected internally to a  $30k\Omega$  pull-down resistor. To access the RTC registers, EXTRAM must be low.

#### RCL RAM clear input

A low level on the  $\overline{RCL}$  pin causes the contents of each of the 242 storage bytes to be set to FF(hex). The contents of the clock and control registers are unaffected. This pin should be used as a user-interface input (pushbutton to ground) and not connected to the output of any active component.  $\overline{RCL}$  input is only recognized when held low for at least 125ms in the presence of  $V_{CC}.$  Using RAM clear does not affect the battery load. This pin is connected internally to a  $30k\Omega$  pull-up resistor.

#### BC 3V backup cell input

BC should be connected to a 3V backup cell for RTC operation and storage register non-volatility in the absence of system power. When  $V_{CC}$  slews down past  $V_{BC}$  (3V typical), the integral control circuitry switches the power source to BC. When  $V_{CC}$  returns above  $V_{BC}$ , the power source is switched to  $V_{CC}$

Upon power-up, a voltage within the  $V_{BC}$  range must be present on the BC pin for the oscillator to start up.

### RST Reset input

The bq3285EC/LC is reset when  $\overline{RST}$  is pulled low. When reset,  $\overline{INT}$  becomes high impedance, and the bq3285EC/LC is not accessible. Table 4 in the Control/Status Registers section lists the register bits that are cleared by a reset.

Reset may be disabled by connecting  $\overline{RST}$  to  $V_{CC}$ . This allows the control bits to retain their states through power-down/power-up cycles.

### X1-X2 Crystal inputs

The X1–X2 inputs are provided for an external 32.768kHz quartz crystal, Daiwa DT-26 or equivalent, with 6pF load capacitance. A trimming capacitor may be necessary for extremely precise time-base generation.

In the absence of a crystal, a 32.768kHz waveform can be fed into the X1 input.

## **Functional Description**

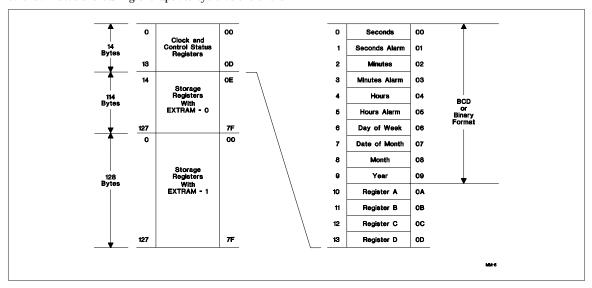

### **Address Map**

The bq3285EC/LC provides 14 bytes of clock and control/status registers and 242 bytes of general nonvolatile storage. Figure 1 illustrates the address map for the bq3285EC/LC.

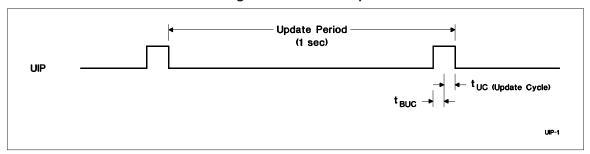

## **Update Period**

The update period for the bq3285EC/LC is one second. The bq3285EC/LC updates the contents of the clock and calendar locations during the update cycle at the end of

each update period (see Figure 2). The alarm flag bit may also be set during the update cycle.

The bq3285EC/LC copies the local register updates into the user buffer accessed by the host processor. When a 1 is written to the update transfer inhibit bit (UTI) in register B, the user copy of the clock and calendar bytes remains unchanged, while the local copy of the same bytes continues to be updated every second.

The update-in-progress bit (UIP) in register A is set  $t_{BUC}$  time before the beginning of an update cycle (see Figure 2). This bit is cleared and the update-complete flag (UF) is set at the end of the update cycle.

Figure 1. Address Map

Figure 2. Update Period Timing and UIP

# **Programming the RTC**

The time-of-day, alarm, and calendar bytes can be written in either the BCD or binary format (see Table 2).

These steps may be followed to program the time, alarm, and calendar:

- 1. Modify the contents of register B:

- Write a 1 to the UTI bit to prevent transfers between RTC bytes and user buffer.

- Write the appropriate value to the data format (DF) bit to select BCD or binary format for all time, alarm, and calendar bytes.

- c. Write the appropriate value to the hour format (HF) bit.

- 2. Write new values to all the time, alarm, and calendar locations.

- 3. Clear the UTI bit to allow update transfers.

On the next update cycle, the RTC updates all  $10\ \text{bytes}$  in the selected format.

Table 2. Time, Alarm, and Calendar Formats

|         |                             |         | Range                     |                           |

|---------|-----------------------------|---------|---------------------------|---------------------------|

| Address | RTC Bytes                   | Decimal | Binary                    | Binary-Coded<br>Decimal   |

| 0       | Seconds                     | 0-59    | 00H-3BH                   | 00H-59H                   |

| 1       | Seconds alarm               | 0-59    | 00H-3BH                   | 00H-59H                   |

| 2       | Minutes                     | 0-59    | 00H-3BH                   | 00H-59H                   |

| 3       | Minutes alarm               | 0-59    | 00H-3BH                   | 00H-59H                   |

| 4       | Hours, 12-hour format       | 1–12    | 01H-OCH AM;<br>81H-8CH PM | 01H-12H AM;<br>81H-92H PM |

|         | Hours, 24-hour format       | 0-23    | 00H-17H                   | 00H-23H                   |

| 5       | Hours alarm, 12-hour format | 1–12    | 01H-OCH AM;<br>81H-8CH PM | 01H-12H AM;<br>81H-92H PM |

|         | Hours alarm, 24-hour format | 0-23    | 00H-17H                   | 00H-23H                   |

| 6       | Day of week (1=Sunday)      | 1–7     | 01H-07H                   | 01H-07H                   |

| 7       | Day of month                | 1-31    | 01H-1FH                   | 01H-31H                   |

| 8       | Month                       | 1–12    | 01H-0CH                   | 01H-12H                   |

| 9       | Year                        | 0-99    | 00H-63H                   | 00H-99H                   |

## 32kHz Output

The bq3285EC/LC provides for a 32.768kHz output. For the bq3285EC, the output is always active whenever  $V_{\rm CC}$  is valid ( $V_{\rm PFD}+t_{\rm CSR}$ ). The bq3285EC output is not affected by the bit settings in Register A. Time-keeping aspects, however, still require setting OS0-OS2. The bq3285LC output is active when the oscillator is turned on by setting the OSC0-OSC2 bits in Register A.

### Interrupts

The bq3285EC/LC allows three individually selected interrupt events to generate an interrupt request. These three interrupt events are:

- The periodic interrupt, programmable to occur once every 122µs to 500ms.

- The alarm interrupt, programmable to occur once per second to once per day, is active in battery-backup mode, providing a "wake-up" feature.

- The update-ended interrupt, which occurs at the end of each update cycle.

Each of the three interrupt events is enabled by an individual interrupt-enable bit in register B. When an event occurs, its event flag bit in register C is set. If the corresponding event enable bit is also set, then an interrupt request is generated. The interrupt request flag bit (INTF) of register C is set with every interrupt request. Reading register C clears all flag bits, including INTF, and makes INT high-impedance.

Two methods can be used to process bq3285EC/LC interrupt events:

- Enable interrupt events and use the interrupt request output to invoke an interrupt service routine.

- Do not enable the interrupts and use a polling routine to periodically check the status of the flag bits.

The individual interrupt sources are described in detail in the following sections.

**Table 3. Periodic Interrupt Rate**

|      |      | R    | egister A Bi | ts  |     |     | Periodic Inte             | errupt |

|------|------|------|--------------|-----|-----|-----|---------------------------|--------|

| OSC2 | OSC1 | OSC0 | RS3          | RS2 | RS1 | RS0 | Period                    | Units  |

| 0    | 1    | 0    | 0            | 0   | 0   | 0   | None                      |        |

| 0    | 1    | 0    | 0            | 0   | 0   | 1   | 3.90625                   | ms     |

| 0    | 1    | 0    | 0            | 0   | 1   | 0   | 7.8125                    | ms     |

| 0    | 1    | 0    | 0            | 0   | 1   | 1   | 122.070                   | μs     |

| 0    | 1    | 0    | 0            | 1   | 0   | 0   | 244.141                   | μs     |

| 0    | 1    | 0    | 0            | 1   | 0   | 1   | 488.281                   | μs     |

| 0    | 1    | 0    | 0            | 1   | 1   | 0   | 976.5625                  | μs     |

| 0    | 1    | 0    | 0            | 1   | 1   | 1   | 1.95315                   | ms     |

| 0    | 1    | 0    | 1            | 0   | 0   | 0   | 3.90625                   | ms     |

| 0    | 1    | 0    | 1            | 0   | 0   | 1   | 7.8125                    | ms     |

| 0    | 1    | 0    | 1            | 0   | 1   | 0   | 15.625                    | ms     |

| 0    | 1    | 0    | 1            | 0   | 1   | 1   | 31.25                     | ms     |

| 0    | 1    | 0    | 1            | 1   | 0   | 0   | 62.5                      | ms     |

| 0    | 1    | 0    | 1            | 1   | 0   | 1   | 125                       | ms     |

| 0    | 1    | 0    | 1            | 1   | 1   | 0   | 250                       | ms     |

| 0    | 1    | 0    | 1            | 1   | 1   | 1   | 500                       | ms     |

| 0    | 1    | 1    | X            | X   | X   | X   | same as above<br>by RS3-R |        |

### **Periodic Interrupt**

If the periodic interrupt event is enabled by writing a 1 to the periodic interrupt enable bit (PIE) in register C, an interrupt request is generated once every  $122\mu s$  to 500ms. The period between interrupts is selected with bits RS3-RS0 in register A (see Table 3).

#### **Alarm Interrupt**

The alarm interrupt is active in battery-backup mode, providing a "wake-up" capability. During each update cycle, the RTC compares the hours, minutes, and seconds bytes with the three corresponding alarm bytes. If a match of all bytes is found, the alarm interrupt event flag bit, AF in register C, is set to 1. If the alarm event is enabled, an interrupt request is generated.

An alarm byte may be removed from the comparison by setting it to a "don't care" state. An alarm byte is set to a "don't care" state by writing a 1 to each of its two most-significant bits. A "don't care" state may be used to select the frequency of alarm interrupt events as follows:

- If none of the three alarm bytes is "don't care," the frequency is once per day, when hours, minutes, and seconds match.

- If only the hour alarm byte is "don't care," the frequency is once per hour, when minutes and seconds match.

- If only the hour and minute alarm bytes are "don't care," the frequency is once per minute, when seconds match.

- If the hour, minute, and second alarm bytes are "don't care," the frequency is once per second.

### **Update Cycle Interrupt**

The update cycle ended flag bit (UF) in register C is set to a 1 at the end of an update cycle. If the update interrupt enable bit (UIE) of register B is 1, and the update transfer inhibit bit (UTI) in register B is 0, then an interrupt request is generated at the end of each update cycle.

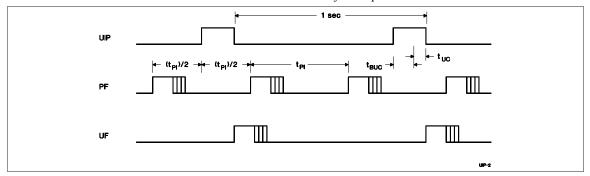

## Accessing RTC bytes

The EXTRAM pin must be low to access the RTC registers. Time and calendar bytes read during an update cycle may be in error. Three methods to access the time and calendar bytes without ambiguity are:

- Enable the update interrupt event to generate interrupt requests at the end of the update cycle. The interrupt handler has a maximum of 999ms to access the clock bytes before the next update cycle begins (see Figure 3).

- Poll the update-in-progress bit (UIP) in register A. If UIP = 0, the polling routine has a minimum of  $t_{BUC}$  time to access the clock bytes (see Figure 3).

- Use the periodic interrupt event to generate interrupt requests every  $t_{PI}$  time, such that UIP = 1 always occurs between the periodic interrupts. The interrupt handler has a minimum of  $t_{PI}/2 + t_{BUC}$  time to access the clock bytes (see Figure 3).

#### **Oscillator Control**

When power is first applied to the bq3285LC and  $V_{CC}$  is above  $V_{PFD}$ , the internal oscillator and frequency divider are turned on by writing a 010 pattern to bits 4 through 6 of register A. A pattern of 11X turns the oscillator on but keeps the frequency divider disabled. Any other pattern to these bits keeps the oscillator off. A pattern of 010 must be set for the bq3285EC/LC to keep time in battery backup mode.

Figure 3. Update-Ended/Periodic Interrupt Relationship

## Power-Down/Power-Up Cycle

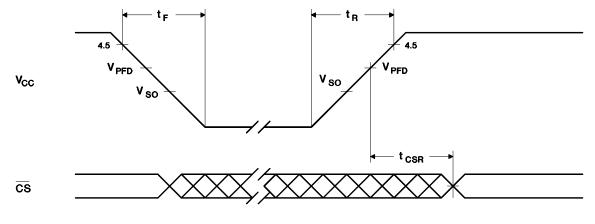

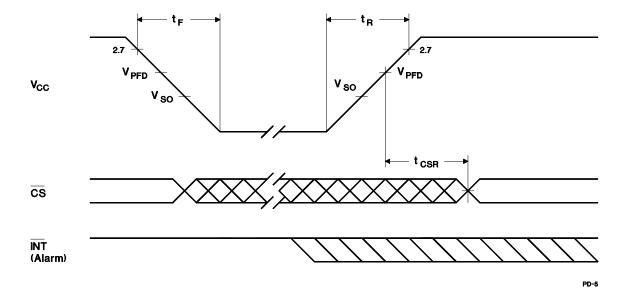

The bq3285EC and bq3285LC power-up/power-down cycles are different. The bq3285LC continuously monitors  $V_{\rm CC}$  for out-of-tolerance. During a power failure, when  $V_{\rm CC}$  falls below  $V_{\rm PFD}$  (2.53V typical), the bq3285LC write-protects the clock and storage registers. The power source is switched to BC when  $V_{\rm CC}$  is less than  $V_{\rm PFD}$  and BC is greater than  $V_{\rm PFD}$ , or when  $V_{\rm CC}$  is less than  $V_{\rm BC}$  and  $V_{\rm BC}$  is less than  $V_{\rm PFD}$ . RTC operation and storage data are sustained by a valid backup energy source. When  $V_{\rm CC}$  is above  $V_{\rm PFD}$ , the power source is  $V_{\rm CC}$ . Write-protection continues for  $t_{\rm CSR}$  time after  $V_{\rm CC}$  rises above  $V_{\rm PFD}$ .

The bq3285EC continuously monitors  $V_{CC}$  for out-of-tolerance. During a power failure, when  $V_{CC}$  falls below  $V_{PFD}$  (4.17V typical), the bq3285EC write-protects the clock and storage registers. When  $V_{CC}$  is below  $V_{BC}$  (3V typical), the power source is switched to BC. RTC operation and storage data are sustained by a valid backup energy source. When  $V_{CC}$  is above  $V_{BC}$ , the power source is  $V_{CC}$ . Write-protection continues for  $t_{CSR}$  time after  $V_{CC}$  rises above  $V_{PFD}$ .

## Control/Status Registers

The four control/status registers of the bq3285EC/LC are accessible regardless of the status of the update cycle (see Table 4).

#### Register A

|     | Register A Bits |     |     |     |     |     |     |  |  |  |  |

|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

| UIP | OS2             | OS1 | OS0 | RS3 | RS2 | RS1 | RS0 |  |  |  |  |

Register A programs:

- The frequency of the periodic event rate.

- Oscillator operation.

Time-keeping

Register A provides:

Status of the update cycle.

RS0-RS3 - Frequency Select

| 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|

| - | - | - | - | RS3 | RS2 | RS1 | RS0 |

These bits select the periodic interrupt rate, as shown in Table 3.

#### OS0-OS2 - Oscillator Control

| 7 | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|---|-----|-----|-----|---|---|---|---|

| - | OS2 | OS1 | OS0 | - | - | - | - |

These three bits control the state of the oscillator and divider stages. A pattern of 010 or 011 enables RTC operation by turning on the oscillator and enabling the frequency divider. This pattern must be set to turn the oscillator on for the bq3285EC and to ensure that the bq3285EC/LC will keep time in battery-backup mode. A pattern of 11X turns the oscillator on, but keeps the frequency divider disabled. When 010 is written, the RTC begins its first update after 500ms.

**UIP - Update Cycle Status**

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| UIP | - | - | - | - | - | - | - |

This read-only bit is set prior to the update cycle. When UIP equals 1, an RTC update cycle may be in progress. UIP is cleared at the end of each update cycle. This bit is also cleared when the update transfer inhibit (UTI) bit in register B is 1.

**Table 4. Control/Status Registers**

|      | Loc. |      |                  |      | Bit Name and State on Reset |     |    |     |    |     |    |     |    |     |    |     |    |      |     |

|------|------|------|------------------|------|-----------------------------|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|------|-----|

| Reg. |      | Read | Write            | 7 (M | SB)                         | (   | 6  | į   | 5  | 4   | Ļ  | 3   |    | 2   | 2  | 1   | ı  | 0 (L | SB) |

| A    | 0A   | Yes  | Yes <sup>1</sup> | UIP  | na                          | OS2 | na | OS1 | na | OS0 | na | RS3 | na | RS2 | na | RS1 | na | RS0  | na  |

| В    | 0B   | Yes  | Yes              | UTI  | na                          | PIE | 0  | AIE | 0  | UIE | 0  | -   | 0  | DF  | na | HF  | na | DSE  | na  |

| С    | 0C   | Yes  | No               | INTF | 0                           | PF  | 0  | AF  | 0  | UF  | 0  | -   | 0  | -   | na | -   | 0  | -    | 0   |

| D    | 0D   | Yes  | No               | VRT  | na                          | -   | 0  | -   | 0  | -   | 0  | -   | 0  | -   | 0  | -   | 0  | -    | 0   |

Notes:

na = not affected.

1. Except bit 7.

## Register B

|     | Register B Bits |     |     |   |    |    |     |  |  |  |  |

|-----|-----------------|-----|-----|---|----|----|-----|--|--|--|--|

| 7   | 6               | 5   | 4   | 3 | 2  | 1  | 0   |  |  |  |  |

| UTI | PIE             | AIE | UIE | - | DF | HF | DSE |  |  |  |  |

Register B enables:

- Update cycle transfer operation

- Interrupt events

- Daylight saving adjustment

Register B selects:

Clock and calendar data formats

All bits of register B are read/write.

#### Bit 3 - Unused Bit.

### **DSE - Daylight Saving Enable**

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| - | - | - | - | - | - | 1 | DSE |

This bit enables daylight-saving time adjustments when written to 1:

- On the last Sunday in October, the first time the bq3285EC/LC increments past 1:59:59 AM, the time falls back to 1:00:00 AM.

- On the first Sunday in April, the time springs forward from 2:00:00 AM to 3:00:00 AM.

#### **HF** - Hour Format

| 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|---|---|---|---|---|---|----|---|

| - | - | - | - | - | - | HF | - |

This bit selects the time-of-day and alarm hour format:

- 1 = 24-hour format

- 0 = 12-hour format

#### **DF - Data Format**

| 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|---|---|---|---|----|---|---|

| - | - | - | _ | - | DF | _ | - |

This bit selects the numeric format in which the time, alarm, and calendar bytes are represented:

- 1 = Binary

- 0 = BCD

July 1996

#### **UIE - Update Cycle Interrupt Enable**

| 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|---|---|---|-----|---|---|---|---|

| - | - | - | UIE | - | - | - | - |

This bit enables an interrupt request due to an update ended interrupt event:

- 1 = Enabled

- 0 = Disabled

The UIE bit is automatically cleared when the UTI bit equals 1.

#### AIE - Alarm Interrupt Enable

| 7 | 6 | 5   | 4 | 3 | 2 | 1 | 0 |

|---|---|-----|---|---|---|---|---|

| _ | - | AIE | - | - | - | - | - |

This bit enables an interrupt request due to an alarm interrupt event:

- 1 = Enabled

- 0 = Disabled

#### PIE - Periodic Interrupt Enable

| 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|---|-----|---|---|---|---|---|---|

| _ | PIE | _ | _ | _ | _ | _ | _ |

This bit enables an interrupt request due to a periodic interrupt event:

- 1 = Enabled

- 0 = Disabled

#### **UTI - Update Transfer Inhibit**

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| UTI | - | _ | - | - | _ | - | - |

This bit inhibits the transfer of RTC bytes to the user buffer:

- 1 = Inhibits transfer and clears UIE

- 0 = Allows transfer

### Register C

| Register C Bits |      |    |    |   |   |   |   |  |

|-----------------|------|----|----|---|---|---|---|--|

| 7               | 6    | 5  | 4  | 3 | 2 | 1 | 0 |  |

| INT             | F PF | AF | UF | 0 | - | 0 | 0 |  |

Register C is the read-only event status register.

#### Bits 0, 1, 2, 3 - Unused Bits

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | 0 | - | 0 | 0 |

These bits are always set to 0.

### **UF - Update Event Flag**

| 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|---|---|---|----|---|---|---|---|

| - | - | - | UF | - | - | - | - |

This bit is set to a 1 at the end of the update cycle. Reading register  $\boldsymbol{C}$  clears this bit.

#### AF - Alarm Event Flag

| 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|---|---|----|---|---|---|---|---|

| - | - | AF | - | - | - | - | - |

This bit is set to a 1 when an alarm event occurs. Reading register  $\boldsymbol{C}$  clears this bit.

### PF - Periodic Event Flag

| 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----|---|---|---|---|---|---|

| - | PF | _ | - | - | - | - | - |

This bit is set to a 1 every  $t_{PI}$  time, where  $t_{PI}$  is the time period selected by the settings of RS0–RS3 in register A. Reading register C clears this bit.

### **INTF - Interrupt Request Flag**

|      |   |   |   | - |   |   |   |

|------|---|---|---|---|---|---|---|

| 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| INTF | _ | _ | _ | _ | _ | _ | _ |

This flag is set to a 1 when any of the following is true:

AIE = 1 and AF = 1

PIE = 1 and PF = 1

UIE = 1 and UF = 1

Reading register C clears this bit.

### Register D

| Register D Bits |   |   |   |   |   |   |   |  |  |

|-----------------|---|---|---|---|---|---|---|--|--|

| 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| VRT             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

Register D is the read-only data integrity status register.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Bits 0-6 - Unused Bits

These bits are always set to 0.

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| VRT | - | - | _ | - | - | - | - |

#### VRT - Valid RAM and Time

- 1 = Valid backup energy source

- $0 = Backup \ energy \ source \ is \ depleted$

When the backup energy source is depleted (VRT=0), data integrity of the RTC and storage registers is not guaranteed.

## Absolute Maximum Ratings—bq3285EC

| Symbol              | Parameter                                                             | Value       | Unit | Conditions             |

|---------------------|-----------------------------------------------------------------------|-------------|------|------------------------|

| Vcc                 | DC voltage applied on $V_{CC}$ relative to $V_{SS}$                   | -0.3 to 7.0 | V    |                        |

| $V_{\mathrm{T}}$    | DC voltage applied on any pin excluding $V_{CC}$ relative to $V_{SS}$ | -0.3 to 7.0 | V    | $V_T \le V_{CC} + 0.3$ |

| T <sub>OPR</sub>    | Operating temperature                                                 | 0 to +70    | °C   | Commercial             |

| $T_{STG}$           | Storage temperature                                                   | -55 to +125 | °C   |                        |

| T <sub>BIAS</sub>   | Temperature under bias                                                | -40 to +85  | °C   |                        |

| T <sub>SOLDER</sub> | Soldering temperature                                                 | 260         | °C   | For 10 seconds         |

Note:

Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

## Absolute Maximum Ratings—bq3285LC

| Symbol              | Parameter                                                             | Value       | Unit | Conditions              |

|---------------------|-----------------------------------------------------------------------|-------------|------|-------------------------|

| $V_{CC}$            | DC voltage applied on $V_{CC}$ relative to $V_{SS}$                   | -0.3 to 7.0 | V    |                         |

| $V_{\mathrm{T}}$    | DC voltage applied on any pin excluding $V_{CC}$ relative to $V_{SS}$ | -0.3 to 7.0 | V    | $V_T \leq V_{CC} + 0.3$ |

| T <sub>OPR</sub>    | Operating temperature                                                 | 0 to +70    | °C   | Commercial              |

| T <sub>STG</sub>    | Storage temperature                                                   | -55 to +125 | °C   |                         |

| T <sub>BIAS</sub>   | Temperature under bias                                                | -40 to +85  | °C   |                         |

| T <sub>SOLDER</sub> | Soldering temperature                                                 | 260         | °C   | For 10 seconds          |

Note:

Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

# Recommended DC Operating Conditions—bq3285EC $(T_A = T_{OPR})$

| Symbol          | Parameter           | Minimum | Typical | Maximum               | Unit |

|-----------------|---------------------|---------|---------|-----------------------|------|

| V <sub>CC</sub> | Supply voltage      | 4.5     | 5.0     | 5.5                   | V    |

| $V_{SS}$        | Supply voltage      | 0       | 0       | 0                     | V    |

| $V_{\rm IL}$    | Input low voltage   | -0.3    | -       | 0.8                   | V    |

| V <sub>IH</sub> | Input high voltage  | 2.2     | -       | V <sub>CC</sub> + 0.3 | V    |

| V <sub>BC</sub> | Backup cell voltage | 2.4     | -       | 4.0                   | V    |

Note: Typical values indicate operation at  $T_A$  = 25°C.

# Recommended DC Operating Conditions—bq3285LC $(T_A = T_{OPR})$

| Symbol          | Parameter           | Minimum | Typical | Maximum               | Unit |

|-----------------|---------------------|---------|---------|-----------------------|------|

| Vcc             | Supply voltage      | 2.7     | 3.0     | 5.5                   | V    |

| V <sub>SS</sub> | Supply voltage      | 0       | 0       | 0                     | V    |

| V <sub>IL</sub> | Input low voltage   | -0.3    | -       | 0.6                   | V    |

| V <sub>IH</sub> | Input high voltage  | 2.2     | -       | V <sub>CC</sub> + 0.3 | V    |

| V <sub>BC</sub> | Backup cell voltage | 2.4     | -       | 4.0                   | V    |

**Note:** Typical values indicate operation at  $T_A = 25$ °C.

## Crystal Specifications—bq3285EC/LC (DT-26 or Equivalent)

| Symbol                         | Parameter                    | Minimum | Typical | Maximum | Unit   |

|--------------------------------|------------------------------|---------|---------|---------|--------|

| fo                             | Oscillation frequency        | -       | 32.768  | -       | kHz    |

| $C_{L}$                        | Load capacitance             | -       | 6       | -       | pF     |

| T <sub>P</sub>                 | Temperature turnover point   | 20      | 25      | 30      | °C     |

| k                              | Parabolic curvature constant | -       | -       | -0.042  | ppm/°C |

| Q                              | Quality factor               | 40,000  | 70,000  | -       |        |

| R <sub>1</sub>                 | Series resistance            | -       | -       | 45      | ΚΩ     |

| C <sub>0</sub>                 | Shunt capacitance            | -       | 1.1     | 1.8     | pF     |

| C <sub>0</sub> /C <sub>1</sub> | Capacitance ratio            | -       | 430     | 600     |        |

| $D_{L}$                        | Drive level                  | -       | -       | 1       | μW     |

| $\Delta f/f_O$                 | Aging (first year at 25°C)   | -       | 1       | -       | ppm    |

# DC Electrical Characteristics—bq3285EC ( $T_A = T_{OPR}, V_{CC} = 5V$ )

| Symbol             | Parameter                                      | Minimum | Typical  | Maximum | Unit | Conditions/Notes                                                                                                                                        |

|--------------------|------------------------------------------------|---------|----------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{LI}$           | Input leakage current                          | -       | -        | ± 1     | μΑ   | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                    |

| $I_{LO}$           | Output leakage current                         | -       | -        | ± 1     | μΑ   | $\begin{aligned} &AD_0 - AD_7 \text{ and } \overline{INT} \text{ in} \\ &high \text{ impedance,} \\ &V_{OUT} = V_{SS} \text{ to } V_{CC} \end{aligned}$ |

| VoH                | Output high voltage                            | 2.4     | -        | -       | V    | I <sub>OH</sub> = -2.0 mA                                                                                                                               |

| V <sub>OL</sub>    | Output low voltage                             | -       | -        | 0.4     | V    | I <sub>OL</sub> = 4.0 mA                                                                                                                                |

| $I_{CC}$           | Operating supply current                       | -       | 7        | 15      | mA   | $\label{eq:min.cycle} \begin{aligned} & \text{Min. cycle, duty} = 100\%, \\ & I_{OH} = 0 m A, \ I_{OL} = 0 m A \end{aligned}$                           |

| $I_{CCSB}$         | Standby supply current                         | -       | 300      | -       | μΑ   | $\frac{V_{IN} = V_{SS} \text{ or } V_{CC},}{CS \ge V_{CC} - 0.2}$                                                                                       |

| $V_{SO}$           | Supply switch-over voltage                     | -       | $V_{BC}$ | -       | V    |                                                                                                                                                         |

| I <sub>CCB</sub>   | Battery operation current                      | -       | 0.3      | 0.5     | μΑ   | $V_{\rm BC}=3V,T_{\rm A}=25^{\circ}{\rm C}$                                                                                                             |

| $V_{\mathrm{PFD}}$ | Power-fail-detect voltage                      | 4.0     | 4.17     | 4.35    | V    |                                                                                                                                                         |

| I <sub>RCL</sub>   | Input current when $\overline{RCL} = V_{SS}$ . | -       | -        | 185     | μΑ   | Internal 30K pull-up                                                                                                                                    |

| I <sub>MOTH</sub>  | Input current when MOT = V <sub>CC</sub>       | -       | -        | -185    | μΑ   | Internal 30K pull-down                                                                                                                                  |

| -WOTT              | Input current when MOT = V <sub>SS</sub>       | -       | -        | 0       | μΑ   | Internal 30K pull-down                                                                                                                                  |

| Towns and          | Input current when EXTRAM = VCC                | -       | -        | -185    | μΑ   | Internal 30K pull-down                                                                                                                                  |

| IXTRAM             | Input current when EXTRAM = V <sub>SS</sub>    | -       | -        | 0       | μΑ   | Internal 30K pull-down                                                                                                                                  |

$\label{eq:Note:Note:Typical values indicate operation at $T_A=25^{\circ}$C, $V_{CC}=5V$ or $V_{BC}=3V$.}$

# DC Electrical Characteristics—bq3285LC ( $T_A$ = $T_{OPR}$ , $V_{CC}$ = 3V $\pm$ 10%)

| Symbol             | Parameter                                      | Minimum | Typical <sup>1</sup> | Maximum | Unit | Conditions/Notes                                                                                                                   |

|--------------------|------------------------------------------------|---------|----------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------|

| $I_{LI}$           | Input leakage current                          | -       | -                    | ± 1     | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                      |

| $I_{LO}$           | Output leakage current                         | -       | -                    | ± 1     | μA   | $\begin{array}{c} AD_0\text{-}AD_7 \ and \ \overline{IN}T \ in \ high \\ impedance, \\ V_{OUT} = V_{SS} \ to \ V_{CC} \end{array}$ |

| $V_{OH}$           | Output high voltage                            | 2.2     | -                    | -       | V    | $I_{OH}$ = -1.0 mA                                                                                                                 |

| Vol                | Output low voltage                             | -       | -                    | 0.4     | V    | $I_{OL} = 2.0 \text{ mA}$                                                                                                          |

| $I_{CC}$           | Operating supply current                       | -       | 5 <sup>2</sup>       | 9       | mA   | $\begin{aligned} & \text{Min. cycle, duty} = 100\%, \\ & I_{OH} = 0\text{mA}, I_{OL} = 0\text{mA} \end{aligned}$                   |

| $I_{CCSB}$         | Standby supply current                         | -       | 100 <sup>3</sup>     | -       | μA   | $\frac{V_{IN} = V_{SS} \text{ or } V_{CC},}{\overline{CS} \ge V_{CC} - 0.2}$                                                       |

| V                  | Complex quitals are valte as                   | -       | $V_{\mathrm{PFD}}$   | -       | V    | $V_{BC} > V_{PFD}$                                                                                                                 |

| Vso                | Supply switch-over voltage                     | -       | $V_{BC}$             | -       | V    | $V_{BC} < V_{PFD}$                                                                                                                 |

| $I_{CCB}$          | Battery operation current                      | -       | 0.3                  | 0.5     | μA   | $\begin{aligned} V_{BC} &= 3V, T_A = 25^{\circ}C, \\ V_{CC} &< V_{BC} \end{aligned}$                                               |

| $V_{\mathrm{PFD}}$ | Power-fail-detect voltage                      | 2.4     | 2.53                 | 2.65    | V    |                                                                                                                                    |

| $I_{RCL}$          | Input current when $\overline{RCL} = V_{SS}$ . | -       | -                    | 120     | μΑ   | Internal 30K pull-up                                                                                                               |

| $I_{MOTH}$         | Input current when MOT = V <sub>CC</sub>       | -       | -                    | -120    | μА   | Internal 30K pull-down                                                                                                             |

| ZWO III            | Input current when MOT = V <sub>SS</sub>       | -       | -                    | 0       | μА   | Internal 30K pull-down                                                                                                             |

| T                  | Input current when EXTRAM = Vcc                | -       | -                    | -120    | μА   | Internal 30K pull-down                                                                                                             |

| IXTRAM             | Input current when EXTRAM = Vss                | -       | -                    | 0       | μА   | Internal 30K pull-down                                                                                                             |

Notes:

- 1. Typical values indicate operation at  $T_A$  = 25°C,  $V_{CC}$  = 3V.

- 2. 7mA at  $V_{CC} = 5V$

- 3.  $300\mu A$  at  $V_{CC} = 5V$

# Capacitance—bq3285EC/LC ( $T_A = 25$ °C, F = 1MHz, $V_{CC} = 5.0$ V)

| Symbol           | Parameter                | Minimum | Typical | Maximum | Unit | Conditions     |

|------------------|--------------------------|---------|---------|---------|------|----------------|

| C <sub>I/O</sub> | Input/output capacitance | -       | -       | 7       | pF   | $V_{OUT} = 0V$ |

| C <sub>IN</sub>  | Input capacitance        | -       | -       | 5       | pF   | $V_{IN} = 0V$  |

**Note:** This parameter is sampled and not 100% tested. It does not include the X1 or X2 pin.

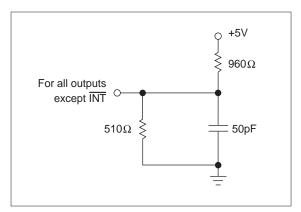

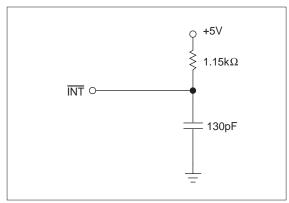

# AC Test Conditions—bq3285EC

| Parameter                                | Test Conditions                    |  |  |

|------------------------------------------|------------------------------------|--|--|

| Input pulse levels                       | 0 to 3.0 V                         |  |  |

| Input rise and fall times                | 5 ns                               |  |  |

| Input and output timing reference levels | 1.5 V (unless otherwise specified) |  |  |

| Output load (including scope and jig)    | See Figures 4 and 5                |  |  |

Figure 4. Output Load—bq3285EC

Figure 5. Output Load—bq3285EC

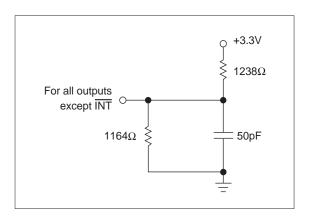

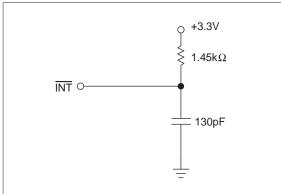

## AC Test Conditions—bq3285LC

| Parameter                                | Test Conditions                    |  |  |  |

|------------------------------------------|------------------------------------|--|--|--|

| Input pulse levels                       | 0 to 2.3 V, $V_{CC} = 3V^1$        |  |  |  |

| Input rise and fall times                | 5 ns                               |  |  |  |

| Input and output timing reference levels | 1.2 V (unless otherwise specified) |  |  |  |

| Output load (including scope and jig)    | See Figures 6 and 7                |  |  |  |

**Note:** 1. For 5V timing, please refer to bq3285EC.

Figure 6. Output Load—bq3285LC

Figure 7. Output Load B—bq3285LC

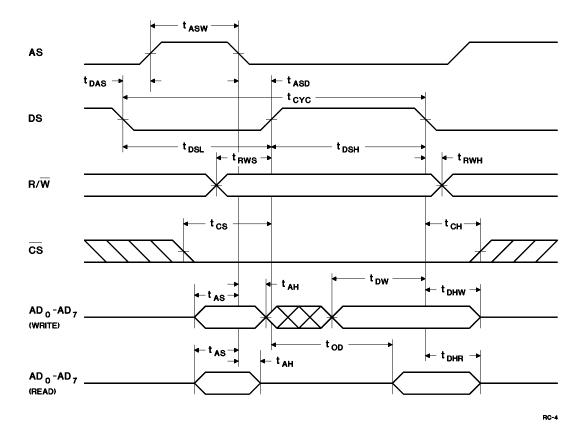

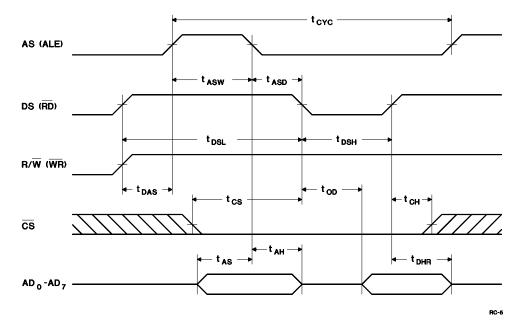

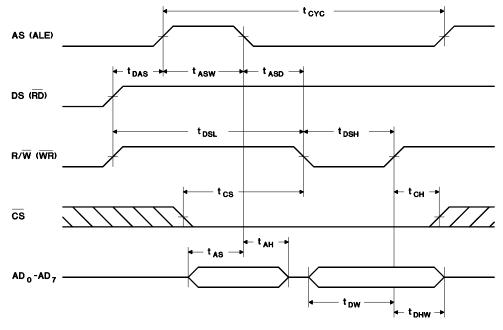

# Read/Write Timing—bq3285EC ( $T_A = T_{OPR}$ , $V_{CC} = 5V \pm 10\%$ )

| Symbol             | Parameter                                                      | Minimum | Typical | Maximum | Unit | Notes       |

|--------------------|----------------------------------------------------------------|---------|---------|---------|------|-------------|

| t <sub>CYC</sub>   | Cycle time                                                     | 160     | -       | -       | ns   |             |

| t <sub>DSL</sub>   | DS low or $\overline{RD}/\overline{WR}$ high time              | 80      | -       | -       | ns   |             |

| t <sub>DSH</sub>   | DS high or $\overline{RD}/\overline{WR}$ low time              | 55      | -       | -       | ns   |             |

| t <sub>RWH</sub>   | $R/\overline{W}$ hold time                                     | 0       | -       | -       | ns   |             |

| t <sub>RWS</sub>   | R/W setup time                                                 | 10      | -       | -       | ns   |             |

| tcs                | Chip select setup time                                         | 5       | -       | -       | ns   |             |

| t <sub>CH</sub>    | Chip select hold time                                          | 0       | -       | -       | ns   |             |

| $t_{\mathrm{DHR}}$ | Read data hold time                                            | 0       | -       | 25      | ns   |             |

| t <sub>DHW</sub>   | Write data hold time                                           | 0       | -       | -       | ns   |             |

| t <sub>AS</sub>    | Address setup time                                             | 20      | -       | -       | ns   |             |

| t <sub>AH</sub>    | Address hold time                                              | 5       | -       | -       | ns   |             |

| $t_{DAS}$          | Delay time, DS to AS rise                                      | 10      | -       | -       | ns   |             |

| t <sub>ASW</sub>   | Pulse width, AS high                                           | 30      | -       | -       | ns   |             |

| t <sub>ASD</sub>   | Delay time, AS to DS rise $(\overline{RD}/\overline{WR}$ fall) | 35      | -       | -       | ns   |             |

| t <sub>OD</sub>    | Output data delay time from DS rise (RD fall)                  | -       | -       | 50      | ns   |             |

| $t_{DW}$           | Write data setup time                                          | 30      | -       | -       | ns   |             |

| t <sub>BUC</sub>   | Delay time before update cycle                                 | -       | 244     | -       | μs   |             |

| tPI                | Periodic interrupt time interval                               | -       | -       | -       | -    | See Table 3 |

| t <sub>UC</sub>    | Time of update cycle                                           | -       | 1       | -       | μs   |             |

# Read/Write Timing—bq3285LC ( $T_A = T_{OPR}, V_{CC} = 3V \pm 10\%$ )

| Symbol           | Parameter                                         | Minimum | Typical | Maximum | Unit | Notes       |

|------------------|---------------------------------------------------|---------|---------|---------|------|-------------|

| tcyc             | Cycle time                                        | 270     | -       | -       | ns   |             |

| t <sub>DSL</sub> | DS low or $\overline{RD}/\overline{WR}$ high time | 135     | -       | -       | ns   |             |

| t <sub>DSH</sub> | DS high or $\overline{RD}/\overline{WR}$ low time | 90      | -       | -       | ns   |             |

| t <sub>RWH</sub> | $R/\overline{W}$ hold time                        | 0       | -       | -       | ns   |             |

| $t_{RWS}$        | R/W setup time                                    | 15      | -       | -       | ns   |             |

| tcs              | Chip select setup time                            | 8       | -       | -       | ns   |             |

| t <sub>CH</sub>  | Chip select hold time                             | 0       | -       | -       | ns   |             |

| t <sub>DHR</sub> | Read data hold time                               | 0       | -       | 40      | ns   |             |

| t <sub>DHW</sub> | Write data hold time                              | 0       | -       | -       | ns   |             |

| tas              | Address setup time                                | 30      | -       | -       | ns   |             |

| t <sub>AH</sub>  | Address hold time                                 | 15      | -       | -       | ns   |             |

| t <sub>DAS</sub> | Delay time, DS to AS rise                         | 15      | -       | -       | ns   |             |

| t <sub>ASW</sub> | Pulse width, AS high                              | 50      | -       | -       | ns   |             |

| t <sub>ASD</sub> | Delay time, AS to DS rise (RD/WR fall)            | 55      | -       | -       | ns   |             |

| t <sub>OD</sub>  | Output data delay time from DS rise (RD fall)     | -       | -       | 100     | ns   |             |

| $t_{DW}$         | Write data setup time                             | 50      | -       | -       | ns   |             |

| t <sub>BUC</sub> | Delay time before update cycle                    | -       | 244     | -       | μs   |             |

| t <sub>PI</sub>  | Periodic interrupt time interval                  | -       | -       | -       | -    | See Table 3 |

| tuc              | Time of update cycle                              | -       | 1       | -       | μs   |             |

# Motorola Bus Read/Write Timing—bq3285EC/LC

# Intel Bus Read Timing—bq3285EC/LC

# Intel Bus Write—bq3285EC/LC

# Power-Down/Power-Up Timing—bq3285EC $(T_A = T_{OPR})$

| Symbol           | Parameter                                         | Minimum | Typical | Maximum | Unit | Conditions                                                                                                                                    |

|------------------|---------------------------------------------------|---------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\mathrm{F}}$ | V <sub>CC</sub> slew from 4.5V to 0V              | 300     | -       | -       | μs   |                                                                                                                                               |

| t <sub>R</sub>   | V <sub>CC</sub> slew from 0V to 4.5V              | 100     | -       | -       | μs   |                                                                                                                                               |

| t <sub>CSR</sub> | $\overline{\text{CS}}$ at $V_{IH}$ after power-up | 20      | -       | 200     | ms   | $\begin{array}{c} \text{Internal write-protection} \\ \text{period after } V_{CC} \text{ passes } V_{PFD} \\ \text{on power-up.} \end{array}$ |

${\bf Caution:} \quad {\bf Negative \ under shoots \ below \ the \ absolute \ maximum \ rating \ of \ -0.3V \ in \ battery-backup \ mode \\ may \ affect \ data \ integrity.}$

## Power-Down/Power-Up Timing—bq3285EC

PD-4A

# Power-Down/Power-Up Timing—bq3285LC $(T_A = T_{OPR})$

| Symbol           | Parameter                            | Minimum | Typical | Maximum | Unit | Conditions                                                                                                         |

|------------------|--------------------------------------|---------|---------|---------|------|--------------------------------------------------------------------------------------------------------------------|

| $t_{\mathrm{F}}$ | V <sub>CC</sub> slew from 2.7V to 0V | 300     | -       | -       | μs   |                                                                                                                    |

| $t_R$            | V <sub>CC</sub> slew from 0V to 2.7V | 100     | -       | -       | μs   |                                                                                                                    |

| t <sub>CSR</sub> | CS at V <sub>IH</sub> after power-up | 20      | -       | 200     | ms   | $\begin{array}{c} Internal\ write-protection\\ period\ after\ V_{CC}\ passes\ V_{PFD}\\ on\ power-up. \end{array}$ |

Caution: Negative undershoots below the absolute maximum rating of -0.3V in battery-backup mode may affect data integrity.

## Power-Down/Power-Up Timing—bq3285LC

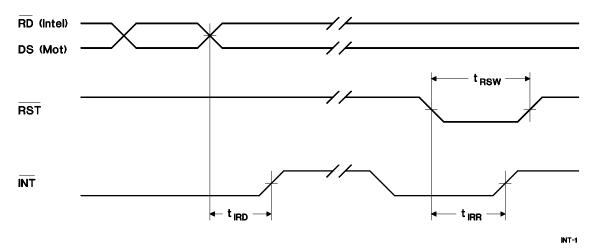

# Interrupt Delay Timing—bq3285EC/LC $(T_A = T_{OPR})$

| Symbol           | Parameter            | Minimum | Typical | Maximum | Unit |

|------------------|----------------------|---------|---------|---------|------|

| t <sub>RSW</sub> | Reset pulse width    | 5       | -       | -       | μs   |

| t <sub>IRR</sub> | INT release from RST | -       | -       | 2       | μs   |

| $t_{IRD}$        | INT release from DS  | -       | -       | 2       | μs   |

# Interrupt Delay Timing—bq3285EC/LC

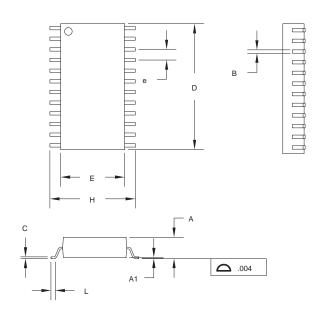

# 24-Pin SOIC (S)

## 24-Pin S (0.300" SOIC)

|           | Inc   | hes   | Millin | neters |  |  |  |

|-----------|-------|-------|--------|--------|--|--|--|

| Dimension | Min.  | Max.  | Min.   | Max.   |  |  |  |

| A         | 0.095 | 0.105 | 2.41   | 2.67   |  |  |  |

| A1        | 0.004 | 0.012 | 0.10   | 0.30   |  |  |  |

| В         | 0.013 | 0.020 | 0.33   | 0.51   |  |  |  |

| С         | 0.008 | 0.013 | 0.20   | 0.33   |  |  |  |

| D         | 0.600 | 0.615 | 15.24  | 15.62  |  |  |  |

| Е         | 0.290 | 0.305 | 7.37   | 7.75   |  |  |  |

| e         | 0.045 | 0.055 | 1.14   | 1.40   |  |  |  |

| Н         | 0.395 | 0.415 | 10.03  | 10.54  |  |  |  |

| L         | 0.020 | 0.040 | 0.51   | 1.02   |  |  |  |

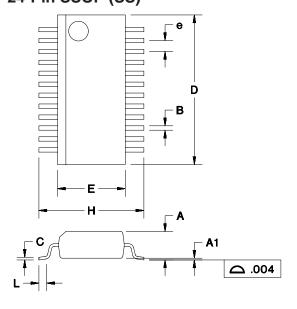

# 24-Pin SSOP (SS)

# 24-Pin SS (0.150" SSOP)

|               | Inches        |             | Millin | neters |

|---------------|---------------|-------------|--------|--------|

| Dimension     | Min. Max.     |             | Min.   | Max.   |

| A             | 0.061         | .061 0.068  |        | 1.73   |

| A1            | 0.004 0.010   |             | 0.10   | 0.25   |

| В             | B 0.008 0.012 |             | 0.20   | 0.30   |

| С             | 0.007         | 0.007 0.010 |        | 0.25   |

| D             | 0.337         | 0.344       | 8.56   | 8.74   |

| E 0.150 0.157 |               | 0.157       | 3.81   | 3.99   |

| e             | .025 BSC      |             | 0.64   | BSC    |

| Н             | 0.230         |             | 5.84   | 6.20   |

| L             | 0.016         | 0.035       | 0.41   | 0.89   |

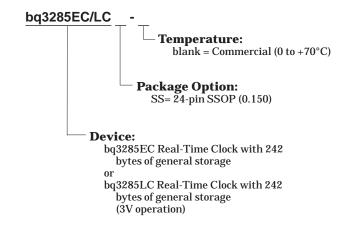

# **Ordering Information**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331