# Battery Charging IC, 98% Efficient, Safe 6 A Direct with Regulation and Protection

The FAN54161UCX is a low loss direct charger which charges the battery safely at 6 A and provides active protection, regulation and monitoring features.

Integrated Protection and Regulation features control a pair of MOSFETs to ensure that the FAN54161UCX output voltage and current stay within a safe programmed operating range. Configurable hardware based safety features turn off the MOSFET in the event of a fault and notify the system.

An integrated 10-bit Analog-to-Digital Converter (ADC) provides real-time monitoring of input, output voltage, currents and temperature so that the system host or microcontroller can effectively use this information to optimize adapter and charger configuration.

#### Features

- Integrated Back-to-Back Common Source N-channel MOSFETs with Combined  $R_{ON} = 11 \text{ m}\Omega$

- Maximum Input Voltage Tolerance of +22 V

- Reverse Input Voltage Tolerance of -2 V

- External N-channel MOSFET Drive Capability with Tolerance up to +32 V

- Regulation Modes

- Charge Current

- Input Current

- Output Voltage

- Battery Cell Voltage

- Hardware-based Safety Protections

- Input Over–Voltage

- Input Under-Voltage

- Output Over–Voltage

- Input Over-Current

- Die Over-Temperature

- Internal Switch Short

- 10-bit High-accuracy ADC

### **Typical Applications**

- Mobile Devices

- Tablets

## **ON Semiconductor®**

www.onsemi.com

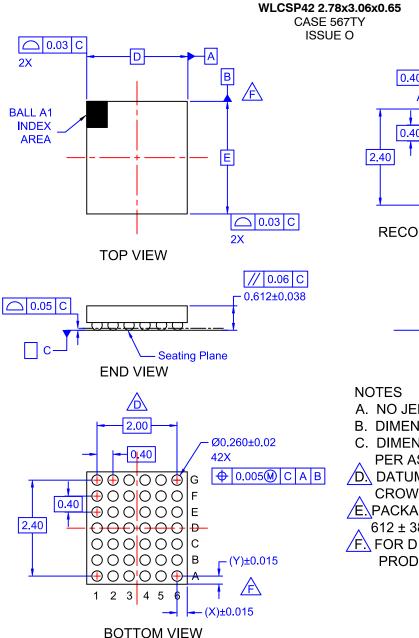

WLCSP42 CASE 567TY

### MARKING DIAGRAM

12 = Specific Device Code

KK = Lot Run Code

X = Year Code

- Y = 2-Weeks Date Code

- Z = Assembly Plant Code

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

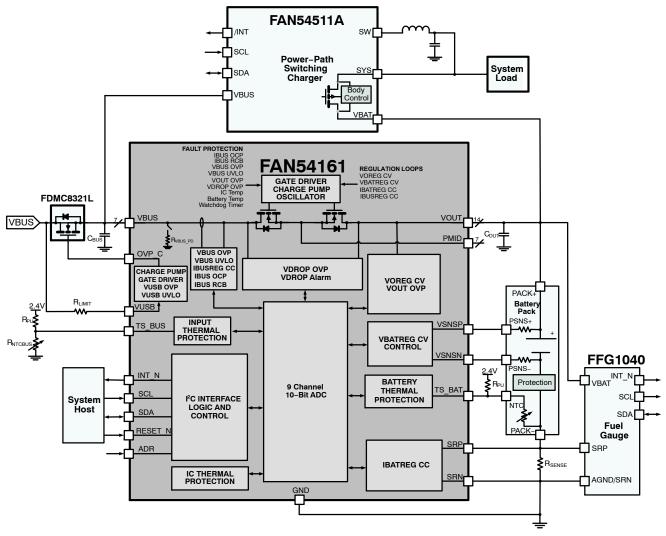

### **Block Diagram and Application Schematic**

Figure 1. FAN54161, External FET, Switching Charger, Battery Pack with Exposed Cell, and External Fuel Gauge

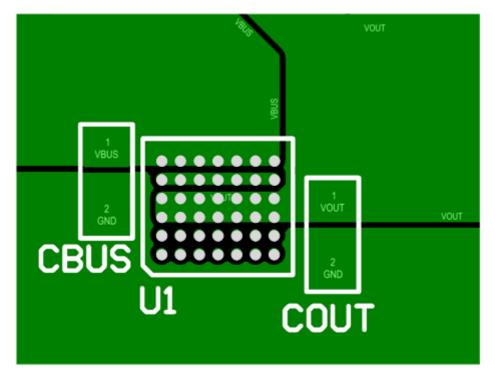

### **RECOMMENDED COMPONENTS**

| Component                        | Manufacturer | Part Number    | Value           | Case Size          | Rating |

|----------------------------------|--------------|----------------|-----------------|--------------------|--------|

| C <sub>BUS</sub>                 | Murata       | GRM188R61E105K | 1.0 μF          | 0603 (1608 metric) | 25 V   |

| C <sub>BUS</sub> (alternative)   | TDK          | C1608X5R1E105K | 1.0 μF          | 0603 (1608 metric) | 25 V   |

| C <sub>OUT</sub>                 | TDK          | C1608X5R0J226M | 22 µF           | 0603 (1608 metric) | 6.3 V  |

| R <sub>SENSE</sub>               | Ohmite       | MCS1632R010FER | 0.01 (±1%) Ohm  | 1206 (3216 metric) | 1 W    |

| R <sub>SENSE</sub> (alternative) | Ohmite       | MCS1632R005FER | 0.005 (±1%) Ohm | 1206 (3216 metric) | 1 W    |

#### **ORDERING INFORMATION**

| Part Number | Temperature Range | Package                       | Packing Method |

|-------------|-------------------|-------------------------------|----------------|

| FAN54161UCX | –40°C to +85°C    | 2.78 x 3.06 mm, 42–Bump WLCSP | Tape and Reel  |

# Pin Connections and Functional Description

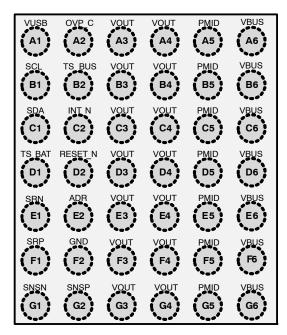

Figure 2. WLCSP-42 Pin Assignments

### Table 1. PIN DESCRIPTIONS

| Name    | Position                      | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR     | E2                            | Digital Input                | I <sup>2</sup> C Slave Device Address Selection Pin<br>Refer to I2C Interface section for details<br>ADR logic level must be set before releasing RESET_N high. Recommend connecting this<br>pin to the appropriate logic level before power is applied (VBUS or VOUT).                                                                                                              |

| GND     | F2                            | Ground                       | Device Ground<br>Connect to the ground node in the PCB.                                                                                                                                                                                                                                                                                                                              |

| INT_N   | C2                            | Open-Drain<br>Digital Output | Interrupt Output (Active Low)<br>Pull-up with 100 k $\Omega$ resistor to logic supply voltage. When an un-masked interrupt bit is<br>set this pin will assert low.<br>Connect to GND if not used.                                                                                                                                                                                    |

| RESET_N | D2                            | Digital Input                | <ul> <li>Reset Input (Active Low)</li> <li>0 (Logic Low) – IC held in reset condition (lowest power state), switch is open, ADC is disabled, and I<sup>2</sup>C communication is not available.</li> <li>1 (Logic High) – IC logic allowed to operate, switch closed if SW_EN = 1; ADC enabled if ADC_EN = 1.</li> <li>If not used, it is recommended to pull-up to VOUT.</li> </ul> |

| SCL     | B1                            | Digital Input                | I <sup>2</sup> C Serial Clock Input<br>Pull-up with a resistor to logic supply voltage.                                                                                                                                                                                                                                                                                              |

| SDA     | C1                            | Open-drain<br>Digital I/O    | I <sup>2</sup> C Serial Data<br>Pull-up with a resistor to logic supply voltage.                                                                                                                                                                                                                                                                                                     |

| VBUS    | A6, B6, C6, D6,<br>E6, F6, G6 | Power Input                  | Switch Input, Device Supply and Input Voltage Sense<br>Connect to the input power source of system. If an external N-channel MOSFET is used<br>for protection, connect VBUS to the source of this MOSFET.<br>VBUS has an internal 100 $\Omega$ pulldown resistor that is active when VBUSPD_EN = 1.                                                                                  |

| PMID    | A5, B5, C5, D5,<br>E5, F5, G5 |                              | Switch Common Source Point<br>Leave floating. Connect to a floating copper plane to provide an additional thermal relief<br>path to the PCB.                                                                                                                                                                                                                                         |

#### Table 1. PIN DESCRIPTIONS

| Name   | Position                                                        | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOUT   | A3, A4, B3, B4,<br>C3, C4, D3,<br>D4, E3, E4, F3,<br>F4, G3, G4 | Power Output  | Switch Output, Device Supply, and Output Voltage Sense<br>Connect to the battery pack.<br>VOUT will be regulated to a maximum level, relative to GND, as set by the VOREG(TH)<br>register value.                                                                                                                                                                                                                                      |

| SNSN   | G1                                                              | Analog Input  | Battery Cell Voltage Sense Negative<br>Connect to the negative side of the cell inside the battery pack through a 1 k $\Omega$ resistor in<br>series. If the battery pack does not provide access to the negative side of the cell, connect<br>SNSN physically as close as possible to the negative terminal of the pack.<br>If the voltage sensed across SNSP and SNSN tries to exceed the threshold                                 |

| SNSP   | G2                                                              | Analog Input  | $V_{BATREG(TH)}$ , the voltage across SNSP and SNSN is regulated to the threshold.<br><b>Battery Cell Voltage Sense Positive</b><br>Connect to the positive side of the cell inside the battery pack through a 1 k $\Omega$ resistor in series.                                                                                                                                                                                       |

|        |                                                                 |               | If the voltage sensed across SNSP and SNSN tries to exceed the threshold $V_{BATREG(TH)}$ , the voltage across SNSP and SNSN is regulated to the threshold.<br>If the battery pack does not provide access to the positive side of the cell, connect SNSP to VOUT.                                                                                                                                                                    |

| SRN    | E1                                                              | Analog Input  | Battery Current Sense Negative<br>Connect to the negative side of the sense resistor in series with the cell.<br>If the current through R <sub>SENSE</sub> tries to exceed the threshold I <sub>BATREG(TH)</sub> , the voltage across<br>SRN and SRP is regulated to the threshold.                                                                                                                                                   |

| SRP    | F1                                                              | Analog Input  | Battery Current Sense Positive<br>Connect to the positive side of the sense resistor in series with the cell.<br>If the current through R <sub>SENSE</sub> tries to exceed the threshold I <sub>BATREG(TH)</sub> , the voltage across<br>SRN and SRP is regulated to the threshold.                                                                                                                                                   |

| TS_BUS | B2                                                              | Analog Input  | Thermistor Input for input connector temperature sense<br>Connect an NTC thermistor from TS_BUS to GND. Connect a pull-up resistor from<br>TS_BUS to an external 2.4 V supply.<br>Connect to GND if not used.                                                                                                                                                                                                                         |

| TS_BAT | D1                                                              | Analog Input  | Thermistor Input for battery temperature sense<br>Connect an NTC thermistor from TS_BAT to GND. Connect a pull-up resistor from<br>TS_BAT to an external 2.4 V supply.<br>Connect to GND if not used.                                                                                                                                                                                                                                 |

| VUSB   | A1                                                              | Power Input   | Input Voltage Sense for external VBUS over voltage protection control<br>Connect this pin to the drain of external N–channel MOSFET (which is also the USB sup-<br>ply voltage) with a 500 $\Omega$ series resistor, R <sub>LIMIT</sub> . The source of the external N–channel<br>MOSFET must be connected to the VBUS pin. If an external MOSFET is not used, the<br>VUSB pin must be left floating. Do not connect this pin to GND. |

| OVP_C  | A2                                                              | Analog Output | Gate Control Output for external VBUS OVP blocking FET<br>Connect to the gate of external N-channel MOSFET. If an external MOSFET is not used,<br>the OVP_C pin should be tied to VBUS or float. Do not connect this pin to GND.                                                                                                                                                                                                      |

| Symbol                                                     | Parameter                                                                       | Min  | Тур | Max   | Units |

|------------------------------------------------------------|---------------------------------------------------------------------------------|------|-----|-------|-------|

| V <sub>BUS</sub>                                           | Protected Input Supply Voltage, VBUS to GND                                     | -2.0 |     | +22.0 | V     |

| V <sub>OUT</sub>                                           | Battery Voltage, VOUT to GND                                                    | -0.3 |     | +7.0  | V     |

| V <sub>USB</sub>                                           | Input connector sense pin, $R_{LIMIT}$ = 500 $\Omega$                           | -2.0 |     | +32.0 | V     |

| V <sub>OVP_C</sub>                                         | OVP Gate Control Output, OVP_C = VBUS                                           | -2.0 |     | +29.0 | V     |

| V <sub>SNSP</sub> , V <sub>SRP</sub> ,<br>V <sub>SRN</sub> | Battery Positive Voltage and Current Sense, SNSP to GND, SRP to GND, SRN to GND | -0.3 |     | +6.0  | V     |

| V <sub>SNSN</sub>                                          | Battery Negative Voltage Sense, SNSN to GND                                     | -4.6 |     | +6.0  | V     |

| V <sub>TS_BUS</sub> ,<br>V <sub>TS_BAT</sub>               | Thermistor Voltage Sense Inputs, TS_BUS to GND, TS_BAT to GND                   | -0.3 |     | +6.0  | V     |

| V <sub>IOD</sub>                                           | Digital Input and Open Drain Output Pins (SCL, SDA, ADR, RESET_N, INT_N)        | -0.3 |     | +6.0  | V     |

| IPASS                                                      | Maximum Continuous Switch Current                                               |      |     | 7.50  | Α     |

| T <sub>A</sub>                                             | Operating Free-air Temperature                                                  | -40  |     | +85   | °C    |

| T <sub>J(MAX)</sub>                                        | Maximum Junction Temperature                                                    | -40  |     | +150  | °C    |

| T <sub>STG</sub>                                           | Storage Temperature Range                                                       | -65  |     | +150  | °C    |

| ΤL                                                         | Lead Soldering Temperature, 10 secs                                             |      |     | 260   | °C    |

| ESD                                                        | Human-Body Model (HBM-JESD22-A114), VBUS and VUSB                               | 3000 |     |       | V     |

|                                                            | Human-Body Model (HBM-JESD22-A114), All Other Pins                              | 2000 |     |       | V     |

|                                                            | Charged Device Model (CDM-JESD22-C101), All Pins                                | 500  |     |       | V     |

#### Table 2. ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All voltages are referenced to ground, GND, unless otherwise noted.

2. Pins should be protected with external TVS devices when tested for IEC compliance.

#### **Table 3. THERMAL CHARACTERISTICS**

| Symbol  | Parameter                               | Conditions           | Min | Тур | Max | Units |

|---------|-----------------------------------------|----------------------|-----|-----|-----|-------|

| ThetaJA | Junction -to-Ambient Thermal Resistance | JEDEC, 2S2P, No Vias |     | 50  |     | °C/W  |

NOTES: Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with two-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperature T<sub>A</sub>.

#### Table 4. RECOMMENDED OPERATING RANGES (Note 3)

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings. The recommended operating conditions assume the following:  $V_{OUT} = 2.7$  V to 4.5 V,  $V_{PU} = 1.8$  V to 4.5 V,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted.

| Symbol                                    | Parameter                                        | Min  | Тур | Max  | Units |

|-------------------------------------------|--------------------------------------------------|------|-----|------|-------|

| V <sub>BUS</sub>                          | Input Voltage                                    | 2.66 |     | 6.4  | V     |

| V <sub>USB</sub>                          | Input Connector Voltage Sense                    | 2.5  |     | 15   | V     |

| V <sub>OUT</sub>                          | Battery Voltage                                  | 2.66 |     | 5.2  | V     |

| V <sub>SNSP</sub>                         | Battery Positive Voltage Sense                   | 2.66 |     | 5.2  | V     |

| V <sub>SNSN</sub>                         | Battery Negative Voltage Sense                   | -0.2 |     | +0.2 | V     |

| V <sub>SRP</sub> , V <sub>SRN</sub>       | Battery Current Sense                            | -0.2 |     | +0.2 | V     |

| V <sub>PU</sub>                           | I <sup>2</sup> C External Pull-up Supply Voltage | 1.62 |     | 3.63 | V     |

| V <sub>TS_BUS</sub> , V <sub>TS_BAT</sub> | Thermistor Input Voltage Sense                   | 0.1  |     | 2.3  | V     |

| T <sub>A</sub>                            | Operating Free-air temperature                   | -40  |     | +85  | °C    |

| TJ                                        | Operating Junction Temperature                   | -30  |     | +120 | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3. All voltages are measured relative to GND.

Table 5. ELECTRICAL CHARACTERISTICS (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1; recommended operating range for  $T_J$  and  $T_A$ ; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} = 2.7 \text{ V}$  to 4.5 V and  $T_A = -40^{\circ}\text{C}$  to 85°C, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = 3.8 \text{ V}$ ,  $V_{PU} = 1.8 \text{ V}$ .

| Symbol                | Parameter                  | Conditions                                                                              | Min | Тур | Max | Units |

|-----------------------|----------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SUPPLY CURREN         | T                          | · · · ·                                                                                 |     |     |     |       |

| IACTIVE               | Active Mode Current        | Switch Closed, RESET_N=HIGH,<br>I <sub>PASS</sub> =6A, V <sub>USB</sub> =0V, [ADC_EN]=0 |     | 5   | 9   | mA    |

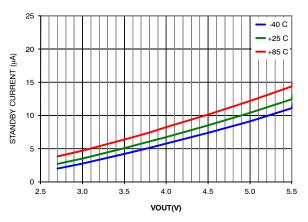

| ISTANDBY_ADCOFF       | VOUT Standby Mode Current  | RESET_N=HIGH, [ADC_EN]=0,<br>V <sub>BUS</sub> =Open                                     |     | 5.5 | 10  | μΑ    |

|                       |                            | RESET_N=HIGH, [ADC_EN]=0,<br>V <sub>BUS</sub> =5V                                       |     | 1.5 | 3.0 | μΑ    |

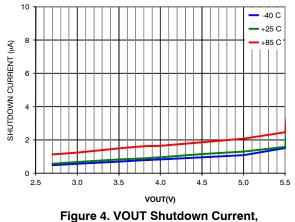

| I <sub>SHUTDOWN</sub> | VOUT Shutdown Mode Current | RESET_N=LOW, V <sub>BUS</sub> =5V                                                       |     | 1.5 | 3.0 | μA    |

|                       |                            | RESET_N=LOW, V <sub>BUS</sub> =Open                                                     |     | 1.5 | 3.0 | μA    |

| ISTANDBY_ADCOFF       | VBUS Standby Mode Current  | RESET_N=HIGH, [ADC_EN]=0,<br>V <sub>BUS</sub> =5V, V <sub>OUT</sub> =3.8V               |     | 10  | 25  | μΑ    |

|                       |                            | RESET_N=HIGH, [ADC_EN]=0,<br>V <sub>BUS</sub> =5V, V <sub>OUT</sub> =Open               |     | 10  | 25  | μΑ    |

| ISHUTDOWN             | VBUS Shutdown Mode Current | RESET_N=LOW, V <sub>BUS</sub> =5V, V <sub>OUT</sub> =3.8V                               |     | 3   | 18  | μA    |

|                       |                            | RESET_N=LOW, V <sub>BUS</sub> =5V, V <sub>OUT</sub> =Open                               |     | 3   | 18  | μA    |

| I <sub>VUSB</sub>     | VUSB Quiescent Current     | V <sub>USB</sub> =5V                                                                    |     | 63  | 100 | μA    |

#### SWITCH CHARACTERISTICS

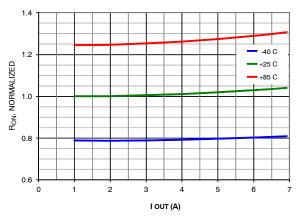

| R <sub>ON</sub>      | On-Resistance from VBUS to<br>VOUT | $3.0 \le V_{OUT} \le 4.5 V$ , $I_{PASS} = 1A$ , $T_A = 25^{\circ}C$ |    | 11  |     | mΩ |

|----------------------|------------------------------------|---------------------------------------------------------------------|----|-----|-----|----|

| R <sub>VBUS_PD</sub> | VBUS Pulldown Resistance           | [VBUSPD_EN] = 1                                                     | 80 | 100 | 120 | Ω  |

#### SWITCH DYNAMIC CHARACTERISTICS

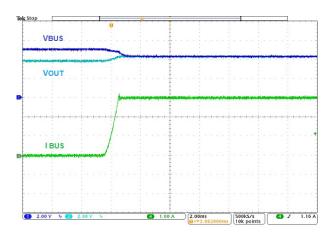

| t <sub>ENABLE</sub>      | Switch Turn_On Time                                           | V <sub>BUS</sub> =5V, V <sub>OUT</sub> =3.8V, [SW_EN]=0 to 1,<br>[ADC_EN]=0, RESET_N=HIGH, [IBUS-<br>REG]=3.5A               |      | 1.7 | ms |

|--------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

|                          |                                                               | V <sub>BUS</sub> =5V, V <sub>OUT</sub> =3.8V, [SW_EN]=0 to 1,<br>[ADC_EN]=1, RESET_N=HIGH, [IBUS-<br>REG]=3.5A               |      | 1.6 | ms |

| <sup>t</sup> DISABLE     | Switch Turn_Off Time                                          | [SW_EN] = 1 to 0                                                                                                             |      | 0.4 | ms |

| <sup>t</sup> OFF_BUSOVP  | Time to Isolate VBUS from VOUT for VBUS OVP                   | V <sub>BUS</sub> Overdrive = 100 mV above<br>VBUSOVP(th)                                                                     |      | 5.7 | μs |

| toff_BUSUVLO             | Time to Isolate VBUS from VOUT for VBUS UVLO                  | VBUS Underdrive = 100 mV below<br>VBUSUVLO(th)                                                                               |      | 5.7 | μs |

| toff_vdropovp            | Time to Isolate VBUS from VOUT for VDROP OVP                  | (V <sub>BUS</sub> -V <sub>OUT</sub> ) Overdrive = 10 mV above<br>VDROPOVP(TH)                                                |      | 5.7 | μs |

| <sup>t</sup> OFF_IBUSOCP | Time to Isolate VBUS from VOUT for IBUS Over Current Fault    | I <sub>PASS</sub> Overdrive = 200 mA above I <sub>BU</sub> -<br><sub>SOCP(TH)</sub> , no Regulation Mode control<br>(Note 9) |      | 425 | μs |

| toff_tshdn               | Time to Isolate VBUS from VOUT for Die Over Temperature Fault | T <sub>J</sub> > T <sub>SDN(TH)</sub>                                                                                        |      | 1.2 | ms |

| <sup>t</sup> OFF_RCB     | Time to Isolate VBUS from VOUT for Reverse Current Fault      | (V <sub>OUT</sub> – V <sub>BUS</sub> ) Overdrive = 10 mV above<br>VRCB(TH)                                                   |      | 10  | μs |

| twl_reset                | RESET_N Input Pulse Width Low                                 |                                                                                                                              | 1200 |     | μs |

4. V<sub>IH(max)</sub> = V<sub>PU</sub> + 0.5 V or V<sub>BAT</sub> whichever is lower

5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply V<sub>PU</sub>.

6. V<sub>IH</sub> and V<sub>IL</sub> have been chosen to be fully compliant to I<sup>2</sup>C specification at V<sub>PU</sub> = 1.8 V± 10%. At 2.25V ≤ V<sub>PU</sub> ≤ 3.63 V the V<sub>IL(max)</sub> provides > 200 mV on noise margin to the required V<sub>OL(max)</sub> of the transmitter.

7. I<sup>2</sup>C standard specifies V<sub>OL(max)</sub> for V<sub>PU</sub> ≤ 2.0 V to be 0.2 x V<sub>PU</sub>.

8. Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce tOFF\_IBUSOCP

Table 5. ELECTRICAL CHARACTERISTICS (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1; recommended operating range for T<sub>J</sub> and T<sub>A</sub>; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} = 2.7 \text{ V}$  to 4.5 V and T<sub>A</sub> = -40°C to 85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, V<sub>OUT</sub> = 3.8 V, V<sub>PU</sub> = 1.8 V.

| Symbol                     | Parameter                                         | Conditions                                                                                      | Min  | Тур  | Max  | Units |

|----------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| SWITCH DYNAMI              | C CHARACTERISTICS                                 | · · ·                                                                                           |      | •    |      |       |

| tRL_RESETI2C               | RESET_N Release to I <sup>2</sup> C Delay<br>Time | Duration required between rising edge of RESET_N and first I2C START (Note 8)                   | 120  |      |      | μs    |

| HARDWARE PRO               | TECTION (Bypass Switch)                           |                                                                                                 |      |      |      |       |

| V <sub>BUSOVP(TH)</sub>    | VBUS OVP Threshold Range                          |                                                                                                 | 4.2  |      | 6.5  | V     |

|                            | VBUS OVP Threshold Stepsize                       |                                                                                                 |      | 25   |      | mV    |

|                            | VBUS OVP Threshold Accuracy                       | [VBUSOVP_TH] = 6.5 V                                                                            | 6.4  | 6.5  | 6.6  | V     |

| t <sub>BUSOVPGLTCH</sub>   | VBUS OVP Deglitch Time                            | [OVP_DLY]=0                                                                                     |      | 4    |      | μs    |

|                            |                                                   | [OVP_DLY]=1                                                                                     |      | 20   |      | μs    |

| V <sub>BUSUVLO(TH)</sub>   | VBUS UVLO Threshold                               | $V_{BUS} > V_{BUSUVLO(TH)}$ allows the switch to close                                          | 2.84 | 2.9  | 2.96 | V     |

| V <sub>BUSUVLO(HYS)</sub>  | VBUS UVLO Hysteresis                              | Falling                                                                                         |      | 300  |      | mV    |

| t <sub>BUSUVLOGLTCH</sub>  | VBUS UVLO Deglitch Time                           |                                                                                                 |      | 4    |      | μs    |

| V <sub>DROPOVP(TH)</sub>   | VDROP OVP Threshold Range                         | V <sub>BUS</sub> – V <sub>OUT</sub>                                                             | 0    |      | 1000 | mV    |

|                            | VDROP OVP Threshold Stepsize                      | V <sub>BUS</sub> – V <sub>OUT</sub>                                                             |      | 5    |      | mV    |

|                            | VDROP OVP Threshold<br>Accuracy                   | V <sub>BUS</sub> – V <sub>OUT</sub> , 2.66V < V <sub>OUT</sub> < 4.5 V,<br>[VDROPOVP_TH]=300mV  | 295  | 300  | 305  | mV    |

| t <sub>VDROPGLTCH</sub>    | VDROP OVP Deglitch Time                           | [OVP_DLY]=0                                                                                     |      | 4    |      | μs    |

|                            |                                                   | [OVP_DLY]=1                                                                                     |      | 20   |      | μs    |

| V <sub>DROPALM(TH)</sub>   | VDROP Alarm Threshold Range                       | V <sub>BUS</sub> – V <sub>OUT</sub>                                                             | 0    |      | 1000 | mV    |

|                            | VDROP Alarm Threshold<br>Stepsize                 | V <sub>BUS</sub> – V <sub>OUT</sub>                                                             |      | 5    |      | mV    |

|                            | VDROP Alarm Threshold<br>Accuracy                 | V <sub>BUS</sub> – V <sub>OUT</sub> , 2.66 V < V <sub>OUT</sub> < 4.5 V,<br>[VDROPOVP_TH]=100mV | 80   | 100  | 115  | mV    |

| t <sub>VDROPALMGLTCH</sub> | VDROP Alarm Deglitch Time                         | [OVP_DLY]=0                                                                                     |      | 4    |      | μs    |

|                            |                                                   | [OVP_DLY]=1                                                                                     |      | 20   |      | μs    |

| IBUSOCP(TH)                | IBUS OCP Threshold Range                          |                                                                                                 | 0.5  |      | 7.5  | А     |

|                            | IBUS OCP Threshold Stepsize                       |                                                                                                 |      | 500  |      | mA    |

|                            | IBUS OCP Threshold Accuracy                       | 2.66V < V <sub>OUT</sub> < 4.5V, [IBUSOCP_TH]=5A                                                | 4.75 | 5.00 | 5.25 | А     |

| t <sub>IBUSOCPGLTCH</sub>  | IBUS OCP Deglitch Time                            | [IBUSOCP_MODE]=0                                                                                |      | 50   |      | μs    |

|                            |                                                   | [IBUSOCP_MODE]=1; Deglitch time<br>before entering Hiccup Mode                                  |      | 8    |      | μs    |

| thiccup                    | IBUS OCP Hiccup Mode Retry<br>Time                | [IBUSOCP_MODE]=1                                                                                | 80   | 100  | 125  | ms    |

| I <sub>RCB(TH)</sub>       | RCB Threshold                                     | [IRCB]=0, Current from V <sub>OUT</sub> to V <sub>BUS</sub> , V <sub>BUS</sub> $\geq$ 3 V       | -100 | 100  | +300 | mA    |

|                            |                                                   | [IRCB]=1, Current from V <sub>OUT</sub> to V <sub>BUS</sub> , V <sub>BUS</sub> $\geq$ 3 V       | 2.6  | 3    | 3.3  | A     |

| t <sub>RCBGLTCH</sub>      | RCB Deglitch Time                                 |                                                                                                 |      | 8    |      | μs    |

4.  $V_{IH(max)} = V_{PU} + 0.5 \text{ V or } V_{BAT}$  whichever is lower 5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply  $V_{PU}$ . 6.  $V_{IH}$  and  $V_{IL}$  have been chosen to be fully compliant to I<sup>2</sup>C specification at  $V_{PU} = 1.8 \text{ V} \pm 10\%$ . At 2.25V  $\leq V_{PU} \leq 3.63 \text{ V the } V_{IL(max)}$  provides > 200 mV on noise margin to the required  $V_{OL(max)}$  of the transmitter. 7. I<sup>2</sup>C standard specifies  $V_{OL(max)}$  for  $V_{PU} \le 2.0$  V to be 0.2 x  $V_{PU}$ . 8. Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce toFF\_IBUSOCP

**Table 5. ELECTRICAL CHARACTERISTICS** (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1;recommended operating range for T<sub>J</sub> and T<sub>A</sub>; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} =$ 2.7 V to 4.5 V and T<sub>A</sub> = -40°C to 85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C,  $V_{OUT} =$ 8.8 V,  $P_{PU} =$ 9.8 V,  $P_{PU} =$ 9.9 C to 85°C, unless otherwise noted.

| Symbol                      | Parameter                              | Conditions                                                                                                                                     | Min  | Тур | Max  | Units |

|-----------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| HARDWARE PRO                | TECTION (Bypass Switch)                |                                                                                                                                                |      |     |      |       |

| T <sub>SDN(TH)</sub>        | Thermal Shutdown Threshold Range       |                                                                                                                                                | 115  |     | 145  | °C    |

|                             | Thermal Shutdown Threshold<br>Stepsize |                                                                                                                                                |      | 10  |      | °C    |

|                             | Thermal Shutdown Threshold             | 3.0V < V <sub>BUS</sub> < 5.9V, [TJSHDN]=125°C                                                                                                 |      | 125 |      | °C    |

| t <sub>TSDGLTCH</sub>       | Thermal Shutdown Deglitch Time         |                                                                                                                                                |      | 800 |      | μs    |

| V <sub>FAIL</sub>           | VFAIL Short Detect Threshold           | Active only when SW_EN=0, ADC_EN=1                                                                                                             | 1.9  | 2   | 2.2  | V     |

| R <sub>VFAIL</sub>          | VFAIL Pulldown Resistor (PMID to GND)  | Active only when SW_EN=0                                                                                                                       |      | 23  |      | kΩ    |

| t <sub>VFAIL_GLTCH</sub>    | VFAIL Deglitch Time                    |                                                                                                                                                |      | 4   |      | μs    |

| VBATINSERT(TH)              | VBAT Insert Voltage                    | V <sub>BUS</sub> > V <sub>BUSUVLO(TH)</sub> ; V <sub>SNSP</sub> rising<br>above V <sub>BATINSERT(TH)</sub> indicates a con-<br>nected battery. | 1.9  | 2.0 | 2.2  | V     |

| V <sub>BATINSERT(HYS)</sub> | VBAT Insert Hysteresis                 | Falling                                                                                                                                        |      | 100 |      | mV    |

| V <sub>OUTOVP(TH)</sub>     | VOUT OVP Threshold Range               |                                                                                                                                                | 4.5  |     | 5.3  | V     |

|                             | VOUT OVP Threshold                     | [VOUTOVP_TH]=4.7V                                                                                                                              | 4.55 | 4.7 | 4.85 |       |

| V <sub>OUTOVP(HYS)</sub>    | VOUT OVP Hysteresis                    | Falling                                                                                                                                        |      | 100 |      | mV    |

| tvoutovpgltch               | VOUT OVP Deglitch Time                 | [VOUTOVP_DLY]=0                                                                                                                                |      | 4   |      | μs    |

|                             |                                        | [VOUTOVP_DLY]=1                                                                                                                                |      | 20  | 1    | μs    |

#### VOUT VOLTAGE REGULATION

| 0.23(1)) | VOREG Regulation Threshold<br>Range    |                                     | 4.2 |    | 5   | V  |

|----------|----------------------------------------|-------------------------------------|-----|----|-----|----|

|          | VOREG Regulation Threshold<br>Stepsize |                                     |     | 10 |     | mV |

|          | VOREG Regulation Threshold<br>Accuracy | [VOREG]=4.4V, T <sub>J</sub> = 25°C | -10 |    | +10 | mV |

#### **VBAT VOLTAGE REGULATION**

| VBATREG Regulation Threshold<br>Range    | V <sub>SNSP</sub> – V <sub>SNSN</sub> | 4.2 |    | 5   | V  |

|------------------------------------------|---------------------------------------|-----|----|-----|----|

| VBATREG Regulation Threshold<br>Stepsize | V <sub>SNSP</sub> – V <sub>SNSN</sub> |     | 10 |     | mV |

| VBATREG Regulation Threshold<br>Accuracy | [VBATREG]=4.3V, T <sub>J</sub> = 25°C | -10 |    | +10 | mV |

4.  $V_{IH(max)} = V_{PU} + 0.5 V \text{ or } V_{BAT}$  whichever is lower 5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply  $V_{PU}$ . 6.  $V_{IH}$  and  $V_{IL}$  have been chosen to be fully compliant to  $I^2C$  specification at  $V_{PU} = 1.8 V \pm 10\%$ . At 2.25V  $\leq V_{PU} \leq 3.63 V$  the  $V_{IL(max)}$  provides > 200 mV on noise margin to the required  $V_{OL(max)}$  of the transmitter. 7. I<sup>2</sup>C standard specifies  $V_{OL(max)}$  for  $V_{PU} \le 2.0$  V to be 0.2 x  $V_{PU}$ . 8. Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce tOFF IBUSOCP.

**Table 5. ELECTRICAL CHARACTERISTICS** (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1;recommended operating range for T<sub>J</sub> and T<sub>A</sub>; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} = 2.7$  V to 4.5 V and T<sub>A</sub> = -40°C to 85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C,  $V_{OUT} = 3.8$  V,  $V_{PU} = 1.8$  V.

| Symbol       | Parameter                                | Conditions                                                                | Min | Тур | Max  | Units |

|--------------|------------------------------------------|---------------------------------------------------------------------------|-----|-----|------|-------|

| IBAT CURRENT | REGULATION                               |                                                                           |     |     |      |       |

| IBATREG(TH)  | IBATREG Regulation Threshold<br>Range    | $V_{SRP}$ – $V_{SRN}$ sensed across $R_{SENSE}$ .                         | 0.1 |     | 6.35 | А     |

|              | IBATREG Regulation Threshold<br>Stepsize |                                                                           |     | 50  |      | mA    |

|              | IBATREG Regulation Threshold<br>Accuracy | 2.5V < V <sub>OUT</sub> < 4.5V,<br>R <sub>SENSE</sub> =10mΩ, [IBATREG]=2A | -5  |     | +5   | %     |

|              |                                          | 2.5V < V <sub>OUT</sub> < 4.5V,<br>R <sub>SENSE</sub> =5mΩ, [IBATREG]=4A  | -5  |     | +5   | %     |

#### **IBUS CURRENT REGULATION**

| () | IBUSREG Regulation Threshold<br>Range    |                                                  | 0.1 |    | 6.5 | A  |

|----|------------------------------------------|--------------------------------------------------|-----|----|-----|----|

|    | IBUSREG Regulation Threshold<br>Stepsize |                                                  |     | 50 |     | mA |

|    | IBUSREG Regulation Threshold<br>Accuracy | 2.66 < V <sub>OUT</sub> < 4.5; [IBUSREG] = 3.5 A | -5  |    | +5  | %  |

#### BATTERY CELL VOLTAGE SENSE INPUTS (VSNSP, VSNSN)

| I <sub>SNSP</sub> | SNSP Input Current | 2.66 V < V <sub>SNSP</sub> < 4.5 V |  | 5 | μΑ |

|-------------------|--------------------|------------------------------------|--|---|----|

| I <sub>SNSN</sub> | SNSN Input Current | 0.0 V < V <sub>SNSN</sub> < 0.2 V  |  | 1 | μΑ |

#### LOGIC LEVELS (SCL, SDA, ADR, INT N, RESET N)

| V <sub>IH</sub> | Input High Voltage Level       |                               | 1.05 |     | V  |

|-----------------|--------------------------------|-------------------------------|------|-----|----|

| V <sub>IL</sub> | Input Low Voltage Level        |                               |      | 0.4 | V  |

| V <sub>OL</sub> | Output Low Voltage, INT_N, SDA | I <sub>OL</sub> = 3 mA        |      | 0.4 | V  |

| l <sub>IN</sub> | Input current each I/O pin     | V <sub>PIN</sub> = 0 V or 5 V | -10  | +10 | μΑ |

#### BATTERY CURRENT SENSE INPUTS (VSRP, VSRN)

| I <sub>SRP</sub> | V <sub>SRP</sub> Input Current | 0 < V <sub>SRP</sub> < 0.2  |    | 1 | μΑ |

|------------------|--------------------------------|-----------------------------|----|---|----|

| I <sub>SRN</sub> | V <sub>SRN</sub> Input Current | –0.2 < V <sub>SRN</sub> < 0 | -1 |   | μΑ |

### WATCH DOG TIMER

| t <sub>WDT</sub> | Watchdog Timer Range    |                    | 0.5 | 2   | s |

|------------------|-------------------------|--------------------|-----|-----|---|

|                  | Watchdog Timer Accuracy | All [WDT] Settings | -10 | +10 | % |

#### ANALOG TO DIGITAL CONVERTER

| RES               | Resolution                    | (Note 8) | 10  |     |     | Bits |

|-------------------|-------------------------------|----------|-----|-----|-----|------|

| INL               | Integral Non-Linearity        |          |     | ±1  |     | LSB  |

| DNL               | Differential Non-Linearity    |          |     | ±1  |     | LSB  |

| OE                | Offset Error                  |          |     | ±1  |     | LSB  |

| GE                | Gain Error (Full Scale Error) |          |     | ±1  |     | LSB  |

| f <sub>CONV</sub> | Conversion Clock              |          | 2.7 | 3.0 | 3.3 | MHz  |

4.  $V_{IH(max)} = V_{PU} + 0.5 V$  or  $V_{BAT}$  whichever is lower 5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply  $V_{PU}$ .

N is assumed that the SCL and SDA pins are open dram with external pun-ups resistors tied to an external supply vpg.

V<sub>IH</sub> and V<sub>IL</sub> have been chosen to be fully compliant to l<sup>2</sup>C specification at V<sub>PU</sub> = 1.8 V± 10%. At 2.25V ≤ V<sub>PU</sub> ≤ 3.63 V the V<sub>IL(max)</sub> provides > 200 mV on noise margin to the required V<sub>OL(max)</sub> of the transmitter.

I<sup>2</sup>C standard specifies V<sub>OL(max)</sub> for V<sub>PU</sub> ≤ 2.0 V to be 0.2 x V<sub>PU</sub>.

Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce tOFF IBUSOCP

Table 5. ELECTRICAL CHARACTERISTICS (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1; recommended operating range for  $T_J$  and  $T_A$ ; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} = 2.7 \text{ V}$  to 4.5 V and  $T_A = -40^{\circ}\text{C}$  to 85°C, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = 3.8 \text{ V}$ ,  $V_{PU} = 1.8 \text{ V}$ .

| Symbol                  | Parameter                                        | Conditions                                                                                                                         | Min  | Тур  | Max  | Units |

|-------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| NALOG TO DIGI           | TAL CONVERTER                                    |                                                                                                                                    |      |      |      |       |

| <sup>t</sup> THR_ONE    | Throughput time (Single-shot conversion)         | No Averaging, 1 channel, One-shot con-<br>version (ADC_RATE = 0, ADC_EN written<br>from 0 to 1)                                    |      | 47   |      | μs    |

|                         |                                                  | 8-sample Averaging (AVG_EN=1, SAM-<br>PLES=0), 1 channel, One-shot conver-<br>sion (ADC_RATE = 0, ADC_EN written<br>from 0 to 1)   |      | 84   |      | μs    |

|                         |                                                  | 16-sample Averaging (AVG_EN=1, SAM-<br>PLES=1), 1 channel, One-shot conver-<br>sion (ADC_RATE = 0, ADC_EN written<br>from 0 to 1)  |      | 127  |      | μs    |

|                         |                                                  | 16-sample Averaging (AVG_EN=1, SAM-<br>PLES=1), 9 channels, One-shot conver-<br>sion (ADC_RATE = 0, ADC_EN written<br>from 0 to 1) |      | 1031 |      | μs    |

| t <sub>THR_CONT</sub>   | Throughput time (Continuous<br>Conversion)       | No Averaging, 1 channel, Continuous<br>conversion (ADC_RATE = 1, ADC_EN=1)                                                         |      | 33   |      | μs    |

|                         |                                                  | 8-sample Averaging (AVG_EN=1, SAM-<br>PLES=0), 1 channel, Continuous conver-<br>sion (ADC_RATE = 1, ADC_EN=1)                      |      | 70   |      | μs    |

|                         |                                                  | 16-sample Averaging (AVG_EN=1, SAM-<br>PLES=1), 1 channel, Continuous conver-<br>sion (ADC_RATE = 1, ADC_EN=1)                     |      | 113  |      | μs    |

|                         |                                                  | 16-sample Averaging (AVG_EN=1, SAM-<br>PLES=1), 9 channels, Continuous con-<br>version (ADC_RATE = 1, ADC_EN=1)                    |      | 1018 |      | μs    |

| GAIN <sub>IBAT</sub>    | Battery Current ADC Gain Range                   | RSENSE = 0                                                                                                                         |      | 40   |      | V/V   |

|                         |                                                  | RSENSE = 1                                                                                                                         |      | 20   |      | V/V   |

| VBUS <sub>ADC</sub>     | VBUS Channel Full Scale Range                    | Signal sensed at VBUS pin, 7.3 mV per<br>LSB                                                                                       | 0    |      | 6.1  | V     |

| VBAT <sub>ADC</sub>     | VBAT Channel Full Scale Range                    | Signal sensed across and SNSP and SNSN pins, 5.3 mV per LSB                                                                        | 2.5  |      | 5.0  | V     |

| VOUT <sub>ADC</sub>     | VOUT Channel Full Scale Range                    | Signal sensed at VOUT, 5.3 mV per LSB                                                                                              | 0    |      | 5.0  | V     |

| VDROP <sub>ADC</sub>    | VDROP Channel Full Scale<br>Range                | Signal sensed between VBUS and VOUT pins, 2.9 mV per LSB                                                                           | 0    |      | 1.0  | V     |

| IBUS <sub>ADC</sub>     | IBUS Channel Full Scale Range                    | Signal sensed across internal switch, 14.6 mA per LSB                                                                              | 0    |      | 7.0  | A     |

| IBAT <sub>ADC</sub>     | IBAT Channel Full Scale Range                    | Signal sensed across SRP and SRN pins, 14.6 mA per LSB                                                                             | -7.0 |      | +7.0 | A     |

| TBUS_BAT <sub>ADC</sub> | TBUS and TBAT Channel Full<br>Scale Range        | Signal sensed at TS_BUS and TS_BAT<br>pins, 2.9 mV per LSB respectively                                                            | 0    |      | 2.4  | V     |

| TBUS_TBAT_GLTCH         | TBUS and TBAT Temperature<br>Fault Deglitch Time | Deglitch time to open switch when<br>V <sub>TBUS</sub> falls below TBUS_TH or<br>V <sub>TBAT</sub> falls below TBAT_TH             | 0.9  | 1    | 1.1  | s     |

| TDIE <sub>ADC</sub>     | TDIE Channel Full Scale Range                    | Signal sensed by internal temperature<br>sensor, 1°C per LSB                                                                       | 25   |      | 150  | °C    |

4.  $V_{IH(max)} = V_{PU} + 0.5 V$  or  $V_{BAT}$  whichever is lower 5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply  $V_{PU}$ .

6. V<sub>IH</sub> and V<sub>IL</sub> have been chosen to be fully compliant to I<sup>2</sup>C specification at V<sub>PU</sub> = 1.8 V  $\pm$  10%. At 2.25V  $\leq$  V<sub>PU</sub>  $\leq$  3.63 V the V<sub>IL(max)</sub> provides > 200 mV on noise margin to the required  $V_{OL(max)}$  of the transmitter. 7. I<sup>2</sup>C standard specifies  $V_{OL(max)}$  for  $V_{PU} \le 2.0$  V to be 0.2 x  $V_{PU}$ . 8. Guaranteed by design. Not tested in production. 9. Regulation Mode control will reduce t<sub>OFF\_IBUSOCP</sub>.

**Table 5. ELECTRICAL CHARACTERISTICS** (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1;recommended operating range for T<sub>J</sub> and T<sub>A</sub>; The Recommended Operating Conditions for DC Electrical Characteristics assume  $V_{OUT} = 2.7$  V to 4.5 V and T<sub>A</sub> = -40°C to 85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C,  $V_{OUT} = 3.8$  V,  $V_{PU} = 1.8$  V.

| Symbol                    | Parameter                    | Conditions                                                                                                                                                                                                                                | Min | Тур  | Max | Units |

|---------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| OVP_C CONTRO              | L (External OVP FET Control) |                                                                                                                                                                                                                                           |     | -    | -   |       |

| V <sub>USBOVP(TH)</sub>   | VUSB OVP Threshold           | $V_{USB} > V_{USBOVP(TH)}$ drives OVP_C low                                                                                                                                                                                               | 15  | 16.5 | 18  | V     |

| V <sub>USBOVP(HYS)</sub>  | VUSB OVP Hysteresis          | V <sub>USB</sub> Falling                                                                                                                                                                                                                  |     | 1    |     | V     |

| V <sub>USBUVLO(TH)</sub>  | VUSB UVLO Threshold          | V <sub>USBOVP(TH)</sub> >V <sub>USB</sub> > V <sub>USBUVLO(TH)</sub> will<br>drive OVP_C high                                                                                                                                             | 2.5 | 2.6  | 2.7 | V     |

| V <sub>USBUVLO(HYS)</sub> | VUSB UVLO Hysteresis         | Falling, V <sub>USB</sub> < V <sub>USBUVLO(TH)</sub> -<br>V <sub>USBUVLO(HYS)</sub> will drive OVP_C low                                                                                                                                  |     | 200  |     | mV    |

| OVP_C(HI)                 | OVP_C Gate Drive Voltage     | V <sub>USBUVLO(TH)</sub> < V <sub>USB</sub> < V <sub>USBOVP(TH)</sub> ;<br>measured from OVP_C to VBUS                                                                                                                                    | 4.5 | 4.8  | 5.1 | V     |

| <sup>t</sup> off_usbovp   | OVP_C Gate Turn-Off Time     | Gate Capacitance =5.2nF; 2V/us $V_{USB}$<br>ramp rate; Time from $V_{USB}$ rising above<br>$V_{USBOVP(TH)}$ to external FET open (where<br>VBUS stops increasing); $V_{USB}$ compara-<br>tor delay included; FDMC8321L N-Chan-<br>nel FET |     | 0.7  |     | μs    |

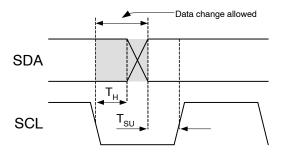

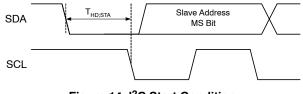

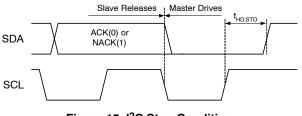

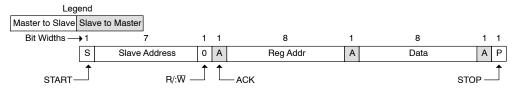

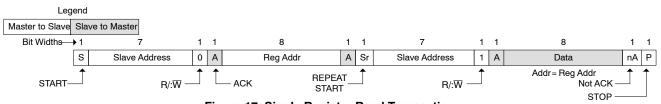

I<sup>2</sup>C TIMING SPECIFICATIONS

| f <sub>SCL</sub>    | SCL Clock Frequency                  | Standard Mode  |     | 100  | kHz |

|---------------------|--------------------------------------|----------------|-----|------|-----|

|                     |                                      | Fast Mode      |     | 400  | kHz |

|                     |                                      | Fast Mode Plus |     | 1000 | kHz |

| t <sub>BUF</sub>    | Bus-Free Time Between STOP           | Standard Mode  | 4.7 |      | μs  |

|                     | and START Conditions                 | Fast Mode      | 1.3 |      | μs  |

|                     |                                      | Fast Mode Plus | 0.5 |      | μs  |

| t <sub>HD;STA</sub> | START or Repeated START Hold<br>Time | Standard Mode  | 4   |      | μs  |

|                     | lime                                 | Fast Mode      | 600 |      | ns  |

|                     |                                      | Fast Mode Plus | 260 |      | ns  |

| t <sub>LOW</sub>    | SCL LOW Period                       | Standard Mode  | 4.7 |      | με  |

|                     |                                      | Fast Mode      | 1.3 |      | μs  |

|                     |                                      | Fast Mode Plus | 0.5 |      | μs  |

| t <sub>HIGH</sub>   | SCL HIGH Period                      | Standard Mode  | 4   |      | μs  |

|                     |                                      | Fast Mode      | 600 |      | ns  |

|                     |                                      | Fast Mode-Plus | 260 |      | ns  |

| t <sub>SU;STA</sub> | Repeated START Setup Time            | Standard Mode  | 4.7 |      | μs  |

|                     |                                      | Fast Mode      | 600 |      | ns  |

|                     |                                      | Fast Mode-Plus | 260 |      | ns  |

| t <sub>SU;DAT</sub> | Data Setup Time                      | Standard Mode  | 250 |      | ns  |

|                     |                                      | Fast Mode      | 100 |      | ns  |

|                     |                                      | Fast Mode Plus | 50  |      | ns  |

4. V<sub>IH(max)</sub> = V<sub>PU</sub> + 0.5 V or V<sub>BAT</sub> whichever is lower

5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply V<sub>PU</sub>.

6. V<sub>IH</sub> and V<sub>IL</sub> have been chosen to be fully compliant to I<sup>2</sup>C specification at V<sub>PU</sub> = 1.8 V± 10%. At 2.25V ≤ V<sub>PU</sub> ≤ 3.63 V the V<sub>IL(max)</sub> provides > 200 mV on noise margin to the required V<sub>OL(max)</sub> of the transmitter.

7. I<sup>2</sup>C standard specifies V<sub>OL(max)</sub> for V<sub>PU</sub> ≤ 2.0 V to be 0.2 x V<sub>PU</sub>.

8. Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce t<sub>OFF\_IBUSOCP</sub>.

| Table 5. ELECTRICAL CHARACTERISTICS (Notes 4, 5, 6, 7) Unless otherwise specified: according to the circuit in Figure 1;                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| recommended operating range for T <sub>J</sub> and T <sub>A</sub> ; The Recommended Operating Conditions for DC Electrical Characteristics assume V <sub>OUT</sub> = |

| 2.7 V to 4.5 V and $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at $T_A = 25^{\circ}$ C, $V_{OUT} = 3.8$ V, $V_{PU} = 1.8$ V.           |

| Symbol              | Parameter                                                         | Conditions     | Min        | Тур | Max  | Units |

|---------------------|-------------------------------------------------------------------|----------------|------------|-----|------|-------|

| C TIMING SPE        | CIFICATIONS                                                       |                |            |     |      |       |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | Standard Mode  | 0          |     | 3.45 | μs    |

|                     |                                                                   | Fast Mode      | 0          |     | 900  | ns    |

|                     |                                                                   | Fast Mode Plus | 0          |     | 450  | ns    |

| t <sub>RCL</sub>    | SCL Rise Time                                                     | Standard Mode  | 20 + 0.1Cb |     | 1000 | ns    |

|                     |                                                                   | Fast Mode      | 20 + 0.1Cb |     | 300  | ns    |

|                     |                                                                   | Fast Mode Plus | 20 + 0.1Cb |     | 120  | ns    |

| t <sub>RDA</sub>    | SDA Rise Time                                                     | Standard Mode  | 20 + 0.1Cb |     | 1000 | ns    |

|                     |                                                                   | Fast Mode      | 20 + 0.1Cb |     | 300  | ns    |

|                     |                                                                   | Fast Mode Plus | 20 + 0.1Cb |     | 120  | ns    |

| t <sub>FDA</sub>    | SDA Fall Time                                                     | Standard Mode  | 20 + 0.1Cb |     | 300  | ns    |

|                     |                                                                   | Fast Mode      | 20 + 0.1Cb |     | 300  | ns    |

|                     |                                                                   | Fast Mode Plus | 20 + 0.1Cb |     | 120  | ns    |

| t <sub>SU;STO</sub> | Stop Condition Setup Time                                         | Standard Mode  |            | 4   |      | μs    |

|                     |                                                                   | Fast Mode      |            | 600 |      | ns    |

|                     |                                                                   | Fast Mode Plus |            | 120 |      | ns    |

| Cb                  | Capacitive Load for SDA and SCL                                   |                |            |     | 400  | pF    |

| t <sub>SP</sub>     | Pulse width of spikes which must<br>be suppressed by input filter | SCL, SDA only  | 0          |     | 50   | ns    |

4. V<sub>IH(max)</sub> = V<sub>PU</sub> + 0.5 V or V<sub>BAT</sub> whichever is lower

5. It is assumed that the SCL and SDA pins are open drain with external pull-ups resistors tied to an external supply V<sub>PU</sub>.

6. V<sub>IH</sub> and V<sub>IL</sub> have been chosen to be fully compliant to I<sup>2</sup>C specification at V<sub>PU</sub> = 1.8 V± 10%. At 2.25V ≤ V<sub>PU</sub> ≤ 3.63 V the V<sub>IL(max)</sub> provides > 200 mV on noise margin to the required V<sub>OL(max)</sub> of the transmitter.

7. I<sup>2</sup>C standard specifies V<sub>OL(max)</sub> for V<sub>PU</sub> ≤ 2.0 V to be 0.2 x V<sub>PU</sub>.

8. Guaranteed by design. Not tested in production.

9. Regulation Mode control will reduce t<sub>OFF\_IBUSOCP</sub>.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### **Typical Characteristics**

Unless otherwise specified: Default register settings,  $T_A = 25^{\circ}C$ , VOUT = 3.8 V, VPU = 1.8 V.

VBUS=Open, RESET\_N=LOW

Figure 5. On Resistance from VBUS to VOUT, Normalized to 1.0 A/25°C

# **Typical Characteristics**

Unless otherwise specified: Default register settings,  $T_A$  = 25°C, VOUT = 3.8 V, VPU = 1.8 V.

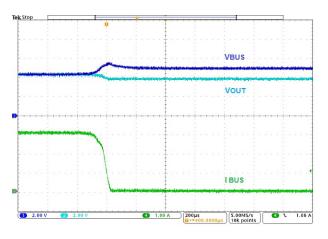

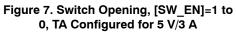

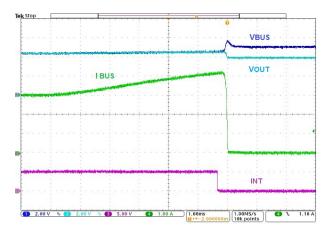

Figure 8. Switch Opening IBUS OCP Fault, [IBUSOCP]=4A, [IBUSREG]=[IBATREG]=max, TA Current Limit Raised from 3 A to 5 A

Figure 9. Load Transient Response, [IBATREG]=2A, [IBUSREG]=3.5A, TA Configured for 5 V/5 A

### **Functional Specifications**

### **Charging Bypass Switch with Regulation Mode**

#### Overview

The FAN54161 is designed to be placed in a system that requires high current charging for a large battery. It is essentially a high current bypass switch with protection that provides a path from a charging source (adapter) to the battery directly through a low resistance path. In order to ensure safety of the battery as well as the system, the FAN54161 features multiple hardware protection mechanisms. Most of these result in the path from the charging source to the battery being opened. Examples of these are input over–voltage, over–current through the switch and reverse current.

Some of the parameters are monitored and regulated such that they are at or below a programmed threshold. This is achieved by controlling the gate of the power switch. However, this mode of operation is only meant to be used temporarily while the system controller/host reacts to this and corrects the system configuration to allow the switch to return to a bypass mode (fully–on state).

Many of the hardware protection mechanisms have  $I^2C$  programmable thresholds, enable/disable controls, interrupts with masks and status bits. The product block diagram (Figure 1) provides an illustrative overview of the functionality within the FAN54161.

The FAN54161 also utilizes a fully independent charge pump based gate drive circuit to control an optional external N-channel MOSFET for an additional level of input protection from over voltage faults up to 32 V applied at the USB port.

#### **Bypass Switch Modes of Operation**

Broadly speaking, the FAN54161 has four modes of bypass switch operation.

- 1. **OFF:** This represents a lack of power to the FAN54161.

- 2. **SHUTDOWN:** Valid power is applied to one of VBUS or VOUT but the RESET\_N input is asserted low. In this state, no communication with the FAN54161 is possible and the switch is forced open.

- 3. **STANDBY:** Valid power is applied to one of VBUS or VOUT and the RESET\_N input is de-asserted high. I2C communication is enabled, but, the switch is not programmed to close.

- 4. **SWITCH ENABLED:** As evidenced by the name, the FAN54161 bypass switch is closed in this state. From the STANDBY state, when the SW\_EN bit is written with a 1, the FAN54161 enters the SWITCH ENABLED state. In this state, the switch's gate is controlled by the control circuit of the FAN54161 to be either fully on (bypass mode) or partially on (regulation mode) based on the parameters being monitored.

#### Power-up and Reset (VBUS and VOUT)

When power is first applied to either VBUS or VOUT, an internal power-on reset (POR) circuit ensures the default state of all registers and circuits and keeps the switch in the OPEN state. Power for all internal logic circuits comes from the higher of VBUS and VOUT. This allows the FAN54161 to be I<sup>2</sup>C programmable even with just one of the supplies present (VBUS or VOUT).

The RESET\_N pin is an active-low reset input. When the RESET\_N pin is asserted low externally, the FAN54161 remains in a reset state and does not support I<sup>2</sup>C communication. The switch is forced OPEN. This corresponds to the SHUTDOWN state. The RESET\_N pin being low also forces the ADC in the FAN54161 to its SHUTDOWN state.

In order to properly control and operate the FAN54161, a valid supply must be present at VBUS or VOUT and the RESET\_N pin must be de-asserted (logic high state).

#### VUSB Power

The VUSB pin does not affect POR behavior of the FAN54161 and should be considered a completely independent power domain with respect to VBUS and VOUT.

#### **Hardware Fault Protection**

The FAN54161 features hardware safety protection monitors, some of which can cause the switch to OPEN if enabled. Other than VBUS UVLO and IC Thermal Shutdown, each hardware safety protection monitor has an independently programmable enable bit.

The high current switch is closed by setting  $SW_EN = 1$ . Before the switch closes, though, the IC is checked against the following safety protection thresholds:

- VBUS UVLO

- VBUS OVP

- VOUT OVP

- VDROP OVP

- Thermal Shutdown

If any of these safety protection monitors are enabled and the associated fault is triggered, the switch is not allowed to close and the appropriate interrupt bit is set to report the fault to the system controller/host. If no faults are triggered when SW EN bit is set, the switch is closed.

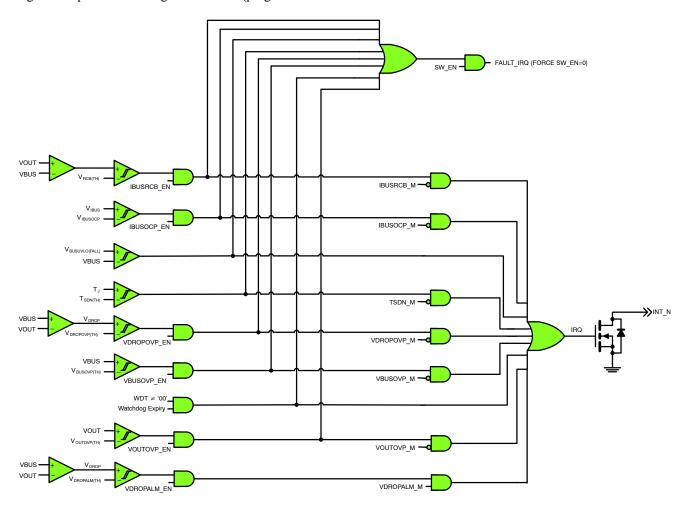

When the switch is closed, all enabled safety protection monitors are armed. With the exception of VOREG, VBATREG, IBATREG, and IBUSREG, if any enabled fault is triggered, the switch is opened and its appropriate interrupt bit is set to 1. Refer to Figure 10 for details.

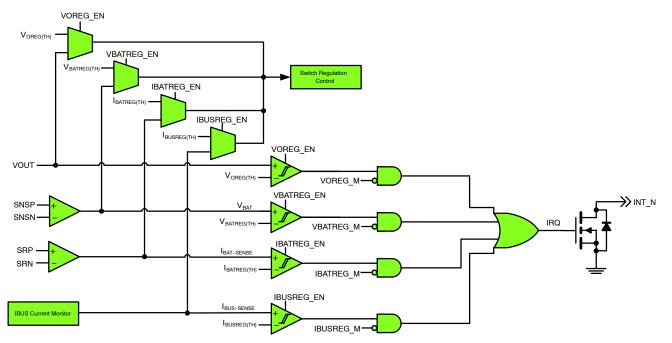

When the switch is closed, if a VOREG, VBATREG, IBATREG, or IBATREG fault is triggered, the internal logic drives the gate of the bypass switch such that the current or voltage does not exceed its regulation threshold. Additionally, its appropriate interrupt bit is set to 1. It is expected that the host will take action to correct the system configuration such that the FAN54161's regulation control loop can drive the gate of the power switch to make it fully on again. Refer to Figure 11 for details.

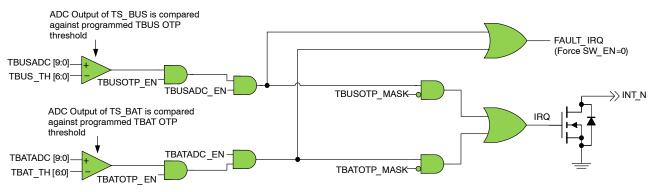

The hardware protections for the VBUS connector and battery (T\_BUS and T\_BAT) are implemented through digital comparisons of a digital threshold (programmed in the TBUSOTP and TBATOTP registers) to the ADC's converted results of these channels. Therefore, if these fault protections are enabled, it must be ensured that the ADC is enabled and programmed to convert this channel.

For additional details on Hardware Fault Protection, refer to Table 6 and Table 7.

Figure 10. Hardware Protection Logic Diagram

### Table 6. HARDWARE FAULT PROTECTION ENTRY SUMMARY

| Safety<br>Feature    | Safety Mode Entry                                                 | Safety Mode Deglitch<br>Time                | Safety Mode Hardware Action                                                                                                                                                                                                                                                | Safety Mode Register Action                                             |  |

|----------------------|-------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| VBUS OVP             | V <sub>BUS</sub> ><br>V <sub>BUSOVP(TH)</sub>                     | 4us (OVP_DLY=0)<br>20us (OVP_DLY=1)         | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>VBUSOVP_INT=1                                                |  |

| VBUS UVLO<br>Falling | $V_{BUS} < (V_{BUSUVLO(TH)} - V_{BUSUVLO(HYS)})$                  | 4us                                         | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | VBUSINSERT_INT=1                                                        |  |

| VDROP<br>Alarm       | $V_{DROP} > V_{DROPALM(TH)}$                                      | 4us (OVP_DLY=0)<br>20us (OVP_DLY=1)         | Pull INT_N low                                                                                                                                                                                                                                                             | VDROPALM_INT=1                                                          |  |

| VDROP OVP            | $V_{DROP} > V_{DROPOVP(TH)}$                                      | 4us (OVP_DLY=0)<br>20us (OVP_DLY=1)         | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>VDROPOVP_INT=1                                               |  |

| TS_BUS<br>Overtemp   | V <sub>TS_BUS</sub> < T <sub>BUS_TH</sub><br>(digital comparator) | 1s                                          | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>TBUSOTP_INT=1                                                |  |

| TS_BAT<br>Overtemp   | V <sub>TS_BAT</sub> < T <sub>BAT_TH</sub><br>(digital comparator) | 1s                                          | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>TBATOTP_INT=1                                                |  |

| Thermal<br>Shutdown  | $T_{\rm J} > T_{\rm SDN(TH)}$                                     | 800us                                       | Open Bypass Switch<br>Disable ADC<br>Pull INT_N Iow                                                                                                                                                                                                                        | SW_EN=0<br>ADC_EN bit does not change state<br>TSDN_INT=1               |  |

| Watchdog<br>Timer    | Watchdog Timer Expired                                            | N/A                                         | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>Reset registers to default (except TIMER_INT)<br>TIMER_INT=1 |  |

|                      |                                                                   | 50us (IBUSOCP_MODE=0)                       | Open Bypass Switch<br>Pull INT_N low                                                                                                                                                                                                                                       | SW_EN=0<br>IBUSOCP_INT=1                                                |  |

| IBUS OCP             | $I_{BUS} > I_{BUSOCP(TH)}$                                        | 4us (IBUSOCP_MODE=1)                        | 1- Open Bypass Switch and enter Hiccup Mode<br>2- Wait 100ms then close switch<br>3- If $I_{UUS} < I_{BUISOP(TH)}$ continue charging<br>4- If $I_{BUS} > I_{BUISOP(TH)}$ return to top (up to 6 attempts)<br>5- If still OCP leave Bypass Switch open<br>6- Pull INT_N low | Set SW_EN=0<br>IBUSOCP_INT=1<br>(Only after 6 failed Hiccup attempts)   |  |

| IBUSREG              | $I_{BUS} > I_{BUSREG(TH)}$                                        | N/A                                         | Enter Regulation Mode<br>Limit I <sub>BUS</sub> to I <sub>BUSREG(TH)</sub><br>Pull INT_N Iow                                                                                                                                                                               | IBUSREG_INT=1                                                           |  |

| IBATREG              | $((V_{SRP} - V_{SRN}) / R_{SENSE}) > I_{BATREG(TH)}$              | N/A                                         | Enter Regulation Mode<br>Limit I <sub>ват</sub> to I <sub>ватвео(Тн)</sub><br>Pull INT_N Iow                                                                                                                                                                               | IBATREG_INT=1                                                           |  |

| VOREG                | $V_{OUT} > V_{OREG(TH)}$                                          | N/A                                         | Enter Regulation Mode<br>Limit V <sub>OUT</sub> to V <sub>OREG(TH)</sub><br>Pull INT_N Iow                                                                                                                                                                                 | VOREG_INT=1                                                             |  |

| VBATREG              | $(V_{SNSP} - V_{SNSN}) > V_{BATREG(TH)}$                          | N/A                                         | Enter Regulation Mode<br>Limit V <sub>SNSP</sub> – V <sub>SNSN</sub> to V <sub>BATREG(TH)</sub><br>Pull INT_N Iow                                                                                                                                                          | VBATREG_INT=1                                                           |  |