# **DS64EV100 Programmable Single Equalizer**

Check for Samples: DS64EV100

### **FEATURES**

- Equalizes up to 24 dB loss at 10 Gbps

- Equalizes up to 22 dB loss at 6.4 Gbps

- 8 levels of programmable equalization

- Operates up to 10 Gbps with 30" FR4 traces

- Operates up to 6.4 Gbps with 40" FR4 traces

- 0.175 UI residual deterministic jitter at 6.4 Gbps with 40" FR4 traces

- Single 2.5V or 3.3V power supply

- Supports AC or DC-Coupling with wide input common-mode

- Low power consumption: 100 mW Typ at 2.5V

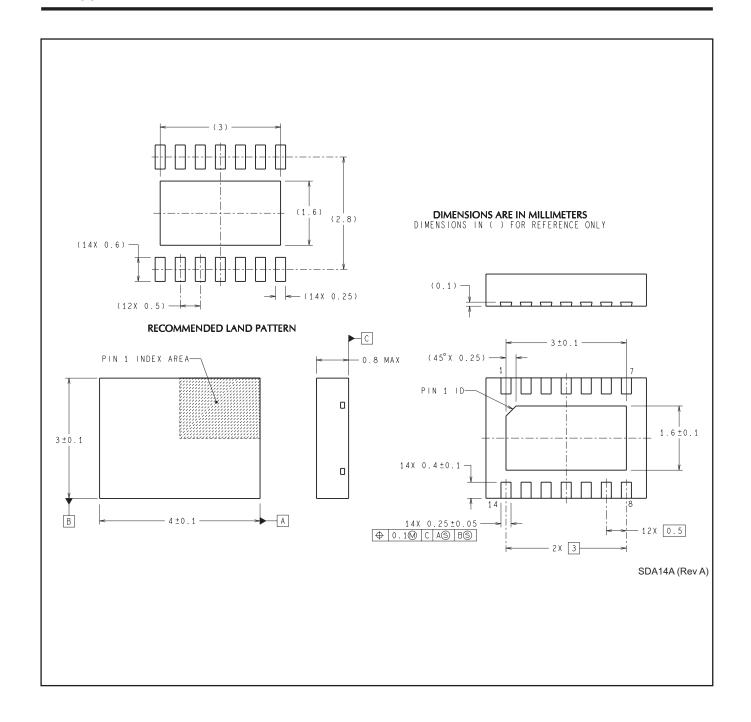

- Small 3 mm x 4 mm 14-pin WSON package

- > 8 kV HBM ESD Rating

- -40 to 85°C operating temperature range

# **DESCRIPTION**

The DS64EV100 programmable equalizer provides compensation for transmission medium losses and reduces the medium-induced deterministic jitter for NRZ data channel. The DS64EV100 is optimized for operation up to 10 Gbps for both cables and FR4 traces. The equalizer channel has eight levels of input equalization that can be programmed by three control pins.

The equalizer supports both AC and DC-coupled data paths for long run length data patterns such as PRBS-31, and balanced codes such as 8b/10b. The device uses differential current-mode logic (CML) inputs and outputs. The DS64EV100 is available in a 3 mm x 4 mm 14-pin leadless WSON package. Power is supplied from either a 2.5V or 3.3V supply.

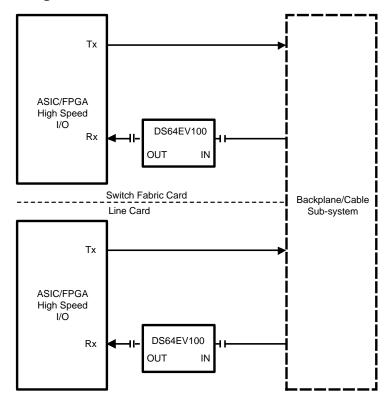

### **Simplified Application Diagram**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

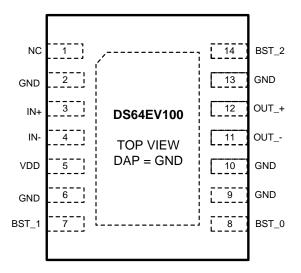

# Pin Diagram

Figure 1. 14-Pin WSON Package (3 mm x 4 mm x 0.8 mm, 0.5 mm pitch) See Package Number NHK0014A

**Table 1. Pin Descriptions**

|                         |                    | 1            |                                                                                                                                                                                                      |

|-------------------------|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                | Pin #              | I/O,<br>Type | Description                                                                                                                                                                                          |

| HIGH SPEED              | DIFFERENTIA        | L I/O        |                                                                                                                                                                                                      |

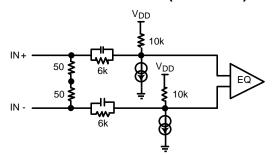

| IN+<br>IN-              | 3<br>4             | I, CML       | Inverting and non-inverting CML differential inputs to the equalizer. An on-chip $100\Omega$ terminating resistor is connected between IN+ and IN Refer to Figure 4.                                 |

| OUT+<br>OUT-            | 12<br>11           | O, CML       | Inverting and non-inverting CML differential outputs from the equalizer. An on-chip $50\Omega$ terminating resistor connects OUT+ to $V_{DD}$ and OUT- to $V_{DD}$ .                                 |

| EQUALIZATION            | ON CONTROL         |              |                                                                                                                                                                                                      |

| BST_2<br>BST_1<br>BST_0 | 14<br>7<br>8       | I, CMOS      | BST_2, BST_1, and BST_0 select the equalizer strength. BST_2 is internally pulled high. BST_1 and BST_0 are internally pulled low.                                                                   |

| POWER                   |                    |              |                                                                                                                                                                                                      |

| $V_{DD}$                | 5                  | I, Power     | $V_{DD}$ = 2.5V ±5% or 3.3V ±10%. $V_{DD}$ pins should be tied to $V_{DD}$ plane through low inductance path. A 0.01µF bypass capacitor should be connected between each $V_{DD}$ pin to GND planes. |

| GND                     | 2, 6, 9, 10,<br>13 | I, Power     | Ground reference. GND should be tied to a solid ground plane through a low impedance path.                                                                                                           |

| DAP                     | PAD                | I, Power     | Ground reference. The exposed pad at the center of the package must be connected to ground plane of the board.                                                                                       |

| OTHER                   |                    |              |                                                                                                                                                                                                      |

| NC                      | 1                  |              | Reserved. Do not connect.                                                                                                                                                                            |

|                         |                    |              |                                                                                                                                                                                                      |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings (1)(2)

| Supply Voltage (V <sub>DD</sub> )                    | −0.5V to +4V    |

|------------------------------------------------------|-----------------|

| CMOS Input Voltage                                   | -0.5V to +4.0V  |

| CMOS Output Voltage                                  | -0.5V to +4.0V  |

| CML Input/Output Voltage                             | -0.5V to +4.0V  |

| Junction Temperature                                 | +150°C          |

| Storage Temperature                                  | −65°C to +150°C |

| Lead Temperature<br>Soldering, 4 sec                 | +260°C          |

| ESD Rating                                           |                 |

| HBM, 1.5 kΩ, 100 pF                                  | > 8 kV          |

| EIAJ, 0Ω, 200 pF                                     | > 250 V         |

| Thermal Resistance, $\theta_{\text{JA}},$ No Airflow | 40 °C/W         |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute Maximum Numbers are guaranteed for a junction temperature range of -40°C to +125°C. Models are validated to Maximum Operating Voltages only.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for availability and specifications.

### **Recommended Operating Conditions**

|                               | MIN   | TYP      | MAX   | UNIT |

|-------------------------------|-------|----------|-------|------|

| Supply Voltage <sup>(1)</sup> |       | <u>'</u> |       | •    |

| V <sub>DD2.5</sub> to GND     | 2.375 | 2.5      | 2.625 | V    |

| V <sub>DD3.3</sub> to GND     | 3.0   | 3.3      | 3.6   | V    |

| Ambient Temperature           | -40   | 25       | +85   | °C   |

<sup>(1)</sup> The  $V_{DD2.5}$  is  $V_{DD}$  = 2.5V ± 5% and  $V_{DD3.3}$  is  $V_{DD}$  = 3.3V ± 10%.

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified. (1) (2)

|                 | PARAMETER                | TEST CONDITIONS                                       | MIN  | TYP <sup>(1)</sup> | MAX               | UNIT                                                            |

|-----------------|--------------------------|-------------------------------------------------------|------|--------------------|-------------------|-----------------------------------------------------------------|

| POWE            | R                        |                                                       |      |                    |                   |                                                                 |

| Р               | Power Supply             | V <sub>DD3.3</sub>                                    |      | 140                | 200               | mW                                                              |

| ۲               | Consumption              | V <sub>DD2.5</sub>                                    |      | 100                | 150               | mW                                                              |

| N               | Supply Noise Tolerance   | 50 Hz – 100 Hz<br>100 Hz – 10 MHz<br>10 MHz – 1.6 GHz |      | 100<br>40<br>10    |                   | $\begin{array}{c} mV_{P-P} \\ mV_{P-P} \\ mV_{P-P} \end{array}$ |

| LVTTL           | DC SPECIFICATIONS        |                                                       |      |                    | <del>.</del>      |                                                                 |

| V               | High Lovel Innet Voltage | V <sub>DD2.5</sub>                                    | 1.6  |                    | V <sub>DD2.</sub> | V                                                               |

| V <sub>IH</sub> | High Level Input Voltage | $V_{IL}$                                              | 2.0  |                    | V <sub>DD3.</sub> | V                                                               |

| V <sub>IL</sub> | Low Level Input Voltage  |                                                       | -0.3 |                    | 0.8               | V                                                               |

| 1/              | High Lovel Input Voltage | $I_{OH} = -3 \text{ mA}, V_{DD3.3}$                   | 2.4  |                    |                   | V                                                               |

| V <sub>OH</sub> | High Level Input Voltage | I <sub>IN</sub>                                       | 2.0  |                    |                   | V                                                               |

| $V_{OL}$        | Low Level Input Voltage  | I <sub>OL</sub> = 3 mA                                |      |                    | 0.4               | V                                                               |

<sup>(1)</sup> Typical values represent most likely parametric norms at V<sub>DD</sub> = 3.3V or 2.5V, T<sub>A</sub> = 25°C., and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

<sup>(2)</sup> The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

<sup>(3)</sup> Allowed supply noise (mV<sub>P-P</sub> sine wave) under typical conditions.

# **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless other specified. (1) (2)

|                                 | PARAMETER                                        | TEST CONDITIONS                                                                                 | MIN                    | TYP <sup>(1)</sup> | MAX                                   | UNIT              |

|---------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|--------------------|---------------------------------------|-------------------|

| POWER                           |                                                  |                                                                                                 |                        |                    |                                       |                   |

|                                 |                                                  | $V_{IN} = V_{DD}$                                                                               |                        | +1.8               | +15                                   | μΑ                |

| I <sub>IN</sub>                 | Input Current                                    | V <sub>IN</sub> = GND                                                                           | -15                    | 0                  |                                       | μA                |

|                                 | Input Leakage Current                            | V <sub>IN</sub> = GND, with internal pull-down resistors                                        |                        | +95                |                                       | μA                |

| I <sub>IN-P</sub>               | with Internal Pull-<br>Down/Up Resistors         | V <sub>IN</sub> = GND, with internal pull-up resistors                                          | -20                    |                    |                                       | μΑ                |

| CML REC                         | CEIVER INPUTS (IN+, IN-)                         |                                                                                                 |                        |                    |                                       |                   |

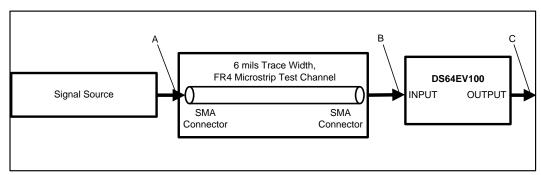

| V <sub>TX</sub>                 | Source Transmit Launch<br>Signal Level (IN diff) | AC-Coupled or DC-Coupled Requirement, Differential measurement at point A. Figure 1             | 400                    |                    | 1600                                  | mV <sub>P-F</sub> |

| V <sub>INTRE</sub>              | Input Threshold Voltage                          | Differential measurement at point B . Figure 1                                                  |                        | 120                |                                       | mV <sub>P-F</sub> |

| $V_{DDTX}$                      | Supply Voltage of<br>Transmitter to EQ           | DC-Coupled Requirement                                                                          | 1.6                    |                    | $V_{DD}$                              | V                 |

| V <sub>ICMDC</sub>              | Input Common-Mode<br>Voltage                     | DC-Coupled Requirement Differential measurement at point A. Figure 1 (4)                        | V <sub>DDTX</sub> -0.8 |                    | V <sub>DDT</sub><br><sub>X</sub> -0.2 | V                 |

| R <sub>LI</sub>                 | Differential Input Return Loss                   | 100 MHz – 3.2 GHz, with fixture's effect de-embedded                                            |                        | 10                 |                                       | dB                |

| R <sub>IN</sub>                 | Input Resistance                                 | Differential Across IN+ and IN Figure 4                                                         | 85                     | 100                | 115                                   | Ω                 |

| CML OUT                         | TPUTS (OUT+, OUT-)                               |                                                                                                 | <del>'</del>           |                    |                                       |                   |

| V <sub>OD</sub>                 | Output Differential<br>Voltage Level (OUT diff)  | Differential measurement with OUT+ and OUT-terminated by $50\Omega$ to GND, AC-Coupled Figure 2 | 550                    | 620                | 725                                   | mV <sub>P-F</sub> |

| V <sub>OCM</sub>                | Output Common-Mode<br>Voltage                    | Single-ended measurement DC-Coupled with $50\Omega$ terminations $^{(5)}$                       | V <sub>DD</sub> -0.2   |                    | V <sub>DD</sub> -<br>0.1              | V                 |

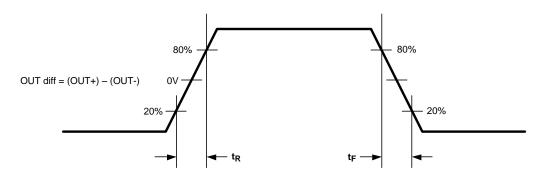

| t <sub>R</sub> , t <sub>F</sub> | Transition Time                                  | 20% to 80% of differential output voltage, measured within 1" from output pins.  Figure 2  (5)  | 20                     |                    | 60                                    | ps                |

| Ro                              | Output Resistance                                | Single-ended to V <sub>DD</sub>                                                                 | 42                     | 50                 | 58                                    | Ω                 |

| R <sub>LO</sub>                 | Differential Output<br>Return Loss               | 100 MHz – 1.6 GHz, with fixture's effect de-<br>embedded. IN+ = static high.                    |                        | 10                 |                                       | dB                |

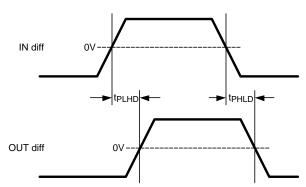

| t <sub>PLHD</sub>               | Differential Low to High Propagation Delay       | Propagation delay measurement at 50% V <sub>OD</sub> between input to output, 100 Mbps          |                        | 240                |                                       | ps                |

| t <sub>PHLD</sub>               | Differential High to Low<br>Propagation Delay    | Figure 3 <sup>(5)</sup>                                                                         |                        | 240                |                                       | ps                |

| EQUALIZ                         | ATION                                            |                                                                                                 |                        |                    |                                       |                   |

| DJ1                             | Residual Deterministic<br>Jitter at 10 Gbps      | 30" of 6 mil microstrip FR4, EQ Setting 0x06, PRBS-7 (2 <sup>7</sup> -1) pattern                |                        | 0.20               |                                       | UI <sub>P-F</sub> |

| DJ2                             | Residual Deterministic<br>Jitter at 6.4 Gbps     | 40" of 6 mil microstrip FR4, EQ Setting 0x06, PRBS-7 (2 <sup>7</sup> -1) pattern (6)(7)         |                        | 0.17               | 0.26                                  | UI <sub>P-P</sub> |

| DJ3                             | Residual Deterministic<br>Jitter at 5 Gbps       | 40" of 6 mil microstrip FR4, EQ Setting 0x07, PRBS-7 (2 <sup>7</sup> -1) pattern (6)(7)         |                        | 0.12               | 0.20                                  | UI <sub>P-P</sub> |

| DJ4                             | Residual Deterministic<br>Jitter at 2.5 Gbps     | 40" of 6 mil microstrip FR4, EQ Setting 0x07, PRBS-7 (2 <sup>7</sup> -1) pattern (6)(7)         |                        | 0.10               | 0.16                                  | UI <sub>P-P</sub> |

<sup>(4)</sup> Measured with clock-like {11111 00000} pattern.

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

Measured with clock-like {11111 00000} pattern.

Specification is guaranteed by characterization at optimal boost setting and is not tested in production.

Deterministic jitter is measured at the differential outputs (point C of Figure 1), minus the deterministic jitter before the test channel (point A of Figure 1). Random jitter is removed through the use of averaging or similar means.

# **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless other specified. (1) (2)

|       | PARAMETER     | TEST CONDITIONS | MIN | TYP <sup>(1)</sup> | MAX | UNIT              |

|-------|---------------|-----------------|-----|--------------------|-----|-------------------|

| POWER |               |                 |     |                    |     |                   |

| RJ    | Random Jitter | (5)(8)          |     | 0.5                |     | ps <sub>rms</sub> |

(8) Random jitter contributed by the equalizer is defined as sqrt (J<sub>OUT</sub><sup>2</sup> – J<sub>IN</sub><sup>2</sup>). J<sub>OUT</sub> is the random jitter at equalizer outputs in ps<sub>rms</sub>, see point C of Figure 1; J<sub>IN</sub> is the random jitter at the input of the equalizer in ps<sub>rms</sub>, see Figure 1.

### **TIMING DIAGRAMS**

Figure 2. Test Setup Diagram

Figure 3. CML Output Transition Times

Figure 4. Propagation Delay Timing Diagram

Copyright © 2006–2013, Texas Instruments Incorporated

### **TIMING DIAGRAMS (continued)**

Figure 5. Simplified Receiver Input Termination Circuit

#### **DS64EV100 APPLICATIONS INFORMATION**

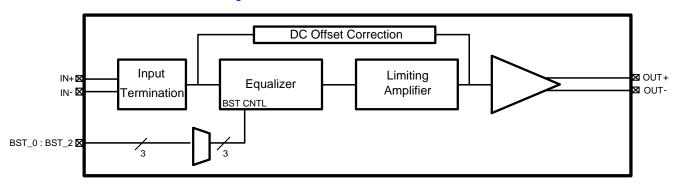

The DS64EV100 is a programmable equalizer optimized for operation up to 10 Gbps for backplane and cable applications. The equalizer channel consists of an equalizer stage, a limiting amplifier, a DC offset correction block, and a CML driver as shown in Figure 5.

Figure 6. Simplified Block Diagram

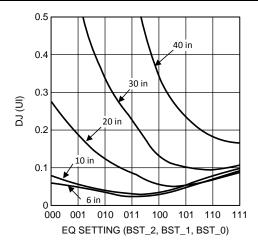

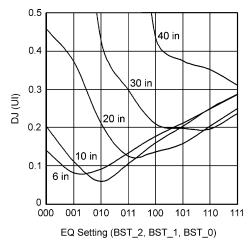

#### **EQUALIZER BOOST CONTROL**

The equalizer channel supports eight programmable levels of equalization boost, and is controlled by the Boost Set pins (BST\_[2:0]) in accordance with Table 2. The eight levels of boost settings enables the DS64EV100 to address a wide range of media loss and data rates.

Table 2. EQ Boost Control Table

| 6 mil Microstrip FR4<br>Trace Length (in) | 24 AWG Twin-AX Cable<br>Length (m) | Channel Loss at 3.2 GHz (db) | Channel Loss at 5 GHz (dB) | BST_N<br>[2, 1, 0] |

|-------------------------------------------|------------------------------------|------------------------------|----------------------------|--------------------|

| 0                                         | 0                                  | 0                            | 0                          | 0 0 0              |

| 5                                         | 2                                  | 5                            | 6                          | 0 0 1              |

| 10                                        | 3                                  | 7.5                          | 10                         | 010                |

| 15                                        | 4                                  | 10                           | 14                         | 011                |

| 20                                        | 5                                  | 12.5                         | 18                         | 1 0 0 (Default)    |

| 25                                        | 6                                  | 15                           | 21                         | 1 0 1              |

| 30                                        | 7                                  | 17                           | 24                         | 110                |

| 40                                        | 10                                 | 22                           | 30                         | 111                |

# **GENERAL RECOMMENDATIONS**

The DS64EV100 is a high performance circuit capable of delivering excellent performance. Careful attention must be paid to the details associated with high-speed design as well as providing a clean power supply. Refer to the LVDS Owner's Manual for more detailed information on high-speed design tips to address signal integrity design issues.

#### PCB LAYOUT CONSIDERATIONS FOR DIFFERENTIAL PAIRS

The CML inputs and outputs must have a controlled differential impedance of  $100\Omega$ . It is preferable to route CML lines exclusively on one layer of the board, particularly for the input traces. The use of vias should be avoided if possible. If vias must be used, they should be used sparingly and must be placed symmetrically for each side of a given differential pair. Route the CML signals away from other signals and noise sources on the printed circuit board. See AN-1187 for additional information on WSON packages.

#### **POWER SUPPLY BYPASSING**

Two approaches are recommended to ensure that the DS64EV100 is provided with an adequate power supply. First, the supply ( $V_{DD}$ ) and ground (GND) pins should be connected to power planes routed on adjacent layers of the printed circuit board. The layer thickness of the dielectric should be minimized so that the  $V_{DD}$  and GND planes create a low inductance supply with distributed capacitance. Second, careful attention to supply bypassing through the proper use of bypass capacitors is required. A  $0.01\mu F$  bypass capacitor should be connected to each  $V_{DD}$  pin such that the capacitor is placed as close as possible to the DS64EV100. Smaller body size capacitors can help facilitate proper component placement. Additionally, three capacitors with capacitance in the range of  $2.2~\mu F$  to  $10~\mu F$  should be incorporated in the power supply bypassing design as well. These capacitors can be either tantalum or an ultra-low ESR ceramic and should be placed as close as possible to the DS64EV100.

#### DC COUPLING

The DS64EV100 supports both AC coupling with external ac coupling capacitor, and DC coupling to its upstream driver, or downstream receiver. With DC coupling, users must ensure the input signal common mode is within the range of the electrical specification  $V_{ICMDC}$  and the device output is terminated with 50  $\Omega$  to  $V_{DD}$ .

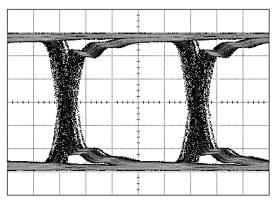

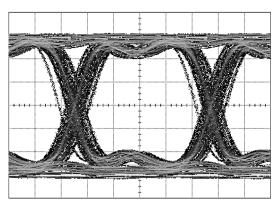

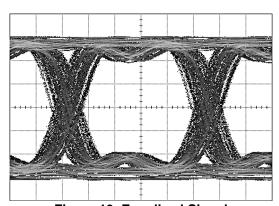

### TYPICAL PERFORMANCE EYE DIAGRAMS AND CURVES

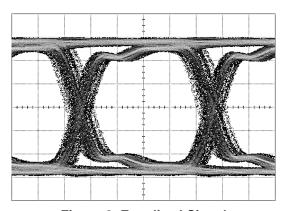

Figure 7. Equalized Signal (40 in FR4, 2.5 Gbps, PRBS7, 0x07 Setting)

Figure 8. Equalized Signal (40 in FR4, 5 Gbps, PRBS7, 0x07 Setting)

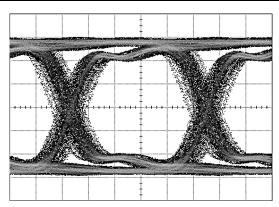

Figure 9. Equalized Signal (40 in FR4, 6.4 Gbps, PRBS7, 0x06 Setting)

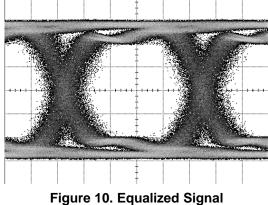

Figure 10. Equalized Signal (40 in FR4, 6.4 Gbps, PRBS31, 0x06 Setting)

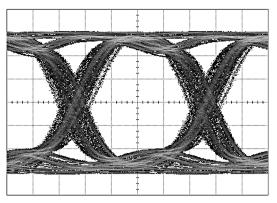

Figure 11. Equalized Signal (30 in FR4, 10 Gbps, PRBS7, 0x06 Setting)

Figure 12. Equalized Signal (10m 24 AWG Twin-AX Cable, 6.4 Gbps, PRBS7, 0x06 Setting)

Figure 13. Equalized Signal (32 in Tyco XAUI Backplane, 6.25 Gbps, PRBS7, 0x06 Setting)

Figure 14. DJ vs. EQ Setting (6.4 Gbps)

Figure 15. DJ vs. EQ Setting (10 Gbps)

# SNLS232E - OCTOBER 2006-REVISED FEBRUARY 2013

# **REVISION HISTORY**

| Cr | nanges from Revision D (February 2013) to Revision E | Page |

|----|------------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format   | 9    |

# PACKAGE OPTION ADDENDUM

20-Feb-2013

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device  | Status | Package Type | Package<br>Drawing |    | Package Qty | Eco Plan                   | Lead/Ball Finish |                    | Op Temp (°C) |         | Samples |

|-------------------|--------|--------------|--------------------|----|-------------|----------------------------|------------------|--------------------|--------------|---------|---------|

|                   | (1)    |              | Diawing            |    |             | (2)                        |                  | (3)                |              | (4)     |         |

| DS64EV100SD/NOPB  | ACTIVE | WSON         | NHK                | 14 | 1000        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | D64E1SD | Samples |

| DS64EV100SDX/NOPB | ACTIVE | WSON         | NHK                | 14 | 4500        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 85    | D64E1SD | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Mar-2013

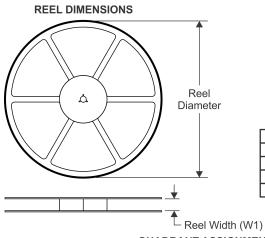

# TAPE AND REEL INFORMATION

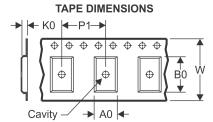

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

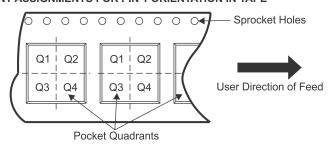

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS64EV100SD/NOPB  | WSON            | NHK                | 14 | 1000 | 178.0                    | 12.4                     | 3.3        | 4.3        | 1.0        | 8.0        | 12.0      | Q1               |

| DS64EV100SDX/NOPB | WSON            | NHK                | 14 | 4500 | 330.0                    | 12.4                     | 3.3        | 4.3        | 1.0        | 8.0        | 12.0      | Q1               |

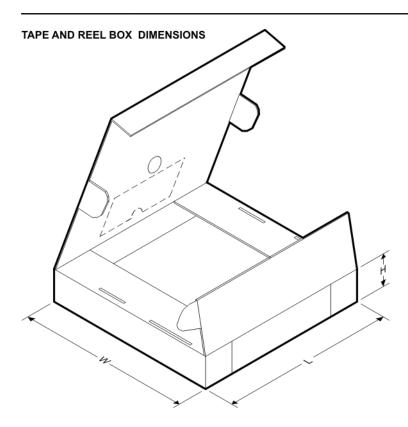

www.ti.com 21-Mar-2013

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS64EV100SD/NOPB  | WSON         | NHK             | 14   | 1000 | 210.0       | 185.0      | 35.0        |

| DS64EV100SDX/NOPB | WSON         | NHK             | 14   | 4500 | 367.0       | 367.0      | 35.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331