# BTM7752G

High Current H-Bridge Trilith IC 3G

**Automotive Power**

# **Table of Contents**

|                                                                                                                                                             | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 2                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 1                                                                                                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 3                                                                         |

| 2                                                                                                                                                           | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 4                                                                         |

| 3                                                                                                                                                           | Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 4                                                                         |

| <b>4</b><br>4.1<br>4.2                                                                                                                                      | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 5                                                                         |

| <b>5</b> 5.1 5.2 5.3                                                                                                                                        | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6<br>. 7                                                                  |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5 | Block Description and Characteristics  Supply Characteristics  Power Stages  Power Stages - Static Characteristics  Switching Times  Power Stages - Dynamic Characteristics  Protection Functions  Overvoltage Lock Out  Undervoltage Shut Down  Overtemperature Protection  Current Limitation  Short Circuit Protection  Electrical Characteristics - Protection Functions  Control and Diagnostics  Input Circuit  Dead Time Generation  Status Flag Diagnosis with Current Sense Capability  Truth Table  Electrical Characteristics - Control and Diagnostics | . 9<br>10<br>11<br>12<br>13<br>13<br>14<br>14<br>16<br>16<br>17<br>17<br>17 |

| <b>7</b><br>7.1                                                                                                                                             | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                          |

| 8                                                                                                                                                           | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

| 9                                                                                                                                                           | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

| J                                                                                                                                                           | - NGVIGIOH HIGGOLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                           |

# High Current H-Bridge Trilith IC 3G

BTM7752G

### 1 Overview

#### **Features**

- Integrated high current H-Bridge

- Path resistance of max. 295 m $\Omega$  @ 150 °C (typ. 150 m $\Omega$  @ 25 °C)

- Low quiescent current of typ. 5μA @ 25 °C

- PWM capability of up to 25kHz combined with active freewheeling

- Current limitation level of 12 A typ. (8 A min.)

- · Driver circuit with logic inputs

- Status flag diagnosis with current sense capability

- Overtemperature shut down with latch behaviour

- · Overvoltage lock out

- Undervoltage shut down

- Switch-mode current limitation for reduced power dissipation in overcurrent situation

- Integrated dead time generation

- · Operation up to 28V

- Green Product (RoHS compliant)

- AEC Qualified

The BTM7752G provides an optimized solution for protected high current PWM motor drives with very low board space consumption.

PG-DSO-36-29

| <del></del> | DI           | 84       |

|-------------|--------------|----------|

| Туре        | Package      | Marking  |

| BTM7752G    | PG-DSO-36-29 | BTM7752G |

Data Sheet 3 Rev. 2.0, 2010-05-28

**Block Diagram**

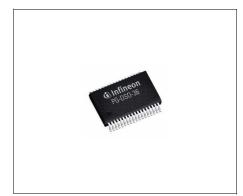

# 2 Block Diagram

Figure 1 Block Diagram

# 3 Terms

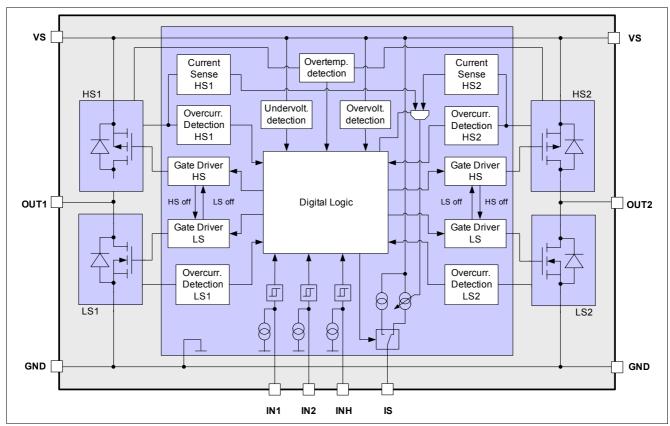

following figure shows the terms used in this data sheet.

Figure 2 Terms

Data Sheet 4 Rev. 2.0, 2010-05-28

**Pin Configuration**

# 4 Pin Configuration

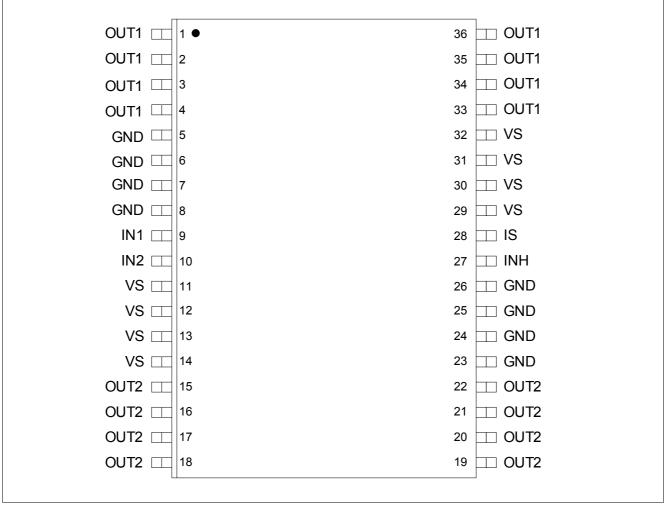

# 4.1 Pin Assignment

Figure 3 Pin Configuration BTM7752G

# 4.2 Pin Definitions and Functions

Pins written in bold type need power wiring.

| Pin        | Symbol | Function                                                |

|------------|--------|---------------------------------------------------------|

| 14, 3336   | OUT1   | Output of first half bridge                             |

| 58, 2326   | GND    | Ground                                                  |

| 9          | IN1    | Input of first half bridge                              |

| 10         | IN2    | Input of second half bridge                             |

| 1114, 2932 | VS     | Supply, all pins to be connected and shorted externally |

| 1522       | OUT2   | Output of second half bridge                            |

| 27         | INH    | Inhibit pin, to set device in sleep/stand-by mode       |

| 28         | IS     | Current sense and error signal                          |

Data Sheet 5 Rev. 2.0, 2010-05-28

**General Product Characteristics**

# 5 General Product Characteristics

# 5.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_i$  = -40 °C to +150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                                | Symbol                                                  | Lin      | nit Values | Unit     | Conditions                       |  |

|--------|------------------------------------------|---------------------------------------------------------|----------|------------|----------|----------------------------------|--|

|        |                                          |                                                         | Min.     | Max.       |          |                                  |  |

| 5.1.1  | Supply voltage                           | $V_{S}$                                                 | -0.3     | 45         | V        | _                                |  |

| 5.1.2  | Logic Input Voltage                      | $V_{\mathrm{IN1},}V_{\mathrm{IN2,}} \ V_{\mathrm{INH}}$ | -0.3     | 5.5        | V        | -                                |  |

| 5.1.3  | HS/LS continuous drain current           | $I_{\rm D(HS)} \\ I_{\rm D(LS)}$                        | -4       | 4          | Α        | $T_{\rm C}$ < 85°C switch active |  |

| 5.1.4  | Voltage between VS and IS pin            | $V_{\rm S}$ - $V_{\rm IS}$                              | -0.3     | 45         | V        | _                                |  |

| Therma | I Maximum Ratings                        | •                                                       |          |            | <u>'</u> | •                                |  |

| 5.1.5  | Junction temperature                     | $T_{\rm j}$                                             | -40      | 150        | °C       | _                                |  |

| 5.1.6  | Storage temperature                      | $T_{ m stg}$                                            | -55      | 150        | °C       | _                                |  |

| ESD Su | sceptibility                             | <u> </u>                                                | -1       | <u>'</u>   |          | -1                               |  |

| 5.1.7  | ESD susceptibility                       | $V_{ESD}$                                               |          |            | kV       | HBM <sup>2)</sup>                |  |

|        | IN1, IN2, IS, INH<br>OUT1, OUT2, GND, VS |                                                         | -2<br>-4 | 2 4        |          |                                  |  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Data Sheet 6 Rev. 2.0, 2010-05-28

<sup>2)</sup> HBM according to EIA/JESD 22-A 114B (1.5 k $\Omega$ , 100pF)

**General Product Characteristics**

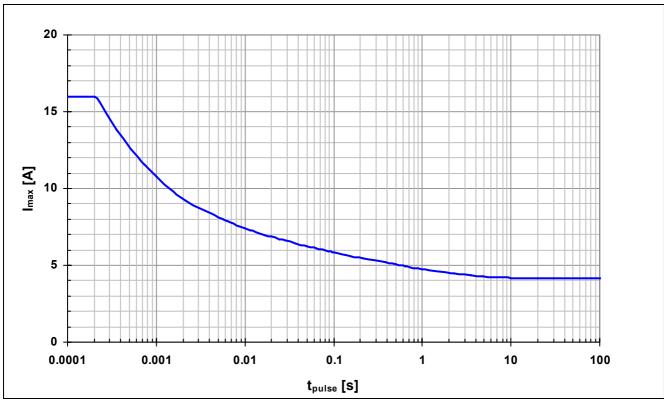

### **Maximum Single Pulse Current**

Figure 4 BTM7752G Maximum Single Pulse Current ( $T_{\rm C} = T_{\rm j(0)} < 85^{\circ}{\rm C}$ )

This diagram shows the maximum single pulse current that can be driven for a given pulse time  $t_{\rm pulse}$ . The maximum reachable current may be smaller depending on the current limitation level. Pulse time may be limited due to thermal protection of the device.

#### 5.2 Functional Range

| Pos.  | Parameter                                   | Symbol              | Liı  | mit Values | Unit | Conditions                                            |  |

|-------|---------------------------------------------|---------------------|------|------------|------|-------------------------------------------------------|--|

|       |                                             |                     | Min. | Max.       |      |                                                       |  |

| 5.2.1 | Supply Voltage Range for Normal Operation   | $V_{S(nor)}$        | 8    | 18         | V    | VS pins shorted                                       |  |

| 5.2.2 | Extended Supply Voltage Range for Operation | V <sub>S(ext)</sub> | 5.5  | 28         | V    | VS pins shorted;<br>Parameter<br>deviations possible; |  |

| 5.2.3 | Junction Temperature                        | $T_{j}$             | -40  | 150        | °C   | _                                                     |  |

<sup>1)</sup> Overtemperature protection available up to supply voltage  $V_{\rm S}$  = 18V.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

Data Sheet 7 Rev. 2.0, 2010-05-28

**General Product Characteristics**

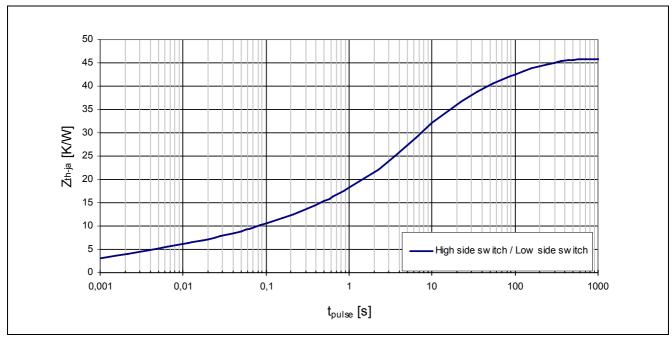

#### 5.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                                                                                                                                                                         | Symbol                   | L    | imit Val | ues  | Unit | Conditions |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|----------|------|------|------------|

|       |                                                                                                                                                                                   |                          | Min. | Тур.     | Max. |      |            |

| 5.3.1 | Thermal Resistance<br>Junction to Soldering Point, Low Side Switch<br>$R_{\text{thjSP(LS)}} = \Delta T_{\text{j(LS)}} / P_{\text{v(LS)}}$                                         | $R_{thjSP(LS)}$          | _    | -        | 29   | K/W  | 1)         |

| 5.3.2 | Thermal Resistance Junction to Soldering Point, High Side Switch $R_{\text{thjSP(HS)}} = \Delta T_{\text{j(HS)}} / P_{\text{v(HS)}}$                                              | $R_{\mathrm{thjSP(HS)}}$ | _    | -        | 29   | K/W  | 1)         |

| 5.3.3 | Thermal Resistance Junction to Soldering Point, both switches $R_{\text{thjSP}} = \max[\Delta T_{\text{j(HS)}}, \Delta T_{\text{j(LS)}}] / (P_{\text{v(HS)}} + P_{\text{v(LS)}})$ | $R_{thjSP}$              | _    | _        | 29   | K/W  | 1)         |

| 5.3.4 | Thermal Resistance Junction-Ambient                                                                                                                                               | $R_{thja}$               | _    | 46       | -    | K/W  | 1), 2)     |

<sup>1)</sup> Not subject to production test, specified by design.

# Transient thermal impedance $Z_{ m thia}$

**Figure 5** is showing the typical transient thermal impedance of high side or low side switch of BTM7752G mounted according to JEDEC JESD51-7 at natural convection on FR4 2s2p board. The device (chip+package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x  $70\mu$ m Cu, 2 x  $35\mu$ m Cu). For the simulation each chip was separately powered with 1W at an ambient temperature  $T_a$  of 85°C.

Figure 5 Typical transient thermal impedance of BTM7752G on JESD51-7 2s2p board (1W each chip (separately heated),  $T_a$  = 85°C, single pulse)

Data Sheet 8 Rev. 2.0, 2010-05-28

<sup>2)</sup> Specified  $R_{\text{thja}}$  value is according to Jedec JESD51-2, -7 at natural convection on FR4 2s2p board; The product (chip+package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu).

# 6 Block Description and Characteristics

# 6.1 Supply Characteristics

$V_{\rm S}$  = 8 V to 18 V,  $T_{\rm j}$  = -40 °C to +150 °C,  $I_{\rm L}$  = 0A, VS pins shorted, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter         | Symbol       | Limit ' | Values |                | Unit | <b>Test Conditions</b>                                                                                          |

|--------|-------------------|--------------|---------|--------|----------------|------|-----------------------------------------------------------------------------------------------------------------|

|        |                   |              | Min.    | Тур.   | Max.           |      |                                                                                                                 |

| Genera | al                | -            |         | -      | <del>-  </del> | -    |                                                                                                                 |

| 6.1.1  | Supply Current    | $I_{S(on)}$  | _       | 5      | 9.5            | mA   | $V_{\text{INH}}$ or $V_{\text{IN1}}$ or $V_{\text{IN2}}$ = 5 V DC-mode normal operation (no fault condition)    |

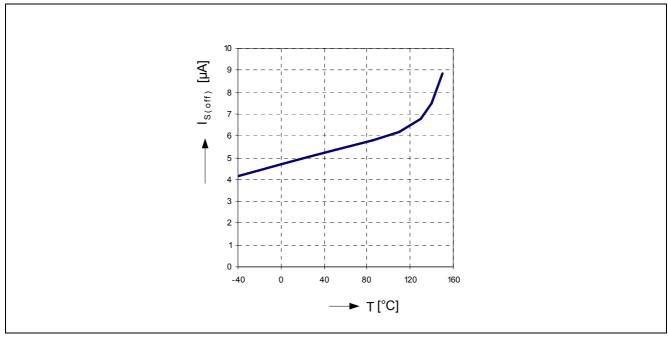

| 6.1.2  | Quiescent Current | $I_{S(off)}$ | -       | 5      | 15             | μΑ   | $V_{\text{INH}} = V_{\text{IN1}} = V_{\text{IN2}} = 0 \text{ V}$<br>$T_{\text{j}} < 85 ^{\circ}\text{C}; ^{1)}$ |

|        |                   |              | _       | _      | 30             | μΑ   | $V_{INH} = V_{IN1} = V_{IN2} = 0 \; V$                                                                          |

<sup>1)</sup> Not subject to production test, specified by design.

Figure 6 Typical Quiescent Current vs. Junction Temperature (typ. @  $V_S$  = 13.5V)

Data Sheet 9 Rev. 2.0, 2010-05-28

# 6.2 Power Stages

The power stages of the BTM7752G consist of p-channel vertical DMOS transistors for the high side switches and n-channel vertical DMOS transistors for the low side switches. All protection and diagnostic functions are located in a separate control chip. Both switches, high side and low side, allow active freewheeling and thus minimize power dissipation in the forward operation of the integrated diodes.

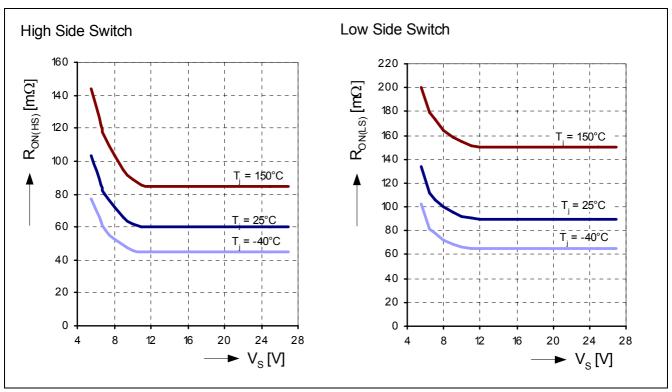

The on state resistance  $R_{\text{ON}}$  is dependent on the supply voltage  $V_{\text{S}}$  as well as on the junction temperature  $T_{\text{j}}$ . The typical on state resistance characteristics are shown in **Figure 7**.

Figure 7 Typical On State Resistance vs. Supply Voltage

# 6.2.1 Power Stages - Static Characteristics

$V_{\rm S}$  = 8 V to 18 V,  $T_{\rm j}$  = -40 °C to +150 °C, VS pins shorted, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                       | Symbol                | Limit ' | Values |      | Unit      | Test Conditions                                                  |

|--------|---------------------------------|-----------------------|---------|--------|------|-----------|------------------------------------------------------------------|

|        |                                 |                       | Min.    | Тур.   | Max. |           |                                                                  |

| High S | ide Switch - Static Characteris | stics                 |         |        |      |           |                                                                  |

| 6.2.1  | On state high side resistance   | $R_{ON(HS)}$          |         |        |      | mΩ        | I <sub>OUT</sub> = 1 A                                           |

|        |                                 |                       |         |        |      |           | $V_{\rm S}$ = 13.5 V                                             |

|        |                                 |                       | _       | 60     | _    |           | $T_{\rm i}$ = 25 °C; 1)                                          |

|        |                                 |                       | _       | 85     | 115  |           | $T_{\rm j}$ = 150 °C                                             |

| 6.2.2  | Leakage current high side       | $I_{L(LKHS)}$         |         |        |      | μA        | $V_{\text{INH}} = V_{\text{IN1}} = V_{\text{IN2}} = 0 \text{ V}$ |

|        |                                 | _(=:::::)             |         |        |      |           | $V_{\text{OUT}} = 0 \text{ V}$                                   |

|        |                                 |                       | _       | _      | 1    |           | $T_{\rm i}$ < 85 °C; 1)                                          |

|        |                                 |                       | _       | _      | 5    |           | T <sub>i</sub> = 150 °C                                          |

| 6.2.3  | Reverse diode                   | $V_{DS(HS)}$          |         |        |      | V         | I <sub>OUT</sub> = -1 A                                          |

|        | forward-voltage high side 2)    | 20(110)               | _       | 0.9    | _    |           | $T_{\rm i}$ = -40 °C; <sup>1)</sup>                              |

|        |                                 |                       | _       | 0.8    | _    |           | $T_{i} = 25  ^{\circ}\text{C}; ^{1)}$                            |

|        |                                 |                       | _       | 0.6    | 0.8  |           | T <sub>i</sub> = 150 °C                                          |

| Low Si | ide Switch - Static Characteris | tics                  | +       | +      | +    | -         |                                                                  |

| 6.2.4  | On state low side resistance    | $R_{ON(LS)}$          |         |        |      | $m\Omega$ | I <sub>OUT</sub> = -1 A                                          |

|        |                                 | ()                    |         |        |      |           | V <sub>S</sub> = 13.5 V                                          |

|        |                                 |                       | _       | 90     | _    |           | $T_{\rm i}$ = 25 °C; 1)                                          |

|        |                                 |                       | _       | 150    | 180  |           | T <sub>i</sub> = 150 °C                                          |

| 6.2.5  | Leakage current low side        | -I <sub>L(LKLS)</sub> |         |        |      | μA        | $V_{\rm INH} = V_{\rm IN1} = V_{\rm IN2} = 0 \text{ V}$          |

|        |                                 | _(=::==;              |         |        |      |           | $V_{\text{OUT}} = V_{\text{S}}$                                  |

|        |                                 |                       | _       | _      | 1    |           | $T_{\rm i}$ < 85 °C; <sup>1)</sup>                               |

|        |                                 |                       | _       | _      | 3    |           | T <sub>i</sub> = 150 °C                                          |

| 6.2.6  | Reverse diode                   | $V_{\rm SD(LS)}$      |         |        |      | V         | I <sub>OUT</sub> = 1 A                                           |

|        | forward-voltage low side 2)     | OD(LO)                | _       | 0.9    | _    |           | $T_i = -40  ^{\circ}\text{C};  ^{1)}$                            |

|        | Ŭ                               |                       | _       | 0.8    | _    |           | $T_{i} = 25  ^{\circ}\text{C};^{1)}$                             |

|        |                                 |                       | _       | 0.6    | 8.0  |           | $T_{i} = 150  ^{\circ}\text{C}$                                  |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 11 Rev. 2.0, 2010-05-28

<sup>2)</sup> Due to active freewheeling diode is conducting only for a few  $\mu$ s.

# 6.2.2 Switching Times

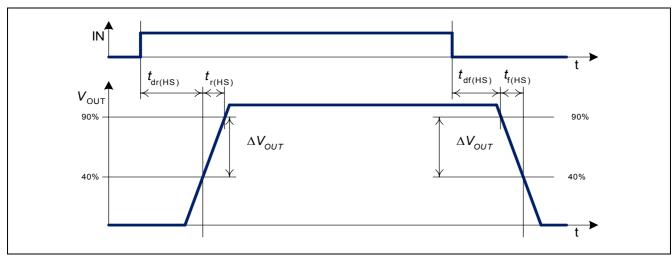

Figure 8 Definition of switching times high side (R<sub>load</sub> to GND)

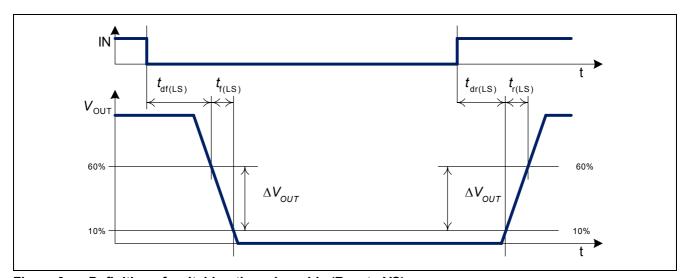

Figure 9 Definition of switching times low side (R<sub>load</sub> to VS)

Due to the timing differences for the rising and the falling edge there will be a slight difference between the length of the input pulse and the length of the output pulse. It can be calculated using the following formulas:

- $\Delta t_{HS} = (t_{dr(HS)} + 0.2 t_{r(HS)}) (t_{df(HS)} + 0.8 t_{f(HS)})$

- $\Delta t_{LS} = (t_{df(LS)} + 0.2 t_{f(LS)}) (t_{dr(LS)} + 0.8 t_{r(LS)}).$

Data Sheet 12 Rev. 2.0, 2010-05-28

# 6.2.3 Power Stages - Dynamic Characteristics

$V_{\rm S}$  = 13.5V,  $T_{\rm j}$  = -40 °C to +150 °C,  $R_{\rm Load}$  = 12  $\Omega$ ,  $V_{\rm INH}$  = 5V, VS pins shorted, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                 | Symbol                               | Limit Values |      |      | Unit | <b>Test Conditions</b> |  |

|--------|---------------------------|--------------------------------------|--------------|------|------|------|------------------------|--|

|        |                           |                                      | Min.         | Тур. | Max. |      |                        |  |

| High S | ide Switch Dynamic Charac | teristics                            |              |      |      |      |                        |  |

| 6.2.7  | Rise-time of HS           | $t_{r(HS)}$                          | 0.35         | 0.7  | 1.05 | μs   | _                      |  |

| 6.2.8  | Slew rate HS on           | $\Delta V_{ m OUT}/$ $t_{ m r(HS)}$  | _            | 9.6  | _    | V/µs | _                      |  |

| 6.2.9  | Switch on delay time HS   | $t_{dr(HS)}$                         | 3            | 5    | 8    | μs   | _                      |  |

| 6.2.10 | Fall-time of HS           | $t_{f(HS)}$                          | 0.35         | 0.7  | 1.05 | μs   | _                      |  |

| 6.2.11 | Slew rate HS off          | $-\Delta V_{ m OUT}/$ $t_{ m f(HS)}$ | -            | 9.6  | -    | V/µs | _                      |  |

| 6.2.12 | Switch off delay time HS  | t <sub>df(HS)</sub>                  | 1.5          | 3.5  | 5.5  | μs   | _                      |  |

| Low Si | de Switch Dynamic Charac  | teristics                            |              |      |      |      |                        |  |

| 6.2.13 | Rise-time of LS           | $t_{r(LS)}$                          | 0.4          | 8.0  | 1.2  | μs   | _                      |  |

| 6.2.14 | Slew rate LS off          | $\Delta V_{OUT} / t_{r(LS)}$         | _            | 8.4  |      | V/µs |                        |  |

| 6.2.15 | Switch off delay time LS  | $t_{dr(LS)}$                         | 1.5          | 3.5  | 5.5  | μs   | _                      |  |

| 6.2.16 | Fall-time of LS           | $t_{f(LS)}$                          | 0.35         | 0.8  | 1.2  | μs   | _                      |  |

| 6.2.17 | Slew rate LS on           | $-\Delta V_{OUT}/$ $t_{f(LS)}$       | _            | 8.4  | _    | V/µs | _                      |  |

| 6.2.18 | Switch on delay time LS   | $t_{\rm df(LS)}$                     | 2.5          | 5    | 7.5  | μs   | _                      |  |

#### 6.3 Protection Functions

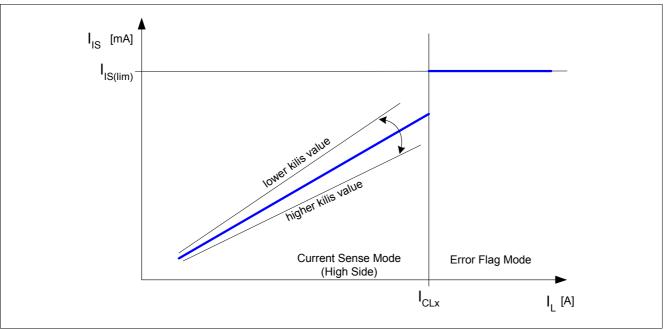

The device provides integrated protection functions. These are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not to be used for continuous or repetitive operation, with the exception of the current limitation (Chapter 6.3.4). Overvoltage, overtemperature and overcurrent are indicated by a fault current I<sub>IS(LIM)</sub> at the IS pin as described in the paragraph "Status Flag Diagnosis with Current Sense Capability" on Page 17 and Figure 13.

In the following the protection functions are listed in order of their priority. Overvoltage lock out overrides all other error modes.

# 6.3.1 Overvoltage Lock Out

To assure a high immunity against overvoltages (e.g. load dump conditions) the device shuts both lowside MOSFETs off and turns both highside MOSFET on, if the supply voltage  $V_{\rm S}$  is exceeding the over voltage protection level  $V_{\rm OV(OFF)}$ . The IC operates in normal mode again with a hysteresis  $V_{\rm OV(HY)}$  if the supply voltage decreases below the switch-on voltage  $V_{\rm OV(ON)}$ . This behavior of the BTM7752G will lead to freewheeling in highside during over voltage.

Data Sheet 13 Rev. 2.0, 2010-05-28

# 6.3.2 Undervoltage Shut Down

To avoid uncontrolled motion of the driven motor at low voltages the device shuts off (both outputs are tri-state), if the supply voltage  $V_{\rm S}$  drops below the switch-off voltage  $V_{\rm UV(OFF)}$ . In this case all latches will be reset. The IC becomes active again with a hysteresis  $V_{\rm UV(HY)}$  if the supply voltage rises above the switch-on voltage  $V_{\rm UV(ON)}$ .

#### 6.3.3 Overtemperature Protection

The BTM7752G is protected against overtemperature by integrated temperature sensors. Each half bridge, which consists of one high side and one low side switch, is protected by one temperature sensor located in the high side switch. Both temperature sensors function independently. A detection of overtemperature through temperature sensor leads to a shut down of both switches in the half bridge. This state is latched until the device is reset by a low signal with a minimum length of  $t_{\text{reset}}$  simultaneously at the INH pin and both IN pins, provided that its temperature has decreased at least the thermal hysteresis  $\Delta T$  in the meantime.

Overtemperature protection is available up to supply voltage  $V_{\rm S}$  = 18V.

For sufficient over temperature protection please consider also operation below the limitations outlined in **Figure 4** and **Figure 5**.

Repetitive use of the overtemperature protection might reduce lifetime.

#### 6.3.4 Current Limitation

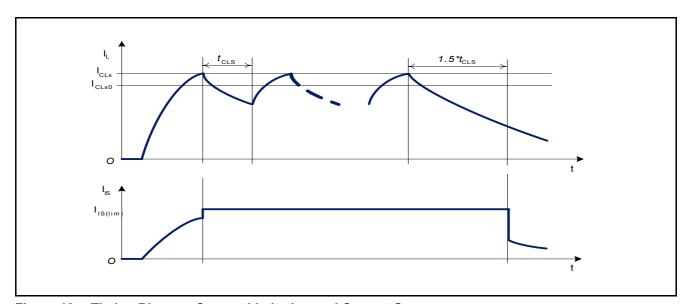

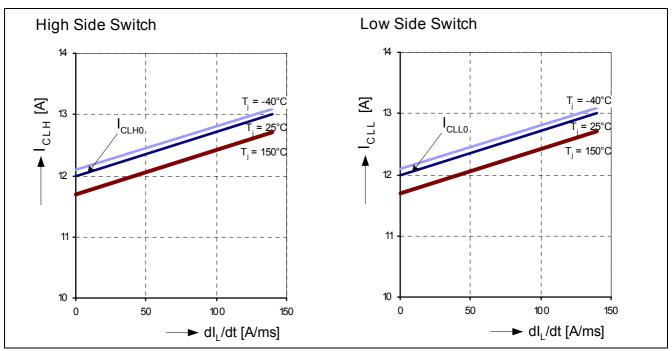

The current in the bridge is measured in all four switches. As soon as the current in forward direction in one switch is reaching the limit  $I_{\rm CLx}$ , this switch is deactivated for  $t_{\rm CLS}$ . In case of INH = 5V (high) the other switch of the same half bridge is activated for the same time ( $t_{\rm CLS}$ ). During that time all changes at the related IN pin are ignored. However, the INH pin can still be used to switch all MOSFETs off. After  $t_{\rm CLS}$  the switches return to their initial setting. The error signal at the IS pin is reset after 1.5 \*  $t_{\rm CLS}$  if no overcurrent state is detected in the meantime. Unintentional triggering of the current limitation by short current spikes (e.g. inflicted by EMI coming from the motor) is suppressed by internal filter circuitry. Due to thresholds and reaction delay times of the filter circuitry the effective current limitation level  $I_{\rm CLx}$  depends on the slew rate of the load current di/dt as shown in **Figure 11**.

Figure 10 Timing Diagram Current Limitation and Current Sense

Data Sheet 14 Rev. 2.0, 2010-05-28

Figure 11 Current Limitation Level vs. Current Slew Rate  $dI_1/dt$

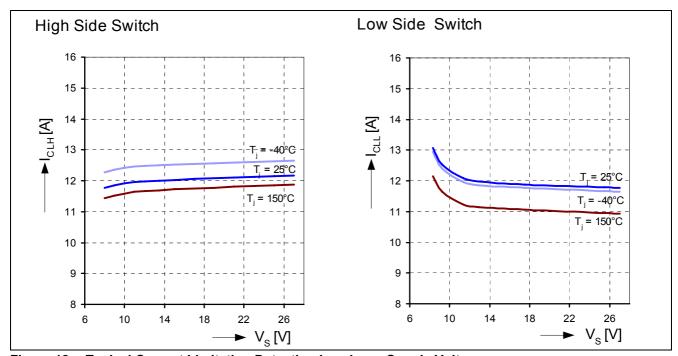

Figure 12 Typical Current Limitation Detection Levels vs. Supply Voltage

In combination with a typical inductive load, such as a motor, this results in a switched mode current limitation. This method of limiting the current has the advantage that the power dissipation in the BTM7752G is much smaller than by driving the MOSFETs in linear mode. Therefore it is possible to use the current limitation for a short time without exceeding the maximum allowed junction temperature (e.g. for limiting the inrush current during motor start up). However, the regular use of the current limitation is allowed as long as the specified maximum junction temperature is not exceeded. Exceeding this temperature can reduce the lifetime of the device.

Data Sheet 15 Rev. 2.0, 2010-05-28

#### 6.3.5 Short Circuit Protection

The device provides embedded protection functions against

- · output short circuit to ground

- · output short circuit to supply voltage

- short circuit of load

The short circuit protection is realized by the previously described current limitation in combination with the over-temperature shut down (see **Chapter 6.3.3**) of the device.

# 6.3.6 Electrical Characteristics - Protection Functions

$V_{\rm S}$  = 8 V to 18 V,  $T_{\rm j}$  = -40 °C to +150 °C, VS pins shorted, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                            | Symbol             | Limit '   | Limit Values |      |          | <b>Test Conditions</b>                   |  |

|---------|------------------------------------------------------|--------------------|-----------|--------------|------|----------|------------------------------------------|--|

|         |                                                      |                    | Min. Typ. |              | Max. |          |                                          |  |

| Over Vo | oltage Lock Out                                      | I                  |           | 1            | 1    | <u> </u> |                                          |  |

| 6.3.1   | Switch-ON voltage                                    | $V_{OV(ON)}$       | 27.8      | _            | _    | V        | $V_{\rm s}$ decreasing                   |  |

| 6.3.2   | Switch-OFF voltage                                   | $V_{OV(OFF)}$      | 28        | _            | 30   | V        | $V_{\rm s}$ increasing                   |  |

| 6.3.3   | ON/OFF hysteresis                                    | $V_{OV(HY)}$       | _         | 0.2          | _    | V        | 1)                                       |  |

| Under \ | oltage Shut Down                                     |                    |           |              |      |          |                                          |  |

| 6.3.4   | Switch-ON voltage                                    | $V_{UV(ON)}$       | -         | _            | 5.5  | V        | $V_{\rm S}$ increasing                   |  |

| 6.3.5   | Switch-OFF voltage                                   | $V_{\sf UV(OFF)}$  | 4.0       | _            | 5.4  | V        | $V_{\rm S}$ decreasing                   |  |

| 6.3.6   | ON/OFF hysteresis                                    | $V_{UV(HY)}$       | _         | 0.2          | _    | V        | 1)                                       |  |

| Therma  | I Shut Down                                          |                    |           |              |      |          |                                          |  |

| 6.3.7   | Thermal shut down junction temperature               | $T_{jSD}$          | 155       | 175          | 200  | °C       | 1); $V_{\rm S} \le 18 \text{ V}$         |  |

| 6.3.8   | Thermal switch on junction temperature               | $T_{\rm jSO}$      | 153       | _            | 190  | °C       | 1)                                       |  |

| 6.3.9   | Thermal hysteresis                                   | $\Delta T$         | _         | 7            | _    | °C       | 1)                                       |  |

| 6.3.10  | Reset pulse at INH and IN pin (INH, IN1 and IN2 low) | t <sub>reset</sub> | 8         | _            | _    | μs       | 1)                                       |  |

| Current | t Limitation                                         |                    | *         |              |      | -        |                                          |  |

| 6.3.11  | Current limitation detection level high side         | $I_{CLH0}$         | 8         | 12           | 16   | A        | V <sub>S</sub> = 13.5 V                  |  |

| 6.3.12  | Current limitation detection level low side          | $I_{CLL0}$         | 8         | 12           | 16   | A        | V <sub>S</sub> = 13.5 V                  |  |

| 6.3.13  | Shut off time for HS and LS                          | $t_{CLS}$          | 50        | 100          | 200  | μs       | $V_{\rm S}$ = 13.5 V, $T_{\rm i}$ = 25 ° |  |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 16 Rev. 2.0, 2010-05-28

### 6.4 Control and Diagnostics

### 6.4.1 Input Circuit

The control inputs INx and INH consist of TTL/CMOS compatible schmitt triggers with hysteresis which control the integrated gate drivers for the MOSFETs. To set the device in stand-by mode, INH and INx pins need to be all connected to GND. When the INH is high, in each half bridge one of the two power switches (HSx or LSx) is switched on, while the other power switch is switched off, depending on the status of the INx pin. When INH is low, a high INx signal will turn the corresponding highside switches on. This provides customer the possibility to switch on one high side switch while keeping the other switches off and therefore to do an open load detection together with external circuitry (see also **Chapter 7** - Application Information). A low on all INx and INH signal will turn off both power switches. To drive the logic inputs no external driver is needed, therefore the BTM7752G can be interfaced directly to a microcontroller.

#### 6.4.2 Dead Time Generation

In bridge applications it has to be assured that the highside and lowside MOSFET are not conducting at the same time, connecting directly the battery voltage to GND. This is assured by a circuit in the driver IC, which senses the status of the MOSFETs to ensure that the high or low side switch can be switched on only if the corresponding low or high side switch is completely turned off.

#### 6.4.3 Status Flag Diagnosis with Current Sense Capability

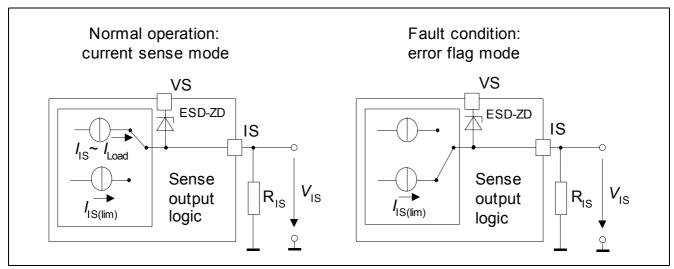

The status pin IS is used as a combined current sense and error flag output. In normal operation (current sense mode), a current source is connected to the status pin, which delivers a current proportional to the forward load current flowing through the active high side switch. If the high side switch is inactive or the current is flowing in the reverse direction no current will be driven except for a marginal leakage current  $I_{\rm IS(LK)}$ . If both high side switches are in on state, the IS provides the sense current of the high side switch, which has been turned on first. To reset this assignment both inputs IN1 and IN2 has to be set to low and both high side switches has to be off.

The external resistor  $R_{\rm IS}$  determines the voltage per output current. E.g. with the nominal value of **3.1**k for the current sense ratio  $k_{\rm ILIS}$  =  $I_{\rm L}$  /  $I_{\rm IS}$ , a resistor value of  $R_{\rm IS}$  = 1k $\Omega$  leads to  $V_{\rm IS}$  = ( $I_{\rm L}$  / **3.1**A)V. In case of a fault condition the status output is connected to a current source which is independent of the load current and provides  $I_{\rm IS(lim)}$ . The maximum voltage at the IS pin is determined by the choice of the external resistor and the supply voltage. In case of current limitation the  $I_{\rm IS(lim)}$  is activated for 1.5 \*  $t_{\rm CLS}$ .

Figure 13 Sense current and fault current

Data Sheet 17 Rev. 2.0, 2010-05-28

Figure 14 Sense Current vs. Load Current

# 6.4.4 Truth Table

| Device State                          | Inpu | ts  |     | Outp | uts   |     |     | Mode                 |                                                                            |

|---------------------------------------|------|-----|-----|------|-------|-----|-----|----------------------|----------------------------------------------------------------------------|

|                                       | INH  | IN1 | IN2 | HS1  | LS1   | HS2 | LS2 | IS                   |                                                                            |

| Normal operation                      | 0    | 0   | 0   | OFF  | OFF   | OFF | OFF | 0                    | Stand-by mode, reset                                                       |

|                                       | 1    | 0   | 0   | OFF  | ON    | OFF | ON  | 0                    | _                                                                          |

|                                       | 1    | 0   | 1   | OFF  | ON    | ON  | OFF | CSHS2 <sup>1)</sup>  | -                                                                          |

|                                       | 1    | 1   | 0   | ON   | OFF   | OFF | ON  | CS HS1 <sup>1)</sup> | _                                                                          |

|                                       | 1    | 1   | 1   | ON   | OFF   | ON  | OFF | CS <sup>2)</sup>     | _                                                                          |

| Open-Load detection                   | 0    | 0   | 1   | OFF  | OFF   | ON  | OFF | CS HS2 <sup>1)</sup> | Enable Open-load detection                                                 |

| mode                                  | 0    | 1   | 0   | ON   | OFF   | OFF | OFF | CS HS1 <sup>1)</sup> | Enable Open-load detection                                                 |

|                                       | 0    | 1   | 1   | ON   | OFF   | ON  | OFF | CS <sup>2)</sup>     |                                                                            |

| Over-voltage (OV)                     | Х    | Х   | Х   | ON   | OFF   | ON  | OFF | 1                    | Shut-down of LSS, HSS activated, error detected                            |

| Under-voltage (UV)                    | Х    | Х   | Х   | OFF  | OFF   | OFF | OFF | 0                    | UV lockout, reset                                                          |

| Overtemperature or                    | 0    | 0   | 0   | OFF  | OFF   | OFF | OFF | 0                    | Stand-by mode, reset of latch                                              |

| short circuit of HSS or               | 1    | Х   | Х   | OFF  | F OFF | OFF | OFF | F 1                  | Shut-down with latch, error                                                |

| LSS 3)                                | Χ    | 1   | Х   |      |       |     |     |                      | detected                                                                   |

|                                       | Χ    | Х   | 1   |      |       |     |     |                      |                                                                            |

| Current limitation mode half bridge 1 | 1    | 0   | X   | ON   | OFF   | X   | X   | 1                    | Short Circuit in LS1 detected, half bridge 2 operates in normal mode       |

|                                       | 1    | 1   | X   | OFF  | ON    | X   | X   | 1                    | Short Circuit in HS1 detected, half bridge 2 operates in normal mode       |

|                                       | 0    | 1   | Х   | OFF  | OFF   | Χ   | Х   | 1                    | Short Circuit in HS1 detected                                              |

| Current limitation mode half bridge 2 | 1    | Х   | 0   | Х    | Х     | ON  | OFF | 1                    | Short Circuit in LS2 detected,<br>half bridge 1 operates in normal<br>mode |

|                                       | 1    | Х   | 1   | Х    | Х     | OFF | ON  | 1                    | Short Circuit in HS2 detected,<br>half bridge 1 operates in normal<br>mode |

|                                       | 0    | Χ   | 1   | Х    | Χ     | OFF | OFF | 1                    | Short Circuit in HS2 detected                                              |

<sup>1)</sup> Previous current sense assignment to be reset by IN1=IN2=low and both high side switches off (see Chapter 6.4.3).

<sup>3)</sup> In short circuit of HSS or LSS, the junction temperature will arise and as soon as the over temperature shut down threshold is reached the device will shut down and latch the status. Short circuit of HSS and LSS itself won't be detected as failure.

| Inputs:        | Switches               | Status Flag IS:         |

|----------------|------------------------|-------------------------|

| 0 = Logic LOW  | OFF = switched off     | CS = Current sense mode |

| 1 = Logic HIGH | ON = switched on       | 1 = Logic HIGH (error)  |

| X = 0 or 1     | X = switched on or off |                         |

Data Sheet 19 Rev. 2.0, 2010-05-28

<sup>2)</sup> When both high side switches are in on state, the CS provides the sense signal for the high side switch, which has been turned on first.

# 6.4.5 Electrical Characteristics - Control and Diagnostics

$V_{\rm S}$  = 8 V to 18 V,  $T_{\rm j}$  = -40 °C to +150 °C, VS pins shorted, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                                          | Symbol                                                        | Limit \         | /alues            |                 | Unit            | <b>Test Conditions</b>                                                                     |  |

|--------|------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|--------------------------------------------------------------------------------------------|--|

|        |                                                                                    |                                                               | Min.            | n. Typ. Max.      |                 |                 |                                                                                            |  |

| Contro | Inputs (IN and INH)                                                                | 1                                                             |                 | 1                 |                 | II.             |                                                                                            |  |

| 6.4.1  | High level threshold voltage INH, IN1, IN2                                         | $V_{\text{INH(H)}},$ $V_{\text{IN1(H)}},$ $V_{\text{IN2(H)}}$ | _               | 1.6               | 2               | V               | -                                                                                          |  |

| 6.4.2  | Low level threshold voltage INH, IN1, IN2                                          | $V_{\text{INH(L)}},$ $V_{\text{IN1(L)}},$ $V_{\text{IN2(L)}}$ | 1.1             | 1.4               | _               | V               | -                                                                                          |  |

| 6.4.3  | Input voltage hysteresis                                                           | $V_{INHHY}, V_{INHY}$                                         | _               | 200               | _               | mV              | 1)                                                                                         |  |

| 6.4.4  | Input current                                                                      | $I_{\text{INH(H)}},$ $I_{\text{IN1(H)}}, I_{\text{IN2(H)}}$   | _               | 30                | 200             | μΑ              | $V_{\text{IN1}}, V_{\text{IN2}}, V_{\text{INH}} = 5.5 \text{ V}$                           |  |

| 6.4.5  | Input current                                                                      | $I_{\text{INH(L)}}$ , $I_{\text{IN2(L)}}$                     | _               | 25                | 125             | μΑ              | $V_{\rm IN1}, V_{\rm IN2}, V_{\rm INH} = 0.4 \text{ V}$                                    |  |

| Curren | nt Sense                                                                           | ,                                                             |                 |                   | *               |                 | •                                                                                          |  |

| 6.4.6  | Current sense ratio in static on-condition $k_{\rm ILIS} = I_{\rm L} / I_{\rm IS}$ | k <sub>ILIS</sub>                                             | 2<br>1.7<br>1.5 | 3.1<br>3.1<br>3.1 | 4.2<br>4.6<br>5 | 10 <sup>3</sup> | $R_{\rm IS}$ = 1 k $\Omega$<br>$I_{\rm L}$ = 6 A<br>$I_{\rm L}$ = 2 A<br>$I_{\rm L}$ = 1 A |  |

| 6.4.7  | Differential Current sense ratio in static on-condition $dk_{ILIS} = dI_L/dI_{IS}$ | $dk_{ILIS}$                                                   | 2               | 3.1               | 4.2             | 10 <sup>3</sup> | $R_{\rm IS} = 1 \text{ k}\Omega$<br>$I_{\rm L} > 0.5 \text{ A}$                            |  |

| 6.4.8  | Maximum analog sense current - Sense current in fault condition                    | $I_{IS(lim)}$                                                 | 4.25            | 5                 | 7               | mA              | $V_{\rm S}$ = 13.5 V<br>$R_{\rm IS}$ = 1 k $\Omega$                                        |  |

| 6.4.9  | Isense leakage current                                                             | I <sub>ISL</sub>                                              | _               | _                 | 1               | μΑ              | $V_{\text{IN1}} = V_{\text{IN2}} = 0 \text{ V},$<br>no error detected                      |  |

| 6.4.10 | Isense leakage current, active high side switch                                    | I <sub>ISH</sub>                                              | _               | 1                 | 100             | μΑ              | $V_{\text{IN1}}$ or $V_{\text{IN2}}$ = 5 V $I_{\text{L}}$ = 0 A                            |  |

<sup>1)</sup> Not subject to production test, specified by design.

**Application Information**

# 7 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

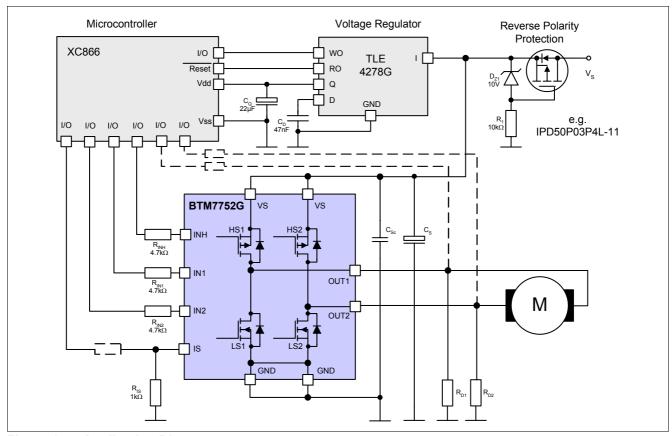

Figure 15 Application Diagram

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

# 7.1 Application and Layout Considerations

Due to the fast switching times for high currents, special care has to be taken during the PCB layout. Stray inductances have to be minimized in the power bridge design as it is necessary in all switched high power bridges. The BTM7752G has no separate pin for power ground and logic ground. Therefore it is recommended to ensure that the offset between power ground and logic ground pins of the device is minimized. It is also necessary to ensure that all VS pins are at the same voltage level. Therefore the VS pins need to be shorted together. Voltage differences between the VS pins may cause parameter deviations (such as reduced current limits and current sense ratio (kilis)) up to a latched shutdown of the device with error signal on the IS pin, similar to overtemperature shutdown.

Due to the fast switching behavior of the device in current limitation mode or overvoltage lock out a low ESR electrolytic capacitor  $C_s$  of at least 100  $\mu$ F from VS to GND is recommended. This prevents destructive voltage peaks and drops on VS. This is recommended for both PWM and non PWM controlled applications. The value of the capacitor must be verified in the real application.

In addition a ceramic capacitor  $C_{\rm sc}$  from VS to GND close to each device is recommended to provide current for the switching phase via a low inductance path and therefore reducing noise and ground bounce. A reasonable value for this capacitor would be about 470 nF.

Data Sheet 21 Rev. 2.0, 2010-05-28

#### **Application Information**

It is recommended to do the freewheeling in the low side path to ensure a proper function and avoid unintended overtemperature detection and shutdown. For proper operation it is also recommended to put a pull-down resistor  $R_{\rm Dx}$  on each output OUTx to GND with a value in the range of e.g. 1...10 k $\Omega$ . These resistors can also be used for open load detection.

#### **Considerations for Open Load Detection Mode**

As mentioned in **Chapter 6.4.1** both high side switches can be switched on independently while all other switches are off. This will be realized by setting the corresponding IN signal to high while INH and the other IN are low.

| Device State        | Inputs |     | Outputs |     |     |     |     | Mode                 |                     |

|---------------------|--------|-----|---------|-----|-----|-----|-----|----------------------|---------------------|

|                     | INH    | IN1 | IN2     | HS1 | LS1 | HS2 | LS2 | IS                   |                     |

| Open-Load detection | 0      | 0   | 1       | OFF | OFF | ON  | OFF | CS HS2 <sup>1)</sup> | HS2 active          |

| mode                | 0      | 1   | 0       | ON  | OFF | OFF | OFF | CS HS1 <sup>1)</sup> | HS1 active          |

|                     | 0      | 1   | 1       | ON  | OFF | ON  | OFF | CS <sup>2)</sup>     | both HSx are active |

<sup>1)</sup> Previous current sense assignment to be reset by IN1=IN2=low and both high side switches off (see Chapter 6.4.3)

Together with the recommended pull-down resistors on the outputs OUTx to GND this provides the possibility to do an open load detection in H-bridge configuration.

In case of one high side is active while the other half bridge is off (HS off and LS off) a current of up to 2mA will be sourced out of the OUT of the high ohmic half bridge. This has to be considered while choosing the right value of the pull-down resistor.

Data Sheet 22 Rev. 2.0, 2010-05-28

<sup>2)</sup> When both high side switches are in on state, the CS provides the sense signal for the high side switch, which has been turned on at first.

**Package Outlines**

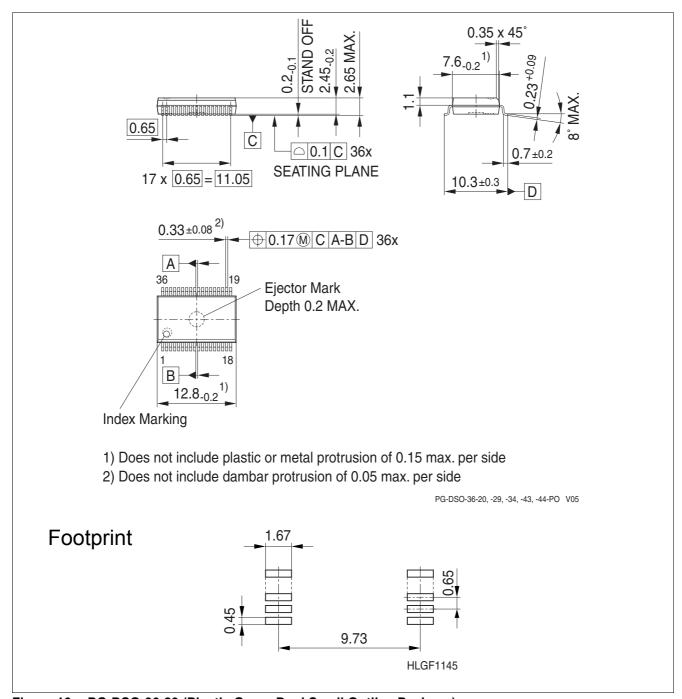

# 8 Package Outlines

Figure 16 PG-DSO-36-29 (Plastic Green Dual Small Outline Package)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: <a href="http://www.infineon.com/packages">http://www.infineon.com/packages</a>.

Dimensions in mm

**Revision History**

# 9 Revision History

| Revision | Date       | Changes                    |

|----------|------------|----------------------------|

| 2.0      | 2010-05-28 | Initial version Data Sheet |

Data Sheet 24 Rev. 2.0, 2010-05-28

Edition 2010-05-28

Published by Infineon Technologies AG 81726 Munich, Germany © 2010 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331