#### 2.5Gbps Burst Mode Laser Driver with Integrated Limiting Amplifier

# **General Description**

The SY88236L is a single supply 3.3V integrated burst mode laser driver and post amplifier for A-PON, B-PON, EPON, GE-PON, and G-PON applications with data rates from 155Mbps up to 2.5Gbps. The driver can deliver modulation current up to 85mA, and provides a high compliance voltage that makes it suitable for high-current operation with the laser DC-coupled to it. The post amplifier can detect signals with amplitude as low as  $5mV_{PP}$ .

The SY88236AL is a version of the SY88236L without  $50\Omega$  termination resistors at the inputs of the driver and the post amplifier. The SY88236AL is to be used specially in SFF modules mounted on ONU mother boards which have preinstalled terminations. Removing post amplifier input terminations will allow for receiver gain control.

All support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

# Features

- 2.4V minimum laser compliance voltage

- Operation up to 2.5Gbps

- Fast burst mode enable/disable delay

- Modulation current up to 85mA

- Bias current up to 70mA

- Infinite bias current hold time between bursts

- Bias, Modulation, and power monitoring

- High input sensitivity post amplifier, 5mV<sub>PP</sub>

- Programmable LOS level

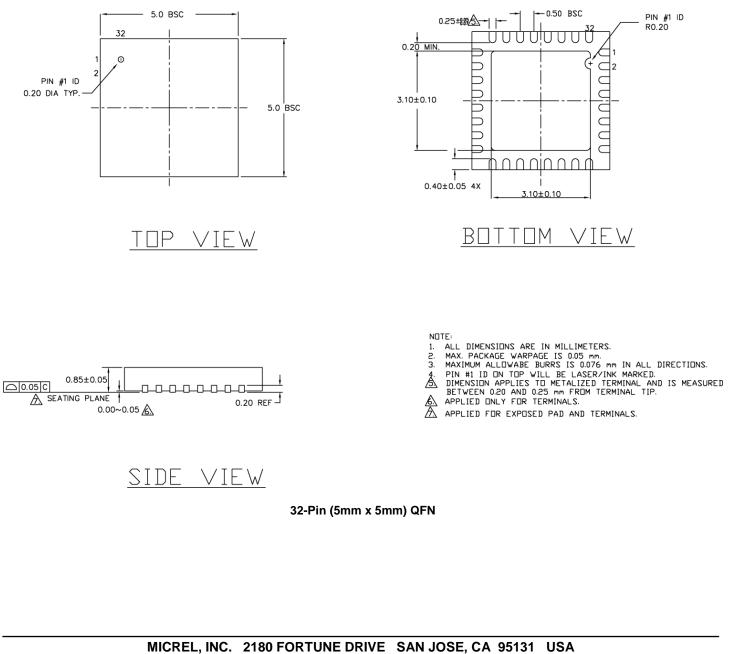

- Available in 32-pin (5mm x 5mm) QFN package

# **Applications**

• Multi-rate burst mode applications: A-PON, B-PON, G-PON, E-PON, GE-PON

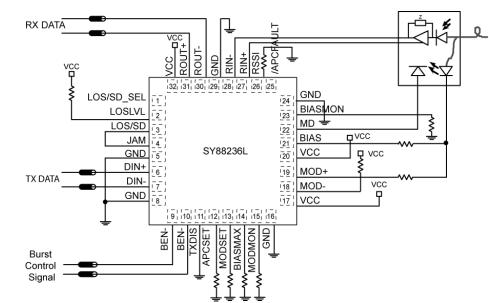

# **Typical Application**

# Ordering Information<sup>(1)</sup>

| Part Number                  | Voltage | Temperature<br>Range | Package Type | Package Marking                             | Lead<br>Finish    |

|------------------------------|---------|----------------------|--------------|---------------------------------------------|-------------------|

| SY88236LMG                   | 3.3V    | –40° to +85°C        | QFN-32       | SY88236L with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

| SY88236LMGTR <sup>(2)</sup>  | 3.3V    | –40° to +85°C        | QFN-32       | SY88236L with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

| SY88236ALMG                  | 3.3V    | –40° to +85°C        | QFN-32       | SY88236A with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

| SY88236ALMGTR <sup>(2)</sup> | 3.3V    | –40° to +85°C        | QFN-32       | SY88236A with<br>Pb-Free bar-line indicator | NiPdAu<br>Pb-Free |

Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = +25^{\circ}C$ , DC Electricals only.

2. Tape and Reel.

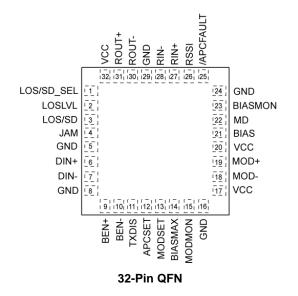

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name   | Pin Function                                                                                                                                                                                                                                                              |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LOS/SD_SEL | LOS or SD selection, TTL input. Set high, connect to VCC, or leave open to select LOS. Set low or connect to GND to select SD.                                                                                                                                            |

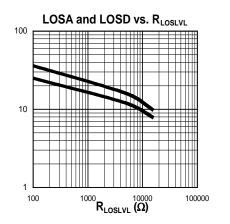

| 2          | LOSLVL     | Loss-of-Signal Level Set. A resistor from this pin to $V_{CC}$ sets the threshold for the data input amplitude at which LOS will be asserted.                                                                                                                             |

| 3          | LOS/SD     | Loss-of-Signal (LOS selected): asserts high when the data input amplitude falls below the threshold set by $LOS_{LVL}$ .                                                                                                                                                  |

|            |            | Signal Detect (SD selected): asserts low when the data input amplitude falls below the threshold set by $LOS_{LVL}$ .                                                                                                                                                     |

| 4          | JAM        | Active low TTL/CMOS. Internally pulled-up with $75k\Omega$ . Connect to GND or apply a low level signal (<0.8 V) to enable the post amp output. Can be shorted to LOS/SD (pin 3) to create a squelch function. The polarity of this input follows the polarity of LOS/SD. |

| 6          | DIN+       | SY88236L: Driver Non-inverting input data. Internally terminated with $50\Omega$ to a reference voltage.                                                                                                                                                                  |

|            |            | SY88236AL: Driver Non-inverting input data. No internal termination.                                                                                                                                                                                                      |

| 7          | DIN-       | SY88236L: Driver inverting input data. Internally terminated with 50 $\Omega$ to a reference voltage.                                                                                                                                                                     |

|            |            | SY88236AL: Driver inverting input data. No internal termination.                                                                                                                                                                                                          |

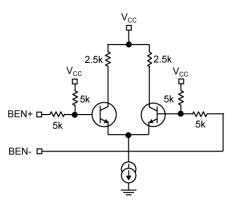

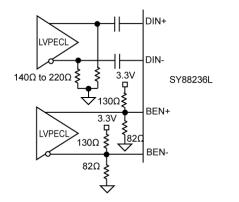

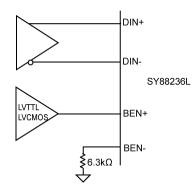

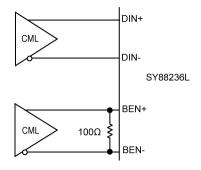

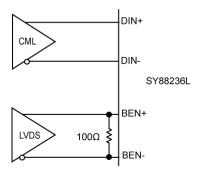

| 9          | BEN+       | Non-Inverting burst enable. Accepts any input, single-ended or differential: TTL/CMOS, LVPECL, CML, LVDS, and HSTL. BEN requires an external termination. See Figure 2-a-d.                                                                                               |

| 10         | BEN-       | Inverting burst enable. Accepts any input, single-ended or differential: TTL/CMOS, LVPECL, CML, LVDS, and HSTL. BEN requires an external termination. See Figure 2-a-d.                                                                                                   |

| 11         | TXDIS      | Internally pulled-up. Pull-down with a $22k\Omega$ or lower resistance or apply a low level signal (<0.8 V) to enable bias and modulation. Keep floating or apply a high level (>2V) to disable bias and modulation.                                                      |

# Pin Description (continued)

| Pin Number       | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12               | APCSET    | Bias current setting and control. The bias current is set by installing an external resistor from this pin to ground or using a current source. Connect a 50k $\Omega$ resistor to GND for open loop operation.                                                                                                                                                             |

| 13               | MODSET    | Modulation current setting and control. The modulation current is set by installing an external resistor from this pin to ground or using a current source.                                                                                                                                                                                                                 |

| 14               | BIASMAX   | Install a resistor between this pin and GND to set the maximum bias current for the closed loop operation. The APC loop controls the bias current up to the level of BIASMAX. When the bias current reaches the maximum value set through this pin, the driver continues to sink a current equal to this maximum. For open loop operations, this pin sets the bias current. |

| 15               | MODMON    | Modulation Current Monitor. Provides a current, which represents 1/100 of the modulation current. Install a resistor between this pin and GND to convert that current to a voltage proportional to the modulation current.                                                                                                                                                  |

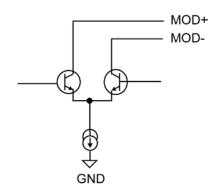

| 18               | MOD-      | Inverted modulation current output. Provides modulation current when input data is negative.                                                                                                                                                                                                                                                                                |

| 19               | MOD+      | Non-inverted modulation current output. Provides modulation current when input data is positive.                                                                                                                                                                                                                                                                            |

| 21               | BIAS      | Bias current output, sources current when BEN+ is high. Connect to the cathode of the laser through a resistor.                                                                                                                                                                                                                                                             |

| 22               | MD        | Input from the laser monitoring photodiode. Connect to the anode of the laser photodiode for APC operation.                                                                                                                                                                                                                                                                 |

| 23               | BIASMON   | Bias Monitor. Provides a current, which represents 1/50 of the bias current. Install a resistor between this pin and GND to convert that current to a voltage.                                                                                                                                                                                                              |

| 24               | RSSI      | Received Signal Strength Indicator. Install a resistor from this pin to GND to get a voltage proportional to the received signal.                                                                                                                                                                                                                                           |

| 25               | /APCFAULT | Indicates APC failure when Low. Active Low TTL/CMOS.                                                                                                                                                                                                                                                                                                                        |

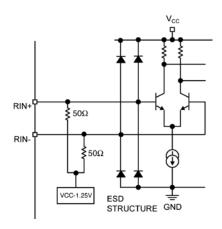

| 27               | RIN+      | <b>SY88236L:</b> Post amplifier Non-inverting input data. Internally terminated with $50\Omega$ to a reference voltage.                                                                                                                                                                                                                                                     |

|                  |           | SY88236AL: Post amplifier Non-inverting input data. No internal termination.                                                                                                                                                                                                                                                                                                |

| 28               | RIN-      | <b>SY88236L:</b> Driver inverting input data. Internally terminated with $50\Omega$ to a reference voltage.                                                                                                                                                                                                                                                                 |

|                  |           | SY88236AL: Driver inverting input data. No internal termination.                                                                                                                                                                                                                                                                                                            |

| 30               | ROUT-     | Post Amplifier Complementary CML data output.                                                                                                                                                                                                                                                                                                                               |

| 31               | ROUT+     | Post Amplifier true CML data output.                                                                                                                                                                                                                                                                                                                                        |

| 5, 8, 16, 24, 29 | GND       | Ground. Ground and exposed pad must be connected to the plane of the most negative potential.                                                                                                                                                                                                                                                                               |

| 17, 20, 32       |           | Supply Voltage. Bypass with a 0.1µF//0.01µF low ESR capacitor as close to VCC pin as possible.                                                                                                                                                                                                                                                                              |

# **Truth Tables**

| ſ | DIN+ | DIN- | TXDIS | MOD+ <sup>(2)</sup> | MOD- | Laser<br>Output<br>Power <sup>(3)</sup> |

|---|------|------|-------|---------------------|------|-----------------------------------------|

| ſ | L    | Н    | L     | Н                   | L    | L                                       |

| ſ | Н    | L    | L     | L                   | Н    | Н                                       |

|   | Х    | Х    | Х     | Н                   | L    | L                                       |

Table 1. Modulation Output Truth Table<sup>(1, 3)</sup>

| TXDIS | BEN+ | BEN- | BIAS |

|-------|------|------|------|

| L     | Н    | L    | ON   |

| L     | L    | Н    | OFF  |

| Н     | Х    | Х    | OFF  |

#### Table 2. BIAS Output Truth Table

#### Notes:

- 1. Assuming BEN+ = H and BEN- = L.

- 2.  $I_{MOD} = 0$  when MOD+ = H.

- 3. Assuming that the cathode of the laser is connected to MOD+.

| LOS/SD_SEL | Function<br>Selected | JAM | Output   |

|------------|----------------------|-----|----------|

| Н          | LOS                  | L   | Enabled  |

| Н          | LOS                  | Н   | Disabled |

| L          | SD                   | L   | Disabled |

| L          | SD                   | Н   | Enabled  |

Table 3. Post Amp Output Truth Table

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN</sub> )     | -0.5V to +4.0V                           |

|---------------------------------------|------------------------------------------|

| CML Input Voltage (VIN)               | $V_{\rm CC}$ -1.2V to $V_{\rm CC}$ +0.5V |

| TTL Control Input Voltage (VIN)       | 0V to V <sub>CC</sub>                    |

| Lead Temperature (soldering, 20sec.   | )+260°C                                  |

| Storage Temperature (T <sub>s</sub> ) | 65°C to +150°C                           |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )                                                  | +3.0V to +3.6V |

|------------------------------------------------------------------------------------|----------------|

| Ambient Temperature (T <sub>A</sub> )                                              | 40°C to +85°C  |

| Ambient Temperature (T <sub>A</sub> )<br>Package Thermal Resistance <sup>(3)</sup> |                |

| QFN                                                                                |                |

| $(\theta_{JA})$ Still-air                                                          | 60°C/W         |

| (ψ <sub>JB</sub> )                                                                 | 33°C/W         |

# **DC Electrical Characteristics**

$T_A = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.0V$  to +3.6V, unless otherwise noted. Typical values are  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ ,  $T_A = 25^{\circ}C$ ,  $I_{MOD} = -40^{\circ}C$  to +85°C and  $V_{CC} = +3.3V$ . 30mA,  $I_{BIAS} = 30mA$ .

| Symbol          | Parameter                                | Condition                             | Min  | Тур | Мах                   | Units |

|-----------------|------------------------------------------|---------------------------------------|------|-----|-----------------------|-------|

| I <sub>CC</sub> | Power Supply Current                     | Modulation and Bias currents excluded |      | 90  | 150 <sup>(4)</sup>    | mA    |

| V <sub>IL</sub> | TXDIS, JAM, and LOS/SD_SEL<br>Input Low  |                                       | -0.3 |     | 0.8                   | V     |

| V <sub>IH</sub> | TXDIS, JAM, and LOS/SD_SEL<br>Input High |                                       | 2    |     | V <sub>CC</sub> + 0.3 | V     |

| V <sub>MOD_MIN</sub>               | Minimum Voltage Required at<br>the Driver Output, MOD+ and<br>MOD-, for Proper Operation |                                                      | 0.6  |     |                       | V  |

|------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------|------|-----|-----------------------|----|

| V <sub>BIAS_MIN</sub>              | Minimum Voltage Required at the Driver Output, BIAS pin, for Proper Operation            |                                                      | 0.8  |     |                       | V  |

| I <sub>BIAS</sub>                  | Bias-ON Current                                                                          | Voltage at Bias pin ≥ 0.8V                           | 1    |     | 70                    | mA |

| IBIAS_OFF                          | Bias-OFF Current                                                                         | Current at BIAS pin when TXDIS is high or BEN is low |      |     | 150                   | μA |

| R <sub>IN</sub><br>(SY88236L only) | Input Resistance at DIN+ and DIN-                                                        | Single ended                                         | 42.5 | 50  | 57.5                  | Ω  |

| BEN+, BEN-                         | Burst Mode Enable Signal                                                                 | Single ended                                         |      | 0.8 |                       | V  |

| V <sub>IH</sub> (BEN)              | High Voltage                                                                             | BEN+, BEN-                                           | 2    |     | V <sub>CC</sub> + 0.3 | V  |

| V <sub>IL</sub> (BEN)              | Low Voltage                                                                              | BEN+, BEN-                                           | -0.3 |     | 0.8                   | V  |

| V <sub>OL</sub>                    | /APCFAULT Output Low                                                                     | $I_{OL} = 2mA$                                       |      |     | 0.5                   | V  |

| I <sub>OH</sub>                    | /APCFAULT Output Leakage                                                                 | $V_{OH} = V_{CC}$                                    |      |     | 100                   | μA |

| I <sub>MD</sub>                    | Current range at MD pin                                                                  |                                                      | 50   |     | 1500                  | μA |

Notes:

1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

3. Package Thermal Resistance assumes exposed pad is soldered (or equivalent) to the devices most negative potential on the PCB.  $\theta_{JB}$  uses a 4-layer and  $\theta_{JA}$  in still air unless otherwise stated.

4.  $I_{CC}$  = 150mA for worst-case conditions with  $I_{MOD}$  = 85mA,  $I_{Bias}$  = 70mA,  $T_A$  = +85°C,  $V_{CC}$  = 3.6V.

# Post Amplifier

| Symbol                                  | Parameter                        | Condition         | Min                    | Тур                    | Max                    | Units |

|-----------------------------------------|----------------------------------|-------------------|------------------------|------------------------|------------------------|-------|

| LOS <sub>LVL</sub>                      | LOS <sub>LVL</sub> Voltage       |                   | V <sub>CC</sub> -1.3   |                        | Vcc                    | V     |

| V <sub>OH</sub>                         | ROUT+, ROUT- HIGH Voltage        |                   | V <sub>CC</sub> -0.020 | V <sub>CC</sub> -0.005 | V <sub>CC</sub>        | V     |

| V <sub>OL</sub>                         | ROUT+, ROUT- LOW Voltage         |                   | V <sub>CC</sub> -0.475 | V <sub>CC</sub> -0.400 | V <sub>CC</sub> -0.350 | V     |

| VOFFSET                                 | Differential Output Offset       |                   |                        |                        | ±80                    | mV    |

| Z <sub>0</sub> (ROUT)                   | Single-Ended Output<br>Impedance |                   | 42.5                   | 50                     | 57.5                   | Ω     |

| Z <sub>I</sub> (RIN)<br>(SY88236L only) | Single-Ended Input Impedance     |                   | 42.5                   | 50                     | 57.5                   | Ω     |

| V <sub>OL</sub> (LOS/SD)                | LOS/SD Output Low                | $I_{OL} = 2mA$    |                        |                        | 0.5                    | V     |

| I <sub>OH</sub> (LOS/SD)                | LOS/SD Output Leakage            | $V_{OH} = V_{CC}$ |                        |                        | 100                    | μA    |

# **AC Electrical Characteristics**

$T_A = -40^{\circ}$ C to +85°C and  $V_{CC} = +3.0$ V to +3.6V, unless otherwise noted. Typical values are  $V_{CC} = +3.3$ V,  $T_A = 25^{\circ}$ C,  $I_{MOD} = 30$ mA,  $I_{BIAS} = 30$ mA.

| Symbol                              | Parameter                             | Condition                                                  | Min   | Тур | Max                                                                                                                        | Units            |

|-------------------------------------|---------------------------------------|------------------------------------------------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------|------------------|

| Laser Drive                         | r                                     |                                                            |       |     |                                                                                                                            |                  |

|                                     | Data Rate                             | NRZ                                                        | 0.155 |     | 2.5                                                                                                                        | Gbps             |

| V <sub>DIFF-IN</sub> (DIN)          | Differential Input Voltage<br>Swing   |                                                            | 100   |     | 2400                                                                                                                       | mV <sub>PP</sub> |

| V <sub>IN</sub><br>(BEN+/BEN-)      | Input Voltage Swing,<br>Single Ended  | BEN+, BEN-                                                 | 100   |     |                                                                                                                            | mV               |

| V <sub>DIFF-IN</sub><br>(BEN+/BEN-) | Differential Input Voltage<br>Swing   | BEN+, BEN-                                                 | 200   |     |                                                                                                                            | mV <sub>PP</sub> |

| 1                                   | Modulation Current <sup>(5)</sup>     | AC-coupled                                                 | 10    |     | 85                                                                                                                         | mA               |

| I <sub>MOD</sub>                    | Modulation Current                    | DC-coupled, Voltage at MOD pin ≥0.6V                       | 10    |     | 70 <sup>(6)</sup>                                                                                                          | mA               |

| l                                   | Modulation OFF Current                | Current at MOD+ when TXDIS is high or BEN+ is low          |       |     | 150                                                                                                                        | μA               |

| I <sub>MOD_OFF</sub>                | Modulation OFF Current                | Current at MOD- when TXDIS is high or BEN+ is low          |       |     | 150                                                                                                                        | μA               |

| tr                                  | Output Current Rise Time              | 20% to 80%, $I_{MOD}$ = 60mA                               |       | 60  | 85                                                                                                                         | ps               |

| t <sub>f</sub>                      | Output Current Fall Time              | 20% to 80%, I <sub>MOD</sub> = 60mA                        |       | 60  | 85                                                                                                                         | ps               |

| Jitter                              | Total Jitter <sup>(7)</sup>           | 155Mbps data rate                                          |       |     | 30                                                                                                                         | ps <sub>PP</sub> |

|                                     |                                       | 622Mbps data rate                                          |       |     | 30                                                                                                                         | ps <sub>PP</sub> |

|                                     |                                       | 1.25Gbps data rate                                         |       |     | 30                                                                                                                         | ps <sub>PP</sub> |

|                                     |                                       | 2.5Gbps data rate                                          |       |     | 60         85           60         85           30         30                                                              | PSPP             |

|                                     |                                       | Power up with TXDIS low and BEN+ high                      |       |     |                                                                                                                            | μs               |

| t <sub>INIT</sub>                   | APC Loop Initialization               | TXDIS changes from high to low with power ON and BEN+ high |       |     | 10                                                                                                                         | μs               |

|                                     |                                       | BEN changes from low to high with power ON and TXDIS low   |       |     | 2400<br>2400<br>85<br>70 <sup>(6)</sup><br>150<br>150<br>60 85<br>60 85<br>60 85<br>30<br>30<br>30<br>30<br>30<br>12<br>12 | ns               |

|                                     | Burst Enable Delay <sup>(8, 9)</sup>  |                                                            |       |     |                                                                                                                            | ns               |

|                                     | Burst Disable Delay <sup>(8,10)</sup> |                                                            |       |     | 2                                                                                                                          | ns               |

|                                     |                                       | 155Mbps                                                    | 1.9   |     |                                                                                                                            | μs               |

|                                     | Durat ON Time                         | 622Mbps                                                    | 720   |     |                                                                                                                            | ns               |

|                                     | Burst ON-Time                         | 1.25Gbps                                                   | 576   |     |                                                                                                                            | ns               |

|                                     |                                       | 2.5Gbps                                                    | 576   |     |                                                                                                                            | ns               |

|                                     |                                       | 155Mbps                                                    | 1.9   |     |                                                                                                                            | μs               |

|                                     |                                       | 622Mbps                                                    | 720   |     |                                                                                                                            | ns               |

|                                     | Burst OFF-Time                        | 1.25Gbps                                                   | 576   |     |                                                                                                                            | ns               |

|                                     |                                       | 2.5Gbps                                                    | 576   |     |                                                                                                                            | ns               |

Notes:

5. Load = 15Ω.

6. Assuming  $V_{CC} = 3.0V$ , Laser bandgap voltage = 1V, laser package inductance = 1nH, laser equivalent series resistor = 5  $\Omega$ , and damping resistor = 10 $\Omega$ .

7. Total jitter is measured using 2<sup>7</sup> – 1 PRBS pattern.

8. Measured with a laser equivalent resistive load.

9. Burst Enable Delay is measured as the time between the instant when the BEN+ signal going from low to high reaches 50% of its amplitude and the instant at which the modulation current or the bias current (whichever takes longer) reaches 90% of its final value.

10. Burst Disable Delay is measured as the time between the instant when the BEN+ signal going from high to low reaches 50% of its amplitude and the instant at which the modulation current or the bias current (whichever takes longer) goes below 10% of its final value.

| Symbol                          | Parameter                                    | Condition                                        | Min | Тур   | Max  | Units                    |

|---------------------------------|----------------------------------------------|--------------------------------------------------|-----|-------|------|--------------------------|

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time<br>(20% to 80%)        | Note 11                                          |     | 60    | 120  | ps                       |

| <b>İ</b> JITTER                 | Deterministic                                | Note 12                                          |     | 15    |      | PSPP                     |

|                                 | Random                                       | Note 13                                          |     | 5     |      | <b>ps</b> <sub>RMS</sub> |

| V <sub>Diff_IN</sub><br>(RIN)   | Differential Input Voltage Swing             |                                                  | 5   |       | 1800 | $mV_{PP}$                |

| V <sub>Diff_OUT</sub><br>(ROUT) | Differential Output Voltage<br>Swing         | Note 11                                          | 700 | 800   | 950  | mV <sub>PP</sub>         |

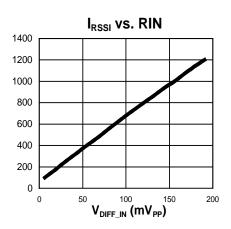

| G <sub>RSSI</sub>               | RSSI Gain = $I_{RSSI} / V_{Diff_{IN}}$ (RIN) | $5mV_{PP} \le V_{Diff_{IN}}(RIN) \le 200mV_{PP}$ |     | 5     |      | μΑ/<br>mV <sub>PP</sub>  |

| RSSI<br>Linearity               |                                              | $5mV_{PP} \le V_{Diff_{IN}}(RIN) \le 200mV_{PP}$ |     | ± 2.5 |      | %                        |

| LOS <sub>AL</sub>               | Low LOS Assert Level                         | $R_{LOSLVL} = 15k\Omega$                         | 2   | 8     |      | $mV_{PP}$                |

| LOS <sub>DL</sub>               | Low LOS De-assert Level                      | $R_{LOSLVL} = 15k\Omega$                         |     | 10    | 20   | $mV_{PP}$                |

| $HSY_{L}$                       | Low LOS Hysteresis                           | $R_{LOSLVL} = 15k\Omega$ , Note 14               | 1.5 | 2.6   | 6    | dB                       |

| LOSAM                           | Medium LOS Assert Level                      | $R_{LOSLVL} = 5k\Omega$                          | 4   | 12    |      | $mV_{PP}$                |

| LOS <sub>DM</sub>               | Medium LOS De-assert Level                   | $R_{LOSLVL} = 5k\Omega$                          |     | 16    | 30   | $mV_{PP}$                |

| HSYM                            | Medium LOS Hysteresis                        | $R_{LOSLVL} = 5k\Omega$ , Note 14                | 1.5 | 2.8   | 6    | dB                       |

| LOSAH                           | High LOS Assert Level                        | $R_{LOSLVL} = 100\Omega$                         | 15  | 25    |      | $mV_{PP}$                |

| LOS <sub>DH</sub>               | High LOS De-assert Level                     | $R_{LOSLVL} = 100\Omega$                         |     | 36    | 50   | $mV_{PP}$                |

| HSY <sub>H</sub>                | High LOS Hysteresis                          | $R_{LOSLVL} = 100\Omega$                         | 1.5 | 3.2   | 6    | dB                       |

| TOFF                            | LOS Release Time                             | Note 15                                          |     | 2     | 10   | μs                       |

| T <sub>ON</sub>                 | LOS Assert Time                              | Note 15                                          |     | 2     | 10   | μs                       |

| B-3dB                           | 3dB Bandwidth                                |                                                  |     | 2.0   |      | GHz                      |

| A <sub>V(Diff)</sub>            | Differential Voltage Gain                    |                                                  |     | 38    |      | dB                       |

| S <sub>21</sub>                 | Single-Ended Small-Signal<br>Gain            |                                                  | 26  | 32    |      | dB                       |

#### **Post Amplifier**

Notes:

11. Amplifier in limiting mode. Input is a 200MHz square wave.

12. Deterministic jitter measured using 2.5Gbps K28.5 pattern,  $V_{ID}$  = 10m $V_{PP}$ .

13. Random jitter measured using 2.5Gbps K28.7 pattern,  $V_{ID}$  = 10m $V_{PP}$ .

14. This specification defines electrical hysteresis as 20log (LOS De-Assert/LOS Assert). The ratio between optical hysteresis and electrical hysteresis is found to vary between 1.5 and 2 depending upon the level of received optical power and ROSA characteristics. Based on that ratio, the optical hysteresis corresponding to the electrical hysteresis range 1dB-4.5 dB, shown in the AC characteristics table, will be 0.5dB-3dB Optical Hysteresis.

15. In real world applications, the LOS Release/Assert time can be strongly influenced by the RC time constant of the AC-coupling cap and the 50Ω input termination. To keep this time low, use a decoupling cap with the lowest value that is allowed by the data rate and the number of consecutive identical bits in the application (typical values are in the range of 0.001µF to 1.0µF).

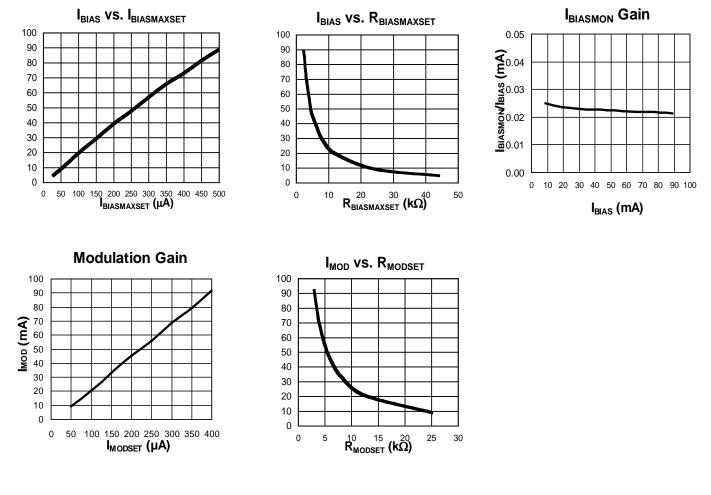

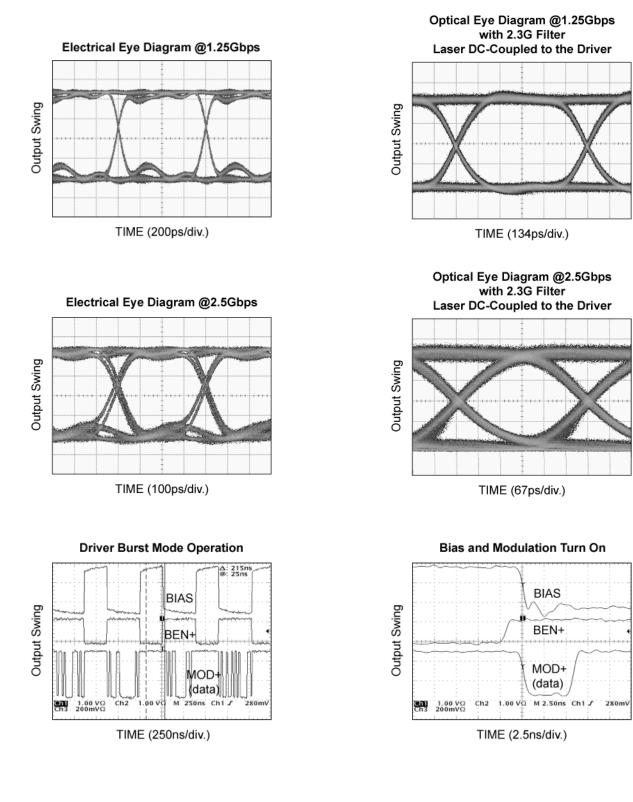

# Typical Characteristics Laser Driver

# **Post Amplifier**

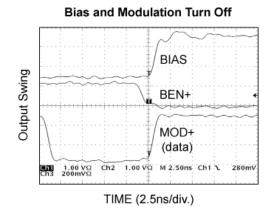

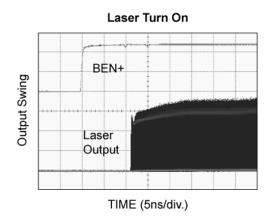

# Functional Characteristics Laser Driver

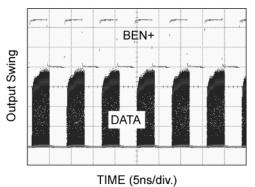

Burst Mode Operation with Laser

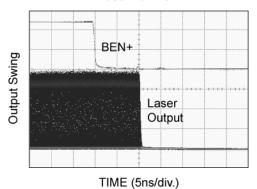

Laser Turn Off

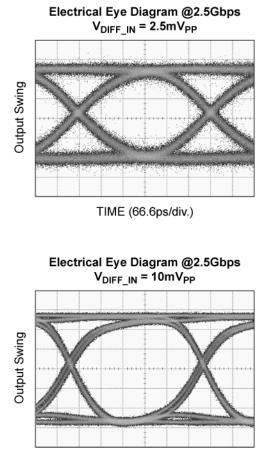

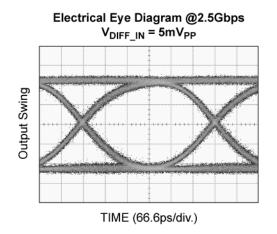

# Functional Characteristics (continued) Post Amplifier

TIME (66.6ps/div.)

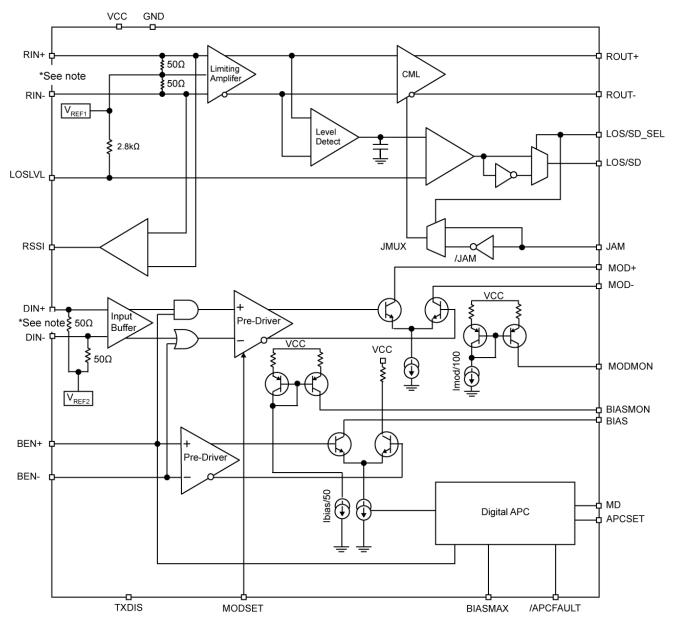

# **Functional Diagram**

\*note: The internal terminations at DIN+, DIN-, RIN+, RIN- apply for SY88236L only. SY88236AL doesn't have internal terminations at those inputs

The SY88236L is shown. For the SY88236AL,  $50\Omega$  terminations should be removed from DIN± and RIN±.

# Functional Description

#### Laser Driver

The laser driver is comprised from a modulator, a bias circuit, and a digital APC loop.

The driver features bias and modulation current monitoring functions, which can be configured for optical power monitoring.

#### BIAS and Modulation Setting

Bias and modulation currents are set by installing resistors from APCSET to ground and from MODSET to ground respectively or by applying a negative current at those pins.  $I_{BIAS}$  variation versus  $R_{BIASMAXSET}$  resistor and  $I_{BIASMAXSET}$ , and  $I_{MOD}$  variation versus  $R_{MODSET}$  resistor and  $I_{MODSET}$  are shown on page 10.

#### BIASMAX

A resistor between BIASMAX pin and ground sets the maximum bias the driver can sink. At normal operation, the bias current tracks the laser optical power through the laser monitoring photodiode and the APC loop to compensate for any power deviation from the nominal value set at the start of operation using APCSET. If for any failure (laser or photodiode degradation, open feedback circuit, etc.) the APC loop keeps increasing the bias current to compensate for the low power indication, the bias current will stop increasing when it reaches BIASMAX value and continues to operate at that maximum value and APCFAULT is asserted.

BIASMAX also sets the bias current when the circuit is operating in the open loop mode.

#### **APC Loop Function**

At start up, with the driver enabled, TXDIS low and BEN+ high, the laser turns ON within a few microseconds and its back facet monitoring photodiode starts to generate a photocurrent proportional to the optical power. The photocurrent is fed back to the MD pin on the driver where it's converted to a voltage. The conversion voltage is compared to APCSET on the driver. At equilibrium, the feedback voltage equals the APCSET voltage and the laser optical power reaches its nominal value. If the laser power deviates from its nominal value, the APC loop brings it back to its nominal setting.

#### APC Loop Failure

The APCFAULT is asserted Low if the bias current reaches BIASMAX or if the APC loop counter reaches its minimum or its maximum counts.

#### Interfacing the Driver with the Laser Diode

As shown on the "Typical Application" drawing, MOD+ pin is connected to the laser cathode through **Q** 10

resistor and MOD- pin is connected to VCC with a 1 $\Omega$  resistor equivalent to 1 $\Omega$  (damping resistor) in series with the laser (equivalent resistor of  $\Omega$ ). The laser can be driven differentially by connecting MOD- to the anode of the laser through  $\Omega 5$  (15 $\Omega$  pull -up removed) and isolating the anode of the laser from VCC with an inductor.

## **Post Amplifier**

The post amplifier detects and amplifies signals with data rates from DC up to 3.2Gbps, and amplitude as small as  $5mV_{PP}$ . To reduce the noise at the output of the post amplifier when the input signal is absent or lower than the minimum detectable level set by  $LOS_{LVL}$ , a JAM pin is provided, which can be connected to LOS/SD output to turn off the output buffer when LOSS/SD is asserted.

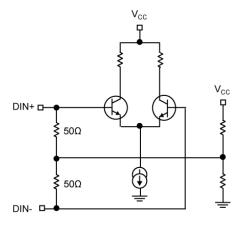

#### Input Amplifier/Buffer

Figure 1-d shows a simplified schematic of the input stage. The high-sensitivity of the input amplifier allows signals as small as  $5mV_{PP}$  to be detected and amplified. The input amplifier allows input signals as large as  $1800mV_{PP}$ . Small input signals below typically  $12mV_{PP}$  are linearly amplified with a typically 38dB differential voltage gain. For input signals larger than  $12mV_{PP}$ , the output signal is limited to typically  $800mV_{PP}$ .

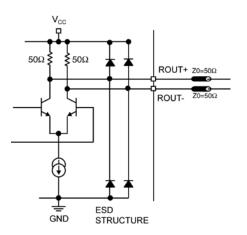

#### Output Buffer

The post amplifier CML output buffer is designed to drive  $50\Omega$  lines and is internally terminated with  $50\Omega$  to V<sub>CC</sub>. Figure 1e shows a simplified schematic of the output stage.

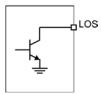

#### Loss-of-Signal

The post amplifier generates a selectable chatter-free loss-of-signal (LOS) or signal detect (SD) open-collector TTL output as shown in Figure 2g. LOS/SD is used to determine that the input amplitude is too small to be considered as a valid input. When the LOSS function is selected (LOS/SD\_SEL=1), LOS/SD asserts high if the input amplitude falls below the threshold set by LOSLVL and de-asserts low otherwise. IF SD function is selected (LOS/SD\_SEL=0), LOS/SD asserts low if the input amplitude falls below the threshold set by LOSLVL and de-asserts high otherwise. LOS/SD can be fed back to the JAM input to maintain output stability under a loss of signal condition. Jam de-asserts low the true output signal without removing the input signals. Typically, 3dB LOS hysteresis is provided to prevent chattering.

#### Loss/Signal Detect Selection

A pin (LOS/SD\_SEL) is provided to select between LOS (set to high) or SD (set to low) function. It also controls the internal circuitry of JAM input to follow LOS/SD selection.

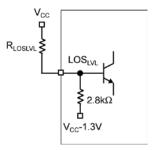

A programmable LOS/SD level set pin (LOS<sub>LVL</sub>) sets the threshold of the input amplitude detection. Connecting an external resistor between  $V_{CC}$  and  $LOS_{LVL}$  sets the voltage at  $LOS_{LVL}$ . This voltage ranges from  $V_{CC}$  to  $V_{CC}$  -1.3V. The external resistor creates a voltage divider between  $V_{CC}$  and  $V_{CC}$ -1.3V, as shown in Figure 2f.

#### Hysteresis

The post amplifier provides typically 3dB LOS electrical hysteresis, which is defined as 20log (VIN<sub>LOS-Assert</sub> / VIN<sub>LOS-De-Assert</sub>). Since the relationship between the voltage out of the ROSA to optical power at its input is linear, the optical hysteresis will be typically half of the electrical hysteresis reported in the datasheet, but in practice, the ratio between electrical and optical hysteresis is found to be within the range 1.5 to 1.8. Thus, 3dB electrical hysteresis will correspond to an optical hysteresis within the range 1.6dB to 2dB.

#### RSSI Pin

The post amplifier has an RSSI (Received Signal Strength) pin, which provides a current proportional to the amplitude of the signal at the input of the post amplifier from the ROSA. Install a resistor between this pin and GND to convert the current into a monitoring voltage proportional to the amplitude of the signal at the input of the post amplifier. The value of the resistor should be selected to keep the voltage at the RSSI pin under its limits of 1.2V to maintain RSSI linearity.

# Input and Output Stages (SY88236L)<sup>(1)</sup>

Figure 1a. Simplified Driver Input Stage<sup>(1)</sup>

Figure 1c. Simplified Driver Output Stage

Figure 1e. Post Amplifier Output Stage

## Note:

1. Applies for SY88236L only. For SY88236AL input terminations need to be removed.

Figure 1b. Simplified BEN Input Stage

Figure 1d. Post Amplifier Input Stage<sup>(1)</sup>

# Interfacing DIN and BEN Inputs to Different Logic Drivers (SY88236L)<sup>(1)</sup>

Figure 2a. Driving DIN and BEN with PECL Outputs<sup>(1)</sup>

Figure 2c. Driving BEN with LVTTL/CMOS Outputs<sup>(1)</sup>

Figure 2e. Driving BEN with Single-Ended LVTTL/CMOS

Figure 2g. LOS Output Structure

#### Note:

1. Applies for SY88236L only. For SY88236AL input terminations need to be added.

Figure 2b. Driving DIN and BEN with CML Outputs<sup>(1)</sup>

Figure 2d. Driving BEN with LVDS Outputs<sup>(1)</sup>

Figure 2f. LOS<sub>LVL</sub> Setting Circuit

# **Package Information**

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2009 Micrel, Incorporated.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331