# Spread Spectrum Frequency Timing Generator

## Features

- Maximized EMI suppression using Cypress's Spread Spectrum technology

- Generates a spread spectrum copy of the provided input

- Integrated loop filter components

- · Operates with a 5V supply

- Low power CMOS design

- Available in 8-pin SOIC (Small Outline Integrated Circuit)

## **Overview**

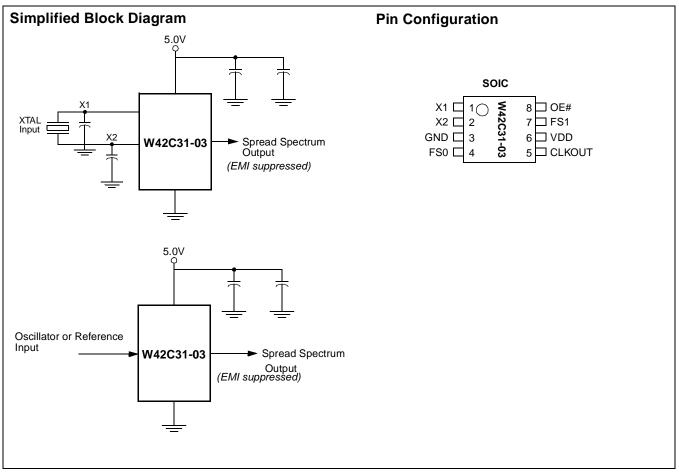

The W42C31-03 incorporates the latest advances in PLL spread spectrum frequency synthesizer techniques. By frequency modulating the output with a low-frequency carrier, EMI is greatly reduced. Use of this technology allows systems to pass increasingly difficult EMI testing without resorting to costly shielding or redesign. In a system, not only is EMI reduced in the various clock lines, but also in all signals which are synchronized to the clock. Therefore, the benefits of using this technology increase with the number of address and data lines in the system. The Simplified Block Diagram shows a simple implementation.

Table 1. Frequency Spread Selection

| W42C | 2C31-03 Oscillator |                             |                                  | Output                       |  |

|------|--------------------|-----------------------------|----------------------------------|------------------------------|--|

| FS1  | FS0                | Input<br>Frequency<br>(MHz) | XTAL Input<br>Frequency<br>(MHz) | Output<br>Frequency<br>(MHz) |  |

| 0    | 0                  | 10 to 20                    | 10 to 20                         | f <sub>IN</sub> ±1.875%      |  |

| 0    | 1                  | 10 to 20                    | 10 to 20                         | f <sub>IN</sub> ±1.0%        |  |

| 1    | 0                  | 20 to 33                    | 20 to 25                         | f <sub>IN</sub> ±1.875%      |  |

| 1    | 1                  | 20 to 33                    | 20 to 25                         | f <sub>IN</sub> -2.0%        |  |

## **Pin Definitions**

| Pin Name | Pin No. | Pin<br>Type | Pin Description                                                                                                                                                                     |  |  |

|----------|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLKOUT   | 5       | 0           | <b>Output Modulated Frequency:</b> Frequency modulated copy of the unmodulated input clock                                                                                          |  |  |

| X1       | 1       | I           | <i>Crystal Connection or External Reference Frequency Input:</i> This pin has dual functions. It may either be connected to an external crystal, or to an external reference clock. |  |  |

| X2       | 2       | I           | Crystal Connection: If using an external reference, this pin must be left unconnected.                                                                                              |  |  |

| OE#      | 8       | I           | <b>Output Enable (Active LOW):</b> This pin three-states the output when HIGH. It has an internal pull-down resistor.                                                               |  |  |

| FS0      | 4       | I           | <i>Frequency Selection Bit 0:</i> This pin selects the frequency spreading characteristic Refer to <i>Table 1</i> . This pin has a pull-up resistor.                                |  |  |

| FS1      | 7       | I           | <i>Frequency Selection Bit 1:</i> This pin selects the frequency range. Refer to <i>Table 1</i> This pin has a pull-up resistor.                                                    |  |  |

| VDD      | 6       | Р           | Power Connection: Connected to 5V power supply.                                                                                                                                     |  |  |

| GND      | 3       | G           | Ground Connection: This should be connected to the common ground plane.                                                                                                             |  |  |

## **Functional Description**

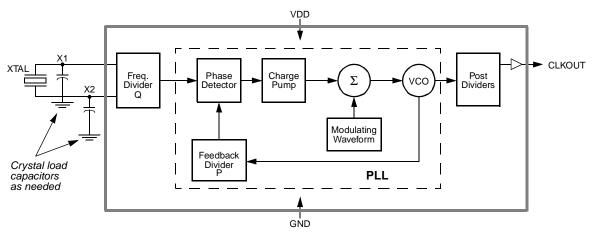

The W42C31-03 uses a phase-locked loop (PLL) to frequency modulate an input clock. The result is an output clock whose frequency is slowly swept over a narrow band near the input signal. The basic circuit topology is shown in Figure 1. An on-chip crystal driver causes the crystal to oscillate at its fundamental. The resulting reference signal is divided by Q and fed to the phase detector. A signal from the VCO is divided by P and fed back to the phase detector also. The PLL will force the frequency of the VCO output signal to change until the divided output signal and the divided reference signal match at the phase detector input. The output frequency is then equal to the ratio of P/Q times the reference frequency. The unique feature of the Spread Spectrum Clock Generator is that a modulating waveform is superimposed at the input to the VCO. This causes the VCO output to be slowly swept across a predetermined frequency band.

Because the modulating frequency is typically 1000 times slower than the fundamental clock, the spread spectrum process has little impact on system performance.

## **Frequency Selection With SSFTG**

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and frequency of the modulating waveform. While the shape and frequency of the modulating waveform are fixed, the modulation percentage may be varied.

Using frequency select bits (FS1:0 pins), various spreading percentages can be chosen (see *Table 1*).

A larger spreading percentage improves EMI reduction. However, large spread percentages may either exceed system maximum frequency ratings or lower the average frequency to a point where performance is affected. For these reasons, spreading percentages between  $\pm 0.5\%$  and  $\pm 2.5\%$  are most common.

The W42C31 features the ability to select from various spread spectrum characteristics. Selections specific to the W42C31-03 are shown in *Table 1*. Other spreading characteristics are available (see separate data sheets) or can be created with a custom mask.

Figure 1. System Block Diagram

# Spread Spectrum Frequency Timing Generation

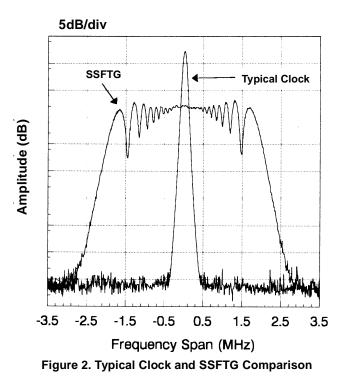

The benefits of using Spread Spectrum Frequency Timing Generation are depicted in *Figure 2*. An EMI emission profile of a clock harmonic is shown.

Contrast the typical clock EMI with the Cypress Spread Spectrum Frequency Timing Generation EMI. Notice the spike in the typical clock. This spike can make systems fail quasi-peak EMI testing. The FCC and other regulatory agencies test for peak emissions. With spread spectrum enabled, the peak energy is much lower (at least 8 dB) because the energy is spread out across a wider bandwidth.

#### **Modulating Waveform**

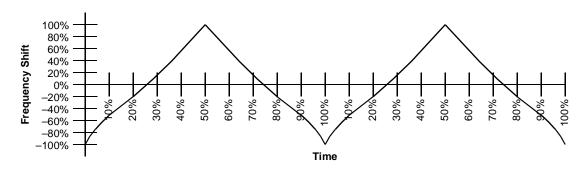

The shape of the modulating waveform is critical to EMI reduction. The modulation scheme used to accomplish the maximum reduction in EMI is shown in *Figure 3*. The period of the modulation is shown as a percentage of the period length along the X axis. The amount that the frequency is varied is shown along the Y axis, also shown as a percentage of the total frequency spread.

Cypress frequency selection tables express the modulation percentage in two ways. The first method displays the spreading frequency band as a percent of the programmed average output frequency, symmetric about the programmed average frequency. This method is always shown using the expression  $f_{Center} \pm X_{MOD}\%$  in the frequency spread selection table.

The second approach is to specify the maximum operating frequency and the spreading band as a percentage of this frequency. The output signal is swept from the lower edge of the band to the maximum frequency. The expression for this approach is  $f_{MAX} - X_{MOD}$ %. Whenever this expression is used, Cypress has taken care to ensure that  $f_{MAX}$  will never be exceeded. This is important in applications where the clock drives components with tight maximum clock speed specifications.

### OE# Pin

An internal pull-down resistor defaults the chip into a mode in which all outputs are active. If OE# goes HIGH, all outputs are three-stated. The chip will not prevent short cycles in a transition from three-state to enabled.

Figure 3. Modulation Waveform Profile

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| Т <sub>В</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>                    | Power Dissipation                      | 0.5          | W    |

# DC Electrical Characteristics: 0°C < $T_A$ < 70°C, $V_{DD}$ = 5V ±10%

| Parameter        | Description                        | Test Condition                               | Min                | Тур | Max                 | Unit |

|------------------|------------------------------------|----------------------------------------------|--------------------|-----|---------------------|------|

| I <sub>DD</sub>  | Supply Current                     |                                              |                    | 18  | 32                  | mA   |

| t <sub>ON</sub>  | Power Up Time                      | First locked clock cycle after<br>Power Good |                    |     | 5                   | ms   |

| V <sub>IL</sub>  | Input Low Voltage                  |                                              |                    |     | 0.15V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input High Voltage                 |                                              | 0.7V <sub>DD</sub> |     |                     | V    |

| V <sub>OL</sub>  | Output Low Voltage                 |                                              |                    |     | 0.4                 | V    |

| V <sub>OH</sub>  | Output High Voltage                |                                              | 2.5                |     |                     | V    |

| IIL              | Input Low Current                  | Note 1                                       |                    |     | -100                | μA   |

| IIH              | Input High Current                 | Note 1                                       |                    |     | 10                  | μA   |

| I <sub>OL</sub>  | Output Low Current                 | @ 0.4V, V <sub>DD</sub> = 5V                 |                    | 24  |                     | mA   |

| I <sub>OH</sub>  | Output High Current                | @ 2.4V, V <sub>DD</sub> = 5V                 |                    | 24  |                     | mA   |

| CI               | Input Capacitance                  | All pins except X1, X2                       |                    |     | 7                   | pF   |

| CL               | Load Capacitance (as seen by XTAL) | Pins X1, X2 <sup>[2]</sup>                   |                    | 17  |                     | pF   |

| R <sub>P</sub>   | Input Pull-Up Resistor             |                                              |                    | 500 |                     | kΩ   |

| Z <sub>OUT</sub> | Clock Output Impedance             |                                              |                    | 20  |                     | Ω    |

# AC Electrical Characteristics: $T_A = 0^{\circ}C$ to +70°C, $V_{DD} = 5V \pm 10\%$

| Symbol            | Parameter              | Test Condition                       | Min | Тур | Max | Unit |

|-------------------|------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>IN</sub>   | Input Frequency        | Input Clock                          | 10  |     | 33  | MHz  |

| f <sub>OUT</sub>  | Output Frequency       |                                      | 10  |     | 33  | MHz  |

| t <sub>R</sub>    | Output Rise Time       | V <sub>DD</sub> , 15-pF load 0.8–2.4 |     | 2   | 5   | ns   |

| t <sub>F</sub>    | Output Fall Time       | V <sub>DD</sub> , 15-pF load 2.4–0.8 |     | 2   | 5   | ns   |

| t <sub>OD</sub>   | Output Duty Cycle      | 15-pF load                           | 45  |     | 55  | %    |

| t <sub>ID</sub>   | Input Duty Cycle       |                                      | 40  |     | 60  | %    |

| t <sub>JCYC</sub> | Jitter, Cycle-to-Cycle |                                      |     |     | 300 | ps   |

|                   | Harmonic Reduction     |                                      | 8   |     |     | dB   |

Notes:

Inputs FS1:0 have a pull-up resistor; Input OE# has a pull-down resistor. Pins X1 and X2 each have a 34-pF capacitance. When used with a XTAL, the two capacitors combined load the crystal with 17 pF. If driving X1 with a reference clock signal, the load capacitance will be 34 pF (typical). 1. 2.

## **Application Information**

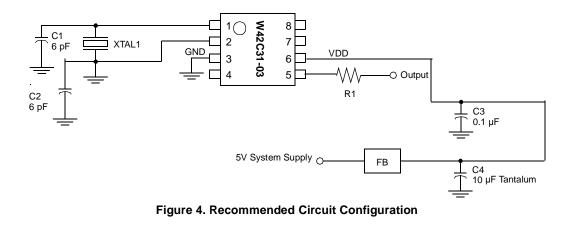

### **Recommended Circuit Configuration**

For optimum performance in system applications the power supply decoupling scheme shown in *Figure 4* should be used.

$V_{DD}$  decoupling is important to both reduce phase jitter and EMI radiation. The 0.1- $\mu$ F decoupling capacitor should be placed as close to the  $V_{DD}$  pin as possible, otherwise the increased trace inductance will negate its decoupling capability.

The 10- $\mu$ F decoupling capacitor shown should be a tantalum type. For further EMI protection, the V<sub>DD</sub> connection can be made via a ferrite bead, as shown.

The 6-pF XTAL load capacitors can be used to raise the integrated 17-pF capacitance up to a total load of 20 pF on the crystal.

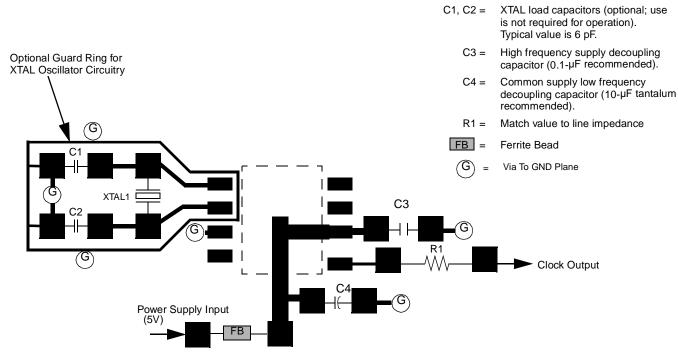

### **Recommended Board Layout**

Figure 5 shows a recommended 2-layer board layout.

Figure 5. Recommended Board Layout (2-Layer Board)

## **Ordering Information**

| Ordering Code | Freq. Mask<br>Code | Package<br>Name | Package Type                 |

|---------------|--------------------|-----------------|------------------------------|

| W42C31        | 03                 | G               | 8-pin Plastic SOIC (150-mil) |

Document #: 38-00802

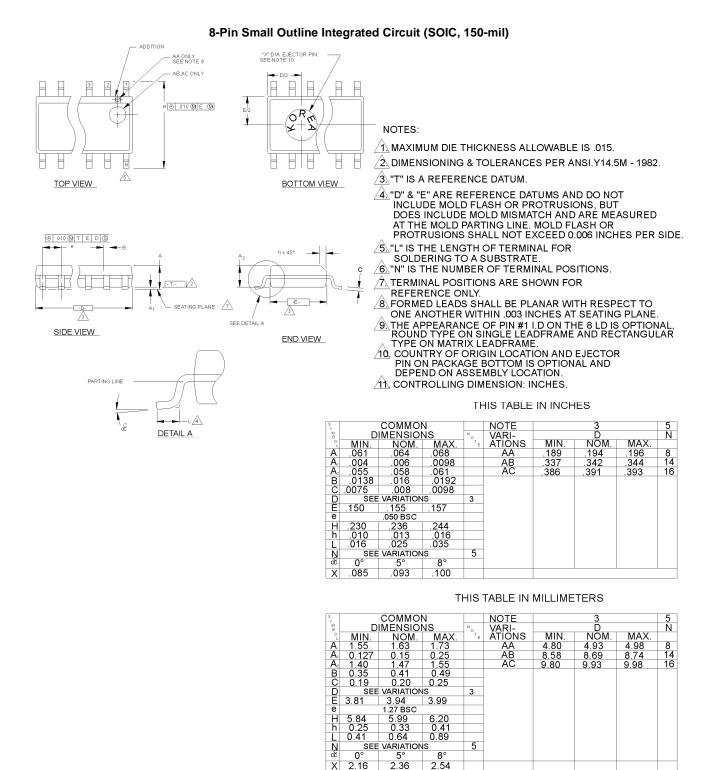

# Package Diagram

© Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

## Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331