# RENESAS

# DATASHEET

# ISL9301

High Input Voltage Charger With Power Path Management

FN6435 Rev 3.00 September 21, 2011

The ISL9301 is a fully integrated high input voltage single-cell Li-ion battery charger with power path management function. This charger performs the CC/CV charge function required by Li-ion batteries. The charger accepts an input voltage up to 28V but is disabled when the input voltage exceeds 10.5V OVP threshold. The 28V rating eliminates the overvoltage protection circuit required in a low-voltage charger. The charge current and the end-of-charge (EOC) current are programmable with external resistors. When the battery voltage is lower than 2.8V, the charger preconditions the battery with 16% of the programmed charge current. When the charge current reduces to the programmable EOC current level during the CV charge phase, the EOC indicator (CHG) will toggle to logic HIGH to indicate the end-of-charge condition. The charger will continue to charge until the user programmed timeout interval has elapsed, then the charger is terminated.

The ISL9301 uses separate power paths to supply the system load and charge the battery. This feature allows the system to immediately operate with a completely discharged battery. This feature also allows the charge to terminate when the battery is full while continuing to supply the system with the input source, thus minimizing unnecessary charge/discharge cycles and improving the battery life.

Two indication pins ( $\overline{PPR}$  and  $\overline{CHG}$ ) allow simple interface to a microprocessor or LEDs.

# **Ordering Information**

| PART<br>NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|-----------------------------------|-----------------|------------------------|----------------------|----------------|

| ISL9301IRZ                        | 9301            | -40 to +85             | 10 Ld 3x3 DFN        | L10.3x3C       |

| ISL9301IRZ-T                      | 9301            | -40 to +85             | 10 Ld 3x3 DFN        | L10.3x3C       |

NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL9301</u>. For more information on MSL, please see Technical Brief <u>TB363</u>.

## Features

- Complete Charger for Single-Cell Li-ion/Polymer Batteries

- Power Path Management Optimize Charge and System Currents

- Intelligent Timeout Interval Based on Actual Charge

Current

- · Integrated Disconnect Switch to Disconnect the Battery

- 1% Charger Output Voltage Accuracy

- Programmable Charge Current

- Programmable End-of-Charge Current

- · Charge Current Thermal Foldback for Thermal Protection

- Trickle Charge for Fully Discharged Batteries

- · 28V Maximum Voltage at VIN pin

- · Power Presence and Charge Indications

- Ambient Temperature Range: -40°C to +85°C

- 10 Ld 3x3 DFN Package

- · Pb-Free (RoHS Compliant)

## Applications

- Mobile Phones

- Blue-Tooth Devices

- PDAs

- MP3 Players

- Stand-Alone Chargers

- · Other Handheld Devices

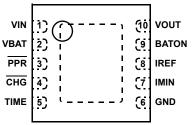

## Pinout

| Absolute Maximum Ratings (Reference to GN | D) |

|-------------------------------------------|----|

|-------------------------------------------|----|

| VIN            | -0.3V to 30V |

|----------------|--------------|

| All other pins | 0.3V to 7V   |

#### **Recommended Operating Conditions**

| Ambient Temperature Range          | 40°C to +85°C   |

|------------------------------------|-----------------|

| Maximum Supply Voltage (VIN Pin)   | 28V             |

| Operating Supply Voltage (VIN Pin) | 4.3V to 10V     |

| Programmed Charge Current          | . 50mA to 450mA |

| Output Current                     | 0mA to 800mA    |

#### **Thermal Information**

| Thermal Resistance (Typical)            | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| DFN Package (Notes 4, 5)                | 40.5                   | 2.5                    |

| Maximum Junction Temperature (Plastic P | ackage)                | +150°C                 |

| Maximum Storage Temperature Range       | 65°                    | 'C to +150°C           |

| Pb-free Reflow Profile                  |                        | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeR | eflow.asp              |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Typical values are tested at VIN = 5V and the ambient temperature at +25°C. Range.  $V_{SUPPLY}$  = ±5V,  $A_V$  = +1,  $R_L$  = 100 $\Omega$ ; Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| PARAMETER                            | SYMBOL              | TEST CONDITIONS                                                       |       | TYP  | MAX   | UNITS |

|--------------------------------------|---------------------|-----------------------------------------------------------------------|-------|------|-------|-------|

| POWER-ON RESET                       | 1                   |                                                                       |       | 1    |       |       |

| Rising POR Threshold                 | V <sub>POR</sub>    | $V_{BAT}$ = 3.0V, use $\overline{PPR}$ to indicate the comparator     | 3.3   | 3.9  | 4.3   | V     |

| Falling POR Threshold                | V <sub>POR</sub>    | output.                                                               |       | 3.6  | 4.15  | V     |

| V <sub>OUT-BAT</sub> OFFSET VOLTAGE  | 1                   |                                                                       |       | 1    |       |       |

| Rising Edge                          | V <sub>OS</sub>     | $V_{BAT}$ = 4.0V, use $\overline{CHG}$ pin to indicate the comparator |       | 110  | 250   | mV    |

| Falling Edge                         | V <sub>OS</sub>     | output (Note 6)                                                       | 10    | 100  | -     | mV    |

| VIN OVERVOLTAGE PROTECTION           | l                   |                                                                       |       | I    |       |       |

| Overvoltage Protection Threshold     | V <sub>OVP</sub>    | Use PPR to indicate the comparator output                             |       | 10.5 | 13    | V     |

| OVP Threshold Hysteresis             |                     |                                                                       | 200   | 400  | 500   | mV    |

| STANDBY CURRENT                      |                     |                                                                       |       | I    |       |       |

| BAT Pin Sink Current                 | ISTANDBY            | Charger disabled or the input is floating                             | -     | -    | 1.0   | μA    |

| BAT Pin Supply Current               | I <sub>VBAT</sub>   | No supply at V <sub>IN</sub> , BATON = HI                             |       | 10   | -     | μA    |

| VIN Pin Supply Current               | I <sub>VIN</sub>    | Charger enabled                                                       |       | 1    | -     | mA    |

| VOLTAGE REGULATION                   |                     |                                                                       |       | I    |       |       |

| Output Voltage                       | V <sub>OUT</sub>    | System current + charge current = 15mA                                |       | 4.50 | 4.60  | V     |

| Output PPM Threshold Voltage         | V <sub>DPPM</sub>   |                                                                       | 4.22  | 4.35 | 4.45  | V     |

| Charger Output Voltage               | VBAT                | Charge current = 10mA                                                 | 4.158 | 4.20 | 4.242 | V     |

| IREF PIN Voltage                     | VIREF               | V <sub>BAT</sub> = 3.8V                                               | 1.165 | 1.20 | 1.245 | V     |

| MOSFET ON-RESISTANCE                 |                     |                                                                       |       | I    |       |       |

| Regulator MOSFET r <sub>DS(ON)</sub> | r <sub>DS(ON)</sub> | V <sub>OUT</sub> = 4.4V, Total current = 0.3A                         | -     | 0.8  | 1.2   | Ω     |

| Charger MOSFET r <sub>DS(ON)</sub>   | r <sub>DS(ON)</sub> | V <sub>BAT</sub> = 3.8V, charge current = 0.2A                        | -     | 0.1  | 0.15  | Ω     |

| RECHARGE THRESHOLD                   | ·                   | ·                                                                     |       |      | •     |       |

| Recharge Voltage Threshold           | V <sub>RECHG</sub>  | Relative to V <sub>BAT</sub>                                          | -200  | -150 | -100  | mV    |

| CURRENT REGULATION (Note 7)          | ·                   | ·                                                                     |       |      |       |       |

| Input Current Limit                  | I <sub>LIM</sub>    | V <sub>OUT</sub> = 4.5V 600                                           |       | 800  | 1200  | mA    |

| Constant Charge Current              | I <sub>CHG</sub>    | R <sub>IREF</sub> = 26.7kΩ, V <sub>BAT</sub> = 2.8V to 4.0V           | 130   | 145  | 160   | mA    |

#### **Electrical Specifications**

Typical values are tested at VIN = 5V and the ambient temperature at +25°C. Range.  $V_{SUPPLY} = \pm 5V$ ,  $A_V = +1$ ,  $R_L = 100\Omega$ ; Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| PARAMETER                                     | SYMBOL              | TEST CONDITIONS                                     | MIN | TYP  | MAX  | UNITS |

|-----------------------------------------------|---------------------|-----------------------------------------------------|-----|------|------|-------|

| Trickle Charge Current                        | I <sub>TRK</sub>    | R <sub>IREF</sub> = 26.7kΩ, V <sub>BAT</sub> = 2.4V | 17  | 23   | 30   | mA    |

| End-of-Charge Current                         | I <sub>MIN</sub>    | $R_{IMIN} = 137 k\Omega$                            | 18  | 23   | 28   | mA    |

| PRECONDITIONING CHARGE THR                    | ESHOLD              |                                                     | I   |      |      |       |

| Preconditioning Charge Threshold<br>Voltage   | V <sub>MIN</sub>    |                                                     | 2.7 | 2.8  | 3.0  | V     |

| Preconditioning Voltage Hysteresis            | V <sub>MINHYS</sub> |                                                     | 40  | 100  | 150  | mV    |

| INTERNAL TEMPERATURE MONIT                    | ORING (Not          | e 8)                                                |     | 1    |      |       |

| Charger Current Thermal Foldback<br>Threshold | T <sub>FOLD</sub>   |                                                     | -   | 115  | -    | °C    |

| OVER-TEMPERATURE PROTECTIO                    | ON (Note 8)         | -                                                   | 1   |      | J    |       |

| Shutdown Rising Threshold                     | T <sub>R</sub>      |                                                     | -   | 142  | -    | °C    |

| Shutdown Falling Threshold                    | Τ <sub>F</sub>      |                                                     | -   | 110  | -    | °C    |

| OSCILLATOR PERIOD                             | 1                   | 1                                                   |     | l    |      |       |

| Oscillator Period                             | tosc                | R <sub>TIME</sub> = 1MΩ                             | 60  | 75   | 90   | μs    |

| LOGIC INPUT AND OUTPUTS                       | 1                   |                                                     | I   |      |      |       |

| BATON Pin Logic Input High                    |                     | V <sub>BAT</sub> < 4.5V                             | 1.1 | -    | -    | V     |

| BATON Pin Logic Input Low                     |                     | V <sub>BAT</sub> > 2V                               | -   | -    | 0.4  | V     |

| BAT Pin Internal Pull-Down<br>Resistance      |                     |                                                     | 800 | 1000 | 1200 | kΩ    |

| PPR, CHG                                      |                     |                                                     | I.  |      | l    | 1     |

| Driving Capability when LOW                   |                     | Pin Voltage = 1V                                    | 10  | -    | -    | mA    |

| Leakage Current When HIGH                     |                     | Pin Voltage = 6.5V                                  | -   | -    | 1    | μA    |

NOTES:

6. The 4.0V  $V_{BAT}$  is selected so that the CHG output can be used as the indication for the offset comparator output indication. If the  $V_{BAT}$  is lower than the POR threshold, no output pin can be used for indication.

7. The input current charge current can be affected by the thermal foldback function if the IC under the test setup cannot dissipate the heat.

8. Limits established by characterization and are not production tested.

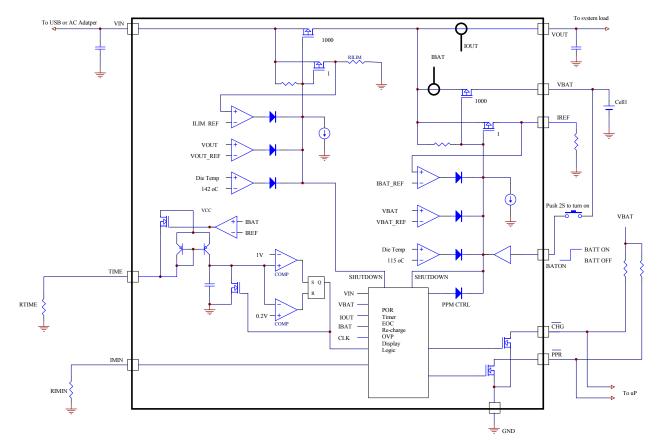

# Block Diagram

# **Pin Descriptions**

VIN - Power input. The absolute maximum input voltage is 28V. A 10µF or larger value capacitor is recommended to be placed very close to the input pin for decoupling purposes. Additional capacitance may be required to provide a stable input voltage.

**VBAT** - Charger output pin. Connect this pin to the battery. A  $1\mu$ F or larger X5R ceramic capacitor is recommended for decoupling and stability purposes. When the BATON pin is pulled to logic LOW or left floating, the VBAT pin is disconnected from the IC.

**TIME** - Timing resistor pin. The TIME pin determines the oscillation period by connecting a timing resistor between this pin and GND. The oscillator also provides a time reference for the charger calculated in Equation 1.

$$t_{OSC} = 75 \times R_{TIME}$$

(µs) (EQ. 1)

Where  $R_{TIME}$  is in M $\Omega$ . The nominal timeout interval is given by Equation 2:

$$t_{\text{TIMEOUT}} = \frac{2^{28} \times t_{\text{OSC}}}{3600}$$

(Hour) (EQ. 2)

Where  $t_{OSC}$  is in seconds. For an  $1M\Omega R_{TIME}$ , the nominal timeout interval is approximately 5.6 hours.

**PPR** - Open-drain power presence indication. The open-drain MOSFET turns on when the input voltage is above the POR threshold but below the OVP threshold and off otherwise. This pin is capable to sink 10mA (minimum) current to drive a LED. The maximum voltage rating for this pin is 7V.

**CHG** - Open-drain charge indication pin. This pin outputs a logic LOW when a charge cycle starts and turns to HIGH when the end-of-charge (EOC) condition is qualified. This pin is capable to sink 10mA min. current to drive an LED. When the charger is disabled, the  $\overline{CHG}$  outputs high impedance.

**IMIN -** End-of-charge (EOC) current program pin. Connect a resistor between this pin and the GND pin to set the EOC current. The EOC current IMIN can be programmed by Equation 3:

$$I_{MIN} = \frac{3151}{R_{IMIN}}$$

(mA) (EQ. 3)

Where  $R_{IMIN}$  is in k $\Omega$ . The programmable range covers 5% (or 10mA, whichever is higher) to 50% of IREF when programmed to less than 5% or 10mA.

**IREF** - Charge-current program and monitoring pin. Connect a resistor between this pin and the GND pin to set the charge current limit determined by Equation 4:

$$I_{\mathsf{REF}} = \frac{3886}{\mathsf{R}_{\mathsf{IREF}}} \tag{mA}$$

Where  $R_{IREF}$  is in k $\Omega$ . The IREF pin voltage also monitors the actual charge current during the entire charge cycle, including the trickle, constant-current, and constant-voltage phases. When disabled,  $V_{IREF}$  = 0V.

**BATON** - Battery disconnect pin. The BATON pin is a logic input pin to allow the disconnection of the battery from the system to eliminate the unwanted drainage current from the battery. There is an internal 1M $\Omega$  pull-down resistor at this pin. Drive to HIGH to connect the battery to the system. When this pin is driven to LOW or left floating, the battery is disconnected from the system.

**VOUT** - Output connection to the system. This pin provides a 4.5V regulated voltage for the system when a valid input power is present. If no valid input is present, and BATON is driven HI, the VOUT pin is connected to VBAT through an internal MOSFET. If no valid input is present and BATON is LOW, the voltage at VOUT pin is zero. A 4.7µF or larger X5R ceramic capacitor is recommended for decoupling and stability purposes.

**EPAD** - Exposed pad. Connect as much copper as possible to this pad either on the component layer or other layers through thermal vias to enhance the thermal performance.

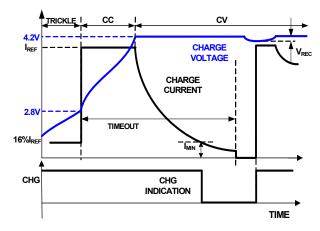

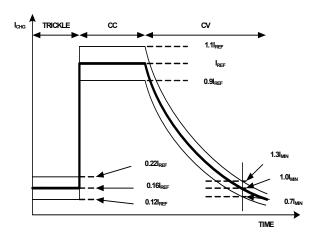

FIGURE 1. TYPICAL CHARGING CYCLE

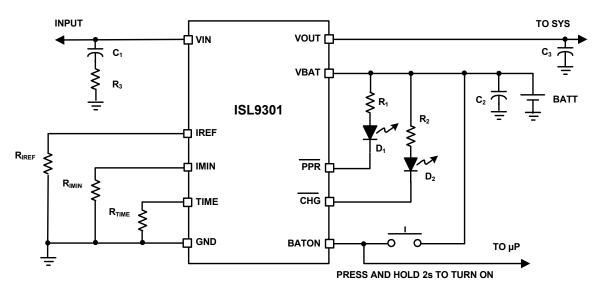

# Typical Application Circuit

| PART                            | DESCRIPTION                                           |  |  |

|---------------------------------|-------------------------------------------------------|--|--|

| C <sub>1</sub>                  | 10µF X5R ceramic capacitor                            |  |  |

| C <sub>2</sub>                  | 1µF X5R ceramic capacitor                             |  |  |

| C3                              | 4.7µF X5R ceramic capacitor                           |  |  |

| R <sub>3</sub>                  | 1Ω, 5% resistor                                       |  |  |

| R <sub>IREF</sub>               | 26.7k $\Omega$ , 1%, for 150mA charge current         |  |  |

| R <sub>IMIN</sub>               | 137kΩ, 1%, for 23mA EOC current                       |  |  |

| R <sub>TIME</sub>               | 1M $\Omega$ , 1% resistor for 75 $\mu$ s clock period |  |  |

| R <sub>1</sub> , R <sub>2</sub> | 470Ω, 5% resistor                                     |  |  |

| D <sub>1</sub> , D <sub>2</sub> | LEDs for indication                                   |  |  |

# Theory of Operation

When a valid input voltage is applied at VIN, the ISL9301 first regulates  $V_{OUT}$  at 4.5V for system power need. In the mean time, if the battery is attached, the ISL9301 also charges the battery while supplying current to the system. When the system exceeds the maximum available current, either limited by the IC or by the input power supply, the charger FET is operated in a reverse mode, i.e. it discharges current to the system instead of charging.

The charger function is similar to other Li-ion battery chargers, i.e. it charges the battery at a constant current (CC) or a constant voltage (CV) depending on the battery terminal voltage. The constant current  $I_{REF}$  is set with the external resistor  $R_{IREF}$ , as shown in the "Typical Application Circuit" on page 6. The constant voltage is fixed at 4.2V. If the battery voltage is below a typical 2.8V trickle charge threshold, the ISL9301 charges the battery with a trickle current (~16% of the programmed constant current) until the battery voltage rises above the trickle charge threshold. When the battery voltage reaches the final voltage of 4.2V,

the charger enters the CV mode and regulates the battery voltage at 4.2V to fully charge the battery without the risk of overcharging. Upon reaching an end-of-charge (EOC) current, the charger indicates the charge completion with the  $\overline{CHG}$  pin, but the charger continues to deliver 4.2V at the VBAT pin until the timeout limit has reached. Figure 1 shows the typical charge profile with the EOC/reset events.

The EOC current level IMIN is programmable with the external resistor R<sub>IMIN</sub>. The CHG signal turns to LO when the trickle charge starts and rises to HIGH at an EOC event. After the EOC is reached, the CHG status is latched at HI. The CHG status will be reset to logic LO when the V<sub>BAT</sub> voltage drops to below the recharge threshold (4.05V), as shown in Figure 1.

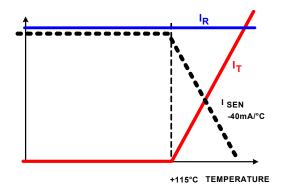

A thermal foldback function reduces the charge current anytime when the die temperature reaches typically +115°C. This function guarantees safe operation when the printed-circuit board (PCB) is not capable of dissipating the heat generated by the linear charger.

The ISL9301 accepts an input voltage up to 28V but will be disabled when the input voltage exceeds the OVP threshold, minimum 10V, to protect against unqualified or faulty AC adapters.

## **PPR** Indication

The  $\overrightarrow{PPR}$  pin is an open-drain output to indicate the presence of the AC adapter. Whenever the input voltage is higher than the POR threshold, the  $\overrightarrow{PPR}$  pin turns on the internal open-drain MOSFET to indicate a logic LOW signal. When the internal open-drain FET is turned off, the  $\overrightarrow{PPR}$  pin should leak less than 1µA current. When turned on, the  $\overrightarrow{PPR}$  pin should be able to sink at least 10mA current under all operating conditions.

The PPR pin can be used to drive an LED (see "Typical Application Circuit" on page 6) or to interface with a microprocessor.

#### Power-Good Range

The power-good range is defined by the following three conditions:

- 1.  $V_{IN} > V_{POR}$

- 2. V<sub>IN</sub> V<sub>OUT</sub> > V<sub>OS</sub>

- 3.  $V_{IN} < V_{OVP}$

where VOS is the offset voltage for the input and output voltage comparator and the VOVP is the overvoltage protection threshold given in the "Electrical Specifications" beginning on page 2. All V<sub>POR</sub>, V<sub>OS</sub>, and V<sub>OVP</sub> have hysteresis. The IC will not deliver any output if the input voltage is not in the power-good range.

## CHG Indication

The CHG is an open-drain output. The open drain FET turns on when the charger starts to charge and turns off when the EOC condition is qualified. Once the EOC condition is qualified, the CHG signal is latched in off state. The EOC condition is qualified when both of the following conditions are satisfied:

- 1. V<sub>BAT</sub> > V<sub>RECHG</sub>

- 2.  $I_{CHG} < I_{MIN}$

The  $\overline{CHG}$  indication will not be turned on again until a recharge condition is qualified. A recharge condition is reached under one of the three conditions:

- 1. Input power being re-cycled

- 2. A recharge cycle starts when the battery voltage drops below the recharge threshold

The  $\overline{CHG}$  signal can be interfaced either with a microprocessor GPIO or a LED for indication. A de-glitch delay of 1ms for both edges is required to prevent nuisance triggering due to some transient conditions.

#### Charge Termination, Recharge and Timeout

When an EOC condition is reached, the  $\overline{CHG}$  pin changes to logic HI to indicate the end-of-charge. However the charger continues to deliver current to the battery until the timeout interval has elapsed, then the charging will be terminated. The setting of the timeout interval is described in "Intelligent Timer" on page 8. When a recharge condition is met after a timeout event, the timer will be reset to zero and the charging re-starts.

In the event when the timeout interval has elapsed before the EOC condition is reached, a timeout fault condition is triggered. The timeout fault condition is indicated by the CHG pin being toggled between HI and LO every 3s ( $R_{TIME} = 1M\Omega$ ). The timeout fault condition can be cleared by removing and reapplying the input power to the IC.

Under the EOC, timeout and timeout fault conditions, the power delivery to  $V_{OUT}$  is not impacted. The battery continues to supply current to VOUT if needed, as described in "Dynamic Power Path Management" on page 8.

## **Battery Disconnection**

The BATON pin provides an option for disconnection of the battery from the system if battery power is not needed and no power source is applied at VIN. The disconnection will prevent the IC leakage current from draining the battery for an extended period of time. To reconnect the battery, pull the BATON pin to logic HI for 2s. Once the system is powered on, the host micro process will send a logic signal to keep BATON at logic HI level. The BATON pin has a  $1M\Omega$  internal pull-down resistor thus, when left floating, the input is equivalent to a logic LOW state. The logic threshold levels are given in the "Electrical Specifications" table starting on page 2.

## **BATON Interlock**

When a valid voltage source is applied at  $V_{IN}$ , the BATON function is disabled. This prevents the battery from being connected to a 4.5V regulated voltage source and generating a large circulating current. If the  $V_{IN}$  supply is removed, the BATON function will resume immediately to allow the battery to supply the system.

## **IREF Pin Function**

The IREF pin has the two functions as described in "Pin Descriptions" on page 4. When setting the fast charge current, the charge current is trimmed to have 10% accuracy at 145mA, excluding the programming resistor error. The percent error decreases as the set charge current is higher but increases as the set charge current is lower than 145mA. The trickle charge current is 16% of the programmed fast charge current.

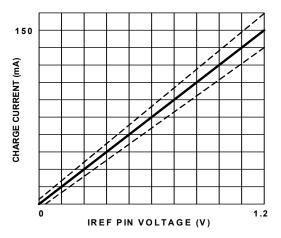

When monitoring the charge current, the accuracy of the IREF pin voltage vs the actual charge current has the same accuracy as the gain from the IREF pin current to the actual charge current. The IREF pin voltage vs the charge current

when  $I_{REF}$  is set to 145mA is shown in Figure 2. Figure 3 shows a typical time domain charge current curve vs time and its accuracy limits for a complete cycle. The accuracy is compared against the voltage on the IREF pin. Thermal foldback may affect the charge current curve as well as the accuracy.

FIGURE 2. IREF PIN VOLTAGE vs CHARGE CURRENT (IREF IS SET TO 150mA. THE DOTTED LINES SHOW THE UPPER AND LOWER LIMITS OF THE TOLERANCE)

#### Dynamic Power Path Management

The power path management function of the ISL9301 controls the charge current and the system current when charging with system load. This is based on the available input current, which is either limited by the IC (800mA) or by the input power source, whichever is smaller. When the output voltage drops to the DPPM threshold (4.35V typical), the dynamic power path management starts to function. The DPPM control will first allocate the available current to the system load, using the remaining current to charge the battery. This is achieved by dynamically reducing the charge

current until V<sub>OUT</sub> is regulated. In the event that the system needs more than the available current, V<sub>OUT</sub> will continue to drop. When V<sub>OUT</sub> drops to below the battery voltage, the DPPM control will turn on the charge control FET, allowing the battery to supply current to the system load. Thus the battery may be charged at a current smaller than the programmed constant current.

#### Intelligent Timer

The internal timer in the ISL9301 provides a time reference for the maximum charge time limit. The nominal clock cycle for the reference time is set by the external resistor connected between the TIME pin and GND and is given by Equation 1.

The nominal maximum charge time interval is calculated based on the assumption that the programmed charge current is always available during the entire charging cycle. However, due to the PPM control or due to the current limit of the input source, or thermal foldback, the actual charge current maybe reduced during the constant current charge period. Under such conditions, the Intelligent Timer control will increase the timeout interval accordingly to allow approximately the same mAh product as the original timeout interval at the programmed current.

#### Thermal Foldback

The thermal foldback function starts to reduce the charge current when the internal temperature reaches a typical value of +115°C. When thermal foldback is encountered, the charge current will be reduced to a value where the die temperature stops rising.

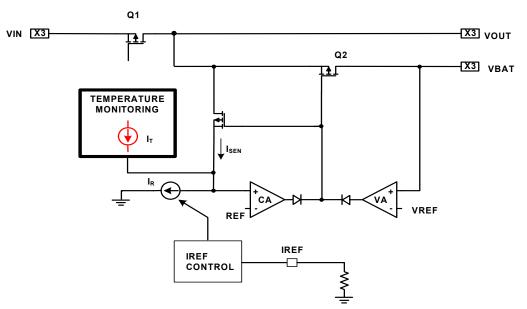

Figure 5 shows the thermal foldback operation whereas the current signals at the summing node of the current error amplifier CA are shown in Figure 4. I<sub>R</sub> is the reference. I<sub>T</sub> is the temperature tracking current generated from the Temperature Monitoring block. The I<sub>T</sub> has no impact on the charge current until the internal temperature reaches approximately +115°C; then I<sub>T</sub> starts to rise. In the meantime, as I<sub>T</sub> rises, I<sub>SEN</sub> will fall at the same rate (as the sum is a constant current IR). As a result, the charging current, which is proportional to I<sub>SEN</sub>, also decreases, keeping the die temperature constant at +115°C.

The system output current, however, is not impacted by the thermal foldback. Thus, when the charge current is reduced to zero, if the die temperature still rises, the IC will shut down to prevent damage to the IC.

FIGURE 4. CHARGE CURRENT THERMAL FOLDBACK CIRCUIT

FIGURE 5. CHARGE CURRENT FOLDBACK

# Applications Information

## Input Bypass Capacitor

The input capacitor is required to suppress the power supply transient response during transitions. Typically, a  $10\mu$ F or larger capacitor should be sufficient to suppress the power supply noise.

Due to the inductance of the power leads of the wall adapter or USB source, the input capacitor type must be properly selected to prevent high voltage transient during a hot-plug event. A tantalum capacitor is a good choice for its high ESR, providing damping to the voltage transient. Multi-layer ceramic capacitors, however, have a very low ESR and hence when chosen as input capacitor, a 1 $\Omega$  series resistor must be used (as shown in the "Typical Application Circuit" on page 6) to provide adequate damping.

## VOUT and VBAT Capacitor Selection

The criteria for selecting the capacitor at the VOUT and VBAT pins is to maintain the stability as well as to bypass any transient load current. The recommended capacitance is a  $4.7\mu$ F X5R ceramic capacitor for VOUT and  $1\mu$ F for VBAT. The actual capacitance connected to the output is dependent on the actual application requirement.

## Layout Guidance

The ISL9301 uses a thermally-enhanced DFN package that has an exposed thermal pad at the bottom side of the package. The layout should connect as much as possible to copper on the exposed pad. Typically, the component layer is more effective in dissipating heat. The thermal impedance can be further reduced by using other layers of copper connecting to the exposed pad through a thermal via array. Each thermal via is recommended to have 0.3mm diameter and 1mm distance from other thermal vias.

## Input Power Sources

The input power source is typically a well-regulated wall cube with 1m length wire or a USB port. The input voltage ranges from 4.3V to 10V. The ISL9301 can withstand up to 28V on the input without damaging the IC. If the input voltage is higher than the OVP threshold, the IC is disabled.

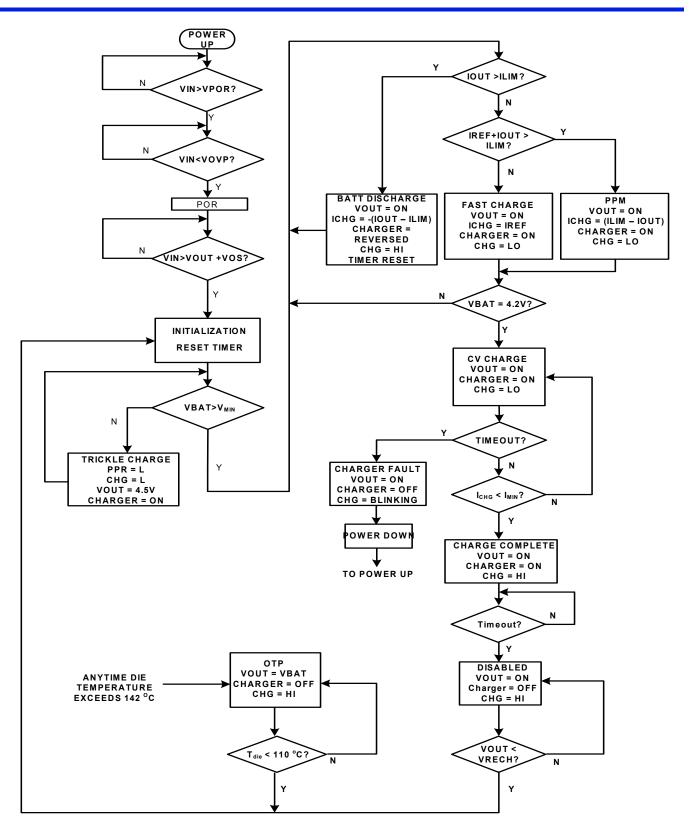

## State Diagram

The state diagram is shown in Figure 6. There are 8 states to cover all the operation modes, including the Trickle Charge, Batt Discharge, PPM, CV Charge, Charge Fault, Charge Complete, Disabled and OTP states.

The IC starts with a trickle charge or constant current charge state depending on V<sub>BAT</sub> when input power is applied. In the Trickle Charge state, the  $\overline{\text{PPR}}$  is LO and the  $\overline{\text{CHG}}$  is LO,

$V_{\mbox{OUT}}$  is regulated at 4.5V, the charger is ON, delivering a trickle charge current.

The IC moves to a fast charge constant current mode when  $V_{BAT}$  reaches the  $V_{MIN}$  threshold. There are 3 possible states in this mode depending on the output current. When the sum of the output current and the fast charge current is smaller than the input current limit, the IC enters the Fast Charge state with the charge current set by R<sub>IREF</sub>. When the output current limit, the IC enters than the input current limit, the IC enters the sum of output current limit, the IC will enter the PPM mode, where the charging current is reduced to a point such that the sum of output current and the charging current equals to the input current limit. If the output current by itself is greater than the input current limit, the IC enters the Battery Discharge state, where the battery is discharged to the system to supply a part of the output demand.

When the battery voltage reaches 4.2V, the IC enters the CV Charge state, where  $\overline{PPR}$  is LO,  $\overline{CHG}$  is LO and  $V_{OUT}$  is regulated at 4.5V. The battery is being charged at a constant voltage while the charging current decreases.

When the charging current is reduced to the IMIN threshold, the IC enters a Charge Complete state, where  $\overrightarrow{PPR}$  is LO,  $\overrightarrow{CHG}$  is HI,  $V_{OUT}$  is regulated at 4.5V and the charger continues to charge the battery.

When the timeout interval has elapsed after the Charge Complete state, the IC will enter the Disabled state, where the  $\overrightarrow{PPR}$  is LO,  $\overrightarrow{CHG}$  is HI,  $V_{OUT}$  is regulated at 4.5V and the charger is OFF. After the Charge Complete state, if VBAT is below the re-charge threshold, the IC will re-initialize and start a new cycle.

If the timeout limit is reached before the Charge Complete state, the IC enters the Charger Fault state, where PPR is LO, CHG is blinking, VOUT is regulated at 4.5V and the charger is OFF. This state is latched until the input power is removed and re-applied to start a new cycle.

Any time during the operation, if the die temperature reaches the OTP threshold, the IC will enter the OTP state, where  $\overrightarrow{PPR}$  is LO,  $\overrightarrow{CHG}$  is HI, and the charger is OFF. VOUT is disconnected from VIN and connected to VBAT internally to maintain system power need.

# Summary of Output States

The output states under various fault conditions are summarized in Table 1.

| OTP | OVP | BATON | M1         | M2       |

|-----|-----|-------|------------|----------|

| Y   | Y   | Н     | OFF        | ON       |

| Y   | Ν   | Н     | OFF        | ON       |

| Ν   | Y   | Н     | OFF        | ON       |

| Y   | Y   | L     | OFF        | OFF      |

| Y   | Ν   | L     | OFF        | OFF      |

| Ν   | Y   | L     | OFF        | OFF      |

| N   | Ν   | Х     | Regulating | Charging |

NOTES: 1. BATON: BATON Pin

2. OVP: Input Overvoltage Protection

3. OTP: Over-Temperature Protection

4. M1: Output Path MOSFET

5. M2: Battery Path MOSFET

© Copyright Intersil Americas LLC 2008-2011. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6435 Rev 3.00 September 21, 2011

FIGURE 6. STATE DIAGRAM

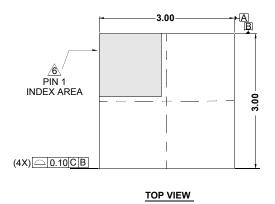

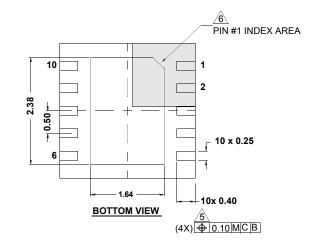

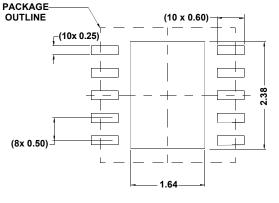

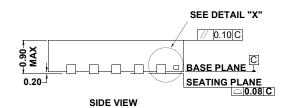

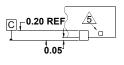

# Package Outline Drawing

#### L10.3x3C

10 LEAD DUAL FLAT PACKAGE (DFN) Rev 2, 09/09

TYPICAL RECOMMENDED LAND PATTERN

DETAIL "X"

- NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.18mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.

- 7. COMPLAINT TO JEDEC MO-229-WEED-3 except for E-PAD dimensions.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331