# I<sup>2</sup>C-Compatible, 256-Position Digital Potentiometers

### **Data Sheet**

### FEATURES

256 positions 10 kΩ, 100 kΩ, 1 MΩ Low temperature coefficient: 30 ppm/°C Internal power on midscale preset Single-supply 2.7 V to 5.5 V or dual-supply ±2.7 V for ac or bipolar operation I<sup>2</sup>C-compatible interface with readback capability Extra programmable logic outputs Self-contained shutdown feature Extended temperature range: -40°C to +105°C

#### **APPLICATIONS**

Multimedia, video, and audio Communications Mechanical potentiometer replacement Instrumentation: gain, offset adjustment Programmable voltage-to-current conversion Line impedance matching

## AD5241/AD5242

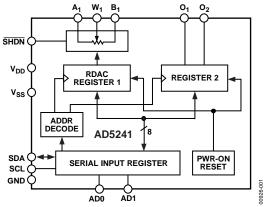

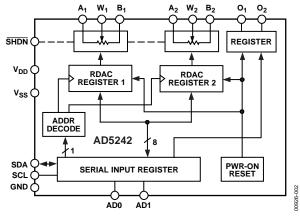

### FUNCTIONAL BLOCK DIAGRAM

Figure 1. AD5241 Functional Block Diagram

Figure 2. AD5242 Functional Block Diagram

#### **GENERAL DESCRIPTION**

The AD5241/AD5242 provide a single-/dual-channel, 256position, digitally controlled variable resistor (VR) device. These devices perform the same electronic adjustment function as a potentiometer, trimmer, or variable resistor. Each VR offers a completely programmable value of resistance between the A terminal and the wiper, or the B terminal and the wiper. For the AD5242, the fixed A-to-B terminal resistance of 10 k $\Omega$ , 100 k $\Omega$ , or 1 M $\Omega$  has a 1% channel-to-channel matching tolerance. The nominal temperature coefficient of both parts is 30 ppm/°C. Wiper position programming defaults to midscale at system power on. When powered, the VR wiper position is programmed by an I<sup>2</sup>C-compatible, 2-wire serial data interface. Both parts have two extra programmable logic outputs available that enable users to drive digital loads, logic gates, LED drivers, and analog switches in their system.

The AD5241/AD5242 are available in surface-mount, 14-lead SOIC and 16-lead SOIC packages and, for ultracompact solutions, 14-lead TSSOP and 16-lead TSSOP packages. All parts are guaranteed to operate over the extended temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

Rev. D Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2001–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 | 1 |

| Functional Block Diagram                     | 1 |

| General Description                          | 1 |

| Revision History                             | 2 |

| Specifications                               | 3 |

| 10 kΩ, 100 kΩ, 1 MΩ Version                  | 3 |

| Timing Diagrams                              | 5 |

| Absolute Maximum Ratings                     | 6 |

| ESD Caution                                  | 6 |

| Pin Configurations and Function Descriptions | 7 |

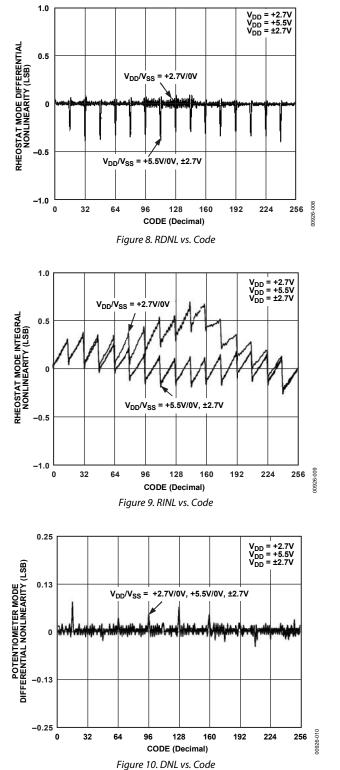

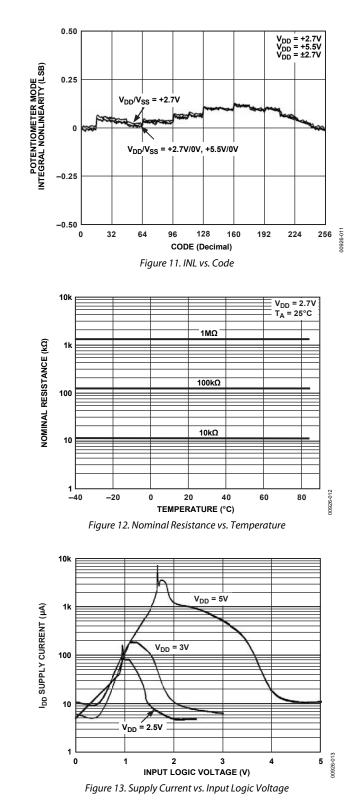

| Typical Performance Characteristics          | 8 |

### **REVISION HISTORY**

| 6/15—Rev. C to Rev. D       |

|-----------------------------|

| Changes to Ordering Guide18 |

#### 12/09—Rev. B to Rev. C

| Changes to Features Section                                              | 1  |

|--------------------------------------------------------------------------|----|

| Changes to 10 k $\Omega$ , 100 k $\Omega$ , 1 M $\Omega$ Version Section | 3  |

| Changes to Table 3                                                       | 6  |

| Deleted Digital Potentiometer Selection Guide Section                    | 14 |

| Changed Self-Contained Shutdown Function Section to                      |    |

| Shutdown Function Section                                                | 15 |

| Changes to Shutdown Function Section                                     | 15 |

| Changes to Ordering Guide                                                | 18 |

### 8/02—Rev. A to Rev. B

| Additions to Features 1                                    |

|------------------------------------------------------------|

| Changes to General Description 1                           |

| Changes to Specifications                                  |

| Changes to Absolute Maximum Ratings 4                      |

| Additions to Ordering Guide 4                              |

| Changes to TPC 8 and TPC 9 8                               |

| Changes to Readback RDAC Value Section 11                  |

| Changes to Additional Programmable Logic Output Section 11 |

| Added Self-Contained Shutdown Section                      |

| Added Figure 812                                           |

| Changes to Digital Potentiometer Selection Guide 14        |

| Test Circuits                           | 11 |

|-----------------------------------------|----|

| Theory of Operation                     |    |

| Programming the Variable Resistor       |    |

| Programming the Potentiometer Divider   |    |

| Digital Interface                       |    |

| Readback RDAC Value                     | 14 |

| Multiple Devices on One Bus             | 14 |

| Level-Shift for Bidirectional Interface | 14 |

| Additional Programmable Logic Output    | 15 |

| Shutdown Function                       | 15 |

| Outline Dimensions                      | 16 |

| Ordering Guide                          |    |

|                                         |    |

### 2/02—Rev. 0 to Rev. A

| Edits to Features                                | 1 |

|--------------------------------------------------|---|

| Edits to Functional Block Diagrams               | 1 |

| Edits to Absolute Maximum Ratings                |   |

| Changes to Ordering Guide                        | 4 |

| Edits to Pin Function Descriptions               | 5 |

| Edits to Figures 1, 2, 3                         | 6 |

| Added Readback RDAC Value Section, Additional    |   |

| Programmable Logic Output Section, and Figure 7; |   |

| Renumbered Sequentially                          |   |

| Changes to Digital Potentiometer Selection Guide |   |

### SPECIFICATIONS 10 kΩ, 100 kΩ, 1 MΩ VERSION

$V_{\text{DD}}$  = 2.7 V to 5.5 V,  $V_{\text{A}}$  =  $V_{\text{DD}},$   $V_{\text{B}}$  = 0 V,  $-40^{\circ}C < T_{\text{A}} < +105^{\circ}C$ , unless otherwise noted.

Table 1.

| Parameter                                                                           | Symbol                                           | Conditions                                                                                                            | Min                 | Typ <sup>1</sup> | Мах                  | Unit   |

|-------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|------------------|----------------------|--------|

| DC CHARACTERISTICS, RHEOSTAT MODE                                                   |                                                  |                                                                                                                       |                     | 71               | -                    |        |

| (SPECIFICATIONS APPLY TO ALL VRs)                                                   |                                                  |                                                                                                                       |                     |                  |                      |        |

| Resolution                                                                          | Ν                                                |                                                                                                                       | 8                   |                  |                      | Bits   |

| Resistor Differential Nonlinearity <sup>2</sup>                                     | R-DNL                                            | $R_{WB}$ , $V_A$ = no connect                                                                                         | -1                  | ±0.4             | +1                   | LSB    |

| Resistor Integral Nonlinearity <sup>2</sup>                                         | R-INL                                            | $R_{WB}$ , $V_A$ = no connect                                                                                         | -2                  | ±0.5             | +2                   | LSB    |

| Nominal Resistor Tolerance                                                          | $\Delta R_{AB}/R_{AB}$                           | $T_A = 25^{\circ}C$ , $R_{AB} = 10 \text{ k}\Omega$                                                                   | -30                 |                  | +30                  | %      |

|                                                                                     |                                                  | $ \begin{array}{l} T_{A}=25^{\circ}\text{C},\\ R_{AB}=100\ \text{k}\Omega/1\ \text{M}\Omega \end{array} \end{array} $ | -30                 |                  | +50                  | %      |

| Resistance Temperature Coefficient                                                  | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^{6}$  | V <sub>AB</sub> = V <sub>DD</sub> , wiper = no connect                                                                |                     | 30               |                      | ppm/°C |

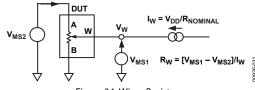

| Wiper Resistance                                                                    | Rw                                               | $I_W = V_{DD}/R$                                                                                                      |                     | 60               | 120                  | Ω      |

| DC CHARACTERISTICS, POTENTIOMETER DIVIDER<br>MODE (SPECIFICATIONS APPLY TO ALL VRs) |                                                  |                                                                                                                       |                     |                  |                      |        |

| Resolution                                                                          | Ν                                                |                                                                                                                       | 8                   |                  |                      | Bits   |

| Differential Nonlinearity <sup>3</sup>                                              | DNL                                              |                                                                                                                       | -1                  | ±0.4             | +1                   | LSB    |

| Integral Nonlinearity <sup>3</sup>                                                  | INL                                              |                                                                                                                       | -2                  | ±0.5             | +2                   | LSB    |

| Voltage Divider Temperature Coefficient                                             | $(\Delta V_w/V_w)/\Delta T \times 10^6$          | Code = 0x80                                                                                                           |                     | 5                |                      | ppm/°C |

| Full-Scale Error                                                                    | Vwese                                            | Code = 0xFF                                                                                                           | -1                  | -0.5             | 0                    | LSB    |

| Zero-Scale Error                                                                    | V <sub>WZSE</sub>                                | Code = 0x00                                                                                                           | 0                   | 0.5              | 1                    | LSB    |

| RESISTOR TERMINALS                                                                  |                                                  |                                                                                                                       | -                   |                  | -                    |        |

| Voltage Range <sup>4</sup>                                                          | V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> |                                                                                                                       | V <sub>ss</sub>     |                  | V <sub>DD</sub>      | v      |

| Capacitance (A, B) <sup>5</sup>                                                     | C <sub>A</sub> , C <sub>B</sub>                  | f = 1 MHz, measured<br>to GND, code = 0x80                                                                            |                     | 45               |                      | pF     |

| Capacitance (W) <sup>5</sup>                                                        | Cw                                               | f = 1 MHz, measured<br>to GND, code = 0x80                                                                            |                     | 60               |                      | pF     |

| Common-Mode Leakage                                                                 | Ісм                                              | $V_A = V_B = V_W$                                                                                                     |                     | 1                |                      | nA     |

| DIGITAL INPUTS                                                                      |                                                  |                                                                                                                       |                     |                  |                      |        |

| Input Logic High (SDA and SCL)                                                      | VIH                                              |                                                                                                                       | $0.7 \times V_{DD}$ |                  | $V_{DD} + 0.5 V$     | V      |

| Input Logic Low (SDA and SCL)                                                       | VIL                                              |                                                                                                                       | -0.5                |                  | $+0.3 \times V_{DD}$ | V      |

| Input Logic High (AD0 and AD1)                                                      | VIH                                              | $V_{DD} = 5 V$                                                                                                        | 2.4                 |                  | V <sub>DD</sub>      | V      |

| Input Logic Low (AD0 and AD1)                                                       | VIL                                              | $V_{DD} = 5 V$                                                                                                        | 0                   |                  | 0.8                  | v      |

| Input Logic High                                                                    | VIH                                              | $V_{DD} = 3 V$                                                                                                        | 2.1                 |                  | V <sub>DD</sub>      | v      |

| Input Logic Low                                                                     | VIL                                              | $V_{DD} = 3 V$                                                                                                        | 0                   |                  | 0.6                  | v      |

| Input Current                                                                       | lı.                                              | $V_{\rm H} = 5  \text{V} \text{ or } V_{\rm IL} = \text{GND}$                                                         |                     |                  | 1                    | μA     |

| Input Capacitance⁵                                                                  | C <sub>IL</sub>                                  |                                                                                                                       |                     | 3                |                      | pF     |

| DIGITAL OUTPUT                                                                      | VoL                                              | $I_{OL} = 3 \text{ mA}$                                                                                               |                     |                  | 0.4                  | V      |

| Output Logic Low (SDA)                                                              | V <sub>OL</sub>                                  | $I_{OL} = 6 \text{ mA}$                                                                                               |                     |                  | 0.6                  | V      |

| Output Logic Low ( $O_1$ and $O_2$ )                                                | Vol                                              | $I_{SINK} = 1.6 \text{ mA}$                                                                                           |                     |                  | 0.4                  | v      |

| Output Logic High ( $O_1$ and $O_2$ )                                               | Vон                                              | $I_{SOURCE} = 40 \ \mu A$                                                                                             | 4                   |                  |                      | v      |

| Three-State Leakage Current (SDA)                                                   | loz                                              | $V_{IH} = 5 V \text{ or } V_{IL} = GND$                                                                               |                     |                  | ±1                   | μA     |

| Output Capacitance <sup>5</sup>                                                     | Coz                                              |                                                                                                                       |                     | 3                | 8                    | pF     |

| POWER SUPPLIES                                                                      |                                                  |                                                                                                                       |                     | -                | -                    | 1-     |

| Power Single-Supply Range                                                           | V <sub>DD RANGE</sub>                            | $V_{SS} = 0 V$                                                                                                        | 2.7                 |                  | 5.5                  | v      |

| Power Dual-Supply Range                                                             | VDD/VSS RANGE                                    |                                                                                                                       | ±2.3                |                  | ±2.7                 | v      |

| Positive Supply Current                                                             |                                                  | $V_{IH} = 5 V \text{ or } V_{IL} = GND$                                                                               |                     | 0.1              | 50                   | μA     |

| Negative Supply Current                                                             | lss                                              | $V_{SS} = -2.5 \text{ V}, V_{DD} = +2.5 \text{ V}$                                                                    |                     | +0.1             | -50                  | μΑ     |

| Power Dissipation <sup>6</sup>                                                      | P <sub>DISS</sub>                                | $V_{IH} = 5 V \text{ or } V_{IL} = GND,$<br>$V_{DD} = 5 V$                                                            |                     | 0.5              | 250                  | μW     |

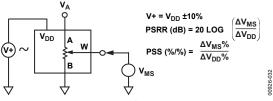

| Power Supply Sensitivity                                                            | PSS                                              |                                                                                                                       | -0.01               | +0.002           | +0.01                | %/%    |

| Parameter                                                                   | Symbol                   | Conditions                                                                   | Min | Typ¹  | Max | Unit  |

|-----------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|-----|-------|-----|-------|

| DYNAMIC CHARACTERISTICS <sup>5, 7, 8</sup>                                  |                          |                                                                              |     |       |     |       |

| –3 dB Bandwidth                                                             | BW_10 kΩ                 | $R_{AB} = 10 \text{ k}\Omega$ , code = 0x80                                  |     | 650   |     | kHz   |

|                                                                             | BW_100 kΩ                | $R_{AB} = 100 \text{ k}\Omega, \text{ code} = 0x80$                          |     | 69    |     | kHz   |

|                                                                             | BW_1 MΩ                  | $R_{AB} = 1 M\Omega$ , code = 0x80                                           |     | 6     |     | kHz   |

| Total Harmonic Distortion                                                   | THDw                     | $V_A = 1 V rms + 2 V dc,$<br>$V_B = 2 V dc, f = 1 kHz$                       |     | 0.005 |     | %     |

| V <sub>w</sub> Settling Time                                                | ts                       | $V_{A} = V_{DD}, V_{B} = 0 V, \pm 1 LSB$ error band, $R_{AB} = 10 \ k\Omega$ |     | 2     |     | μs    |

| Resistor Noise Voltage                                                      | <b>е</b> <sub>N_WB</sub> | $R_{WB} = 5 k\Omega, f = 1 kHz$                                              |     | 14    |     | nV√Hz |

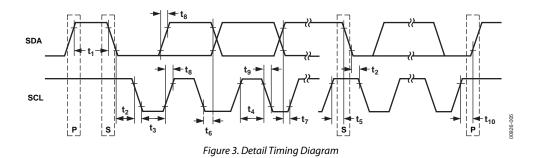

| INTERFACE TIMING CHARACTERISTICS<br>(APPLIES TO ALL PARTS <sup>5, 9</sup> ) |                          |                                                                              |     |       |     |       |

| SCL Clock Frequency                                                         | f <sub>scl</sub>         |                                                                              | 0   |       | 400 | kHz   |

| Bus Free Time Between Stop and Start, $t_{\mbox{\scriptsize BUF}}$          | <b>t</b> 1               |                                                                              | 1.3 |       |     | μs    |

| Hold Time (Repeated Start), t <sub>HD; STA</sub>                            | t2                       | After this period, the first clock pulse is generated                        | 600 |       |     | ns    |

| Low Period of SCL Clock, tLOW                                               | t <sub>3</sub>           |                                                                              | 1.3 |       |     | μs    |

| High Period of SCL Clock, t <sub>HIGH</sub>                                 | t4                       |                                                                              | 0.6 |       | 50  | μs    |

| Setup Time for Repeated Start Condition, tsu; STA                           | t5                       |                                                                              | 600 |       |     | ns    |

| Data Hold Time, t <sub>HD; DAT</sub>                                        | t <sub>6</sub>           |                                                                              |     |       | 900 | ns    |

| Data Setup Time, tsu; dat                                                   | t <sub>7</sub>           |                                                                              | 100 |       |     | ns    |

| Rise Time of Both SDA and SCL Signals, $t_{\mbox{\tiny R}}$                 | t <sub>8</sub>           |                                                                              |     |       | 300 | ns    |

| Fall Time of Both SDA and SCL Signals, t⊧                                   | t9                       |                                                                              |     |       | 300 | ns    |

| Setup Time for Stop Condition, tsu; sto                                     | t <sub>10</sub>          |                                                                              |     |       |     |       |

<sup>1</sup> Typicals represent average readings at  $25^{\circ}$ C,  $V_{DD} = 5$  V.

<sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See Test Circuits.

$^{3}$  INL and DNL are measured at V<sub>W</sub> with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = 0 V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions. See Figure 37.

<sup>4</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>5</sup> Guaranteed by design, not subject to production test. <sup>6</sup> P<sub>DISS</sub> is calculated from ( $I_{DD} \times V_{DD}$ ). CMOS logic level inputs result in minimum power dissipation.

<sup>7</sup> Bandwidth, noise, and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value results in the minimum overall power consumption.

<sup>8</sup> All dynamic characteristics use  $V_{DD} = 5$  V.

<sup>9</sup> See timing diagram in Figure 3 for location of measured values.

### **TIMING DIAGRAMS**

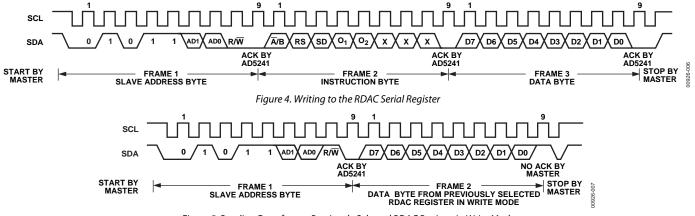

Data of AD5241/AD5242 is accepted from the I<sup>2</sup>C bus in the following serial format.

#### Table 2.

| S | 0 | 1 | 0 | 1     | 1     | AD1      | AD0 | R/W | Α | Ā/B              | RS | SD | <b>O</b> 1 | <b>O</b> <sub>2</sub> | Х | Х | X | Α | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Α | Ρ |

|---|---|---|---|-------|-------|----------|-----|-----|---|------------------|----|----|------------|-----------------------|---|---|---|---|----|----|----|----|----|----|----|----|---|---|

|   |   |   |   | Slave | e Ade | dress By | te  |     |   | Instruction Byte |    |    |            | Data Byte             |   |   |   |   |    |    |    |    |    |    |    |    |   |   |

where:

S = start condition

P = stop condition

A = acknowledge

X = don't care

AD1, AD0 = Package pin programmable address bits. Must be matched with the logic states at Pin AD1 and Pin AD0.

$R/\overline{W}$  = Read enable at high and output to SDA. Write enable at low.

$\overline{A}/B = RDAC$  subaddress select; 0 for RDAC1 and 1 for RDAC2.

RS = Midscale reset, active high.

SD = Shutdown in active high. Same as SHDN except inverse logic.

$O_1$ ,  $O_2$  = Output logic pin latched values

D7, D6, D5, D4, D3, D2, D1, D0 = data bits.

Figure 5. Reading Data from a Previously Selected RDAC Register in Write Mode

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                         | Rating                                           |

|---------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> to GND                            | –0.3 V to +7 V                                   |

| V <sub>ss</sub> to GND                            | 0 V to –7 V                                      |

| V <sub>DD</sub> to V <sub>SS</sub>                | 7 V                                              |

| $V_A$ , $V_B$ , $V_W$ to GND                      | V <sub>ss</sub> to V <sub>DD</sub>               |

| IA, IB, IW                                        |                                                  |

| $R_{AB} = 10 \text{ k}\Omega \text{ in TSSOP-14}$ | 5.0 mA <sup>1</sup>                              |

| $R_{AB} = 100 \text{ k}\Omega$ in TSSOP-14        | 1.5 mA <sup>1</sup>                              |

| $R_{AB} = 1 M\Omega$ in TSSOP-14                  | 0.5 mA <sup>1</sup>                              |

| Digital Input Voltage to GND                      | $0 \text{ V}$ to $V_{\text{DD}} + 0.3 \text{ V}$ |

| Operating Temperature Range                       | -40°C to +105°C                                  |

| Thermal Resistance θ <sub>JA</sub>                |                                                  |

| 14-Lead SOIC                                      | 158°C/W                                          |

| 16-Lead SOIC                                      | 73°C/W                                           |

| 14-Lead TSSOP                                     | 206°C/W                                          |

| 16-Lead TSSOP                                     | 180°C/W                                          |

| Maximum Junction Temperature (TJ max)             | 150°C                                            |

| Package Power Dissipation                         | $P_D = (T_J max - T_A)/\theta_{JA}$              |

| Storage Temperature Range                         | -65°C to +150°C                                  |

| Lead Temperature                                  |                                                  |

| Vapor Phase, 60 sec                               | 215°C                                            |

| Infrared, 15 sec                                  | 220°C                                            |

<sup>1</sup> Maximum current increases at lower resistance and different packages.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

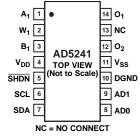

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

003

00926-

Figure 6. AD5241 Pin Configuration

#### Table 4. AD5241 Pin Function Descriptions

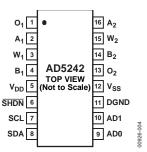

Figure 7. AD5242 Pin Configuration

#### Table 5. AD5242 Pin Function Descriptions

| 1 4010 10 |                       |                                                                               |         |                       |                                                                                |  |  |  |  |  |

|-----------|-----------------------|-------------------------------------------------------------------------------|---------|-----------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No.   | Mnemonic              | Description                                                                   | Pin No. | Mnemonic              | Description                                                                    |  |  |  |  |  |

| 1         | A <sub>1</sub>        | Resistor Terminal A <sub>1</sub> .                                            | 1       | O <sub>1</sub>        | Logic Output Terminal O <sub>1</sub> .                                         |  |  |  |  |  |

| 2         | <b>W</b> <sub>1</sub> | Wiper Terminal W <sub>1</sub> .                                               | 2       | <b>A</b> <sub>1</sub> | Resistor Terminal A <sub>1</sub> .                                             |  |  |  |  |  |

| 3         | B <sub>1</sub>        | Resistor Terminal B <sub>1</sub> .                                            | 3       | <b>W</b> <sub>1</sub> | Wiper Terminal W <sub>1</sub> .                                                |  |  |  |  |  |

| 4         | V <sub>DD</sub>       | Positive Power Supply, Specified for                                          | 4       | B1                    | Resistor Terminal B <sub>1</sub> .                                             |  |  |  |  |  |

|           |                       | Operation from 2.2 V to 5.5 V.                                                | 5       | V <sub>DD</sub>       | Positive Power Supply, Specified for                                           |  |  |  |  |  |

| 5         | SHDN                  | Active low, asynchronous connection of                                        |         |                       | Operation from 2.2 V to 5.5 V.                                                 |  |  |  |  |  |

|           |                       | Wiper W to Terminal B, and open circuit of Terminal A. RDAC register contents | 6       | SHDN                  | Active Low, Asynchronous Connection                                            |  |  |  |  |  |

|           |                       | unchanged. SHDN should tie to $V_{DD}$                                        |         |                       | of Wiper W to Terminal B, and Open<br>Circuit of Terminal A. RDAC register     |  |  |  |  |  |

|           |                       | if not used.                                                                  |         |                       | contents unchanged. SHDN should                                                |  |  |  |  |  |

| 6         | SCL                   | Serial Clock Input.                                                           |         |                       | tie to $V_{DD}$ , if not used.                                                 |  |  |  |  |  |

| 7         | SDA                   | Serial Data Input/Output.                                                     | 7       | SCL                   | Serial Clock Input.                                                            |  |  |  |  |  |

| 8         | AD0                   | Programmable Address Bit for Multiple                                         | 8       | SDA                   | Serial Data Input/Output.                                                      |  |  |  |  |  |

|           |                       | Package Decoding. Bit AD0 and Bit AD1                                         | 9       | AD0                   | Programmable Address Bit for Multiple                                          |  |  |  |  |  |

|           |                       | provide four possible addresses.                                              |         |                       | Package Decoding. Bit AD0 and Bit AD1                                          |  |  |  |  |  |

| 9         | AD1                   | Programmable Address Bit for Multiple                                         | 4.0     | 1.54                  | provide four possible addresses.                                               |  |  |  |  |  |

|           |                       | Package Decoding. Bit AD0 and Bit AD1 provide four possible addresses.        | 10      | AD1                   | Programmable Address Bit for Multiple<br>Package Decoding. Bit AD0 and Bit AD1 |  |  |  |  |  |

| 10        | DGND                  | Common Ground.                                                                |         |                       | provide four possible addresses.                                               |  |  |  |  |  |

| 10        | Vss                   | Negative Power Supply, Specified for                                          | 11      | DGND                  | Common Ground.                                                                 |  |  |  |  |  |

|           | V 55                  | Operation from $0 \text{ V}$ to $-2.7 \text{ V}$ .                            | 12      | V <sub>SS</sub>       | Negative Power Supply, Specified for                                           |  |  |  |  |  |

| 12        | O <sub>2</sub>        | Logic Output Terminal $O_2$ .                                                 |         | • 55                  | Operation from $0 \text{ V}$ to $-2.7 \text{ V}$ .                             |  |  |  |  |  |

| 13        | NC                    | No Connect.                                                                   | 13      | O <sub>2</sub>        | Logic Output Terminal O <sub>2</sub> .                                         |  |  |  |  |  |

| 14        | O1                    | Logic Output Terminal O <sub>1</sub> .                                        | 14      | B <sub>2</sub>        | Resistor Terminal B <sub>2</sub> .                                             |  |  |  |  |  |

|           | 1                     |                                                                               | 15      | W <sub>2</sub>        | Wiper Terminal W <sub>2</sub> .                                                |  |  |  |  |  |

|           |                       |                                                                               | 16      | A <sub>2</sub>        | Resistor Terminal A <sub>2</sub> .                                             |  |  |  |  |  |

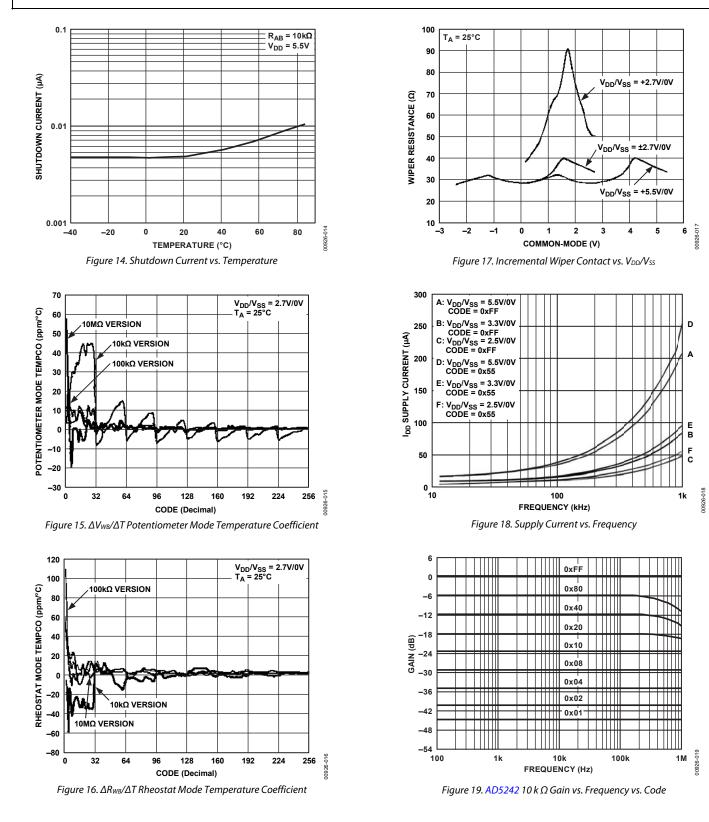

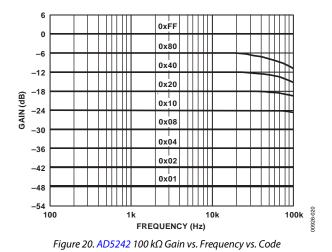

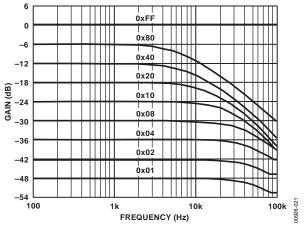

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **Data Sheet**

## AD5241/AD5242

Figure 21. AD5242 1 M $\Omega$  Gain vs. Frequency vs. Code

### **TEST CIRCUITS**

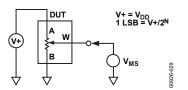

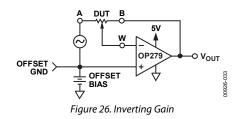

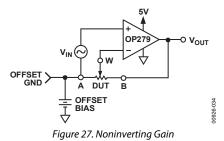

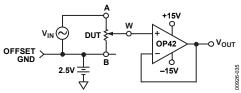

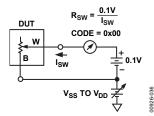

Figure 22 to Figure 30 define the test conditions used in the product specifications table.

Figure 22. Potentiometer Divider Nonlinearity Error (INL, DNL)

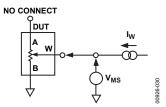

Figure 23. Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

Figure 25. Power Supply Sensitivity (PSS, PSRR)

Figure 28. Gain vs. Frequency

Figure 29. Incremental On Resistance

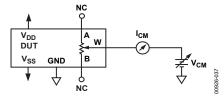

Figure 30. Common-Mode Leakage Current

### THEORY OF OPERATION

The AD5241/AD5242 provide a single-/dual-channel, 256position digitally controlled variable resistor (VR) device. The terms VR, RDAC, and programmable resistor are commonly used interchangeably to refer to digital potentiometer.

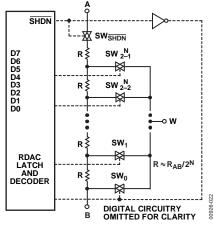

To program the VR settings, refer to the Digital Interface section. Both parts have an internal power-on preset that places the wiper in midscale during power-on that simplifies the fault condition recovery at power-up. In addition, the shutdown pin (SHDN) of AD5241/AD5242 places the RDAC in an almost zero power consumption state where Terminal A is open circuited and Wiper W is connected to Terminal B, resulting in only leakage current being consumed in the VR structure. During shutdown, the VR latch contents are maintained when the RDAC is inactive. When the part returns from shutdown, the stored VR setting is applied to the RDAC.

Figure 31. Equivalent RDAC Circuit

### PROGRAMMING THE VARIABLE RESISTOR Rheostat Operation

The nominal resistance of the RDAC between Terminal A and Terminal B is available in 10 k $\Omega$ , 100 k $\Omega$ , and 1 M $\Omega$ . The final two or three digits of the part number determine the nominal resistance value, for example,  $10 \text{ k}\Omega = 10$ ,  $100 \text{ k}\Omega = 100$ , and  $1 \text{ M}\Omega = 1 \text{ M}$ . The nominal resistance  $(R_{AB})$  of the VR has 256 contact points accessed by the wiper terminal, plus the B terminal contact. The 8-bit data in the RDAC latch is decoded to select one of the 256 possible settings. Assume a 10 k $\Omega$  part is used; the first connection of the wiper starts at the B terminal for Data 0x00. Because there is a 60  $\Omega$  wiper contact resistance, such connection yields a minimum of 60  $\Omega$  resistance between Terminal W and Terminal B. The second connection is the first tap point that corresponds to 99  $\Omega$  $(R_{WB} = R_{AB}/256 + R_W = 39 + 60)$  for Data 0x01. The third connection is the next tap point representing 138  $\Omega$  (39 × 2 + 60) for Data 0x02, and so on. Each LSB data value increase moves the wiper up the resistor ladder until the last tap point is reached at 10,021  $\Omega$  $[R_{AB} - 1 LSB + R_W].$

Figure 31 shows a simplified diagram of the equivalent RDAC circuit where the last resistor string is not accessed; therefore, there is 1 LSB less of the nominal resistance at full scale in addition to the wiper resistance.

The general equation determining the digitally programmed resistance between W and B is

$$R_{WB}(D) = \frac{D}{256} \times R_{AB} + R_W \tag{1}$$

where:

*D* is the decimal equivalent of the binary code between 0 and 255, which is loaded in the 8-bit RDAC register.

$R_{AB}$  is the nominal end-to-end resistance.

$R_W$  is the wiper resistance contributed by the on resistance of the internal switch.

Again, if  $R_{AB} = 10 \text{ k}\Omega$ , Terminal A can be either open circuit or tied to W. Table 6 shows the  $R_{WB}$  resistance based on the code set in the RDAC latch.

Table 6.  $R_{WB}$  (D) at Selected Codes for  $R_{AB} = 10 \text{ k}\Omega$

| D (DEC) | R <sub>WB</sub> (Ω) | Output State                                           |

|---------|---------------------|--------------------------------------------------------|

| 255     | 10021               | Full-scale (R <sub>WB</sub> – 1 LSB + R <sub>W</sub> ) |

| 128     | 5060                | Midscale                                               |

| 1       | 99                  | 1 LSB                                                  |

| 0       | 60                  | Zero-scale (wiper contact resistance)                  |

Note that in the zero-scale condition, a finite wiper resistance of 60  $\Omega$  is present. Care should be taken to limit the current flow between W and B in this state to a maximum current of no more than 20 mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the RDAC between Wiper W and Terminal A also produces a digitally controlled resistance,  $R_{WA}$ . When these terminals are used, Terminal B can be opened or tied to the wiper terminal. The minimum  $R_{WA}$  resistance is for Data 0xFF and increases as the data loaded in the latch decreases in value. The general equation for this operation is

$$R_{WA}(D) = \frac{256 - D}{256} \times R_{AB} + R_W$$

(2)

For  $R_{AB} = 10 \text{ k}\Omega$ , Terminal B can be either open circuit or tied to W. Table 7 shows the  $R_{WA}$  resistance based on the code set in the RDAC latch.

Table 7.  $R_{WA}$  (D) at Selected Codes for  $R_{AB} = 10 \text{ k}\Omega$

| D (DEC) | R <sub>WA</sub> (Ω) | Output State |  |

|---------|---------------------|--------------|--|

| 255     | 99                  | Full-scale   |  |

| 128     | 5060                | Midscale     |  |

| 1       | 10021               | 1 LSB        |  |

| 0       | 10060               | Zero-scale   |  |

### Data Sheet

The typical distribution of the nominal resistance  $R_{AB}$  from channel to channel matches within ±1% for AD5242. Deviceto-device matching is process lot dependent, and it is possible to have ±30% variation. Because the resistance element is processed in thin film technology, the change in  $R_{AB}$  with temperature has no more than a 30 ppm/°C temperature coefficient.

### PROGRAMMING THE POTENTIOMETER DIVIDER Voltage Output Operation

The digital potentiometer easily generates output voltages at wiper-to-B and wiper-to-A to be proportional to the input voltage at A-to-B. Unlike the polarity of  $V_{DD}$  / $V_{SS}$ , which must be positive, voltage across terminal A to terminal B, terminal W to terminal A, and terminal W to terminal B can be at either polarity provided that  $V_{SS}$  is powered by a negative supply.

If ignoring the effect of the wiper resistance for approximation, connecting Terminal A to 5 V and Terminal B to ground produces an output voltage at the wiper-to-B starting at 0 V up to 1 LSB less than 5 V. Each LSB of voltage is equal to the voltage applied across Terminal AB divided by the 256 positions of the potentiometer divider. Because AD5241/AD5242 can be supplied by dual supplies, the general equation defining the output voltage at V<sub>w</sub> with respect to ground for any valid input voltage applied to Terminal A and Terminal B is

$$V_W(D) = \frac{D}{256} V_A + \frac{256 - D}{256} V_B$$

(3)

which can be simplified to

$$V_{W}(D) = \frac{D}{256} V_{AB} + V_{B}$$

(4)

where *D* is the decimal equivalent of the binary code between 0 to 255 that is loaded in the 8-bit RDAC register.

For a more accurate calculation, including the effects of wiper resistance,  $V_{\rm W}$  can be found as

$$V_{W}(D) = \frac{R_{WB}(D)}{R_{AB}} V_{A} + \frac{R_{WA}(D)}{R_{AB}} V_{B}$$

(5)

where  $R_{WB}(D)$  and  $R_{WA}(D)$  can be obtained from Equation 1 and Equation 2.

Operation of the digital potentiometer in divider mode results in a more accurate operation over temperature. Unlike rheostat mode, the output voltage is dependent on the ratio of the internal resistors,  $R_{WA}$  and  $R_{WB}$ , and not the absolute values; therefore, the temperature drift reduces to 5 ppm/°C.

### **DIGITAL INTERFACE**

#### 2-Wire Serial Bus

The AD5241/AD5242 are controlled via an I<sup>2</sup>C-compatible serial bus. The RDACs are connected to this bus as slave devices.

Referring to Figure 3 and Figure 4, the first byte of AD5241/ AD5242 is a slave address byte. It has a 7-bit slave address and an  $R/\overline{W}$  bit. The five MSBs are 01011 and the following two bits are determined by the state of the AD0 and AD1 pins of the device. AD0 and AD1 allow users to use up to four of these devices on one bus.

The 2-wire, I<sup>2</sup>C serial bus protocol operates as follows:

1. The master initiates a data transfer by establishing a start condition, which is when a high-to-low transition on the SDA line occurs while SCL is high (see Figure 4). The following byte is the Frame 1, slave address byte, which consists of the 7-bit slave address followed by an R/W bit (this bit determines whether data is read from or written to the slave device).

The slave whose address corresponds to the transmitted address responds by pulling the SDA line low during the ninth clock pulse (this is the acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its serial register. If the  $R/\overline{W}$  bit is high, the master reads from the slave device. If the  $R/\overline{W}$  bit is low, the master writes to the slave device.

- A write operation contains an extra instruction byte more 2. than the read operation. The Frame 2 instruction byte in write mode follows the slave address byte. The MSB of the instruction byte labeled A/B is the RDAC subaddress select. A low selects RDAC1 and a high selects RDAC2 for the dualchannel AD5242. Set  $\overline{A}/B$  to low for the AD5241. The second MSB, RS, is the midscale reset. A logic high of this bit moves the wiper of a selected RDAC to the center tap where  $R_{WA} = R_{WB}$ . The third MSB, SD, is a shutdown bit. A logic high on SD causes the RDAC to open circuit at Terminal A while shorting the wiper to Terminal B. This operation yields almost a 0  $\Omega$  rheostat mode or 0 V in potentiometer mode. This SD bit serves the same function as the SHDN pin except that the SHDN pin reacts to active low. The following two bits are  $O_2$  and  $O_1$ . They are extra programmable logic outputs that users can use to drive other digital loads, logic gates, LED drivers, analog switches, and the like. The three LSBs are don't care (see Figure 4).

- 3. After acknowledging the instruction byte, the last byte in write mode is the, Frame 3 data byte. Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL (see Figure 4).

- 4. Unlike the write mode, the data byte follows immediately after the acknowledgment of the slave address byte in Frame 2 read mode. Data is transmitted over the serial bus in sequences of nine clock pulses (slightly different from the write mode, there are eight data bits followed by a no acknowledge Logic 1 bit in read mode). Similarly, the transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL (see Figure 5).

- 5. When all data bits have been read or written, a stop condition is established by the master. A stop condition is defined as a low-to-high transition on the SDA line while SCL is high. In write mode, the master pulls the SDA line high during the tenth clock pulse to establish a stop condition (see Figure 4). In read mode, the master issues a no acknowledge for the ninth clock pulse (that is, the SDA line remains high). The master then brings the SDA line low before the tenth clock pulse, which goes high to establish a stop condition (see Figure 5).

A repeated write function gives the user flexibility to update the RDAC output a number of times after addressing and instructing the part only once. During the write cycle, each data byte updates the RDAC output. For example, after the RDAC has acknowledged its slave address and instruction bytes, the RDAC output is updated. If another byte is written to the RDAC while it is still addressed to a specific slave device with the same instruction, this byte updates the output of the selected slave device. If different instructions are needed, the write mode has to start a completely new sequence with a new slave address, instruction, and data bytes transferred again. Similarly, a repeated read function of the RDAC is also allowed.

### **READBACK RDAC VALUE**

Specific to the AD5242 dual-channel device, the channel of interest is the one that was previously selected in the write mode. In addition, to read both RDAC values consecutively, users have to perform two write-read cycles. For example, users may first specify the RDAC1 subaddress in write mode (it is not necessary to issue the data byte and stop condition), and then change to read mode to read the RDAC1 value. To continue reading the RDAC2 value, users have to switch back to write mode, specify the subaddress, and then switch once again to read mode to read the RDAC2 value. It is not necessary to issue the write mode data byte or the first stop condition for this operation. Users should refer to Figure 4 and Figure 5 for the programming format.

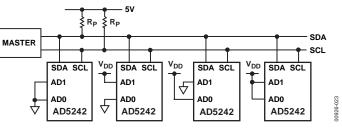

### **MULTIPLE DEVICES ON ONE BUS**

Figure 33 shows four AD5242 devices on the same serial bus. Each has a different slave address because the state of their AD0 and AD1 pins are different. This allows each RDAC within each device to be written to or read from independently. The master device output bus line drivers are open-drain pull-downs in a fully I<sup>2</sup>C-compatible interface. Note, a device is addressed properly only if the bit information of AD0 and AD1 in the slave address byte matches with the logic inputs at the AD0 and AD1 pins of that particular device.

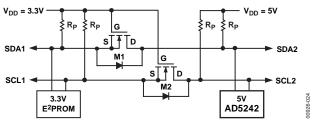

### LEVEL-SHIFT FOR BIDIRECTIONAL INTERFACE

While most old systems can operate at one voltage, a new component may be optimized at another. When they operate the same signal at two different voltages, a proper method of level-shifting is needed. For instance, a 3.3 V E<sup>2</sup>PROM can be used to interface with a 5 V digital potentiometer. A level-shift scheme is needed to enable a bidirectional communication so that the setting of the digital potentiometer can be stored to and retrieved from the E<sup>2</sup>PROM. Figure 32 shows one of the techniques. M1 and M2 can be N-channel FETs (2N7002) or low threshold FDV301N if V<sub>DD</sub> falls below 2.5 V.

Figure 33. Multiple AD5242 Devices on One Bus

### ADDITIONAL PROGRAMMABLE LOGIC OUTPUT

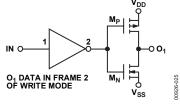

The AD5241/AD5242 feature additional programmable logic outputs,  $O_1$  and  $O_2$ , that can be used to drive digital load, analog switches, and logic gates. They can also be used as a self-contained shutdown preset to Logic 0 that is further explained in the Shutdown Function section.  $O_1$  and  $O_2$  default to Logic 0 during power-up. The logic states of  $O_1$  and  $O_2$  can be programmed in Frame 2 under the write mode (see Figure 4). Figure 34 shows the output stage of  $O_1$ , which employs large P-channel and Nchannel MOSFETs in push-pull configuration. As shown in Figure 34, the output is equal to  $V_{DD}$  or  $V_{SS}$ , and these logic outputs have adequate current driving capability to drive milliamperes of load.

Figure 34. Output Stage of Logic Output, O1

Users can also activate  $O_1$  and  $O_2$  in the following three different ways without affecting the wiper settings:

- 1. Start, slave address byte, acknowledge, instruction byte with O<sub>1</sub> and O<sub>2</sub> specified, acknowledge, stop.

- 2. Complete the write cycle with stop, then start, slave address byte, acknowledge, instruction byte with O<sub>1</sub> and O<sub>2</sub> specified, acknowledge, stop.

- 3. Do not complete the write cycle by not issuing the stop, then start, slave address byte, acknowledge, instruction byte with O<sub>1</sub> and O<sub>2</sub> specified, acknowledge, stop.

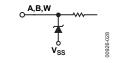

All digital inputs are protected with a series input resistor and the parallel Zener ESD structures shown in Figure 36. This applies to the digital input pins, SDA, SCL, and SHDN.

### SHUTDOWN FUNCTION

Shutdown can be activated by strobing the  $\overline{\text{SHDN}}$  pin or programming the SD bit in the write mode instruction byte (see Table 2). If the RDAC Register 1 or RDAC Register 2 (AD5242 only) is placed in shutdown mode by the software, SD bit, the part returns the wiper to its prior position when a new command is received.

In addition, shutdown can be implemented with the device digital output, as shown in Figure 35. In this configuration, the device is shutdown during power-up but users are allowed to program the device. Thus, when  $O_1$  is programmed high, the device exits shutdown mode and responds to the new setting. This self-contained shutdown function allows absolute shutdown during power-up, which is crucial in hazardous environments, and it does not add extra components.

Figure 35. Shutdown by Internal Logic Output, O1

Figure 36. ESD Protection of Digital Pins

Figure 37. ESD Protection of Resistor Terminals

**Data Sheet**

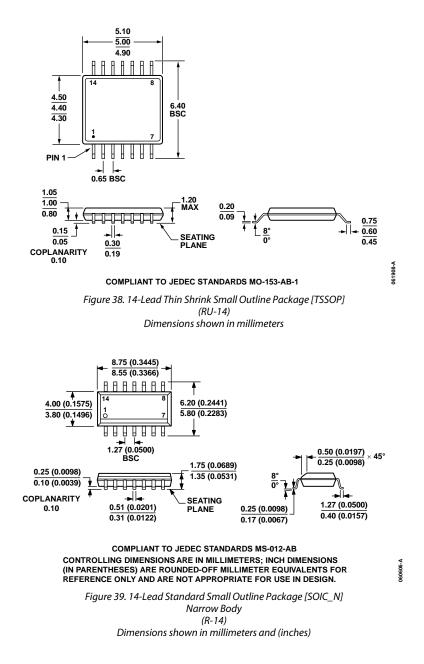

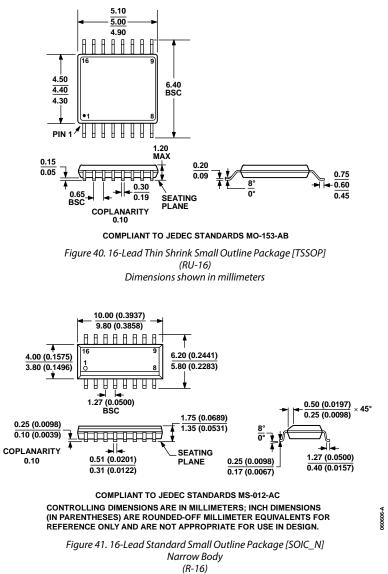

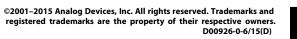

### **OUTLINE DIMENSIONS**

Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | No. of Channels | End-to-End R <sub>AB</sub> | Temperature Range | Package Description | Package Option |

|-----------------------|-----------------|----------------------------|-------------------|---------------------|----------------|

| AD5241BRZ10           | 1               | 10 kΩ                      | -40°C to +105°C   | 14-Lead SOIC_N      | R-14           |

| AD5241BRZ10-RL7       | 1               | 10 kΩ                      | -40°C to +105°C   | 14-Lead SOIC_N      | R-14           |

| AD5241BRUZ10          | 1               | 10 kΩ                      | -40°C to +105°C   | 14-Lead TSSOP       | RU-14          |

| AD5241BRUZ10-R7       | 1               | 10 kΩ                      | -40°C to +105°C   | 14-Lead TSSOP       | RU-14          |

| AD5241BRZ100          | 1               | 100 kΩ                     | -40°C to +105°C   | 14-Lead SOIC_N      | R-14           |

| AD5241BRUZ100         | 1               | 100 kΩ                     | -40°C to +105°C   | 14-Lead TSSOP       | RU-14          |

| AD5241BRUZ100-R7      | 1               | 100 kΩ                     | -40°C to +105°C   | 14-Lead TSSOP       | RU-14          |

| AD5241BRZ1M           | 1               | 1 MΩ                       | -40°C to +105°C   | 14-Lead SOIC_N      | R-14           |

| AD5241BRZ1M-REEL      | 1               | 1 MΩ                       | -40°C to +105°C   | 14-Lead SOIC_N      | R-14           |

| AD5241BRU1M-REEL7     | 1               | 1 MΩ                       | -40°C to +105°C   | 14-Lead TSSOP       | RU-14          |

| AD5242BR10-REEL7      | 2               | 10 kΩ                      | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRZ10           | 2               | 10 kΩ                      | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRZ10-REEL7     | 2               | 10 kΩ                      | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRUZ10          | 2               | 10 kΩ                      | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRUZ10-RL7      | 2               | 10 kΩ                      | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRZ100          | 2               | 100 kΩ                     | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRZ100-REEL7    | 2               | 100 kΩ                     | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRU100          | 2               | 100 kΩ                     | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRUZ100         | 2               | 100 kΩ                     | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRUZ100-RL7     | 2               | 100 kΩ                     | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRZ1M           | 2               | 1 MΩ                       | -40°C to +105°C   | 16-Lead SOIC_N      | R-16           |

| AD5242BRUZ1M          | 2               | 1 MΩ                       | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| AD5242BRUZ1M-REEL7    | 2               | 1 MΩ                       | -40°C to +105°C   | 16-Lead TSSOP       | RU-16          |

| EVAL-AD5242DBZ        | 2               | <b>Evaluation Board</b>    |                   |                     |                |

<sup>1</sup> The AD5241/AD5242 die size is 69 mil × 78 mil, 5,382 sq. mil. Contains 386 transistors for each channel. Patent Number 5,495,245 applies.

$^{2}$  Z = RoHS Compliant Part.

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

Rev. D | Page 18 of 18

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331