**High-Performance 8-Bit Microcontrollers**

### Z8 Encore! XP® F0823 Series

**Product Specification**

PS024315-1011

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

### **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                           | Description                                                                                                                                                                                        | Page<br>No.                             |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Sep         | 15                | LED Drive Enable Register                                                                                                                 | Clarified statement surrounding the Alternate Function Register as it relates to the LED function; revised Flash Sector Protect Register description; revised Packaging chapter.                   | <u>51,</u><br><u>144,</u><br><u>210</u> |

| Mar<br>2008 | 14                | n/a                                                                                                                                       | Changed branding to Z8 Encore! XP F0823 Series where appropriate.                                                                                                                                  | All                                     |

| Dec<br>2007 | 13                | Pin Description, General-Purpose Input/Output, Interrupt Controller, Watchdog Timer, Electrical Characteristics, and Ordering Information | Updated title from Z8 Encore! 8K and 4K Series to Z8 Encore! XP Z8F0823 Series. Updated Figure 3, Table 15, Table 35, Tables 59 through 61, Table 119 and Part Number Suffix Designations section. | 8, 36,<br>60, 95,<br>199,<br>and<br>220 |

| Aug<br>2007 | 12                | Part Selection Guide, External<br>Clock Setup, and Program<br>Memory                                                                      | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                             | 2, <u>35,</u><br>and <u>13</u>          |

| Jun<br>2007 | 11                | n/a                                                                                                                                       | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                         | All                                     |

| Dec<br>2006 | 10                | Ordering Information                                                                                                                      | Updated Ordering Information chapter.                                                                                                                                                              | <u>211</u>                              |

### **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                    |

| List of Tables                                                                                                                                                                                                                                                                                                     |

| Overview Features Part Selection Guide Block Diagram CPU and Peripheral Overview General-Purpose I/O Flash Controller Internal Precision Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Universal Asynchronous Receiver/Transmitter Timers Interrupt Controller Reset Controller On-Chip Debugger |

| Pin Description                                                                                                                                                                                                                                                                                                    |

| Address Space 13 Register File 13 Program Memory 13 Data Memory 15 Flash Information Area 15                                                                                                                                                                                                                       |

| Register Map                                                                                                                                                                                                                                                                                                       |

| Reset and Stop Mode Recovery 21 Reset Types 21 Reset Sources 23 Power-On Reset 23                                                                                                                                                                                                                                  |

| Voltage Brown-Out Reset                                                                                                                                                                                                                                                                                            |

#### Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Uy          | l |

|-------------|---|

| led in Life | ı |

| 0           | ı |

| External Reset Input                                | 25 |

|-----------------------------------------------------|----|

| External Reset Indicator                            | 26 |

| On-Chip Debugger Initiated Reset                    | 26 |

| Stop Mode Recovery                                  | 26 |

| Stop Mode Recovery Using Watchdog Timer Time-Out    | 27 |

| Stop Mode Recovery Using a GPIO Port Pin Transition | 27 |

| Stop Mode Recovery Using the External RESET Pin     |    |

| Reset Register Definitions                          | 28 |

| Low-Power Modes                                     | 30 |

| STOP Mode                                           | 30 |

| HALT Mode                                           | 31 |

| Peripheral-Level Power Control                      | 31 |

| Power Control Register Definitions                  | 31 |

| General-Purpose Input/Output                        | 33 |

| GPIO Port Availability By Device                    |    |

| Architecture                                        | 34 |

| GPIO Alternate Functions                            | 34 |

| Direct LED Drive                                    | 38 |

| Shared Reset Pin                                    | 39 |

| Shared Debug Pin                                    |    |

| Crystal Oscillator Override                         | 39 |

| 5 V Tolerance                                       | 39 |

| External Clock Setup                                | 40 |

| GPIO Interrupts                                     | 40 |

| GPIO Control Register Definitions                   | 40 |

| Port A–C Address Registers                          | 41 |

| Port A–C Control Registers                          |    |

| Port A–C Data Direction Subregisters                |    |

| Port A–C Alternate Function Subregisters            |    |

| Port A–C Input Data Registers                       |    |

| Port A–C Output Data Register                       |    |

| LED Drive Enable Register                           |    |

| LED Drive Level High Register                       |    |

| LED Drive Level Low Register                        | 53 |

| Interrupt Controller                                |    |

| Interrupt Vector Listing                            | 54 |

| Architecture                                        |    |

| Operation                                           | 56 |

| Master Interrupt Enable                             | 56 |

| Interrupt Vectors and Priority                      | 57 |

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

νi

| Interrupt Assertion                                      | 57  |

|----------------------------------------------------------|-----|

| Software Interrupt Assertion                             | 58  |

| Watchdog Timer Interrupt Assertion                       | 58  |

| Interrupt Control Register Definitions                   | 59  |

| Interrupt Request 0 Register                             | 59  |

| Interrupt Request 1 Register                             | 60  |

| Interrupt Request 2 Register                             | 61  |

| IRQ0 Enable High and Low Bit Registers                   | 61  |

| IRQ1 Enable High and Low Bit Registers                   | 63  |

| IRQ2 Enable High and Low Bit Registers                   | 65  |

| Interrupt Edge Select Register                           | 66  |

| Shared Interrupt Select Register                         | 67  |

| Interrupt Control Register                               | 68  |

| Timers                                                   | 69  |

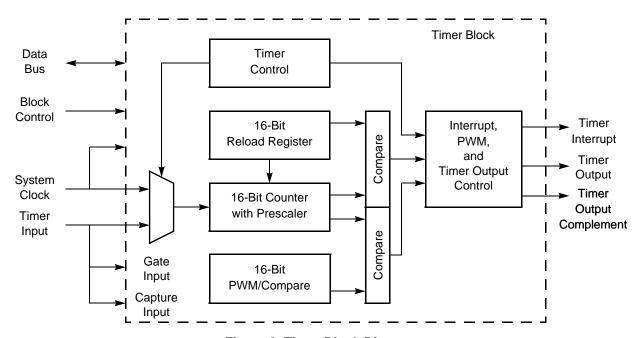

| Architecture                                             | 70  |

| Operation                                                | 70  |

| Timer Operating Modes                                    | 70  |

| Reading the Timer Count Values                           | 83  |

| Timer Pin Signal Operation                               | 83  |

| Timer Control Register Definitions                       | 83  |

| Timer 0–1 High and Low Byte Registers                    | 83  |

| Timer Reload High and Low Byte Registers                 | 84  |

| Timer 0–1 PWM High and Low Byte Registers                | 86  |

| Timer 0–1 Control Registers                              | 86  |

| Watchdog Timer                                           | 91  |

| Operation                                                | 91  |

| Watchdog Timer Refresh                                   | 92  |

| Watchdog Timer Time-Out Response                         | 92  |

| Watchdog Timer Reload Unlock Sequence                    | 93  |

| Watchdog Timer Control Register Definitions              | 93  |

| Watchdog Timer Control Register                          | 94  |

| Watchdog Timer Reload Upper, High and Low Byte Registers | 94  |

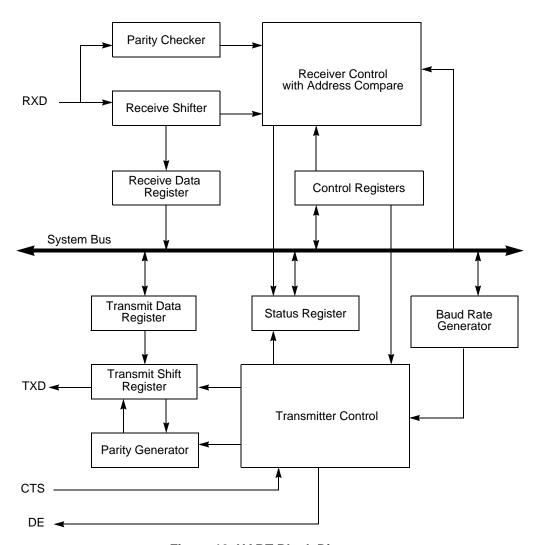

| Universal Asynchronous Receiver/Transmitter              | 97  |

| Architecture                                             | 97  |

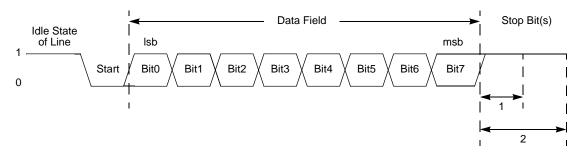

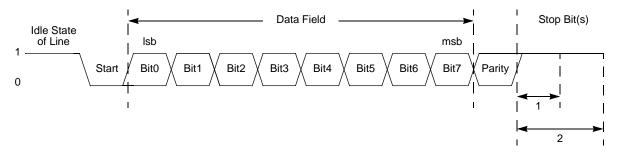

| Operation                                                | 98  |

| Transmitting Data Using the Polled Method                | 99  |

| Transmitting Data Using the Interrupt-Driven Method      | 100 |

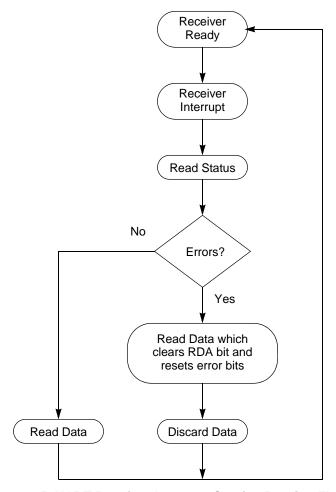

| Receiving Data Using the Polled Method                   | 101 |

| Receiving Data Using the Interrupt-Driven Method         | 102 |

| Clear To Send (CTS) Operation                            | 103 |

#### Z8 Encore! XP® F0823 Series **Product Specification**

| MULTIPROCESSOR (9-Bit) Mode                                | 103 |

|------------------------------------------------------------|-----|

| External Driver Enable                                     | 105 |

| UART Interrupts                                            | 105 |

| UART Baud Rate Generator                                   | 108 |

| UART Control Register Definitions                          | 108 |

| UART Transmit Data Register                                | 109 |

| UART Receive Data Register                                 | 109 |

| UART Status 0 Register                                     | 110 |

| UART Status 1 Register                                     | 111 |

| UART Control 0 and Control 1 Registers                     | 112 |

| UART Address Compare Register                              | 115 |

| UART Baud Rate High and Low Byte Registers                 | 115 |

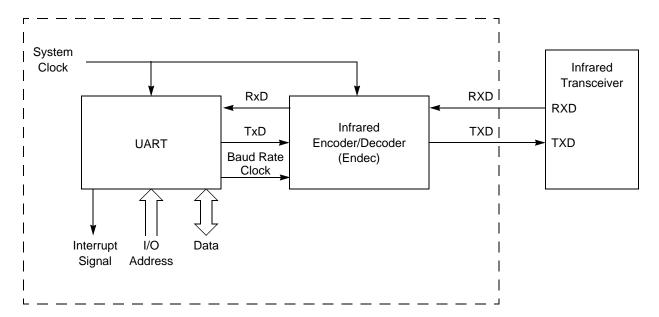

| Infrared Encoder/Decoder                                   | 117 |

| Architecture                                               | 117 |

| Operation                                                  | 117 |

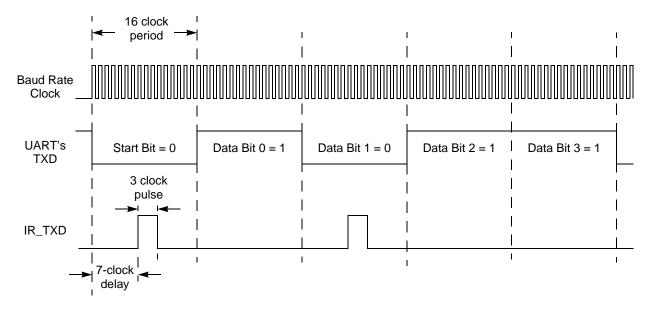

| Transmitting IrDA Data                                     | 118 |

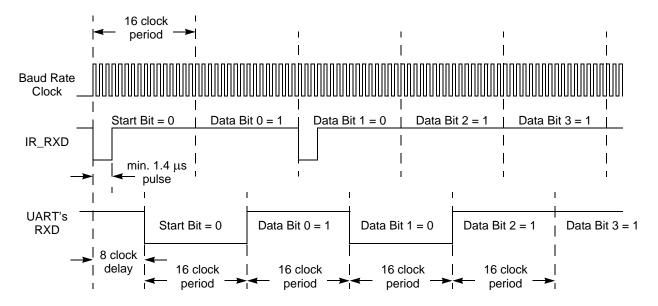

| Receiving IrDA Data                                        | 119 |

| Infrared Encoder/Decoder Control Register Definitions      | 120 |

| Analog-to-Digital Converter                                | 121 |

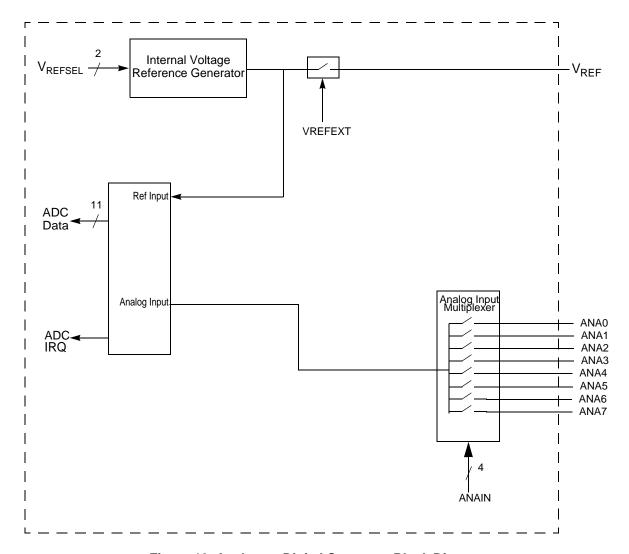

| Architecture                                               |     |

| Operation                                                  | 122 |

| Automatic Powerdown                                        | 123 |

| Single-Shot Conversion                                     | 123 |

| Continuous Conversion                                      | 124 |

| Interrupts                                                 | 125 |

| Calibration and Compensation                               | 125 |

| ADC Control Register Definitions                           | 126 |

| ADC Control Register 0                                     | 126 |

| ADC Control/Status Register 1                              | 129 |

| ADC Data High Byte Register                                | 130 |

| ADC Data Low Bits Register                                 | 131 |

| Comparator                                                 | 132 |

| Operation                                                  | 132 |

| Comparator Control Register Definition                     | 133 |

| Flash Memory                                               | 134 |

| Flash Information Area                                     |     |

| Operation                                                  |     |

| Flash Operation Timing Using the Flash Frequency Registers |     |

| Flash Code Protection Against External Access              | 137 |

|                                                            |     |

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| 1/ | ı | ı |

|----|---|---|

|    |   |   |

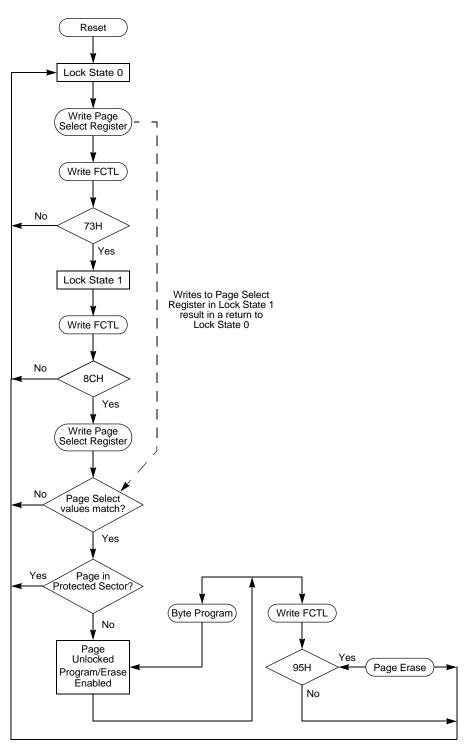

| Flash Code Protection Against Accidental Program and Erasure | . 137 |

|--------------------------------------------------------------|-------|

| Byte Programming                                             | . 139 |

| Page Erase                                                   | . 139 |

| Mass Erase                                                   | . 139 |

| Flash Controller Bypass                                      |       |

| Flash Controller Behavior in DEBUG Mode                      | . 140 |

| Flash Control Register Definitions                           | . 141 |

| Flash Control Register                                       | . 141 |

| Flash Status Register                                        | . 142 |

| Flash Page Select Register                                   | . 142 |

| Flash Sector Protect Register                                | . 144 |

| Flash Frequency High and Low Byte Registers                  | . 144 |

| Flash Option Bits                                            | . 146 |

| Operation                                                    | . 146 |

| Option Bit Configuration By Reset                            | . 146 |

| Option Bit Types                                             |       |

| Reading the Flash Information Page                           | . 148 |

| Flash Option Bit Control Register Definitions                | . 148 |

| Trim Bit Address Register                                    |       |

| Trim Bit Data Register                                       | . 149 |

| Flash Option Bit Address Space                               | . 149 |

| Trim Bit Address Space                                       | . 151 |

| Zilog Calibration Data                                       | . 152 |

| ADC Calibration Data                                         | . 153 |

| Serialization Data                                           | . 154 |

| Randomized Lot Identifier                                    | . 154 |

| On-Chip Debugger                                             | . 156 |

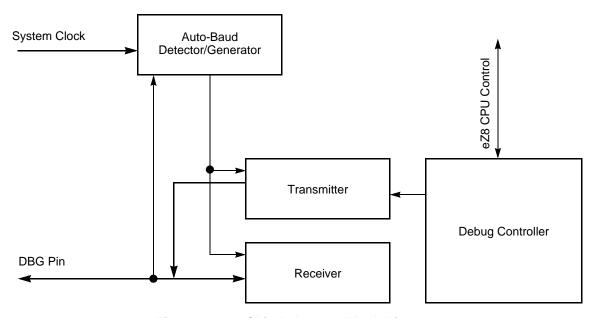

| Architecture                                                 |       |

| Operation                                                    |       |

| OCD Interface                                                |       |

| DEBUG Mode                                                   |       |

| OCD Data Format                                              |       |

| OCD Autobaud Detector/Generator                              |       |

| OCD Serial Errors                                            |       |

| OCD Unlock Sequence (8-Pin Devices Only)                     |       |

| Breakpoints                                                  |       |

| Runtime Counter                                              |       |

| On-Chip Debugger Commands                                    |       |

| On-Chip Debugger Control Register Definitions                |       |

| OCD Control Register                                         |       |

|                                                              |       |

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| v |

|---|

| ж |

| OCD Status Register                                     | 168 |

|---------------------------------------------------------|-----|

| Oscillator Control                                      |     |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Internal Precision Oscillator                           |     |

| Operation                                               | 173 |

| eZ8 CPU Instruction Set                                 |     |

| Assembly Language Programming Introduction              |     |

| Assembly Language Syntax                                |     |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             | 182 |

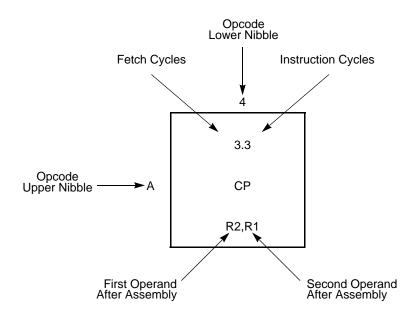

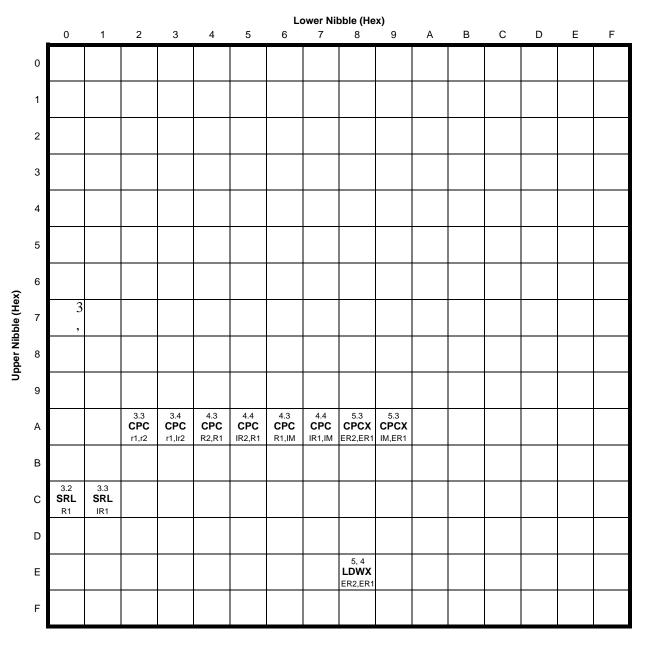

| Opcode Maps                                             | 192 |

| Electrical Characteristics                              | 196 |

| Absolute Maximum Ratings                                | 196 |

| DC Characteristics                                      | 197 |

| AC Characteristics                                      | 200 |

| On-Chip Peripheral AC and DC Electrical Characteristics | 201 |

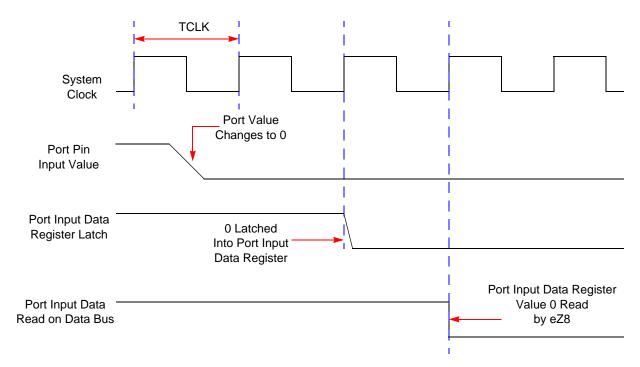

| General Purpose I/O Port Input Data Sample Timing       | 204 |

| General Purpose I/O Port Output Timing                  | 206 |

| On-Chip Debugger Timing                                 | 207 |

| UART Timing                                             | 208 |

| Packaging                                               | 210 |

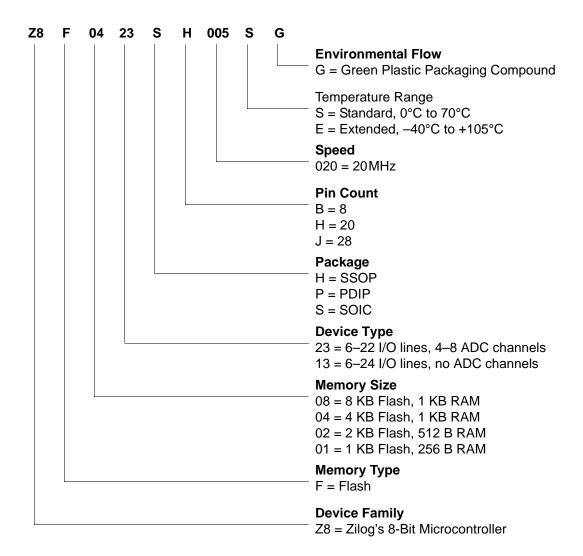

| Ordering Information                                    | 211 |

| Part Number Suffix Designations                         |     |

| Index                                                   | 221 |

| Customer Support                                        | 230 |

|                                                         |     |

## List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram                                      | 3    |

|------------|-------------------------------------------------------------------------------|------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package | 8    |

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package      | 8    |

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package      | 8    |

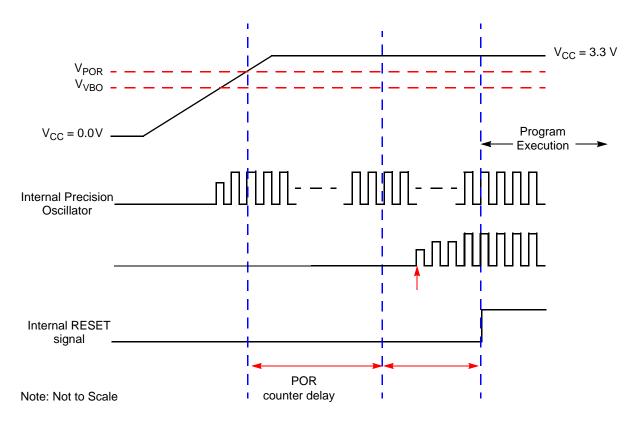

| Figure 5.  | Power-On Reset Operation                                                      | . 24 |

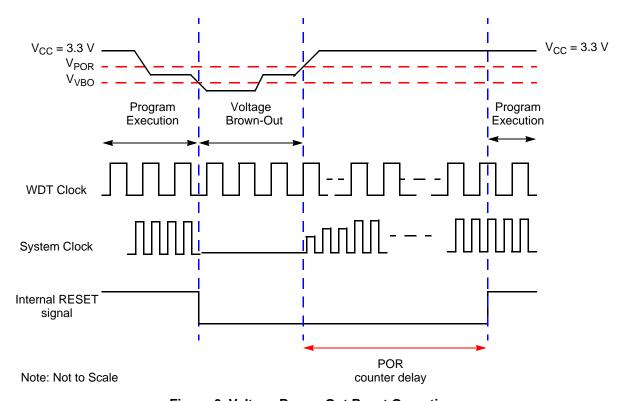

| Figure 6.  | Voltage Brown-Out Reset Operation                                             | . 25 |

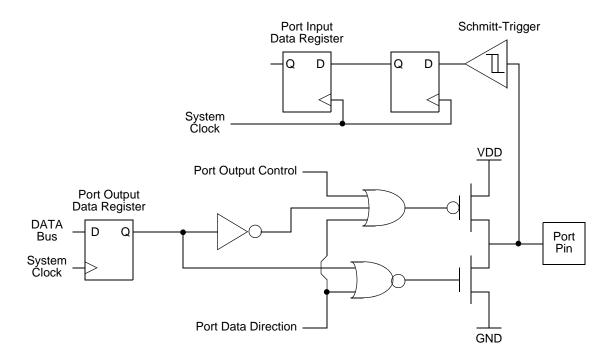

| Figure 7.  | GPIO Port Pin Block Diagram                                                   | . 34 |

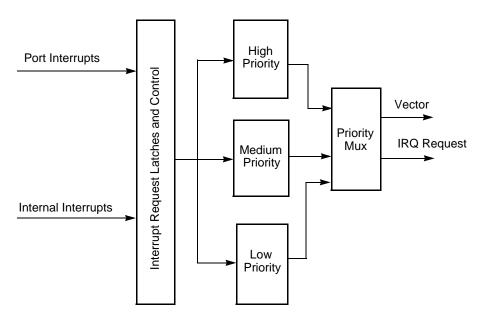

| Figure 8.  | Interrupt Controller Block Diagram                                            | . 56 |

| Figure 9.  | Timer Block Diagram                                                           | . 70 |

| Figure 10. | UART Block Diagram                                                            | . 98 |

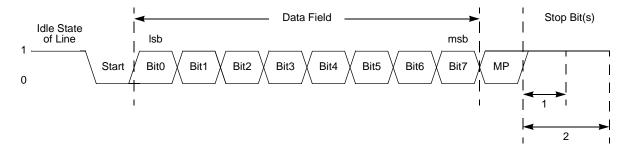

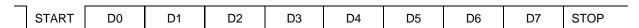

| Figure 11. | UART Asynchronous Data Format without Parity                                  | . 99 |

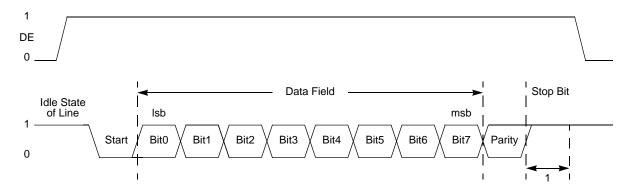

| Figure 12. | UART Asynchronous Data Format with Parity                                     | . 99 |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format                             | 103  |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)           | 105  |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                  | 107  |

| Figure 16. | Infrared Data Communication System Block Diagram                              | 117  |

| Figure 17. | Infrared Data Transmission                                                    | 118  |

| Figure 18. | IrDA Data Reception                                                           | 119  |

| Figure 19. | Analog-to-Digital Converter Block Diagram                                     | 122  |

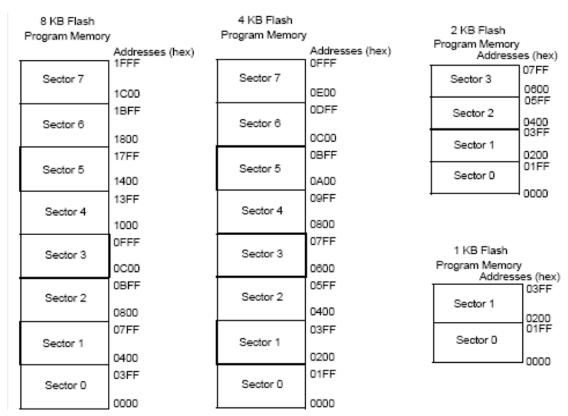

| Figure 20. | Flash Memory Arrangement                                                      | 135  |

| Figure 21. | Flash Controller Operation Flowchart                                          | 136  |

| Figure 22. | On-Chip Debugger Block Diagram                                                | 156  |

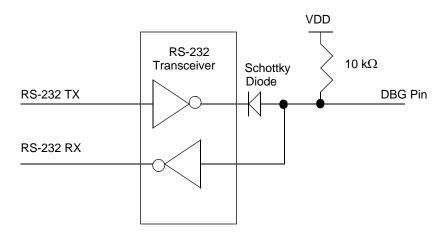

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 1 of 2 | 157  |

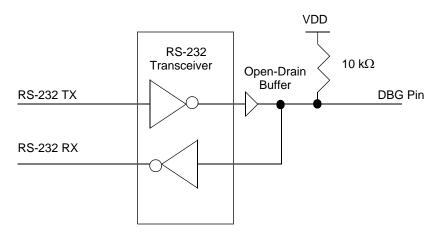

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2 | 158  |

| Figure 25. | OCD Data Format                                                               | 159  |

| Figure 26. | Opcode Map Cell Description                                                   | 192  |

| Figure 27. | First Opcode Map                                                              |      |

| Figure 28. | Second Opcode Map after 1FH                                                   |      |

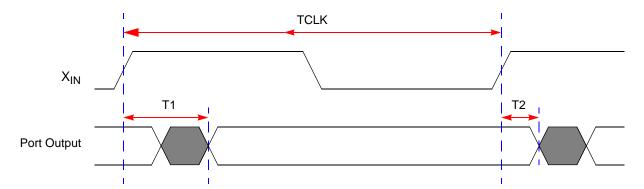

| Figure 29. | Port Input Sample Timing                                                      |      |

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| v | ī |

|---|---|

| ^ |   |

| Figure 30. | GPIO Port Output Timing | 206 |

|------------|-------------------------|-----|

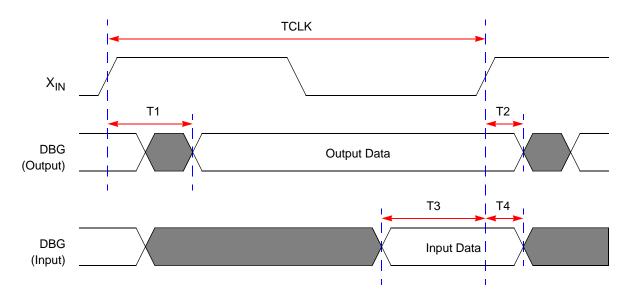

| Figure 31. | On-Chip Debugger Timing | 207 |

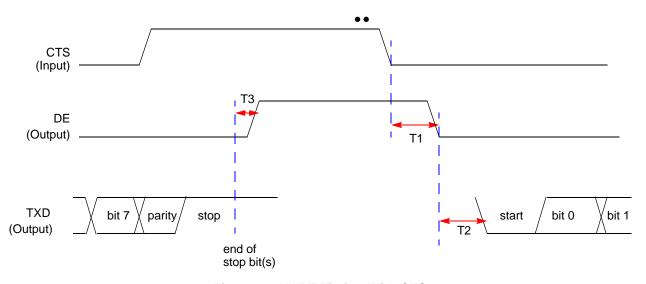

| Figure 32. | UART Timing With CTS    | 208 |

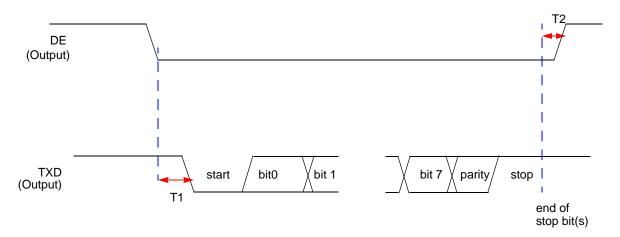

| Figure 33. | UART Timing Without CTS | 209 |

### List of Tables

| Table 1.  | F0823 Series Family Part Selection Guide                          | 2    |

|-----------|-------------------------------------------------------------------|------|

| Table 2.  | F0823 Series Package Options                                      | 7    |

| Table 3.  | Signal Descriptions                                               | 9    |

| Table 4.  | Pin Characteristics (20- and 28-pin Devices)*                     | . 11 |

| Table 5.  | Pin Characteristics (8-Pin Devices)                               | . 12 |

| Table 6.  | Z8 Encore! XP F0823 Series Program Memory Maps                    | . 14 |

| Table 7.  | F0823 Series Flash Memory Information Area Map                    | . 15 |

| Table 8.  | Register File Address Map                                         | . 16 |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency          | . 21 |

| Table 10. | Reset Sources and Resulting Reset Type                            | . 23 |

| Table 11. | Stop Mode Recovery Sources and Resulting Action                   | . 27 |

| Table 12. | Reset Status Register (RSTSTAT)                                   | . 28 |

| Table 13. | POR Indicator Values                                              | . 29 |

| Table 14. | Power Control Register 0 (PWRCTL0)                                | . 32 |

| Table 15. | Port Availability by Device and Package Type                      | . 33 |

| Table 16. | Port Alternate Function Mapping (8-Pin Parts)                     | . 35 |

| Table 17. | Port Alternate Function Mapping (Non 8-Pin Parts)                 | . 36 |

| Table 18. | GPIO Port Registers and Subregisters                              | . 40 |

| Table 19. | Port A–C GPIO Address Registers (PxADDR)                          | . 41 |

| Table 20. | PADDR[7:0] Subregister Functions                                  | . 41 |

| Table 21. | Port A–C Control Registers (PxCTL)                                | . 42 |

| Table 22. | Port A–C Data Direction Subregisters (PxDD)                       | . 43 |

| Table 23. | Port A–C Alternate Function Subregisters (PxAF)                   | . 44 |

| Table 24. | Port A–C Output Control Subregisters (PxOC)                       | . 44 |

| Table 25. | Port A–C High Drive Enable Subregisters (PHDEx)                   | . 45 |

| Table 26. | Port A–C Stop Mode Recovery Source Enable Subregisters (PSMREx) . | . 46 |

| Table 27. | Port A–C Pull-Up Enable Subregisters (PPUEx)                      | . 47 |

| Table 28. | Port A–C Alternate Function Set 1 Subregisters (PAFS1x)           | . 48 |

| Table 29. | Port A–C Alternate Function Set 2 Subregisters (PxAFS2)           | . 49 |

| Table 30. | Port A–C Input Data Registers (PxIN)                              | . 50 |

| Table 31. | Port A–C Output Data Register (PxOUT)                             | . 51 |

| Table 32. | LED Drive Enable (LEDEN)                                          | . 51 |

| Table 33. | LED Drive Level High Register (LEDLVLH)                           | . 52 |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Table 34. | LED Drive Level Low Register (LEDLVLL)           | 53  |

|-----------|--------------------------------------------------|-----|

| Table 35. | Trap and Interrupt Vectors in Order of Priority  | 55  |

| Table 36. | Interrupt Request 0 Register (IRQ0)              | 59  |

| Table 37. | Interrupt Request 1 Register (IRQ1)              | 60  |

| Table 38. | Interrupt Request 2 Register (IRQ2)              | 61  |

| Table 39. | IRQ0 Enable and Priority Encoding                | 61  |

| Table 40. | IRQ0 Enable High Bit Register (IRQ0ENH)          | 62  |

| Table 41. | IRQ0 Enable Low Bit Register (IRQ0ENL)           | 62  |

| Table 42. | IRQ1 Enable and Priority Encoding                | 63  |

| Table 43. | IRQ1 Enable Low Bit Register (IRQ1ENL)           | 64  |

| Table 44. | IRQ1 Enable High Bit Register (IRQ1ENH)          | 64  |

| Table 45. | IRQ2 Enable and Priority Encoding                | 65  |

| Table 46. | IRQ2 Enable High Bit Register (IRQ2ENH)          | 65  |

| Table 47. | IRQ2 Enable Low Bit Register (IRQ2ENL)           | 66  |

| Table 48. | Interrupt Edge Select Register (IRQES)           | 66  |

| Table 49. | Shared Interrupt Select Register (IRQSS)         | 67  |

| Table 50. | Interrupt Control Register (IRQCTL)              | 68  |

| Table 51. | Timer 0–1 High Byte Register (TxH)               | 84  |

| Table 52. | Timer 0–1 Low Byte Register (TxL)                | 84  |

| Table 53. | Timer 0–1 Reload High Byte Register (TxRH)       | 85  |

| Table 54. | Timer 0–1 Reload Low Byte Register (TxRL)        | 85  |

| Table 55. | Timer 0–1 PWM High Byte Register (TxPWMH)        | 86  |

| Table 56. | Timer 0–1 PWM Low Byte Register (TxPWML)         | 86  |

| Table 57. | Timer 0–1 Control Register 0 (TxCTL0)            | 87  |

| Table 58. | Timer 0–1 Control Register 1 (TxCTL1)            | 88  |

| Table 59. | Watchdog Timer Approximate Time-Out Delays       | 91  |

| Table 60. | Watchdog Timer Control Register (WDTCTL)         | 94  |

| Table 61. | Watchdog Timer Reload Upper Byte Register (WDTU) | 95  |

| Table 62. | Watchdog Timer Reload High Byte Register (WDTH)  | 95  |

| Table 63. | Watchdog Timer Reload Low Byte Register (WDTL)   | 95  |

| Table 64. | UART Transmit Data Register (U0TXD)              | 109 |

| Table 65. | UART Receive Data Register (U0RXD)               | 109 |

| Table 66. | UART Status 0 Register (U0STAT0)                 | 110 |

| Table 67. | UART Status 1 Register (U0STAT1)                 | 111 |

| Table 68. | UART Control 0 Register (U0CTL0)                 | 112 |

| Table 69. | UART Control 1 Register (U0CTL1)                 | 113 |

### Z8 Encore! XP® F0823 Series Product Specification

| Table 70.  | UART Address Compare Register (U0ADDR)                 | 115 |

|------------|--------------------------------------------------------|-----|

| Table 71.  | UART Baud Rate High Byte Register (U0BRH)              | 115 |

| Table 72.  | UART Baud Rate Low Byte Register (U0BRL)               | 115 |

| Table 73.  | UART Baud Rates                                        | 116 |

| Table 74.  | ADC Control Register 0 (ADCCTL0)                       | 127 |

| Table 75.  | ADC Control/Status Register 1 (ADCCTL1)                | 129 |

| Table 76.  | ADC Data High Byte Register (ADCD_H)                   | 130 |

| Table 77.  | ADC Data Low Bits Register (ADCD_L)                    | 131 |

| Table 78.  | Comparator Control Register (CMP0)                     | 133 |

| Table 79.  | Z8 Encore! XP F0823 Series Flash Memory Configurations | 134 |

| Table 80.  | Flash Code Protection Using the Flash Option Bits      | 138 |

| Table 81.  | Flash Control Register (FCTL)                          | 141 |

| Table 82.  | Flash Status Register (FSTAT)                          | 142 |

| Table 83.  | Flash Page Select Register (FPS)                       | 143 |

| Table 84.  | Flash Sector Protect Register (FPROT)                  | 144 |

| Table 85.  | Flash Frequency High Byte Register (FFREQH)            | 145 |

| Table 86.  | Flash Frequency Low Byte Register (FFREQL)             |     |

| Table 87.  | Trim Bit Address Register (TRMADR)                     | 148 |

| Table 88.  | Trim Bit Data Register (TRMDR)                         | 149 |

| Table 89.  | Flash Option Bits at Program Memory Address 0000H      | 149 |

| Table 90.  | Flash Options Bits at Program Memory Address 0001H     | 150 |

| Table 91.  | Trim Options Bits at Address 0000H                     | 151 |

| Table 92.  | Trim Option Bits at 0001H                              | 152 |

| Table 93.  | Trim Option Bits at 0002H (TIPO)                       | 152 |

| Table 94.  | ADC Calibration Bits                                   | 153 |

| Table 95.  | ADC Calibration Data Location                          | 153 |

| Table 96.  | Serial Number at 001C-001F (S_NUM)                     | 154 |

| Table 97.  | Serialization Data Locations                           | 154 |

| Table 98.  | Lot Identification Number (RAND_LOT)                   | 154 |

| Table 99.  | Randomized Lot ID Locations                            | 155 |

| Table 100. | OCD Baud-Rate Limits                                   | 160 |

| Table 101. | OCD Commands                                           | 162 |

| Table 102. | OCD Control Register (OCDCTL)                          | 167 |

| Table 103. | OCD Status Register (OCDSTAT)                          | 168 |

|            | Oscillator Configuration and Selection                 |     |

| Table 105. | Oscillator Control Register (OSCCTL)                   | 172 |

|            |                                                        |     |

### Z8 Encore! XP® F0823 Series Product Specification

| v | • |  |

|---|---|--|

| А | v |  |

| Table 106.  | Assembly Language Syntax Example 1                                         | 175 |

|-------------|----------------------------------------------------------------------------|-----|

| Table 107.  | Assembly Language Syntax Example 2                                         | 176 |

| Table 108.  | Notational Shorthand                                                       | 176 |

| Table 109.  | Additional Symbols                                                         | 177 |

| Table 110.  | Arithmetic Instructions                                                    | 178 |

| Table 111.  | Bit Manipulation Instructions                                              | 179 |

| Table 112.  | Block Transfer Instructions                                                | 179 |

| Table 113.  | CPU Control Instructions                                                   | 180 |

| Table 114.  | Load Instructions                                                          | 180 |

| Table 115.  | Logical Instructions                                                       | 181 |

| Table 116.  | Program Control Instructions                                               | 181 |

| Table 117.  | Rotate and Shift Instructions                                              | 181 |

| Table 118.  | eZ8 CPU Instruction Summary                                                | 182 |

| Table 119.  | Opcode Map Abbreviations                                                   | 193 |

| Table 120.  | Absolute Maximum Ratings                                                   | 196 |

| Table 121.  | DC Characteristics                                                         | 197 |

| Table 122.  | Power Consumption                                                          | 199 |

| Table 123.  | AC Characteristics                                                         | 200 |

| Table 124.  | Internal Precision Oscillator Electrical Characteristics                   | 200 |

| Table 125.  | Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing | 201 |

| Table 126   | Flash Memory Electrical Characteristics and Timing                         |     |

|             | Watchdog Timer Electrical Characteristics and Timing                       |     |

|             | Analog-to-Digital Converter Electrical Characteristics and Timing          |     |

|             | Comparator Electrical Characteristics                                      |     |

|             | GPIO Port Input Timing                                                     |     |

|             | GPIO Port Output Timing                                                    |     |

|             | On-Chip Debugger Timing                                                    |     |

|             | UART Timing With CTS                                                       |     |

|             | UART Timing Without CTS                                                    |     |

|             | Z8 Encore! XP F0823 Series Ordering Matrix                                 |     |

| 1 4010 133. | 20 Encore. 21 1 0025 belies Ordering mania                                 | 411 |

#### **Overview**

Zilog's Z8 Encore! XP microcontroller unit (MCU) family of products are the first Zilog microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brown-Out (VBO) protection

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- $0^{\circ}$ C to  $+70^{\circ}$ C and  $-40^{\circ}$ C to  $+105^{\circ}$ C for operating temperature ranges

#### **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore!  $XP^{\textcircled{\tiny{B}}}$  F0823 Series product line.

Table 1. F0823 Series Family Part Selection Guide

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

### **Block Diagram**

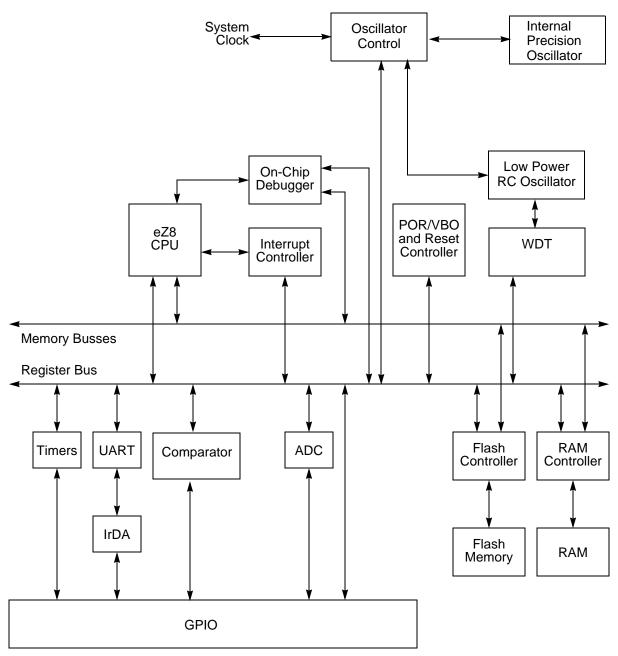

Figure 1 displays a block diagram of the F0823 Series architecture.

Figure 1. Z8 Encore! XP F0823 Series Block Diagram

#### **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

#### General-Purpose I/O

F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V-tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

#### Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

#### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

#### 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

#### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

#### **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

#### **Timers**

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

#### **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

Z8 Encore!  $XP^{\textcircled{0}}$  F0823 Series products can be reset using the  $\overline{RESET}$  pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The  $\overline{RESET}$  pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

#### **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

### Pin Description

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

#### **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

Part 8-pin 8-pin 20-pin 20-pin 20-pin 28-pin 28-pin 28-pin 8-pin QFN/ Number **ADC PDIP** SOIC **PDIP** SOIC **SSOP PDIP** SOIC **SSOP** MLF-S Z8F0823 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0813 No Z8F0423 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0413 Χ Χ Χ Χ Χ Χ Χ Χ Χ No Z8F0223 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0213 Χ Χ Χ No Χ Z8F0123 Yes Χ Χ Χ Χ Χ Χ Χ Χ Z8F0113 Χ Χ Χ Χ Χ Χ Χ Χ Χ No

**Table 2. F0823 Series Package Options**

#### **Pin Configurations**

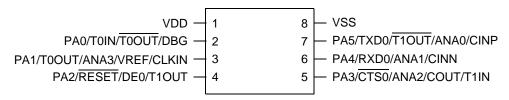

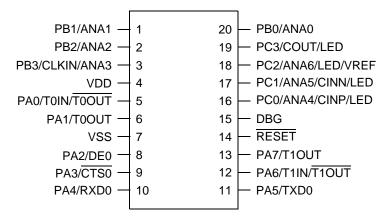

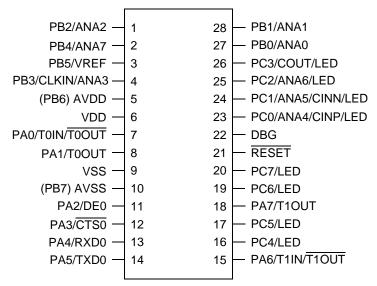

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

**>**

**Note:** \*Analog input alternate functions (ANA) are not available on Z8F0x13 devices.

#### **Signal Descriptions**

Table 3 lists the Z8 Encore! XP F0823 Series signals. To determine the signals available for the specific package styles, see **the** Pin Configurations **section on page 7**.

**Table 3. Signal Descriptions**

| Signal Mnemonic         | I/O                           | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| General-Purpose I/0     | General-Purpose I/O Ports A–D |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| PA[7:0]                 | I/O                           | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| PB[7:0] <sup>1</sup>    | I/O                           | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |  |  |  |

| PC[7:0]                 | I/O                           | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| <b>UART Controllers</b> |                               |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TXD0                    | 0                             | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |  |  |

| RXD0                    | I                             | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CTS0                    | I                             | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| DE                      | 0                             | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |  |  |

| Timers                  |                               |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| T0OUT/T1OUT             | 0                             | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| T0OUT/T1OUT             | 0                             | Timer Complement Output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                                                                                                                                                                                          |  |  |  |  |  |  |

| T0IN/T1IN               | I                             | Timer Input 0–1. These signals are used as the capture, gating and counter inputs. The ToIN signal is multiplexed TOOUT signals.                                                                                                                                                                        |  |  |  |  |  |  |

| Comparator              |                               |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CINP/CINN               | I                             | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |  |  |  |

#### Notes:

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

- 2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

**Table 3. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                          |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.  Caution: The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                            |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| $V_{DD}$                      | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | ı   | Analog Power Supply.                                                                                                                                                                                                  |

| $\overline{V_{SS}}$           | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | ı   | Analog Ground.                                                                                                                                                                                                        |

| NI (                          |     |                                                                                                                                                                                                                       |

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are

- replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

PS024315-1011 PRELIMINARY Signal Descriptions

#### **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

**Note:** All six I/O pins on the 8-pin packages are 5V-tolerant (unless the pull-up devices are enabled). The right-most column in Table 4 describes 5V tolerance for the 20- and 28-pin packages only.

Table 4. Pin Characteristics (20- and 28-pin Devices)\*

| Symbol<br>Mnemonic | Direction | Reset<br>Direction               | Active<br>Low or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up<br>or Pull-<br>down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output           | 5V<br>Tolerance |

|--------------------|-----------|----------------------------------|------------------------------------|----------------------|-----------------------------------------|------------------------------|--------------------------------|-----------------|

| AVDD               | N/A       | N/A                              | N/A                                | N/A                  | N/A                                     | N/A                          | N/A                            | N/A             |

| AVSS               | N/A       | N/A                              | N/A                                | N/A                  | N/A                                     | N/A                          | N/A                            | NA              |

| DBG                | I/O       | ļ                                | N/A                                | Yes                  | No                                      | Yes                          | Yes                            | Yes             |

| PA[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable           | PA[7:2] only    |

| PB[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable           | PB[7:6] only    |

| PC[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable           | PC[7:3] only    |

| RESET              | I/O       | I/O<br>(defaults<br>to<br>RESET) | Low (in<br>Reset<br>mode)          | Yes<br>(PD0<br>only) | Always<br>on for<br>RESET               | Yes                          | Alw <u>ays on</u> for<br>RESET | Yes             |

| VDD                | N/A       | N/A                              | N/A                                | N/A                  |                                         |                              | N/A                            | N/A             |

| VSS                | N/A       | N/A                              | N/A                                | N/A                  |                                         |                              | N/A                            | N/A             |

Note: PB6 and PB7 are available only in the devices without ADC.

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

**Table 5. Pin Characteristics (8-Pin Devices)**

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br>to<br>RESET)                                           | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

### Address Space

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O Port Control Registers

- The Program Memory contains addresses for all memory locations having executable code and/or data

- The Data Memory contains addresses for all memory locations that contain data only

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to the eZ8 CPU\_Core User Manual (UM0128), available for download at www.zilog.com.

#### **Register File**

The Register File address space in the Z8 Encore! XP<sup>TM</sup> MCU is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256B–1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

#### **Program Memory**

The eZ8 CPU supports 64KB of Program Memory address space. F0823 Series devices contain 1KB to 8KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash memory addresses

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

|                              | , ,                      |

|------------------------------|--------------------------|

| Program Memory Address (Hex) | Function                 |

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038-003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038-003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038-003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

|                              |                          |

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

| Program Memory Address (Hex) Function                                                          |                          |

|------------------------------------------------------------------------------------------------|--------------------------|

| Z8F0123 and Z8F0113 Products                                                                   |                          |

| 0000–0001                                                                                      | Flash Option Bits        |

| 0002–0003                                                                                      | Reset Vector             |

| 0004–0005                                                                                      | WDT Interrupt Vector     |

| 0006–0007                                                                                      | Illegal Instruction Trap |

| 0008–0037                                                                                      | Interrupt Vectors*       |

| 0038-003D                                                                                      | Oscillator Fail Traps*   |

| 003E-03FF                                                                                      | Program Memory           |

| Note: *See the <u>Trap and Interrupt Vectors in</u> for a list of the interrupt vectors and tr |                          |

#### **Data Memory**

Z8 Encore! XP F0823 Series does not use the eZ8 CPU's 64KB Data Memory address space.

#### **Flash Information Area**

Table 7 lists the F0823 Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

Table 7. F0823 Series Flash Memory Information Area Map

| Program Memory<br>Address (Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00-FE3F                       | Zilog Option Bits.                                                                         |

| FE40-FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60-FE7F                       | Zilog Calibration Data.                                                                    |

| FE80-FFFF                       | Reserved.                                                                                  |

### Register Map

Table 8 lists an address map of the Z8 Encore! XP F0823 Series Register File. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, nor all GPIO ports. Consider registers for unimplemented peripherals to be reserved.

Table 8. Register File Address Map

| Address (Hex)  | Register Description              | Mnemonic | Reset (Hex) | Page<br>No. |

|----------------|-----------------------------------|----------|-------------|-------------|

| General-Purpos | e RAM                             |          |             |             |

| Z8F0823/Z8F081 | 13 Devices                        |          |             |             |

| 000-3FF        | General-Purpose Register File RAM | _        | XX          |             |

| 400-EFF        | Reserved                          | _        | XX          |             |

| Z8F0423/Z8F041 | 13 Devices                        |          |             |             |

| 000–3FF        | General-Purpose Register File RAM | _        | XX          |             |

| 400-EFF        | Reserved                          | _        | XX          |             |

| Z8F0223/Z8F021 | 13 Devices                        |          |             |             |

| 000–1FF        | General-Purpose Register File RAM | _        | XX          |             |

| 200-EFF        | Reserved                          | _        | XX          |             |

| Z8F0123/Z8F011 | 13 Devices                        |          |             |             |

| 000-0FF        | General-Purpose Register File RAM | _        | XX          |             |

| 100-EFF        | Reserved                          | _        | XX          |             |

| Timer 0        |                                   |          |             |             |

| F00            | Timer 0 High Byte                 | T0H      | 00          | <u>84</u>   |

| F01            | Timer 0 Low Byte                  | T0L      | 01          | <u>84</u>   |

| F02            | Timer 0 Reload High Byte          | T0RH     | FF          | <u>85</u>   |

| F03            | Timer 0 Reload Low Byte           | T0RL     | FF          | <u>85</u>   |

| F04            | Timer 0 PWM High Byte             | T0PWMH   | 00          | <u>86</u>   |

| F05            | Timer 0 PWM Low Byte              | T0PWML   | 00          | <u>86</u>   |

| F06            | Timer 0 Control 0                 | T0CTL0   | 00          | <u>87</u>   |

| F07            | Timer 0 Control 1                 | T0CTL1   | 00          | <u>88</u>   |

| Timer 1        |                                   |          |             |             |

| F08            | Timer 1 High Byte                 | T1H      | 00          | <u>84</u>   |

| F09            | Timer 1 Low Byte                  | T1L      | 01          | <u>84</u>   |

Table 8. Register File Address Map (Continued)

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |