# X28C010, X28HT010

Data Sheet

### February 12, 2007

### FN8105.1

## 5V, Byte Alterable EEPROM

The Intersil X28C010/X28HT010 is a 128K x 8 EEPROM, fabricated with Intersil's proprietary, high performance, floating gate CMOS technology. Like all Intersil programmable non-volatile memories, the X28C010/X28HT010 is a 5V only device. The X28C010/X28HT010 features the JEDEC approved pin out for byte-wide memories, compatible with industry standard EEPROMs.

The X28C010/X28HT010 supports a 256-byte page write operation, effectively providing a 19µs/byte write cycle and enabling the entire memory to be typically written in less than 2.5 seconds. The X28C010/X28HT010 also features DATA Polling and Toggle Bit Polling, system software support schemes used to indicate the early completion of a write cycle. In addition, the X28C010/X28HT010 supports Software Data Protection option.

Intersil EEPROMs are designed and tested for applications requiring extended endurance. Data retention is specified to be greater than 100 years.

### Features

- Access time: 120ns

- · Simple byte and page write

- Single 5V supply

- No external high voltages or V<sub>PP</sub> control circuits

- Self-timed

- No erase before write

- No complex programming algorithms

- No overerase problem

- · Low power CMOS

- Active: 50mA

- Standby: 500µA

- Software data protection

- Protects data against system level inadvertent writes

- High speed page write capability

- Highly reliable Direct Write<sup>™</sup> cell

- Endurance: 100,000 write cycles

- Data retention: 100 years

- · Early end of write detection

- DATA polling

- Toggle bit polling

- X28HT010 is fuly functional @ +175°C

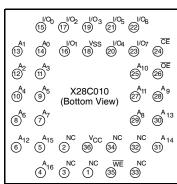

### **Pinouts**

| CERDIP<br>Flat Pack<br>SOIC (R) |    |            |    |   |                  |

|---------------------------------|----|------------|----|---|------------------|

| NC                              | 1  | $\bigcirc$ | 32 |   | Vcc              |

| A <sub>16</sub>                 | 2  |            | 31 |   | WE               |

| A <sub>15</sub>                 | 3  |            | 30 |   | NC               |

| A <sub>12</sub>                 | 4  |            | 29 |   | A <sub>14</sub>  |

| A <sub>7</sub>                  | 5  |            | 28 |   | A <sub>13</sub>  |

| A <sub>6</sub>                  | 6  |            | 27 |   | A <sub>8</sub>   |

| A <sub>5</sub>                  | 7  |            | 26 |   | Ag               |

| A <sub>4</sub>                  | 8  | X28C010    | 25 |   | A <sub>11</sub>  |

| A <sub>3</sub>                  | 9  | 7200010    | 24 |   | OE               |

| $A_2 \square$                   | 10 |            | 23 |   | A <sub>10</sub>  |

| A <sub>1</sub>                  | 11 |            | 22 |   | CE               |

| A <sub>0</sub>                  | 12 |            | 21 |   | 1/0 <sub>7</sub> |

| 1/0 <sub>0</sub>                | 13 |            | 20 |   | 1/0 <sub>6</sub> |

| I/O <sub>1</sub>                | 14 |            | 19 |   | I/O5             |

| I/O <sub>2</sub>                | 15 |            | 18 |   | I/04             |

| v <sub>ss</sub> ⊡               | 16 |            | 17 | þ | 1/0 <sub>3</sub> |

PGA

1

# **Ordering Information**

| PART NUMBER    | PART MARKING    | ACCESS<br>TIME | TEMP RANGE<br>(°C) | PACKAGE                        | PKG. DWG #   |

|----------------|-----------------|----------------|--------------------|--------------------------------|--------------|

| X28C010D-12    | X28C010D-12     | 120ns          | 0 to +70           | 32-Ld Cerdip                   | F32.6        |

| X28C010D-15    | X28C010D-15     | 150ns          | 0 to +70           | 32-Ld Cerdip                   | F32.6        |

| X28C010DI      | X28C010DI       | -              | -40 to +85         | 32-Ld Cerdip                   | F32.6        |

| X28C010DI-12   | X28C010DI-12    | 120ns          | -40 to +85         | 32-Ld Cerdip                   | F32.6        |

| X28C010DI-15   | X28C010DI-15    | 150ns          | -40 to +85         | 32-Ld Cerdip                   | F32.6        |

| X28C010DM      | X28C010DM       | -              | -55 to +125        | 32-Ld Cerdip                   | F32.6        |

| X28C010DM-12   | X28C010DM-12    | 120ns          | -55 to +125        | 32-Ld Cerdip                   | F32.6        |

| X28C010DM-15   | X28C010DM-15    | 150ns          | -55 to +125        | 32-Ld Cerdip                   | F32.6        |

| X28C010DMB-12  | C X28C010DMB-12 | 120ns          | MIL-STD-883        | 32-Ld Cerdip                   | F32.6        |

| X28C010DMB-15  | C X28C010DMB-15 | 150ns          | MIL-STD-883        | 32-Ld Cerdip                   | F32.6        |

| X28C010DMB-20  | C X28C010DMB-20 | 200ns          | MIL-STD-883        | 32-Ld Cerdip                   |              |

| X28C010FI-12   | X28C010FI-12    | 120ns          | -40 to +85         | 32-Ld Flat Pack                |              |

| X28C010FI-15   | X28C010FI-15    | 150ns          | -40 to +85         | 32-Ld Flat Pack                |              |

| X28C010FI-20   | X28C010FI-20    | 200ns          | -40 to +85         | 32-Ld Flat Pack                |              |

| X28C010FM      | X28C010FM       | -              | -55 to +125        | 32-Ld Flat Pack                |              |

| X28C010FM-12   | X28C010FM-12    | 120ns          | -55 to +125        | 32-Ld Flat Pack                |              |

| X28C010FMB-12  | C X28C010FMB-12 | 120ns          | MIL-STD-883        | 32-Ld Flat Pack                |              |

| X28C010FMB-15  | C X28C010FMB-15 | 150ns          | MIL-STD-883        | 32-Ld Flat Pack                |              |

| X28C010K-25    | X28C010K-25     | 250ns          | 0 to +70           | 36-Ld Pin Grid Array           | G36.760x760A |

| X28C010KM-12   | X28C010KM-12    | 120ns          | -55 to +125        | 36-Ld Pin Grid Array           | G36.760x760A |

| X28C010KM-25   | X28C010KM-25    | 250ns          | -55 to +125        | 36-Ld Pin Grid Array           | G36.760x760A |

| X28C010KMB-12  | C X28C010KMB-12 | 120ns          | MIL-STD-883        | 36-Ld Pin Grid Array           | G36.760x760A |

| X28C010KMB-15  | C X28C010KMB-15 | 150ns          | MIL-STD-883        | 36-Ld Pin Grid Array           | G36.760x760A |

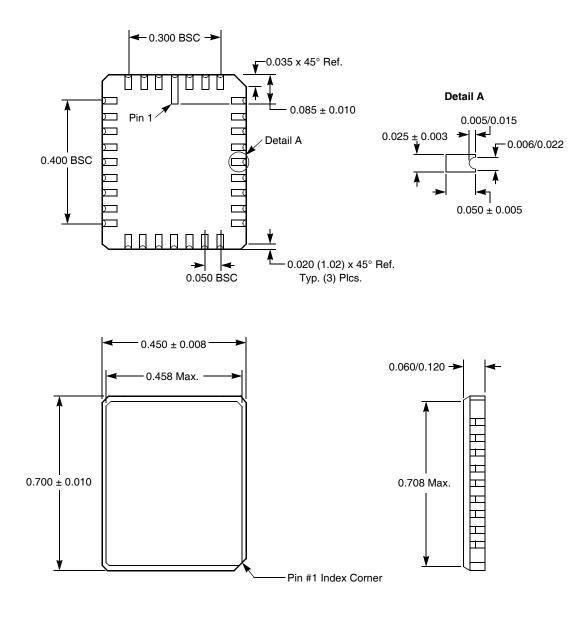

| X28C010NM-12   | X28C010NM-12    | 120ns          | -55 to +125        | 32-Ld Extended LCC             |              |

| X28C010NM-15   | X28C010NM-15    | 150ns          | -55 to +125        | 32-Ld Extended LCC             |              |

| X28C010NMB-12  | C X28C010NMB-12 | 120ns          | MIL-STD-883        | 32-Ld Extended LCC             |              |

| X28C010NMB-15  | C X28C010NMB-15 | 150ns          | MIL-STD-883        | 32-Ld Extended LCC             |              |

| X28C010RI-12   | X28C010RI-12    | 120ns          | -40 to +85         | 32-Ld Ceramic SOIC (Gull Wing) |              |

| X28C010RI-20   | X28C010RI-20    | 200ns          | -40 to +85         | 32-Ld Ceramic SOIC (Gull Wing) |              |

| X28C010RI-20T1 | X28C010RI-20    | 200ns          | -40 to +85         | 32-Ld Ceramic SOIC (Gull Wing) |              |

| X28C010RM-15   | X28C010RM-15    | 150ns          | -55 to +125        | 32-Ld Ceramic SOIC (Gull Wing) |              |

| X28C010RMB-25  | C X28C010RMB-25 | 250ns          | MIL-STD-883        | 32-Ld Ceramic SOIC (Gull Wing) |              |

| X28HT010W      |                 | 200ns          | -40 to +175        | Wafer                          |              |

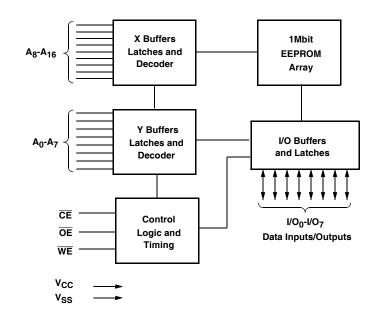

## Block Diagram

## **Pin Descriptions**

### Addresses (A<sub>0</sub>-A<sub>16</sub>)

The Address inputs select an 8-bit memory location during a read or write operation.

### Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/write operations. When  $\overline{CE}$  is HIGH, power consumption is reduced.

### Output Enable (OE)

The Output Enable input controls the data output buffers, and is used to initiate read operations.

### Data In/Data Out (I/O0-I/O7)

Data is written to or read from the X28C010/X28HT010 through the I/O pins.

### Write Enable (WE)

The Write Enable input controls the writing of data to the X28C010/X28HT010.

### Back Bias Voltage (VBB) (X28HT010 only)

It is required to provide -3V on pin 1. This negative voltage improves higher temperature functionality.

### Pin Names

| SYMBOL                             | DESCRIPTION       |

|------------------------------------|-------------------|

| A <sub>0</sub> -A <sub>16</sub>    | Address Inputs    |

| 1/0 <sub>0</sub> -1/0 <sub>7</sub> | Data Input/Output |

| WE                                 | Write Enable      |

| CE                                 | Chip Enable       |

| OE                                 | Output Enable     |

| V <sub>CC</sub>                    | +5V               |

| V <sub>SS</sub>                    | Ground            |

| NC                                 | No Connect        |

| V <sub>BB</sub> *                  | -3V               |

$^{\ast}\mathrm{V}_{BB}$  applies to X28HT010 only.

## **Device Operation**

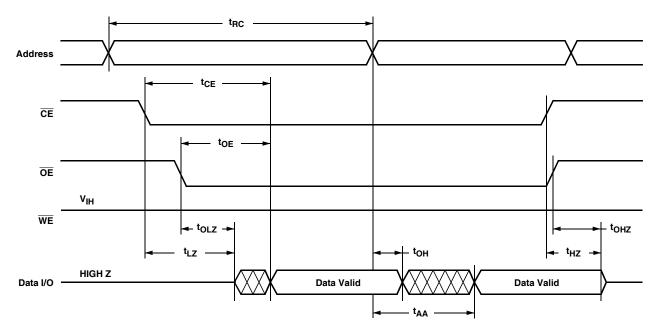

### Read

Read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This two line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedance state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

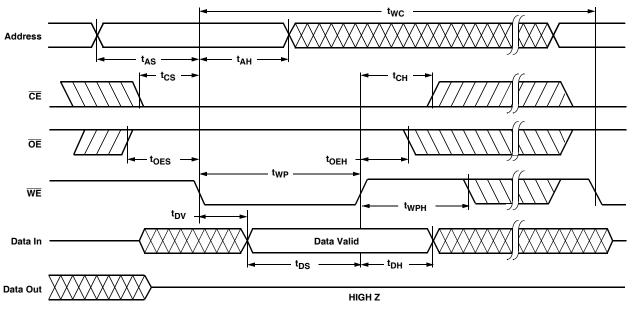

### Write

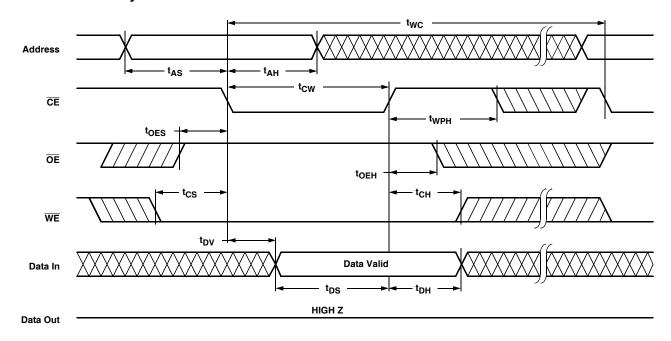

Write operations are initiated when both  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{OE}$  is HIGH. The X28C010/X28HT010 supports both a  $\overline{CE}$  and  $\overline{WE}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs last. Similarly, the data is latched internally by the rising edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs first. A byte write operation, once initiated, will automatically continue to completion, typically within 5ms.

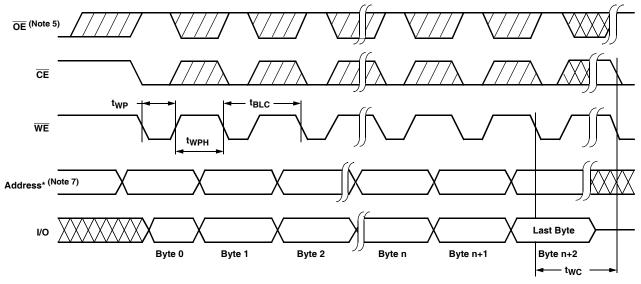

### Page Write Operation

The page write feature of the X28C010/X28HT010 allows the entire memory to be written in 5 seconds. Page write allows two to two hundred fifty-six bytes of data to be consecutively written to the X28C010/X28HT010 prior to the commencement of the internal programming cycle. The host can fetch data from another device within the system during a page write operation (change the source address), but the page address (A<sub>8</sub> through A<sub>16</sub>) for each subsequent valid write cycle to the part during this operation must be the same as the initial page address.

The page write mode can be initiated during any write operation. Following the initial byte write cycle, the host can write an additional one to two hundred fifty six bytes in the same manner as the first byte was written. Each successive byte load cycle, started by the  $\overline{WE}$  HIGH to LOW transition, must begin within 100µs of the falling edge of the preceding  $\overline{WE}$ . If a subsequent  $\overline{WE}$  HIGH to LOW transition is not detected within 100µs, the internal automatic programming cycle will commence. There is no page write window limitation. Effectively the page write window is infinitely wide, so long as the host continues to access the device within the byte load cycle time of 100µs.

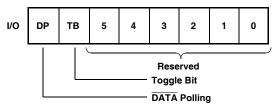

### Write Operation Status Bits

The X28C010/X28HT010 provides the user two write operation status bits. These can be used to optimize a system write cycle time. The status bits are mapped onto the I/O bus as shown in Figure 1.

FIGURE 1. STATUS BIT ASSIGNMENT

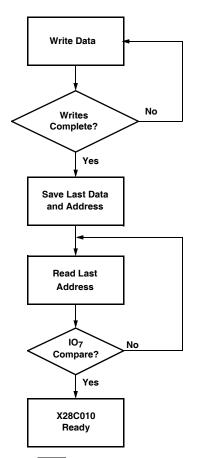

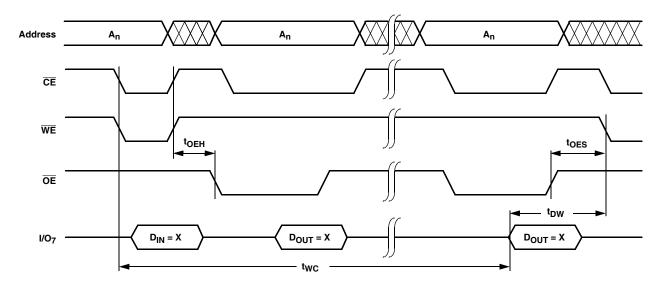

## DATA Polling (I/O7)

The X28C010/X28HT010 features DATA Polling as a method to indicate to the host system that the byte write or page write cycle has completed. DATA Polling allows a simple bit test operation to determine the status of the X28C010/X28HT010, eliminating additional interrupt inputs or external hardware. During the internal programming cycle, any attempt to read the last byte written will produce the complement of that data on  $I/O_7$  (i.e., write data = 0xxx xxxx, read data = 1xxx xxx). Once the programming cycle is complete,  $I/O_7$  will reflect true data. Note: If the X28C010/X28HT010 is in the protected state, and an illegal write operation is attempted, DATA Polling will not operate.

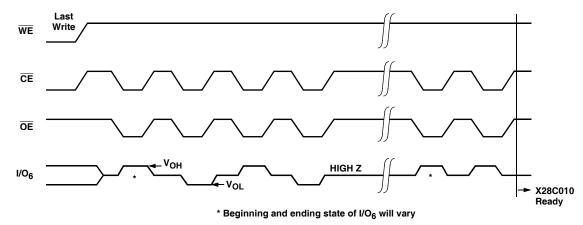

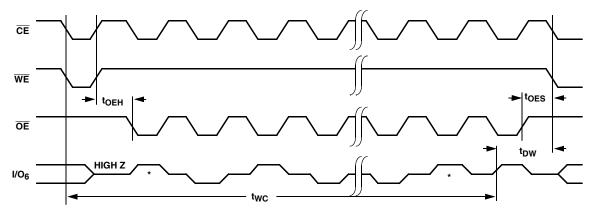

### Toggle Bit (I/O<sub>6</sub>)

The X28C010/X28HT010 also provides another method for determining when the internal write cycle is complete. During the internal programming cycle,  $I/O_6$  will toggle from HIGH to LOW and LOW to HIGH on subsequent attempts to read the device. When the internal cycle is complete the toggling will cease and the device will be accessible for additional read or write operations.

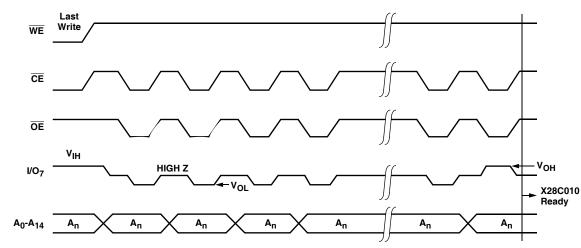

FIGURE 2. DATA POLLING BUS SEQUENCE

### DATA Polling I/O7

DATA Polling can effectively halve the time for writing to the X28C010/X28HT010. The timing diagram in Figure 2 illustrates the sequence of events on the bus. The software flow diagram in Figure 3 illustrates one method of implementing the routine.

FIGURE 3. DATA POLLING SOFTWARE FLOW

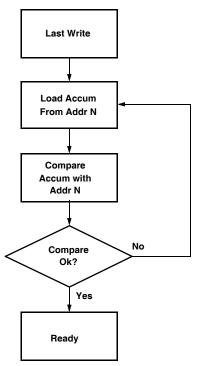

FIGURE 4. TOGGLE BIT BUS SEQUENCE

FIGURE 5. TOGGLE BIT SOFTWARE FLOW

The Toggle Bit can eliminate the software housekeeping chore of saving and fetching the last address and data written to a device in order to implement DATA Polling. This can be especially helpful in an array comprised of multiple X28C010/X28HT010 memories that is frequently updated. Toggle Bit Polling can also provide a method for status checking in multiprocessor applications. The timing diagram in Figure 4 illustrates the sequence of events on the bus. The software flow diagram in Figure 5 illustrates a method for polling the Toggle Bit.

## Hardware Data Protection

The X28C010/X28HT010 provides three hardware features that protect nonvolatile data from inadvertent writes.

- Noise Protection—A WE pulse less than 10ns will not initiate a write cycle.

- Default V\_{CC} Sense—All functions are inhibited when V\_{CC} is  $\leq$  3.5V.

- Write inhibit—Holding either OE LOW, WE HIGH, or CE HIGH will prevent an inadvertent write cycle during powerup and power-down, maintaining data integrity.

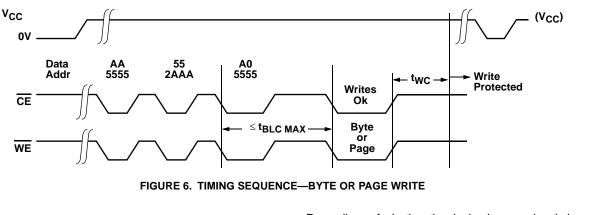

## Software Data Protection

The X28C010/X28HT010 offers a software controlled data protection feature. The X28C010/X28HT010 is shipped from Intersil with the software data protection NOT ENABLED: that is the device will be in the standard operating mode. In this mode data should be protected during power-up/-down operations through the use of external circuits. The host would then have open read and write access of the device once  $V_{CC}$  was stable.

The X28C010/X28HT010 can be automatically protected during power-up and power-down without the need for external circuits by employing the software data protection feature. The internal software data protection circuit is enabled after the first write operation utilizing the software algorithm. This circuit is nonvolatile and will remain set for the life of the device unless the reset command is issued.

Once the software protection is enabled, the X28C010/X28HT010 is also protected from inadvertent and accidental writes in the powered-up state. That is, the software algorithm must be issued prior to writing additional data to the device.

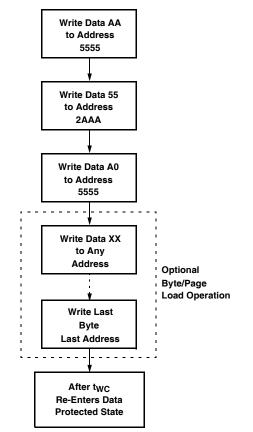

## Software Algorithm

Selecting the software data protection mode requires the host system to precede data write operations by a series of three write operations to three specific addresses. Refer to Figures 6 and 7 for the sequence. The three byte sequence opens the page write window enabling the host to write from one to two hundred fifty-six bytes of data. Once the page load cycle has been completed, the device will automatically be returned to the data protected state.

### Software Data Protection

FIGURE 7. WRITE SEQUENCE FOR SOFTWARE DATA PROTECTION

Regardless of whether the device has previously been protected or not, once the software data protection algorithm is used and data has been written, the X28C010/X28HT010 will automatically disable further writes unless another command is issued to cancel it. If no further commands are issued the X28C010/X28HT010 will be write protected during power-down and after any subsequent power-up. The state of  $A_{15}$  and  $A_{16}$  while executing the algorithm is don't care.

**Note:** Once initiated, the sequence of write operations should not be interrupted.

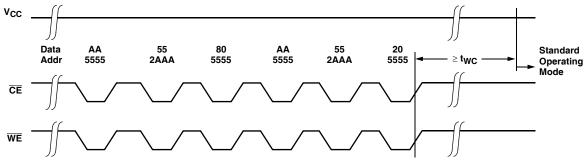

#### **Resetting Software Data Protection**

FIGURE 8. RESET SOFTWARE DATA PROTECTION TIMING SEQUENCE

#### FIGURE 9. SOFTWARE SEQUENCE TO DEACTIVATE SOFTWARE DATA PROTECTION

In the event the user wants to deactivate the software data protection feature for testing or reprogramming in an EEPROM programmer, the following six step algorithm will reset the internal protection circuit. After  $t_{WC}$ , the X28C010/X28HT010 will be in standard operating mode.

**Note:** Once initiated, the sequence of write operations should not be interrupted.

### System Considerations

Because the X28C010/X28HT010 is frequently used in large memory arrays, it is provided with a two line control architecture for both read and write operations. Proper usage can provide the lowest possible power dissipation and eliminate the possibility of contention where multiple I/O pins share the same bus.

To gain the most benefit, it is recommended that  $\overline{CE}$  be decoded from the address bus and be used as the primary device selection input. Both  $\overline{OE}$  and  $\overline{WE}$  would then be common among all devices in the array. For a read operation this assures that all deselected devices are in their standby mode and that only the selected device(s) is outputting data on the bus.

Because the X28C010/X28HT010 has two power modes, standby and active, proper decoupling of the memory array is of prime concern. Enabling  $\overline{CE}$  will cause transient current spikes. The magnitude of these spikes is dependent on the output capacitive loading of the I/Os. Therefore, the larger the array sharing a common bus, the larger the transient spikes. The voltage peaks associated with the current transients can be suppressed by the proper selection and placement of decoupling capacitors. As a minimum, it is recommended that a 0.1µF high frequency ceramic capacitor be used between V<sub>CC</sub> and V<sub>SS</sub> at each device. Depending on the size of the array, the value of the capacitor may have to be larger.

In addition, it is recommended that a  $4.7\mu$ F electrolytic bulk capacitor be placed between V<sub>CC</sub> and V<sub>SS</sub> for each eight devices employed in the array. This bulk capacitor is employed to overcome the voltage droop caused by the inductive effects of the PC board traces.

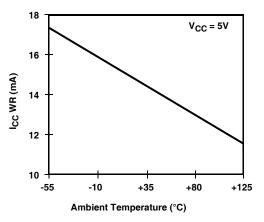

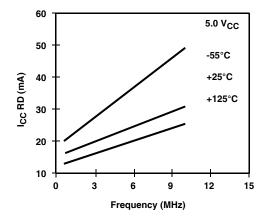

### Active Supply Current vs. Ambient Temperature

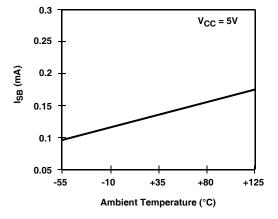

Standby Supply Current vs. Ambient Temperature

I<sub>CC</sub> (RD) by Temperature Over Frequency

#### **Absolute Maximum Ratings**

Temperature under bias

| X28C01010°C to +85°C                                         |  |

|--------------------------------------------------------------|--|

| X28C010I                                                     |  |

| X28C010M                                                     |  |

| X28HT01055°C to +175°C                                       |  |

| Storage temperature65°C to +150°C                            |  |

| Voltage on any pin with respect to V <sub>SS</sub> 1V to +7V |  |

| D.C. output current                                          |  |

| Lead temperature                                             |  |

| (soldering, 10 seconds)+300°C                                |  |

|                                                              |  |

#### **Recommended Operating Conditions**

| Commercial 0°C to +70°C        |

|--------------------------------|

| ndustrial40°C tp +85°C         |

| /lilitary                      |

| Supply Voltage                 |

| High Temperature40°C to +175°C |

CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions (above those indicated in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| SYMBOL                   | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                   | MIN | MAX                 | UNIT |

|--------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|------|

| ICC                      | V <sub>CC</sub> Current (Active) (TTL Inputs)      | $\label{eq:cell} \overline{CE} = \overline{OE} = V_{IL}, \ \overline{WE} = V_{IH}, \ All \ I/O's = Open, \\ Address \ Inputs = 0.4 V/2.4V \ Levels \ @ \ f = 5MHz \\ \end{array}$ |     | 50                  | mA   |

| I <sub>SB1</sub>         | V <sub>CC</sub> Current (Standby) (TTL Inputs)     | $\overline{CE} = V_{IH}, \overline{OE} = V_{IL}, All I/O's = Open, Other Inputs = V_{IH}$                                                                                         |     | 3                   | mA   |

| I <sub>SB2</sub>         | V <sub>CC</sub> Current (Standby) (CMOS<br>Inputs) | $\overline{CE} = V_{CC} - 0.3V$ , $\overline{OE} = V_{IL}$ , All I/O's = Open,<br>Other Inputs = $V_{CC}$                                                                         |     | 500                 | μA   |

| ILI                      | Input Leakage Current                              | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                                     |     | 10                  | μA   |

|                          |                                                    | $V_{IN} = V_{SS}$ to $V_{CC}$ (Note 2)                                                                                                                                            |     | 20                  | μA   |

| I <sub>LO</sub>          | Output Leakage Current                             | $V_{OUT} = V_{SS}$ to $V_{CC}$ , $\overline{CE} = V_{IH}$                                                                                                                         |     | 10                  | μA   |

|                          |                                                    | $V_{OUT} = V_{SS}$ to $V_{CC}$ , $\overline{CE} = V_{IH}$ (Note 2)                                                                                                                |     | 20                  | μA   |

| V <sub>IL</sub> (Note 1) | Input LOW Voltage                                  |                                                                                                                                                                                   | -1  | 0.8                 | V    |

|                          |                                                    | (Note 2)                                                                                                                                                                          | -1  | 0.6                 | V    |

| V <sub>IH</sub> (Note 1) | Input HIGH Voltage                                 |                                                                                                                                                                                   | 2   | V <sub>CC</sub> + 1 | V    |

|                          |                                                    | (Note 2)                                                                                                                                                                          | 2.2 | V <sub>CC</sub> + 1 | V    |

| V <sub>OL</sub>          | Output LOW Voltage                                 | I <sub>OL</sub> = 2.1mA                                                                                                                                                           |     | 0.4                 | V    |

|                          |                                                    | I <sub>OL</sub> = 1mA (Note 2)                                                                                                                                                    |     | 0.5                 | V    |

| V <sub>OH</sub>          | Output HIGH Voltage                                | Ι <sub>OH</sub> = -400μΑ                                                                                                                                                          | 2.4 |                     | V    |

|                          |                                                    | I <sub>OH</sub> = -400μA                                                                                                                                                          | 2.6 |                     | V    |

| I <sub>BB</sub>          | Back Bias Current                                  | V <sub>BB</sub> = -3V ±10% (Note 2)                                                                                                                                               |     | 200                 | μA   |

DC Electrical Specifications Over the recommended operating conditions, unless otherwise specified.

NOTE:

1.  $V_{\text{IL}}$  min. and  $V_{\text{IH}}$  max. are for reference only and are not tested.

2. X28HT010W

#### **Power-Up Timing**

| SYMBOL                    | PARAMETER                   | MAX | UNIT |

|---------------------------|-----------------------------|-----|------|

| t <sub>PUR</sub> (Note 3) | Power-up to Read operation  | 100 | μs   |

| t <sub>PUW</sub> (Note 3) | Power-up to Write operation | 5   | ms   |

### **Capacitance** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| SYMBOL                    | PARAMETER                | TEST CONDITIONS | МАХ | UNIT |

|---------------------------|--------------------------|-----------------|-----|------|

| C <sub>I/O</sub> (Note 3) | Input/Output capacitance | $V_{I/O} = 0V$  | 10  | pF   |

| C <sub>IN</sub> (Note 3)  | Input capacitance        | $V_{IN} = 0V$   | 10  | pF   |

NOTE:

3. This parameter is periodically sampled and not 100% tested.

### **Endurance and Data Retention**

| PARAMETER      | MIN     | MAX | UNIT            |

|----------------|---------|-----|-----------------|

| Endurance      | 10,000  |     | Cycles per byte |

| Endurance      | 100,000 |     | Cycles per page |

| Data Retention | 100     |     | Years           |

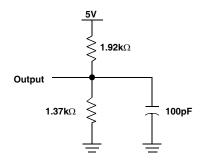

### A.C. Conditions of Test

| Input pulse levels             | 0V to 3V |

|--------------------------------|----------|

| Input rise and fall times      | 10ns     |

| Input and output timing levels | 1.5V     |

### **Mode Selection**

| CE | OE | WE | MODE                         | I/O              | POWER   |

|----|----|----|------------------------------|------------------|---------|

| L  | L  | Н  | Read                         | D <sub>OUT</sub> | Active  |

| L  | н  | L  | Write                        | D <sub>IN</sub>  | Active  |

| Н  | Х  | Х  | Standby and<br>Write Inhibit | High Z           | Standby |

| Х  | L  | Х  | Write Inhibit                | —                | _       |

| Х  | Х  | Н  | Write Inhibit                | _                | _       |

## Equivalent A.C. Load Circuit

## Symbol Table

| WAVEFORM | INPUTS                            | OUTPUTS                             |

|----------|-----------------------------------|-------------------------------------|

|          | Must be<br>steady                 | Will be<br>steady                   |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH  |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW  |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known     |

|          | N/A                               | Center Line<br>is High<br>Impedance |

### AC Electrical Specifications Over the recommended operating conditions, unless otherwise specified.

|                           |                                 | X28C010-12 |     | X28C010-15 |     | X28C010-20,<br>X28HT010W |     | X28C010-25 |     |      |

|---------------------------|---------------------------------|------------|-----|------------|-----|--------------------------|-----|------------|-----|------|

| SYMBOL                    | PARAMETER                       | MIN        | MAX | MIN        | MAX | MIN                      | MAX | MIN        | MAX | UNIT |

| READ CYCLE                | LIMITS                          |            |     |            |     |                          |     |            |     |      |

| t <sub>RC</sub>           | Read cycle time                 | 120        |     | 150        |     | 200                      |     | 250        |     | ns   |

| <sup>t</sup> CE           | Chip enable access time         |            | 120 |            | 150 |                          | 200 |            | 250 | ns   |

| t <sub>AA</sub>           | Address access time             |            | 120 |            | 150 |                          | 200 |            | 250 | ns   |

| tOE                       | Output enable access time       |            | 50  |            | 50  |                          | 50  |            | 50  | ns   |

| t <sub>LZ</sub> (Note 4)  | CE LOW to active output         | 0          |     | 0          |     | 0                        |     | 0          |     | ns   |

| t <sub>OLZ</sub> (Note 4) | OE LOW to active output         | 0          |     | 0          |     | 0                        |     | 0          |     | ns   |

| t <sub>HZ</sub> (Note 4)  | CE HIGH to high Z output        |            | 50  |            | 50  |                          | 50  |            | 50  | ns   |

| t <sub>OHZ</sub> (Note 4) | OE HIGH to high Z output        |            | 50  |            | 50  |                          | 50  |            | 50  | ns   |

| tон                       | Output hold from address change | 0          |     | 0          |     | 0                        |     | 0          |     | ns   |

### Read Cycle

NOTE:

4. t<sub>LZ</sub> min.,t<sub>HZ</sub>, t<sub>OLZ</sub> min., and t<sub>OHZ</sub> are periodically sampled and not 100% tested. t<sub>HZ</sub> max. and t<sub>OHZ</sub> max. are measured, with C<sub>L</sub> = 5pF, from the point when CE or OE return HIGH (whichever occurs first) to the time when the outputs are no longer driven.

| SYMBOL                   | PARAMETER           | MIN | MAX | UNIT |

|--------------------------|---------------------|-----|-----|------|

| t <sub>WC</sub> (Note 5) | Write cycle time    |     | 10  | ms   |

| t <sub>AS</sub>          | Address setup time  | 0   |     | ns   |

| t <sub>AH</sub>          | Address hold time   | 50  |     | ns   |

| tcs                      | Write setup time    | 0   |     | ns   |

| <sup>t</sup> CH          | Write hold time     | 0   |     | ns   |

| t <sub>CW</sub>          | CE pulse width      | 100 |     | ns   |

| tOES                     | OE HIGH setup time  | 10  |     | ns   |

| <sup>t</sup> OEH         | OE HIGH hold time   | 10  |     | ns   |

| t <sub>WP</sub>          | WE pulse width      | 100 |     | ns   |

| tWPH                     | WE HIGH recovery    | 100 |     | ns   |

| t <sub>DV</sub>          | Data valid          |     | 1   | μs   |

| t <sub>DS</sub>          | Data setup          | 50  |     | ns   |

| <sup>t</sup> DH          | Data hold           | 0   |     | ns   |

| <sup>t</sup> DW          | Delay to next write | 10  |     | μs   |

| t <sub>BLC</sub>         | Byte load cycle     | 0.2 | 100 | μs   |

### Write Cycle Limits

## WE Controlled Write Cycle

NOTE:

5. t<sub>WC</sub> is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is the maximum time the device requires to complete internal write operation.

## CE Controlled Write Cycle

### Page Write Cycle

\*For each successive write within the page write operation, A<sub>8</sub>-A<sub>16</sub> should be the same or writes to an unknown address could occur.

#### NOTES:

- 6. Between successive byte writes within a page write operation,  $\overline{OE}$  can be strobed LOW: e.g. this can be done with  $\overline{CE}$  and  $\overline{WE}$  HIGH to fetch data from another memory device within the system for the next write; or with  $\overline{WE}$  HIGH and  $\overline{CE}$  LOW effectively performing a polling operation.

- 7. The timings shown above are unique to page write operations. Individual byte load operations within the page write must conform to either the CE or WE controlled write cycle timing.

#### DATA Polling Timing Diagram (Note 8)

## Toggle Bit Timing Diagram

$^{\ast}$  I/O\_6 beginning and ending state will vary.

NOTE:

8. Polling operations are by definition read cycles and are therefore subject to read cycle timings.

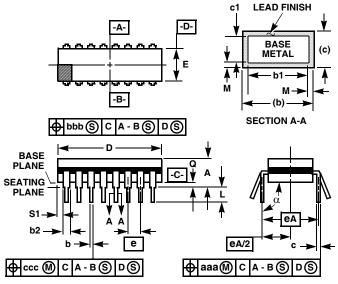

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- 2. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- 4. Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

| F32.6 MIL-STD-1835 GDIP1-T32 (D-16, CONFIGURATION A) |

|------------------------------------------------------|

| 32 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE       |

|        | INCHES    |        | MILLIM |       |       |  |

|--------|-----------|--------|--------|-------|-------|--|

| SYMBOL | MIN MAX   |        | MIN    | MAX   | NOTES |  |

| А      | -         | 0.232  | -      | 5.92  | -     |  |

| b      | 0.014     | 0.026  | 0.36   | 0.66  | 2     |  |

| b1     | 0.014     | 0.023  | 0.36   | 0.58  | 3     |  |

| b2     | 0.045     | 0.065  | 1.14   | 1.65  | -     |  |

| b3     | 0.023     | 0.045  | 0.58   | 1.14  | 4     |  |

| С      | 0.008     | 0.018  | 0.20   | 0.46  | 2     |  |

| c1     | 0.008     | 0.015  | 0.20   | 0.38  | 3     |  |

| D      | -         | 1.690  | -      | 42.95 | 5     |  |

| Е      | 0.500     | 0.610  | 12.70  | 15.49 | 5     |  |

| е      | 0.100 BSC |        | 2.54   | -     |       |  |

| eA     | 0.600 BSC |        | 15.24  | -     |       |  |

| eA/2   | 0.300 BSC |        | 7.62   | -     |       |  |

| L      | 0.125     | 0.200  | 3.18   | 5.08  | -     |  |

| Q      | 0.015     | 0.060  | 0.38   | 1.52  | 6     |  |

| S1     | 0.005     | -      | 0.13   | -     | 7     |  |

| α      | 90°       | 105°   | 90°    | 105°  | -     |  |

| aaa    | -         | 0.015  | -      | 0.38  | -     |  |

| bbb    | -         | 0.030  | -      | 0.76  | -     |  |

| ccc    | -         | 0.010  | -      | 0.25  | -     |  |

| М      | -         | 0.0015 | -      | 0.038 | 2, 3  |  |

| Ν      | 32        |        | 3      | 8     |       |  |

Rev. 0 8/06

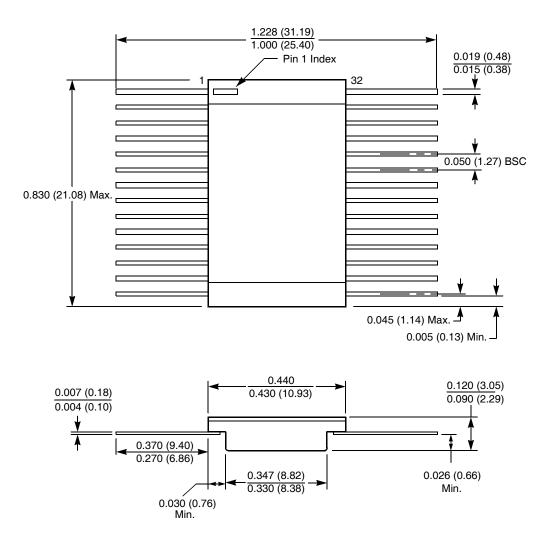

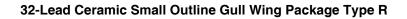

### 32-Lead Ceramic Flat Pack Type F

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

NOTES: 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS) 2. TOLERANCE: ±1% NLT±0.005 (0.127)

NOTES: 1. ALL DIMENSIONS IN INCHES 2. FORMED LEAD SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITHIN 0.004 INCHES

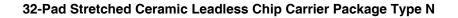

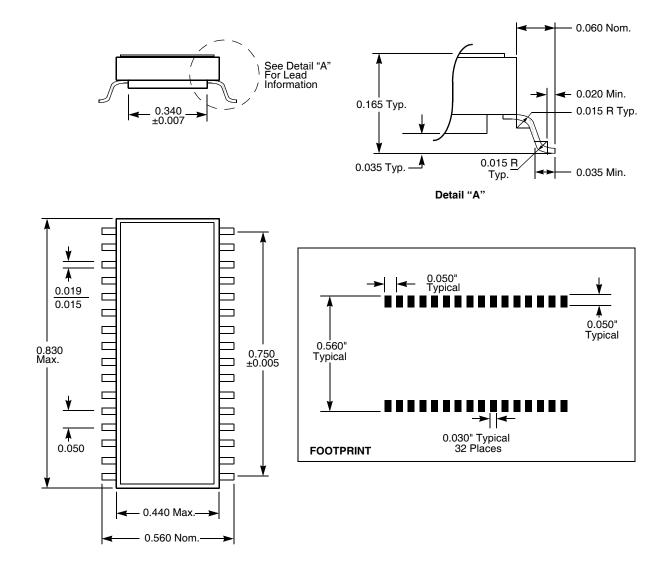

36 Lead Ceramic Pin Grid Array Package Package Code G36.760x760A

#### NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331