## Octal, High-Speed, Industrial, High-Side Switch

### **General Description**

The MAX14900E is an octal power switch that features per-channel configuration for high-side or push-pull operation. Low propagation delay, high-rate load-switching makes the device suitable for next-generation high-speed PLC systems. Each high-side switch sources 850mA continuous current with a low 165m $\Omega$  (max) on-resistance at 500mA at  $T_A$  = +125°C. The high-side switches feature 2µs (max) input-to-output propagation delay when driving resistive loads. Long cables can be driven with switching rates of up to 100kHz for PWM/PPO control in push-pull operation. Multiple high-side switches can be connected in parallel to achieve higher drive currents. The device features a wide supply input range of 10V to 36V.

The MAX14900E is configured, monitored, and driven by an SPI and/or parallel interface. In parallel mode, eight logic inputs directly control the outputs and the serial interface can be used for configuration/monitoring. Serial mode utilizes the serial interface for both setting and configuration, and features CRC error detection to ensure robust SPI communication.

Current limiting and per-channel thermal shutdown protect each switch/driver. The device features a global diagnostics output as well as per-channel diagnostics and monitoring through the serial interface.

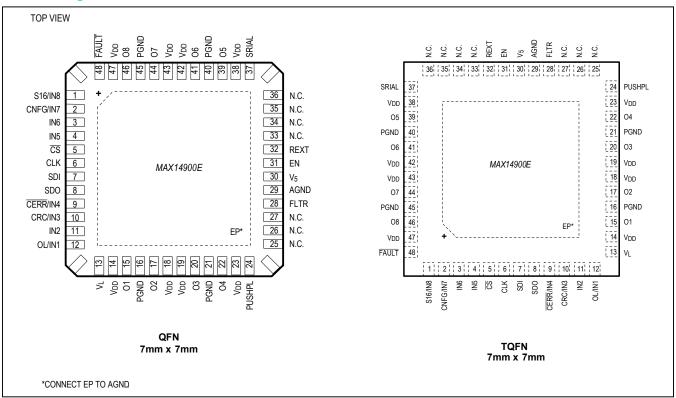

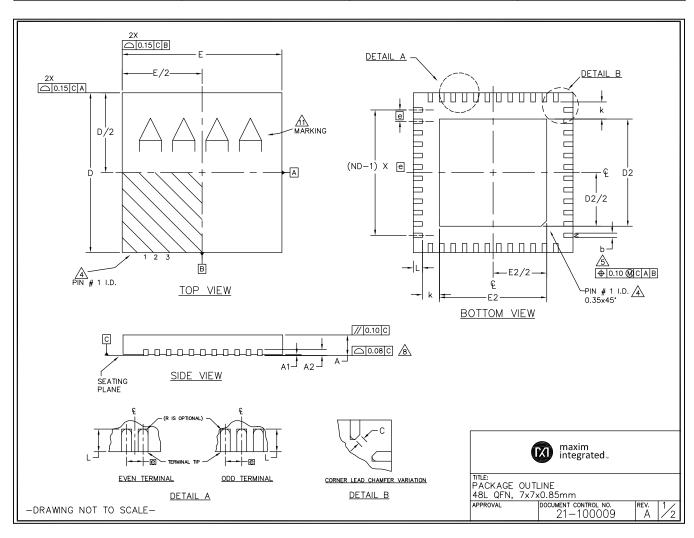

The MAX14900E is available in a 48-pin (7mm x 7mm) QFN-EP or standard 48-pin TQFN-EP package, and is specified over the  $-40^{\circ}$ C to  $+125^{\circ}$ C temperature range.

### **Applications**

- Programmable Logic Controllers

- High-Density Digital Output Modules

- Motor Controllers

- PWM/PPO Control

<u>Ordering Information</u> and <u>Typical Operating Circuit</u> appear at end of data sheet.

### **Benefits and Features**

- Low Power for High-Density Modules

- · 3mA (max) Total Supply Current

- 165mΩ (max) High-Side R<sub>ON</sub> at +125°C

- Fast Switching Ideal for Accurate, High-Speed Control Systems

- 2µs Propagation Delays (High-Side Mode)

- 0.8µs Propagation Delays (Push-Pull Mode)

- 100kHz (max) Push-Pull Mode Switching Rate

- Extensive Fault Feedback Eases Maintenance and Reduces Installation Time

- · Global and Per-Channel Diagnostics

- · Open Load/Wire Detection

- · Thermal Shutdown Fault Indication

- · Output Logic State Feedback

- · Undervoltage Lockout

- Small Packages with Serial Interface Allows Making High-Density Modules

- Daisy-Chainable SPI Minimizes Isolation Cost

- 7mm x 7mm, 48-Pin QFN and TQFN Packages

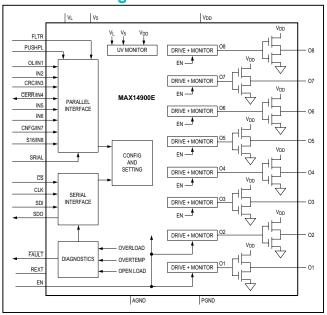

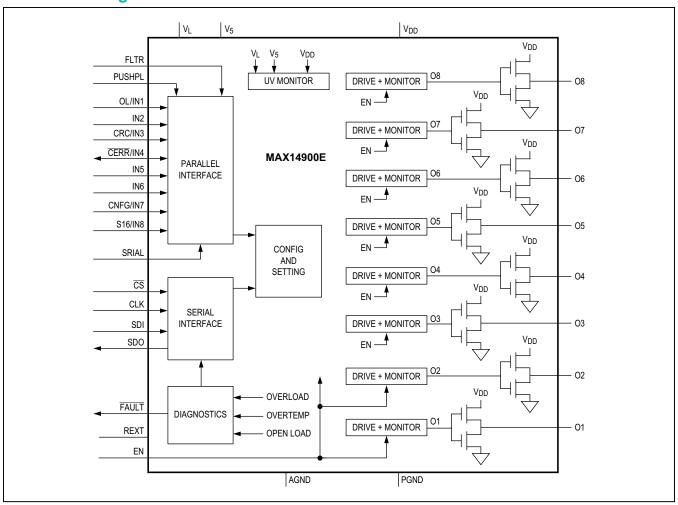

### **Functional Diagram**

## **Absolute Maximum Ratings**

| (All voltages referenced to AGND = PGI                            | ND.)                   |

|-------------------------------------------------------------------|------------------------|

| V <sub>DD</sub>                                                   | 0.3V to +40V           |

| O                                                                 |                        |

| V <sub>5</sub> , V <sub>L</sub> , <del>FAULT</del> , IN_, PUSHPL, |                        |

| FLTR, SRIAL, CLK, SDI, CS, EN                                     | 0.3V to +6V            |

| REXT                                                              | 0.3V to $(V_5 + 0.3V)$ |

| SDO                                                               | 0.3V to $(V_L + 0.3V)$ |

| Continuous Reverse Current (O_)                                   | 2.0A                   |

| Inductive Kickback Current (O_)                                   | 1.9A                   |

|                                                                   |                        |

| Continuous Current (Any Other Terminal)             | ±100mA             |

|-----------------------------------------------------|--------------------|

| Continuous Power Dissipation $(T_A = +70^{\circ}C)$ |                    |

| (derate 38.5mW/°C above +70°C)                      | 4400mW             |

| Operating Temperature Range                         | 40°C to +125°C     |

| Junction Temperature                                | Internally Limited |

| Storage Temperature Range                           | 65°C to +150°C     |

| Lead Temperature (soldering, 10s)                   | +300°C             |

| Soldering Temperature (reflow)                      | +260°C             |

|                                                     |                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | .18°C/W |

|-----------------------------------------------------------|---------|

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    | 1°C/W   |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Electrical Characteristics**

$(V_{DD}$  = 10V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                          | SYMBOL                     | CONDITIONS                                   | MIN | TYP | MAX | UNITS |  |

|----------------------------------------------------|----------------------------|----------------------------------------------|-----|-----|-----|-------|--|

| DC CHARACTERISTICS                                 |                            |                                              |     |     |     |       |  |

| V <sub>DD</sub> Supply Voltage                     | V <sub>DD</sub>            |                                              | 10  |     | 36  | V     |  |

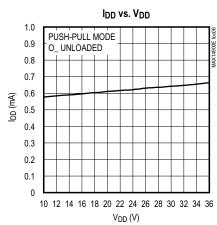

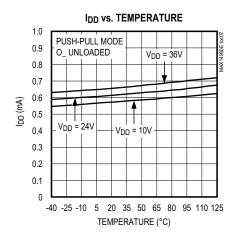

| V - Supply Current                                 | 1                          | EN = high, O_ in push-pull mode and unloaded |     | 0.7 | 1.5 | mA    |  |

| V <sub>DD</sub> Supply Current                     | I <sub>DD</sub>            | EN = high, O_ in high-side mode and unloaded |     | 0.7 | 1.5 | IIIA  |  |

| V <sub>DD</sub> Disable Supply Current             | I <sub>DD_DIS</sub>        | EN = low                                     |     | 0.7 | 1.5 | mA    |  |

| V <sub>DD</sub> Undervoltage-Lockout<br>Threshold  | VDD_<br>UVLO               | V <sub>5</sub> = 5V, V <sub>DD</sub> rising  | 7.0 | 7.8 | 8.5 | V     |  |

| V <sub>DD</sub> Undervoltage-Lockout<br>Hysteresis | V <sub>DD</sub> _<br>UVHYS | V <sub>5</sub> = 5V                          |     | 2.5 |     | V     |  |

| V <sub>5</sub> Supply Voltage                      | V <sub>5</sub>             |                                              | 4.5 |     | 5.5 | V     |  |

| V <sub>5</sub> Supply Current                      | I <sub>5</sub>             | O_ in push-pull or high-side mode,           |     | 0.9 | 1.5 | mA    |  |

| V <sub>5</sub> Undervoltage-Lockout<br>Threshold   | V <sub>5_UVLO</sub>        | V <sub>DD</sub> = 24V, V <sub>5</sub> rising | 3.8 | 4   | 4.2 | V     |  |

| V <sub>5</sub> Undervoltage-Lockout<br>Hysteresis  | V <sub>5_UVHYS</sub>       | V <sub>DD</sub> = 24V                        |     | 0.3 |     | V     |  |

| V <sub>5</sub> POR Threshold                       | V <sub>5_POR</sub>         |                                              |     | 1.6 | 2.4 | V     |  |

| V <sub>L</sub> Supply Voltage                      | VL                         |                                              | 2.5 |     | 5.5 | V     |  |

| V <sub>L</sub> Supply Current                      | ΙL                         | Logic inputs unconnected                     |     | 9   | 40  | μA    |  |

| V <sub>L</sub> POR Threshold                       | V <sub>L_POR</sub>         |                                              |     | 1.6 | 2.4 | V     |  |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = 10V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL              | CC                                                          | ONDITIONS                                                                    | MIN                  | TYP                     | MAX                  | UNITS |

|------------------------------------------|---------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|-------------------------|----------------------|-------|

| DRIVER OUTPUTS (O_)                      |                     | 1                                                           |                                                                              | 1                    |                         |                      |       |

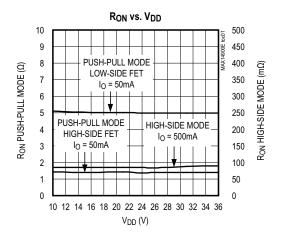

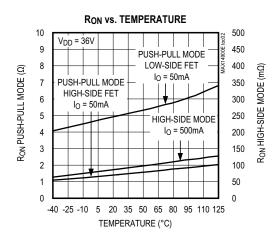

| High-Side Mode On-Resistance             | R <sub>ON_HS</sub>  | High-side mode, EN = high, O_ = high, IO = 500mA            |                                                                              |                      | 85                      | 165                  | mΩ    |

| High-Side Mode Current Limit             | I <sub>LIM_HS</sub> | High-side mode,                                             | EN = high, O_ = high                                                         | 1.4                  | 1.7                     | 2.0                  | Α     |

| High-Side Mode Leakage<br>Current        | I <sub>LKG_HS</sub> | EN = low, V <sub>O</sub> _ =                                | 0V                                                                           | -1                   |                         | +20                  | μΑ    |

| Push-Pull Mode On-Resistance             | R <sub>ON_PP</sub>  | Push-pull<br>mode,<br>EN = high                             | I <sub>O</sub> _ = +50mA,<br>O_ = high<br>I <sub>O</sub> _ = -50mA, O_ = low |                      | 1.6<br>5.2              | 4                    | Ω     |

| D 1 D 11 D 11 11                         |                     | Push-pull mode,                                             | $0V < V_{O} < V_{DD} - 3V,$<br>$O_{D} = high$                                | 200                  | 500                     |                      |       |

| Push-Pull Current Limit                  | ILIM_PP             | EN = high,<br>during blanking<br>time                       | 3V < V <sub>O</sub> _ < V <sub>DD</sub> ,<br>O_ = low                        | 200                  | 300                     |                      | mA    |

| Current-Limit Autoretry Blanking Time    | t <sub>BLANK</sub>  | Push-pull mode,<br>O_ connected to                          | <u> </u>                                                                     |                      | 90                      |                      | μs    |

| Current-Limit Autoretry Off-Time         | t <sub>RETRY</sub>  | Push-pull mode,<br>O_ connected to                          | <u> </u>                                                                     |                      | 11                      |                      | ms    |

| OPEN-LOAD DETECTION (O_)                 |                     |                                                             |                                                                              |                      |                         |                      |       |

| Open-Load Pullup Current                 | I <sub>OL</sub>     | High-side mode,<br>0V < V <sub>O</sub> _ < (V <sub>DE</sub> | O_ = off,<br>o – 2V), OL detect = on                                         | 65                   | 80                      | 110                  | μΑ    |

| Open-Load and Status-Detect<br>Threshold | V <sub>TOL</sub> _  | EN = high, OL de high-side mode,                            | •                                                                            | 6.3                  | 7                       | 7.7                  | ٧     |

| LOGIC INPUTS (IN_, PUSHPL, F             | LTR, SRIAL,         | CLK, SDI, CS, EN)                                           |                                                                              |                      |                         |                      |       |

| Input Logic-High Voltage                 | V <sub>IH</sub>     |                                                             |                                                                              | 0.7 x V <sub>L</sub> |                         |                      | V     |

| Input Logic-Low Voltage                  | V <sub>IL</sub>     |                                                             |                                                                              |                      |                         | 0.3 x V <sub>L</sub> | V     |

| Input Threshold Hysteresis               | V <sub>ITHYS</sub>  |                                                             |                                                                              |                      | 0.1 x<br>V <sub>L</sub> |                      | V     |

| Input Pulldown/Pullup Resistor           | R <sub>PULL</sub>   | (Note 3)                                                    |                                                                              | 140                  | 200                     | 270                  | kΩ    |

| LOGIC OUTPUTS (FAULT, CERR/IN4, SDO)     |                     |                                                             |                                                                              |                      |                         |                      |       |

| Open-Drain Output Logic-Low<br>Voltage   | V <sub>ODL</sub>    | I <sub>SINK</sub> = 5mA                                     |                                                                              |                      |                         | 0.33                 | V     |

| Open-Drain Output Leakage<br>Current     | I <sub>LKG_OD</sub> | SRIAL = high, output not asserted, VOUT = 5.5V              |                                                                              | -1                   |                         | +1                   | μΑ    |

| SDO Output Logic-High Voltage            | V <sub>OH</sub>     | I <sub>SOURCE</sub> = 5mA                                   |                                                                              | V <sub>L</sub> - 0.3 | 3                       |                      | V     |

| SDO Output Logic-Low Voltage             | V <sub>OL</sub>     | I <sub>SINK</sub> = 5mA                                     |                                                                              |                      |                         | 0.33                 | V     |

| SDO Pulldown Resistor                    | R <sub>SDO</sub>    | CS = high                                                   |                                                                              | 140                  | 200                     | 270                  | kΩ    |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = 10V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                      | SYMBOL                                         | CONDITIONS                                                                                                                                                                                                                                                   | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| TIMING CHARACTERISTICS                         |                                                |                                                                                                                                                                                                                                                              |      |      | -    | ,     |

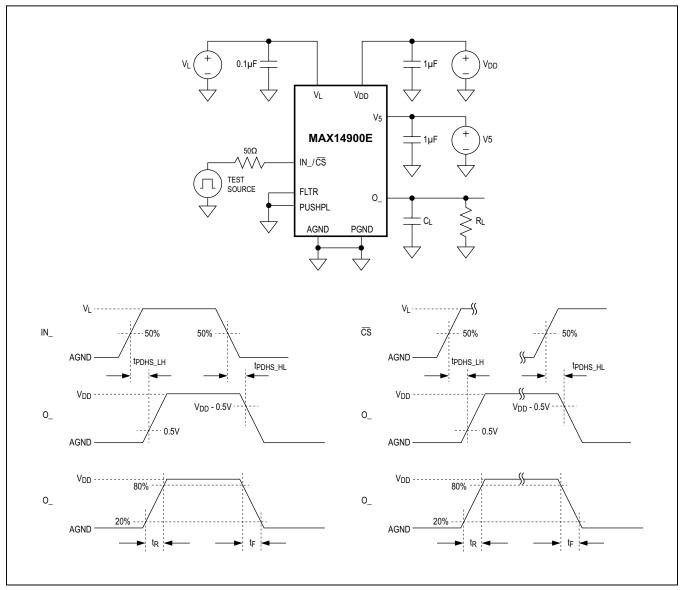

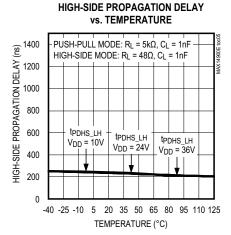

| High-Side Mode LTH Output<br>Propagation Delay | tpDHS_LH                                       | High-side mode, delay from IN_ transition (parallel mode) or $\overline{CS}$ rising-edge (serial mode) to O_ rising by 0.5V; R <sub>L</sub> = 48 $\Omega$ , C <sub>L</sub> = 1nF, t <sub>R</sub> /t <sub>F</sub> $\leq$ 20ns, FLTR = low, Figure 1 (Note 4)  |      | 0.2  | 1    | μs    |

| High-Side Mode HTL Output<br>Propagation Delay | <sup>t</sup> PDHS_HL                           | High-side mode, delay from IN_ transition (parallel mode) or $\overline{CS}$ rising-edge (serial mode) to O_ falling by 0.5V, R <sub>L</sub> = 48 $\Omega$ , C <sub>L</sub> = 1nF, t <sub>R</sub> /t <sub>F</sub> $\leq$ 20ns, FLTR = low, Figure 1 (Note 4) |      | 0.9  | 2    | μs    |

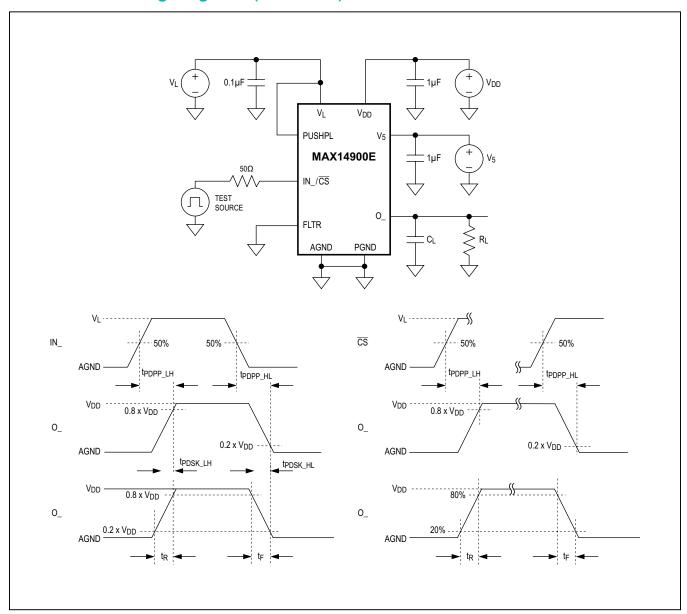

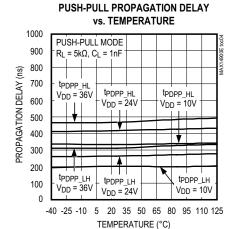

| Push-Pull Output LTH<br>Propagation Delay      | tPDPP_LH                                       | Push-pull mode, delay from IN_ transition (parallel mode) or $\overline{CS}$ rising-edge (serial mode) to O_ settling to within 0.8 x V <sub>DD</sub> , R <sub>L</sub> = 5k $\Omega$ , C <sub>L</sub> = 1nF, FLTR = low, Figure 2                            |      | 0.3  | 0.7  | μs    |

| Push-Pull Output HTL<br>Propagation Delay      | tPDPP_HL                                       | Push-pull mode, delay from IN_ transition (parallel mode) or $\overline{CS}$ rising-edge (serial mode) to O_ settling to within 0.2 x V <sub>DD</sub> , R <sub>L</sub> = 5k $\Omega$ , C <sub>L</sub> = 1nF, FLTR = low, Figure 2                            |      | 0.3  | 0.8  | μs    |

|                                                |                                                | High-side mode, 20% to 80%, $R_L$ = 48 $\Omega$ , $C_L$ = 1nF, Figure 1                                                                                                                                                                                      |      | 1.5  | 4    |       |

| Output Rise and Fall Time                      | t <sub>R</sub> , t <sub>F</sub>                | Push-pull mode, 20% to 80%, $R_L$ = 5k $\Omega$ , $C_L$ = 1nF, Figure 2                                                                                                                                                                                      |      | 0.1  | 0.4  | μs    |

|                                                |                                                | Push-pull mode, 20% to 80%, $R_L$ = 240 $\Omega$ , $V_{CC}$ = 24V, $C_L$ = 1nF, Figure 2                                                                                                                                                                     |      | 0.1  | 0.4  |       |

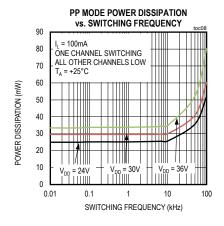

| Output Switching Rate                          | f <sub>O</sub>                                 | Push-pull mode, $R_L = 5k\Omega$ or $I_L = 100mA$ to ground, $C_L = 1nF$ , $SRIAL = low$                                                                                                                                                                     |      |      | 100  | kHz   |

| Channel-to-Channel Skew                        | t <sub>PDSK_LH</sub> ,<br>t <sub>PDSK_HL</sub> | Push-pull mode, Figure 2 (Note 5)                                                                                                                                                                                                                            | -100 |      | +100 | ns    |

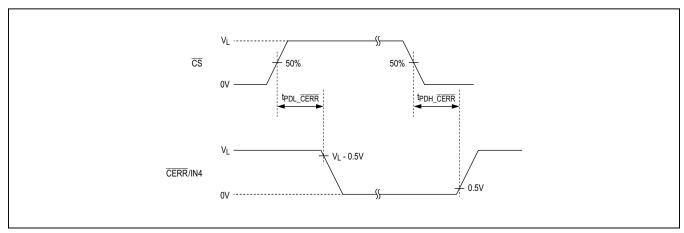

| CRC Error-Detect Propagation<br>Delay          | t <sub>PDL</sub><br>CERR                       | Error detected on SDI data, from $\overline{\text{CS}}$ rising-edge to $\overline{\text{CERR}}/\text{IN4}$ falling-edge; I <sub>SOURCE</sub> = 5mA, Figure 3                                                                                                 |      | 14.5 | 30   | ns    |

| CRC Error-Clear Propagation<br>Delay           | t <sub>PDH_CERR</sub>                          | Error cleared, from $\overline{\text{CS}}$ rising-edge to $\overline{\text{CERR}}$ /IN4 rising, I <sub>SOURCE</sub> = 5mA, Figure 3                                                                                                                          |      | 17   | 40   | ns    |

| Pulse Length of Rejected Glitch                | t <sub>GL</sub>                                | FLTR = high                                                                                                                                                                                                                                                  | 0    |      | 80   | ns    |

| Admitted Pulse Length                          |                                                | FLTR = high                                                                                                                                                                                                                                                  | 300  |      |      | ns    |

| Glitch Filter Propagation<br>Delay Time        | t <sub>PDGF</sub>                              | FLTR = high                                                                                                                                                                                                                                                  |      | 140  | 300  | ns    |

### **Electrical Characteristics (continued)**

$(V_{DD}$  = 10V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                             | SYMBOL                | CONDITIONS                                            | MIN | TYP  | MAX | UNITS |  |

|---------------------------------------|-----------------------|-------------------------------------------------------|-----|------|-----|-------|--|

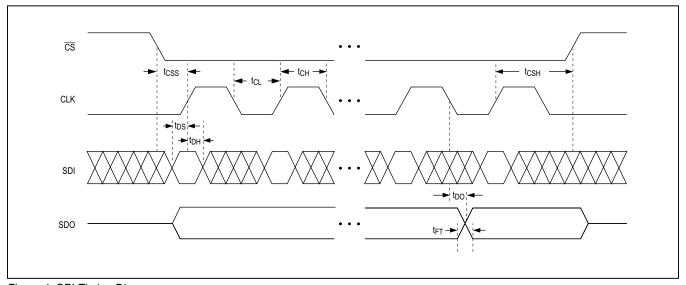

| SPI TIMING CHARACTERISTICS (Figure 4) |                       |                                                       |     |      |     |       |  |

| CLK Clock Period                      | t <sub>CH+CL</sub>    |                                                       | 50  |      |     | ns    |  |

| CLK Pulse-Width High                  | t <sub>CH</sub>       |                                                       | 5   |      |     | ns    |  |

| CLK Pulse-Width Low                   | t <sub>CL</sub>       |                                                       | 5   |      |     | ns    |  |

| CS Fall-to-CLK Rise Time              | 4                     | FLTR = low (Note 4)                                   | 5   |      |     | no    |  |

| CS Fail-to-CLK Rise Time              | tcss                  | FLTR = high                                           | 300 |      |     | ns    |  |

| SDI Hold Time                         | t <sub>DH</sub>       |                                                       | 5   |      |     | ns    |  |

| SDI Setup Time                        | t <sub>DS</sub>       |                                                       | 5   |      |     | ns    |  |

| Output Data Propagation Delay         | t <sub>DO</sub>       | C <sub>L</sub> = 10pF. CLK falling-edge to SDO stable |     |      | 25  | ns    |  |

| SDO Rise and Fall Times               | t <sub>FT</sub>       | C <sub>L</sub> = 10pF                                 |     | 4    |     | ns    |  |

| CS Hold Time                          | tcsh                  | (Note 4)                                              | 50  |      |     | ns    |  |

| CS Pulse-Width High                   | 4                     | FLTR = low (Note 4)                                   | 50  |      |     | no    |  |

| C3 Pulse-Width High                   | tCSPW                 | FLTR = high                                           | 280 |      |     | ns    |  |

| PROTECTION SPECIFICATIONS             | 3                     |                                                       |     |      |     |       |  |

| Channel Thermal-Shutdown Threshold    | T <sub>C_SD</sub>     | Temperature rising                                    |     | +170 |     | °C    |  |

| Thermal-Shutdown Hysteresis           | T <sub>C_SD_HYS</sub> |                                                       |     | 15   |     | °C    |  |

| Global Thermal-Shutdown<br>Threshold  | T <sub>G_SD</sub>     | Temperature rising                                    |     | 150  |     | °C    |  |

| Global Thermal-Shutdown<br>Hysteresis | T <sub>G_SD_HYS</sub> |                                                       |     | 10   |     | °C    |  |

| ESD Protection                        | V                     | O_ pins, Human Body Model (Note 6)                    |     | ±15  |     | 10/   |  |

| ESD Protection                        | V <sub>ESD</sub>      | All other pins, Human Body Model                      | ±2  |      |     | kV    |  |

- Note 2: All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

- **Note 3:** All logic input pins except  $\overline{CS}$  have a pulldown resistor.  $\overline{CS}$  has a pullup resistor.

- Note 4: Specifications are guaranteed by design; not production tested.

- Note 5: Channel-to-channel skew is defined as the difference in propagation delays between channels on the same device with the same polarity.

- Note 6: Bypass V<sub>DD</sub> pins to AGND with a 1µF capacitor as close as possible to the device for high-ESD protection.

## **Test Circuits/Timing Diagrams**

Figure 1. High-Side Mode Timing Characteristics

## **Test Circuits/Timing Diagrams (continued)**

Figure 2. Push-Pull Mode Timing Characteristics

## **Test Circuits/Timing Diagrams (continued)**

Figure 3. CRC Error Detection Timing

Figure 4. SPI Timing Diagram

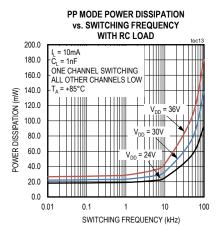

### **Typical Operating Characteristics**

$(V_{DD} = +24V, V_5 = V_L = 5.0V, T_A = +25$ °C, unless otherwise noted.)

## PROPAGATION DELAY vs. V<sub>DD</sub> PUSH-PULL MODE: $R_L = 5k\Omega$ , $C_L = 1nF$ 1400 HIGH-SIDE MODE: $R_L = 48\Omega$ , $C_L = 1nF$ PROPAGATION DELAY (ns) 000 000 000 000 000 000 tpDpp\_lh 200 tpdhs\_lh 0 10 12 14 16 18 20 22 24 26 28 30 32 34 36

### **Typical Operating Characteristics (continued)**

( $V_{DD}$  = +24V,  $V_5$  =  $V_L$  = 5.0V,  $T_A$  = +25°C, unless otherwise noted.)

## **Pin Configurations**

## **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | S16/IN8  | 16-Bit Serial-Select Input/IN8 Input. In serial mode (SRIAL = high), drive S16/IN8 high to select 16-bit serial operation. Drive S16/IN8 low to select 8-bit serial operation. In parallel mode (SRIAL = low), S16/IN8 sets the O8 output on/off in high-side mode or high/low in push-pull mode. S16/IN8 has an internal $200k\Omega$ pulldown resistor.                                               |

| 2   | CNFG/IN7 | Configure Select Input/IN7 Input. In serial mode (SRIAL = high), drive CNFG/IN7 high to select perchannel configuration over the serial interface. Drive CNFG/IN7 low to select setting the O_ outputs over the serial interface. In parallel mode (SRIAL = low), CNFG/IN7 sets the O7 output on/off in high-side mode or high/low in push-pull mode. CNFG/IN7 has an internal 200kΩ pulldown resistor. |

| 3   | IN6      | IN6 Input. In parallel mode (SRIAL = low), IN6 sets the O6 output on/off in high-side mode or high/low in push-pull mode. IN6 has an internal 200kΩ pulldown resistor.                                                                                                                                                                                                                                  |

| 4   | IN5      | IN5 Input. In parallel mode (SRIAL = low), IN5 sets the O5 output on/off in high-side mode or high/low in push-pull mode. IN5 has an internal 200kΩ pulldown resistor.                                                                                                                                                                                                                                  |

| 5   | CS       | SPI Chip-Select Input. $\overline{\text{CS}}$ is the SPI active-low chip select. $\overline{\text{CS}}$ has an internal 200k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                  |

| 6   | CLK      | Serial-Clock Input. CLK is the SPI serial-clock input (up to 20MHz) and has an internal 200kΩ pulldown resistor.                                                                                                                                                                                                                                                                                        |

| 7   | SDI      | Serial-Data Input. SDI is the SPI serial-data input and has an internal 200kΩ pulldown resistor.                                                                                                                                                                                                                                                                                                        |

| 8   | SDO      | Serial-Data Output. SDO is the SPI serial-data output. SDO has an internal 200k $\Omega$ pulldown resistor when $\overline{\text{CS}}$ is logic-high.                                                                                                                                                                                                                                                   |

## **Pin Description (continued)**

| PIN                                     | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                                       | CERR/IN4        | CRC Error Detection Output/IN4 Input. In serial mode (SRIAL = high) with error checking enabled (CRC/IN3 = high), $\overline{CERR}$ /IN4 is an active-low open-drain output that asserts when a CRC error is detected on SDI data. In parallel mode (SRIAL = low), $\overline{CERR}$ /IN4 sets the O4 output on/off in high-side mode or high/low in push-pull mode. $\overline{CERR}$ /IN4 has an internal 200k $\Omega$ pulldown resistor when SRIAL = 0.                                           |

| 10                                      | CRC/IN3         | CRC Enable Input/IN3 Input. In serial mode (SRIAL = high), drive CRC/IN3 high to enable CRC generation/error detection on SPI data. In parallel mode (SRIAL = low), CRC/IN3 sets the O3 output on/off in high-side mode or high/low in push-pull mode. CRC/IN3 has an internal 200kΩ pulldown resistor.                                                                                                                                                                                               |

| 11                                      | IN2             | IN2 Input. In parallel mode (SRIAL = low), IN2 sets the O2 output on/off in high-side mode or high/low in push-pull mode. IN2 has an internal $200k\Omega$ pulldown resistor.                                                                                                                                                                                                                                                                                                                         |

| 12                                      | OL/IN1          | Open-Load Enable Input/IN1 Input. In serial mode (SRIAL = high), drive OL/IN1 high to enable open-load detection on all eight O_ outputs that are configured in high-side mode, overriding the serial configuration. Drive OL/IN1 low to disable open-load detection unless enabled by the serial interface. In parallel mode (SRIAL = low), OL/IN1 sets the O1 output on/off in high-side mode or high/low in push-pull mode. OL/IN1 has a $200 k\Omega$ pulldown resistor that is always connected. |

| 13                                      | V <sub>L</sub>  | Logic Supply Input. $V_L$ defines the logic levels on all I/O logic interface pins from 2.5V to 5.5V. Bypass $V_L$ to AGND with a 0.1 $\mu$ F ceramic capacitor as close as possible to the device.                                                                                                                                                                                                                                                                                                   |

| 14, 18,<br>19, 23,<br>38, 42,<br>43, 47 | V <sub>DD</sub> | Supply Voltage Input. $V_{DD}$ supply is 10V to 36V. Bypass the $V_{DD}$ pins to a ground plane with a 1µF ceramic capacitor. Externally connect all $V_{DD}$ pins and ensure that the maximum trace resistance between each $V_{DD}$ pin is less than $10m\Omega$ .                                                                                                                                                                                                                                  |

| 15                                      | O1              | Driver Output 1. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16, 21,<br>40, 45                       | PGND            | Power Ground. Connect PGND to the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17                                      | O2              | Driver Output 2. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20                                      | O3              | Driver Output 3. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22                                      | 04              | Driver Output 4. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24                                      | PUSHPL          | Global Push-Pull/High-Side Select Input. In parallel mode (SRIAL = low), drive PUSHPL high to globally configure all O_ outputs to operate in push-pull mode, overriding the serial configuration. Drive PUSHPL low to configure all O_ outputs to operate in high-side mode unless configured as push-pull by the serial interface. PUSHPL has an internal 200kΩ pulldown resistor.                                                                                                                  |

| 25–27,<br>33–36                         | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 28                                      | FLTR            | Glitch Filter Enable Input. Set FLTR high to enable glitch filtering on every logic input except SDI and CLK. FLTR has an internal $200k\Omega$ pulldown resistor.                                                                                                                                                                                                                                                                                                                                    |

| 29                                      | AGND            | Analog Ground. Connect AGND to the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30                                      | V <sub>5</sub>  | 5V Supply Input. Bypass V <sub>5</sub> to AGND with a 1μF ceramic capacitor as close as possible to the device.                                                                                                                                                                                                                                                                                                                                                                                       |

| 31                                      | EN              | Enable Input. Drive EN high to enable normal operation for all O_ outputs. Drive EN low to force all O_ outputs into high-impedance mode. EN has an internal 200kΩ pulldown resistor.                                                                                                                                                                                                                                                                                                                 |

| 32                                      | REXT            | External Resistor Connection. Connect a 56kΩ ±1% resistor from REXT to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                          |

## **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37  | SRIAL | Serial/Parallel Select Input. Drive SRIAL high to set and configure the O_ outputs through the serial interface. Drive SRIAL low to set the O_ outputs through the parallel (IN_) pins. SRIAL does not affect the read back of diagnostics/status information through the serial interface. SRIAL has an internal $200k\Omega$ pulldown resistor. |

| 39  | O5    | Driver Output 5. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                     |

| 41  | 06    | Driver Output 6. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                     |

| 44  | 07    | Driver Output 7. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                     |

| 46  | O8    | Driver Output 8. May be configured as a high-side switch or push-pull output.                                                                                                                                                                                                                                                                     |

| 48  | FAULT | Global Fault Output. FAULT is an open-drain, active-low output that asserts when a fault condition (thermal shutdown, open-load, and/or overload protection) is detected on any O_ output.                                                                                                                                                        |

| _   | EP    | Exposed Pad. Connect EP to a large ground plane, which is electrically connected to PGND, using a via farm to minimize thermal impedance; not intended as an electrical connection point.                                                                                                                                                         |

## **Functional Diagram**

**SDI DATA SDO DATA** CNFG/ **SRIAL** S16/IN8 **OPERATING MODE** IN7 **SETTING** CONFIG **FAULT STATUS** Parallel mode with optional SPI 0 Χ Χ N/A 16-bit 8-bit 8-bit configuration, diagnostics, and monitoring 8-bit serial mode with SPI setting and 1 0 0 8-bit N/A 8-bit N/A diagnostics 8-bit serial mode with SPI configuration 0 1 1 N/A N/A 8-bit 8-bit and diagnostics 16-bit serial mode with SPI setting, 1 0 8-bit 1 8-bit 8-bit 8-bit configuration, diagnostics, and monitoring 16-bit serial mode with SPI configuration, 1 1 N/A 16-bit 8-bit 8-bit 1 diagnostics, and monitoring

**Table 1. Serial/Parallel Operating Modes**

X = Don't care

### **Detailed Description**

The MAX14900E is an octal low-propagation delay 850mA high-side switch that can be operated as a push-pull driver with high switching-rate capability. Each channel can be configured to operate in high-side or push-pull mode. Push-pull mode drives capacitive loads such as long cables that need to be driven at high switching rates. In high-side mode, each channel switches up to 850mA load current with 165m $\Omega$  (max) on-resistance.

The MAX14900E's switches/drivers are configured either individually by a serial SPI interface and/or globally by a parallel interface. In parallel operating mode (SRIAL = low), the IN\_ inputs directly control the O\_ outputs and the SPI interface configures each channel and reads back diagnostic and state status. In serial operating mode (SRIAL = high), the SPI interface is used to configure and set the state of each channel while the parallel inputs provide optional configuration possibilities.

Current limiting, overload protection, and thermal shutdown circuitry protect each switch/driver. The device features per-channel diagnostic detection that feeds back per-channel thermal shutdown and output state information. In high-side mode, multiple channels can be connected in parallel to achieve higher load currents.

### **Serial/Parallel Operating Modes**

A serial SPI and parallel interface allow configuration, monitoring, and driving of the MAX14900E. The serial interface supports per-channel configuration, setting, and diagnostics/monitoring while the parallel interface allows direct driving of the switches/outputs. Table 1 details how

**Table 2. Parallel Driving Truth Table**

| IN  | O_ ST     | ATE       |

|-----|-----------|-----------|

| ""- | PUSH-PULL | HIGH-SIDE |

| 0   | Low       | Off       |

| 1   | High      | On        |

the device utilizes each interface depending on the status of the configuration select inputs.

### **Parallel Operating Mode**

In parallel operating mode (SRIAL = low), the eight IN\_inputs directly set the O\_ switches on/off in high-side mode or high/low in push-pull mode (Table 2). The serial interface can optionally be used to configure each output as a high-side switch or as a push-pull driver and to enable open-load detection for each high-side switch. The serial interface can also be used in parallel mode to read out per-channel fault, open-load detection, and output logic state information.

The outputs can be configured globally for push-pull operation by the PUSHPL input. Global diagnostic fault and open-load information is reported by the FAULT output.

### **Serial Operating Mode**

In serial operating mode (SRIAL = high), the switches/drivers are set, configured, and monitored by the SPI interface. The S16/IN8, CNFG/IN7, CRC/IN3, and OL/IN1 inputs and the CERR/IN4 output provide further configuration and monitoring options in serial operating mode. The remaining IN\_ inputs are not used. See the <u>Serial Controller Interface</u> section for more information.

### Configuration

The global configuration inputs affect all eight O\_ channels while serial configuration is per channel. See Table 3.

The serial interface can be used to configure each output individually to be in push-pull or high-side mode and to enable open-load detection for that channel if it is in high-side mode. The PUSHPL and OL/IN1 inputs override the per-channel serial configuration when they are set high.

### **Output Drivers**

The drivers can be configured for high-side or push-pull operation. When configured in high-side mode, each driver can safely source 850mA (max) load current continuously. The high-side switches have active current limiting in the range between 1.4A (min) and 2.0A (max).

When a driver is in push-pull mode, the output drives resistive/capacitive loads at high switching rates with load currents up to 100mA to ground. The  $R_{ON}$  is  $4\Omega$  (max) for the high-side and  $10\Omega$  (max) for the low-side drivers in push-pull mode.

### **Monitoring the Output Logic State**

The voltage state of each O\_ driver/switch can be read out via SPI. If the voltage on an O\_ output is higher than

the 7V (typ) threshold, then the corresponding S\_ bit is logic 1 in the status byte. If the voltage on an O\_ output is below the threshold, then the corresponding S\_ bit is logic 0. Status monitoring can be read out via 16-bit serial mode. This is possible on all modes and states of the outputs: on/off/high/low.

### **Open-Load Detection**

When configured in high-side mode, the device can detect when no load is connected to the O\_ outputs or when a wire to a load is open circuit. Open-load detection can be globally enabled in serial mode via the OL/IN1 input, or on a per-channel basis via the serial interface in parallel and serial modes. The detection circuitry applies an 80µA current to the load and monitors the O\_ voltage. Open-load detection occurs when the outputs are configured in high-side mode and is active while the high-side driver is off.

When an open-load condition is detected on a high-side switch, the corresponding switch's fault bit is set and the global FAULT output is asserted. Turning off a high-side driver that has a large capacitive load and low bleed resistance triggers a temporary detection of an open-load condition and assert FAULT until the O\_ voltage decays to below the 7V (typ) threshold.

**Table 3. Global Configuration Inputs**

| INPUT   | SRIAL | CONFIGURATION FUNCTION                                                                                                                                                                |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLTR    | X     | Enables anti-glitch filtering on all logic input pins except SDI and CLK 0 = Glitch filtering disabled 1 = Glitch filtering enabled                                                   |

| PUSHPL  | X     | Configures all O_ outputs as push-pull or high-side 0 = All drivers high-side mode unless configured as push-pull by serial interface 1 = All drivers push-pull mode                  |

| EN      | X     | Enables normal operation of all O_ outputs 0 = All O_ outputs high impedance 1 = Normal operation                                                                                     |

| OL/IN1  | 1     | Enables global open-load detection in serial mode 0 = Open-load detection disabled unless enabled by serial interface 1 = Open-load detection enabled for all high-side mode switches |

| CRC/IN3 | 1     | Enables CRC generation and error detection of SPI data 0 = CRC disabled 1 = CRC enabled                                                                                               |

X = Don't care

### **Thermal Shutdown Protection**

Thermal overload circuitry constantly monitors each switch/driver and a global thermal shutdown circuit monitors average chip temperature. When a local thermal shutdown condition occurs for one of the drivers, it is disabled while the others continue to operate. When the local temperature falls to below the activation threshold ( $T_{C\_SD} - T_{C\_SD\_HYS}$ ), that driver automatically re-enables. A global thermal shutdown does not disable the O\_ outputs but prevents any channel from re-enabling itself until the global temperature sensor is below the limit.

The FAULT output is asserted when any thermal shutdown condition occurs. In addition, F\_ bits are set for channels that are in thermal shutdown in the SPI SDO data

#### **Overload and Short-Circuit Protection**

The device protects each O\_ output against overload and short-circuit conditions while operating in push-pull and high-side mode.

In high-side mode, the device actively limits each channel's output current to 1.7A. As long as no thermal shutdown occurs, this current limiting condition persists continuously.

In push-pull mode, the device limits the load current to 300mA/500mA (typ). Overload faults are detected when an O\_ output is in push-pull mode and an overcurrent condition forces the output voltage to above 1V (for O\_ = low) or below (VDD - 1V) (for O\_ = high) for more than the blanking time  $90\mu$ s (typ). When the cause of the output voltage level mismatch is removed, the driver resumes normal operation.

### **POR and UVLO Conditions**

The MAX14900E features undervoltage lockout (UVLO) and power-on reset (POR) circuitry on its power supply inputs to ensure that the device is in a known state on power-up or when there is a droop on one of the supplies. If either  $V_L$  or  $V_5$  falls to below its POR threshold, the device goes into its reset state and all configuration settings are lost.

When  $V_{DD}$  or  $V_5$  is below its UVLO threshold, all O\_outputs are disabled and the  $80\mu A$  open-load detection current sources are turned off. The device resumes normal operation when the UVLO condition is removed. As long as  $V_L$  and  $V_5$  stay above their POR thresholds, the SPI interface remains active and configuration settings are not affected.

In 16-bit serial mode when a UVLO is present, a series of all ones in the serial SDO status/fault read back bits reports this condition.

### **FAULT** Output

The global FAULT output asserts when a fault condition is detected on any O\_ output. The types of fault conditions reported by FAULT are thermal shutdown, open-load (if enabled), and overload protection (in push-pull mode only). The global FAULT is not initiated in a UVLO condition.

Thermal shutdown faults are detected when the internal temperature of any driver exceeds the thermal shutdown threshold ( $T_{C\_SD}$ ). The fault is cleared when the temperature falls to below the activation threshold ( $T_{C\_SD}$  –  $T_{C\_SD\_HYS}$ ).

Open-load faults are detected when the voltage at an O\_output in high-side mode with the HS switch turned off is above the detection threshold of 7V. This happens when the O\_output is not connected to any external load and the 80µA pullup current charges the node. A brief open-load condition can occur after an HS switch is turned off and the load has not discharged capacitance yet.

In push-pull mode, if the voltage level at an  $O_-$  output differs from the programmed value for longer than the  $90\mu s$  (typ) blanking time due to overcurrent, the driver is turned off for the 11ms (typ) retry time. During the retry period, the  $\overline{FAULT}$  output is asserted and the fault bit is set for that driver in the serial data. The fault is cleared after the fault condition is removed at the end of the current retry period (11ms).

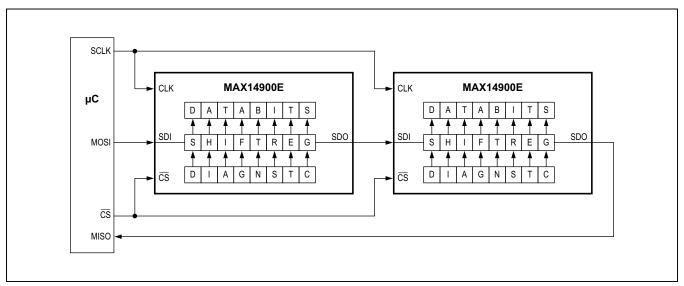

### **Serial Controller Interface**

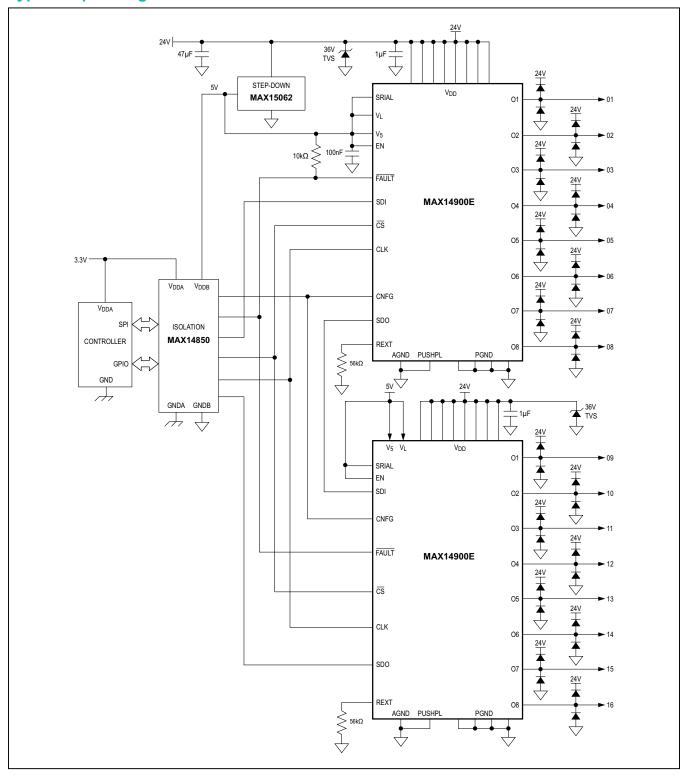

The MAX14900E can be configured, controlled and/or monitored on a per-channel basis via its SPI interface (see <u>Table 1</u>). Daisy-chaining multiple MAX14900E devices is supported to reduce the required number of  $\overline{\text{CS}}$  and/or isolator pins. <u>Figure 5</u> shows an example of daisy-chaining two MAX14900E devices. Daisy-chaining operates both with 8-bit and 16-bit serial data: S16/IN8 = X.

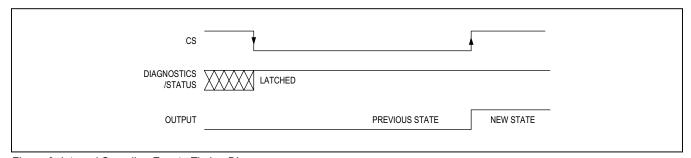

The MAX14900E uses SPI mode 0 with CPOL = 0 and CPHA = 0. When the  $\overline{\text{CS}}$  input transitions low, diagnostics

and status information is sampled and stored in the internal SPI shift register and the SDO output becomes active. This data is clocked out of SDO on each falling CLK edge while new SDI data is sampled and stored in the shift register on each rising CLK edge. When  $\overline{\text{CS}}$  transitions high at the end of the SPI cycle, the current data in the SPI shift register is latched into the MAX14900E and the new configuration and/or setting data changes the driver states. Figure  $\underline{6}$  illustrates the sampling of internal signals dependent on  $\overline{\text{CS}}$  transitions.

Figure 5. Daisy-Chained MAX14900E Devices with 8-Bit Serial Mode

Figure 6. Internal Sampling Events Timing Diagram

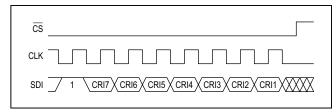

### 8-Bit Serial Mode with Setting and Monitoring

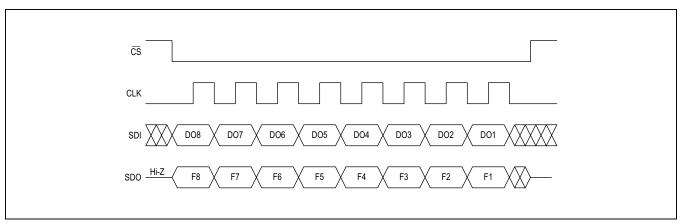

In serial mode with 8-bit setting and 8-bit monitoring (SRIAL = high, S16/IN8 = low, CNFG/IN7 = low), the SPI shift register is 8 bits long (Figure 7). The DO\_ bits set the state of the respective O\_ output (Table 4). The F\_ bits report fault information of the respective O\_ output (Table 7).

## 8-Bit Serial Mode with Configuration and Monitoring

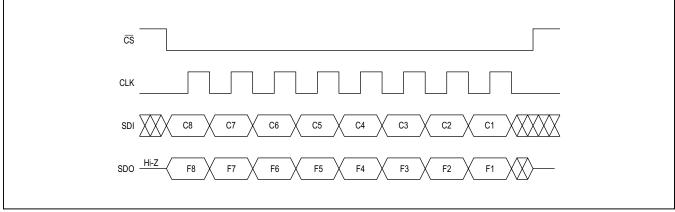

In serial mode with 8-bit configuration and 8-bit monitoring (SRIAL = high, S16/IN8 = low, CNFG/IN7 = high), the SPI shift register is 8 bits long (Figure 8). The C\_ bits configure push-pull/high-side mode for the respective O\_ output (Table 5). The F\_ bits report fault information for the respective O\_ output (Table 7).

Figure 7. Serial Timing in 8-Bit Setting Serial Mode

Figure 8. Serial Timing in 8-Bit Configuration Serial Mode

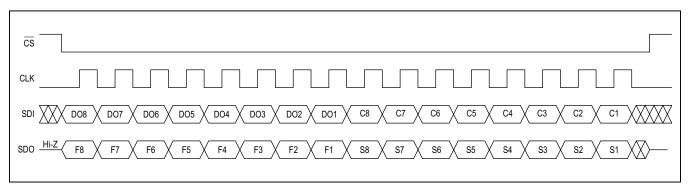

## 16-Bit Serial Mode with 8-Bit Setting/8-Bit Configuration

In serial mode with 8-bit setting/8-bit configuration and 16-bit monitoring (SRIAL = high, S16/IN8 = high, CNFG/IN7 = low), the SPI shift register is 16 bits long (Figure 9). The DO\_ bits set the state of the respective O\_ output and the C\_ bits configure push-pull/high-side mode (Table 4 and Table 5). The F\_ and S\_ bits report the status information for each channel (Table 8).

## Parallel Mode/16-Bit Serial Mode with 16-Bit Configuration

In parallel and serial mode with 16-bit serial configuration and 16-bit monitoring (SRIAL = low or SRIAL = high, S16/

IN8 = high, CNFG/IN7 = high), the SPI shift register is 16 bits long (Figure 10). The C1\_ and C0\_ bits configure push-pull/high-side mode and open-load detection for each respective channel (Table 6). The F\_ and S\_ bits report the status information for each channel (Table 8).

# **Setting, Configuration, and Monitor Bit Definitions**

<u>Table 3</u> to <u>Table 8</u> define the effects of the setting, configuration, and monitoring bits.

If PUSHPL = high, then all outputs are configured as push-pull mode regardless of C .

**Table 4. Serial Setting Truth Table**

| DO_ | O_ STATE               |                        |  |  |  |  |  |

|-----|------------------------|------------------------|--|--|--|--|--|

|     | PUSH-PULL<br>OPERATION | HIGH-SIDE<br>OPERATION |  |  |  |  |  |

| 0   | Low                    | Off                    |  |  |  |  |  |

| 1   | High                   | On                     |  |  |  |  |  |

Table 5. 8-Bit Serial Configuration Truth Table

| C_ | O_ CONFIGURATION |

|----|------------------|

| 0  | High-side mode   |

| 1  | Push-pull mode   |

Figure 9. 16-Bit Serial Timing with 8-Bit Setting/8-Bit Configuration

Figure 10. 16-Bit Serial Timing with 16-Bit Configuration

### 16-Bit Serial Configuration

Open-load detection is only available for outputs configured in high-side mode. If PUSHPL = high, then all outputs are configured as push-pull mode regardless of the C\_ bits. In serial modes, if OL/IN1 = high, then all outputs that are configured as high side will have open-load detect on, regardless of the C1 bits.

### 8-Bit Serial Diagnostics

If a driver is configured in push-pull mode, then a fault means that an overload or a thermal shutdown is present on that channel. If the driver is configured in highside mode, then a fault means that an overtemperature condition is detected. If open-load detection is enabled in high-side mode, then the F bit is set when either an open-load (only possible with the high-side switch off) or an overtemperature is detected. In a UVLO condition, eight F\_ bits are logic one.

### **16-Bit Serial Diagnostics**

Logic-level status (S bits) detection is only valid when no fault is present. Each S\_ bit in normal (no fault) operating condition reports whether or not the O voltage is above (= 1) or below (= 0) 7V (typ).

When all F\_ and S\_ bits are logic one, a UVLO condition is present.

### **Table 6. 16-Bit Serial Configuration Truth Table**

| C1_ | C0_ | O_ CONFIGURATION                     |

|-----|-----|--------------------------------------|

| 0   | 0   | High-side mode, open-load detect off |

| 0   | 1   | Push-pull mode                       |

| 1   | 0   | High-side mode, open-load detect on  |

| 1   | 1   | Push-pull mode                       |

### **Table 7. 8-Bit Diagnostics Truth Table**

| F_ | O_ CONDITION                                 |

|----|----------------------------------------------|

| 0  | No fault present                             |

| 1  | Fault (overload, open load, or UVLO) present |

### **Table 8. 16-Bit Serial Diagnostics Truth Table**

| F_ | S_ | O_ STATUS                                    |

|----|----|----------------------------------------------|

| 0  | 0  | No fault detected, logic state of O_ is low  |

| 0  | 1  | No fault detected, logic state of O_ is high |

| 1  | 0  | Fault detected, logic state not defined      |

| 1  | 1  | UVLO detected                                |

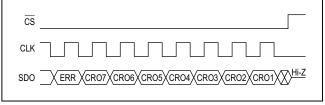

### **CRC Error Checking on Serial Interface**

In serial mode (SRIAL = high), CRC error detection can be enabled by setting CRC/IN3 high to minimize incorrect operation due to noise on the SDI/SDO/CLK signals. With CRC error detection enabled, the MAX14900E detects errors on the SDI data that it receives from the controller and it calculates a CRC on the SDO data that it sends to the controller and appends this check byte to the SDO data.

This ensures that both the SPI data sent and received by the MAX14900E has a low likelihood of undetected errors.

The check byte appended to all 8-bit/16-bit SDO data by the MAX14900E contains a 7-bit frame check sequence (FCS). This FCS is based on the CRC generator polynomial  $x^7 + x^5 + x^4 + x^2 + x + 1$ . The CRC initialization condition is 0x7F. The MAX14900E in turn expects a check byte appended to all 8-/16-bit SDI data that it receives containing a FCS based on the same polynomial (Figure 11).

The controller should calculate the 7 FCS bits (CRI ) on the 8-/16-bit data including the logic 1 in the first position of the check byte. Thus the CRC is calculated on 9 or 17 bits. CRI1 is the LSB of the FCS. The MAX14900E verifies this received CRC. If the MAX14900E detects CRC errors on the received SDI data, then it ignores this data and does not change its configuration and/or output setting. Instead, the CERR/IN4 output is asserted and the ERR bit is set in the check byte that it appends to the 8-/16-bit SDO diagnostic/status data that it sends back to the controller during the following serial communication cycle (Figure 12).

ERR is the error feedback bit that is sent back to the controller to signal that a CRC error was detected on the

Figure 11. CRC Check Byte Expected From Controller

Figure 12. CRC Check Byte Sent by MAX14900E

previous SDI data reception. Note that ERR is delayed by one SPI cycle, i.e., it indicates that a CRC error was detected in the previous SPI data cycle. The CERR/IN4 output is immediately set active when a CRC error is detected, allowing the controller to resend the last SDI data or take other action.

The CRO\_ bits are the CRC bits that the MAX14900E calculates on the 8-/16-bit diagnostics and/or status data plus the ERR bit i.e., the output FCS is calculated on 9/17 bits. This allows the controller to detect errors on the SDO data received from the MAX14900E.

### **Applications Information**

### **Driving Inductive Loads**

In high-side mode, when the high-side switch turns off, an inductive load will cause the O\_ voltage to swing negative in order to continue sourcing the load's inductive current while the inductor field collapses. The internal diodes support turn-off of inductive loads of up to 1.5H and currents of up to 1.9A.

### **Driving Lamp Loads**

Lamp loads are incandescent lamps where the filament resistance is strongly dependent on the filament's temperature. The initial startup current is high because a cold filament has a very low resistance. The MAX14900E will reliably turn on 15W lamps over the operating temperature range.

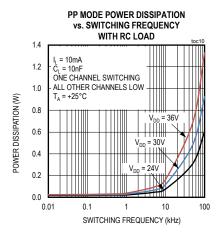

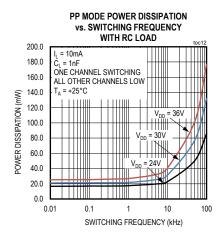

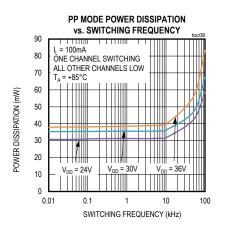

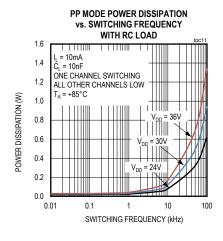

### **Driving Capacitive Loads**

When charging/discharging purely capacitive loads with a push-pull driver, the driver dissipates power that is proportional to switching frequency. The power can be estimated by  $P_D \sim C \times V_{DD}^2 \times f$ , where C is the load capacitance,  $V_{DD}$  is the supply voltage, and f is the switching frequency. For example, in an application with a 1nF load and 100kHz switching frequency, each driver dissipates 130mW at  $V_{DD} = 36V$ . When driving purely capacitive loads consider a maximum capacitance of around 10nF.

### Multiple SPI Devices on Shared Bus

The SDO output is high impedance when CS is logichigh to allow connecting multiple devices in parallel on a shared SPI bus with the SDO lines connected together. When SDO is high impedance, an internal  $200k\Omega$  pull-down resistor is enabled to pull SDO to GND weakly.

### Paralleling of Outputs

In high-side mode, multiple outputs can be connected together in parallel to achieve higher load currents. The total load current should be shared equally between these high-side switches that are operated in parallel. This is achieved by having identical trace resistances for all the PCB tracks from the O\_ pins to the common star

connection point. This is particularly important, since the on-resistance of each high-side switch is low:  $85m\Omega$  (typ).

### **Board Layout**

High-speed switches require proper layout and design procedures for optimum performance. Ensure that power-supply bypass capacitors are placed as close as possible to the device. Connect all  $V_{DD}$  pins to a  $V_{DD}$  plane. Ensure that all  $V_{DD}$  pins have no more than  $10 m\Omega$  between them. In this case a  $1 \mu F$  capacitor should be placed to the ground plane as close to the  $V_{DD}$  pins as possible. In the case low resistance paths are not possible between the  $V_{DD}$  pins, bypass each pin to GND via a 100 nF capacitor.

A suppressor/TVS diode should be used between  $V_{DD}$  and GND to clamp high-surge transients on the  $V_{DD}$  supply input and surges from the  $O_{}$  outputs. The standoff voltage should be higher than the maximum operating voltage of the equipment while the breakdown voltage should be around 40V.

As long field supply cables can generate large voltage transients on the  $V_{DD}$  supply due to large di/dt, it is recommended to add a large capacitor on  $V_{DD}$  at the point of field supply entry. Capacitance should be as large as possible, but  $47\mu F$  electrolytic capacitor is recommended as a minimum.

### **High ESD Protection**

Electrostatic discharge (ESD)-protection structures are incorporated on all pins to protect against electrostatic discharges up to ±2kV Human Body Model (HBM) encountered during handling and assembly.

All O\_ outputs are further protected against ESD up to  $\pm 15 \text{kV}$  (HBM) without damage, when the part is operative in the application circuit with a 1 $\mu$ F bypass capacitor on VDD and a suppressor/TVS diode.

In order to achieve even higher ESD levels, connect external diodes from each output to GND and to  $V_{DD}$  as described in the *Surge Protection* section.

### **Surge Protection**

The MAX14900E O\_ pin is tolerant to  $\pm 600V/(42\Omega + 0.5\mu F)$  1.2 $\mu s/50\mu s$  surge testing, when only using a TVS diode on V<sub>DD</sub> and without protection diodes on the O\_ pins. It achieved over  $\pm 1.5kV/(42\Omega + 0.5\mu F)$  IEC61000-4-5 surge testing when using the *Typical Operating Circuit*. The silicon diodes on O\_ must have low forward voltage diodes that support the surge currents, like MURA205T3G. A surge-suppressor diode on the V<sub>DD</sub> supply must have low output impedance at the high surge currents. The SM30TY is suitable for this. Place all diodes and the V<sub>DD</sub> capacitor as close to the MAX14900E pins as possible.

## **Typical Operating Circuit**

## **Ordering Information**

| PART              | TEMP<br>RANGE (°C) | PIN-<br>PACKAGE |

|-------------------|--------------------|-----------------|

| MAX14900EAGM+CKT  | -40 to +125        | 48 QFN-EP**     |

| MAX14900EAGM+TCKT | -40 to +125        | 48 QFN-EP**     |

| MAX14900EAGM+CKH  | -40 to +125        | 48 TQFN-EP**    |

| MAX14900EAGM+TCKH | -40 to +125        | 48 TQFN-EP**    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Chip Information**

PROCESS: BiCMOS

T =Tape and reel.

<sup>\*\*</sup>EP = Exposed pad.

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

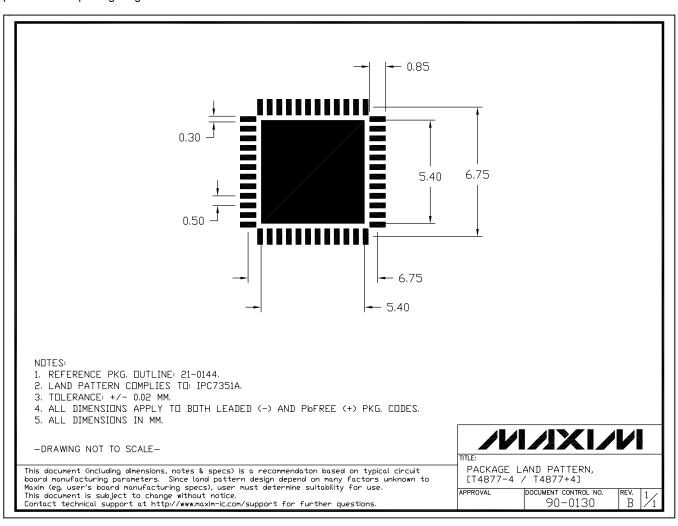

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

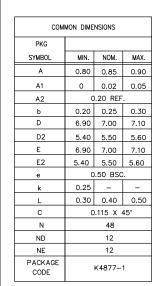

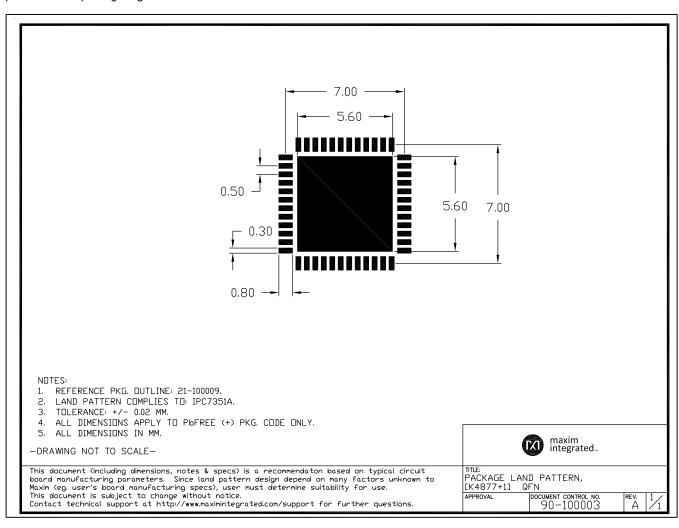

| 48 QFN          | K4877+1         | 21-100009      | 90-100003           |

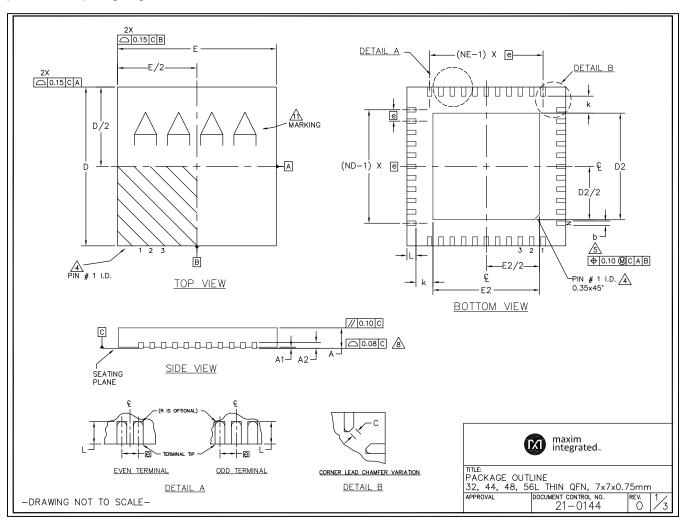

| 48 TQFN         | T4877+6         | 21-0144        | 90-0130             |

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9: WARPAGE SHALL NOT EXCEED 0.10 mm.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. NUMBER OF LEADS SHOWN ARE FOR REFFRENCE ONLY.

- 12. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND PHFREE (+) PKG. CODES.

PACKAGE OUTLINE

DOCUMENT CONTROL NO. 21-10009 APPROVAL

Ä

-DRAWING NOT TO SCALE-

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

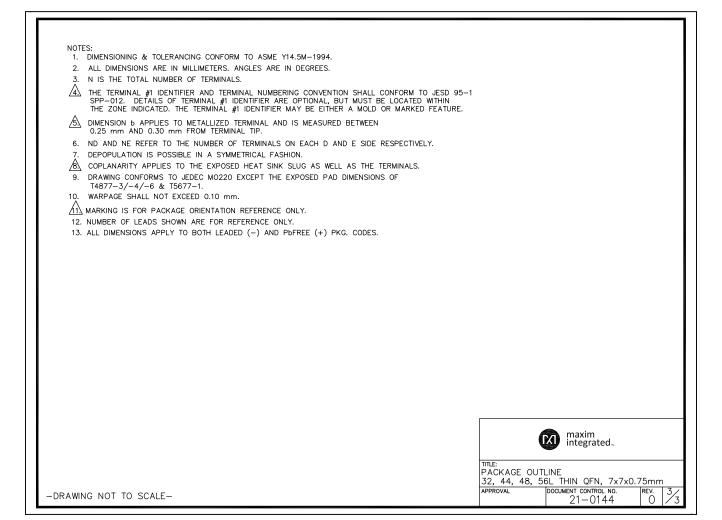

|        | COMMON DIMENSIONS |        |      |           |       |         |           |         |                          |           |      |           |      |      |      |

|--------|-------------------|--------|------|-----------|-------|---------|-----------|---------|--------------------------|-----------|------|-----------|------|------|------|

|        |                   |        |      |           |       |         |           |         | CUSTOM PKG.<br>(T4877-1) |           |      |           |      |      |      |

| PKG    | ;                 | 32L 7x | 7    | 44L 7x7   |       | 48L 7x7 |           | 48L 7x7 |                          | 56L 7x7   |      |           |      |      |      |

| SYMBOL | MIN.              | NOM.   | MAX. | MIN.      | NOM.  | MAX.    | MIN.      | NOM.    | MAX.                     | MIN.      | NOM. | MAX.      | MIN. | NOM. | MAX. |

| Α      | 0.70              | 0.75   | 0.80 | 0.70      | 0.75  | 0.80    | 0.70      | 0.75    | 0.80                     | 0.70      | 0.75 | 0.80      | 0.70 | 0.75 | 0.80 |

| A1     | 0                 | 0.02   | 0.05 | 0         | 0.02  | 0.05    | 0         | 0.02    | 0.05                     | 0         | 0.02 | 0.05      | О    | _    | 0.05 |

| A2     | 0                 | .20 R  | EF.  | 0.20 REF. |       |         | 0.20 REF. |         | 0.20 REF.                |           |      | 0.20 REF. |      |      |      |

| b      | 0.25              | 0.30   | 0.35 | 0.20      | 0.25  | 0.30    | 0.20      | 0.25    | 0.30                     | 0.20      | 0.25 | 0.30      | 0.15 | 0.20 | 0.25 |

| D      | 6.90              | 7.00   | 7.10 | 6.90      | 7.00  | 7.10    | 6.90      | 7.00    | 7.10                     | 6.90      | 7.00 | 7.10      | 6.90 | 7.00 | 7.10 |

| E      | 6.90              | 7.00   | 7.10 | 6.90      | 7.00  | 7.10    | 6.90      | 7.00    | 7.10                     | 6.90      | 7.00 | 7.10      | 6.90 | 7.00 | 7.10 |

| е      | 0                 | .65 B  | SC.  | C         | .50 B | SC.     | (         | ).50 B  | SC.                      | 0.50 BSC. |      | 0.40 BSC. |      |      |      |

| k      | 0.25              | -      | -    | 0.25      | -     | -       | 0.25      | _       | -                        | 0.25      | _    | _         | 0.25 | _    | -    |

| L      | 0.45              | 0.55   | 0.65 | 0.45      | 0.55  | 0.65    | 0.30      | 0.40    | 0.50                     | 0.45      | 0.55 | 0.65      | 0.30 | 0.40 | 0.50 |

| N      | 32 44             |        | 48   |           |       | 44      |           | 56      |                          |           |      |           |      |      |      |

| ND     | 8 11              |        |      | 12        |       |         | 10        |         |                          | 14        |      |           |      |      |      |

| NE     |                   | 8      |      |           | 11    |         |           | 12      |                          | 12        |      |           | 14   |      |      |

| CORNER LE  | AD CHAMFER  |

|------------|-------------|

| VARI       | ATION       |

| PKG. CODES | С           |

| T4877-3    | 0.115 X 45* |

| T4877-4    | 0.115 X 45* |

| T4877-4C   | 0.115 X 45° |

| T4877-6    | 0.115 X 45* |

| T4877-7    | 0.115 X 45* |

| T4877-10   | 0.115 X 45* |

| T4877M-1   | 0.115 X 45* |