# Digital Multi-Mode PFC + LLC Combo Controller

### **Product Highlights**

- Integrated 600V startup cell

- Integrated floating driver based on coreless transformer technology

- Digital multi-mode operation for higher efficiency curve

- Supports low stand-by power by means of direct X-cap discharge function and advanced burst mode control

- Eliminates the auxiliary power supply by means of integrated startup cell and burst mode

- UART interface for communication and in-circuit configuration

- Flexible design-in by means of one time programming capability for a wide range of parameters

### Description

The IDP2303 is a multi-mode PFC and LLC controller combined with a floating high side driver and a startup cell. A digital engine provides advanced algorithms for multi-mode operation to support highest efficiency over the whole load range. A comprehensive and configurable protection feature set is implemented. Only a minimum of external components are required with the low pin count DSO-16 package. The integrated HV startup cell and advanced burst mode enable to achieve low stand-by power. In addition a one-time-programming (OTP) unit is integrated to provide a wide set of configurable parameters that help to ease the design in phase.

#### **Features**

- Multi-mode PFC

- Configurable PFC gate driver

- Synchronous PFC and LLC burst mode control

- Configurable non-linear LLC VCO curve

- Configurable soft-start

- V<sub>AC</sub> input voltage sensing and X cap discharge via HV pin

### **Applications**

- LCD-TV 75W ~ 300W

- Generarl SMPS

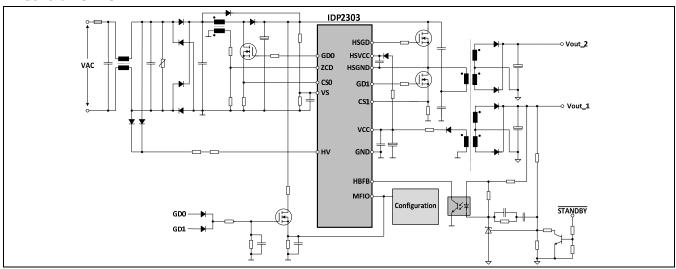

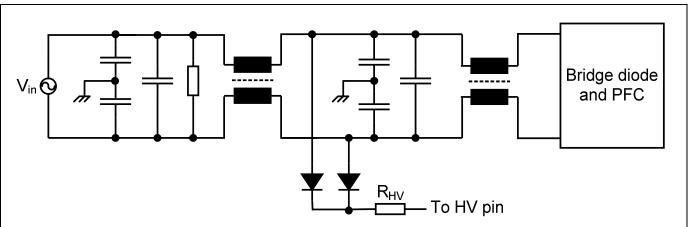

Figure 1 Typical Application

| Product Type | Package   |

|--------------|-----------|

| IDP2303      | PG-DSO-16 |

# Digital Multi-Mode PFC + LLC Combo Controller

| 1       | Pin Configuration and Description                                     | 4  |

|---------|-----------------------------------------------------------------------|----|

| 2       | Representative Blockdiagram                                           | 6  |

| 3       | Functional Description                                                | 7  |

| 3.1     | Introduction                                                          | 7  |

| 3.2     | Overview Controller Features                                          | 7  |

| 3.3     | Overview Controller Features                                          | 7  |

| 3.3.1   | System and Device overview                                            |    |

| 3.3.1.1 | Processor and memory operations                                       |    |

| 3.3.1.2 | Communication interface                                               | 9  |

| 3.3.1.3 | Voltage and current sensors                                           |    |

| 3.3.2   | IC Power Supply and High Voltage Startup Cell                         |    |

| 3.3.2.1 | Direct AC input monitoring combined with VCC startup function         |    |

| 3.3.2.2 | X-cap discharge function via the integrated HV startup-cell           |    |

| 3.3.3   | Standby Mode with synchronous PFC-LLC burst operation                 | 13 |

| 3.3.4   | IC protection                                                         |    |

| 3.3.4.1 | Undervoltage lockout for VCC                                          |    |

| 3.3.4.2 | Overvoltage protection for VCC                                        | 14 |

| 3.3.4.3 | Over temperature protection                                           |    |

| 3.3.4.4 | Auto Restart Mode                                                     |    |

| 3.3.5   | AC detection                                                          | 14 |

| 3.4     | PFC Controller                                                        | 14 |

| 3.4.1   | PFC Softstart                                                         | 15 |

| 3.4.2   | PFC Multi-mode operation                                              | 15 |

| 3.4.3   | PFC Protection                                                        | 17 |

| 3.4.3.1 | PFC Open Control Loop Protection (PFCOCLP)                            |    |

| 3.4.3.2 | PFC Inductor Over Current Protection (PFCOCP)                         |    |

| 3.4.3.3 | PFC Output Over Voltage Protection (PFCOVP)                           |    |

| 3.4.3.4 | PFC Output Redundant Over Voltage Protection (PFCROVP)                |    |

| 3.4.3.5 | PFC Output Under Voltage Protection (PFCUVP)                          | 18 |

| 3.4.3.6 | PFC Brownin Protection for AC Input Line (PFCBIP)                     |    |

| 3.4.3.7 | PFC Brownout Protection for AC Input Line (PFCBOP)                    | 18 |

| 3.4.3.8 | PFC Long Time Continuous Conduction Mode Protection (PFCCCMP)         |    |

| 3.5     | Half-bridge LLC Controller                                            |    |

| 3.5.1   | LLC Softstart (Time Controlled Oscillator TCO)                        |    |

| 3.5.2   | LLC Normal Operation (Voltage Controlled Oscillator VCO)              | 19 |

| 3.5.3   | LLC Smooth Transition of Frequency Control from TCO to VCO            |    |

| 3.5.4   | LLC Half-bridge Protection                                            |    |

| 3.5.4.1 | LLC Open Control Loop Protection (LLCOCLP)                            |    |

| 3.5.4.2 | LLC Over Load Protection (LLCOLP)                                     |    |

| 3.5.4.3 | LLC Over Current Protection Level 1 (LLCOCP1)                         |    |

| 3.5.4.4 | LLC Over Current Protection Level 2 (LLCOCP2)                         |    |

| 3.6     | Operation Flow                                                        | 22 |

| 3.6.1   | IC Initialization                                                     |    |

| 3.6.2   | Operation Flow of the PFC Controller                                  |    |

| 3.6.3   | Operation Flow of the Halfbridge LLC Controller                       |    |

| 3.7     | Overview Protection Features                                          |    |

| 3.7.1   | Undervoltage Lockout for VCC                                          |    |

| 3.7.2   | Overvoltage Protection for VCC                                        |    |

| 3.7.3   | Overtemperature Protection by means of internal Temperature Detection |    |

| 3.8     | Fixed and Configurable Parameters                                     | 27 |

2

# Digital Multi-Mode PFC + LLC Combo Controller

| 3.8.1      | Fixed Parameters                                   | 27 |

|------------|----------------------------------------------------|----|

| 3.8.2      | Fixed ParametersConfigurable Parameters            | 27 |

| 4          | Electrical Characteristics                         | 30 |

| 4.1        | Electrical CharacteristicsAbsolute Maximum Ratings | 30 |

| 4.2        | Package Characteristics                            | 31 |

| 4.3        | Operating Conditions                               | 31 |

| 4.4        | DC Electrical Characteristics                      | 31 |

| 4.4.1      | Power Supply Characteristics                       | 31 |

| 4.4.2      | Characteristics of the MFIO Pin                    | 32 |

| 4.4.3      | Characteristics of the HBFB Pin                    | 32 |

| 4.4.4      | Characteristics of the Current Sense Inputs CSx    | 32 |

| 4.4.5      | Characteristics of the Zero Crossing Input ZCD     | 33 |

| 4.4.6      | Characteristics of the Gate Driver Pins GDxGDx     | 33 |

| 4.4.7      | Characteristics of the High-Voltage Pin HV         |    |

| 4.4.8      | Characteristics of the VS Pin                      | 34 |

| 4.4.9      | Characteristics of the HSGD Pin                    | 34 |

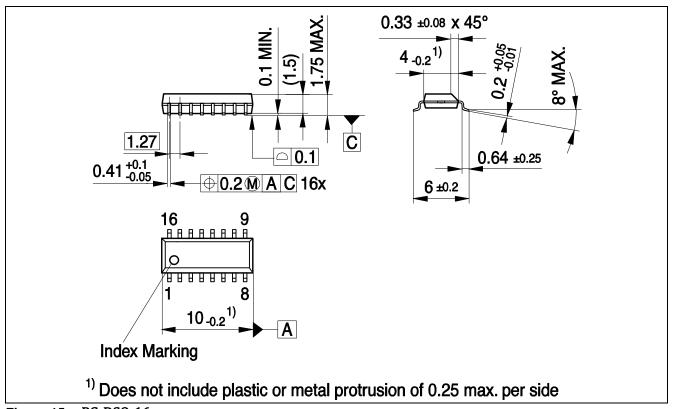

| 5          | Outline Dimensions                                 | 36 |

| Revision 1 | History                                            | 37 |

# 1 Pin Configuration and Description

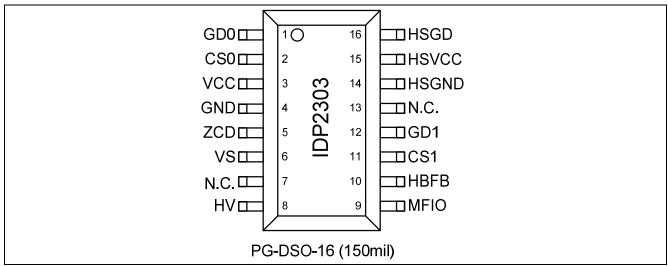

The pin configuration is shown in Figure 2 and Table 1. The Pin functions are described below.

Figure 2 Pin Configuration

**Table 1** Pin Definitions and Functions

| Symbol  | Pin | Type | Function                                                                                                                                                                                                                                                                                                                                         |

|---------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GD0     | 1   | 0    | Gate Driver Output 0 (PFC Gate Driver)                                                                                                                                                                                                                                                                                                           |

| (PFCGD) |     |      | Output for directly driving the PFC PowerMOS. The default peak source current capability is 156 mA and the peak sink current capability is 800 mA.                                                                                                                                                                                               |

| CS0     | 2   | I    | Current Sense 0 (PFC Current Sense)                                                                                                                                                                                                                                                                                                              |

| (PFCCS) |     |      | Pin CS0 is connected to an external shunt resistor and the source of the PFC PowerMOS.                                                                                                                                                                                                                                                           |

| VCC     | 3   | P    | Positive Voltage Supply IC power supply                                                                                                                                                                                                                                                                                                          |

| GND     | 4   | G    | Ground IC ground                                                                                                                                                                                                                                                                                                                                 |

| ZCD     | 5   | I    | <b>Zero Crossing Detection</b> Pin ZCD is connected to the auxiliary winding of the PFC choke.                                                                                                                                                                                                                                                   |

| VS      | 6   | I    | Voltage Sensing Pin VS is connected to a high ohmic resistor divider for directly sensing the bus voltage.                                                                                                                                                                                                                                       |

| N.C.    | 7   | _    | Creepage Distance                                                                                                                                                                                                                                                                                                                                |

| HV      | 8   | I    | High Voltage Input Pin HV is connected to the AC input via an external resistor and 2 diodes. There is a 600 V HV startup-cell internally connected that is used for initial VCC charge. It is also used to discharge the x-capacitors of the EMI network. Furthermore sampled high voltage sensing is supported for brownin/brownout detection. |

| MFIO    | 9   | I    | MFIO Pin MFIO provides a half duplex UART communication IO interface for parameter configuration. It also can be used for PFC output redundant over voltage protection. In that case it is mandatory to use a BSS127 transistor as shown in Figure 1 and the described in section 4.4.3.4.                                                       |

| HBFB    | 10  | I    | Half Bridge Feedback                                                                                                                                                                                                                                                                                                                             |

Datasheet 4 Rev. V2.0, 2017-03-21

# Digital Multi-Mode PFC + LLC Combo Controller

| Symbol | Pin | Туре | Function                                                                         |

|--------|-----|------|----------------------------------------------------------------------------------|

|        |     |      | Pin HBFB is connected to an optocoupler for the feedback path to control the     |

|        |     |      | LLC switching frequency.                                                         |

| CS1    | 11  | I    | Current Sense 1 (Hallf Bridge current Sense)                                     |

| (HBCS) |     |      | Pin CS1 is connected to an external shunt resistor and the source of the         |

|        |     |      | PowerMOS in the half-bridge stage.                                               |

| GD1    | 12  | 0    | Gate Driver Output 1 (Half Bridge Low Side Gate Driver)                          |

| (LSGD) |     |      | Output for directly driving the lowside PowerMOS in the half-bridge. The peak    |

|        |     |      | source current capability is 120 mA and the peak sink current capability is 500  |

|        |     |      | mA.                                                                              |

| N.C.   | 13  | _    | Creepage Distance                                                                |

| HSGND  | 14  | G    | High side Ground                                                                 |

|        |     |      | Ground for floating high side driver                                             |

| HSVCC  | 15  | P    | High side VCC                                                                    |

|        |     |      | Power supply of the high side floating driver, supplied via bootstrap            |

| HSGD   | 16  | 0    | High side floating Gate Driver                                                   |

|        |     |      | Output for directly driving the high side PowerMOS in the half-bridge. The       |

|        |     |      | peak source current capability is 0.52 A and the peak sink current capability is |

|        |     |      | 1.3 A. Refer to item 4.4.9 for more details.                                     |

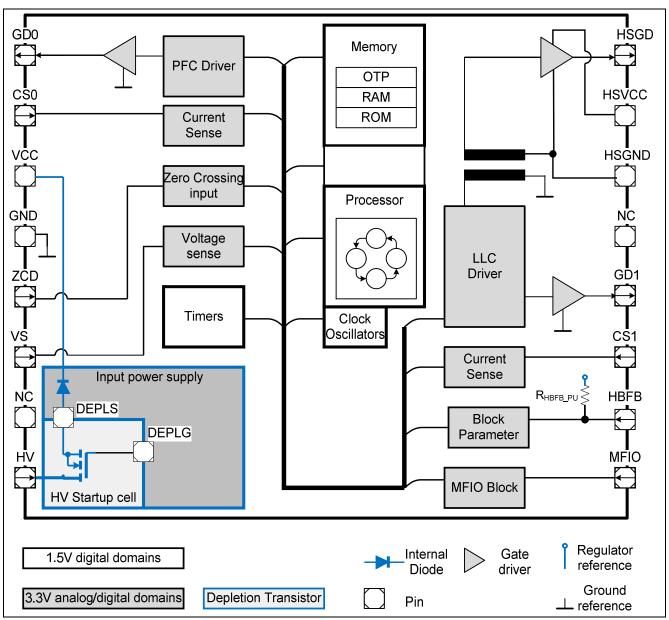

# 2 Representative Blockdiagram

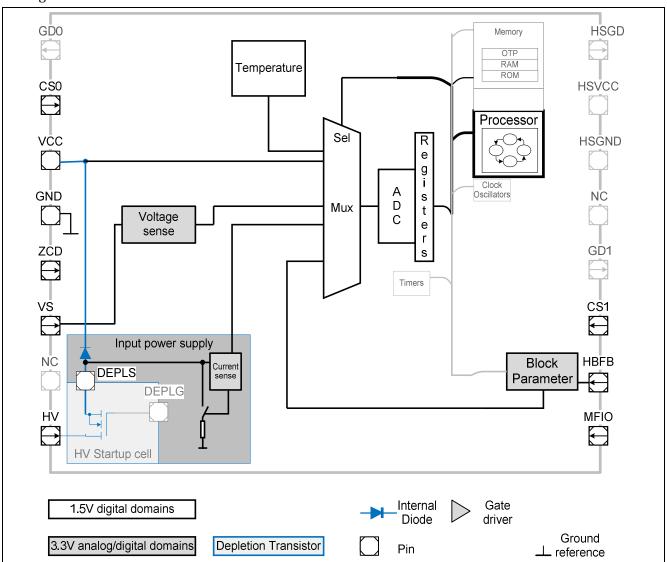

A simplified functional block diagram is given in Figure 3. Note that this figure only represents the principle functionality.

IDP2303 digital combo-PFC & LLC controller consists of an Infineon 66MHz ( $f_{MCLK}$ ) NanoDSP processor to actualize both the power factor correction (PFC) and a half-bridge resonant function. The PFC and LLC controllers function with their configured parameter to optimize the performance. The current sense, zero-crossing and voltage sense provide the controller as well as the processor inputs for its control.

Figure 3 Representative Blockdiagram

Datasheet 6 Rev. V2.0, 2017-03-21

## 3 Functional Description

The functional description gives an overview about the integrated functions and features and their relationship. The mentioned parameters and equations are based on typical values at  $T_A = 25$ °C. The correlated minimum and maximum values are shown in the electrical characteristics in Chapter 4.

This chapter contains following main descriptions:

- Introduction (Chapter 3.1)

- Overview Controller Features (Chapter 3.2)

- General control features (Chapter 3.3)

- PFC Controller (Chapter 3.4)

- Half-bridge LLC Controller (Chapter 3.5)

- Operation Flow (Chapter 3.6)

- Overview Protection Features (Chapter 3.7)

- Fixed and configurable parameters (Chapter 3.8)

#### 3.1 Introduction

The IDP2303 is a digital Combo-LLC controller to support application topologies with a multi-mode PFC and half-bridge LLC stage. The IC consists of a smart digital core that provides advanced algorithms for multi-mode operation and a variety of protection features. A high degree of forward integration is realized by implementing a floating HV gate driver and a HV startup cell in a slim PG-DSO-16 package. Multifunctional pins ensure a very low component count in the application. General controller features are summarized in Table 2.

The IC supports highest design-in flexibility in the application by means of an advanced set of configurable parameters. The configuration can be done via a half duplex UART interface at pin MFIO.

#### 3.2 Overview Controller Features

- General Controller Features (Table 2)

- PFC Controller Features (Table 5)

- LLC Controller Features (Table 6)

#### 3.3 Overview Controller Features

This chapter provides an overview of functional blocks for Figure 3. The general control features are

**Table 2** General Controller Features

| System and Devices overview                                   | Chapter 3.3.1   |

|---------------------------------------------------------------|-----------------|

| IC Power System and High Voltage Startup Cell                 | Chapter 3.3.2   |

| Direct AC input monitoring combined with VCC startup function | Chapter 3.3.2.1 |

| X-cap discharge function via the integrated HV startup-cell   | Chapter 3.3.2.2 |

| Standby Mode with synchronous PFC-LLC burst operation         | Chapter 3.3.3   |

| IC protection                                                 | Chapter 3.3.4   |

| Auto restart mode                                             | Chapter 3.3.4.4 |

| AC detection                                                  | Chapter 3.3.5   |

### 3.3.1 System and Device overview

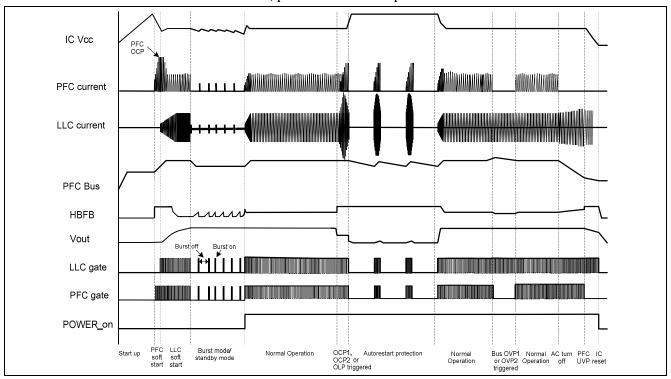

The device is dominantly used in an AC/DC application with a working scenario as illustrated below. The device on powering-up enters start-up and soft-start stage. Once the voltage at the primary side and

Datasheet 7 Rev. V2.0, 2017-03-21

secondary side of the transformer stabilizes, depending on the load condition, the device operates in extremely light load or normal operation.

In extremely light load condition, the device operates in burst, meaning the gate drivers are driven at a lower frequency ranges and switching on periodically only to maintain the supply voltage and the VCC of the device.

In normal operating condition, the device actively switches its gate driver to regulate the voltage and current supplies to the load.

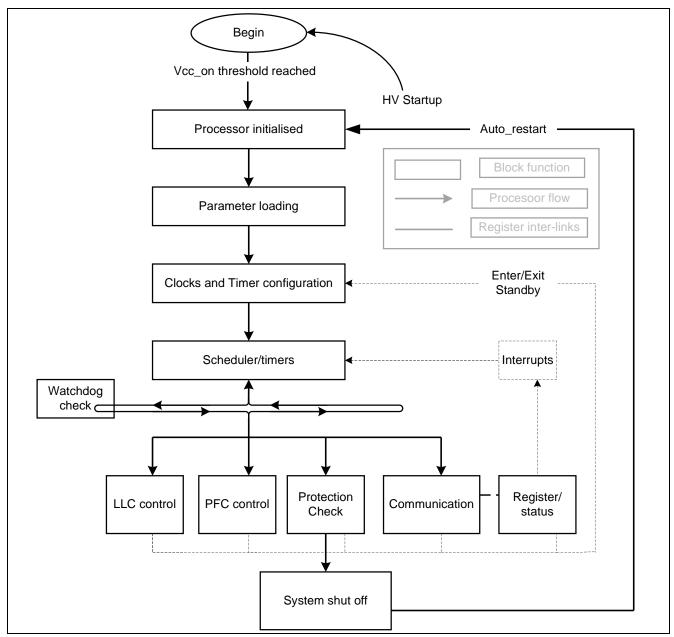

In Figure 4, when overcurrent protection mechanism is triggered, the device shall shut down its LLC and PFC controller and enter a restart of the system and attempt to re-power the system. There are many protection and shut-down scenario. For further detail, please refer to Chapter 3.7.

Figure 4 IDP2303 Operation Overview

### 3.3.1.1 Processor and memory operations

This chapter describes the IC power processor function and its operation.

On powering up, the device's processor initializes and loads its configuration from its one-time-programmable memory and configures the device to its application needs. The timer for the scheduler is programmed and the processor run within a scheduler timing function to continuous monitor for any protection event as well as optimize the parameter for the PFC and LLC controllers.

The processor runs in an active scheduler mode when the PFC and the LLC controller are running and runs in the following mode in specific condition of the system.

- HV-startup: System "cold start" with VCC startup via the integrated HV startup cell.

- Standby: System operates in synchronous PFC-LLC burst operation to keep output voltage regulated and yet maintain very low system power consumption

- Auto-restart: A protection mode that stops all PFC and LLC switching operations, puts the IC into a suitable sleep mode, and initiates a new startup after a configurable break time<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Please refer to Chapter 4.7 for more detail about the protection mechanisms.

Figure 5 Overview of Processor operations

The processor runs its program from its Read Only Memory (ROM) with random access memory (RAM) as main data space for computation and control-flow state records during operation.

The processor monitors and processes the analog-to-digital (ADC) data. The processed data is provided to control the power-factor-correction (PFC) and Resonant LLC converter. The processor also monitors the input line (AC), its own monitoring lines as well as the output load feedback voltage for protection condition and mitigates according to the conditions with the protection function. All the information are registered and interrupts are triggered when interrupt event occurs.

#### 3.3.1.2 Communication interface

The communication to external host is via the MFIO pin and is handled by the processor in firmware. A half-duplex UART communication data between the host and the device is transferred through internal UART.

Datasheet 9 Rev. V2.0, 2017-03-21

### 3.3.1.3 Voltage and current sensors

IDP2303 sensing nodes are multiplexed to an analog-to-digital (ADC) module to allow the device to monitor the system behavior and its internal behavior. The voltage and current sensors are multiplexed to the ADC as well.

Each of the sensing node samples its voltage or current and the sampling is multiplexed onto the ADC where the digital read-out is measured.

Figure 6 Voltage and current sensing multiplexing to ADC

Figure 6 shows the sensing paths that are multiplexed to the ADC. The ADC sensing is time-multiplexed to the sensing nodes and is managed internally by the processor. Timers are used to enable and disable the sample and hold circuit in the current sense block. Within each of the sensing block, there are sub-sensing nodes that allow measurement for each specific function. See Chapter 4.4.3 and Chapter 4.4.4 for further details.

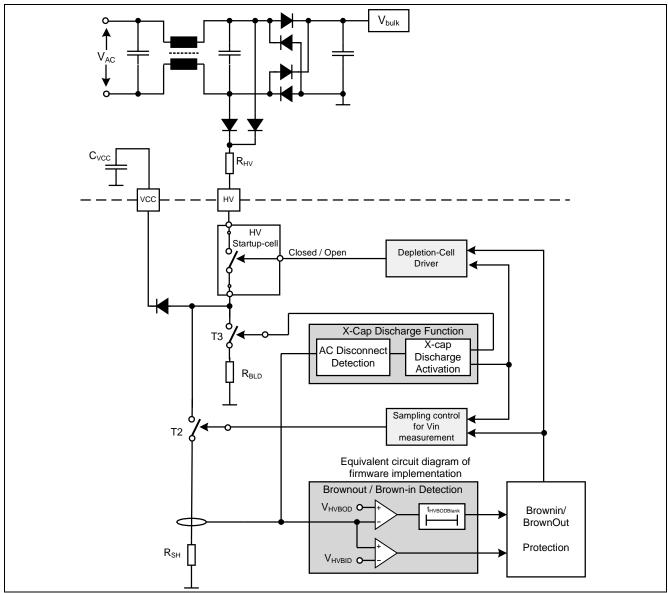

## 3.3.2 IC Power Supply and High Voltage Startup Cell

This chapter describes the IC power supply approach and the functions correlated with the high voltage startup cell for Figure 1. The functions supported by the high voltage startup cell are

- Direct AC input monitoring combined with VCC startup function (Chapter 3.3.2.1)

- X-cap discharge function via the integrated HV startup-cell (3.3.2.2)

IDP2303 contains four power supply pins VCC, GND, HSVCC and HSGND. The VCC is the main low voltage supply input at the IC. All the internal circuits except the integrated floating driver are connected to pin VCC and pin GND, which is the common ground. A capacitor needs to be placed directly at the pins VCC and GND to provide a proper buffering of the IC power supply voltage.

The pins HSVCC and HSGND are the power supply pins for the integrated floating high side driver. The high side driver is supplied by an external bootstrap buffer capacitor that also needs to be connected close to pins HSVCC and HSGND. The external bootstrap capacitor is charged via an external bootstrap diode and resistor which are connected in serial to the VCC supply.

In order to avoid unexpected delay of startup cell, upper resistance of the voltage divider for VS pin shall be selected above  $8M\Omega$ .

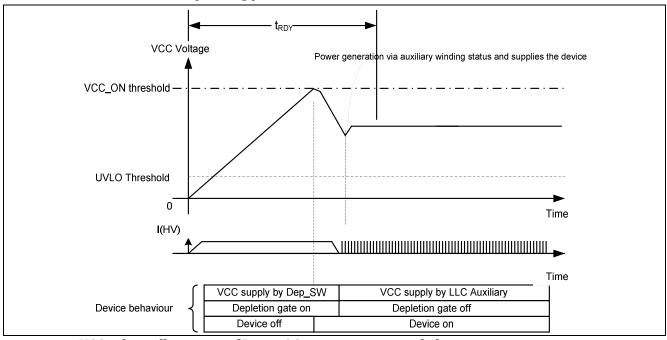

### 3.3.2.1 Direct AC input monitoring combined with VCC startup function

There are two main functions supported at pin HV, with the connection of the AC input voltage via a resistor,  $R_{HV}$  (51k $\Omega$ ) and two diodes (See Figure 8).

The integrated HV startup-cell is switched on during the VCC startup phase, when the IC is inactive. A current is flowing from pin HV to pin VCC via an internal diode, which charges the capacitor at pin VCC. This current is limited by the  $R_{\text{HV}}$  and the  $R_{\text{DS(on)}}$  of the HV startup-cell. Once the voltage at pin VCC exceeds the VCC on- threshold, the active operating phase is entered.

Figure 7 VCC voltage illustration of Direct AC input powering up behavior

Within the device, a direct AC input monitoring is supported by a resistive sense that is switched on periodically by an internal timer. The timer switches on the HV startup cell and the switch T2 for a very short time after a defined period. During this short on-time, the voltage across  $R_{SH}$  is sensed to estimate the HV voltage (See Figure 8).

Datasheet 11 Rev. V2.0, 2017-03-21

Figure 8 High voltage sensing at pin HV

### 3.3.2.2 X-cap discharge function via the integrated HV startup-cell

Safety standard requires X-caps to be discharged within one second once the switching mode power supply is disconnected from the AC line.

The AC waveform is closely monitored by the HV pin through external resistor  $R_{HV}$  (51 k $\Omega$ ). An AC detection algorithm checks if there is an alternating voltage at the converter input. This function works reliably for input voltages as specified in Table 3. As soon as the voltage stops alternating an AC unplug event is detected and input capacitors (XCAPs) are getting discharged via the depletion cell of IDP2303 between pins HV and GND. AC unplug detection time is typically within a few hundred Milliseconds and maximum 800 ms. The maximum discharge time constant for the maximum XCAP capacitance value of  $2\mu F$  (see Table 4) is then appr. 104 ms (with  $R_{HV} = 51k\Omega$  and the IC internal resistance of about  $1k\Omega$ ). Therefore the XCAPs are safely discharged within 1s to ES1 or SELV limits according to IEC62368 and IEC60950.

The X-caps are then discharged to fulfil the safety standard. The discharging current is determined by the external resistor  $R_{HV}$  (51  $k\Omega$ ) and  $R_{BLD}$  (see Figure 8). The X-cap discharge function is a configurable parameter.

Datasheet 12 Rev. V2.0, 2017-03-21

#### Digital Multi-Mode PFC + LLC Combo Controller

Table 3 Input voltage ratings for reliable AC detection

| Parameters    |         | Min. | Max. | Unit | Remarks |

|---------------|---------|------|------|------|---------|

| Input voltage |         | 90   | 264  | VAC  |         |

|               | Range 1 | 47   | 53   | Hz   |         |

| Frequency     | Range 2 | 57   | 63   | Hz   |         |

Table 4 XCAP discharge component ratings

| Parameters                                           | Min. | Max. | Unit | Remarks         |

|------------------------------------------------------|------|------|------|-----------------|

| Total capacitance of all XCAPs                       | 0.1  | 2    | μF   |                 |

| Total discharge resistance from AC voltage to HV pin | 51   | 51   | kΩ   | R <sub>HV</sub> |

### 3.3.3 Standby Mode with synchronous PFC-LLC burst operation

For IDP2303, a "STANDBY" signal from the application will trigger the start to enter standby mode. The "STANDBY" signal will cause a change in resistor divider ratio such that the rated output voltage is regulated at lower voltage in standby mode. If  $V_{HBFB}$  is less than  $V_{\_burst\_enter}$  for a blanking time of  $t_{\_blk\_burst}$ , both PFC and LLC will stop switching immediately. The IC is put into power saving mode. The controller enters into burst pause phase of standby mode.

During the standby mode, the HBFB pin is monitored to control the burst mode operation. When the HBFB voltage rises up and reaches the burst on threshold  $V_{burst\_on}$ , or VCC drops below  $V_{VCC\_burst\_off}$ , the device will wake up and start burst mode operation. LLC burst on time  $t_{\_burst\_on\_max}$  is constant and configurable with soft-start and soft-stop. After LLC completes one full busrt on switching, the device will stop switching and enters sleep mode to save the power consumption.

The LLC busrt frequency  $f_{sw\_busrt}$  and  $t_{burst\_on\_max}$  are optimized at typical standby power load in order to achieve lowest input power and output ripple. Meanwhile, under ultra light load condition, e.g. no load condition, LLC will increase burst frequency adaptively according burst off time. In the end, burst frequency is stabilized so as to regulate busrt off time around maximum burst off time  $t_{burst\_off\_max}$ . By setting proper  $t_{burst\_off\_max}$ , LLC can deliver right-fit energy adaptively to different load and avoid deep saturation of feedback loop, which is able to reduce output ripple, minimize power consumption at secondary feedback path and perform excellent dynamic load response.

When heavy load comes, the HBFB voltage will rise up and hit the leaving burst mode threshold  $V_{burst\_exit}$ . Then the device will leave burst mode operation. Another leaving burst mode condition is when the burst off time reaches the minimum burst off time limit  $t_{burst\_off\_min}$ .

### 3.3.4 IC protection

### 3.3.4.1 Undervoltage lockout for VCC

There is an undervoltage lockout unit (UVLO) implemented, that ensures a defined enabling and disabling of the IC operation depending on the supply voltage at pin VCC. The UVLO contains a hysteresis with the voltage thresholds  $V_{\text{VCCon}}$  for enabling the IC and  $V_{\text{VCCoff}}$  for disabling the IC.

Datasheet 13 Rev. V2.0, 2017-03-21

### 3.3.4.2 Overvoltage protection for VCC

### 3.3.4.3 Over temperature protection

When the internal temperature exceeds the over temperature protection level  $T_{\_OTP}$ , the system enters into auto restart mode. If the temperature is lower than  $T_{\_OTP\_reset}$  at the end of the auto restart breaktime, the system exits auto restart mode and enters startup mode. Otherwise, if the temperature is higher than  $T_{\_OTP\_reset}$  at the end of the auto restart breaktime, the system remains in auto restart mode.

#### 3.3.4.4 Auto Restart Mode

Once the auto restart mode is entered, the IC stops both PFC and LLC switching operations and enters sleep mode. During this auto restart off-phase the HV startup-cell is activated to maintain the VCC voltage. After the configurable auto restart breaktime t<sub>.AR</sub> the IC initiates a new start-up.

#### 3.3.5 AC detection

This feature is used for detecting AC unplug condition during standby mode and is implemented via a combination of built-in hardware and firmware. The figure below shows the configuration of the EMI filter and where input voltage is sensed through the HV pin.

Figure 9 Circuit with AC detection with EMI filter

During standby mode, low power consumption is the main challenge. IDP2303 makes use of the AC detection function to detect the AC unplug quicky and reliably. With the AC detection, it neither needs to sample the AC voltage too often nor needs to trigger the wakeup of the IC too often and hence it can maintain low standby power consumption. Having detected the AC unplugged, the X-cap discharge function would be triggered. In the AC detection function, IDP2303 would take AC samples after defined time intervals and based on proprietary algorithm it determines the decision of unplug condition.

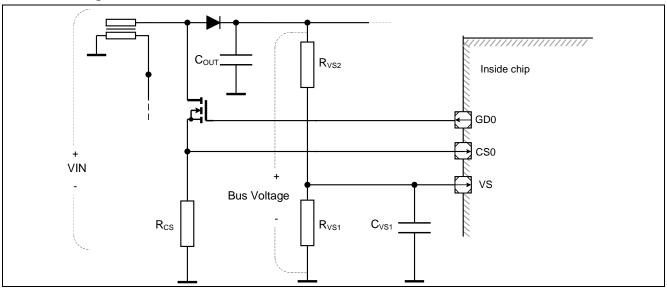

#### 3.4 PFC Controller

The PFC controller turns on and off the PFC gate driver so that a desired bus voltage is maintained while the AC input current is approximately proportional to the AC line voltage resulting in high power factor and low THD. A gate driver switching cycle has divided into three phases:

- the on-time, t<sub>on</sub>, where the PFC MOSFET is turned on, and the PFC choke current increases

- the freewheeling time, t<sub>f</sub>, where the PFC MOSFET is turned off, the choke current decreases and charges the PFC output capacitor via the freewheeling diode

Datasheet 14 Rev. V2.0, 2017-03-21

• the waiting time t<sub>w</sub>, which starts when the choke current decreased to zero and an oscillation is observed at the drain-source voltage of the switching MOSFET and the voltage at the auxiliary winding.

Figure 10 PFC control at GD0 pin and Voltage and current sensing at VS and CS pins

The following PFC functionality of the controller is described:

**Table 5** PFC Controller Features

| PFC Softstart                                                 | Chapter 3.4.1   |

|---------------------------------------------------------------|-----------------|

| Multi-mode PFC control                                        | Chapter 3.4.2   |

| PFC Protection                                                | Chapter 3.4.3   |

| PFC Open Control Loop Protection (PFCOLP)                     | Chapter 3.4.3.1 |

| PFC Inductor Over Current Protection (PFCOCP)                 | Chapter 3.4.3.2 |

| PFC Output Over Voltage Protection (PFCOVP)                   | Chapter 3.4.3.3 |

| PFC Output Redundant Over Voltage Protection (PFCROVP)        | Chapter 3.4.3.4 |

| PFC Output Under Voltage Protection (PFCUVP)                  | Chapter 3.4.3.5 |

| PFC Brownin Protection for AC Input Line (PFCBID)             | Chapter 3.4.3.6 |

| PFC Brownout Protection for AC Input Line (PFCBOD)            | Chapter 3.4.3.7 |

| PFC Long Time Continuous Conduction Mode Protection (PFCCCMP) | Chapter 3.4.3.8 |

#### 3.4.1 PFC Softstart

PFC softstart, a PI controller calculates the on-time as a function of the difference between the reference bus voltage and the actual PFC bus voltage. To compensate for the on-time and hence line dependency of the boost power stage, the output of the PI controller is multiplied with on-time. The PFC operates in fixed QR-1 operation with minimum on-time. With the minimum on-time multiplied to the output of the PI controller, it will form an exponential softstart ramp for on-time that limits the switching frequency and startup current. Once the desired PFC bus voltage is reached, it resumes to normal multimode PFC operation.

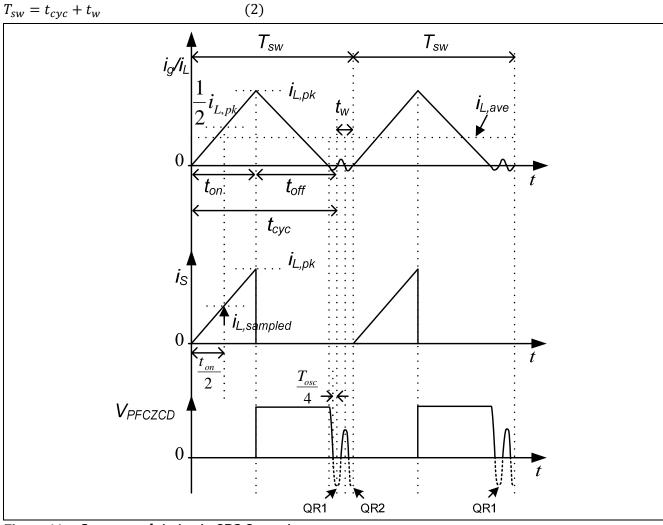

### 3.4.2 PFC Multi-mode operation

For PFC operating in critical conduction mode CrCM, the MOSFET is turned on with a constant on-time throughout the complete AC half cycle and the off-time is varying during the AC half cycle depending on the instantaneous input voltage applied. Thus, the switching frequency is varying within each AC half cycle with the lowest switching frequency at the peak of the AC input voltage and the highest switching frequency near the zero crossings of the input voltage. A new switching cycle starts immediately when the inductor current

Datasheet 15 Rev. V2.0, 2017-03-21

reaches zero. CrCM is also equivalent to quasi-resonant switching at first inductor current valley or QR1 operation. The switching period of CrCM operation is given by

$$T_{sw} = t_{cyc} = t_{on} + t_{off} \tag{1}$$

CrCM is ideal for full load operation, where the constant on-time is large. However, the constant on-time reduces at light load, resulting in very high switching frequency particularly near the zero crossings of the input voltage. The high switching frequency will increase the switching losses, resulting in poor efficiency at light load.

The new multimode PFC control algorithm implemented in IDP2303 can lower the switching frequency by adding an additional delay into each switching cycle through selecting further inductor current valleys to achieve QR2, QR3 and up to QR10 operation. In this way, the switching frequency is limited between a minimum and maximum value. The switching period of the multimode PFC operation, consisting of QR1 to QR10 operation and DCM, is given by

Figure 11 Current and timing in QR2 Operation

Introduction of the delay helps to reduce switching frequency but it also distorts the input current waveform and thus affects the PFC THD performance. The multimode PFC control also consists of an algorithm that optimizes the applied on-time on a cycle by cycle basis so as to ensure good input current shaping and improve PFC THD performance.

Datasheet 16 Rev. V2.0, 2017-03-21

#### 3.4.3 PFC Protection

The PFC stage is protected against:

- PFC Open Control Loop Protection (PFCOCLP) (Chapter 3.4.3.1)

- PFC Inductor Over Current Protection (PFCOCP) (Chapter 3.4.3.2)

- PFC Output Over Voltage Protection (PFCOVP) (Chapter 3.4.3.3)

- PFC Output Redundant Over Voltage Protection (PFCROVP) (Chapter 3.4.3.4)

- PFC Output Under Voltage Protection (PFCUVP) (Chapter 3.4.3.5)

- PFC Brownin Protection for AC Input Line (PFCBID) (Chapter 3.4.3.6)

- PFC Brownout Protection for AC Input Line (PFCBOD) (Chapter 3.4.3.7)

- PFC Long Time Continuous Conduction Mode Protection (PFCCCMP) (Chapter 3.4.3.8)

### 3.4.3.1 PFC Open Control Loop Protection (PFCOCLP)

Open control loop is detected if the voltage value at pin VS is lower than the threshold  $V_{OlpPFC}$ . This may happen in case that the voltage sensing loop is highside open circuit or the input voltage is too low. If open loop is detected at the IC startup, both the PFC and the HB LLC controller do not start up. If this open loop condition is detected during system operation, the system enters into auto restart mode.

### 3.4.3.2 PFC Inductor Over Current Protection (PFCOCP)

In the converter system, the peak current through the MOSFET is monitored via the PFC shunt resistor  $R_{PCS}$  to minimise stress for the MOSFET, the inductor  $L_{PFC}$  and the diode  $D_{PFC}$ . Once the voltage across the shunt resistor exceeds the over current threshold  $V_{CSOocpset}$ , the MOSFET gate is turned off. Afterwards, the ZCD signal, or the PFC maximal period time-out signal, initializes the next switching cycle. This protection mechanism is active in every switching cycle.

### 3.4.3.3 PFC Output Over Voltage Protection (PFCOVP)

A two stage overvoltage protection scheme is implemented where a slower average measurement of the bus voltage shall trigger a shutdown of the PFC under OVP1 of a lower threshold by firmware, and a faster immediate measurement of the bus voltage shall also trigger a shutdown of the PFC under OVP2 by hardware. For OVP1, if the average sensed PFC bus voltage exceeds the threshold  $V_{\text{OvpSwSetPFC}}$ , the PFC will stop switching while the LLC continues to run. OVP2 is implemented by hardware. The threshold of this comparator is fixed at  $V_{\text{OvpHwSetPFC}}$  =2.8V. Once the sensed bus voltage exceeds this threshold for a configurable filter delay time, the PFC will stop switching while the LLC continues to run. Once the average sensed PFC bus voltage reduces and reaches the reference bus voltage  $V_{\text{RefPFC}}$ , the PFC converter resumes normal operation.

### 3.4.3.4 PFC Output Redundant Over Voltage Protection (PFCROVP)

For ROVP, if the PFC bus voltage exceeds  $V_{ROVP\_set}$ , one ROVP count is recorded. The PFC will stop switching but the LLC continues to run. Once the average sensed PFC bus voltage reduces and reaches the reference bus voltage  $V_{ROVP\_reset}$ , the PFC converter resumes to normal operation. If another ROVP is recorded within  $t_{ROVP}$  (8s), it is recorded as  $2^{nd}$  ROVP count. The PFC will stop switching again but the LLC continues to run. However, the ROVP count will be reset to zero if a next ROVP event occurs after  $t_{ROVP}$  (8s). The  $t_{ROVP}$  (8s) starts counting when the last occurring ROVP event is triggered. Whenever the ROVP count accumulates to maximum ROVP count  $n_{ROVP}$  (10), the IC enters auto-restart mode.

In normal operations, the ROVP acts similar to the behavior of OVP1. When either OVP1 at VS pin or ROVP at MFIO pin is triggered, the same behavior occurs. In event that the OVP1 resistor divider has faulty resistance level, if VS voltage is lower, the PFC bus voltage would increase. In this case, the ROVP triggers to protect the

Datasheet 17 Rev. V2.0, 2017-03-21

#### Digital Multi-Mode PFC + LLC Combo Controller

system. Since the faulty resistance level remains unchanged, the ROVP will re-trigger again and again once the bus voltage drops to normal level when the switching is stopped and results in auto-restart mode.

This feature is disabled by default, which is selectable in the configurable parameters. Since the MFIO pin is a multifunction pin, not dedicated for high impedance bus voltage sensing, it must not be connect to the Bus voltage divider at start-up. Leakage into the pin during system start-up could affect the IC start-up behaviour. If this feature is enabled, the proposed solution with BSS127 shown in Figure 1 ensures a proper start-up and almost lossless ROVP function, not effecting standby performance.

### 3.4.3.5 PFC Output Under Voltage Protection (PFCUVP)

The PFC undervoltage protection (UVP) is a protection for the LLC converter from entering capacitive operation range. Since UVP is detected by sensing the PFC bus voltage, it is placed under PFC protection features. UVP is implemented by firmware. If the average sensed PFC bus voltage falls below a configurable UVP threshold  $V_{\text{UvpSetPFC}}$  for a blanking time of  $t_{\text{UvpBlkPFC}}$ , PFC undervoltage is detected. PFC and LLC will stop switching.

### 3.4.3.6 PFC Brownin Protection for AC Input Line (PFCBIP)

PFC brownin protection is implemented by firmware and it utilizes HV pin for AC input voltage sampling for better input voltage measurement.

The desired brownin input voltage threshold is  $V_{\text{HVBID}}$ . If  $V_{\text{ACrms}} > V_{\text{HVBID}}$ , brown-in is detected and the system enters into startup.

### 3.4.3.7 PFC Brownout Protection for AC Input Line (PFCBOP)

The PFC brownout protection prevents the system from operating at very low input voltage that is out of the normal operating range. This helps to protect the system from high current stress or device failures at very low input voltage. PFC brownout protection is implemented by firmware and it utilizes HV pin for AC input voltage sampling for better input voltage measurement.

The desired brownout input voltage threshold is  $V_{LMVBOD}$ . If  $V_{AC,rms} < V_{LMVBOD}$  and after a blanking time of  $t_{LMVBODblank}$ , brownout is detected. PFC will stop switching and LLC will continue switching.

### 3.4.3.8 PFC Long Time Continuous Conduction Mode Protection (PFCCCMP)

Continuous conduction mode (CCM) operation may occur during PFC startup for limited time duration. It is considered as a failure in the system only if CCM operation of the PFC converter is observed over a longer period of time. The PFC converter may run into CCM operation for a longer period due to shorted bypass diode, heavy load step that is out of specification or very low input voltage that is out of the normal operating range.

When CCM occurs, the magnetizing current in the PFC choke does not have a chance to decay to zero before the MOSFET turns on. There will be no quasi-resonant oscillation observed at the ZCD signal before the maximum switching period time-out is reached that turns the MOSFET on. This turn-on event without ZCD oscillation is monitored to protect the PFC converter from continuous CCM operation. The long time CCM protection is implemented by firmware.

At every sampling period, if the maximum switching period time-out occurs before any quasi-resonant oscillation is observed at the ZCD signal, the CCM time counter is increased by 1. If the PFC switching period is less than the time-out period, the CCM time counter is decreased by 1. Once the CCM time counter exceeds  $t_{\text{\tiny LCcmpPFC}}$ , the system enters into auto restart mode. The long time CCM protection is active only if the PFC ontime is above the threshold  $t_{\text{\tiny OnMinPFC}}$  by 200ns.

Datasheet 18 Rev. V2.0, 2017-03-21

### 3.5 Half-bridge LLC Controller

Following LLC functionality is described:

**Table 6** Half-bridge LLC Controller Features

| LLC Softstart (Time Controlled Oscillator TCO)             | Chapter 3.5.1   |

|------------------------------------------------------------|-----------------|

| LLC Normal Operation (Voltage Controlled Oscillator VCO)   | Chapter 3.5.2   |

| LLC Smooth Transition of Frequency Control From TCO to VCO | Chapter 3.5.3   |

| LLC Half-bridge Protection                                 | Chapter 3.5.4   |

| LLC Open Control Loop Protection (LLCOCLP)                 | Chapter 3.5.4.1 |

| LLC Over Load Protection (LLCOLP)                          | Chapter 3.5.4.2 |

| LLC Over Current Protection Level 1 (LLCOCP1)              | Chapter 3.5.4.3 |

| LLC Over Current Protection Level 2 (LLCOCP2)              | Chapter 3.5.4.4 |

|                                                            |                 |

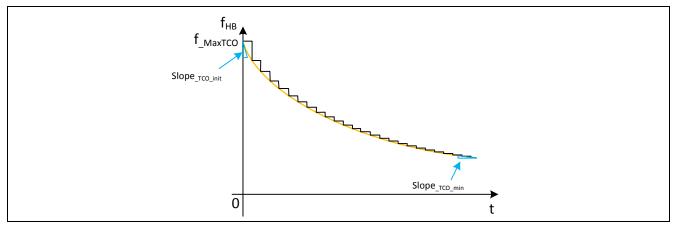

### 3.5.1 LLC Softstart (Time Controlled Oscillator TCO)

The half-bridge LLC controller enters softstart for every VCC power up and upon recovering from certain protection mode provided the bus voltage is in the proper range. In softstart, the switching frequency changes with the elapsing time (a time controlled oscillator - TCO), as shown in Figure 12.

The switching frequency starts at a maximum value and decrease with a defined frequency step change at every 2ms. The initial frequency step change is larger and the frequency step change will gradually decrease at every 2ms until it reaches the minimum frequency step change value.

Once the softstart switching frequency is close to the switching frequency output of the free-running voltage controlled oscillator (VCO), the external secondary side LLC bus voltage controller and VCO will take over the regulation of the LLC output voltage. The LLC enters into normal operation.

Figure 12 Frequency vs. Time of the TCO

### 3.5.2 LLC Normal Operation (Voltage Controlled Oscillator VCO)

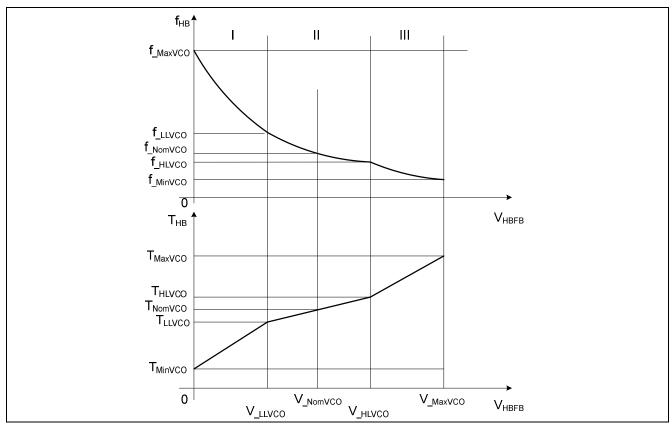

During normal operation, a voltage controlled oscillator (VCO) generates the HB LLC converter switching frequency  $f_{HB}$  based on the HB feedback voltage  $V_{HBFB}$ . In this controller, the curve of the HB switching frequency  $f_{HB}$  in response to the feedback voltage  $V_{HBFB}$  is schematically shown as in Figure 13.

The VCO switching period vs. feedback voltage inside this controller consists of three pieces of direct line with different slew rate. As shown in Figure 13, the line in area II (normal operation) has much lower slew rate than the area I (Light Load) and III (Heavy Load). Therefore, the VCO in the area II has a much better frequency resolution than in the area I and III. In this way, fine frequency resolution around the nominal operating point  $V_{\text{NomHB}}$  is realized, while a wide operating frequency range can be covered with fast response to the load change in both heavy and light load is realized.

Datasheet 19 Rev. V2.0, 2017-03-21

Figure 13 Frequency vs. Feedback Voltage of the VCO

The switching period curve is defined by following key points: feedback origin (0,  $T_{MinVCO}$ ), VCO light load ( $V_{LLVCO}$ ,  $T_{LLVCO}$ ), VCO nominal point ( $V_{NomVCO}$ ,  $T_{NomVCO}$ ), VCO heavy load ( $V_{HLVCO}$ ,  $T_{LLVCO}$ ) and feedback maximal point ( $V_{MaxVCO}$ ,  $T_{MaxVCO}$ ). In this controller, all values are calculated based on the VCO nominal frequency  $f_{NomVCO}$  and nominal feedback voltage  $V_{NomVCO}$  with certain factors, as:

the minimal and maximal HB LLC switching frequency  $f_{\_MinVCO}$  and  $f_{\_MaxVCO}$ :

$$f_{\underline{MinVCO}} = k_{fMinVCO} \cdot f_{\underline{NomVCO}}$$

(3)

$$f_{MaxVCO} = k_{fMaxVCO} \cdot f_{-NomVCO} \tag{4}$$

the frequency at the corners:

$$f_{HLVCO} = k_{fHLVCO} \cdot f_{-NomVCO} \tag{5}$$

$$f_{LLVCO} = k_{fLLVCO} \cdot f_{NomVCO} \tag{6}$$

and the feedback voltages:.

$$V_{HLVCO} = k_{vHLVCO} . V_{NomVCO}$$

(7)

$$V_{\_LLVCO} = k_{vLLVCO} . V_{\_NomVCO}$$

(8)

Once these points are defined, the switching period is calculated by a linear interpolation of the switching period to the feedback voltage, and the switching frequency curve over the whole feedback range is resulted, which is naturally non-linear function of the feedback voltage, as shown in Figure 13.

For an optimal HB LLC operation, the frequency  $f_{\_NomVCO}$  should be set as the resonant frequency of the LLC resonant tank, while the respected feedback voltage  $V_{\_NomVCO}$  is taken at the middle of the regulation feedback range.

Datasheet 20 Rev. V2.0, 2017-03-21

### 3.5.3 LLC Smooth Transition of Frequency Control from TCO to VCO

With built-in HB LLC softstart, the output voltage rises up smoothly and feedback voltage  $V_{\text{HBFB}}$  is available once the output voltage reaches in the regulation range. During the startup, LLC leaves the softstart mode and enters normal operation mode if the switching frequency determined by the VCO is equal to or higher than the switching frequency determined by the TCO, then the voltage controlled oscillator (VCO) takes over the frequency control.

### 3.5.4 LLC Half-bridge Protection

The LLC half-bridge is protected against:

- LLC Open Control Loop Protection (LLCOCLP) (Chapter 3.5.4.1)

- LLC Over Load Protection (LLCOLP) (Chapter 3.5.4.2)

- LLC Over Current Protection 1 (LLCOCP1) (Chapter 3.5.4.3)

- LLC Over Current Protection 2 (LLCOCP2) (Chapter 3.5.4.4)

In this controller, the HB LLC converter is protected against HB open loop and over load (OLP), over current

### 3.5.4.1 LLC Open Control Loop Protection (LLCOCLP)

Open control loop may happen due to open circuit in opto-coupler either at the diode or at the transistor, open circuit in HB feedback pin or the broken connection of the IC pin to the opto-coupler transistor source terminal. In this case, the HB feedback  $V_{HBFB}$  stays at high. After the end of the softstart, the averaged value of the feedback voltage  $V_{HBFB}$  over time period of  $N_{AccHB}$  \*  $t_{SrHB}$  is compared with the threshold  $V_{OlpHB}$ . If the measured value is higher than the threshold for time  $t_{OlpHB}$ , then the open loop protection is triggered and the whole system enters auto-restart mode. The system will be stopped and a time break  $t_{AR}$  follows. After this time break, the HB LLC converter restarts again with softstart. This is open loop protection.

### 3.5.4.2 LLC Over Load Protection (LLCOLP)

Over load at the HB LLC output during normal operation leads to rise of the feedback voltage  $V_{HBFB}$ . Once the averaged value of the feedback voltage  $V_{HBFB}$  over time period of  $N_{AccHB}$  \*  $t_{SrHB}$  is high than the threshold  $V_{OlpHB}$  for time  $t_{OlpHB}$ , the over load protection is triggered and the HB controller, together with PFC, enters auto-restart mode. The HB LLC converter will be stopped and a time break  $t_{AR}$  follows. After this time break, the HB LLC converter restarts again with softstart.

## 3.5.4.3 LLC Over Current Protection Level 1 (LLCOCP1)

LLC OCP1 is implemented with hardware comparator and firmware handling and the condition is checked at every LLC switching. The voltage across the shunt resistor  $R_{HB}$  at the low-side MOSFET is sensed via the CS1 pin.

If the voltage across the shunt resistor  $R_{HB}$  at the low-side MOSFET exceeds the OCP1 threshold, OCP1 protection is triggered to increase the current switching frequency t at rate of  $t_{Slope\_after\ OCP1}$  to limit the power. The higher switching frequency results in reduced current flowing in the LLC tank and limits the output power transfer. If the sensed current falls below the OCP threshold, the LLC switching frequency starts to be reduced. At the point where the calculated LLC switching frequency based on the HBFB signal is higher than the switching frequency as defined by the OCP1 protection, the LLC converter resumes control under VCO.

If above scenario occurs continuously more than  $N_{\_0cp1\_max}$  times, then there will be a serious fault condition, IC will enter auto restart protection mode to protect the whole system. In the meantime, due to the limited

Datasheet 21 Rev. V2.0, 2017-03-21

power transfer during OCP1 protection, the open loop protection or overload protection could also be triggered to enter auto restart protection mode.

Table 7 LLC Overcurrent protection 1 parameters <sup>1</sup>

| Parameters                                      |                 |                   | Symbol                 | Values                    |      |       | Unit | Note/Test Condition |    |

|-------------------------------------------------|-----------------|-------------------|------------------------|---------------------------|------|-------|------|---------------------|----|

|                                                 |                 |                   |                        |                           | Min. | Тур.  | Max. |                     |    |

| LLC                                             | OCP1            | detection         | during                 | V <sub>Ocp1_startup</sub> | -    | 550   | -    | mV                  | 13 |

| startı                                          | up <sup>2</sup> |                   |                        |                           |      |       |      |                     |    |

| LLC                                             | OCP1            | detection         | during                 | $V_{\text{Ocp1\_burst}}$  | -    | 750   | -    | mV                  | 13 |

| leavii                                          | ng burst        | mode <sup>2</sup> |                        |                           |      |       |      |                     |    |

| LLC                                             | OCP1            | detection         | during                 | $V_{\mathrm{Ocp1\_norm}}$ | -    | 427.5 | -    | mV                  |    |

| normal operation mode 4                         |                 |                   | ŀ                      |                           |      |       |      |                     |    |

| Maximum overcurrent count for N <sub>Ocp1</sub> |                 |                   | $N_{\text{Ocp1\_max}}$ | -                         | 8    | -     | -    |                     |    |

| overd                                           | current         | protectio         | n to                   |                           |      |       |      |                     |    |

| trigge                                          | er              |                   |                        |                           |      |       |      |                     |    |

<sup>&</sup>lt;sup>1</sup> This setting is application specific and is changed accordingly for application. Please check setting when application varies.

### 3.5.4.4 LLC Over Current Protection Level 2 (LLCOCP2)

LLC OCP2 could be triggered by a large primary side current through the shunt resistor. OCP2 is implemented by hardware via the OCP2 comparator. The status of OCP2 hardware can be read by firmware to detect if OCP2 event has occurred for subsequent action to be taken. If the voltage across the shunt resistor is higher than the threshold  $V_{\text{Ocp2}}$ , the system enters into auto restart mode.

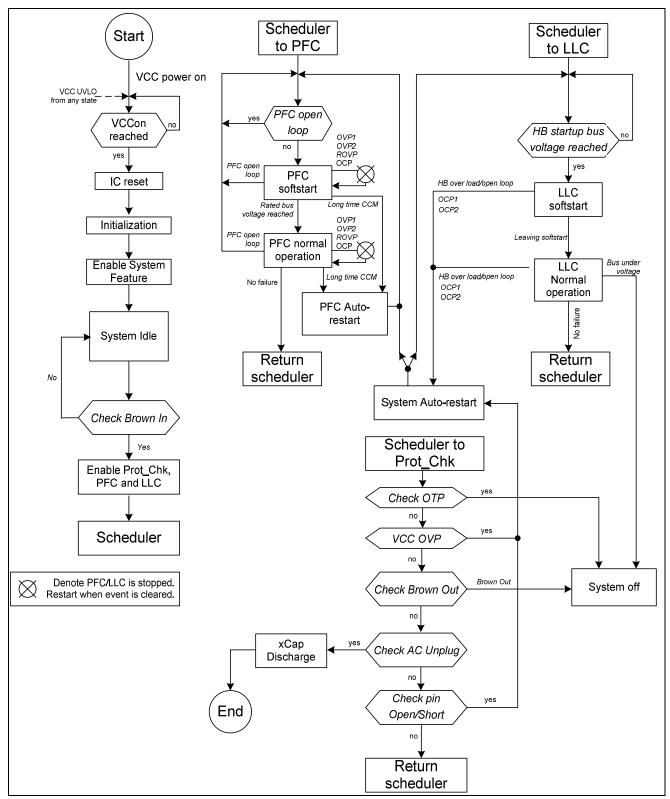

### 3.6 Operation Flow

In this chapter the control flow of the IC are described. Operating flowchart is shown in Figure 14.

- IC Initialization (Section 4.6.1)

- Operation flow of the PFC Controller (Section 4.6.2)

- Operation flow of the HB LLC Controller (Section 4.6.3)

#### 3.6.1 IC Initialization

As mentioned previously, once the VCC is above the turn-on threshold, the IC is active. The IC enters initialization state immediately after the VCC is powered up. In the initialization state, the correct setup values are assigned to the control units and then both PFC and HB are enabled. Also refer to Figure 5 for scheduler.

Datasheet 22 Rev. V2.0, 2017-03-21

<sup>&</sup>lt;sup>2</sup> Voltage level triggered only during start up and burst mode.

<sup>&</sup>lt;sup>3</sup> Parameter is not tested in production test.

<sup>&</sup>lt;sup>4</sup> Applicable in normal operation only. Voltage level not triggered for soft-start and burst mode.

Figure 14 General Operation Flow of the Controller

# 3.6.2 Operation Flow of the PFC Controller

If the PFC is disabled, there is no sensing of any PFC related signal and no switching of the PFC gate driver, the PFC MOSFET gate is actively pulled down to ground.

Once the PFC is enabled, the bus voltage is checked against open loop. If no open loop is detected, the PFC begins its operation with softstart.

Datasheet 23 Rev. V2.0, 2017-03-21

During PFC softstart, the PFC starts its operation according to the sensed signals at ZCD, CSO, and VS. The voltage control loop (PI regulator) is kept fast enough and the integrator of the PI regulator growth is limited to avoid output voltage overshoot. As soon as the bus voltage is getting close to the rated value, the PFC enters normal operation state where it is regulated to improve the power factor. The bus voltage is regulated to its rated value.

From the PFC protections, OCP does not cause any break of the PFC converter operation but OVP1 and OVP2 will cause a short break of the PFC operation. After the bus voltage comes back to the rated value, the PFC resumes its operation immediately. In case of long time CCM operation, the PFC enters auto-restart state. After the auto-restart time break, the PFC restarts with softstart.

### 3.6.3 Operation Flow of the Halfbridge LLC Controller

If the HB LLC is disabled, there is no sensing of any HB LLC converter related signal and no switching of the high and low side gate driver. The MOSFET gates are actively pulled down to ground.

Once the HB LLC is enabled, the controller checks the bus voltage against the HB startup bus voltage  $V_{HBstrt}$ . After the HB startup voltage at the PFC bus is reached, the HB LLC controller enters softstart state. In this state, the HB LLC converter switching frequency is controlled by TCO and decreases with time. The output will be built up and feedback signal should be available within the softstart time,  $t_{ss\_max}$ . Once the feedback voltage reaches a certain value that the frequency determined by VCO is equal to current frequency determined by the TCO, the controller enters normal operation state, feedback signal is then used for the output regulation by the VCO.

Some failures may stop the HB operation and lead the controller back to valid bus voltage check, i.e. by bus under voltage, or the softstart state after the HB auto-restart time break, i.e. by open loop or over load. In case of the over current protection 2 (OCP2), the HB LLC converter enters system auto-restart mode.

A comprehensive set of protection is integrated inside this controller for PFC and HB LLC converter. Some of them have just influence on the PFC or HB LLC only while some have influence on the other part of the controller. This information is summarized as in the Table 8 and Table 9.

Table 8 PFC Protections If Enabled

| Protection                    | Effect on PFC converter                                                                                                             | Effect on HB converter                                           |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| Bus over voltage protection 1 | $V_{VS} > V_{_{_{_{_{_{_{_{_{_{_{_{_{}}}}}}}}}}}}$                                                                                  | no influence                                                     |  |

| Bus over voltage protection 2 | $V_{VS} > V_{_{_{_{_{_{_{_{_{_{_{_{_{_{}}}}}}}}}}$                                                                                  | no influence                                                     |  |

| Bus under voltage             | $V_{VS} < V_{\_UvpSetPFC}$ : stops operation                                                                                        | $V_{\text{VS}} < V_{\text{UvpSetPFC}}$ : LLC continues switching |  |

| VS open loop<br>protection    | $V_{VS}$ < $V_{\_OlpPFC}$ for : no startup of PFC                                                                                   | no start up                                                      |  |

| PFC over current protection   | $V_{CS0} > V_{CS0ocpSet}$ for $t_{OcpLebPFC}$ : stops gate immediately; next gate turn-on triggered by ZCD or $t_{maxPFC}$          | no effect                                                        |  |

| PFC minimal on-time           | PFC on time from regulator $t_{on} < t_{\_OnMinPFC}$ : blocks PFC gate signal; $t_{on} > t_{\_OnMinPFC}$ : releases PFC gate signal | no effect                                                        |  |

| PFC maximal on-time           | $t_{on} > t_{OnMaxPFC} : t_{on} = t_{OnMaxPFC}$                                                                                     | no effect                                                        |  |

| PFC Brownin                   | V <sub>ACrms</sub> > V <sub>_HVBID</sub> : Enters startup                                                                           | no effect                                                        |  |

| PFC Brownout                  | $V_{ACrms} < V_{LHVBOD}$ : After a blanking time of $t_{LHVBODblank}$ , stops PFC operation                                         | LLC continues switching                                          |  |

| PFC long time CCM protection  | CCM operation for longer than $t_{\text{\_CcmpPFC}}$ : sys                                                                          | tem Auto-restart                                                 |  |

Table 9 LLC Protections If Enabled

Datasheet 24 Rev. V2.0, 2017-03-21

#### Digital Multi-Mode PFC + LLC Combo Controller

| Protec     | tion                                                                               |           | Effect on PFC converter                                                                  | Effect on HB converter |  |  |  |  |

|------------|------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| НВ         | HB over current $V_{CS1} > V_{\_OCP1}$ for $N_{\_Ocp1\_max}$ : system Auto-restart |           |                                                                                          |                        |  |  |  |  |

| prote      | ction 1                                                                            |           | V <sub>CS1</sub> > V <sub>_OCP1</sub> 101 IV <sub>_OCP1</sub> max. System rideo restaire |                        |  |  |  |  |

| HB         | over                                                                               | current   | $V_{CS1} > V_{OCP2}$ : system Auto-restart                                               |                        |  |  |  |  |

| prote      | ction 2                                                                            |           | VCS1 > V_OCP2: System Auto-restart                                                       |                        |  |  |  |  |

| НВ о       | pen con                                                                            | trol loop |                                                                                          |                        |  |  |  |  |

| protection |                                                                                    |           | V N fort motors Antomotors                                                               |                        |  |  |  |  |

| НВ         | over                                                                               | load      | $V_{HBFB} > V_{OlpHB}$ for $t_{OlpHB}$ : system Auto-restart                             |                        |  |  |  |  |

| protection |                                                                                    |           |                                                                                          |                        |  |  |  |  |

#### 3.7 Overview Protection Features

The following table provides an overview about the complete protection feature set. The corresponding default actions are listed for the cases where a protection feature is triggered.

If the application requires different behavior for the items in the table 8, please contact Infineon representatives.

**Table 10** Overview Protection Features

| Protection Fatures                   | Symbol  | Default Action                      | Description     |

|--------------------------------------|---------|-------------------------------------|-----------------|

| Undervoltage Lockout for VCC         | ULVO    | PFC and LLC stop switching          | Chapter 3.7.1   |

| Overvoltage Protection for VCC       | VCCOVP  | Auto restart                        | Chapter 3.7.2   |

| Overtemperature Protection by means  | OTP     | Auto restart                        | Chapter 3.7.3   |

| of internal Temperature Detection    |         |                                     |                 |

| PFC Open Control Loop Protection     | PFCOCLP | Auto restart                        | Chapter 3.4.3.1 |

| PFC Inductor Over Current Protection | PFCOCP  | PFC turns off switch immediately    | Chapter 3.4.3.2 |

| PFC Output Over Voltage Protection   | PFCOVP  | PFC stops switching                 | Chapter 3.4.3.3 |

| PFC Output Redundtant Over Voltage   | PFCROVP | Auto restart                        | Chapter 3.4.3.4 |

| Protection                           |         |                                     |                 |

| PFC Output Under Voltage Protection  | PFCUVP  | PFC stops switching while LLC       | Chapter 3.4.3.5 |

|                                      |         | continues switching                 |                 |

| PFC Brownin Protection for AC Input  | PFCBIP  | IC starts switching operation after | Chapter 3.4.3.6 |

| Line (PFCBIP)                        |         | threshold exceeded                  |                 |

| PFC Brownout Protection for AC Input | PFCBOP  | PFC stops switching while LLC       | Chapter 3.4.3.7 |

| Line                                 |         | continues switching                 |                 |

| PFC Long Time Continuous Conduction  | PFCCMP  | Auto restart                        | Chapter 3.4.3.8 |

| Mode Protection                      |         |                                     |                 |

| LLC Open Control Loop Protection     | LLCOCLP | Auto restart                        | Chapter 3.5.4.1 |

| LLC Over Load Protection             | LLCOLP  | Auto restart                        | Chapter 3.5.4.2 |

| LLC Over Current Protection 1        | LLCOCP1 | Frequency increases                 | Chapter 3.5.4.3 |

| LLC Over Current Protection 2        | LLCOCP2 | Auto restart                        | Chapter 3.5.4.4 |

### 3.7.1 Undervoltage Lockout for VCC

There is an undervoltage lockout unit (UVLO) implemented, that ensures a defined enabling and disabling of the IC operation depending on the supply voltage at pin VCC. The UVLO contains a hysteresis with the voltage thresholds  $V_{\text{VCCon}}$  for enabling the IC and  $V_{\text{VCCoff}}$  for disabling the IC.

Once the mains input voltage is applied, a current is flowing through an external resistor into pin HV via the integrated diode to pin VCC. The IC is enabled once VCC exceeds the threshold  $V_{\text{VCCon}}$  and enters normal operation if no fault condition is detected. In this phase  $V_{\text{VCC}}$  will drop until the self supply via the auxiliary winding takes over the supply at pin VCC. The self supply via the auxiliary winding must be therefore in place before  $V_{\text{VCC}}$  undershoots the  $V_{\text{VCCoff}}$  threshold.

Datasheet 25 Rev. V2.0, 2017-03-21

#### Digital Multi-Mode PFC + LLC Combo Controller

### 3.7.2 Overvoltage Protection for VCC

There is an over voltage detection at pin VCC implemented. The detection function consists of a threshold  $V_{\text{\tiny VCCOVP}}$  and a blanking time of  $t_{\text{\tiny VCCOVP}}$ . The IC is disabled once the overvoltage protection is triggered at pin VCC.

### 3.7.3 Overtemperature Protection by means of internal Temperature Detection

There is an over temperature protection implemented, that initiates a thermal shutdown once the internal temperature level  $T_{\tiny OTP}$  is exceeded. Subsequently if the temperature falls down and hits the reset value  $T_{\tiny OTP}$  reset, device will resume switching with softstart.

### 3.8 Fixed and Configurable Parameters

In this chapter all the fixed and configurable parameters are shown. The list of parameters shown in the following tables is default value and has been verified in a reference design system.

#### 3.8.1 Fixed Parameters

The below parameters are fixed and cannot be changed.

**Table 11** General Parameters

| Parameter Symbol Parameter Description |                           | Pin | Fixed Value | Unit |

|----------------------------------------|---------------------------|-----|-------------|------|

| V_VCCOVP                               | VCC OVP                   | VCC | 23.5        | V    |

| t_HVBODBlank                           | AC brownout blanking time | -   | 120         | ms   |

| T_OTP                                  | IC OTP                    | -   | 125         | °C   |

| T_OTP_reset                            | IC OTP reset              | -   | 90          | °C   |

#### **Table 12** PFC Parameters

| Parameter Symbol    | Parameter Description                             | Pin | Fixed Value | Unit |

|---------------------|---------------------------------------------------|-----|-------------|------|

| $V_{\text{OlpPFC}}$ | PFC open loop                                     | VS  | 0.39        | V    |

| V_startup           | PFC startup voltage                               | VS  | 0.59        | V    |

| $V_{RefPFC}$        | PFC control_normal                                | VS  | 2.45        | V    |

| t_ZCDfilter         | PFC ZCD filter time                               | ZCD | 160         | ns   |

| t_ringsup           | PFC Ringing suppression time                      | ZCD | 400         | ns   |

| n_valley_min        | Minimum PFC valley number for multimode operation | -   | 1           | -    |

| n_valley_max        | Maximum PFC valley number for multimode operation | -   | 10          | -    |

| t_CcmpPFC           | PFC Blanking time for CCM protection              | -   | 60          | ms   |

| t_maxPFC            | PFC max switching periodtosc                      | -   | 40          | μs   |

| t_OcpLebPFC         | Blanking time for PFC OCP                         | CS0 | 0           | S    |

**Table 13** LLC Parameters

| Parameter Symbol Parameter Description |                                                                    | Pin  | Fixed Value | Unit                 |

|----------------------------------------|--------------------------------------------------------------------|------|-------------|----------------------|

| Step_LLC_VCO_decrease                  | LLC VCO frequency decrement step                                   | HBFB | 3           | 1/ f <sub>MCLK</sub> |

| Step_LLC_VCO_increase                  | LLC VCO frequency increment step                                   | HBFB | 20          | 1/ f <sub>MCLK</sub> |

| t_Ocp1_leb                             | LLC LEB of OCP1                                                    | CS1  | 0.4         | μs                   |

| t_Ocp2_filter                          | LLC noise blanking CS1 OCP2                                        | CS1  | 110         | ns                   |

| Slope_after OCP1                       | LLC softstart slope after OCP1 event                               | CS1  | 80          | ns/32µs              |

| $V_{\mathrm{burst\_on}}$               | LLC HRFR voltage burst on in burst                                 |      | 1.65        | V                    |

| t_Ocp1_blk_Leave_burst                 | LLC OCP1 blanking time during burst mode to normal mode transition |      |             | ms                   |

| t_ss_max                               | LLC max. soft start duration                                       | -    | 131         | ms                   |

### 3.8.2 Configurable Parameters

Table 14

The below parameters are defined and can be configured. General Parameters

| Parameter Symbol     | Parameter Description   | Pin | Default | Range     | Unit |

|----------------------|-------------------------|-----|---------|-----------|------|

| V_HVBID              | AC brownin              | HV  | 70      | 1 ~ 255   | Vac  |

| $V_{\text{\_HVBOD}}$ | AC brownout             | HV  | 60      | 1 ~ 255   | Vac  |

| t_AR                 | Auto restart break time | -   | 2       | 0.01~2.08 | S    |

Datasheet 27 Rev. V2.0, 2017-03-21

### Digital Multi-Mode PFC + LLC Combo Controller

| Parameter Symbol Parameter Description |                       | Pin | Default | Range | Unit |

|----------------------------------------|-----------------------|-----|---------|-------|------|

| t_vccovp                               | VCC OVP blanking time | -   | 9       | 1~17  | ms   |

**Table 15** PFC Parameters

| Parameter Symbol         | Parameter Description                   | Pin | Default | Range             | Unit     |  |

|--------------------------|-----------------------------------------|-----|---------|-------------------|----------|--|

| V_GD0H 1                 | PFC GD0 drive voltage                   | GD0 | 10.5    | 4.5 ~ 15          | V        |  |

| I_GD0H 1                 | PFC GD0 drive current                   | GD0 | 0.156   | $0.087 \sim 0.36$ | A        |  |

| $V_{\tt UvpSetPFC}$      | PFC bus under voltage                   | VS  | 1.77    | $0.1 \sim 2.3$    | V        |  |

| $V_{\tt RefPFC\_burst}$  | PFC control_burst                       | VS  | 2.2     | $0.1 \sim 2.3$    | V        |  |

| $V_{\mathtt{HBstrt}}$    | LLC enter soft start                    | VS  | 2.05    | $0.1 \sim 2.3$    | V        |  |

| t_UvpBlkPFC              | PFC blanking time for bus under         | VS  | 3       | 0.128 ~ 8388      | ms       |  |

|                          | voltage                                 |     |         |                   | <u> </u> |  |

| $t_{\mathtt{ovc}}$       | PFC over voltage comparator filter time | VS  | 10000   | 0 ~ 31500         | ns       |  |

| V_OvpSwSetPFC            | PFC bus over voltage                    | VS  | 2.572   | 2 ~ 2.8           | V        |  |

| V_OvpSwClearPFC          | PFC bus over voltage clear              | VS  | 2.45    | 2 ~ 2.8           | V        |  |

| V_CS0ocpSet <sup>2</sup> | PFC over current                        | CS0 | 0.6     | $0.05 \sim 1.15$  | V        |  |

| f_sw_max_pfc             | PFC max switching frequency             | -   | 120     | 1 ~ 300           | kHz      |  |

| f_sw_min_pfc             | PFC min switching frequency             | -   | 60      | 1 ~ 300           | kHz      |  |

| svp_startup              | PFC PIT1 P-coe during startup           | -   | 4       | 0 ~ 7             | -        |  |

| Svp                      | PFC PIT1 P-coe                          | -   | 6       | 0 ~ 7             | -        |  |

| Svi                      | PFC PIT1 I-coe                          | -   | 7       | 0 ~ 7             | -        |  |

| Svt                      | PFC PIT1 T-coe                          | -   | 4       | 0 ~ 7             | -        |  |

| t_OnMinPFC               | PFC min on time                         | -   | 0.1     | 0.016 ~ 63.98     | μs       |  |

| t_OnMaxPFC               | PFC max on time                         | -   | 20      | 0.016 ~ 63.98     | μs       |  |

<sup>&</sup>lt;sup>1</sup> Refer to 5.4.6 for limits

**Table 16** LLC Parameters

| Parameter Symbol  | Parameter Description                       | Pin  | Default | Range             | Unit |

|-------------------|---------------------------------------------|------|---------|-------------------|------|

| V_GD1H 1          | LLC GD1 drive voltage                       | GD1  | 10.5    | 4.5 ~ 15          | V    |

| I_GD1H 1          | LLC GD1 drive current                       | GD1  | 0.12    | $0.026 \sim 0.12$ | A    |

| V_0cp1_norm 1     | LLC OCP1 during steady state                | CS1  | 0.4275  | $0.05 \sim 1.15$  | V    |