## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **General Description**

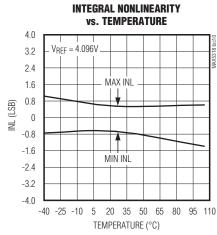

The MAX5318 is a high-accuracy, 18-bit, serial SPI input, buffered voltage output digital-to-analog converter (DAC) in a 4.4mm x 7.8mm, 24-lead TSSOP package. The device features ±2 LSB INL (max) accuracy and a ±1 LSB DNL (max) accuracy over the full temperature range

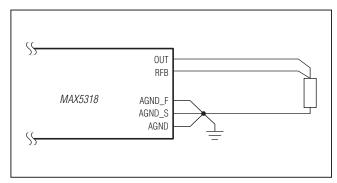

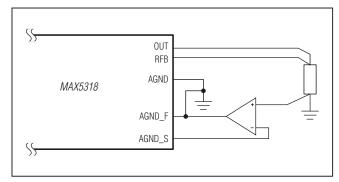

The DAC voltage output is buffered resulting in a fast settling time of  $3\mu s$  and a low offset and gain drift of  $\pm 0.5 ppm/^{\circ}C$  of FSR (typ). The force-sense output (OUT) maintains accuracy while driving loads with long lead lengths. Additionally, a separate AVSS supply, allows the output amplifier to go to 0V (GND) while maintaining full linearity performance.

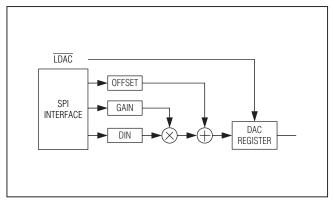

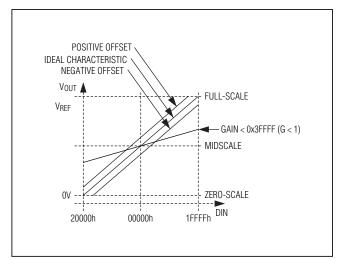

The MAX5318 includes user-programmable digital gain and offset correction to enable easy system calibration.

At power-up, the device resets its outputs to zero or midscale. The wide 2.7V to 5.5V supply voltage range and integrated low-drift, low-noise reference buffer amplifier make for ease of use.

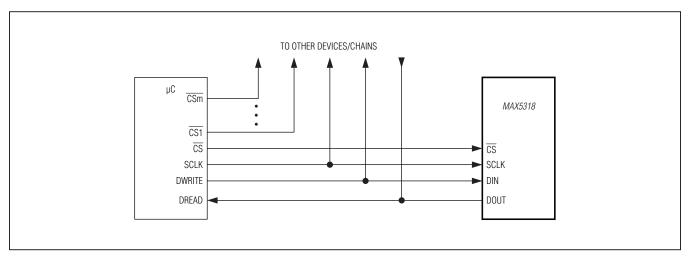

The MAX5318 features a 50MHz 3-wire SPI interface. The MAX5318 is available in a 24-lead TSSOP package and operates over the -40 $^{\circ}$ C to +105 $^{\circ}$ C temperature range.

#### **Benefits and Features**

- ♦ Ideal for ATE and High-Precision Instruments

- ♦ INL Accuracy Guaranteed with ±2 LSB (Max) Over Temperature

- ♦ Fast Settling Time (3µs) with 10kΩ || 100pF Load

- ♦ Safe Power-Up-Reset to Zero or Midscale DAC Output (Pin-Selectable)

- Predetermined Output Device State in Power-Up and Reset in System Design

- Negative Supply (AVSS) Option Allows Full INL and DNL Performance to 0V

- ♦ SPI Interface Compatible with 1.8V to 5.5V Logic

- High Integration Reduces Development Time and PCB Area

- Buffered Voltage Output Directly Drives

2kΩ Load Rail-to-Rail

- ♦ Integrated Reference Buffer

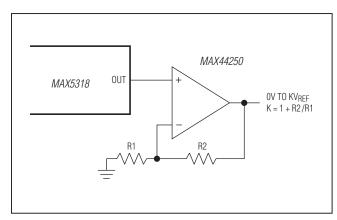

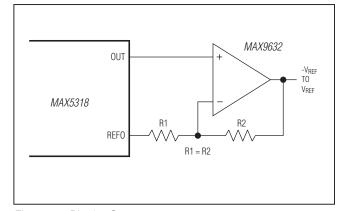

- ♦ No External Amplifiers Required

- ♦ Small 4.4mm x 7.8mm, 24-Pin TSSOP Package

<u>Ordering Information</u> and <u>Typical Operating Circuit</u> appear at end of data sheet.

#### **Applications**

Test and Measurement Equipment Automatic Test Equipment Gain and Offset Adjustment Data-Acquisition Systems Process Control and

Servo Loops

of -40°C to +105°C.

Programmable Voltage and Current Sources Automatic Tuning and Calibration Communication Systems Medical Imaging

For related parts and recommended products to use with this part, refer to <a href="www.maximintegrated.com/MAX5318.related">www.maximintegrated.com/MAX5318.related</a>.

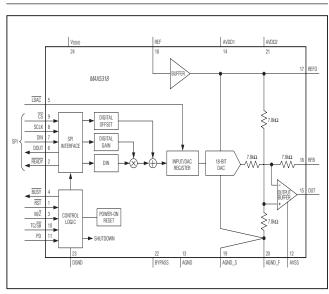

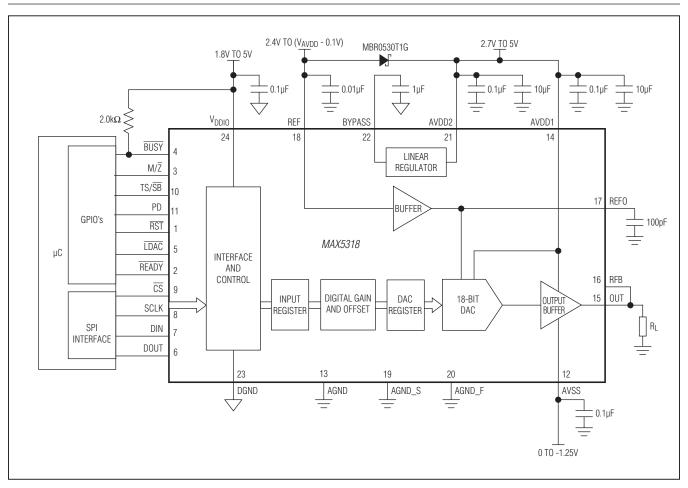

### **Functional Diagram**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ABSOLUTE MAXIMUM RATINGS**

| AGND to DGND0.3V to +0.3V                                   | REF to AGND0.3V to the lower of VAVDD and +6V                                                   |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| AGND_F, AGND_S to AGND0.3V to +0.3V                         | SCLK, DIN, CS, BUSY, LDAC, READY,                                                               |

| AGND_F, AGND_S to DGND0.3V to +0.3V                         | $M/\overline{Z}$ , $TC/\overline{SB}$ , $\overline{RST}$ , PD, DOUT to DGND0.3V to the lower of |

| AVDD to AGND0.3V to +6V                                     | $(V_{DDIO} + 0.3V)$ and +6V                                                                     |

| AVDD to REF0.3V to +6V                                      | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                           |

| AVSS to AGND2V to +0.3V                                     | TSSOP (derate 13.9mW/°C above +70°C)1111.1mW                                                    |

| V <sub>DDIO</sub> to DGND0.3V to +6V                        | Operating Temperature Range40°C to +105°C                                                       |

| BYPASS to DGND0.3V to the lower of                          | Maximum Junction Temperature+150°C                                                              |

| $(V_{AVDD} \text{ or } V_{DDIO} + 0.3V) \text{ and } +4.5V$ | Storage Temperature Range65°C to +150°C                                                         |

| OUT, REFO, RFB to AGND0.3V to the lower of                  | Lead Temperature (soldering, 10s)+300°C                                                         |

| $(V_{AVDD} + 0.3V)$ and +6V                                 | Soldering Temperature (reflow)+260°C                                                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

**TSSOP**

Junction-to-Case Thermal Resistance ( $\theta_{JA}$ ).......13°C/W Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......72°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{DDIO} = \textbf{4.5V to 5.5V}, \ V_{AVSS} = -1.25 V, \ V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0 V, \ V_{REF} = 4.096 V, \ TC/\overline{SB} = PD = \overline{LDAC} = M/\overline{Z} = DGND, \ \overline{RST} = V_{DDIO}, \ C_{REFO} = 100 pF, \ C_L = 100 pF, \ R_L = 10 k\Omega, \ C_{BYPASS} = 1 \mu F, \ T_A = -40 ^{\circ}C \ to +105 ^{\circ}C, \ unless otherwise noted. Typical values are at T_A = +25 ^{\circ}C.) (GAIN = 0x3FFFF and OFFSET = 0x00000.) (Note 2)$

| PARAMETER                                      | SYMBOL | CONDITIONS                                                                                                       | MIN  | TYP    | MAX                     | UNITS            |

|------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|------|--------|-------------------------|------------------|

| STATIC PERFORMANCE                             |        |                                                                                                                  |      |        |                         |                  |

| Resolution                                     | N      |                                                                                                                  | 18   |        |                         | Bits             |

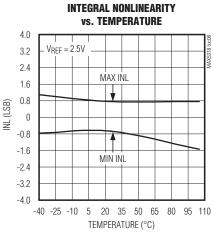

| Integral Nonlinearity (Note 3)                 | INII   | DIN = 0x00000 to 0x3FFFF<br>(binary mode), DIN = 0x20000 to 0x1FFFF<br>(two's complement mode)                   | -2   | . 0. 5 | . 0                     | . 00             |

|                                                | INL    | DIN = 0x01900 to 0x3FFFF (binary mode), DIN = 0x21900 to 0x1FFFF (two's complement mode), V <sub>AVSS</sub> = 0V | -2   | ±0.5   | +2                      | LSB              |

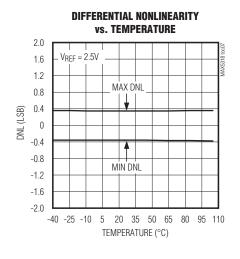

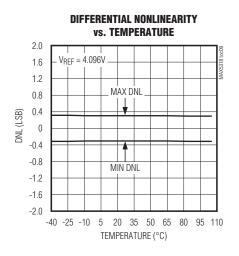

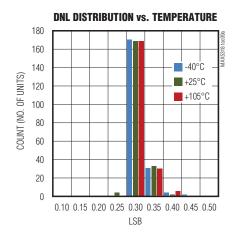

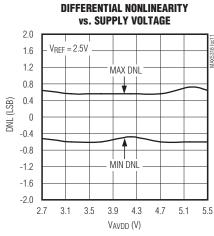

| Differential Nonlinearity (Note 3)             | DNL    |                                                                                                                  | -1   | ±0.275 | +1                      | LSB              |

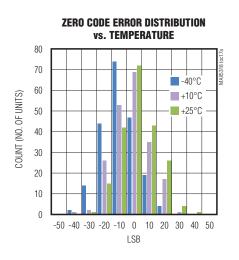

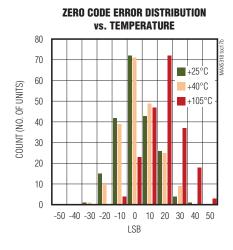

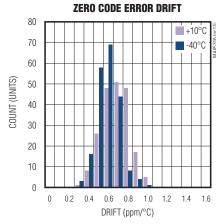

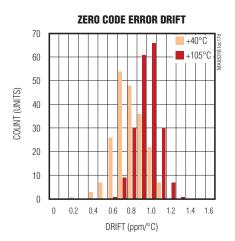

| Zero Code Error                                | OE     | DIN = 0, $T_A = +25^{\circ}C$                                                                                    | -48  | ±4     | +48                     | LSB              |

| Zero Gode Error                                |        | DIN = 0, $T_A = -40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$                                                   |      | ±14    |                         | LOD              |

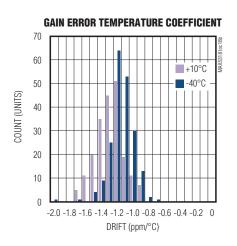

| Zero Code Error Drift (Note 4)                 |        | DIN = 0                                                                                                          | -1.6 | ±0.10  | +1.6                    | ppm/°C           |

| Gain Error                                     | GE     | $T_A = +25^{\circ}C$                                                                                             | -16  | ±1     | +16                     | LSB              |

| Gain Endi                                      | GE     | $T_A = -40^{\circ}\text{C to } + 105^{\circ}\text{C}$                                                            |      | ±27    |                         | LOD              |

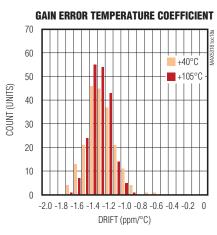

| Gain Error Temperature<br>Coefficient (Note 4) | TCGE   |                                                                                                                  | -2.5 | ±0.10  | +2.5                    | ppm/°C<br>of FSR |

| Output Voltage Range                           |        | No load                                                                                                          | 0    |        | V <sub>AVDD</sub> - 0.1 | V                |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DDIO} = \textbf{4.5V to 5.5V}, \ V_{AVSS} = -1.25V, \ V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V, \ V_{REF} = 4.096V, \ TC/\overline{SB} = PD = \overline{LDAC} = M/\overline{Z} = DGND, \ \overline{RST} = V_{DDIO}, \ C_{REFO} = 100pF, \ C_L = 100pF, \ R_L = 10k\Omega, \ C_{BYPASS} = 1\mu F, \ T_A = -40^{\circ}C \ to +105^{\circ}C, \ unless otherwise noted. \ Typical values are at T_A = +25^{\circ}C.) \ (GAIN = 0x3FFFF \ and OFFSET = 0x00000.) \ (Note 2)$

| PARAMETER                                | SYMBOL                 | CONE                                         | OITIONS                     | MIN   | TYP        | MAX                     | UNITS      |

|------------------------------------------|------------------------|----------------------------------------------|-----------------------------|-------|------------|-------------------------|------------|

|                                          |                        | DOT                                          | $M/\overline{Z} = DGND$     |       | 75         |                         | μV         |

|                                          |                        | RST = pulse low                              | $M/\overline{Z} = V_{DDIO}$ |       | 2.048      |                         | V          |

|                                          |                        | $\overline{RST} = pulse \; low,$             | $M/\overline{Z} = DGND$     |       | 10         |                         | mV         |

| Reset Voltage Output                     | V <sub>OUT-RESET</sub> | $V_{AVSS} = 0V$ $M/\overline{Z} = V_{DDIO}$  |                             | 2.048 |            | V                       |            |

| Theodi Vellage Galpat                    | *OUT-RESET             | RST = DGND                                   | $M/\overline{Z} = DGND$     |       | -68        |                         | mV         |

|                                          |                        |                                              | $M/\overline{Z} = V_{DDIO}$ |       | 2.036      |                         | V          |

|                                          |                        | $\overline{RST} = DGND,$                     | $M/\overline{Z} = DGND$     |       | 10         |                         | mV         |

|                                          |                        | V <sub>AVSS</sub> = 0V                       | $M/\overline{Z} = V_{DDIO}$ |       | 2.036      |                         | V          |

| DC Output Impedance (Normal Mode)        | R <sub>OUT</sub>       | Closed-loop connec<br>to OUT)                | tion (RFB connected         |       | 4          |                         | mΩ         |

| Output Resistance (Power-Down Mode)      |                        | PD = V <sub>DDIO</sub>                       |                             |       | 2          |                         | kΩ         |

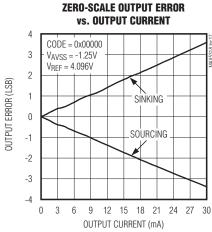

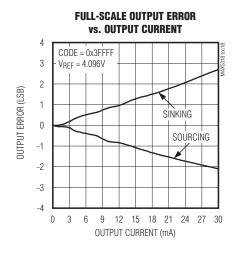

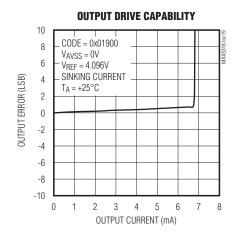

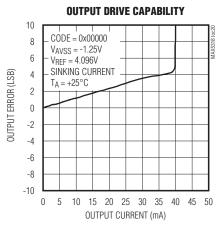

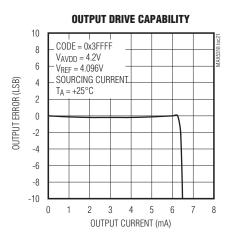

| Output Current                           | la=                    | Source/sink within 10 rails                  | 00mV of the supply          |       | ±4         |                         | mA         |

| Output Gurrent                           | lout                   | Source/sink within 800mV of the supply rails |                             |       | ±25        |                         | ША         |

| Load Capacitance to GND                  | CL                     |                                              |                             |       |            | 200                     | рF         |

| Load Resistance to GND                   | R <sub>L</sub>         | For specified perforr                        | nance                       | 2     |            |                         | kΩ         |

|                                          |                        | OUT shorted to AGN                           | ID or AVDD                  |       | ±60        |                         |            |

| Short-Circuit Current                    | I <sub>SC</sub>        | REFO shorted to AG                           | ±65                         |       |            | mA                      |            |

|                                          |                        | BYPASS shorted to AGND or AVDD               |                             | ±48   |            |                         |            |

| Short-Circuit Duration                   | T <sub>SC</sub>        | Short to AGND or A\                          | /DD                         |       | Indefinite |                         | S          |

| DC Power-Supply Rejection                | DC PSRR                | V <sub>OUT</sub> at full scale, V,           | AVDD = 4.5V to 5.5V         | -2.5  | ±0.20      | +2.5                    | LSB/V      |

| Do i ower-supply riejection              | DOTOIN                 | $V_{AVSS} = -1.5V \text{ to } -0.8$          | 5V                          | -2.5  | ±0.012     | +2.5                    | LOD/ V     |

| STATIC PERFORMANCE—VOLT                  | AGE REFER              | ENCE INPUT SECTION                           | DN                          |       |            |                         |            |

| Reference High Input Range               | V <sub>REF</sub>       |                                              |                             | 2.4   |            | V <sub>AVDD</sub> - 0.1 | V          |

| Reference Input Capacitance              | C <sub>REF</sub>       |                                              |                             |       | 10         |                         | рF         |

| Reference Input Resistance               | R <sub>REF</sub>       |                                              |                             |       | 10         |                         | $M\Omega$  |

| Reference Input Current                  | I <sub>B</sub>         |                                              |                             |       | ±0.15      |                         | μΑ         |

| STATIC PERFORMANCE—VOLT                  | AGE REFER              | ENCE OUTPUT SEC                              | TION                        |       |            |                         |            |

| Reference High Output Range              |                        |                                              |                             | 2.4   |            | V <sub>AVDD</sub> - 0.1 | V          |

| Reference High Output Load<br>Regulation |                        |                                              |                             |       | 500        |                         | ppm/<br>mA |

| Reference Output Capacitor               |                        | $R_{\rm ESR} < 5\Omega$                      |                             |       | 0.1        |                         | nF         |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DDIO} = \textbf{4.5V to 5.5V}, \ V_{AVSS} = -1.25V, \ V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V, \ V_{REF} = 4.096V, \ TC/\overline{SB} = PD = \overline{LDAC} = M/\overline{Z} = DGND, \ \overline{RST} = V_{DDIO}, \ C_{REFO} = 100pF, \ C_L = 100pF, \ R_L = 10k\Omega, \ C_{BYPASS} = 1\mu F, \ T_A = -40^{\circ}C \ to +105^{\circ}C, \ unless otherwise noted. \ Typical values are at T_A = +25^{\circ}C.) \ (GAIN = 0x3FFFF \ and OFFSET = 0x00000.) \ (Note 2)$

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                                                                          | MIN  | TYP   | MAX               | UNITS             |

|----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|-------------------|-------------------|

| STATIC PERFORMANCE—VBYP                            | ASS OUT SE          | CTION                                                                                                               |      |       |                   |                   |

| Output Voltage                                     | V <sub>BYPASS</sub> |                                                                                                                     | 2.3  | 2.4   | 2.5               | V                 |

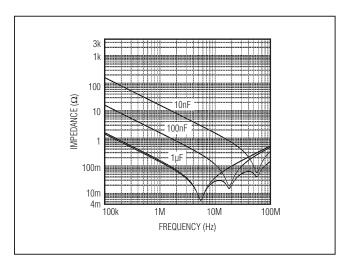

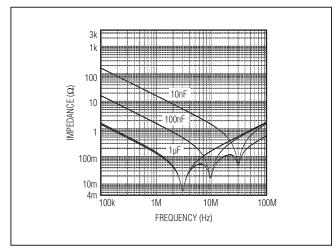

| Load Capacitance to GND                            | CL                  | Required for stability, $R_{ESR} = 0.1\Omega$ (typ)                                                                 | 1    |       | 8                 | μF                |

| POWER-SUPPLY REQUIREMEN                            | TS                  |                                                                                                                     |      |       |                   |                   |

| Positive Analog Power-Supply Range                 | V <sub>AVDD</sub>   |                                                                                                                     | 4.5  |       | 5.5               | V                 |

| Digital Interface Power-Supply Range               | V <sub>DDIO</sub>   |                                                                                                                     | 1.8  |       | V <sub>AVDD</sub> | V                 |

| Negative Analog Power-Supply<br>Range              | V <sub>AVSS</sub>   |                                                                                                                     | -1.5 | -1.25 | 0                 | V                 |

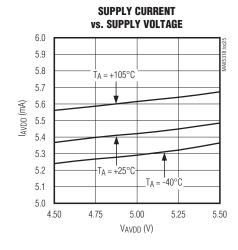

| Positive Analog Power-Supply<br>Current            | I <sub>AVDD</sub>   | No load, external reference, output at zero scale                                                                   |      | 5.2   | 6.5               | mA                |

| Negative Analog Power-Supply<br>Current            | I <sub>AVSS</sub>   | No load, external reference, output at zero scale                                                                   | -1.5 | -1.0  |                   | mA                |

| Interface Power-Supply Current                     | I <sub>VDDIO</sub>  | Digital inputs at V <sub>DDIO</sub> or DGND                                                                         |      | 0.2   | 5.0               | μΑ                |

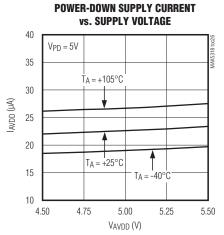

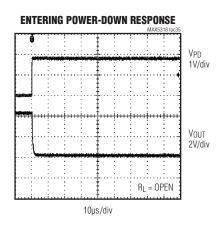

| Positive Analog Power-Supply Power-Down Current    |                     | PD = V <sub>DDIO</sub> , power-down mode                                                                            |      | 20    | 50                | μΑ                |

| Negative Analog Power-Supply<br>Power-Down Current |                     | PD = V <sub>DDIO</sub> , power-down mode                                                                            | -5   | -3    |                   | μΑ                |

| DYNAMIC PERFORMANCE                                |                     |                                                                                                                     |      |       |                   |                   |

| Voltage Output Slew Rate                           | SR                  | From 10% to 90% full scale, positive and negative transitions                                                       |      | 4.9   |                   | V/µs              |

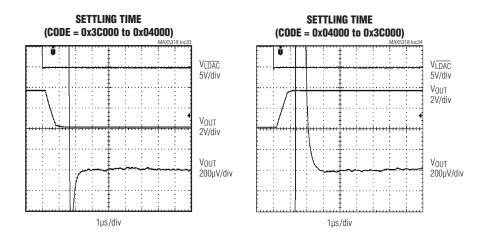

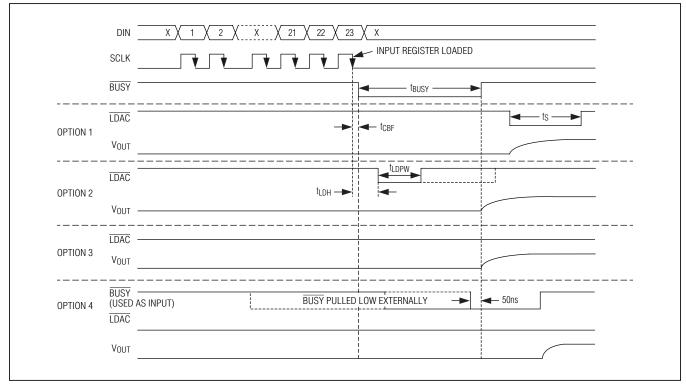

| Voltage Output Settling Time                       | t <sub>S</sub>      | From falling edge of LDAC to within 0.003% FS, $R_L$ = 10k $\Omega$ , DIN = 04000h (6.25% FS) to 3C000h (93.75% FS) |      | 3     |                   | μs                |

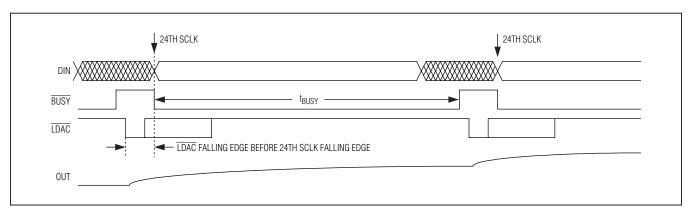

| Busy Time                                          | t <sub>BUSY</sub>   | (Note 5)                                                                                                            |      | 1.9   |                   | μs                |

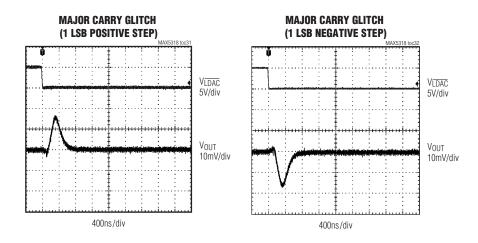

| DAC Glitch Impulse                                 |                     | Major code transition (1FFFFh to 20000h), $R_L = 10k\Omega$ , $C_L = 50pF$                                          |      | 4     |                   | nVs               |

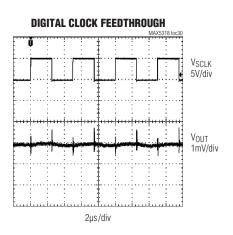

| Digital Feed Through                               |                     | CSB = V <sub>DDIO</sub> , f <sub>SCLK</sub> = 1kHz, all digital inputs from 0V to V <sub>DDIO</sub>                 |      | 1     |                   | nVs               |

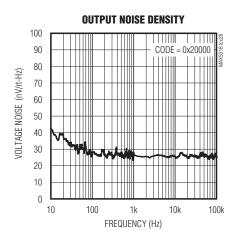

| Output Voltage-Noise Spectral<br>Density           |                     | At f = 1kHz to 10kHz, without reference, code = 20000h                                                              |      | 26    |                   | nV/√Hz            |

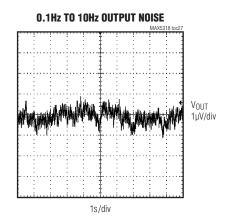

| Output Voltage Noise                               |                     | At f = 0.1Hz to 10Hz, without reference, code = 20000h                                                              |      | 1.55  |                   | μV <sub>P-P</sub> |

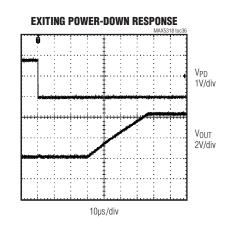

| Wake-Up Time                                       |                     | From power-down mode                                                                                                |      | 75    |                   | μs                |

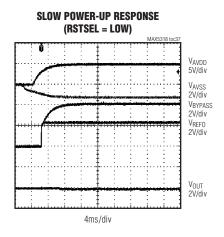

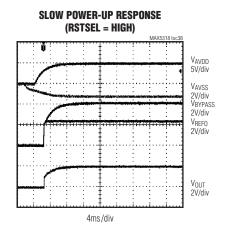

| Power-Up Time                                      |                     | From power-off                                                                                                      |      | 2     |                   | ms                |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ELECTRICAL CHARACTERISTICS**

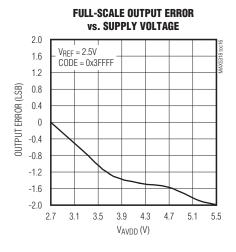

$(V_{AVDD} = V_{DDIO} = \textbf{2.7V to 3.3V}, V_{AVSS} = -1.25 \text{V}, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0 \text{V}, V_{REF} = 2.5 \text{V}, \text{TC}/\overline{SB} = \text{PD} = \overline{\text{LDAC}} = M/\overline{Z} = DGND, \overline{RST} = V_{DDIO}, C_{REFO} = 100 \text{pF}, C_L = 100 \text{pF}, R_L = 10 \text{k}\Omega, C_{BYPASS} = 1 \text{µF}, GAIN = 0x3FFFF}, OFFSET = 0x00000, T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C}.) \text{ (GAIN = 0x3FFFF and OFFSET = 0x00000.)} \text{(Note 2)}$

| PARAMETER                                      | SYMBOL                 | CON                                                          | DITIONS                     | MIN             | TYP                         | MAX                     | UNITS            |  |   |

|------------------------------------------------|------------------------|--------------------------------------------------------------|-----------------------------|-----------------|-----------------------------|-------------------------|------------------|--|---|

| STATIC PERFORMANCE                             |                        |                                                              |                             |                 |                             |                         |                  |  |   |

| Resolution                                     | N                      |                                                              |                             | 18              |                             |                         | Bits             |  |   |

| Integral Marlingarity (Nata 2)                 | INII                   | DIN = 0x00000 to 0<br>mode), DIN = 0x200<br>complement mode) | 000 to 0x1FFFF (two's       | 0.0             | . 0. 75                     | .00                     | LCD              |  |   |

| Integral Nonlinearity (Note 3)                 | INL                    | DIN = 0x01900 to 0<br>mode), DIN = 0x219<br>complement mode) | 900 to 0x1FFFF (two's       | -2.0            | ±0.75                       | +2.0                    | LSB              |  |   |

| Differential Nonlinearity (Note 3)             | DNL                    |                                                              |                             | -1.0            | ±0.3                        | +1.0                    | LSB              |  |   |

| 7 0 1 5                                        | 0.5                    | DIN = 0, $T_A = +25^\circ$                                   | C                           | -50             | ±6                          | +50                     | 1.00             |  |   |

| Zero Code Error                                | OE                     | DIN = 0, $T_A = -40^{\circ}C$                                | C to +105°C                 |                 | ±25                         |                         | LSB              |  |   |

| Zero Code Error Drift (Note 4)                 |                        | DIN = 0                                                      |                             | -2.7            | ±1.4                        | +2.7                    | ppm/°C           |  |   |

| Onlin France                                   | 0.5                    | $T_A = +25^{\circ}C$                                         |                             | -16             | ±1.5                        | +16                     | 1.00             |  |   |

| Gain Error                                     | GE                     | $T_A = -40^{\circ}\text{C to} + 105^{\circ}$                 | °C                          |                 | ±35                         |                         | LSB              |  |   |

| Gain Error Temperature<br>Coefficient (Note 4) | TCGE                   |                                                              |                             | -3.2            |                             | +3.2                    | ppm/°C<br>of FSR |  |   |

| Output Voltage Range                           |                        | No load                                                      |                             | 0               |                             | V <sub>AVDD</sub> - 0.1 | V                |  |   |

|                                                |                        | $M/\overline{Z} = DGN$                                       | $M/\overline{Z} = DGND$     |                 | 75                          |                         | μV               |  |   |

|                                                |                        |                                                              |                             | RST = pulse low | $M/\overline{Z} = V_{DDIO}$ |                         | 1.25             |  | V |

|                                                |                        | RST = pulse low,                                             | $M/\overline{Z} = DGND$     |                 | 10                          |                         | mV               |  |   |

| Reset Voltage Output                           | \/ o = = = = = =       | $V_{AVSS} = 0V$                                              | $M/\overline{Z} = V_{DDIO}$ |                 | 1.25                        |                         | V                |  |   |

| Theset Voltage Output                          | V <sub>OUT-RESET</sub> | DOT DONE                                                     | $M/\overline{Z} = DGND$     |                 | -40                         |                         | mV               |  |   |

|                                                |                        | RST = DGND                                                   | $M/\overline{Z} = V_{DDIO}$ |                 | 1.25                        |                         | V                |  |   |

|                                                |                        | RST = DGND,                                                  | $M/\overline{Z} = DGND$     |                 | 10                          |                         | mV               |  |   |

|                                                |                        | $V_{AVSS} = 0V$                                              | $M/\overline{Z} = V_{DDIO}$ |                 | 1.24                        |                         | V                |  |   |

| DC Output Impedance                            | R <sub>OUT</sub>       | Closed-loop connecto OUT                                     | ction, RFB connected        |                 | 4                           |                         | mΩ               |  |   |

| Output Current                                 | la                     | Source/sink within 10                                        | 00mV of the supply rails    |                 | ±4                          |                         | m A              |  |   |

| Output Guirent                                 | lout                   | Source/sink within 80                                        | 00mV of the supply rails    |                 | ±25                         |                         | mA               |  |   |

| Load Capacitance to GND                        | CL                     |                                                              |                             |                 |                             | 200                     | pF               |  |   |

| Load Resistance to GND                         | RL                     | For specified perfor                                         | mance                       | 2               |                             |                         | kΩ               |  |   |

|                                                |                        | OUT shorted to AGND or AVDD                                  |                             |                 | ±60                         |                         |                  |  |   |

| Short-Circuit Current                          | I <sub>SC</sub>        | REFO shorted to AGND or AVDD                                 |                             |                 | ±65                         |                         | mA               |  |   |

|                                                |                        | BYPASS shorted to                                            |                             |                 | ±48                         |                         |                  |  |   |

| Short-Circuit Duration                         | t <sub>SC</sub>        | Short to AGND or A                                           |                             | Indefinite      |                             | S                       |                  |  |   |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DDIO} = \textbf{2.7V to 3.3V}, V_{AVSS} = -1.25V, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V, V_{REF} = 2.5V, TC/\overline{SB} = PD = \overline{LDAC} = M/\overline{Z} = DGND, \overline{RST} = V_{DDIO}, C_{REFO} = 100pF, C_L = 100pF, R_L = 10k\Omega, C_{BYPASS} = 1\mu F, GAIN = 0x3FFFF, OFFSET = 0x00000, T_A = -40°C to +105°C, unless otherwise noted. Typical values are at <math>T_A = +25°C$ .) (GAIN = 0x3FFFF and OFFSET = 0x00000.)(Note 2)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                                                                          | MIN  | TYP   | MAX                     | UNITS  |

|----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------|--------|

| DO Davia Comarko Dala ati                          | DODODO              | V <sub>OUT</sub> at full scale, V <sub>AVDD</sub> = 2.7V to 3.3V                                                    | -2.5 | ±0.4  | +2.5                    | L CDA/ |

| DC Power-Supply Rejection                          | DCPSRR              | $V_{AVSS} = -1.5V \text{ to } -0.5V$                                                                                | -2.5 | ±0.04 | +2.5                    | LSB/V  |

| STATIC PERFORMANCE—VOLT                            | AGE REFER           | RENCE INPUT SECTION                                                                                                 |      |       |                         |        |

| Reference High Input Range                         | V <sub>REF</sub>    |                                                                                                                     | 2.4  |       | V <sub>AVDD</sub> - 0.1 | V      |

| Reference Input Capacitance                        | C <sub>REF</sub>    |                                                                                                                     |      | 10    |                         | pF     |

| Reference Input Resistance                         | R <sub>REF</sub>    |                                                                                                                     |      | 10    |                         | ΜΩ     |

| Reference Input Current                            | IB                  |                                                                                                                     |      | ±0.15 |                         | μΑ     |

| STATIC PERFORMANCE—VOLT                            | AGE REFER           | RENCE OUTPUT SECTION                                                                                                |      |       |                         | r      |

| Reference High Output Range                        |                     |                                                                                                                     | 2.4  |       | V <sub>AVDD</sub> - 0.1 | V      |

| Reference High Output Load<br>Regulation           |                     |                                                                                                                     |      | 500   |                         | ppm/mA |

| Reference Output Capacitor                         |                     | $R_{\rm ESR} < 5\Omega$                                                                                             |      | 0.1   |                         | nF     |

| STATIC PERFORMANCE—VBYP                            | ASS OUT SE          | CTION                                                                                                               |      |       |                         |        |

| Output Voltage                                     | V <sub>BYPASS</sub> |                                                                                                                     | 2.3  | 2.4   | 2.5                     | V      |

| Load Capacitance to GND                            | CL                  | Required for stability, $R_{ESR} = 0.1\Omega$ (typ)                                                                 | 1    |       | 8                       | μF     |

| POWER-SUPPLY REQUIREMEN                            | TS                  |                                                                                                                     |      |       |                         |        |

| Positive Analog Power-Supply Range                 | V <sub>AVDD</sub>   |                                                                                                                     | 2.7  |       | 3.3                     | V      |

| Interface Power-Supply Range                       | V <sub>DDIO</sub>   |                                                                                                                     | 1.8  |       | 5.5                     | V      |

| Negative Analog Power-Supply<br>Range              | V <sub>AVSS</sub>   |                                                                                                                     | -1.5 | -1.25 | 0                       | ٧      |

| Positive Analog Power-Supply<br>Current            | I <sub>AVDD</sub>   | No load, external reference, output at zero scale                                                                   |      | 5.0   | 6.5                     | mA     |

| Negative Analog Power-Supply<br>Current            | I <sub>AVSS</sub>   | No load, external reference, output at zero scale                                                                   | -1.5 | -0.8  |                         | mA     |

| Interface Power-Supply Current                     | I <sub>VDDIO</sub>  | Digital inputs at V <sub>DDIO</sub> or DGND                                                                         |      | 0.2   | 5.0                     | μΑ     |

| Positive Analog Power-Supply<br>Power-Down Current |                     | PD = V <sub>DDIO</sub> , power-down mode                                                                            |      | 20    | 50                      | μΑ     |

| Negative Analog Power-Supply<br>Power-Down Current |                     | PD = V <sub>DDIO</sub> , power-down mode                                                                            | -5   | -2    |                         | μΑ     |

| DYNAMIC PERFORMANCE                                | 1                   |                                                                                                                     |      |       |                         |        |

| Voltage Output Slew Rate                           | SR                  | From 10% to 90% full scale, positive and negative transitions                                                       |      | 4.9   |                         | V/µs   |

| Voltage Output Settling Time                       | ts                  | From falling edge of LDAC to within 0.003% FS, $R_L$ = 10k $\Omega$ , DIN = 04000h (6.25% FS) to 3C000h (93.75% FS) |      | 3     |                         | μs     |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DDIO} = \textbf{2.7V to 3.3V}, V_{AVSS} = -1.25V, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V, V_{REF} = 2.5V, TC/\overline{SB} = PD = \overline{LDAC} = M/\overline{Z} = DGND, \overline{RST} = V_{DDIO}, C_{REFO} = 100pF, C_L = 100pF, R_L = 10k\Omega, C_{BYPASS} = 1\mu F, GAIN = 0x3FFFF, OFFSET = 0x00000, T_A = -40°C to +105°C, unless otherwise noted. Typical values are at <math>T_A = +25°C$ .) (GAIN = 0x3FFFF and OFFSET = 0x00000.)(Note 2)

| PARAMETER                             | SYMBOL            | CONDITIONS                                                                                          | MIN | TYP  | MAX | UNITS             |

|---------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| Busy Time                             | t <sub>BUSY</sub> | (Note 5)                                                                                            |     | 1.9  |     | μs                |

| DAC Glitch Impulse                    |                   | Major code transition (1FFFFh to 20000h),<br>R <sub>L</sub> = $10k\Omega$ , C <sub>L</sub> = $50pF$ |     | 2.5  |     | nVs               |

| Digital Feedthrough                   |                   | CSB = V <sub>DDIO</sub> , f <sub>SCLK</sub> = 1kHz, all digital inputs from 0V to V <sub>DDIO</sub> |     | 1    |     | nVs               |

| Output Voltage-Noise Spectral Density |                   | At f = 1kHz to 10kHz, without reference, code = 20000h                                              |     | 26   |     | nV/√Hz            |

| Output Voltage Noise                  |                   | At f = 0.1Hz to 10Hz, without reference, code = 20000h                                              |     | 1.55 |     | μV <sub>P-P</sub> |

| Wake-Up Time                          |                   | From power-down mode                                                                                |     | 75   |     | μs                |

| Power-Up Time                         |                   | From power-off                                                                                      |     | 2    |     | ms                |

#### DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS

$(V_{AVDD} = 5V, V_{DDIO} = \textbf{2.7V} \text{ to 5.5V}, V_{AVSS} = -1.25V, V_{REF} = 4.096V, R_L = 10k\Omega, TC/\overline{SB} = M/\overline{Z} = DGND, C_{REFO} = 100pF, C_{BYPASS} = 1\mu F, T_A = -40^{\circ}C$  to +105°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)(GAIN = 0x3FFFF and OFFSET = 0x000000.) (Note 2)

| (Note 2)                       |                    |                                            |                             |      |                    |       |

|--------------------------------|--------------------|--------------------------------------------|-----------------------------|------|--------------------|-------|

| PARAMETER                      | SYMBOL             | CONDITIONS                                 | MIN                         | TYP  | MAX                | UNITS |

| DIGITAL INPUTS (SCLK, DIN, CS  | S, LDAC, M/Z       | , RST)                                     |                             |      |                    |       |

| Input High Voltage             | V <sub>IH</sub>    |                                            | 0.7 x<br>V <sub>DDIO</sub>  |      |                    | V     |

| Input Low Voltage              | V <sub>IL</sub>    |                                            |                             |      | $0.3 x$ $V_{DDIO}$ | V     |

| Input Hysteresis (Note 4)      | V <sub>IHYST</sub> |                                            | 200                         | 300  |                    | mV    |

| Input Leakage Current          | I <sub>IN</sub>    |                                            |                             | ±0.1 | ±1                 | μΑ    |

| Input Capacitance              | C <sub>IN</sub>    |                                            |                             | 10   |                    | рF    |

| DIGITAL OUTPUT CHARACTERI      | ISTICS (DOU        | T, READY, BUSY)                            |                             |      |                    |       |

| Output Low Voltage             | V <sub>OL</sub>    | I <sub>SOURCE</sub> = 5.0mA                |                             |      | 0.25               | V     |

| Output High Voltage            | V <sub>OH</sub>    | I <sub>SINK</sub> = 5.0mA, except for BUSY | V <sub>DDIO</sub><br>- 0.25 |      |                    | V     |

| Output Three-State Leakage     | loz                | DOUT only                                  |                             | ±0.1 | ±1                 | μΑ    |

| Output Three-State Capacitance | C <sub>OZ</sub>    | DOUT only                                  |                             | 15   |                    | рF    |

| Output Short-Circuit Current   | loss               | V <sub>DDIO</sub> = 5.25V                  |                             | ±150 |                    | mA    |

# 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

### **DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 5V, V_{DDIO} = \textbf{2.7V to 5.5V}, V_{AVSS} = -1.25V, V_{REF} = 4.096V, R_L = 10k\Omega, TC/\overline{SB} = M/\overline{Z} = DGND, C_{REFO} = 100pF, C_{BYPASS} = 1\mu F, T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)(GAIN = 0x3FFFF and OFFSET = 0x00000.) (Note 2)

| PARAMETER                       | SYMBOL             |                                     | MIN                                                                    | TYP | MAX | UNITS |     |

|---------------------------------|--------------------|-------------------------------------|------------------------------------------------------------------------|-----|-----|-------|-----|

| TIMING CHARACTERISTICS          |                    |                                     |                                                                        |     |     |       |     |

|                                 |                    | Stand-alone, v                      | write mode                                                             |     |     | 50    |     |

| Serial Clock Frequency          | f <sub>SCLK</sub>  |                                     | Stand-alone, read mode and daisy-chained read and write modes (Note 5) |     |     | 12.5  | MHz |

|                                 |                    | Stand-alone, v                      | write mode                                                             | 20  |     |       |     |

| SCLK Period                     | t <sub>CP</sub>    |                                     | ead mode and daisy-<br>and write modes                                 | 80  |     |       | ns  |

| SCLK Pulse Width High           | t <sub>CH</sub>    | 40% duty cycl                       | le                                                                     | 8   |     |       | ns  |

| SCLK Pulse Width Low            | t <sub>CL</sub>    | 40% duty cycl                       | le                                                                     | 8   |     |       | ns  |

|                                 |                    |                                     | Stand-alone, write mode                                                | 8   |     |       |     |

| CS Fall to SCLK Fall Setup Time | t <sub>CSSO</sub>  | First SCLK falling edge             | Stand-alone, read mode and daisy-chained read and write modes          | 38  |     |       | ns  |

| CS Fall to SCLK Fall Hold Time  | t <sub>CSH0</sub>  | Inactive falling edge               | g edge preceding first falling                                         | 0   |     |       | ns  |

| SCLK Fall to CS Rise Hold Time  | t <sub>CSH1</sub>  | 24th falling ed                     | lge                                                                    | 2   |     |       | ns  |

| DIN to SCLK Fall Setup Time     | t <sub>DS</sub>    |                                     |                                                                        | 5   |     |       | ns  |

| DIN to SCLK Fall Hold Time      | t <sub>DH</sub>    |                                     |                                                                        | 4.5 |     |       | ns  |

| SCLK Rise to DOUT Settle Time   | t <sub>DOT</sub>   | $C_L = 20pF (No$                    | ote 6)                                                                 |     |     | 32    | ns  |

| SCLK Rise to DOUT Hold Time     | t <sub>DOH</sub>   | $C_L = 0pF (Not)$                   | te 6)                                                                  | 2   |     |       | ns  |

| SCLK Fall to DOUT Disable Time  | t <sub>DOZ</sub>   | 24th active ed                      | lge deassertion                                                        | 2   |     | 30    | ns  |

| CS Fall to DOUT Enable          | t <sub>DOE</sub>   | Asynchronous                        | assertion                                                              | 2   |     | 30    | ns  |

| CS Rise to DOUT Disable         | t <sub>CSDOZ</sub> | Stand-alone, a                      | aborted sequence                                                       |     |     | 35    | ns  |

|                                 | CSDOZ              | Daisy-chained, aborted sequence     |                                                                        |     |     | 70    | 110 |

| SCLK Fall to READY Fall         | tCRF               |                                     | lge assertion, C <sub>L</sub> = 20pF                                   |     |     | 30    | ns  |

| SCLK Fall to READY Hold         | t <sub>CRH</sub>   |                                     | lge assertion, C <sub>L</sub> = 0pF                                    | 2   |     |       | ns  |

| SCLK Fall to BUSY Fall          | t <sub>CBF</sub>   | BUSY assertion                      | on                                                                     |     | 5   |       | ns  |

| CS Rise to READY Rise           | t <sub>CSR</sub>   | $C_L = 20pF$                        |                                                                        |     |     | 35    | ns  |

| CS Rise to SCLK Fall            | t <sub>CSA</sub>   | 24th falling edge, aborted sequence |                                                                        | 20  |     |       | ns  |

| CS Pulse Width High             | t <sub>CSPW</sub>  | Stand alone                         |                                                                        | 20  |     | _     | ns  |

| SCLK Fall to CS Fall            | t <sub>CSF</sub>   | 24th falling edge                   |                                                                        | 100 |     |       | ns  |

| LDAC Pulse Width                | t <sub>LDPW</sub>  |                                     |                                                                        | 20  |     |       | ns  |

| LDAC Fall to SCLK Fall Hold     | t <sub>LDH</sub>   | Last active fal                     | 20                                                                     |     |     | ns    |     |

| RST Pulse Width                 | t <sub>RSTPW</sub> |                                     | 20                                                                     |     |     | ns    |     |

# 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = 5V, V_{DDIO} =$  **1.8V to 2.7V**,  $V_{AVSS} = -1.25V$ ,  $V_{REF} = 4.096V$ ,  $R_L = 10k\Omega$ ,  $TC/\overline{SB} = M/\overline{Z} = DGND$ ,  $C_{REFO} = 100pF$ ,  $C_{BYPASS} = 1\mu F$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)(GAIN = 0x3FFFF and OFFSET = 0x000000.) (Note 2)

| PARAMETER                       | SYMBOL             | CONDITIONS                                         |                                                                           | MIN                        | TYP  | MAX                        | UNITS |

|---------------------------------|--------------------|----------------------------------------------------|---------------------------------------------------------------------------|----------------------------|------|----------------------------|-------|

| DIGITAL INPUTS (SCLK, DIN, CS   | S, LDAC, M/Z       | , RST)                                             |                                                                           |                            |      |                            |       |

| Input High Voltage              | V <sub>IH</sub>    |                                                    |                                                                           | 0.8 x<br>V <sub>DDIO</sub> |      |                            | V     |

| Input Low Voltage               | V <sub>IL</sub>    |                                                    |                                                                           |                            |      | 0.2 x<br>V <sub>DDIO</sub> | V     |

| Input Hysteresis (Note 4)       | V <sub>IHYST</sub> |                                                    |                                                                           | 200                        | 300  |                            | mV    |

| Input Leakage Current           | I <sub>IN</sub>    | Input = 0V at                                      | V <sub>DDIO</sub>                                                         |                            | ±0.1 | ±1                         | μΑ    |

| Input Capacitance               | C <sub>IN</sub>    |                                                    |                                                                           |                            | 10   |                            | pF    |

| DIGITAL OUTPUTS CHARACTE        | RISTICS (DO        | UT, READY, BI                                      | JSY)                                                                      |                            |      |                            |       |

| Output Low Voltage              | V <sub>OL</sub>    | I <sub>SOURCE</sub> = 1.0                          | OmA                                                                       |                            |      | 0.2                        | V     |

| Output High Voltage             | V <sub>OH</sub>    | I <sub>SINK</sub> = 1.0mA                          | A, except for BUSY                                                        | V <sub>DDIO</sub><br>- 0.2 |      |                            | V     |

| Output Three-State Leakage      | I <sub>OZ</sub>    | DOUT only                                          |                                                                           |                            | ±0.1 | ±1                         | μΑ    |

| Output Three-State Capacitance  | C <sub>OZ</sub>    | DOUT only                                          |                                                                           |                            | 15   |                            | рF    |

| Output Short-Circuit Current    | I <sub>OSS</sub>   | $V_{DDIO} = 2.7V$                                  |                                                                           | ±150                       |      | mA                         |       |

| TIMING CHARACTERISTICS          |                    | _                                                  |                                                                           |                            |      |                            |       |

|                                 |                    | Stand-alone v                                      | vrite mode                                                                |                            |      | 50                         |       |

| Serial Clock Frequency          | fsclk              |                                                    | Stand-alone read mode and daisy-<br>chained read and write modes (Note 6) |                            |      | 8                          | MHz   |

|                                 |                    | Stand-alone v                                      | vrite mode                                                                | 20                         |      |                            |       |

| SCLK Period                     | t <sub>CP</sub>    |                                                    | ead mode and daisy-<br>and write modes                                    | 125                        |      |                            | ns    |

| SCLK Pulse-Width High           | t <sub>CH</sub>    | 40% duty cyc                                       | le                                                                        | 9                          |      |                            | ns    |

| SCLK Pulse-Width Low            | t <sub>CL</sub>    | 40% duty cyc                                       | le                                                                        | 9                          |      |                            | ns    |

|                                 |                    |                                                    | Stand-alone write mode                                                    | 12                         |      |                            |       |

| CS Fall to SCLK Fall Setup Time | t <sub>CSSO</sub>  | First SCLK falling edge                            | Stand-alone read mode and daisy-chained read and write modes              | 72                         |      |                            | ns    |

| CS Fall to SCLK Fall Hold Time  | t <sub>CSH0</sub>  | Inactive falling edge preceding first falling edge |                                                                           | 0                          |      |                            | ns    |

| SCLK Fall to CS Rise Hold Time  | t <sub>CSH1</sub>  | 24th falling edge                                  |                                                                           | 4                          |      |                            | ns    |

| DIN to SCLK Fall Setup Time     | t <sub>DS</sub>    |                                                    |                                                                           | 8                          |      |                            | ns    |

| DIN to SCLK Fall Hold Time      | t <sub>DH</sub>    |                                                    |                                                                           | 8                          |      |                            | ns    |

| SCLK Rise to DOUT Settle Time   | t <sub>DOT</sub>   | C <sub>L</sub> = 20pF (N                           | ote 7)                                                                    |                            |      | 40                         | ns    |

| SCLK Rise to DOUT Hold Time     | t <sub>DOH</sub>   | C <sub>L</sub> = 0pF (No                           | te 7)                                                                     | 2                          |      |                            | ns    |

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

### **DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 5V, V_{DDIO} =$ **1.8V to 2.7V** $, V_{AVSS} = -1.25V, V_{REF} = 4.096V, R_L = 10k\Omega, TC/\overline{SB} = M/\overline{Z} = DGND, C_{REFO} = 100pF, C_{BYPASS} = 1\mu F, T_A = -40^{\circ}C$  to +105°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ )(GAIN = 0x3FFFF and OFFSET = 0x00000.) (Note 2)

| PARAMETER                      | SYMBOL             | CONDITIONS                                         | MIN | TYP | MAX | UNITS |

|--------------------------------|--------------------|----------------------------------------------------|-----|-----|-----|-------|

| SCLK Fall to DOUT Disable Time | t <sub>DOZ</sub>   | 24th active edge deassertion                       | 2   |     | 40  | ns    |

| CS Fall to DOUT Enable         | t <sub>DOE</sub>   | Asynchronous assertion                             | 2   |     | 50  | ns    |

| CS Rise to DOUT Disable        | +                  | Stand-alone, aborted sequence                      |     |     | 70  | 20    |

| CS Rise to DOUT Disable        | t <sub>CSDOZ</sub> | Daisy-chained, aborted sequence                    |     |     | 130 | ns    |

| SCLK Fall to READY Fall        | tCRF               | 24th falling edge assertion, C <sub>L</sub> = 20pF |     |     | 60  | ns    |

| SCLK Fall to READY Hold        | tcrh               | 24th falling edge assertion, C <sub>L</sub> = 0pF  | 2   |     |     | ns    |

| SCLK Fall to BUSY Fall         | t <sub>CBF</sub>   | BUSY assertion                                     |     | 5   |     | ns    |

| CS Rise to READY Rise          | t <sub>CSR</sub>   | $C_L = 20pF$                                       |     |     | 60  | ns    |

| CS Rise to SCLK Fall           | t <sub>CSA</sub>   | 24th falling edge, aborted sequence                | 20  |     |     | ns    |

| CS Pulse Width High            | tCSPW              | Stand alone                                        | 20  |     |     | ns    |

| SCLK Fall to CS Fall           | t <sub>CSF</sub>   | 24th falling edge                                  | 100 |     |     | ns    |

| LDAC Pulse Width               | t <sub>LDPW</sub>  |                                                    | 20  |     |     | ns    |

| LDAC Fall to SCLK Fall Hold    | t <sub>LDH</sub>   | Last active falling edge                           | 20  | ·   |     | ns    |

| RST Pulse Width                | t <sub>RSTPW</sub> |                                                    | 20  |     |     | ns    |

Note 2: All devices are 100% tested at  $T_A = +25^{\circ}C$  and  $T_A = +105^{\circ}C$ . Limits at  $T_A = -40^{\circ}C$  are guaranteed by design.

Note 3: Linearity is tested from  $V_{REF}$  to AGND.

Note 4: Guaranteed by design.

Note 5: The total analog throughput time from DIN to  $V_{OUT}$  is the sum of  $t_S$  and  $t_{BUSY}$  (4.9 $\mu s$ , typ).

Note 6: Daisy-chain speed is relaxed to accommodate (t<sub>CRF</sub> + t<sub>CSS0</sub>).

Note 7: DOUT speed limits overall SPI speed..

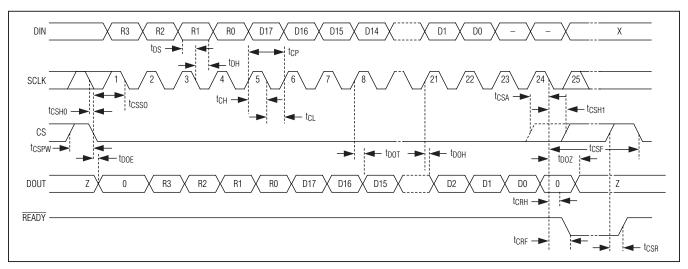

Figure 1. Serial Interface Timing Diagram, Stand-Alone Operation

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

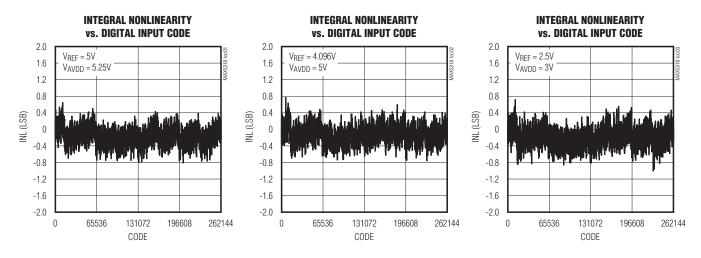

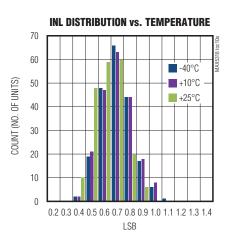

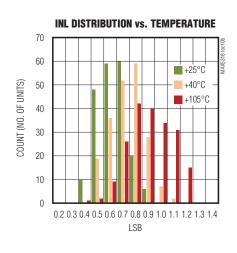

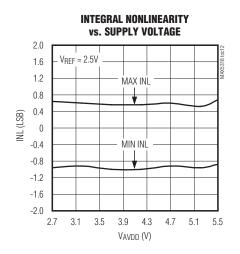

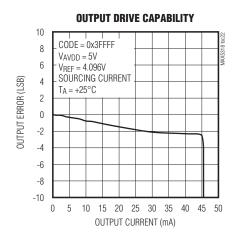

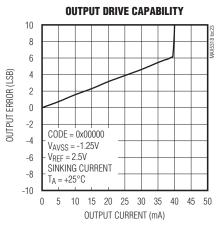

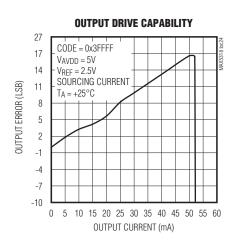

#### **Typical Operating Characteristics**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, RST = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

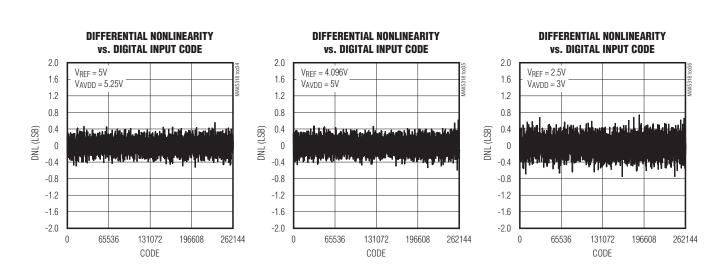

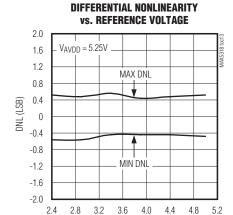

## **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, RST = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

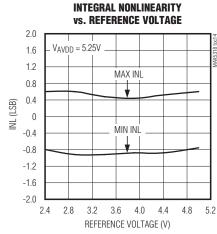

## **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, V_{AVSS} = -1.25V, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; V_{REF} = 4.096V, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \overline{RST} = V_{DDIO}, C_{REFO} = 100pF, C_L = 100pF, R_L = 10k\Omega, C_{BYPASS} = 1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

REFERENCE VOLTAGE (V)

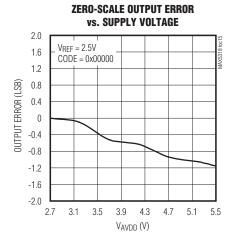

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### Typical Operating Characteristics (continued)

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \ V_{AVSS} = -1.25V, \ V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \ V_{REF} = 4.096V, \ TC/\overline{SB} = PD = M/\overline{Z} = DGND, \ RST = V_{DDIO}, \ C_{REFO} = 100pF, \ C_L = 100pF, \ R_L = 10k\Omega, \ C_{BYPASS} = 1\mu F, \ T_A = +25^{\circ}C, \ unless \ otherwise \ noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

### Typical Operating Characteristics (continued)

$(V_{AVDD} = V_{DDIO} = 5V, V_{AVSS} = -1.25V, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; V_{REF} = 4.096V, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \overline{RST} = V_{DDIO}, C_{REFO} = 100pF, C_L = 100pF, R_L = 10k\Omega, C_{BYPASS} = 1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

### **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, \overline{RST} = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, RST = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, RST = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

## 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

#### **Typical Operating Characteristics (continued)**

$\frac{(V_{AVDD} = V_{DDIO} = 5V, \, V_{AVSS} = -1.25V, \, V_{AGND} = V_{DGND} = V_{AGND\_F} = V_{AGND\_S} = 0V; \, V_{REF} = 4.096V, \, TC/\overline{SB} = PD = M/\overline{Z} = DGND, \, RST = V_{DDIO}, \, C_{REFO} = 100pF, \, C_L = 100pF, \, R_L = 10k\Omega, \, C_{BYPASS} = 1\mu F, \, T_A = +25^{\circ}C, \, unless \, otherwise \, noted.)$

# 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

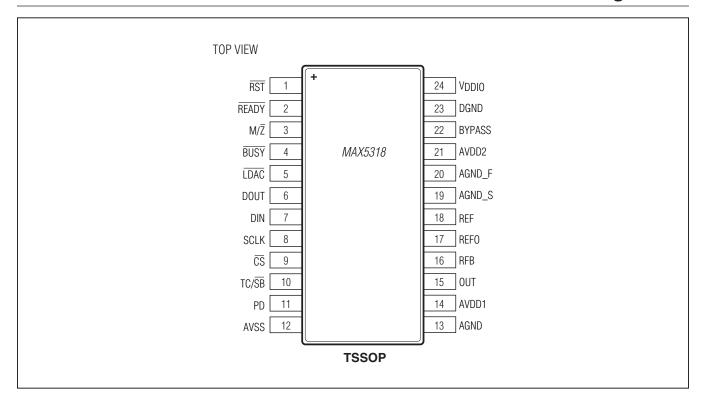

#### **Pin Configuration**

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RST   | Active-Low Reset Input. Drive $\overline{RST}$ low to DGND to put the device into a reset state. A reset state sets all SPI input registers to their default power-on reset states as defined by the state of inputs M/ $\overline{Z}$ and TC/ $\overline{SB}$ . Set $\overline{RST}$ high to VDDIO, the DAC output remains at the state defined by M/ $\overline{Z}$ until $\overline{LDAC}$ is taken low.                                                                                                                                                                                                                                                                                                  |

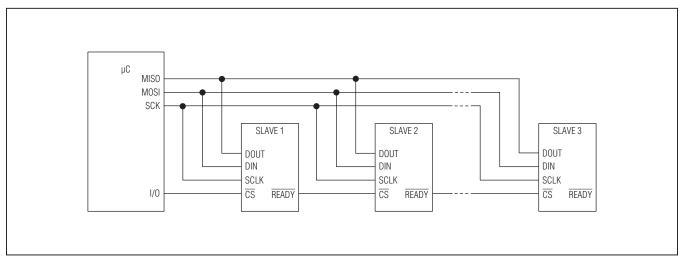

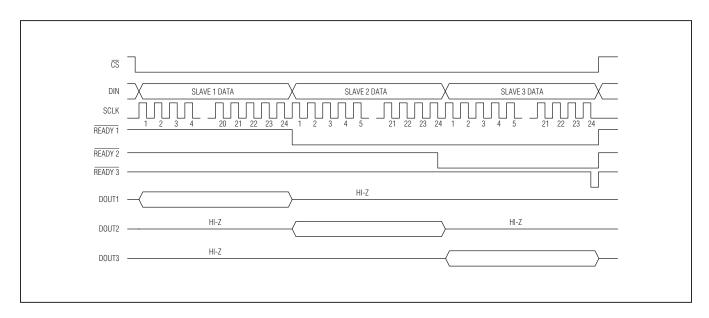

| 2   | READY | SPI Active-Low Ready Output. READY asserts low when the device successfully completes processing an SPI data frame. READY asserts high at the next rising edge of $\overline{CS}$ . In daisy-chain applications, the READY output typically drives the $\overline{CS}$ input of the next device in the chain or a GPIO of a microcontroller.                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | M/Z   | Reset Select Input. $M/\overline{Z}$ selects the default state of the analog output (OUT) after power-on or a hardware or software reset. Connect $M/\overline{Z}$ to $V_{DDIO}$ to set the default output voltage to midscale or to DGND to set the default output voltage to zero scale.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | BUSY  | Digital Input/Open-Drain Output. Connect a $2k\Omega$ pullup resistor from $\overline{BUSY}$ to $V_{DDIO}$ . $\overline{BUSY}$ goes low during the internal calculations of the DAC register data. During this time, the user can continue writing new data to the DIN, OFFSET, and GAIN registers, but no further updates to the DAC register and DAC output can take place. If $\overline{LDAC}$ is asserted low while $\overline{BUSY}$ is low, this event is stored. $\overline{BUSY}$ is bidirectional, and can be asserted low externally to delay $\overline{LDAC}$ action. $\overline{BUSY}$ also goes low during power-on reset, when $\overline{RST}$ is low, or when software reset is activated. |

# 18-Bit, High-Accuracy Voltage Output DAC with Digital Gain, Offset Control, and SPI Interface

## **Pin Description (continued)**

|     |                   | =:wo=rov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 5   | LDAC              | Active-Low Load DAC Logic Input. If $\overline{\text{LDAC}}$ is taken low while $\overline{\text{BUSY}}$ is inactive (high), the contents of the input registers are transferred to the DAC register and the DAC output is updated. If $\overline{\text{LDAC}}$ is taken low while $\overline{\text{BUSY}}$ is asserted low, the $\overline{\text{LDAC}}$ event is stored and the DAC register update is delayed until $\overline{\text{BUSY}}$ deasserts. Any event on $\overline{\text{LDAC}}$ during power-on reset or when $\overline{\text{RST}}$ is low is ignored. |  |  |  |  |  |  |  |

| 6   | DOUT              | SPI Bus Serial Data Output. See the Serial Interface section for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 7   | DIN               | SPI Bus Serial Data Input. See the Serial Interface section for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 8   | SCLK              | SPI Bus Serial Clock Input. See the Serial Interface section for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 9   | CS                | SPI Bus Active-Low Chip-Select Input. See the Serial Interface section for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 10  | TC/SB             | DIN Format Select Input. Connect TC/SB to DGND to set the data input format to straight binary or to VDDIO to set it to two's complement.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 11  | PD                | Active-High Power-Down Input. Connect PD to DGND for normal operation. Connect PD to $V_{DDIO}$ to place the device in power-down. In power-down, OUT (analog voltage output) is connected to AGND through a $2k\Omega$ resistor, but the contents of the input registers and the DAC latch do not change. The SPI interface remains active in power-down.                                                                                                                                                                                                                |  |  |  |  |  |  |  |