# **CPU 5-Bit Synchronous Buck Controller**

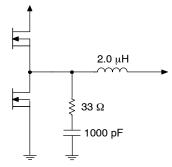

The CS5155H is a 5-bit synchronous dual N-Channel buck controller. It is designed to provide unprecedented transient response for today's demanding high-density, high-speed logic. The regulator operates using a proprietary control method, which allows a 100 ns response time to load transients. The CS5155H is designed to operate over a 4.25-20 V range ( $V_{\rm CC}$ ) using 12 V to power the IC and 5.0 V or 12 V as the main supply for conversion.

The CS5155H is specifically designed to power Pentium® II processors and other high performance core logic. It includes the following features: on board, 5-bit DAC, short circuit protection, 1.0% output tolerance,  $V_{\rm CC}$  monitor, and programmable Soft Start capability. The CS5155H is backwards compatible with the 4-bit CS5150, allowing the mother board designer the capability of using either the CS5150 or the CS5155H with no change in layout. The CS5155H is available in 16 pin surface mount packages.

#### **Features**

- Dual N-Channel Design

- Excess of 1.0 MHz Operation

- 100 ns Transient Response

- 5-Bit DAC

- Backward Compatible with 4-Bit CS5150H/CS5151H

- 30 ns Gate Rise/Fall Times

- 1.0% DAC Accuracy

- 5.0 V & 12 V Operation

- Remote Sense

- Programmable Soft Start

- Lossless Short Circuit Protection

- V<sub>CC</sub> Monitor

- 25 ns FET Nonoverlap Time

- Adaptive Voltage Positioning

- V<sup>2™</sup> Control Topology

- Current Sharing

- Overvoltage Protection

#### ON Semiconductor™

http://onsemi.com

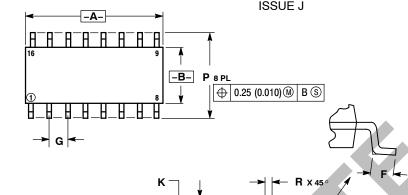

SOIC-16 D SUFFIX CASE 751B

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

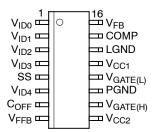

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device       | Package              | Shipping         |

|--------------|----------------------|------------------|

| CS5155HGD16  | 5155HGD16 SO-16 48 U | 48 Units/Rail    |

| CS5155HGDR16 |                      | 2500 Tape & Reel |

1

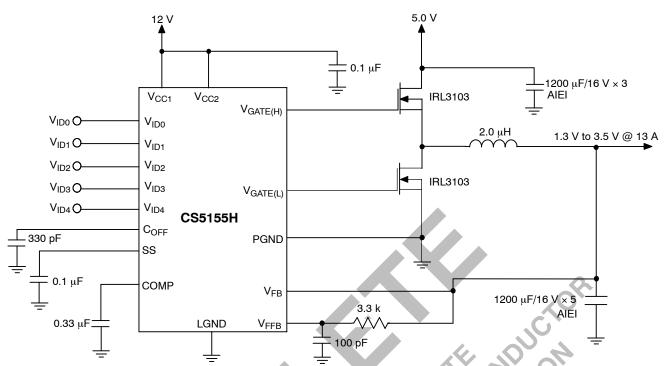

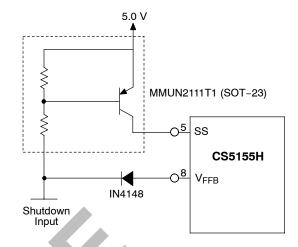

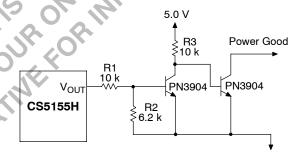

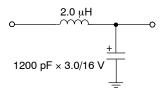

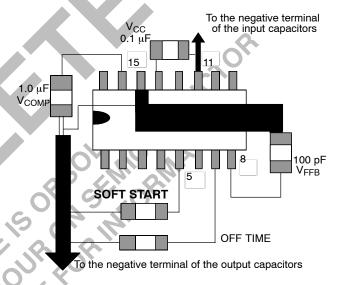

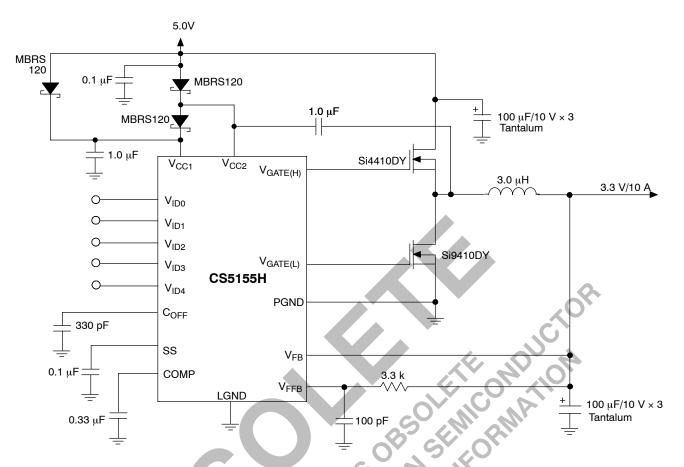

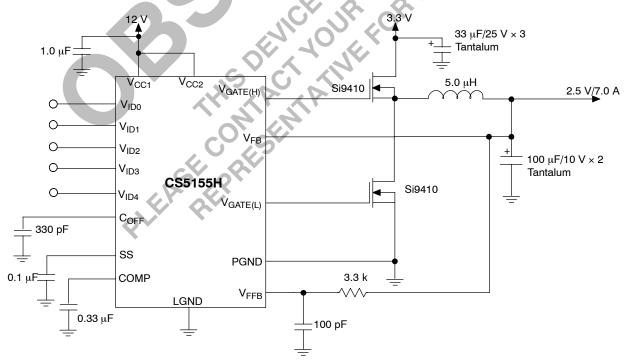

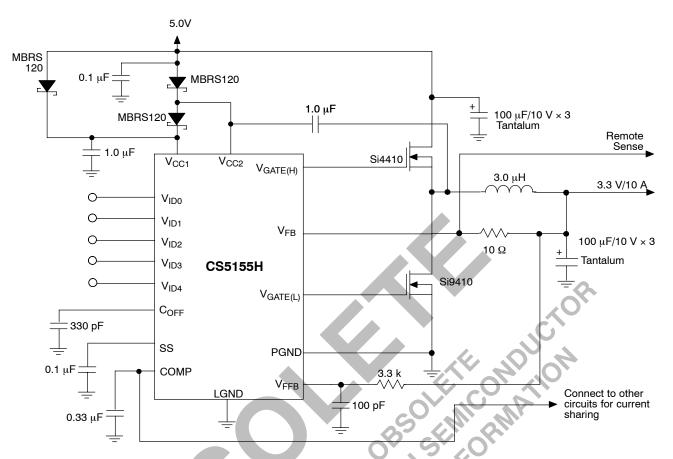

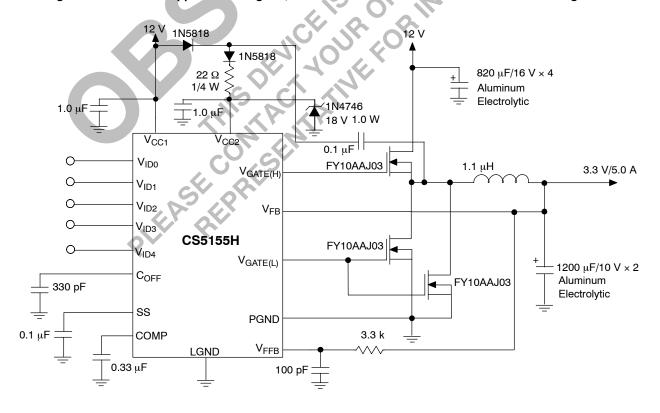

Figure 1. Application Diagram, Switching Power Supply for Core Logic – Pentium® II Processor

# **ABSOLUTE MAXIMUM RATINGS\***

|                                           | Rating                                                                                | Value                | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------|----------------------|------|

| Operating Junction Temperature, T         | 15 014 121                                                                            | 0 to 150             | °C   |

| Lead Temperature Soldering:               | Wave Solder (through hole styles only) (Note 1)<br>Reflow: (SMD styles only) (Note 2) | 260 peak<br>230 peak | °C   |

| Storage Temperature Range, T <sub>S</sub> | 10° K                                                                                 | -65 to +150          | °C   |

| ESD Susceptibility (Human Body Model)     | 0,4,7,6                                                                               | 2.0                  | kV   |

<sup>1. 10</sup> second maximum.

# **ABSOLUTE MAXIMUM RATINGS**

| Pin Name             | Max Operating Voltage | Max Current          |

|----------------------|-----------------------|----------------------|

| V <sub>CC1</sub>     | 16 V/-0.3 V           | 25 mA DC/1.5 A peak  |

| V <sub>CC2</sub>     | 20 V/-0.3 V           | 20 mA DC/1.5 A peak  |

| SS                   | 6.0 V/-0.3 V          | –100 μΑ              |

| COMP                 | 6.0 V/-0.3 V          | 200 μΑ               |

| V <sub>FB</sub>      | 6.0 V/-0.3 V          | -0.2 μΑ              |

| C <sub>OFF</sub>     | 6.0 V/-0.3 V          | -0.2 μΑ              |

| $V_{FFB}$            | 6.0 V/-0.3 V          | -0.2 μΑ              |

| $V_{ID0} - V_{ID4}$  | 6.0 V/-0.3 V          | -50 μΑ               |

| V <sub>GATE(H)</sub> | 20 V/-0.3 V           | 100 mA DC/1.5 A peak |

| V <sub>GATE(L)</sub> | 16 V/-0.3 V           | 100 mA DC/1.5 A peak |

| LGND                 | 0 V                   | 25 mA                |

| PGND                 | 0 V                   | 100 mA DC/1.5 A peak |

<sup>2. 60</sup> second maximum above 183°C.

<sup>\*</sup>The maximum package power dissipation must be observed.

$\begin{array}{ll} \textbf{ELECTRICAL CHARACTERISTICS} & (0 ^{\circ}C < T_{A} < +70 ^{\circ}C; \ 0 ^{\circ}C < T_{J} < +125 ^{\circ}C; \ 8.0 \ V < V_{CC1} < 14 \ V; \ 5.0 \ V < V_{CC2} < 20 \ V; DAC \\ \textbf{Code: V}_{ID4} = V_{ID2} = V_{ID1} = V_{ID0} = 1; \ V_{ID3} = 0; \ CV_{GATE(L)} \ \text{and } \ CV_{GATE(H)} = 1.0 \ \text{nF}; \ C_{OFF} = 330 \ \text{pF}; \ C_{SS} = 0.1 \ \mu\text{F, unless otherwise specified.}) \\ \end{array}$

| Error Amplifier $V_{FB}$ Bias Current $V_{FB} = 0 \text{ V}$ Open Loop Gain $1.25 \text{ V} < \text{V}_{COMP} < 4.0 \text{ V}$ ; Note 3Unity Gain BandwidthNote 3COMP SINK Current $V_{COMP} = 1.5 \text{ V}$ ; $V_{FB} = 3.0 \text{ V}$ ; $V_{SS} > 2.0 \text{ V}$ COMP SOURCE Current $V_{COMP} = 1.2 \text{ V}$ ; $V_{FB} = 2.7 \text{ V}$ ; $V_{SS} = 5.0 \text{ V}$ COMP CLAMP Current $V_{COMP} = 0 \text{ V}$ ; $V_{FB} = 2.7 \text{ V}$ COMP High Voltage $V_{FB} = 2.7 \text{ V}$ ; $V_{SS} = 5.0 \text{ V}$ COMP Low Voltage $V_{FB} = 3.0 \text{ V}$ PSRR $8.0 \text{ V} < \text{V}_{CC1} < 14 \text{ V} @ 1.0 \text{ kHz}$ ; Note 3 $V_{CC1}$ MonitorStart ThresholdOutput switchingStop ThresholdOutput not switchingHysteresisStart-Stop $V_{GATE(H)}$ and $V_{GATE(L)}$ Out SOURCE Sat at 100 mAMeasure $V_{CC1} - V_{GATE(L)}$ ; $V_{CC2} - V_{GATE(H)}$ Out SINK Sat at 100 mAMeasure $V_{GATE(H)} - V_{PGND}$ ; $V_{PGND}$ ; $V_{PGND}$ | -<br>50<br>500<br>0.4<br>30<br>0.4<br>4,0<br>-<br>60 | 0.3<br>60<br>3000<br>2.5<br>50<br>1.0<br>4.3 | 1.0<br>-<br>-<br>8.0<br>80<br>1.6 | μΑ<br>dB<br>kHz<br>mA<br>μΑ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|-----------------------------------|-----------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50<br>500<br>0.4<br>30<br>0.4<br>4,0                 | 60<br>3000<br>2.5<br>50<br>1.0<br>4.3        | -<br>8.0<br>80<br>1.6             | dB<br>kHz<br>mA             |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 500<br>0.4<br>30<br>0.4<br>4.0                       | 3000<br>2.5<br>50<br>1.0<br>4.3              | -<br>8.0<br>80<br>1.6             | kHz<br>mA                   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.4<br>30<br>0.4<br>4.0                              | 2.5<br>50<br>1.0<br>4.3                      | 8.0<br>80<br>1.6                  | mA                          |

| $COMP \ SOURCE \ Current \qquad V_{COMP} = 1.2 \ V; \ V_{FB} = 2.7 \ V; \ V_{SS} = 5.0 \ V$ $COMP \ CLAMP \ Current \qquad V_{COMP} = 0 \ V; \ V_{FB} = 2.7 \ V$ $COMP \ High \ Voltage \qquad V_{FB} = 2.7 \ V; \ V_{SS} = 5.0 \ V$ $COMP \ Low \ Voltage \qquad V_{FB} = 3.0 \ V$ $PSRR \qquad 8.0 \ V < V_{CC1} < 14 \ V \ @ \ 1.0 \ kHz; \ Note \ 3$ $V_{CC1} \ Monitor$ $Start \ Threshold \qquad Output \ switching$ $Stop \ Threshold \qquad Output \ not \ switching$ $Hysteresis \qquad Start_Stop$ $V_{GATE(H)} \ and \ V_{GATE(L)}$ $Out \ SOURCE \ Sat \ at \ 100 \ mA \qquad Measure \ V_{CC1} - V_{GATE(L)}; \ V_{CC2} - V_{GATE(H)}$                                                                                                                                                                                                                                                                                                       | 30<br>0.4<br>4,0                                     | 50<br>1.0<br>4.3                             | 80                                |                             |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.4<br>4.0<br>-                                      | 1.0                                          | 1.6                               | μА                          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                                  | 4.3                                          |                                   |                             |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                    |                                              |                                   | mA                          |

| PSRR  8.0 V < V <sub>CC1</sub> < 14 V @ 1.0 kHz; Note 3  V <sub>CC1</sub> Monitor  Start Threshold  Output switching  Stop Threshold  Output not switching  Hysteresis  Start-Stop  V <sub>GATE(H)</sub> and V <sub>GATE(L)</sub> Out SOURCE Sat at 100 mA  Measure V <sub>CC1</sub> - V <sub>GATE(L)</sub> ; V <sub>CC2</sub> - V <sub>GATE(H)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                   | 160                                          | 5.0                               | V                           |

| V <sub>CC1</sub> Monitor         Start Threshold       Output switching         Stop Threshold       Output not switching         Hysteresis       Start-Stop         V <sub>GATE(H)</sub> and V <sub>GATE(L)</sub> Out SOURCE Sat at 100 mA       Measure V <sub>CC1</sub> - V <sub>GATE(L)</sub> ; V <sub>CC2</sub> - V <sub>GATE(H)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                   |                                              | 600                               | mV                          |

| Start Threshold Output switching Stop Threshold Output not switching Hysteresis Start-Stop  V_GATE(H) and V_GATE(L) Out SOURCE Sat at 100 mA Measure V_CC1 - V_GATE(L); V_CC2 - V_GATE(H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | 85                                           | 0                                 | dB                          |

| Stop Threshold Output not switching Hysteresis Start-Stop  VGATE(H) and VGATE(L)  Out SOURCE Sat at 100 mA Measure VCC1 - VGATE(L); VCC2 - VGATE(H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                                              | .0                                |                             |

| Hysteresis Start-Stop  VGATE(H) and VGATE(L)  Out SOURCE Sat at 100 mA Measure VCC1 - VGATE(L); VCC2 - VGATE(H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.75                                                 | 3.90                                         | 4.05                              | V                           |

| V <sub>GATE(H)</sub> and V <sub>GATE(L)</sub> Out SOURCE Sat at 100 mA  Measure V <sub>CC1</sub> - V <sub>GATE(L)</sub> ; V <sub>CC2</sub> - V <sub>GATE(H)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.70                                                 | 3.85                                         | 4.00                              | V                           |

| Out SOURCE Sat at 100 mA Measure V <sub>CC1</sub> - V <sub>GATE(L)</sub> ; V <sub>CC2</sub> - V <sub>GATE(H)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                    | 50                                           | <b>%</b> -                        | mV                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V CC                                                 |                                              |                                   | -                           |

| Out SINK Sat at 100 mA Measure V <sub>GATE(H)</sub> – V <sub>PGND</sub> ; V <sub>GATE(L)</sub> – V <sub>PGND</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-10                                                | 1.2                                          | 2.0                               | V                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | () - (Q                                              | 1.0                                          | 1.5                               | V                           |

| Out Rise Time $1.0 \text{ V} < \text{V}_{\text{GATE(H)}} < 9.0 \text{ V}; \ 1.0 \text{ V} < \text{V}_{\text{GATE(L)}} < 9.0 \text{ V}; \\ \text{V}_{\text{CC1}} = \text{V}_{\text{CC2}} = 12 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NEO                                                  | 30                                           | 50                                | ns                          |

| Out Fall Time $9.0 \text{ V} > \text{V}_{\text{GATE(H)}} > 1.0 \text{ V}; \ 9.0 \text{ V} > \text{V}_{\text{GATE(L)}} > 1.0 \text{ V}; \\ \text{V}_{\text{CC1}} = \text{V}_{\text{CC2}} = 12 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                    | 30                                           | 50                                | ns                          |

| Shoot-Through Current Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                    | -                                            | 50                                | mA                          |

| Delay $V_{GATE(H)}$ to $V_{GATE(L)}$ $V_{GATE(L)}$ falling to 2.0 V; $V_{CC1} = V_{CC2} = 8.0$ V; $V_{GATE(L)}$ rising to 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                    | 25                                           | 50                                | ns                          |

| Delay $V_{GATE(L)}$ to $V_{GATE(H)}$ $V_{GATE(L)}$ falling to 2.0 V; $V_{CC1} = V_{CC2} = 8.0$ V; $V_{GATE(H)}$ rising to 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                    | 25                                           | 50                                | ns                          |

| V <sub>GATE(H)</sub> , V <sub>GATE(L)</sub> Resistance Resistor to LGND. Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                   | 50                                           | 100                               | kΩ                          |

| V <sub>GATE(H)</sub> , V <sub>GATE(L)</sub> Schottky  LGND to V <sub>GATE(H)</sub> @ 10 mA  LGND to V <sub>GATE(L)</sub> @ 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                    | 600                                          | 800                               | mV                          |

| Soft Start (SS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |                                              |                                   |                             |

| Charge Time -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.6                                                  | 3.3                                          | 5.0                               | ms                          |

| Pulse Period –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                   | 100                                          | 200                               | ms                          |

| Duty Cycle (Charge Time /Pulse Period) × 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.0                                                  | 3.3                                          | 6.0                               | %                           |

| COMP Clamp Voltage V <sub>FB</sub> = 0 V; V <sub>SS</sub> = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.50                                                 | 0.95                                         | 1.10                              | V                           |

| V <sub>FFB</sub> SS Fault Disable V <sub>GATE(H)</sub> = Low; V <sub>GATE(L)</sub> = Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.9                                                  | 1.0                                          | 1.1                               | V                           |

| High Threshold –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                    | 2.5                                          | 3.0                               | V                           |

| PWM Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |                                              |                                   |                             |

| Transient Response $ V_{FFB} = 0 \text{ to } 5.0 \text{ V to } V_{GATE(H)} = 9.0 \text{ V to } 1.0 \text{ V}; $ $ V_{CC1} = V_{CC2} = 12 \text{ V} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                                              |                                   |                             |

| V <sub>FFB</sub> Bias Current V <sub>FFB</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                    | 100                                          | 125                               | ns                          |

<sup>3.</sup> Guaranteed by design, not 100% tested in production.

|                          |                  | racteris         |                                                                                              |           | Test Conditions                                                              | Min    | Тур    | Max     | Unit     |

|--------------------------|------------------|------------------|----------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------|--------|--------|---------|----------|

| DAC                      |                  |                  |                                                                                              |           |                                                                              |        |        |         | <u>I</u> |

| Input                    | Thresh           | old              |                                                                                              |           | $V_{ID0}, V_{ID1}, V_{ID2}, V_{ID3}, V_{ID4}$                                | 1.00   | 1.25   | 2.40    | V        |

| Input Pull Up Resistance |                  |                  | V <sub>ID0</sub> , V <sub>ID1</sub> , V <sub>ID2</sub> , V <sub>ID3</sub> , V <sub>ID4</sub> | 25        | 50                                                                           | 100    | kΩ     |         |          |

| Pull Up Voltage          |                  |                  | -                                                                                            | 4.85      | 5.00                                                                         | 5.15   | V      |         |          |

| Accur                    | racy (all        | codes e          | xcept 11                                                                                     | 111)      | Measure V <sub>FB</sub> = V <sub>COMP</sub> , 25°C ≤[T <sub>J</sub> ≤[] 25°C | _      | _      | 1.0     | %        |

| V <sub>ID4</sub>         | V <sub>ID3</sub> | V <sub>ID2</sub> | V <sub>ID1</sub>                                                                             | $V_{ID0}$ |                                                                              |        |        |         |          |

| 0                        | 1                | 1                | 1                                                                                            | 1         | -                                                                            | 1.3266 | 1.3400 | 1.3534  | V        |

| 0                        | 1                | 1                | 1                                                                                            | 0         | -                                                                            | 1.3761 | 1.3900 | 1.4039  | V        |

| 0                        | 1                | 1                | 0                                                                                            | 1         | -                                                                            | 1.4256 | 1.4400 | 1.4544  | V        |

| 0                        | 1                | 1                | 0                                                                                            | 0         | -                                                                            | 1.4751 | 1.4900 | 1.5049  | V        |

| 0                        | 1                | 0                | 1                                                                                            | 1         | -                                                                            | 1.5246 | 1.5400 | 1.5554  | V        |

| 0                        | 1                | 0                | 1                                                                                            | 0         | -                                                                            | 1.5741 | 1.5900 | 1.6059  | V        |

| 0                        | 1                | 0                | 0                                                                                            | 1         | -                                                                            | 1.6236 | 1.6400 | 1.6564  | V        |

| 0                        | 1                | 0                | 0                                                                                            | 0         | _                                                                            | 1.6731 | 1,6900 | 1.7069  | V        |

| 0                        | 0                | 1                | 1                                                                                            | 1         |                                                                              | 1.7226 | 1.7400 | 1.7574  | V        |

| 0                        | 0                | 1                | 1                                                                                            | 0         |                                                                              | 1,7721 | 1.7900 | 1.8079  | V        |

| 0                        | 0                | 1                | 0                                                                                            | 1         | - 0,5                                                                        | 1.8216 | 1.8400 | 1.8584  | V        |

| 0                        | 0                | 1                | 0                                                                                            | 0         | - 0 <sup>V</sup> , 6                                                         | 1.8711 | 1.8900 | 1.9089  | V        |

| 0                        | 0                | 0                | 1                                                                                            | 1         | - 15 01                                                                      | 1,9206 | 1.9400 | 1.9594  | V        |

| 0                        | 0                | 0                | 1                                                                                            | 0         | -c.V.Q.                                                                      | 1.9701 | 1.9900 | 2.0099  | V        |

| 0                        | 0                | 0                | 0                                                                                            | 1         | 110 01,50.                                                                   | 2.0196 | 2.0400 | 2.0604  | V        |

| 0                        | 0                | 0                | 0                                                                                            | 0         | - V V                                                                        | 2.0691 | 2.0900 | 2.1109  | V        |

| 1                        | 1                | 1                | 1                                                                                            | 1         | G C- (1)                                                                     | 1.2191 | 1.2440 | 1.2689  | V        |

| 1                        | 1                | 1                | 1                                                                                            | 0         | A - A - IN.                                                                  | 2.1186 | 2.1400 | 2.1614  | V        |

| 1                        | 1                | 1                | 0                                                                                            | 1         | 1,67,-67                                                                     | 2.2176 | 2.2400 | 2.2624  | V        |

| 1                        | 1                | 1                | 0                                                                                            | 0         | CO, CK                                                                       | 2.3166 | 2.3400 | 2.3634  | V        |

| 1                        | 1                | 0                | 1                                                                                            | 1         | 4. 64 -                                                                      | 2.4156 | 2.4400 | 2.4644  | V        |

| 1                        | 1                | 0                | 1                                                                                            | 0         | S . P -                                                                      | 2.5146 | 2.5400 | 2.5654  | V        |

| 1                        | 1                | 0                | 0                                                                                            | 1         | -                                                                            | 2.6136 | 2.6400 | 2.6664  | V        |

| 1                        | 1                | 0                | 0                                                                                            | 0         | -                                                                            | 2.7126 | 2.7400 | 2.7674  | V        |

| 1                        | 0                | 1                | 1                                                                                            | 1         | _                                                                            | 2.8116 | 2.8400 | 2.8684  | V        |

| 1                        | 0                | 1                | 1                                                                                            | 0         | _                                                                            | 2.9106 | 2.9400 | 2.9694  | V        |

| 1                        | 0                | 1                | 0                                                                                            | 1         | _                                                                            | 3.0096 | 3.0400 | 3.0704  | V        |

| 1                        | 0                | 1                | 0                                                                                            | 0         | _                                                                            | 3.1086 | 3.1400 | 3.1714  | V        |

| 1                        | 0                | 0                | 1                                                                                            | 1         | _                                                                            | 3.2076 | 3.2400 | 3.2724  | V        |

| 1                        | 0                | 0                | 1                                                                                            | 0         |                                                                              | 3.3066 | 3.3400 | 3.3734  | V        |

| 1                        | 0                | 0                | 0                                                                                            | 1         |                                                                              | 3.4056 | 3.4400 | 3.4744  | V        |

| 1                        | 0                | 0                | 0                                                                                            | 0         | <del>-</del>                                                                 | 3.5046 | 3.5400 | 3.5754  | V        |

| '                        | U                | U                | U                                                                                            | U         |                                                                              | 0.0040 | 0.5400 | 0.07.04 | v        |

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ \, (0^{\circ}\text{C} < T_{A} < +70^{\circ}\text{C}; \ 0^{\circ}\text{C} < T_{J} < +125^{\circ}\text{C}; \ 8.0 \ V < V_{CC1} < 14 \ V; \ 5.0 \ V < V_{CC2} < 20 \ V; \text{DAC Code:} \ \, V_{ID4} = V_{ID2} = V_{ID1} = V_{ID0} = 1; \ V_{ID3} = 0; \ CV_{GATE(L)} \ \, \text{and} \ \, CV_{GATE(H)} = 1.0 \ \, \text{nF}; \ C_{OFF} = 330 \ \, \text{pF}; \ C_{SS} = 0.1 \ \, \mu\text{F}, \ \, \text{unless otherwise specified.} )$

| Characteristic             | Test Conditions                                                                                                    | Min | Тур | Max  | Unit |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Supply Current             |                                                                                                                    | 1   |     |      | ı    |

| I <sub>CC1</sub>           | No Switching                                                                                                       | _   | 8.5 | 13.5 | mA   |

| I <sub>CC2</sub>           | No Switching                                                                                                       | _   | 1.6 | 3.0  | mA   |

| Operating I <sub>CC1</sub> | V <sub>FB</sub> = COMP = V <sub>FFB</sub>                                                                          | _   | 8.0 | 13   | mA   |

| Operating I <sub>CC2</sub> | V <sub>FB</sub> = COMP = V <sub>FFB</sub>                                                                          | _   | 2.0 | 5.0  | mA   |

| C <sub>OFF</sub>           |                                                                                                                    |     |     |      |      |

| Normal Charge Time         | V <sub>FFB</sub> = 1.5 V; V <sub>SS</sub> = 5.0 V                                                                  | 1.0 | 1.6 | 2.2  | μs   |

| Extension Charge Time      | V <sub>SS</sub> = V <sub>FFB</sub> = 0                                                                             | 5.0 | 8.0 | 11.0 | μs   |

| Discharge Current          | C <sub>OFF</sub> to 5.0 V; V <sub>FB</sub> > 1.0 V                                                                 | 5.0 | -   | _    | mA   |

| Time Out Timer             |                                                                                                                    |     |     | 0    |      |

| Time Out Time              | V <sub>FB</sub> = V <sub>COMP</sub> ; V <sub>FFB</sub> = 2.0 V;<br>Record V <sub>GATE(H)</sub> Pulse High Duration | 10  | 30  | 65   | μs   |

| Fault Mode Duty Cycle      | V <sub>FFB</sub> = 0V                                                                                              | 35  | 50  | 70   | %    |

# PACKAGE PIN DESCRIPTION

| PACKAGE PIN # |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO-16         | PIN SYMBOL                         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1, 2, 3, 4, 6 | V <sub>ID0</sub> -V <sub>ID4</sub> | Voltage ID DAC input pins. These pins are internally pulled up to 5.0 V providing logic ones if left open. $V_{ID4}$ selects the DAC range. When $V_{ID4}$ is High (logic one), the DAC range is 2.14 V to 3.54 V with 100 mV increments. When $V_{ID4}$ is Low (logic zero), the DAC range is 1.34 V to 2.09 V with 50 mV increments. $V_{ID0} - V_{ID4}$ select the desired DAC output voltage. Leaving all 5 DAC input pins open results in a DAC output voltage of 1.244 V, allowing for adjustable output voltage, using a traditional resistor divider. |

| 5             | SS                                 | Soft Start Pin. A capacitor from this pin to LGND in conjunction with internal 60 $\mu$ A current source provides Soft Start function for the controller. This pin disables fault detect function during Soft Start. When a fault is detected, the Soft Start capacitor is slowly discharged by internal 2.0 $\mu$ A current source setting the time out before trying to restart the IC. Charge/discharge current ratio of 30 sets the duty cycle for the IC when the regulator output is shorted.                                                           |

| 7             | C <sub>OFF</sub>                   | A capacitor from this pin to ground sets the time duration for the on board one shot, which is used for the constant off time architecture.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8             | V <sub>FFB</sub>                   | Fast feedback connection to the PWM comparator. This pin is connected to the regulator output. The inner feedback loop terminates on time.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9             | V <sub>CC2</sub>                   | Boosted power for the high side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10            | V <sub>GATE(H)</sub>               | High FET driver pin capable of 1.5 A peak switching current. Internal circuit prevents $V_{\text{GATE(H)}}$ and $V_{\text{GATE(L)}}$ from being in high state simultaneously.                                                                                                                                                                                                                                                                                                                                                                                 |

| 11            | PGND                               | High current ground for the IC. The MOSFET driver is referenced to this pin. Input capacitor ground and the source of lower FET should be tied to this pin.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12            | V <sub>GATE(L)</sub>               | Low FET driver pin capable of 1.5 A peak switching current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13            | V <sub>CC1</sub>                   | Input power for the IC and low side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14            | LGND                               | Signal ground for the IC. All control circuits are referenced to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15            | COMP                               | Error amplifier compensation pin. A capacitor to ground should be provided externally to compensate the amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16            | V <sub>FB</sub>                    | Error amplifier DC feedback input. This is the master voltage feedback which sets the output voltage. This pin can be connected directly to the output or a remote sense trace.                                                                                                                                                                                                                                                                                                                                                                               |

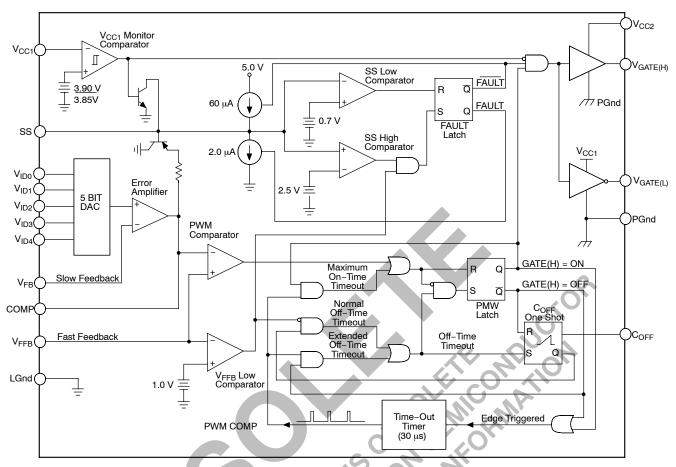

Figure 2. Block Diagram

#### **APPLICATIONS INFORMATION**

#### THEORY OF OPERATION

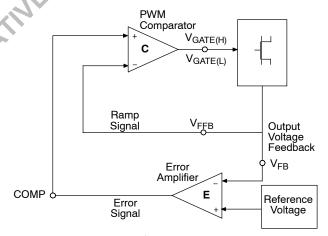

#### V<sup>2</sup> Control Method

The  $V^2$  method of control uses a ramp signal that is generated by the ESR of the output capacitors. This ramp is proportional to the AC current through the main inductor and is offset by the value of the DC output voltage. This control scheme inherently compensates for variation in either line or load conditions, since the ramp signal is generated from the output voltage itself. This control scheme inherently compensates for variation in either line or load conditions, since the ramp signal is generated from the output voltage itself. This control scheme differs from traditional techniques such as voltage mode, which generates an artificial ramp, and current mode, which generates a ramp from inductor current.

Figure 3. V<sup>2</sup> Control Diagram

The  $V^2$  control method is illustrated in Figure 3. The output voltage is used to generate both the error signal and the ramp signal. Since the ramp signal is simply the output voltage, it is affected by any change in the output regardless of the origin of that change. The ramp signal also contains the DC portion of the output voltage, which allows the control circuit to drive the main switch to 0% or 100% duty cycle as required.

A change in line voltage changes the current ramp in the inductor, affecting the ramp signal, which causes the  $V^2$  control scheme to compensate the duty cycle. Since the change in inductor current modifies the ramp signal, as in current mode control, the  $V^2$  control scheme has the same advantages in line transient response.

A change in load current will have an affect on the output voltage, altering the ramp signal. A load step immediately changes the state of the comparator output, which controls the main switch. Load transient response is determined only by the comparator response time and the transition speed of the main switch. The reaction time to an output load step has no relation to the crossover frequency of the error signal loop, as in traditional control methods.

The error signal loop can have a low crossover frequency, since transient response is handled by the ramp signal loop. The main purpose of this 'slow' feedback loop is to provide DC accuracy. Noise immunity is significantly improved, since the error amplifier bandwidth can be rolled off at a low frequency. Enhanced noise immunity improves remote sensing of the output voltage, since the noise associated with long feedback traces can be effectively filtered.

Line and load regulation are drastically improved because there are two independent voltage loops. A voltage mode controller relies on a change in the error signal to compensate for a deviation in either line or load voltage. This change in the error signal causes the output voltage to change corresponding to the gain of the error amplifier, which is normally specified as line and load regulation. A current mode controller maintains fixed error signal under deviation in the line voltage, since the slope of the ramp signal changes, but still relies on a change in the error signal for a deviation in load. The V<sup>2</sup> method of control maintains a fixed error signal for both line and load variation, since the ramp signal is affected by both line and load.

#### **Constant Off Time**

To maximize transient response, the CS5155H uses a constant off time method to control the rate of output pulses. During normal operation, the off time of the high side switch is terminated after a fixed period, set by the  $C_{OFF}$  capacitor. To maintain regulation, the  $V^2$  control loop varies switch on time. The PWM comparator monitors the output voltage ramp, and terminates the switch on time.

Constant off time provides a number of advantages. Switch duty cycle can be adjusted from 0 to 100% on a pulse by pulse basis when responding to transient conditions. Both 0% and 100% duty cycle operation can be maintained for extended periods of time in response to load or line transients. PWM slope compensation to avoid sub–harmonic oscillations at high duty cycles is avoided.

Switch on time is limited by an internal 30  $\mu$ s timer, minimizing stress to the power components.

#### **Programmable Output**

The CS5155H is designed to provide two methods for programming the output voltage of the power supply. A five bit on board digital to analog converter (DAC) is used to program the output voltage within two different ranges. The first range is 2.14 V to 3.54 V in 100 mV steps, the second is 1.34 V to 2.09 V in 50 mV steps, depending on the digital input code. If all five bits are left open, the CS5155H enters adjust mode. In adjust mode, the designer can choose any output voltage by using resistor divider feedback to the  $V_{\rm FB}$  and  $V_{\rm FFB}$  pins, as in traditional controllers. The CS5155H is specifically designed to be backwards compatible with the CS5150, which uses a four bit DAC code.

#### Start Up

Until the voltage on the  $V_{CC1}$  supply pin exceeds the 3.9 V monitor threshold, the Soft Start and gate pins are held low. The FAULT latch is reset (no Fault condition). The output of the error amplifier (COMP) is pulled up to 1.0 V by the comparator clamp. When the  $V_{CC1}$  pin exceeds the monitor threshold, the GATE(H) output is activated, and the Soft Start capacitor begins charging. The GATE(H) output will remain on, enabling the NFET switch, until terminated by either the PWM comparator, or the maximum on time timer.

If the maximum on time is exceeded before the regulator output voltage achieves the 1.0 V level, the pulse is terminated. The GATE(H) pin drives low, and the GATE(L) pin drives high for the duration of the extended off time. This time is set by the time out timer and is approximately equal to the maximum on time, resulting in a 50% duty cycle. The GATE(L) pin will then drive low, the GATE(H) pin will drive high, and the cycle repeats.

When regulator output voltage achieves the 1.0 V level present at the COMP pin, regulation has been achieved and normal off time will ensue. The PWM comparator terminates the switch on time, with off time set by the  $C_{OFF}$  capacitor. The  $V^2$  control loop will adjust switch duty cycle as required to ensure the regulator output voltage tracks the output of the error amplifier.

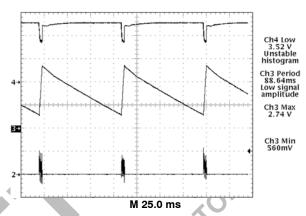

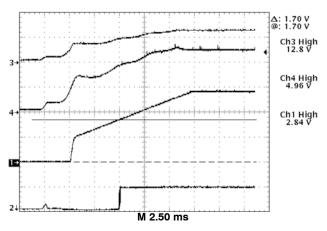

The Soft Start and COMP capacitors will charge to their final levels, providing a controlled turn on of the regulator output. Regulator turn on time is determined by the COMP

capacitor charging to its final value. Its voltage is limited by the Soft Start COMP clamp and the voltage on the Soft Start pin (see Figures 4 and 5).

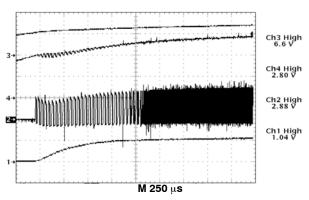

Trace 1- Regulator Output Voltage (1.0 V/div.)

Trace 2- Inductor Switching Node (2.0 V/div.)

Trace 3- 12 V Input (V<sub>CC1</sub> and V<sub>CC2</sub>) (5.0 V/div.)

Trace 4- 5.0 V Input (1.0 V/div.)

Figure 4. CS5155H Demonstration Board Startup in Response to Increasing 12 V and 5.0 V Input Voltages. Extended Off Time is Followed by Normal Off Time Operation when Output Voltage Achieves Regulation to the Error Amplifier Output.

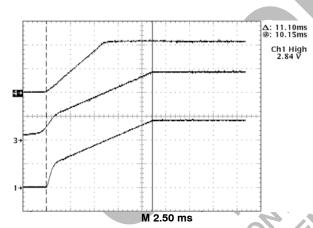

Trace 1- Regulator Output Voltage (1.0 V/div.)

Trace 3- COMP PIn (error amplifier output) (1.0 V/div.)

Trace 4- Soft Start Pin (2.0 V/div.)

Figure 5. CS5155H Demonstration Board Startup Waveforms

If the input voltage rises quickly, or the regulator output is enabled externally, output voltage will increase to the level set by the error amplifier output more rapidly, usually within a couple of cycles (see Figure 6).

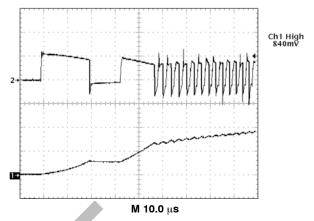

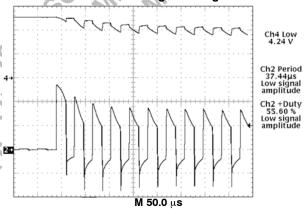

Trace 1 – Regulator Output Voltage (5.0 V/div.)

Trace 2 – Inductor Switching Node (5.0 V/div.)

Figure 6. CS5155H Demonstration Board Enable Startup Waveforms

#### **Normal Operation**

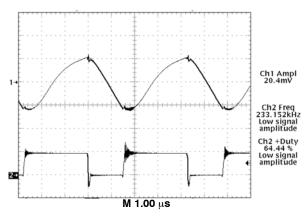

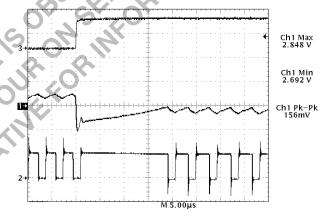

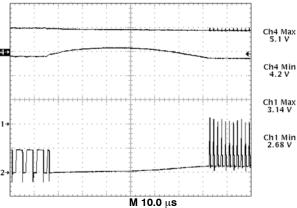

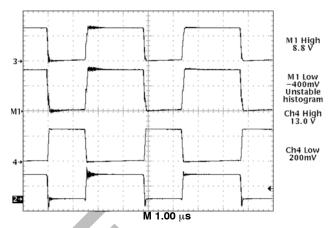

During normal operation, switch off time is constant and set by the  $C_{OFF}$  capacitor. Switch on time is adjusted by the  $V^2$  control loop to maintain regulation. This results in changes in regulator switching frequency, duty cycle, and output ripple in response to changes in load and line. Output voltage ripple will be determined by inductor ripple current working into the ESR of the output capacitors (see Figures 7 and 8).

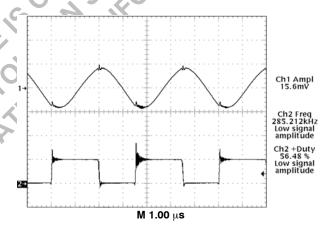

Trace 1- Regulator Output Voltage (10 mV/div.)

Trace 2- Inductor Switching Node (5.0 V/div.)

Figure 7. Peak-to-Peak Ripple on V<sub>OUT</sub> = 2.8 V, I<sub>OUT</sub> = 0.5 A (Light Load)

Trace 1- Regulator Output Voltage (10 mV/div.)

Trace 2- Inductor Switching Node (5.0 V/div.)

Figure 8. Peak-to-Peak Ripple on V<sub>OUT</sub> = 2.8 V, I<sub>OUT</sub> = 13 A (Heavy Load)

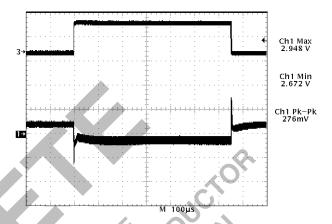

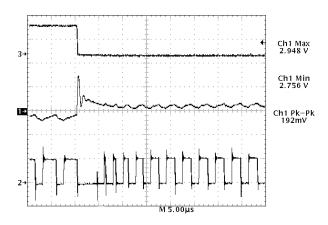

#### **Transient Response**

The CS5155H  $V^2$  control loop's 100 ns reaction time provides unprecedented transient response to changes in input voltage or output current. Pulse by pulse adjustment of duty cycle is provided to quickly ramp the inductor current to the required level. Since the inductor current cannot be changed instantaneously, regulation is maintained by the output capacitor(s) during the time required to slew the inductor current.

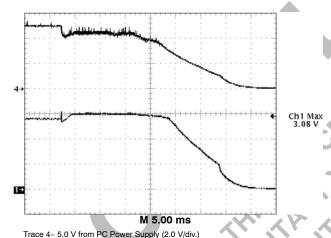

Overall load transient response is further improved through a feature called "adaptive voltage positioning". This technique pre-positions the output capacitor's voltage to reduce total output voltage excursions during changes in load.

Holding tolerance to 1.0% allows the error amplifier's reference voltage to be targeted +40 mV high without compromising DC accuracy. A "droop resistor", implemented through a PC board trace, connects the error amplifier's feedback pin ( $V_{FB}$ ) to the output capacitors and load and carries the output current. With no load, there is no DC drop across this resistor, producing an output voltage tracking the error amplifier's, including the +40 mV offset. When the full load current is delivered, an 80 mV drop is developed across this resistor. This results in output voltage being offset -40 mV low.

The result of adaptive voltage positioning is that additional margin is provided for a load transient before reaching the output voltage specification limits. When load current suddenly increases from its minimum level, the output capacitor is pre-positioned +40 mV. Conversely, when load current suddenly decreases from its maximum

level, the output capacitor is pre-positioned -40 mV (see Figures 9, 10, and 11). For best transient response, a combination of a number of high frequency and bulk output capacitors are usually used.

If the maximum on time is exceeded while responding to a sudden increase in load current, a normal off time occurs to prevent saturation of the output inductor.

Trace 1- Regulator Output Voltage (1.0 V/div.)

Trace 2- Regulator Output Voltage (20 V/div.)

Figure 9. CS5155H Demonstration Board Response to a 0.5 to 13 A Load Pulse (Output Set for 2.8 V)