# 11-Bit Resolution Simultaneous Sampling A/D Converter

AD7861

#### **FEATURES**

11-Bit Resolution Analog-to-Digital Converter

Seven Single-Ended Analog Inputs

Four Input Channels Simultaneously Sampled

Expansion with 4 Multiplexed Inputs

Internal 2.5 V Reference

3.2 µs Conversion Time per Channel

User Definable Channel Sequencing

Single Supply +5 V Operation

Double Buffered Register Outputs

6.25 MHz to 12.5 MHz Operating Clock Range

APPLICATIONS

Motor Control

3-Phase Power Measurement

Cellular Phones

Data Acquisition

#### **GENERAL DESCRIPTION**

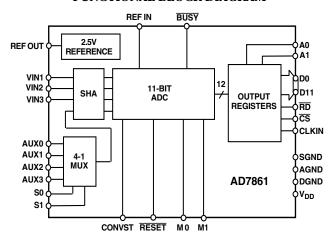

The AD7861 is a multichannel simultaneous sampling A/D Converter (ADC) configured for the acquisition of voltage inputs in a motor control solution or three-phase power system.

The AD7861 combined with Analog Devices' 16-bit fixed-point digital signal processor (DSP) provides a low cost 16-bit fixed-point microcontroller solution.

The input stage has been designed to accommodate the types of signals frequently found in motor drives. The VIN1, VIN2, and VIN3 channels are simultaneously sampled inputs suitable for stator current acquisition. The AUX0–AUX3 channels are multiplexed and are suitable for slower moving inputs such as temperature and bus voltage of the diode rectifier output in a motor control application.

#### **FUNCTIONAL BLOCK DIAGRAM**

#### PRODUCT HIGHLIGHTS

#### **Simultaneous Sampling of Four Inputs**

Four channel sample and hold amplifier (SHA) allows out of phase input signals to be sampled simultaneously, preserving the relative phase information. Sample-and-hold acquisition time is  $1.6~\mu s$  and conversion time per channel is  $3.2~\mu s$  (using a 12.5~MHz system clock).

#### Flexible Analog Channel Sequencing

AD7861 supports acquisition of 2, 3 or 4 channels per group. Converted channel results are stored in registers and the data can be read in any order. The sampling and conversion time for two channels is 8  $\mu$ s, three channels is 11.2  $\mu$ s, and four channels is 14.4  $\mu$ s (using a 12.5 MHz system clock).

#### Single 5 V dc Operation

Low power, digital process.

## $\label{eq:AD7861} \textbf{AD7861-SPECIFICATIONS} \begin{subarray}{l} (V_{DD} = 5 \ V \pm 5\%; T_A = -40 \ ^\circ\text{C} \ \text{to} \ +85 \ ^\circ\text{C}; \ \text{REFIN} = 2.5 \ V; \ \text{Ext CLK} @ 12.5 \ \text{MHz, unless otherwise noted)} \\ \end{subarray}$

| Parameter                                                                                                                                                  | AD7861AP                               | Units                                                        | Conditions/Comments                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC ACCURACY Resolution Relative Accuracy Differential Nonlinearity Bias Offset Error Bias Offset Error Match Full-Scale Error Full-Scale Error Match       | 11<br>±2<br>±2.5<br>±9<br>4<br>±13     | Bits LSB max | Twos Complement Data Format Integral Nonlinearity  Any Channel Between Channels Any Channel Between Channels                                                                                                                                                                                              |

| DYNAMIC PERFORMANCE Signal-to-Noise Ratio (SNR) Total Harmonic Distortion (THD) Peak Harmonic or Spurious Noise Channel-to-Channel Isolation M1 = 0 M1 = 1 | 60<br>-60<br>-60<br>-58<br>-53         | dB min dB max dB max dB max dB max                           | f <sub>IN</sub> = 1 kHz Sine Wave, f <sub>SAMPLE</sub> = 75 kHz<br>f <sub>IN</sub> = 1 kHz Sine Wave, f <sub>SAMPLE</sub> = 75 kHz<br>f <sub>IN</sub> = 1 kHz Sine Wave, f <sub>SAMPLE</sub> = 75 kHz<br>1 kHz Sine Wave Applied to Unselected Channels<br>1 kHz Sine Wave Applied to Unselected Channels |

| REFERENCE Input Voltage Range (REF IN) Input Current Onboard Reference Output (REF OUT) Reference Tolerance Reference Drive Capability                     | 2.5<br>50<br>2.5<br>±5<br>±100         | V<br>μA max<br>V<br>%<br>μA max                              |                                                                                                                                                                                                                                                                                                           |

| SAMPLE-AND-HOLD Acquisition Time Aperture Delay Time Aperture Delay Time Match Droop Rate                                                                  | 1.6<br>200<br>20<br>5                  | μs<br>ns max<br>ns max<br>mV/ms max                          | 20 CLK Cycles @ 12.5 MHz                                                                                                                                                                                                                                                                                  |

| LOGIC Input High Voltage $(V_{IH})$ Input Low Voltage $(V_{IL})$ Input Leakage Current Input Capacitance $(V_{OH})$ $(V_{OL})$ Three-State Leakage Current | 2<br>0.8<br>1<br>20<br>4.5<br>0.4<br>1 | V min V max  µA max  pF typ V min V max  µA max              | $I_{SOURCE}$ Current = 20 $\mu$ A, $V_{DD}$ = 5 V $I_{SINK}$ Current = 400 $\mu$ A, $V_{DD}$ = 5 V                                                                                                                                                                                                        |

| CONVERSION RATE Conversion Time/Channel                                                                                                                    | 40                                     | CLK Cycles                                                   |                                                                                                                                                                                                                                                                                                           |

| CONVST<br>Pulsewidth                                                                                                                                       | 2                                      | CLK Cycles min                                               |                                                                                                                                                                                                                                                                                                           |

| ANALOG INPUTS Nominal Input Level Input Current Input Capacitance                                                                                          | 0-5<br>100<br>10                       | V<br>μA<br>pF                                                | VIN1, VIN2, VIN3, AUX0–AUX3                                                                                                                                                                                                                                                                               |

| SYSTEM CLOCK                                                                                                                                               | 6.25-12.5                              | MHz                                                          |                                                                                                                                                                                                                                                                                                           |

| POWER REQUIREMENTS $V_{DD}$ $I_{DD}$                                                                                                                       | 5<br>10                                | V dc<br>mA max                                               |                                                                                                                                                                                                                                                                                                           |

– 2 – REV. B

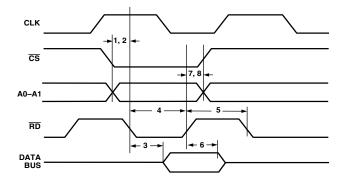

Table I. AD7861 Timing Parameters ( $T_A = -40^{\circ}\text{C}$  to +85°C and  $V_{DD} = +5 \text{ V}$  unless otherwise noted)

| Number | Symbol                    | AD7861 Timing Requirements                               | Min                       | Max | Units |

|--------|---------------------------|----------------------------------------------------------|---------------------------|-----|-------|

| 1      | t <sub>su</sub> csb_rdb   | CS Low Before Falling Edge of RD                         | 0                         | _   | ns    |

| 2      | t <sub>su</sub> addr_rdb  | ADDR Valid Before Falling Edge of $\overline{\text{RD}}$ | 0                         | _   | ns    |

| 3      | t <sub>dly</sub> rdb_data | DATA Valid After Falling Edge of RD                      | _                         | 25  | ns    |

| 4      | t <sub>pwl</sub> rdb      | RD Pulsewidth, Low                                       | 25                        | _   | ns    |

| 5      | t <sub>pwh</sub> rdb      | RD Pulsewidth, High                                      | 25                        | _   | ns    |

| 6      | t <sub>hd</sub> rdb_data  | DATA Hold After Rising Edge of $\overline{\text{RD}}$    | 10                        | _   | ns    |

| 7      | t <sub>hd</sub> rdb_addr  | ADDR Hold After Rising Edge of $\overline{\text{RD}}$    | 0                         | _   | ns    |

| 8      | t <sub>hd</sub> rdb_csb   | CS Hold After Rising Edge of RD                          | 0                         | _   | ns    |

| 9      | t <sub>per</sub> clk      | CLK Period                                               | 80                        | 160 | ns    |

| 10     | t <sub>pwh</sub> clk      | CLK Pulsewidth, High                                     | 20                        | _   | ns    |

| 11     | t <sub>pwl</sub> clk      | CLK Pulsewidth, Low                                      | 20                        | _   | ns    |

| 12     | t <sub>pwl</sub> resetb   | RESET Pulsewidth, Low                                    | $2 \times \text{tperclk}$ | _   | ns    |

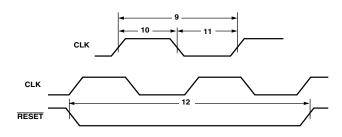

Figure 1. Clock and Reset Timing

Figure 2. Write Cycle Timing Diagram

#### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage $(V_{DD})$            | 0.3 V to +7.0 V              |

|--------------------------------------|------------------------------|

| Digital Input Voltage                | $-0.3 \text{ V to V}_{DD}$   |

| Analog Input Voltage                 | $-0.3 \text{ V to V}_{DD}$   |

| Analog Reference Input Voltage       | $-0.3 \text{ V to V}_{DD}$   |

| Digital Output Voltage Swing         | $-0.3 \text{ V}$ to $V_{DD}$ |

| Analog Reference Output Swing        | $-0.3 \text{ V to V}_{DD}$   |

| Operating Temperature                | 40°C to +85°C                |

| Lead Temperature (Soldering, 10 sec) | +280°C                       |

|                                      |                              |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model    | Temperature Range | Package Option |

|----------|-------------------|----------------|

| AD7861AP | −40°C to +85°C    | P-44A          |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7861 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. B –3–

### **AD7861**

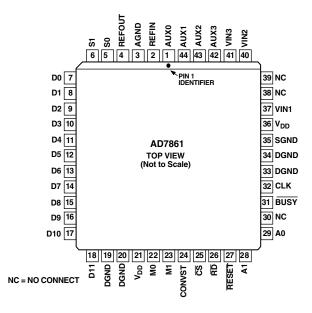

#### PIN DESCRIPTION

| Pin   | Mnemonic               | Type | Description                            |

|-------|------------------------|------|----------------------------------------|

| 1     | AUX0                   | I/P  | Auxiliary Input 0                      |

| 2     | REFIN                  | I/P  | Analog Reference Input                 |

| 3     | AGND                   | GND  | Analog Ground                          |

| 4     | REFOUT                 | O/P  | Internal 2.5 Analog Reference          |

| 5     | S0                     | I/P  | Aux Channel Select 0                   |

| 6     | S1                     | I/P  | Aux Channel Select 1                   |

| 7     | D0                     | O/P  | Data Bit 0 LSB (Tied Low)              |

| 8     | D1                     | O/P  | Data Bit 1                             |

| 9     | D2                     | O/P  | Data Bit 2                             |

| 10    | D3                     | O/P  | Data Bit 3                             |

| 11    | D4                     | O/P  | Data Bit 4                             |

| 12    | D5                     | O/P  | Data Bit 5                             |

| 13    | D6                     | O/P  | Data Bit 6                             |

| 14    | D7                     | O/P  | Data Bit 7                             |

| 15    | D8                     | O/P  | Data Bit 8                             |

| 16    | D9                     | O/P  | Data Bit 9                             |

| 17    | D10                    | O/P  | Data Bit 10                            |

| 18    | D11                    | O/P  | Data Bit 11, MSB                       |

| 19    | DGND                   | GND  | Logic Ground                           |

| 20    | DGND                   | GND  | Logic Ground                           |

| 21    | $V_{ m DD}$            | SUP  | +5 V Digital Supply                    |

| 22    | <b>M</b> 0             | I/P  | Conversion Mode Select 0               |

| 23    | M1                     | I/P  | Conversion Mode Select 1               |

| 24    | CONVST                 | I/P  | A/D Conversion Start                   |

| 25    | CS                     | I/P  | Chip Select                            |

| 26    | $\overline{\text{RD}}$ | I/P  | Read Input                             |

| 27    | RESET                  | I/P  | Chip Reset                             |

| 28    | A1                     | I/P  | Register Address Select 1              |

| 29    | A0                     | I/P  | Register Address Select 0              |

| 30    | NC                     | NC   | No Connect                             |

| 31    | BUSY                   | O/P  | Busy, Conversion in Process            |

| 32    | CLK                    | I/P  | External Clock Input 6.25 MHz-12.5 MHz |

| 33-34 | DGND                   | GND  | Logic Ground                           |

| 35    | SGND                   | GND  | Signal Ground                          |

| 36    | $V_{\mathrm{DD}}$      | SUP  | +5 V Analog Supply                     |

| 37    | VIN1                   | I/P  | Analog Input 1                         |

| 38-39 | NC                     | NC   | No Connect                             |

| 40    | VIN2                   | I/P  | Analog Input 2                         |

| 41    | VIN3                   | I/P  | Analog Input 3                         |

| 42    | AUX3                   | I/P  | Auxiliary Input 3                      |

| 43    | AUX2                   | I/P  | Auxiliary Input 2                      |

| 44    | AUX1                   | I/P  | Auxiliary Input 1                      |

#### PIN CONFIGURATION

| Pin Types        | Pin Types        |

|------------------|------------------|

| I/P = Input Pin  | GND = Ground Pin |

| O/P = Output Pin | SUP = Supply Pin |

REV. B

-4-

#### ANALOG INPUT BLOCK

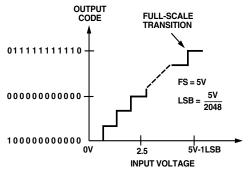

The AD7861 is an 11-bit resolution, successive approximation analog-to-digital (A/D) converter with twos complement output data format. The analog input range is 0 V–5 V with a 2.5 V reference as defined by the reference input pin (REFIN). The AD7861 has an internal 2.5 V  $\pm$  5% reference, which is utilized by connecting the reference output pin (REFOUT) to the REFIN pin.

The A/D conversion time is determined by the system clock frequency, which can range from 6.25 MHz to 12.5 MHz. Forty clock cycles are required to complete each conversion. There is a 4-channel simultaneous sample and hold amplifier (SHA) at the AD7861 input stage. This allows up to 4 channels to be simultaneously held and sequentially digitized. The SHA acquisition time is 20 clock cycles and is independent of the number of channels sampled.

The minimum throughput time can be calculated as follows:

$$t_{AA} = t_{SHA} + (n \times t_{CONV})$$

where  $t_{AA}$  = analog acquisition time,  $t_{SHA}$  = SHA acquisition time, n = # channels,  $t_{CONV}$  = conversion time per channel (40 clock cycles).

A/D conversions are initiated by an external analog sample clock pin (CONVST).

The CONVST input can be run asynchronous to the AD7861 system clock. When CONVST is run asynchronous from CLK, the falling edge of CLK subsequent to CONVST high initiates the conversion.

#### **BUSY**

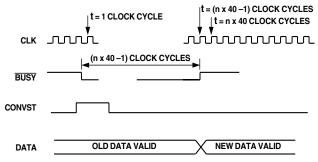

The AD7861  $\overline{BUSY}$  pin goes low at the start of conversion, and remains low for 40 clock cycles per channel. When  $\overline{BUSY}$  goes high, this indicates that the output data buffers have been updated. Data from the previous conversion can be read up to  $(n \times 40 - 1)$  clock cycles after the start of conversion (n = number of channels converted). Refer to Figure 3.

Figure 3. Busy Pulse Timing

#### **CHANNEL SELECTION**

Determining which channels are converted is dependent on the settings of M0 and M1. The available channel combinations are:

| M1 | M0 | Channels Converted    |

|----|----|-----------------------|

| 0  | 0  | VIN2, VIN3            |

| 0  | 1  | VIN2, VIN3, AUX       |

| 1  | 0  | VIN1, VIN2, VIN3      |

| 1  | 1  | VIN1, VIN2, VIN3, AUX |

The user must select which channels to convert using M0/M1, a minimum of two clock cycles before the start of conversion.

The AD7861 provides 4 auxiliary input channels which can be individually multiplexed into the auxiliary ADC channel. Pins S0/S1 are used to multiplex these auxiliary channels according to the following table. It is important to note that the ADC performs a series of conversions based on the input voltage on each pin (including the AUX pin) at the start of the CONVST conversion pulse. The user must select the auxiliary channel using S0/S1 a minimum of two clock cycles before the start of the conversion sequence.

| <b>S</b> 1 | S0 | Channel Selected |

|------------|----|------------------|

| 0          | 0  | AUX0             |

| 0          | 1  | AUX1             |

| 1          | 0  | AUX2             |

| 1          | 1  | AUX3             |

#### **DIGITAL INTERFACE**

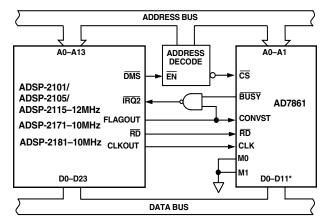

The AD7861 is designed to interface with the ADSP-21xx family of DSPs. The 12-bit parallel interface can also be used with other DSPs and microcontrollers.

The 11-bit A/D conversion output occupies the 11 most significant bits of the 12-bit interface. The LSB (Data Bit 0) is tied low.

#### **REGISTER BASED INPUT/OUTPUT**

To facilitate integration into most designs, a register based input/output structure is provided. These registers can be memory mapped into the user's system along with other memory mapped peripherals.

#### REGISTER ADDRESSING

Two address lines (A0 through A1) are used in conjunction with control lines ( $\overline{CS}$ ,  $\overline{RD}$ ) to select registers VIN1, VIN2, VIN3, or AUX. These control lines are active low. Timing and logical sense is as for the ADSP-2100 family.

| Pin      | Function                                     |

|----------|----------------------------------------------|

| CS<br>RD | Enables the AD7861 Register Interface        |

| RD       | Places the Internal Register on the Data Bus |

#### REGISTER LISTING

The output of each channel is stored in its respective register. The symbolic names and address locations are listed in the following table.

| Name | A1 | A0 | Register Function                  |

|------|----|----|------------------------------------|

| VIN1 | 0  | 0  | A/D Conversion Result Channel VIN1 |

| VIN2 | 0  | 1  | A/D Conversion Result Channel VIN2 |

| VIN3 | 1  | 0  | A/D Conversion Result Channel VIN3 |

| AUX  | 1  | 1  | A/D Conversion Result Channel AUX  |

REV. B \_5\_

#### AD7861

AUX

#### **DESCRIPTION OF THE REGISTERS**

VIN1, VIN2, VIN3 These registers contain the results from

the conversion of the analog input voltages. In the AD7861, this register contains the

conversion result of the auxiliary channel

which had been selected by S0, S1.

#### **Reading Results**

The A/D conversion results for channels VIN1, VIN2, VIN3 and AUX are stored in the VIN1, VIN2, VIN3 and AUX registers respectively. The twos complement data is left justified and the LSB (Data Bit 0) is set to zero. The relationship between input voltage and output coding is shown in Figure 4.

Figure 4. AD7861 Transfer Function

#### Power Supply Connections and Setup

The nominal power supply level ( $V_{DD}$ ) is +5 V  $\pm$  5%. The positive power supply (VDD) should be connected to Pins 21 and 36. The SGND and DGND pins should be star point connected to AGND at a point close to the AD7861.

Power supplies should be bypassed at the power pins using a 0.1 µF capacitor. A 200 nF capacitor should also be connected between REFIN and SGND.

#### DIGITAL SIGNAL PROCESSOR INTERFACING

The AD7861 A/D converter is designed to be easily interfaced to Analog Devices' family of Digital Signal Processors (DSPs). Figure 5 shows the interface between the AD7861 and the ADSP-2101/2105/2115 16-bit fixed point DSP, and the ADSP-2171 and ADSP-2181 DSP Microcomputers. FLAGOUT from the DSP is used to initiate the AD7861 conversion and is also used in conjunction with the BUSY signal to provide an end of conversion interrupt for the DSP. With M0 and M1 tied low, the AD7861 is set up in the VIN2, VIN3 channel conversion mode. By mapping the 12-bit AD7861 data bus into the top 12 bits of the DSP data bus (D12-D23), full-scale outputs from the AD7861 can be represented as  $\pm 1.0$  in fixed point arithmetic.

The AD7861 can operate with a clock frequency in the range of 6.25 MHz to 12.5 MHz. For the ADSP-2101/2105/2115 the CLKOUT frequency is the system clock frequency. In the case of the ADSP-2171/2181, the system clock is internally scaled, a 10 MHz system clock will result in a 20 MHz CLKOUT frequency. If CLKOUT from the ADSP-2171/2181 is above 12.5 MHz, then an external clock divide down circuit will be necessary.

Figure 5. ADI Digital Signal Processor/Microcomputer Interface

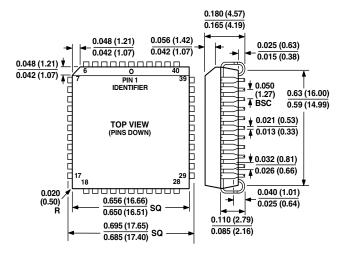

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 44-Lead Plastic Leadless Chip Carrier (P-44A)

-6-

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию .

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331