TOSHIBA CDMOS Integrated Circuit Silicon Monolithic

## TC62D748CFNAG

#### 16-Output Constant Current LED Driver

The TC62D748CFNAG is a constant-current driver for LED and LED display lighting applications.

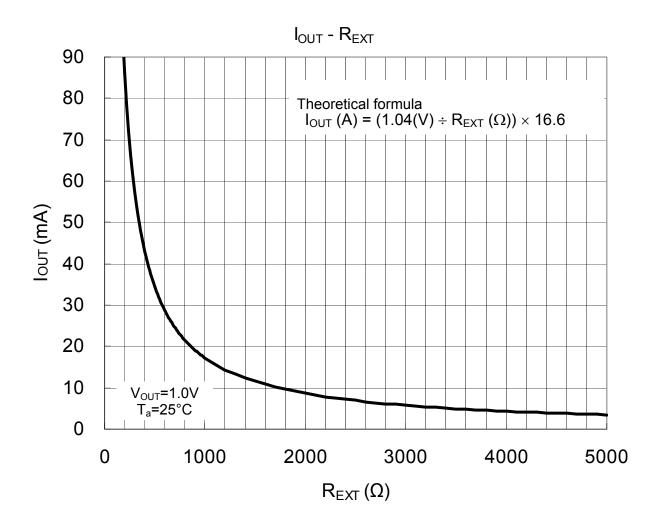

The output current from each of the 16 outputs is programmable via a single external resistor.

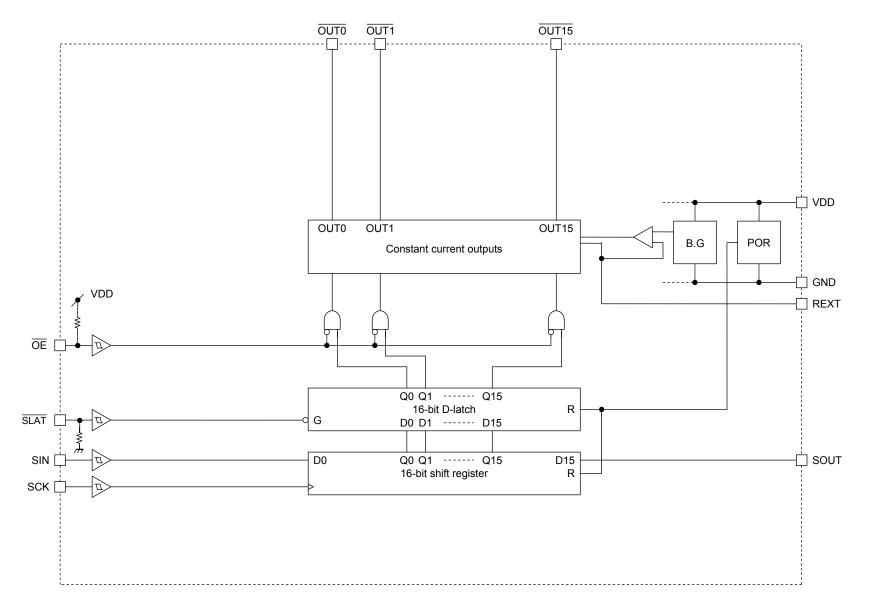

The TC62D748CFNAG contains a 16-channel shift register, a 16-channel latch, a 16-channel AND gate and a 16-channel constant-current output.

Fabricated with a CMOS process, the TC62D748CFNAG allows high-speed data transfer.

It operates with a 3.3- or 5-V power supply.

Weight: 0.14 g (Typ.)

#### Features

| ٠ | Supply voltages                       | $V_{DD} = 3.3 \text{ V to } 5.0 \text{ V}$                                                                 |

|---|---------------------------------------|------------------------------------------------------------------------------------------------------------|

| ٠ | 16-output built-in                    |                                                                                                            |

| ٠ | Output current setup range            | $: I_{OUT} = 1.5 \text{ to } 90 \text{ mA}$                                                                |

| ٠ | Constant current output accuracy (@   | $R_{EXT} = 1.2 \text{ k}\Omega$ , $V_{OUT} = 1.0 \text{ V}$ , $V_{DD} = 3.3 \text{ V}$ , $5.0 \text{ V}$ ) |

|   |                                       | $ m \stackrel{<}{\cdot}$ S rank ; between outputs ± 1.5 % (max)                                            |

|   |                                       | $ m \stackrel{<}{\cdot}$ S rank ; between devices: ± 1.5 % (max)                                           |

|   |                                       | $\therefore$ N rank ; between outputs ± 2.5 % (max)                                                        |

|   |                                       | $\therefore$ N rank ; between devices: $\pm 2.5$ % (max)                                                   |

| ٠ | Output voltage                        | $V_{OUT} = 17 V (max)$                                                                                     |

| ٠ | High-speed output switching           | : $t_{WOE(L)} = 25$ ns (min), $t_{or} = 30$ ns (typ.), $t_{of} = 10$ ns (typ.)                             |

|   |                                       | There is TC62D749 as an output switching high-speed version of this product.                               |

| ٠ | I/O interface                         | : CMOS interfaces (Schmitt trigger input)                                                                  |

| ٠ | Data transfer frequency               | $f_{SCK} = 25 \text{ MHz} (\text{max})$                                                                    |

| ٠ | Operation temperature range           | $: T_{opr} = -40 \text{ to } 85 ^{\circ}\text{C}$                                                          |

| ٠ | Power-on-reset function built-in. (Wh | nen the power supply is turned on, internal data is reset)                                                 |

|   | D I                                   |                                                                                                            |

• Package : P-SSOP24-0409-0.64-001

For detailed part naming conventions, contact your local Toshiba sales representative or distributor.

### **Block Diagram**

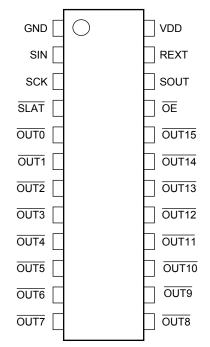

## Pin Assignment (top view)

Short circuiting an output pin to a power supply pin (Power-supply voltage  $V_{DD}$  and LED anode power supply), or short-circuiting the REXT pin to the GND pin will likely exceed the rating, which in turn may result in smoldering and/or permanent damage. Please keep this in mind when determining the wiring layout for the power supply and GND pins.

| Pin No | Pin Name | I/O | Function                                                                                                                                                                                  |

|--------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GND      |     | GND terminal                                                                                                                                                                              |

| 2      | SIN      | I   | Serial data input terminal                                                                                                                                                                |

| 3      | SCK      | I   | Serial data transfer clock input terminal                                                                                                                                                 |

| 4      | SLAT     | I   | Latch signal input pin.                                                                                                                                                                   |

| 5      | OUT0     | 0   | Constant-current output terminal                                                                                                                                                          |

| 6      | OUT1     | 0   | Constant-current output terminal                                                                                                                                                          |

| 7      | OUT2     | 0   | Constant-current output terminal                                                                                                                                                          |

| 8      | OUT3     | 0   | Constant-current output terminal                                                                                                                                                          |

| 9      | OUT4     | 0   | Constant-current output terminal                                                                                                                                                          |

| 10     | OUT5     | 0   | Constant-current output terminal                                                                                                                                                          |

| 11     | OUT6     | 0   | Constant-current output terminal                                                                                                                                                          |

| 12     | OUT7     | 0   | Constant-current output terminal                                                                                                                                                          |

| 13     | OUT8     | 0   | Constant-current output terminal                                                                                                                                                          |

| 14     | OUT9     | 0   | Constant-current output terminal                                                                                                                                                          |

| 15     | OUT10    | 0   | Constant-current output terminal                                                                                                                                                          |

| 16     | OUT11    | 0   | Constant-current output terminal                                                                                                                                                          |

| 17     | OUT12    | 0   | Constant-current output terminal                                                                                                                                                          |

| 18     | OUT13    | 0   | Constant-current output terminal                                                                                                                                                          |

| 19     | OUT14    | 0   | Constant-current output terminal                                                                                                                                                          |

| 20     | OUT15    | 0   | Constant-current output terminal                                                                                                                                                          |

| 21     | ŌĒ       | I   | An output current enable signal input terminal<br>In "H" level input, outputs are turned off compulsorily.<br>In "L" level input, outputs are ON/OFF controlled according to serial data. |

| 22     | SOUT     | 0   | Serial data output terminal.                                                                                                                                                              |

| 23     | REXT     |     | An external resistance for an output current setup is connected between this terminal and ground.                                                                                         |

| 24     | VDD      |     | Power supply terminal                                                                                                                                                                     |

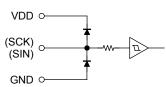

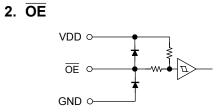

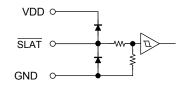

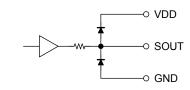

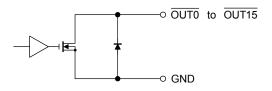

### I/O Equivalent Circuits

1. SCK, SIN

3. SLAT

4. SOUT

### 5. $\overline{\text{OUT0}}$ to $\overline{\text{OUT15}}$

#### Truth Table

| SCK           | SLAT        | ŌĒ | SIN    | OUT0 OUT7 OUT15 (Note1) | SOUT    |

|---------------|-------------|----|--------|-------------------------|---------|

|               | Н           | L  | Dn     | Dn Dn – 7 Dn – 15       | Dn – 15 |

|               | L           | L  | Dn + 1 | No Change               | Dn – 14 |

|               | Н           | L  | Dn + 2 | Dn + 2 Dn – 5 Dn – 13   | Dn – 13 |

| $\neg$        | - (Note2)   | L  | Dn + 3 | Dn + 2 Dn – 5 Dn – 13   | Dn – 13 |

| $\overline{}$ | – (Note2) H |    | Dn + 3 | OFF                     | Dn – 13 |

Note1: When  $\overline{OUT0}$  to  $\overline{OUT15}$  output pins are set to "H" the respective output will be ON and when set to "L" the respective output will be OFF.

Note2: "-" is irrelevant to the truth table.

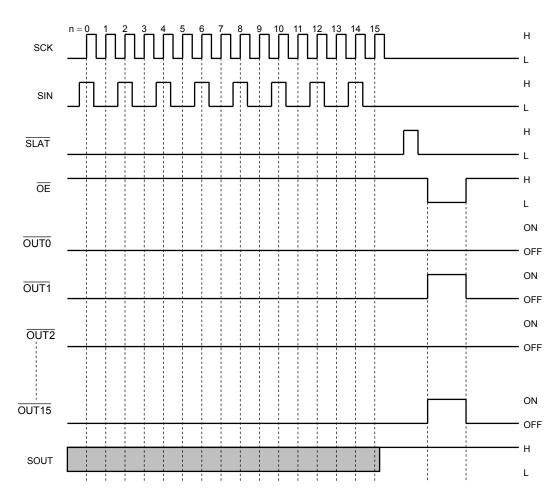

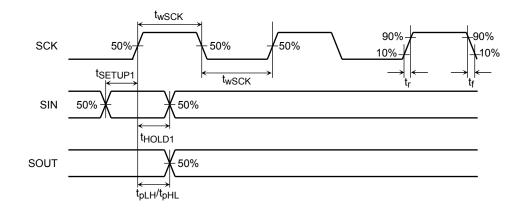

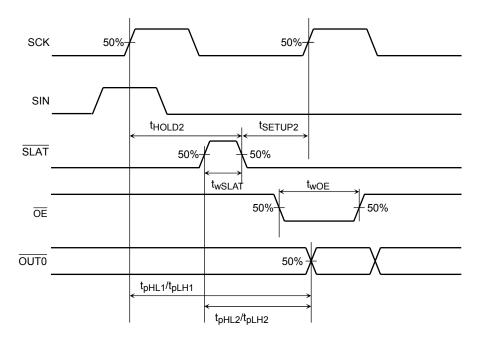

#### Timing Diagram

• The latch circuit is a leveled-latch circuit. Please exercise precaution as it is not triggered-latch circuit.

• Keep the  $\overline{SLAT}$  pin is set to "L" to enable the latch circuit to hold data. In addition, when the  $\overline{SLAT}$  pin is set to "H" the latch circuit does not hold data. The data will instead pass onto output. When the  $\overline{OE}$  pin is set to "L" the  $\overline{OUT0}$  to  $\overline{OUT15}$  output pins will go ON and OFF in response to the data. In addition, when the  $\overline{OE}$  pin is set to "H" all the output pins will be forced OFF regardless of the data.

• This product can use 3.3V and 5.0V power supply, but power supply and input (SCK/SIN/ $\overline{SLAT} / \overline{OE}$ ) must use same voltage.

## Absolute Maximum Ratings (T<sub>a</sub> = 25°C)

| Characteristics       | Symbol           | Rating (Note1)                        | Unit |

|-----------------------|------------------|---------------------------------------|------|

| Supply voltage        | V <sub>DD</sub>  | -0.3 to 6.0                           | V    |

| Output current        | I <sub>OUT</sub> | 95                                    | mA   |

| Logic input voltage   | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3 (Note2) | V    |

| Output voltage        | V <sub>OUT</sub> | –0.3 to 17                            | V    |

| Operating temperature | T <sub>opr</sub> | -40 to 85                             | °C   |

| Storage temperature   | T <sub>stg</sub> | –55 to 150                            | °C   |

| Thermal resistance    | Rth(j-a)         | 80.07                                 | °C/W |

| Power dissipation     | PD               | 1.56 (Note3)                          | W    |

Note1: Voltage is ground referenced.

Note2: Do not exceed 6.0V.

Note3: The power dissipation decreases the reciprocal of the saturated thermal resistance (1/ Rth(j-a)) for each degree (1°C) that the ambient temperature is exceeded (Ta = 25°C).

#### **Operating Conditions**

#### DC Items (Unless otherwise specified, $V_{DD} = 3.0$ to 5.5 V, $T_a = -40^{\circ}$ C to 85°C)

| Characteristics                | Symbol          | Test Conditions                                                 | Min                 | Тур. Мах |                     | Unit |

|--------------------------------|-----------------|-----------------------------------------------------------------|---------------------|----------|---------------------|------|

| Supply voltage                 | V <sub>DD</sub> |                                                                 | 3.0                 | _        | 5.5                 | V    |

| High level logic input voltage | V <sub>IH</sub> | Test terminal are SIN, SCK, $\overline{SLAT}$ , $\overline{OE}$ | $0.7 \times V_{DD}$ |          | V <sub>DD</sub>     | V    |

| Low level logic input voltage  | V <sub>IL</sub> | Test terminal are SIN, SCK, SLAT, OE                            | GND                 |          | $0.3 \times V_{DD}$ | V    |

| High level SOUT output current | I <sub>OH</sub> | _                                                               | _                   | _        | -1                  | mA   |

| Low level SOUT output current  | I <sub>OL</sub> |                                                                 | _                   |          | 1                   | mA   |

| Constant current output        | IOUT            | Test terminal is OUTn                                           | 1.5                 | _        | 90                  | mA   |

## AC Items (Unless otherwise specified, $V_{DD} = 3.0$ to 5.5 V, $T_a = -40^{\circ}$ C to 85°C)

| Characteristics                | Symbol             | Test<br>Circuits | Test Conditions | Min | Тур. | Max | Unit |

|--------------------------------|--------------------|------------------|-----------------|-----|------|-----|------|

| Serial data transfer frequency | fsck               | 6                | —               | _   |      | 25  | MHz  |

| Serial data Hold time          | t <sub>HOLD1</sub> | 6                | —               | 5   | —    |     | ns   |

| Serial data nord time          | t <sub>HOLD2</sub> | 6                | —               | 5   | —    |     | ns   |

| Serial data Setup time         | tSETUP1            | 6                | —               | 5   | —    |     | ns   |

| Serrar Gata Setup time         | tSETUP2            | 6                | —               | 5   |      |     | ns   |

| Maximum clock rise time        | tr                 | 6                | (Note1)         |     | _    | 500 | ns   |

| Maximum clock fall time        | t <sub>f</sub>     | 6                | (Note1)         | _   | —    | 500 | ns   |

Note1: If the device is connected in a cascade and the tr/tf of the clock waveform increases due to deceleration of the clock waveform, it may not be possible to achieve the timing required for data transfer. Please keep these timing conditions in mind when designing your application.

## Electrical Characteristics (Unless otherwise specified, $V_{DD} = 3.3V$ , $T_a = 25^{\circ}C$ )

| Characteristics                                               | Symbol               | Test<br>Circuits | Test Conditions                                                                                | Min                      | Тур. | Max  | Unit |

|---------------------------------------------------------------|----------------------|------------------|------------------------------------------------------------------------------------------------|--------------------------|------|------|------|

| High level<br>SOUT output voltage                             | V <sub>OH</sub>      | 1                | I <sub>OH</sub> = -1 mA                                                                        | V <sub>DD</sub> -<br>0.4 | _    | _    | V    |

| Low level<br>SOUT output voltage                              | V <sub>OL</sub>      | 1                | I <sub>OL</sub> = +1 mA                                                                        | _                        | _    | 0.4  | V    |

| High level logic input current                                | IIН                  | 2                | $V_{IN} = V_{DD}, \overline{OE}$ , SIN, SCK                                                    |                          | _    | 1    | μA   |

| Low level logic input current                                 | ۱ <sub>IL</sub>      | 3                | V <sub>IN</sub> = GND, SLAT , SIN, SCK                                                         |                          | _    | -1   | μΑ   |

| Power supply current                                          | I <sub>DD</sub>      | 4                | $R_{EXT}$ = 1.2 k $\Omega$ , All output on                                                     |                          |      | 8.0  | mA   |

| Output current                                                | IOUT                 | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 kΩ, 1 output on                 | _                        | 14.4 | _    | mA   |

| Constant current error(Ch to Ch)<br>( S r a n k )             | $\Delta I_{OUT(Ch)}$ | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 kΩ, 1 output on                 | _                        | _    | ±1.5 | %    |

| Constant current error(IC to IC)<br>( S r a n k )             | ∆lout(IC)            | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on        | _                        |      | ±1.5 | %    |

| Constant current error(Ch to Ch)<br>( N r a n k )             | $\Delta I_{OUT(Ch)}$ | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 kΩ, 1 output on                 | _                        |      | ±2.5 | %    |

| Constant current error(IC to IC)<br>( N r a n k )             | ∆lout(IC)            | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on        | _                        |      | ±2.5 | %    |

| Output OFF leak current                                       | lок                  | 5                | V <sub>DD</sub> = 3.3 V, V <sub>OUT</sub> = 17 V,<br>R <sub>EXT</sub> = 1.2 kΩ                 | _                        |      | 0.5  | μΑ   |

| Constant current output power supply<br>voltage regulation    | %V <sub>DD</sub>     | 5                | $V_{DD}$ = 3.0 to 3.6 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on |                          | ±1   | ±5   | %/V  |

| Constant current output output voltage<br>r e g u l a t i o n | %V <sub>OUT</sub>    | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 to 3.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on | _                        | ±0.1 | ±0.5 | %/V  |

| Pull-up resistor                                              | R <sub>(Up)</sub>    | 3                | ŌĒ                                                                                             | 400                      | 500  | 600  | kΩ   |

| Pull-down resistor                                            | R (Down)             | 2                | SLAT                                                                                           | 400                      | 500  | 600  | kΩ   |

## Electrical Characteristics (Unless otherwise specified, $V_{DD} = 5.0V$ , Ta = 25°C)

|                                                               | -                     |                  | -                                                                                              |                          |      |      |      |

|---------------------------------------------------------------|-----------------------|------------------|------------------------------------------------------------------------------------------------|--------------------------|------|------|------|

| Characteristics                                               | Symbol                | Test<br>Circuits | Test Conditions                                                                                | Min                      | Тур. | Max  | Unit |

| High level<br>SOUT output voltage                             | V <sub>OH</sub>       | 1                | I <sub>OH</sub> = -1 mA                                                                        | V <sub>DD</sub> -<br>0.4 | _    | _    | V    |

| Low level<br>SOUT output voltage                              | V <sub>OL</sub>       | 1                | I <sub>OL</sub> = +1 mA                                                                        |                          | _    | 0.4  | V    |

| High level logic input current                                | I <sub>IH</sub>       | 2                | $V_{IN} = V_{DD}, \overline{OE}$ , SIN, SCK                                                    |                          | _    | 1    | μA   |

| Low level logic input current                                 | ١ <sub>IL</sub>       | 3                | $V_{IN} = GND, \overline{SLAT}$ , SIN, SCK                                                     |                          | _    | -1   | μA   |

| Power supply current                                          | I <sub>DD</sub>       | 4                | $R_{EXT}$ = 1.2 k $\Omega$ , All output on                                                     | _                        | _    | 8.0  | mA   |

| Output current                                                | I <sub>OUT</sub>      | 5                | $V_{DD}$ = 5.0 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on        |                          | 14.4 | _    | mA   |

| Constant current error(Ch to Ch)<br>( S r a n k )             | $\Delta I_{OUT(Ch)}$  | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 kΩ, 1 output on                 |                          | _    | ±1.5 | %    |

| Constant current error(IC to IC)<br>( S r a n k )             | ∆lout(IC)             | 5                | $V_{DD}$ = 3.3 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 kΩ, 1 output on                 |                          | _    | ±1.5 | %    |

| Constant current error(Ch to Ch)<br>( N r a n k )             | ∆l <sub>OUT(Ch)</sub> | 5                | $V_{DD}$ = 5.0 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on        |                          |      | ±2.5 | %    |

| Constant current error(IC to IC)<br>( N r a n k )             | ∆lout(IC)             | 5                | $V_{DD}$ = 5.0 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on        |                          | _    | ±2.5 | %    |

| Output OFF leak current                                       | I <sub>OK</sub>       | 5                | V <sub>DD</sub> = 5.0 V, V <sub>OUT</sub> = 17 V,<br>R <sub>EXT</sub> = 1.2 kΩ                 |                          |      | 0.5  | μA   |

| Constant current output power supply<br>voltage regulation    | %V <sub>DD</sub>      | 5                | $V_{DD}$ = 4.5 to 5.5 V, $V_{OUT}$ = 1.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on |                          | ±1   | ±5   | %/V  |

| Constant current output output voltage<br>r e g u l a t i o n | %V <sub>OUT</sub>     | 5                | $V_{DD}$ = 5.0 V, $V_{OUT}$ = 1.0 to 3.0 V,<br>R <sub>EXT</sub> = 1.2 k $\Omega$ , 1 output on |                          | ±0.1 | ±0.5 | %/V  |

| Pull-up resistor                                              | R <sub>(Up)</sub>     | 3                | ŌĒ                                                                                             | 400                      | 500  | 600  | kΩ   |

| Pull-down resistor                                            | R <sub>(Down)</sub>   | 2                | SLAT                                                                                           | 400                      | 500  | 600  | kΩ   |

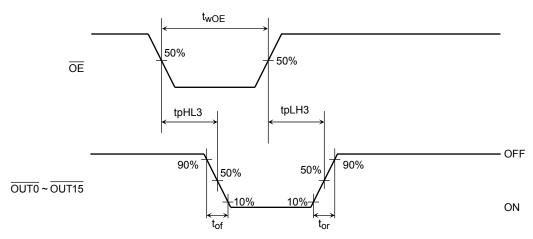

## Switching Characteristics (Unless otherwise specified, $V_{DD}$ = 3.3V, $T_a$ = 25°C)

| Characteristics   |             | Symbol              | Test<br>Circuits | Test Conditions                                              | Min | Тур. | Max | Unit |

|-------------------|-------------|---------------------|------------------|--------------------------------------------------------------|-----|------|-----|------|

|                   | SCK- OUTO   | t <sub>pLH1</sub>   | 6                | $\overline{\text{SLAT}}$ = "H", $\overline{\text{OE}}$ = "L" | _   | 50   | 65  | ns   |

|                   | SLAT - OUTO | t <sub>pLH2</sub>   | 6                | OE = "L"                                                     | _   | 50   | 65  | ns   |

|                   | OE - OUTO   | t <sub>pLH3</sub>   | 6                | $\overline{\text{SLAT}}$ = "H"                               |     | 50   | 65  | ns   |

| Propagation delay | SCK-SOUT    | t <sub>pLH</sub>    | 6                | C <sub>L</sub> =10.5 pF                                      | 10  | 20   | 35  | ns   |

| t i m e           | SCK- OUTO   | t <sub>pHL1</sub>   | 6                | $\overline{\text{SLAT}}$ = "H", $\overline{\text{OE}}$ = "L" |     | 30   | 40  | ns   |

|                   | SLAT - OUTO | t <sub>pHL2</sub>   | 6                | OE = "L"                                                     |     | 30   | 40  | ns   |

|                   | OE - OUTO   | t <sub>pHL3</sub>   | 6                | $\overline{\text{SLAT}}$ = "H"                               |     | 30   | 40  | ns   |

|                   | SCK-SOUT    | t <sub>pHL</sub>    | 6                | C <sub>L</sub> =10.5 pF                                      | 10  | 20   | 35  | ns   |

| Output ri         | se time     | t <sub>or</sub>     | 6                | 10 to 90% of voltage waveform                                |     | 30   | 45  | ns   |

| Output fa         | all time    | t <sub>of</sub>     | 6                | 90 to 10% of voltage waveform                                |     | 10   | 20  | ns   |

| Enable pul        | se width    | t <sub>wOE(L)</sub> | 6                | OE = "L"                                                     | 25  | _    |     | ns   |

|                   | se wrath    | t <sub>wOE(H)</sub> | 6                | OE = "H"                                                     | 50  | —    | _   | 113  |

| Clock puls        | se width    | twSCK               | 6                | SCK = "H" or "L"                                             | 20  | _    | _   | ns   |

| Latch puls        | se width    | t <sub>wSLAT</sub>  | 6                | SLAT = "H"                                                   | 20  | —    | _   | ns   |

## Switching Characteristics (Unless otherwise specified, $V_{DD}=5.0V,\,T_a=25^\circ\text{C})$

| Characteristics   |             | Symbol              | Test<br>Circuits | Test Conditions                                              | Min | Тур. | Max | Unit |

|-------------------|-------------|---------------------|------------------|--------------------------------------------------------------|-----|------|-----|------|

|                   | SCK- OUTO   | t <sub>pLH1</sub>   | 6                | $\overline{\text{SLAT}}$ = "H", $\overline{\text{OE}}$ = "L" |     | 50   | 65  | ns   |

|                   | SLAT - OUTO | t <sub>pLH2</sub>   | 6                | OE = "L"                                                     | _   | 50   | 65  | ns   |

|                   | OE - OUTO   | t <sub>pLH3</sub>   | 6                | $\overline{\text{SLAT}}$ = "H"                               | _   | 50   | 65  | ns   |

| Propagation delay | SCK-SOUT    | t <sub>pLH</sub>    | 6                | C <sub>L</sub> =10.5 pF                                      | 10  | 20   | 35  | ns   |

| t i m e           | SCK-OUTO    | t <sub>pHL1</sub>   | 6                | $\overline{\text{SLAT}}$ = "H", $\overline{\text{OE}}$ = "L" |     | 30   | 40  | ns   |

|                   | SLAT - OUTO | t <sub>pHL2</sub>   | 6                | OE = "L"                                                     |     | 30   | 40  | ns   |

|                   | OE - OUTO   | t <sub>pHL3</sub>   | 6                | SLAT = "H"                                                   |     | 30   | 40  | ns   |

|                   | SCK-SOUT    | t <sub>pHL</sub>    | 6                | C <sub>L</sub> =10.5 pF                                      | 10  | 20   | 35  | ns   |

| Output ri         | se time     | t <sub>or</sub>     | 6                | 10 to 90% of voltage waveform                                |     | 30   | 45  | ns   |

| Output fa         | ıll time    | t <sub>of</sub>     | 6                | 90 to 10% of voltage waveform                                |     | 10   | 20  | ns   |

| Enable pul        | se width    | t <sub>wOE(L)</sub> | 6                | OE = "L"                                                     | 25  | _    | _   | ns   |

| Enable pulse wid  |             | t <sub>wOE(H)</sub> | 6                | OE = "H"                                                     | 50  | —    | _   | 113  |

| Clock puls        | se width    | twsck               | 6                | SCK = "H" or "L"                                             | 20  |      |     | ns   |

| Latch puls        | se width    | t <sub>wSLAT</sub>  | 6                | $\overline{\text{SLAT}}$ = "H"                               | 20  | —    | —   | ns   |

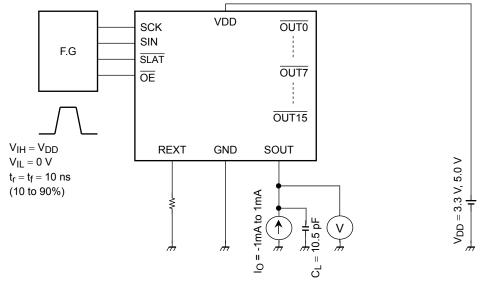

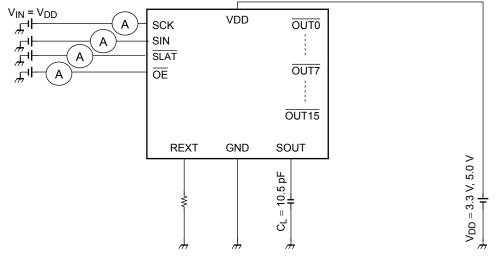

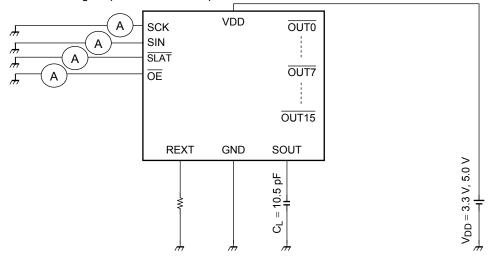

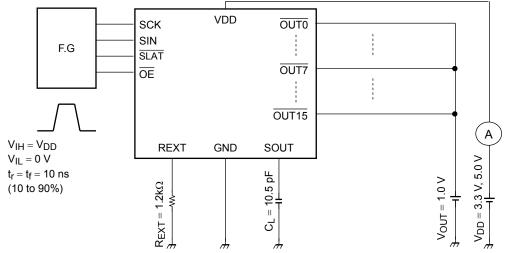

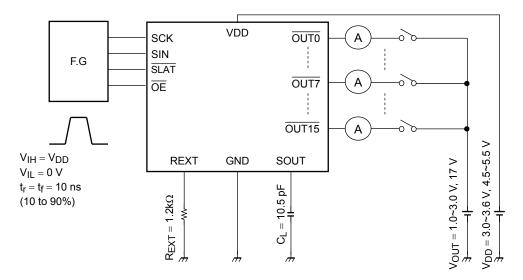

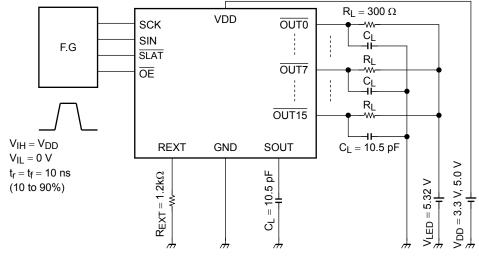

### **Test Circuits**

Test Circuit1: High level SOUT output voltage / Low level SOUT output voltage

Test Circuit2: High level logic input current / Pull-down resistor

Test Circuit3: Low level logic input current / Pull-up resistor

# <u>TOSHIBA</u>

Test Circuit4: Power supply current

Test Circuit5: Constant current output / Output OFF leak current / Constant current error Constant current output power supply voltage regulation Constant current output output voltage regulation

Test Circuit6: Switching Characteristics

## **Timing Waveforms**

1. SCK, SIN, SOUT

## 2. SCK, SIN, $\overline{\text{SLAT}}$ , $\overline{\text{OE}}$ , $\overline{\text{OUT0}}$

## 3. $\overline{OE}$ , $\overline{OUT0} \sim \overline{OUT15}$

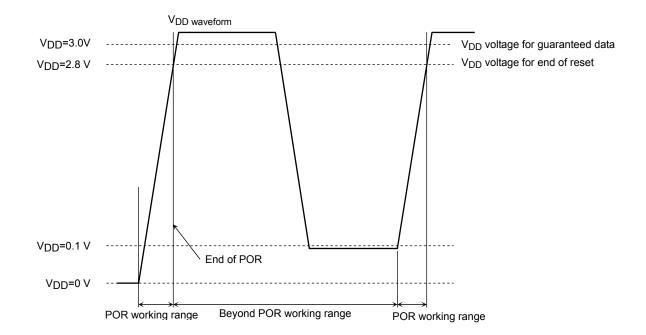

#### Power on reset (POR)

The TC62D748CFNAG provides a power-on reset to reset all internal data in order to prevent malfunctions.

The POR circuitry works properly only when  $V_{DD}$  rises from 0 V. To re-activate the POR circuitry,  $V_{DD}$  must be brought to less than 0.1 V. Internal data is guaranteed to be retained after  $V_{DD}$  exceeds 3.0 V.

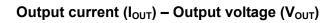

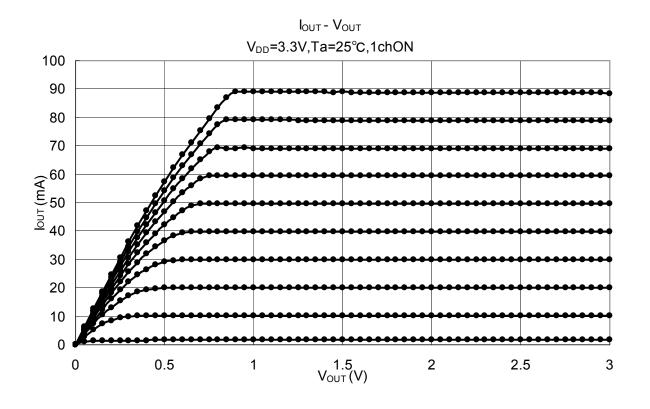

#### **Reference data**

The above data is for reference only, not guaranteed. Careful evaluation is required prior to creating a production design.

Output Current (I<sub>OUT</sub>) – Output current setting resistance (R<sub>EXT</sub>)

#### **Reference data**

The above data is for reference only, not guaranteed. Careful evaluation is required prior to creating a production design.

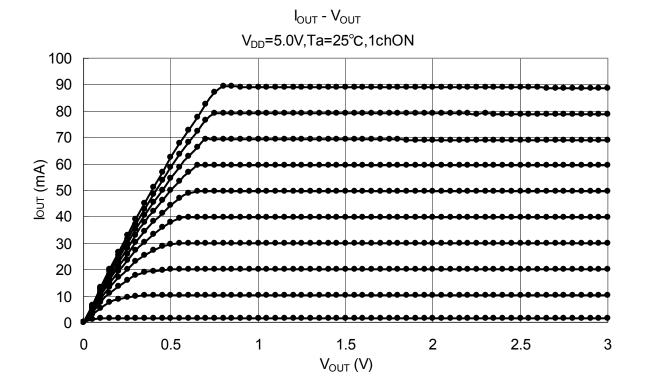

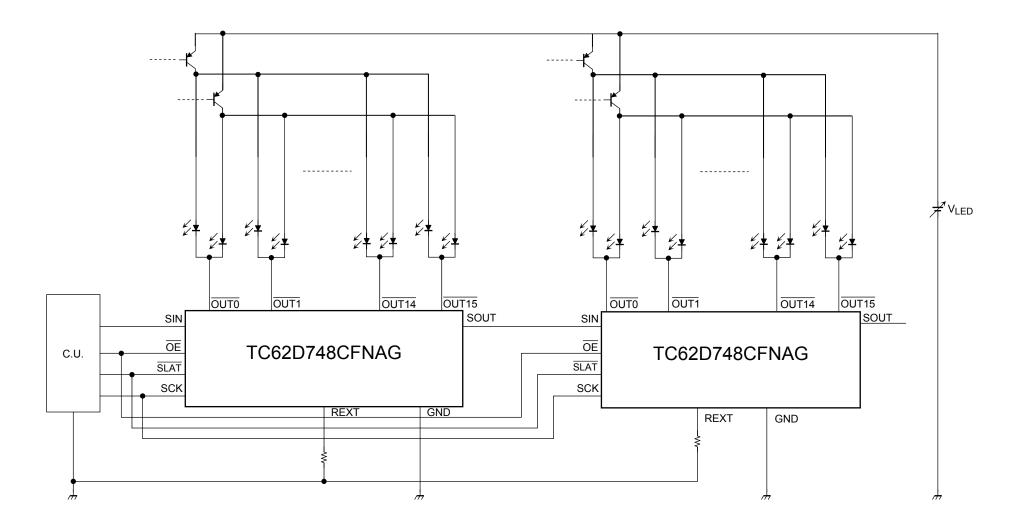

#### Application Circuit: General Composition for Static Lighting of LEDs

In the following diagram, it is recommended that the LED supply voltage ( $V_{LED}$ ) be equal to or greater than the sum of  $V_{f}$  (max) of all LEDs plus 1.0 V.

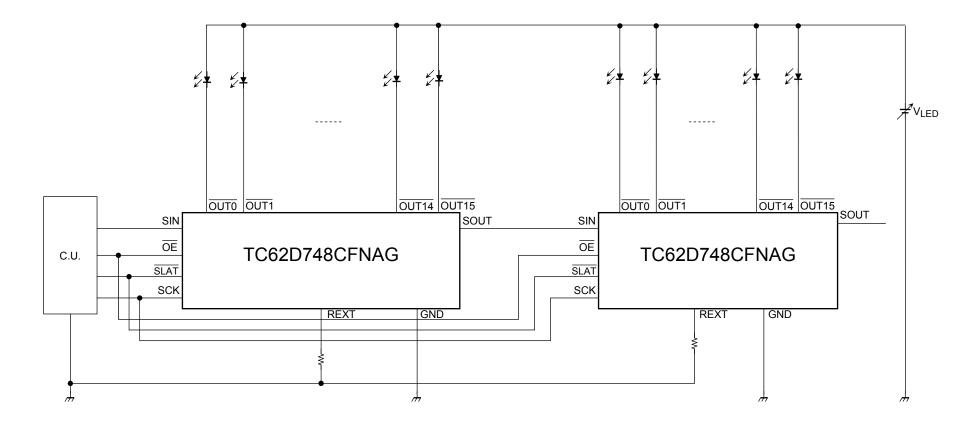

#### Application Circuit: General Composition for Dynamic Lighting of LEDs

In the following diagram, it is recommended that the LED supply voltage ( $V_{LED}$ ) be equal to or greater than the sum of  $V_{f}$  (max) of all LEDs plus 1.0 V.

### Notes on design of ICs

- Decoupling capacitors between power supply and GND It is recommended to place decoupling capacitors between power supply and GND as close to the IC as possible.

- Output current setting resistors When the output current setting resistors (R<sub>EXT</sub>) are shared among multiple ICs, production design should be evaluated carefully.

- 3. Board layout

Ground noise generated by output switching might cause the IC to malfunction if the ground line exhibits inductance and resistance due to PC board traces and wire leads. Also, the inductance between the IC output pins and the LED cathode pins might cause large surge voltage, damaging LEDs and the IC outputs. To avoid this situation, PC board traces and wire leads should be carefully laid out.

4. Consult the latest technical information for mass production.

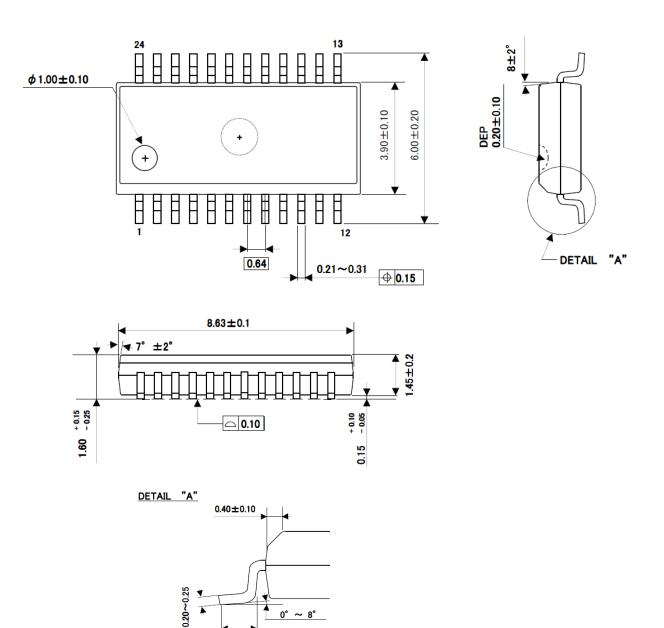

### Package Dimensions

CFNAG Type P-SSOP24-0409-0.64-001

Unit: mm

Weight: 0.14 g (typ.)

0.60 +0.20 -0.15

#### **Notes on Contents**

#### 1. Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

#### 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

#### 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

#### 4. Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage.

Toshiba does not grant any license to any industrial property rights by providing these examples of application circuits.

#### 5. Test Circuits

Components in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.

### IC Usage Considerations

#### Notes on handling of ICs

- [1] The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings. Exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

- [2] Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

- [3] If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. IC breakdown may cause injury, smoke or ignition.

Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury, smoke or ignition.

[4] Do not insert devices in the wrong orientation or incorrectly.

Make sure that the positive and negative terminals of power supplies are connected properly. Otherwise, the current or power consumption may exceed the absolute maximum rating, and exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

In addition, do not use any device that is applied the current with inserting in the wrong orientation or incorrectly even just one time.

[5] Carefully select external components (such as inputs and negative feedback capacitors) and load components (such as speakers), for example, power amp and regulator. If there is a large amount of leakage current such as input or negative feedback condenser, the IC output DC voltage will increase. If this output voltage is connected to a speaker with low input withstand voltage, overcurrent or IC failure can cause smoke or ignition. (The over current can cause smoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load (BTL) connection type IC that inputs output DC voltage to a speaker directly.

#### Points to remember on handling of ICs

(1) Heat Radiation Design

In using an IC with large current flow such as power amp, regulator or driver, please design the device so that heat is appropriately radiated, not to exceed the specified junction temperature  $(T_J)$  at any time and condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, please design the device taking into considerate the effect of IC heat radiation with peripheral components.

(2) Back-EMF

When a motor rotates in the reverse direction, stops or slows down abruptly, a current flow back to the motor's power supply due to the effect of back-EMF. If the current sink capability of the power supply is small, the device's motor power supply and output pins might be exposed to conditions beyond absolute maximum ratings. To avoid this problem, take the effect of back-EMF into consideration in system design.

### About solderability, following conditions were confirmed

#### Solderability

- (1) Use of Sn-37Pb solder Bath

- solder bath temperature: 230°C

- dipping time: 5 seconds

- the number of times: once

- · use of R-type flux

- (2) Use of Sn-3.0Ag-0.5Cu solder Bath

- solder bath temperature: 245°C

- dipping time: 5 seconds

- the number of times: once

- · use of R-type flux

# <u>TOSHIBA</u>

## **RESTRICTIONS ON PRODUCT USE**

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document. Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact ("Unintended Use"). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Toshiba:

TC62D748CFNAG(CEBH TC62D748CFNAG,C,EB

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331