## X98017

## NOT RECOMMENDED FOR NEW DESIGNS -THE ISL98001-170 IS A 100% COMPATIBLE IMPROVED ALTERNATIVE

170MHz Triple Video Digitizer with Digital PLL

FN8218 Rev 3.00 March 8, 2006

The X98017 3-channel, 8-bit Analog Front End (AFE) contains all the components necessary to digitize analog RGB or YUV graphics signals from personal computers, workstations and video set-top boxes. The fully differential analog design provides high PSRR and dynamic performance to meet the stringent requirements of the graphics display industry. The AFE's 170MSPS conversion rate supports resolutions up to UXGA at 60Hz refresh rate, while the front end's high input bandwidth ensures sharp images at the highest resolutions.

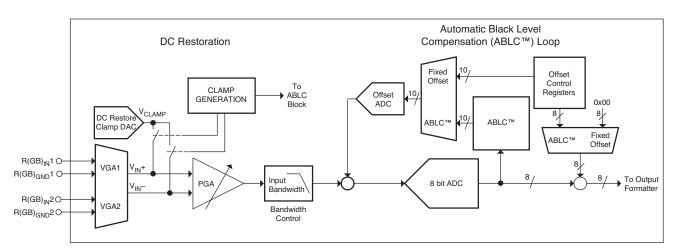

To minimize noise, the X98017's analog section features 2 sets of pseudo-differential RGB inputs with programmable input bandwidth, as well as internal DC restore clamping (including mid-scale clamping for YUV signals). This is followed by the programmable gain/offset stage and the three 170MSPS Analog-to-Digital Converters (ADCs). Automatic Black Level Compensation (ABLC™) eliminates part-to-part offset variation, ensuring perfect black level performance in every application.

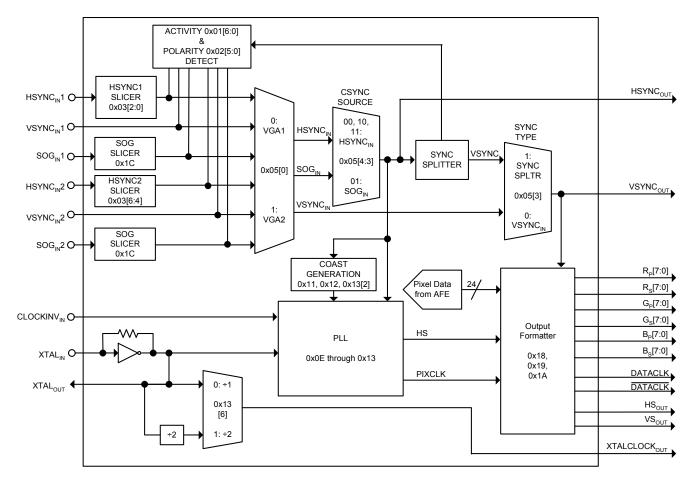

The X98017's digital PLL generates a pixel clock from the analog source's HSYNC or SOG (Sync-On-Green) signals. Pixel clock output frequencies range from 10MHz to 170MHz with sampling clock jitter of 250ps peak to peak.

#### **Features**

- · 170MSPS maximum conversion rate

- Low PLL clock jitter (250ps p-p @ 170MSPS)

- · 64 interpixel sampling positions

- 0.35V<sub>p-p</sub> to 1.4V<sub>p-p</sub> video input range

- Programmable bandwidth (100MHz to 780MHz)

- · 2 channel input multiplexer

- · RGB and YUV 4:2:2 output formats

- 5 embedded voltage regulators allow operation from single 3.3V supply and enhance performance, isolation

- Completely independent 8 bit gain/10 bit offset control

- · CSYNC and SOG support

- · Trilevel sync detection

- 1.05W typical P<sub>D</sub> @ 170MSPS

- · Pb-free plus anneal available (RoHS compliant)

## **Applications**

- · LCD Monitors and Projectors

- · Digital TVs

- · Plasma Display Panels

- RGB Graphics Processing

- · Scan Converters

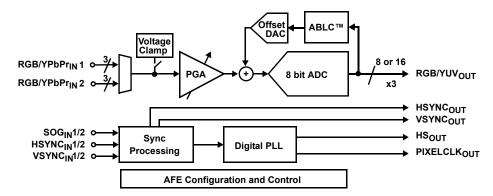

## Simplified Block Diagram

## **Ordering Information**

| PART NUMBER                 | PART MARKING | MAXIMUM PIXEL<br>RATE | TEMP RANGE<br>(°C) | PACKAGE            |

|-----------------------------|--------------|-----------------------|--------------------|--------------------|

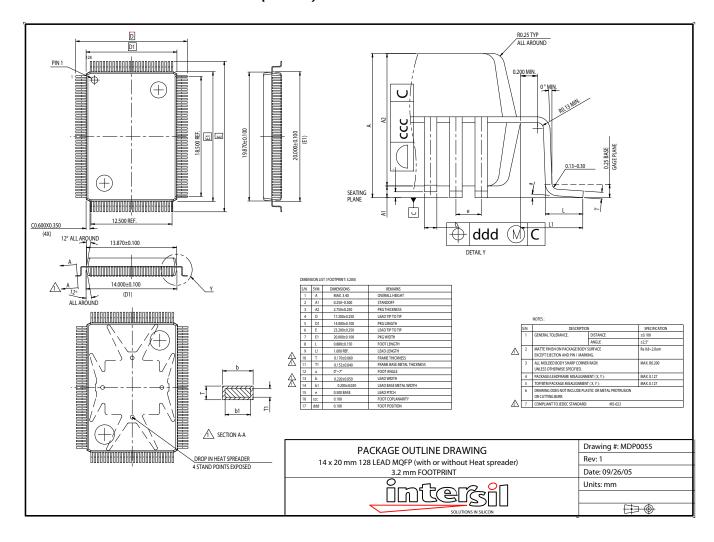

| X98017L128-3.3              | X98017L-3.3  | 170MHz                | 0 to 70            | 128 MQFP           |

| X98017L128-3.3-Z (See Note) | X98017L-3.3Z | 170MHz                | 0 to 70            | 128 MQFP (Pb-free) |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

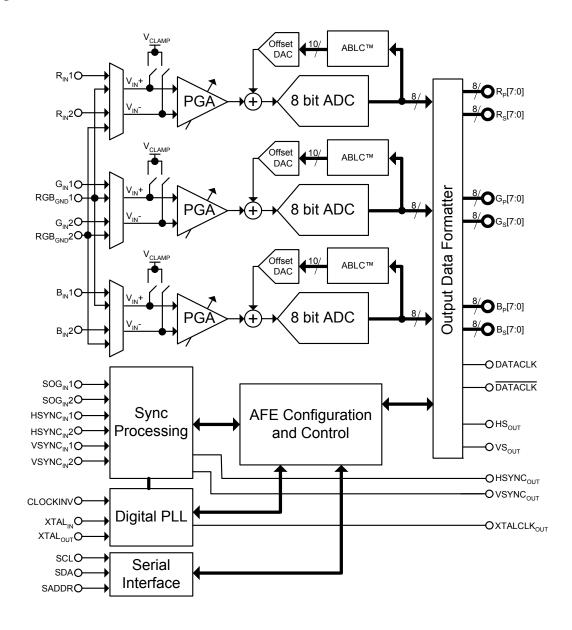

## **Block Diagram**

Page 2 of 29

### Absolute Maximum Ratings

####

#### **Recommended Operating Conditions**

CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Electrical Specifications** Specifications apply for $V_A = V_D = V_X = 3.3V$ , pixel rate = 170MHz, $f_{XTAL} = 25$ MHz, $T_A = 25$ °C, unless otherwise noted

| SYMBOL                           | PARAMETER                                                                                                                                                                                            | COMMENT                                                                                                                     | MIN  | TYP                            | MAX          | UNIT             |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|--------------------------------|--------------|------------------|

| FULL CHA                         | NNEL CHARACTERISTICS                                                                                                                                                                                 |                                                                                                                             |      |                                |              |                  |

|                                  | ADC Resolution                                                                                                                                                                                       |                                                                                                                             | 8    |                                |              | Bits             |

|                                  | Missing Codes                                                                                                                                                                                        | Guaranteed monotonic                                                                                                        |      |                                | None         |                  |

|                                  | Conversion Rate                                                                                                                                                                                      | Per Channel                                                                                                                 | 10   |                                | 170          | MHz              |

| DNL                              | Differential Non-Linearity                                                                                                                                                                           |                                                                                                                             |      | ±0.5                           | +1.0<br>-0.9 | LSB              |

| INL                              | Integral Non-Linearity                                                                                                                                                                               |                                                                                                                             |      | ±1.1                           | ±3.25        | LSB              |

|                                  | Gain Adjustment Range                                                                                                                                                                                |                                                                                                                             |      | ±6                             |              | dB               |

|                                  | Gain Adjustment Resolution                                                                                                                                                                           |                                                                                                                             |      | 8                              |              | Bits             |

|                                  | Gain Matching Between Channels                                                                                                                                                                       | Percent of full scale                                                                                                       |      | ±1                             |              | %                |

|                                  | Full Channel Offset Error, ABLC™ enabled                                                                                                                                                             | ADC LSBs, over time and temperature                                                                                         |      | ±0.125                         | ±0.5         | LSB              |

|                                  | Offset Adjustment Range, ABLC™ enabled or disabled                                                                                                                                                   | ADC LSBs (see ABLC™ applications information section)                                                                       |      | ±127                           |              | LSB              |

|                                  | Overvoltage Recovery Time                                                                                                                                                                            | For 150% overrange, maximum bandwidth setting                                                                               |      | 5                              |              | ns               |

| ANALOG \                         | /IDEO INPUT CHARACTERISTICS (R <sub>IN</sub> 1, C                                                                                                                                                    | G <sub>IN</sub> 1, B <sub>IN</sub> 1, R <sub>IN</sub> 2, G <sub>IN</sub> 2, B <sub>IN</sub> 2)                              |      |                                |              |                  |

|                                  | Input Range                                                                                                                                                                                          |                                                                                                                             | 0.35 | 0.7                            | 1.4          | V <sub>P-P</sub> |

|                                  | Input Bias Current                                                                                                                                                                                   | DC restore clamp off                                                                                                        |      | ±0.01                          | ±1           | μA               |

|                                  |                                                                                                                                                                                                      |                                                                                                                             |      |                                |              |                  |

|                                  | Input Capacitance                                                                                                                                                                                    |                                                                                                                             |      | 5                              | ĺ            | pF               |

|                                  | Input Capacitance Full Power Bandwidth                                                                                                                                                               | Programmable                                                                                                                |      | 5<br>780                       |              | pF<br>MHz        |

| INPUT CHA                        |                                                                                                                                                                                                      | Programmable                                                                                                                |      | -                              |              | •                |

| INPUT CHA                        | Full Power Bandwidth                                                                                                                                                                                 | Programmable - See Register Listing for Details                                                                             |      | -                              |              | •                |

|                                  | Full Power Bandwidth  ARACTERISTICS (SOG <sub>IN</sub> 1, SOG <sub>IN</sub> 2)                                                                                                                       | Programmable - See Register Listing for                                                                                     |      | 780<br>0 to                    |              | MHz              |

|                                  | Full Power Bandwidth  ARACTERISTICS (SOG <sub>IN</sub> 1, SOG <sub>IN</sub> 2)  Input Threshold Voltage                                                                                              | Programmable - See Register Listing for Details                                                                             |      | 780<br>0 to<br>-0.3            |              | MHz              |

| V <sub>IH</sub> /V <sub>IL</sub> | Full Power Bandwidth  ARACTERISTICS (SOG <sub>IN</sub> 1, SOG <sub>IN</sub> 2)  Input Threshold Voltage  Hysteresis                                                                                  | Programmable - See Register Listing for Details                                                                             |      | 780<br>0 to<br>-0.3<br>40      |              | V mV             |

| V <sub>IH</sub> /V <sub>IL</sub> | Full Power Bandwidth  ARACTERISTICS (SOG <sub>IN</sub> 1, SOG <sub>IN</sub> 2)  Input Threshold Voltage  Hysteresis  Input capacitance                                                               | Programmable - See Register Listing for Details                                                                             |      | 780<br>0 to<br>-0.3<br>40      |              | V mV             |

| V <sub>IH</sub> /V <sub>IL</sub> | Full Power Bandwidth  ARACTERISTICS (SOG <sub>IN</sub> 1, SOG <sub>IN</sub> 2)  Input Threshold Voltage  Hysteresis  Input capacitance  ARACTERISTICS (HSYNC <sub>IN</sub> 1, HSYNC <sub>IN</sub> 2) | Programmable - See Register Listing for Details  Centered around threshold voltage  Programmable - See Register Listing for |      | 780<br>0 to<br>-0.3<br>40<br>5 |              | V mV             |

X98017

**Electrical Specifications** Specifications apply for  $V_A = V_D = V_X = 3.3V$ , pixel rate = 170MHz,  $f_{XTAL} = 25$ MHz,  $T_A = 25$ °C, unless otherwise noted **(Continued)**

| SYMBOL            | PARAMETER                                                                   | COMMENT                                                                                                             | MIN                   | TYP  | MAX  | UNIT   |

|-------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|--------|

|                   | Input capacitance                                                           |                                                                                                                     |                       | 5    |      | pF     |

| DIGITAL IN        | IPUT CHARACTERISTICS (SDA, SADDR,                                           | CLOCKINV <sub>IN</sub> , RESET)                                                                                     |                       | 1    |      | II.    |

| V <sub>IH</sub>   | Input HIGH Voltage                                                          |                                                                                                                     | 2.0                   |      |      | V      |

| V <sub>IL</sub>   | Input LOW Voltage                                                           |                                                                                                                     |                       |      | 0.8  | V      |

| Ţ                 | Input leakage current                                                       | $\overline{\text{RESET}}$ has a $70\text{k}\Omega$ pullup to $\text{V}_{\text{D}}$                                  |                       | ±10  |      | nA     |

|                   | Input capacitance                                                           |                                                                                                                     |                       | 5    |      | pF     |

| SCHMITT I         | DIGITAL INPUT CHARACTERISTICS (SCL                                          | , VSYNC <sub>IN</sub> 1, VSYNC <sub>IN</sub> 2)                                                                     | <del>- !</del>        |      |      | •      |

| V <sub>T</sub> +  | Low to High Threshold Voltage                                               |                                                                                                                     | 1.45                  |      |      | V      |

| V <sub>T</sub> -  | High to Low Threshold Voltage                                               |                                                                                                                     |                       |      | 0.95 | V      |

| ı                 | Input leakage current                                                       |                                                                                                                     |                       | ±10  |      | nA     |

|                   | Input capacitance                                                           |                                                                                                                     |                       | 5    |      | pF     |

| DIGITAL O         | UTPUT CHARACTERISTICS (DATACLK, I                                           | DATACLK)                                                                                                            | '                     | 11   | 1    | 1      |

| $V_{OH}$          | Output HIGH Voltage, I <sub>O</sub> = 16mA                                  |                                                                                                                     | 2.4                   |      |      | V      |

| V <sub>OL</sub>   | Output LOW Voltage, I <sub>O</sub> = -16mA                                  |                                                                                                                     |                       |      | 0.4  | V      |

| DIGITAL O         | UTPUT CHARACTERISTICS (R <sub>P</sub> , G <sub>P</sub> , B <sub>P</sub> , I | R <sub>S</sub> , G <sub>S</sub> , B <sub>S</sub> , HS <sub>OUT</sub> , VS <sub>OUT</sub> , HSYNC <sub>OUT</sub> , V | SYNC <sub>OUT</sub> ) | 1    | 1    |        |

| V <sub>OH</sub>   | Output HIGH Voltage, I <sub>O</sub> = 8mA                                   |                                                                                                                     | 2.4                   |      |      | V      |

| V <sub>OL</sub>   | Output LOW Voltage, I <sub>O</sub> = -8mA                                   |                                                                                                                     |                       |      | 0.4  | V      |

| R <sub>TRI</sub>  | Pulldown to GND <sub>D</sub> when three-state                               | R <sub>P</sub> , G <sub>P</sub> , B <sub>P</sub> , R <sub>S</sub> , G <sub>S</sub> , B <sub>S</sub> only            |                       | 58   |      | kΩ     |

| DIGITAL O         | UTPUT CHARACTERISTICS (SDA, XTALO                                           | CLK <sub>OUT</sub> )                                                                                                |                       | 1    | 1    |        |

| V <sub>OH</sub>   | Output HIGH Voltage, I <sub>O</sub> = 4mA                                   | XTALCLK <sub>OUT</sub> only; SDA is open-drain                                                                      | 2.4                   |      |      | V      |

| V <sub>OL</sub>   | Output LOW Voltage, I <sub>O</sub> = -4mA                                   |                                                                                                                     |                       |      | 0.4  | V      |

| POWER SI          | JPPLY REQUIREMENTS                                                          |                                                                                                                     |                       | 1    | 1    |        |

| V <sub>A</sub>    | Analog Supply Voltage                                                       |                                                                                                                     | 3                     | 3.3  | 3.6  | V      |

| $V_{D}$           | Digital Supply Voltage                                                      |                                                                                                                     | 3                     | 3.3  | 3.6  | V      |

| VX                | Crystal Oscillator Supply Voltage                                           |                                                                                                                     | 3                     | 3.3  | 3.6  | V      |

| I <sub>A</sub>    | Analog Supply Current                                                       | Operating                                                                                                           |                       | 185  | 195  | mA     |

| I <sub>D</sub>    | Digital Supply Current                                                      | Operating (grayscale)                                                                                               |                       | 135  | 145  | mA     |

| lχ                | Crystal Oscillator Supply Current                                           |                                                                                                                     |                       | 0.7  | 2    | mA     |

| $P_{D}$           | Total Power Dissipation                                                     | Operating (average)                                                                                                 |                       | 1.05 | 1.25 | W      |

|                   |                                                                             | Power-down Mode                                                                                                     |                       | 50   | 80   | mW     |

| $\Theta_{\sf JA}$ | Thermal Resistance, Junction to Ambient                                     |                                                                                                                     |                       | 30   |      | °C/W   |

| AC TIMING         | CHARACTERISTICS                                                             |                                                                                                                     |                       |      | 1    | •      |

|                   | PLL Jitter                                                                  |                                                                                                                     |                       | 250  | 450  | ps p-p |

|                   | Sampling Phase Steps                                                        | 5.6° per step                                                                                                       | 64                    |      |      |        |

|                   | Sampling Phase Tempco                                                       |                                                                                                                     |                       | ±1   |      | ps/°C  |

|                   | Sampling Phase Differential Nonlinearity                                    | Degrees out of 360°                                                                                                 |                       | ±3   |      | 0      |

|                   | HSYNC Frequency Range                                                       |                                                                                                                     | 10                    |      | 150  | kHz    |

| f <sub>XTAL</sub> | Crystal Frequency Range                                                     |                                                                                                                     | 23                    | 25   | 27   | MHz    |

**Electrical Specifications** Specifications apply for  $V_A = V_D = V_X = 3.3V$ , pixel rate = 170MHz,  $f_{XTAL} = 25$ MHz,  $T_A = 25$ °C, unless otherwise noted (Continued)

| SYMBOL              | PARAMETER                                                     | COMMENT                                    | MIN | TYP | MAX         | UNIT |

|---------------------|---------------------------------------------------------------|--------------------------------------------|-----|-----|-------------|------|

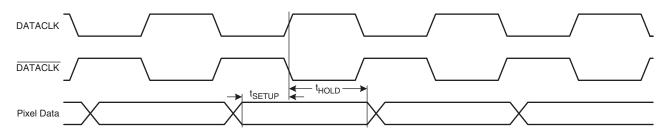

| <sup>t</sup> SETUP  | DATA valid before rising edge of DATACLK                      | 15pF DATACLK load, 15pF DATA load (Note 1) | 1.3 |     |             | ns   |

| tHOLD               | DATA valid after rising edge of DATACLK                       | 15pF DATACLK load, 15pF DATA load (Note 1) | 2.0 |     |             | ns   |

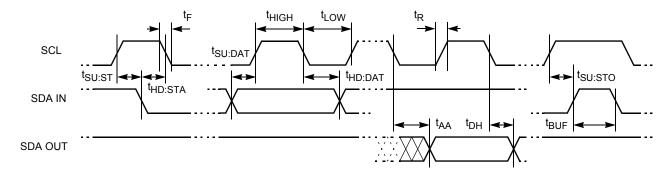

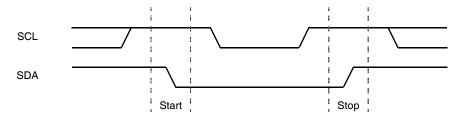

| AC TIMING           | CHARACTERISTICS (2 WIRE INTERFAC                              | E)                                         |     |     |             |      |

| f <sub>SCL</sub>    | SCL Clock Frequency                                           |                                            | 0   |     | 400         | kHz  |

|                     | Maximum width of a glitch on SCL that will be suppressed      | 2 XTAL periods min                         | 80  |     |             | ns   |

| t <sub>AA</sub>     | SCL LOW to SDA Data Out Valid                                 | 5 XTAL periods plus SDA's RC time constant |     |     | See comment | μs   |

| t <sub>BUF</sub>    | Time the bus must be free before a new transmission can start |                                            | 1.3 |     |             | μs   |

| t <sub>LOW</sub>    | Clock LOW Time                                                |                                            | 1.3 |     |             | μs   |

| t <sub>HIGH</sub>   | Clock HIGH Time                                               |                                            | 0.6 |     |             | μs   |

| t <sub>SU:STA</sub> | Start Condition Setup Time                                    |                                            | 0.6 |     |             | μs   |

| t <sub>HD:STA</sub> | Start Condition Hold Time                                     |                                            | 0.6 |     |             | μs   |

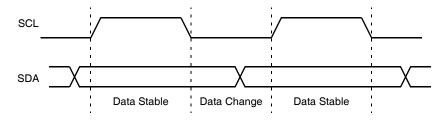

| t <sub>SU:DAT</sub> | Data In Setup Time                                            |                                            | 100 |     |             | ns   |

| t <sub>HD:DAT</sub> | Data In Hold Time                                             |                                            | 0   |     |             | ns   |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                                     |                                            | 0.6 |     |             | μs   |

| t <sub>DH</sub>     | Data Output Hold Time                                         | 4 XTAL periods min                         | 160 |     |             | ns   |

#### NOTES:

1. Setup and hold times are at a 140MHz DATACLK rate.

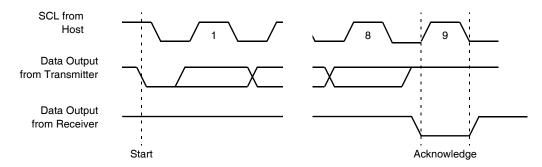

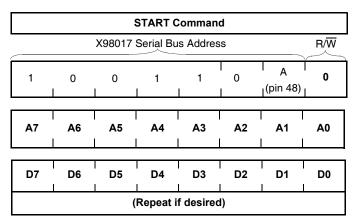

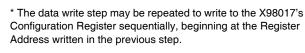

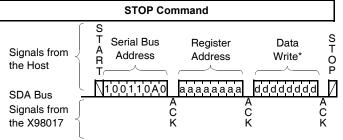

FIGURE 1. 2 WIRE INTERFACE TIMING

FIGURE 2. DATA OUTPUT SETUP AND HOLD TIMING

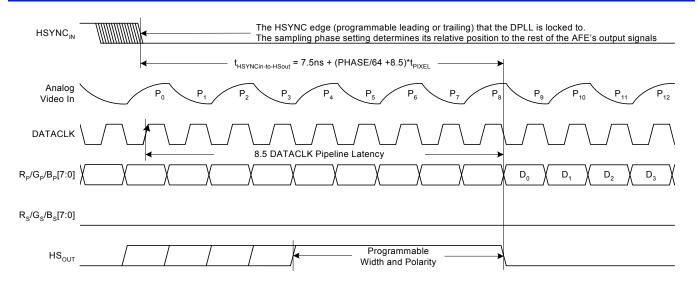

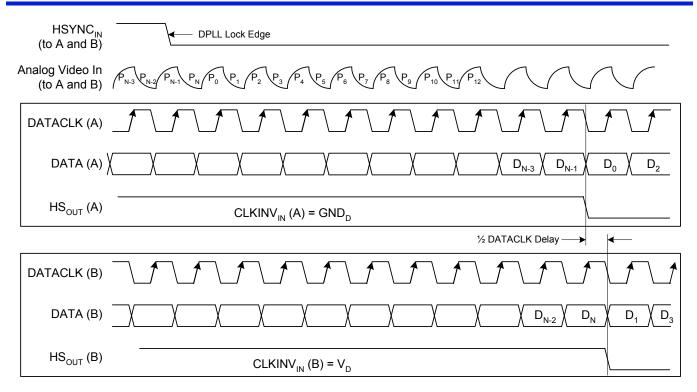

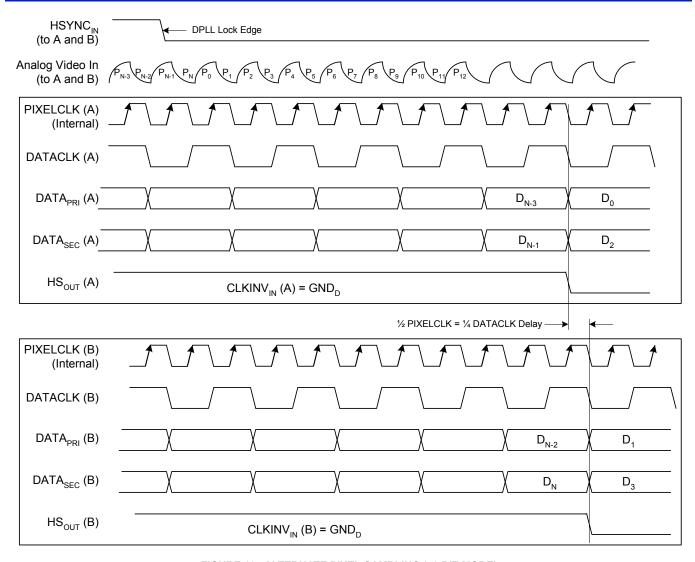

FIGURE 3. 24 BIT OUTPUT MODE

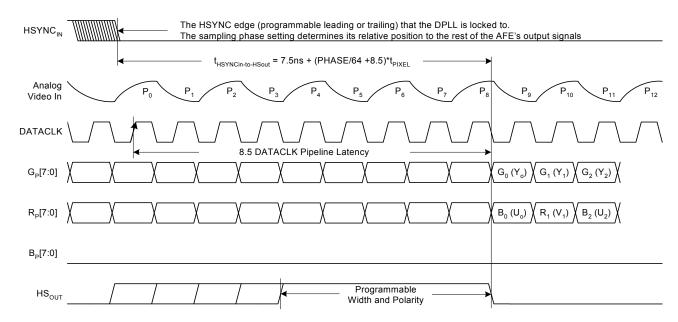

FIGURE 4. 24 BIT 4:2:2 OUTPUT MODE (FOR YUV SIGNALS)

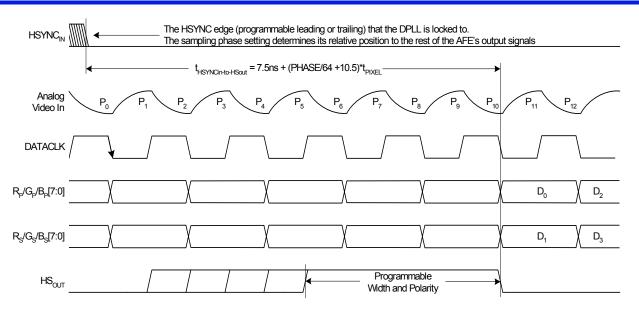

FIGURE 5. 48 BIT OUTPUT MODE

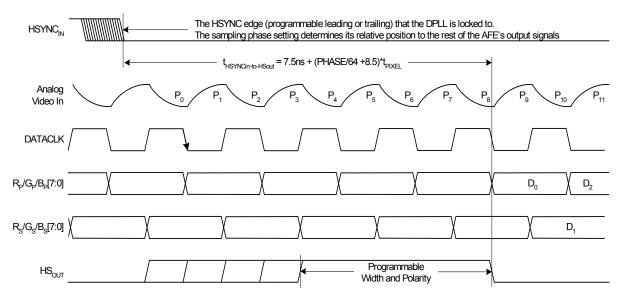

FIGURE 6. 48 BIT OUTPUT MODE, INTERLEAVED TIMING

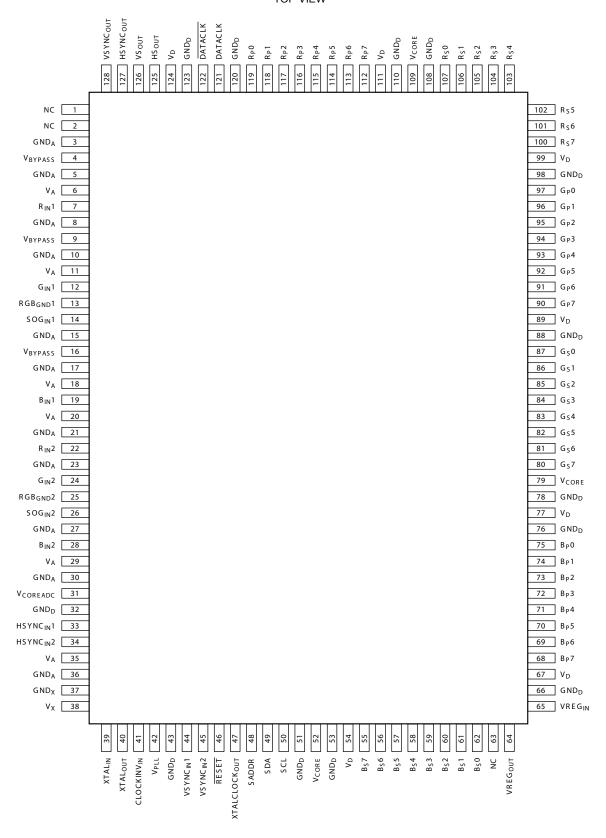

### **Pinout**

#### **X98017** (**128-PIN MQFP**) TOP VIEW

## Pin Descriptions

| SYMBOL                 | PIN     | DESCRIPTION                                                                                                                                                                                                                                                                                          |

|------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>IN</sub> 1      | 7       | Analog input. Red channel 1. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                   |

| G <sub>IN</sub> 1      | 12      | Analog input. Green channel 1. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                 |

| B <sub>IN</sub> 1      | 19      | Analog input. Blue channel 1. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                  |

| RGB <sub>GND</sub> 1   | 13      | Analog input. Ground reference for the R, G, and B inputs of channel 1 in the DC coupled configuration. Connect to the same ground as channel 1's R, G, and B termination resistors. This signal is not used in the AC-coupled configuration, but the pin should still be tied to GND <sub>A</sub> . |

| SOG <sub>IN</sub> 1    | 14      | Analog input. Sync on Green. Connect to $G_{IN}$ 1 through a 0.01 $\mu$ F capacitor in series with a 500 $\Omega$ resistor.                                                                                                                                                                          |

| HSYNC <sub>IN</sub> 1  | 33      | Digital input, 5V tolerant, 240mV hysteresis, $1.2k\Omega$ impedance to GND <sub>A</sub> . Connect to channel 1's HSYNC signal through a $680\Omega$ series resistor.                                                                                                                                |

| VSYNC <sub>IN</sub> 1  | 44      | Digital input, 5V tolerant, 500mV hysteresis. Connect to channel 1's VSYNC signal.                                                                                                                                                                                                                   |

| R <sub>IN</sub> 2      | 22      | Analog input. Red channel 2. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                   |

| G <sub>IN</sub> 2      | 24      | Analog input. Green channel 2. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                 |

| B <sub>IN</sub> 2      | 28      | Analog input. Blue channel 2. DC couple or AC couple through 0.1µF.                                                                                                                                                                                                                                  |

| RGB <sub>GND</sub> 2   | 25      | Analog input. Ground reference for the R, G, and B inputs of channel 2 in the DC coupled configuration. Connect to the same ground as channel 1's R, G, and B termination resistors. This signal is not used in the AC-coupled configuration, but the pin should still be tied to GND <sub>A</sub> . |

| SOG <sub>IN</sub> 2    | 26      | Analog input. Sync on Green. Connect to $G_{IN}$ 1 through a 0.01 $\mu$ F capacitor in series with a 500 $\Omega$ resistor.                                                                                                                                                                          |

| HSYNC <sub>IN</sub> 2  | 34      | Digital input, 5V tolerant, 240mV hysteresis, 1.2k $\Omega$ impedance to GNDA. Connect to channel 2's HSYNC signal through a 680 $\Omega$ series resistor.                                                                                                                                           |

| VSYNC <sub>IN</sub> 2  | 45      | Digital input, 5V tolerant, 500mV hysteresis. Connect to channel 2's VSYNC signal.                                                                                                                                                                                                                   |

| CLOCKINVIN             | 41      | Digital input, 5V tolerant. When high, changes the pixel sampling phase by 180 degrees. Toggle at frame rate during VSYNC to allow 2x undersampling to sample odd and even pixels on sequential frames. Tie to D <sub>GND</sub> if unused.                                                           |

| RESET                  | 46      | Digital input, 5V tolerant, active low, $70k\Omega$ pull-up to $V_D$ . Take low for at least 1 $\mu$ s and then high again to reset the X98017. This pin is not necessary for normal use and may be tied directly to the $V_D$ supply.                                                               |

| XTAL <sub>IN</sub>     | 39      | Analog input. Connect to external 23MHz to 27MHz crystal and load capacitor (see crystal spec for recommended loading). Typical oscillation amplitude is 1.0V <sub>P-P</sub> centered around 0.5V.                                                                                                   |

| XTAL <sub>OUT</sub>    | 40      | Analog output. Connect to external 23MHz to 27MHz crystal and load capacitor (see crystal spec for recommended loading). Typical oscillation amplitude is 1.0V <sub>P-P</sub> centered around 0.5V.                                                                                                  |

| XTALCLK <sub>OUT</sub> | 47      | 3.3V digital output. Buffered crystal clock output at $f_{XTAL}$ or $f_{XTAL}/2$ . May be used as system clock for other system components.                                                                                                                                                          |

| SADDR                  | 48      | Digital input, 5V tolerant. Address = 0x4C (0x98 including R/W bit) when tied low. Address = 0x4D (0x9A including R/W bit) when tied high.                                                                                                                                                           |

| SCL                    | 50      | Digital input, 5V tolerant, 500mV hysteresis. Serial data clock for 2-wire interface.                                                                                                                                                                                                                |

| SDA                    | 49      | Bidirectional Digital I/O, open drain, 5V tolerant. Serial data I/O for 2-wire interface.                                                                                                                                                                                                            |

| R <sub>P</sub> [7:0]   | 112-119 | 3.3V digital output. Red channel, primary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                                |

| R <sub>S</sub> [7:0]   | 100-107 | 3.3V digital output. Red channel, secondary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                              |

| G <sub>P</sub> [7:0]   | 90-97   | 3.3V digital output. Green channel, primary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                              |

| G <sub>S</sub> [7:0]   | 80-87   | 3.3V digital output. Green channel, secondary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                            |

| B <sub>P</sub> [7:0]   | 68-75   | 3.3V digital output. Blue channel, primary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                               |

| B <sub>S</sub> [7:0]   | 55-62   | 3.3V digital output. Blue channel, secondary pixel data. 58K pulldown when three-stated.                                                                                                                                                                                                             |

| DATACLK                | 121     | 3.3V digital output. Data clock output. Equal to pixel clock rate in 24 bit mode, one half pixel clock rate in 4 bit mode.                                                                                                                                                                           |

| DATACLK                | 122     | 3.3V digital output. Inverse of DATACLK.                                                                                                                                                                                                                                                             |

## Pin Descriptions (Continued)

| SYMBOL               | PIN                                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                      |

|----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS <sub>OUT</sub>    | 125                                                             | 3.3V digital output. HSYNC output aligned with pixel data. Use this output to frame the digital output data. This output is always purely horizontal sync (without any composite sync signals)                                                                                                                   |

| VS <sub>OUT</sub>    | 126                                                             | 3.3V digital output.Artificial VSYNC output aligned with pixel data. VSYNC is generated 8 pixel clocks after the trailing edge of HS <sub>OUT</sub> . This signal is usually not needed - use VSYNC <sub>OUT</sub> as VSYNC source.                                                                              |

| HSYNC <sub>OUT</sub> | 127                                                             | 3.3V digital output. Buffered HSYNC (or SOG or CSYNC) output. This is typically used to measure HSYNC period. $HS_{OUT}$ should be used to detect the beginning of a line. This output will pass composite sync signals and Macrovision signals if present on $HSYNC_{IN}$ or $SOG_{IN}$ .                       |

| VSYNC <sub>OUT</sub> | 128                                                             | 3.3V digital output. Buffered VSYNC output. For composite sync signals, this output will be asserted for the duration of the disruption of the normal HSYNC pattern. This is typically used to detect the beginning of a frame and measure the VSYNC period.                                                     |

| VA                   | 6, 11, 18, 20,<br>29, 35                                        | Power supply for the analog section. Connect to a 3.3V supply and bypass each pin to GND <sub>A</sub> with 0.1μF.                                                                                                                                                                                                |

| GND <sub>A</sub>     | 3, 5, 8, 10, 15,<br>17, 21, 23, 27,<br>30, 36                   | Ground return for V <sub>A</sub> and V <sub>BYPASS</sub> .                                                                                                                                                                                                                                                       |

| V <sub>D</sub>       | 54, 67, 77, 89,<br>99, 111, 124                                 | Power supply for all digital I/Os. Connect to a 3.3V supply and bypass each pin to GND <sub>D</sub> with 0.1µF.                                                                                                                                                                                                  |

| GND <sub>D</sub>     | 32, 43, 51, 53,<br>66, 76, 78, 88,<br>98, 108, 110,<br>120, 123 | Ground return for $V_D$ , $V_{CORE}$ , $V_{COREADC}$ , and $V_{PLL}$ .                                                                                                                                                                                                                                           |

| V <sub>X</sub>       | 38                                                              | Power supply for crystal oscillator. Connect to a 3.3V supply and bypass to GND <sub>X</sub> with 0.1µF.                                                                                                                                                                                                         |

| $GND_X$              | 37                                                              | Ground return for V <sub>X</sub> .                                                                                                                                                                                                                                                                               |

| V <sub>BYPASS</sub>  | 4, 9, 16                                                        | Bypass these pins to GND <sub>A</sub> with 0.1μF. Do not connect these pins to each other or anything else.                                                                                                                                                                                                      |

| VREG <sub>IN</sub>   | 65                                                              | 3.3V input voltage for V <sub>CORE</sub> voltage regulator. Connect to a 3.3V source, and bypass to GND <sub>D</sub> with 0.1µF                                                                                                                                                                                  |

| VREG <sub>OUT</sub>  | 64                                                              | Regulated output voltage for $V_{PLL}$ , $V_{COREADC}$ and $V_{CORE}$ ; typically 1.9V. Connect only to $V_{PLL}$ , $V_{COREADC}$ and $V_{CORE}$ and bypass at input pins as instructed below. Do not connect to anything else - this output can only supply power to $V_{PLL}$ , $V_{COREADC}$ and $V_{CORE}$ . |

| V <sub>COREADC</sub> | 31                                                              | Internal power for the ADC's digital logic. Connect to VREG $_{OUT}$ through a $10\Omega$ resistor and bypass to GND $_{D}$ with $0.1\mu F$ .                                                                                                                                                                    |

| V <sub>PLL</sub>     | 42                                                              | Internal power for the PLL's digital logic. Connect to VREG $_{OUT}$ through a $10\Omega$ resistor and bypass to GND $_{D}$ with $0.1\mu F$ .                                                                                                                                                                    |

| V <sub>CORE</sub>    | 52, 79, 109                                                     | Internal power for core logic. Connect to VREG <sub>OUT</sub> and bypass each pin to GND <sub>D</sub> with 0.1µF.                                                                                                                                                                                                |

| NC                   | 1, 2, 63                                                        | Reserved. Do not connect anything to these pins.                                                                                                                                                                                                                                                                 |

## Register Listing

| ADDRESS | REGISTER (DEFAULT VALUE)  | BIT(s) | FUNCTION NAME                          | DESCRIPTION                                                                                                                             |

|---------|---------------------------|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0x01    | SYNC Status (read only)   | 0      | HSYNC1 Active                          | 0: HSYNC1 is Inactive<br>1: HSYNC1 is Active                                                                                            |

|         |                           | 1      | HSYNC2 Active                          | 0: HSYNC2 is Inactive<br>1: HSYNC2 is Active                                                                                            |

|         |                           | 2      | VSYNC1 Active                          | 0: VSYNC1 is Inactive<br>1: VSYNC1 is Active                                                                                            |

|         |                           | 3      | VSYNC2 Active                          | 0: VSYNC2 is Inactive<br>1: VSYNC2 is Active                                                                                            |

|         |                           | 4      | SOG1 Active                            | 0: SOG1 is Inactive<br>1: SOG1 is Active                                                                                                |

|         |                           | 5      | SOG2 Active                            | 0: SOG2 is Inactive<br>1: SOG2 is Active                                                                                                |

|         |                           | 6      | PLL Locked                             | 0: PLL is unlocked 1: PLL is locked to incoming HSYNC                                                                                   |

|         |                           | 7      | CSYNC Detected at Sync Splitter Output | Composite Sync signal not detected     Composite Sync signal is detected                                                                |

| 0x02    | SYNC Polarity (read only) | 0      | HSYNC1<br>Polarity                     | 0: HSYNC1 is Active High<br>1: HSYNC1 is Active Low                                                                                     |

|         |                           | 1      | HSYNC2<br>Polarity                     | 0: HSYNC2 is Active High<br>1: HSYNC2 is Active Low                                                                                     |

|         |                           | 2      | VSYNC1<br>Polarity                     | 0: VSYNC1 is Active High<br>1: VSYNC1 is Active Low                                                                                     |

|         |                           | 3      | VSYNC2<br>Polarity                     | 0: VSYNC2 is Active High<br>1: VSYNC2 is Active Low                                                                                     |

|         |                           | 4      | HSYNC1<br>Trilevel                     | 0: HSYNC1 is Standard Sync<br>1: HSYNC1 is Trilevel Sync                                                                                |

|         |                           | 5      | HSYNC2<br>Trilevel                     | 0: HSYNC2 is Standard Sync<br>1: HSYNC2 is Trilevel Sync                                                                                |

|         |                           | 7:6    | N/A                                    | Returns 0                                                                                                                               |

| 0x03    | HSYNC Slicer (0x44)       | 2:0    | HSYNC1 Threshold                       | 000 = lowest (0.4V) All values referred to<br>100 = default (2.0V) voltage at HSYNC input<br>111 = highest (3.2V) pin, 240mV hysteresis |

|         |                           | 3      | Reserved                               | Set to 00                                                                                                                               |

|         |                           | 6:4    | HSYNC2 Threshold                       | See HSYNC1                                                                                                                              |

|         |                           | 7      | Disable Glitch Filter                  | 0: HSYNC/VSYNC Digital Glitch Filter Enabled (default) 1: HSYNC/VSYNC Digital Glitch Filter Disabled                                    |

| 0x04    | SOG Slicer (0x08)         | 3:0    | SOG1 and SOG2<br>Threshold             | 0x0 = lowest (0mV) 40mV hysteresis at<br>0x8 = default (160mV) all settings<br>0xF = highest (300mV) 20mV step size                     |

|         |                           | 4      | SOG Filter<br>Enable                   | 0: SOG low pass filter disabled (default) 1: SOG low pass filter enabled, 14MHz corner                                                  |

|         |                           | 5      | SOG Hysteresis<br>Disable              | 0: 40mV SOG hysteresis enabled<br>1: 40mV SOG hysteresis disabled (default)                                                             |

|         |                           | 7:6    | Reserved                               | Set to 00.                                                                                                                              |

| ADDRESS | REGISTER (DEFAULT VALUE)        | BIT(s) | FUNCTION NAME            | DESCRIPTION                                                                                                                                                                                  |

|---------|---------------------------------|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x05    | Input configuration (0x00)      | 0      | Channel Select           | 0: VGA1<br>1: VGA2                                                                                                                                                                           |

|         |                                 | 1      | Input Coupling           | 0: AC coupled (positive input connected to clamp DAC during clamp time, negative input disconnected from outside pad and always internally tied to appropriate clamp DAC)                    |

|         |                                 |        |                          | 1: DC coupled (+ and - inputs are brought to pads and never connected to clamp DACs). Analog clamp signal is turned off in this mode.                                                        |

|         |                                 | 2      | RGB/YUV                  | 0: RGB inputs (Clamp DAC = 300mV for R, G, B, half scale analog shift for R, G, and B, base ABLC $^{TM}$ target code = 0x00 for R, G, and B)                                                 |

|         |                                 |        |                          | 1: YUV inputs (Clamp DAC = 600mV for R and B, 300mV for G, half scale analog shift for G channel only, base ABLC™ target code = 0x00 for G, = 0x80 for R and B)                              |

|         |                                 | 3      | Sync Type                | 0: Separate HSYNC/VSYNC 1: Composite (from SOG or CSYNC on HSYNC)                                                                                                                            |

|         |                                 | 4      | Composite Sync<br>Source | 0: SOG <sub>IN</sub> 1: HSYNC <sub>IN</sub> Note: If Sync Type = 0, the multiplexer will pass HSYNC <sub>IN</sub> regardless of the state of this bit.                                       |

|         |                                 | 5      | COAST CLAMP<br>enable    | 0: DC restore clamping and ABLC™ suspended during COAST 1: DC restore clamping and ABLC™ continue during COAST                                                                               |

|         |                                 | 7:6    | Reserved                 | Set to 00.                                                                                                                                                                                   |

| 0x06    | Red Gain (0x55)                 | 7:0    | Red Gain                 | Channel gain, where:<br>gain (V/V) = 0.5 + [7:0]/170                                                                                                                                         |

| 0x07    | Green Gain (0x55)               | 7:0    | Green Gain               | 0x00: gain = 0.5 V/V<br>(1.4VP-P input = full range of ADC)                                                                                                                                  |

| 0x08    | Blue Gain (0x55)                | 7:0    | Blue Gain                | 0x55: gain = 1.0 V/V<br>(0.7VP-P input = full range of ADC)                                                                                                                                  |

|         |                                 |        |                          | 0xFF: gain = 2.0 V/V<br>(0.35VP-P input = full range of ADC)                                                                                                                                 |

| 0x09    | Red Offset (0x80)               | 7:0    | Red Offset               | ABLC™ enabled: digital offset control. A 1 LSB change in this register will shift the ADC output by 1 LSB.                                                                                   |

| 0x0A    | Green Offset (0x80)             | 7:0    | Green Offset             | ABLC™ disabled: analog offset control. These bits go to the upper 8 bits of the 10 bit offset DAC. A 1LSB change in this register will shift the ADC output approximately 1 LSB (Offset      |

| 0x0B    | Blue Offset (0x80)              | 7:0    | Blue Offset              | DAC range = 0) or 0.5LSBs (Offset DAC range = 1).  0x00 = min DAC value or -0x80 digital offset,  0x80 = mid DAC value or 0x00 digital offset,  0xFF = max DAC value or +0x7F digital offset |

| 0x0C    | Offset DAC Configuration (0x00) | 0      | Offset DAC Range         | 0: ±1/2 ADC fullscale (1 DAC LSB ~ 1 ADC LSB)<br>1: ±1/4 ADC fullscale (1 DAC LSB ~ 1/2 ADC LSB)                                                                                             |

|         |                                 | 1      | Reserved                 | Set to 0.                                                                                                                                                                                    |

|         |                                 | 3:2    | Red Offset DAC LSBs      |                                                                                                                                                                                              |

|         |                                 | 5:4    | Green Offset DAC<br>LSBs | DAC control.  Combine with their respective MSBs in registers 0x09, 0x0A, and 0x0B to achieve 10 bit offset DAC control.                                                                     |

|         |                                 | 7:6    | Blue Offset DAC<br>LSBs  |                                                                                                                                                                                              |

| ADDRESS | REGISTER (DEFAULT VALUE)                       | BIT(s) | FUNCTION NAME                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------|------------------------------------------------|--------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x0D    | AFE Bandwidth (0x0E)                           | 0      | Unused                                    | Value doesn't matter                                                                                                                                                                                                                                                                                                                                                                         |  |

|         |                                                | 3:1    | AFE BW                                    | 3dB point for AFE lowpass filter<br>000: 100MHz<br>111: 780MHz (default)                                                                                                                                                                                                                                                                                                                     |  |

|         |                                                | 7:4    | Peaking                                   | 0000: Disabled (default) See Bandwidth and Peaking Control section for more information                                                                                                                                                                                                                                                                                                      |  |

| 0x0E    | PLL Htotal MSB (0x03)                          | 5:0    | PLL Htotal MSB                            | 14 bit HTOTAL (number of active pixels) value                                                                                                                                                                                                                                                                                                                                                |  |

| 0x0F    | PLL Htotal LSB (0x20)                          | 7:0    | PLL Htotal LSB                            | The minimum HTOTAL value supported is 0x200. HTOTAL to PLL is updated on LSB write only.                                                                                                                                                                                                                                                                                                     |  |

| 0x10    | PLL Sampling Phase (0x00)                      | 5:0    | PLL Sampling Phase                        | Used to control the phase of the ADC's sample point relative to the period of a pixel. Adjust to obtain optimum image quality. One step = 5.625° (1.56% of pixel period).                                                                                                                                                                                                                    |  |

| 0x11    | PLL Pre-coast (0x08)                           | 7:0    | Pre-coast                                 | Number of lines the PLL will coast prior to the start of VSYNC. Applies only to internally generated COAST signals.                                                                                                                                                                                                                                                                          |  |

| 0x12    | PLL Post-coast (0x00)                          | 7:0    | Post-coast                                | Number of lines the PLL will coast after the end of VSYNC. Applies only to internally generated COAST signals.                                                                                                                                                                                                                                                                               |  |

| 0x13    | PLL Misc (0x00)                                | 0      | PLL Lock Edge<br>HSYNC1                   | 0: Lock on trailing edge of HSYNC1 (default) 1: Lock on leading edge of HSYNC1                                                                                                                                                                                                                                                                                                               |  |

|         |                                                | 1      | PLL Lock Edge<br>HSYNC2                   | 0: Lock on trailing edge of HSYNC2 (default) 1: Lock on leading edge of HSYNC2                                                                                                                                                                                                                                                                                                               |  |

|         |                                                | 2      | Reserved                                  | Set to 0.                                                                                                                                                                                                                                                                                                                                                                                    |  |

|         |                                                | 3      | CLKINV <sub>IN</sub> Pin<br>Disable       | 0: CLKINV <sub>IN</sub> pin enabled (default) 1: CLKINV <sub>IN</sub> pin disabled (internally forced low)                                                                                                                                                                                                                                                                                   |  |

|         |                                                | 5:4    | CLKINV <sub>IN</sub> Pin<br>Function      | 00: CLKINV (default) 01: External CLAMP (see Note) 10: External COAST 11: External PIXCLK Note: the CLAMP pulse is used to - perform a DC restore (if enabled) - start the ABLC™ function (if enabled), and - update the data to the Offset DACs (always).                                                                                                                                   |  |

|         |                                                |        |                                           | When in the default internal CLAMP mode, the X98017 automatically generates the CLAMP pulse. If External CLAMP is selected, the Offset DAC values will only change on the leading edge of CLAMP. If there is no internal clamp signal, there will be up to a 100ms delay between when the PGA gain or offset DAC register is written to, and when the PGA or offset DAC is actually updated. |  |

|         |                                                | 6      | XTALCLKOUT<br>Frequency                   | 0: XTALCLK <sub>OUT</sub> = f <sub>CRYSTAL</sub> (default)<br>1: XTALCLK <sub>OUT</sub> = f <sub>CRYSTAL</sub> /2                                                                                                                                                                                                                                                                            |  |

|         |                                                | 7      | Disable<br>XTALCLKOUT                     | 0 = XTALCLK <sub>OUT</sub> enabled<br>1 = XTALCLK <sub>OUT</sub> is logic low                                                                                                                                                                                                                                                                                                                |  |

| 0x14    | DC Restore and ABLC™ starting pixel MSB (0x00) | 4:0    | DC Restore and ABLC™ starting pixel (MSB) | Pixel after HSYNC <sub>IN</sub> trailing edge to begin DC restore and ABLC™ functions. 13 bits. Set this register first stable black pixel following the                                                                                                                                                                                                                                     |  |

| 0x15    | DC Restore and ABLC™ starting pixel LSB (0x00) | 7:0    | DC Restore and ABLC™ starting pixel (LSB) | trailing edge of HSYNC <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x16    | DC Restore Clamp Width (0x10)                  | 7:0    | DC Restore clamp width (pixels)           | Width of DC restore clamp used in AC-coupled configurations. Has no effect on ABLC™. Minimum value is 0x02 (a setting of 0x01 or 0x00 will not generate a clamp pulse).                                                                                                                                                                                                                      |  |

| ADDRESS | REGISTER (DEFAULT VALUE)     | BIT(s) | FUNCTION NAME                    | DESCRIPTION                                                                                                                                                                                                                                                                                    |

|---------|------------------------------|--------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x17    | ABLC™ Configuration (0x40)   | 0      | ABLC™ disable                    | 0: ABLC™ enabled (default)<br>1: ABLC™ disabled                                                                                                                                                                                                                                                |

|         |                              | 1      | Reserved                         | Set to 0.                                                                                                                                                                                                                                                                                      |

|         |                              | 3:2    | ABLC™ pixel width                | Number of black pixels averaged every line for ABLC™ function 00: 16 pixels [default] 01: 32 pixels 10: 64 pixels 11: 128 pixels                                                                                                                                                               |

|         |                              | 6:4    | ABLC™ bandwidth                  | ABLC™ Time constant (lines) = 2 <sup>(5+[6:4])</sup> 000 = 32 lines 100 = 512 lines (default) 111 = 4096 lines                                                                                                                                                                                 |

|         |                              | 7      | Reserved                         | Set to 0.                                                                                                                                                                                                                                                                                      |

| 0x18    | Output Format (0x00)         | 0      | Bus Width                        | 0: 24 bits: Data output on R <sub>P</sub> , G <sub>P</sub> , B <sub>P</sub> only; R <sub>S</sub> , G <sub>S</sub> , B <sub>S</sub> are all driven low (default) 1: 48 bits: Data output on R <sub>P</sub> , G <sub>P</sub> , B <sub>P</sub> , R <sub>S</sub> , G <sub>S</sub> , B <sub>S</sub> |

|         |                              | 1      | Interleaving (48 bit mode only)  | 0: No interleaving: data changes on same edge of DATACLK (default) 1: Interleaved: Secondary databus data changes on opposite edge of DATACLK from primary databus                                                                                                                             |

|         |                              | 2      | Bus Swap<br>(48 bit mode only)   | 0: First data byte after trailing edge of HSOUT appears on R <sub>P</sub> , G <sub>P</sub> , B <sub>P</sub> (default)  1: First data byte after trailing edge of HSOUT appears on R <sub>S</sub> , G <sub>S</sub> , B <sub>S</sub> (primary and secondary busses are reversed)                 |

|         |                              | 3      | Reserved                         | Set to 0.                                                                                                                                                                                                                                                                                      |

|         |                              | 4      | 422<br>(24 bit mode only)        | 0: Data is formatted as 4:4:4 (RGB, default) 1: Data is decimated to 4:2:2 (YUV), blue channel is driven low                                                                                                                                                                                   |

|         |                              | 5      | DATACLK<br>Polarity              | 0: HS <sub>OUT</sub> , VS <sub>OUT</sub> , and Pixel Data change on falling edge of DATACLK (default) 1: HS <sub>OUT</sub> , VS <sub>OUT</sub> , and Pixel Data change on rising edge of DATACLK                                                                                               |

|         |                              | 6      | VSOUT Polarity                   | 0: Active High (default) 1: Active Low                                                                                                                                                                                                                                                         |

|         |                              | 7      | HSOUT Polarity                   | 0: Active High (default) 1: Active Low                                                                                                                                                                                                                                                         |

| 0x19    | HSOUT Width (0x10)           | 7:0    | HSOUT Width                      | HSOUT width, in pixels. Minimum value is 0x01 for 24 bit modes, 0x02 for 48 bit modes.                                                                                                                                                                                                         |

| 0x1A    | Output Signal Disable (0x00) | 0      | Three-state R <sub>P</sub> [7:0] | 0 = Output byte enabled                                                                                                                                                                                                                                                                        |

|         |                              | 1      | Three-state R <sub>S</sub> [7:0] | 1 = Output byte three-stated These bits override all other I/O settings                                                                                                                                                                                                                        |

|         |                              | 2      | Three-state G <sub>P</sub> [7:0] | Output data pins have $58k\Omega$ pulldown resistors to GND <sub>D</sub> .                                                                                                                                                                                                                     |

|         |                              | 3      | Three-state G <sub>S</sub> [7:0] |                                                                                                                                                                                                                                                                                                |

|         |                              | 4      | Three-state B <sub>P</sub> [7:0] |                                                                                                                                                                                                                                                                                                |