## Precision 2:6 LVDS Fanout Buffer with Glitchfree Input Reference Switching and On-Chip Input Termination

Data Sheet

November 2012

#### **Features**

#### Inputs/Outputs

- Accepts two differential or single-ended inputs

- LVPECL, LVDS, CML, HCSL, LVCMOS

- · Glitch-free switching of references

- On-chip input termination and biasing for AC coupled inputs

- · Six precision LVDS outputs

- Operating frequency up to 750 MHz

#### **Power**

- Option for 2.5 V or 3.3 V power supply

- Current consumption of 97 mA

- On-chip Low Drop Out (LDO) Regulator for superior power supply rejection

#### **Performance**

Ultra low additive jitter of 165 fs RMS

#### Ordering Information

ZL40221LDG1 32 Pin QFN Trays ZL40221LDF1 32 Pin QFN Tape and Reel

Matte Tin

Package size: 5 x 5 mm -40°C to +85°C

## **Applications**

- · General purpose clock distribution

- · Low jitter clock trees

- Logic translation

- · Clock and data signal restoration

- Redundant clock distribution

- Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC

- Wireless communications

- High performance micro-processor clock distribution

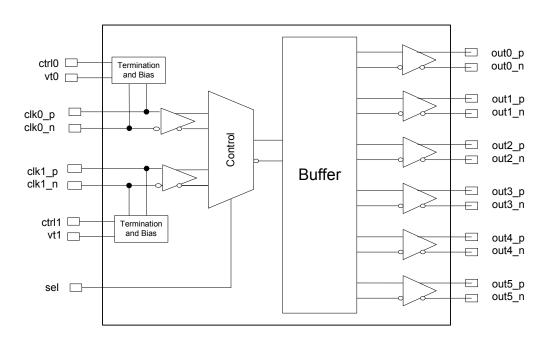

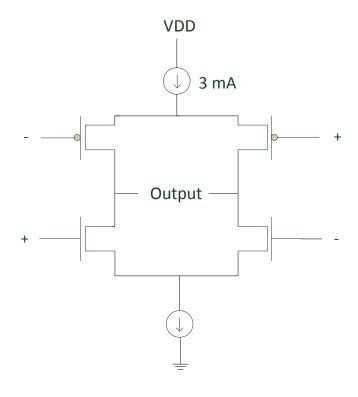

Figure 1 - Functional Block Diagram

## **Table of Contents**

| Features                                 |    |

|------------------------------------------|----|

| Applications                             |    |

| 1.0 Package Description                  |    |

| 2.0 Pin Description                      |    |

| 3.0 Functional Description               |    |

| 3.1 Clock Inputs                         |    |

| 3.1.1 Clock Input Selection              |    |

| 3.1.2 Clock Input Terminations           |    |

| 3.2 Clock Outputs                        |    |

| 3.3 Device Additive Jitter               |    |

| 3.4 Power Supply                         |    |

| 3.4.1 Sensitivity to power supply noise  |    |

| 3.4.2 Power supply filtering             |    |

| 3.4.3 PCB layout considerations          |    |

| 4.0 AC and DC Electrical Characteristics |    |

| 5.0 Performance Characterization         |    |

| 6.0 Typical Behavior                     |    |

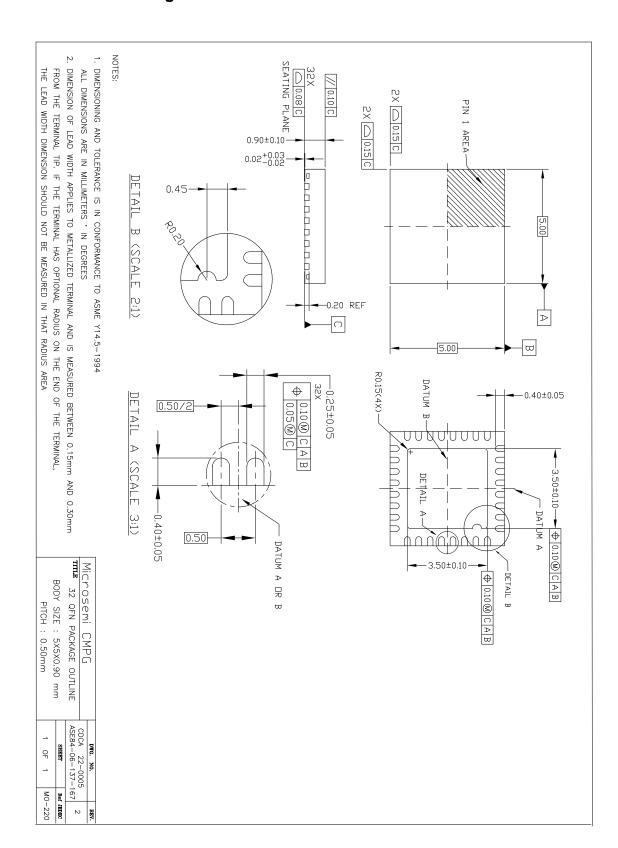

| 7.0 Package Characteristics              |    |

| 8.0 Mechanical Drawing                   | 22 |

## **List of Figures**

| Figure 1 - Functional Block Diagram                                     | 1    |

|-------------------------------------------------------------------------|------|

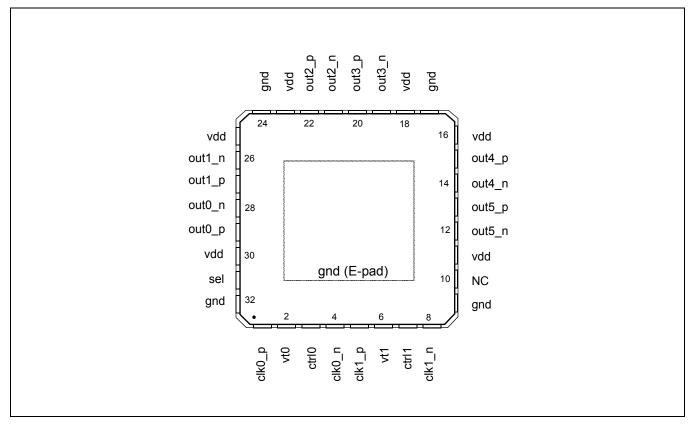

| Figure 2 - Pin Connections                                              |      |

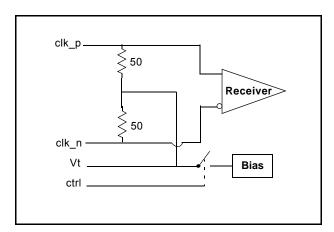

| Figure 3 - Simplified Diagram of input stage                            | 6    |

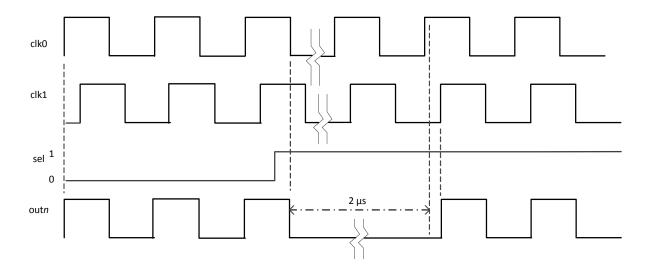

| Figure 4 - Output During Clock Switch - Both Clocks Running             |      |

| Figure 5 - Clock Input - LVPECL - DC Coupled                            |      |

| Figure 6 - Clock Input - LVPECL - AC Coupled                            | 8    |

| Figure 7 - Clock Input - LVDS - DC Coupled                              |      |

| Figure 8 - Clock Input - LVDS - AC Coupled                              | 9    |

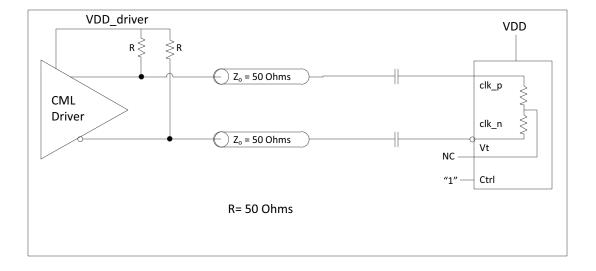

| Figure 9 - Clock Input - CML- AC Coupled                                | 9    |

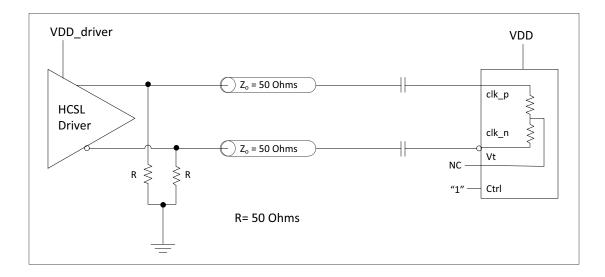

| Figure 10 - Clock Input - HCSL- AC Coupled                              |      |

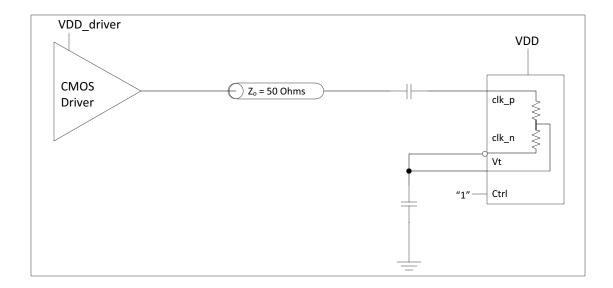

| Figure 11 - Clock Input - AC-coupled Single-Ended                       | . 10 |

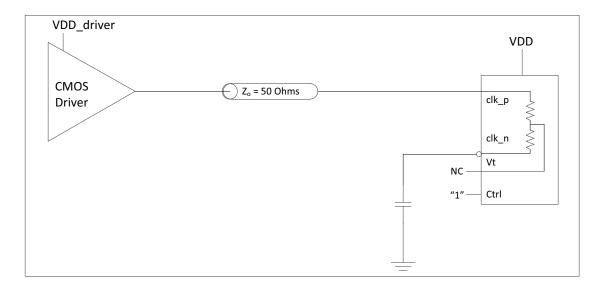

| Figure 12 - Clock Input - DC-coupled 3.3V CMOS                          | . 11 |

| Figure 13 - Simplified LVDS Output Driver                               | . 12 |

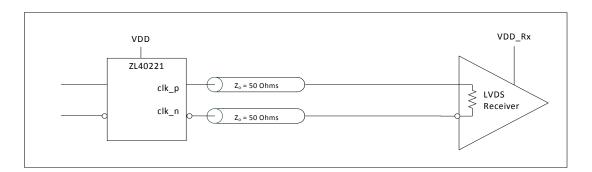

| Figure 14 - LVDS DC Coupled Termination (Internal Receiver Termination) | . 12 |

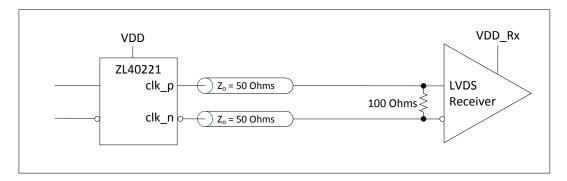

| Figure 15 - LVDS DC Coupled Termination (External Receiver Termination) | . 13 |

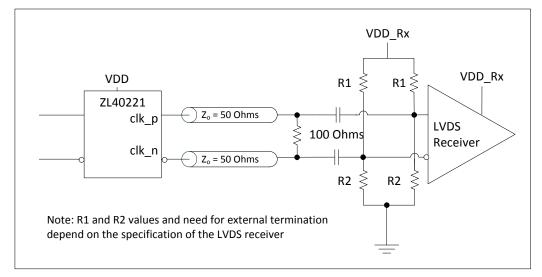

| Figure 16 - LVDS AC Coupled Termination                                 | . 13 |

| Figure 17 - LVDS AC Output Termination for CML Inputs                   | . 14 |

| Figure 18 - Additive Jitter                                             | . 15 |

| Figure 19 - Decoupling Connections for Power Pins                       | . 16 |

| Figure 20 - Differential Voltage Parameter                              | . 18 |

| Figure 21 - Input To Output Timing                                      | . 18 |

## 1.0 Package Description

The device is packaged in a 32 pin QFN

Figure 2 - Pin Connections

ZL40221 Data Sheet

## 2.0 Pin Description

| Pin #                        | Name                              | Description                                                                                                                                                                                                                                                                                                                            |

|------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4,<br>5, 8                | clk0_p, clk0_n,<br>clk1_p, clk1_n | <b>Differential Input (Analog Input).</b> Differential (or singled ended) input signals. For all input signal configuration see Section 3.1, "Clock Inputs".                                                                                                                                                                           |

| 2, 6                         | vt0, vt1                          | On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohm termination resistors.  For a DC coupled LVPECL input connect this pin through a resistor to ground; 50 Ohms for 3.3V LVPECL or 20 Ohms for 2.5V LVPECL.  For a DC coupled LVDS input or for an AC coupled differential input, leave this pin unconnected. |

| 3, 7                         | ctrl0, ctrl1                      | Digital Control for On-Chip Input Termination (Input). Selects differential input mode; 0: DC coupled LVPECL or LVDS modes 1: AC coupled differential modes These pins are internally pulled down to GND.                                                                                                                              |

| 29, 28,                      | out0_p, out0_n                    | Differential Output (Analog Output). Differential outputs.                                                                                                                                                                                                                                                                             |

| 27, 26,                      | out1_p, out1_n                    |                                                                                                                                                                                                                                                                                                                                        |

| 22, 21,                      | out2_p, out2_n                    |                                                                                                                                                                                                                                                                                                                                        |

| 20, 19,                      | out3_p, out3_n                    |                                                                                                                                                                                                                                                                                                                                        |

| 15, 14,                      | out4_p, out4_n                    |                                                                                                                                                                                                                                                                                                                                        |

| 13, 12                       | out5_p, out5_n                    |                                                                                                                                                                                                                                                                                                                                        |

| 11, 16,<br>18, 23,<br>25, 30 | vdd                               | Positive Supply Voltage. 2.5V <sub>DC</sub> or 3.3 V <sub>DC</sub> nominal.                                                                                                                                                                                                                                                            |

| 9, 17,<br>24, 32             | gnd                               | Ground. 0 V.                                                                                                                                                                                                                                                                                                                           |

| 31                           | sel                               | Input Select (Input). Selects the reference input that is buffered; 0: clk0 1: clk1 This pin is internally pulled down to GND.                                                                                                                                                                                                         |

| 10                           | NC                                | No Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                      |

## 3.0 Functional Description

he ZL40221 is an LVDS clock fanout buffer with six output clock drivers capable of operating at frequencies up to 750MHz.

The ZL40221 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40221 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.

The ZL40221 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.

The device block diagram is shown in Figure 1; its operation is described in the following sections.

#### 3.1 Clock Inputs

The device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.

Figure 3 - Simplified Diagram of input stage

#### 3.1.1 Clock Input Selection

The select line chooses which input clock is routed to the outputs.

| Sel | Active Input |

|-----|--------------|

| 0   | clk0         |

| 1   | clk1         |

**Table 1 - Input Selection**

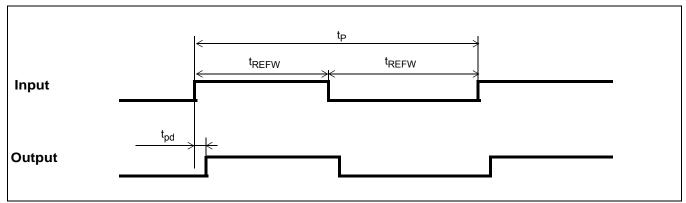

The following figure shows the expected clock switching performance. The output stops at the first falling edge of the initial clock after the select pin changes state. During switching there will be a short time when the output clock is not toggling. After this delay, the output will start toggling again with a rising edge of the newly selected clock. This behavior is independent of the frequencies of the input clocks. For instance, the two clocks could be at different frequencies and the behavior would still be consistent with this figure.

Figure 4 - Output During Clock Switch - Both Clocks Running

## 3.1.2 Clock Input Terminations

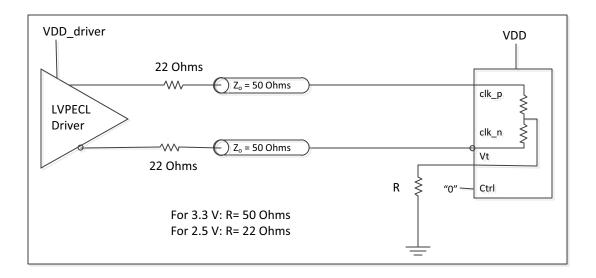

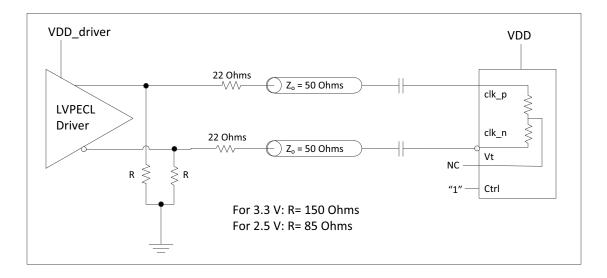

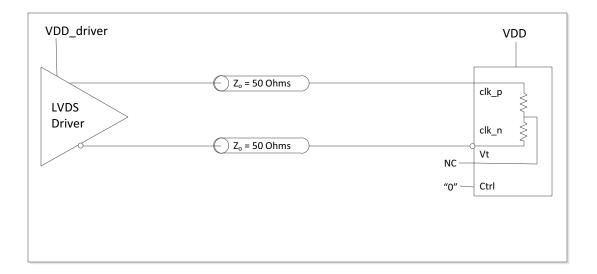

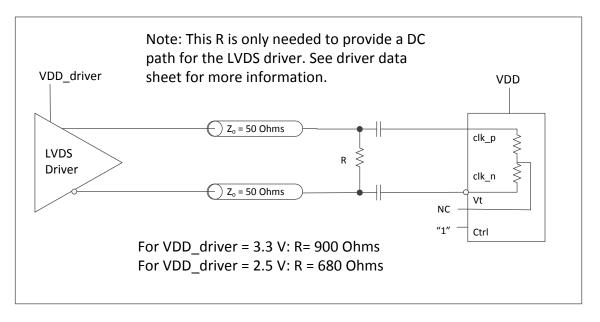

This following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the *Vt* and *ctrl* pins in each case.

In the following diagrams were the *ctrl* pin is '1' and the *Vt* pin is not connected, the *Vt* pin can be instead connected to  $V_{DD}$  with a capacitor. A capacitor can also help in Figure 5 between *Vt* and  $V_{DD}$ . This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.

Figure 5 - Clock Input - LVPECL - DC Coupled

Figure 6 - Clock Input - LVPECL - AC Coupled

Figure 7 - Clock Input - LVDS - DC Coupled

ZL40221 Data Sheet

Figure 8 - Clock Input - LVDS - AC Coupled

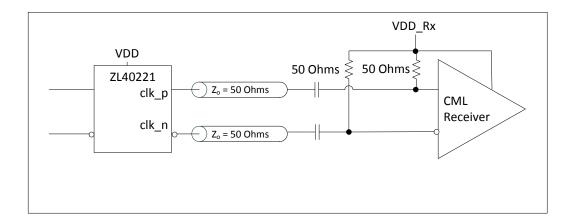

Figure 9 - Clock Input - CML- AC Coupled

Figure 10 - Clock Input - HCSL- AC Coupled

Figure 11 - Clock Input - AC-coupled Single-Ended

Figure 12 - Clock Input - DC-coupled 3.3V CMOS

## 3.2 Clock Outputs

LVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 13.

Figure 13 - Simplified LVDS Output Driver

The methods to terminate the ZL40221 drivers are shown in the following figures.

Figure 14 - LVDS DC Coupled Termination (Internal Receiver Termination)

Figure 15 - LVDS DC Coupled Termination (External Receiver Termination)

Figure 16 - LVDS AC Coupled Termination

Figure 17 - LVDS AC Output Termination for CML Inputs

ZL40221 Data Sheet

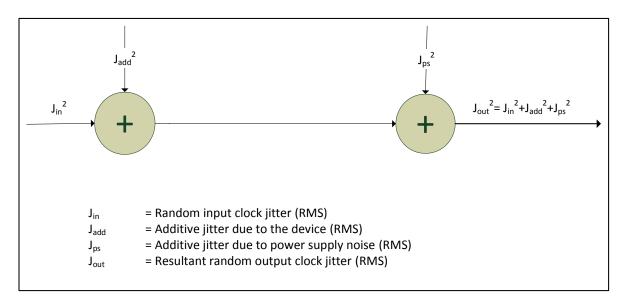

#### 3.3 Device Additive Jitter

The ZL40221 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40221 is random and as such it is not correlated to the jitter of the input clock signal.

The square of the resultant random RMS jitter at the output of the ZL40221 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.

Figure 18 - Additive Jitter

## 3.4 Power Supply

This device operates with either a 2.5V supply or 3.3V supply.

#### 3.4.1 Sensitivity to power supply noise

Power supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40221 is equipped with an on-chip linear power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip measures in combination with the simple recommended power supply filtering and PCB layout minimize additive jitter from power supply noise.

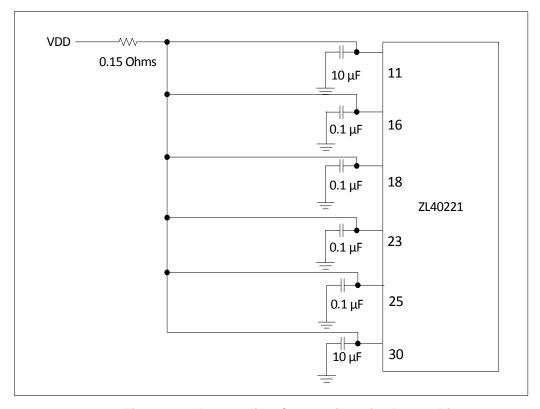

#### 3.4.2 Power supply filtering

For optimal jitter performance, the ZL40221 should be isolated from the power planes connected to its power supply pins as shown in Figure 19.

- 10 μF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating

- 0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating

- · Capacitors should be placed next to the connected device power pins

Figure 19 - Decoupling Connections for Power Pins

#### 3.4.3 PCB layout considerations

The power supply filtering shown in Figure 19 can be implemented either as a plane island, or as a routed power topology with equal effect.

#### 4.0 **AC and DC Electrical Characteristics**

### **Absolute Maximum Ratings\***

|   | Parameter                  | Sym.               | Min. | Max.     | Units |

|---|----------------------------|--------------------|------|----------|-------|

| 1 | Supply voltage             | $V_{DD_R}$         | -0.5 | 4.6      | V     |

| 2 | Voltage on any digital pin | V <sub>PIN</sub>   | -0.5 | $V_{DD}$ | V     |

| 3 | LVPECL output current      | l <sub>out</sub>   |      | 30       | mA    |

| 4 | Soldering temperature      | Т                  |      | 260      | °C    |

| 5 | Storage temperature        | T <sub>ST</sub>    | -55  | 125      | °C    |

| 6 | Junction temperature       | Tj                 |      | 125      | °C    |

| 7 | Voltage on input pin       | V <sub>input</sub> |      | $V_{DD}$ | V     |

| 8 | Input capacitance each pin | C <sub>p</sub>     |      | 500      | fF    |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

\* Voltages are with respect to ground (GND) unless otherwise stated

### **Recommended Operating Conditions\***

|   | Characteristics           | Sym.           | Min.  | Тур. | Max.  | Units |

|---|---------------------------|----------------|-------|------|-------|-------|

| 1 | Supply voltage 2.5 V mode | $V_{DD25}$     | 2.375 | 2.5  | 2.625 | V     |

| 2 | Supply voltage 3.3 V mode | $V_{DD33}$     | 3.135 | 3.3  | 3.465 | V     |

| 3 | Operating temperature     | T <sub>A</sub> | -40   | 25   | 85    | °C    |

<sup>\*</sup> Voltages are with respect to ground (GND) unless otherwise stated

### **DC Electrical Characteristics - Current Consumption**

|   | Characteristics                                               | Sym.                 | Min. | Тур. | Max. | Units | Notes |

|---|---------------------------------------------------------------|----------------------|------|------|------|-------|-------|

| 1 | Supply current LVDS drivers - loaded (all outputs are active) | I <sub>dd_load</sub> |      | 97   |      | mA    |       |

### DC Electrical Characteristics - Inputs and outputs - for 2.5/3.3 V supply

|   | Characteristics                          | Sym.             | Min.                | Тур. | Max.                | Units | Notes                 |

|---|------------------------------------------|------------------|---------------------|------|---------------------|-------|-----------------------|

| 1 | CMOS control logic high-level input      | V <sub>CIH</sub> | 0.7*V <sub>DD</sub> |      |                     | ٧     |                       |

| 2 | CMOS control logic low-level input       | V <sub>CIL</sub> |                     |      | 0.3*V <sub>DD</sub> | ٧     |                       |

| 3 | CMOS control logic Input leakage current | I <sub>IL</sub>  |                     | 1    |                     | μΑ    | $V_I = V_{DD}$ or 0 V |

| 4 | Differential input voltage difference    | $V_{ID}$         | 0.25                |      | 1                   | V     |                       |

| 5 | Differential input common mode           | V <sub>CM</sub>  | 1.1                 |      | 1.6                 | V     | for 2.5 V             |

| 6 | Differential input common mode           | V <sub>CM</sub>  | 1.1                 |      | 2.0                 | ٧     | for 3.3 V             |

| 7 | Differential input resistance            | $V_{IR}$         | 80                  | 100  | 120                 | ohm   |                       |

## DC Electrical Characteristics - Inputs and outputs - for 2.5/3.3 V supply

|   | Characteristics                   | Sym.            | Min. | Тур. | Max.  | Units | Notes |

|---|-----------------------------------|-----------------|------|------|-------|-------|-------|

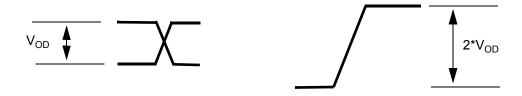

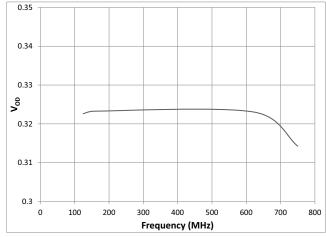

| 8 | LVDS output differential voltage* | V <sub>OD</sub> | 0.25 | 0.30 | 0.40  | V     |       |

| 9 | LVDS output common mode           | $V_{CM}$        | 1.1  | 1.25 | 1.375 | V     |       |

<sup>\*</sup> The VOD parameter was measured from 125 MHz to 750 MHz.

Figure 20 - Differential Voltage Parameter

## AC Electrical Characteristics\* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.

|   | Characteristics                         | Sym.                                | Min. | Тур. | Max. | Units   | Notes |

|---|-----------------------------------------|-------------------------------------|------|------|------|---------|-------|

| 1 | Maximum Operating Frequency             | 1/t <sub>p</sub>                    |      |      | 750  | MHz     |       |

| 2 | Input to output clock propagation delay | t <sub>pd</sub>                     | 0    | 1    | 2    | ns      |       |

| 3 | Output to output skew                   | t <sub>out2out</sub>                |      | 80   | 150  | ps      |       |

| 4 | Part to part output skew                | t <sub>part2part</sub>              |      | 120  | 300  | ps      |       |

| 5 | Output clock Duty Cycle degradation     | t <sub>PWH</sub> / t <sub>PWL</sub> | -5   | 0    | 5    | Percent |       |

| 6 | LVDS Output slew rate                   | r <sub>sl</sub>                     | 0.55 |      |      | V/ns    |       |

| 7 | Reference transition time               | t <sub>switch</sub>                 |      | 2    | 3    | us      |       |

<sup>\*</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions

Figure 21 - Input To Output Timing

## 5.0 Performance Characterization

#### Additive Jitter at 2.5 V\*

|   | Output Frequency (MHz) | Jitter<br>Measurement<br>Filter | Typical<br>RMS (fs) | Notes |

|---|------------------------|---------------------------------|---------------------|-------|

| 1 | 125                    | 12 kHz - 20 MHz                 | 229                 |       |

| 2 | 212.5                  | 12 kHz - 20 MHz                 | 217                 |       |

| 3 | 311.04                 | 12 kHz - 20 MHz                 | 194                 |       |

| 4 | 425                    | 12 kHz - 20 MHz                 | 186                 |       |

| 5 | 500                    | 12 kHz - 20 MHz                 | 169                 |       |

| 6 | 622.08                 | 12 kHz - 20 MHz                 | 165                 |       |

| 7 | 750                    | 12 kHz - 20 MHz                 | 178                 |       |

<sup>\*</sup>The values in this table were taken with an approximate slew rate of 0.8 V/ns.

#### Additive Jitter at 3.3 V\*

|   | Output Frequency (MHz) | Jitter<br>Measurement<br>Filter | Typical<br>RMS (fs) | Notes |

|---|------------------------|---------------------------------|---------------------|-------|

| 1 | 125                    | 12 kHz - 20 MHz                 | 231                 |       |

| 2 | 212.5                  | 12 kHz - 20 MHz                 | 217                 |       |

| 3 | 311.04                 | 12 kHz - 20 MHz                 | 196                 |       |

| 4 | 425                    | 12 kHz - 20 MHz                 | 190                 |       |

| 5 | 500                    | 12 kHz - 20 MHz                 | 173                 |       |

| 6 | 622.08                 | 12 kHz - 20 MHz                 | 167                 |       |

| 7 | 750                    | 12 kHz - 20 MHz                 | 181                 |       |

<sup>\*</sup>The values in this table were taken with an approximate slew rate of 0.8 V/ns.

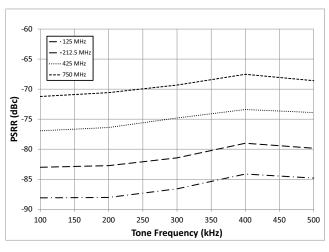

## Additive jitter from a power supply tone\*

| Carrier frequency | Parameter           | Typical | Units  | Notes |

|-------------------|---------------------|---------|--------|-------|

| 125               | 25 mV<br>at 100 kHz | 41      | fs RMS |       |

| 750               | 25 mV<br>at 100 kHz | 43      | fs RMS |       |

<sup>\*</sup> The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for  $V_{DD}$  = 3.3 V. The magnitude of the interfering tone is measured at the DUT.

## 6.0 Typical Behavior

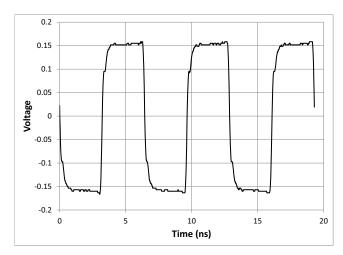

Typical Waveform at 155.52 MHz

V<sub>OD</sub> vs Frequency

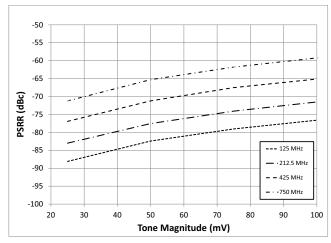

Power Supply Tone Frequency versus PSRR

Power Supply Tone Magnitude versus PSRR

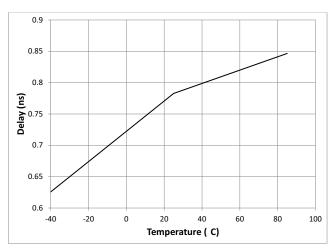

Propogation Delay versus Temperature

Note: This is for a single device. For more details, see the characterization section.

## 7.0 Package Characteristics

## **Thermal Data**

| Parameter                              | Symbol            | Test Condition | Value | Unit |

|----------------------------------------|-------------------|----------------|-------|------|

| Junction to Ambient Thermal Resistance | $\Theta_{JA}$     | Still Air      | 37.4  | °C/W |

|                                        |                   | 1 m/s          | 33.1  |      |

|                                        |                   | 2 m/s          | 31.5  |      |

| Junction to Case Thermal Resistance    | Θ <sub>JC</sub>   |                | 24.4  | °C/W |

| Junction to Board Thermal Resistance   | $\Theta_{JB}$     |                | 19.5  | °C/W |

| Maximum Junction Temperature*          | T <sub>jmax</sub> |                | 125   | °C   |

| Maximum Ambient Temperature            | T <sub>A</sub>    |                | 85    | °C   |

## 8.0 Mechanical Drawing

# For more information about all Microsemi productsvisit our Web Site at www.microsemi.com

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

Purchase of Microsemi's I2C components conveys a license under the Philips I2C Patent rights to use these components in an I2C System, provided that the system conforms to the I2C Standard Specification as defined by Philips.

Microsemi, ZL, and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Microsemi Corporation.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331