### 28/40-Pin, 8-Bit CMOS Microcontrollers w/ 12-Bit A/D

#### Microcontroller Core Features:

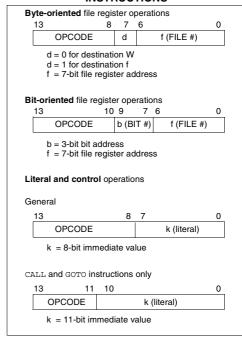

- High-performance RISC CPU

- · Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input

DC 200 ns instruction cycle

- 4K x 14 words of Program Memory, 256 x 8 bytes of Data Memory (RAM)

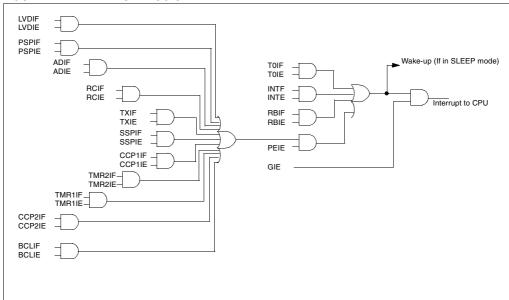

- Interrupt capability (up to 14 internal/external interrupt sources)

- · Eight level deep hardware stack

- · Direct, indirect, and relative addressing modes

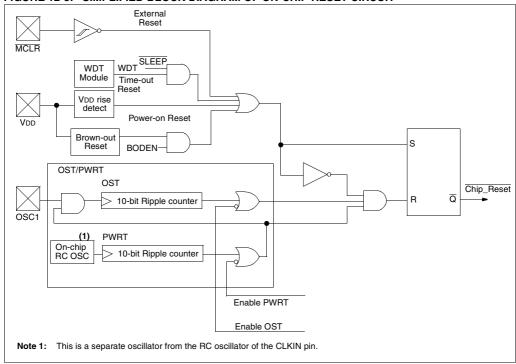

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

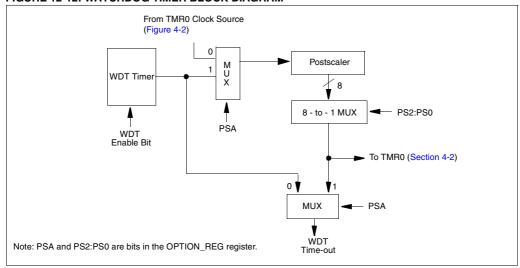

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code-protection

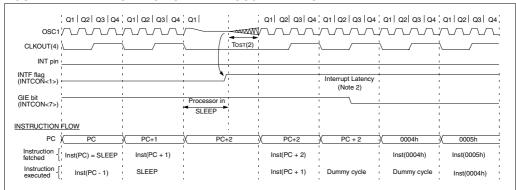

- Power saving SLEEP mode

- · Selectable oscillator options

- Low-power, high-speed CMOS EPROM technology

- · Fully static design

- In-Circuit Serial Programming™ (ISCP)

- Wide operating voltage range: 2.5V to 5.5V

- High Sink/Source Current 25/25 mA

- · Commercial and Industrial temperature ranges

- Low-power consumption:

- < 2 mA @ 5V, 4 MHz

- 22.5 μA typical @ 3V, 32 kHz

- < 1 μA typical standby current

- \* Enhanced features

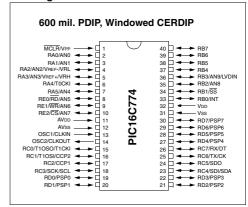

#### Pin Diagram

#### **Peripheral Features:**

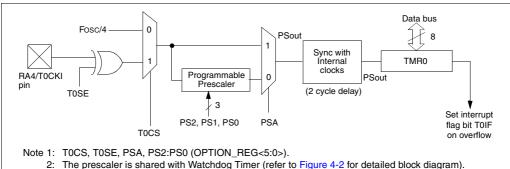

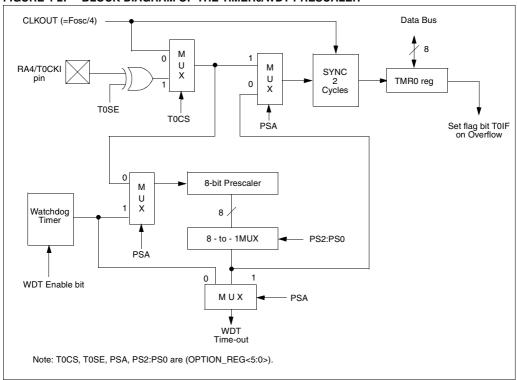

- Timer0: 8-bit timer/counter with 8-bit prescaler

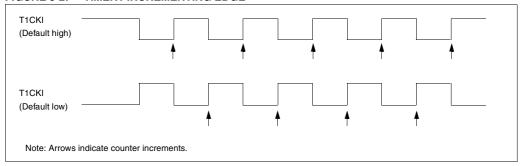

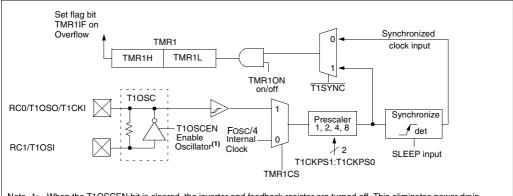

- Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep via external crystal/clock

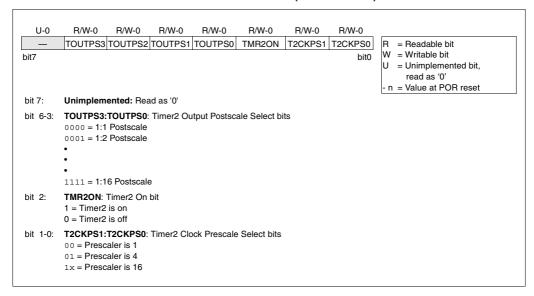

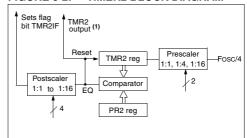

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

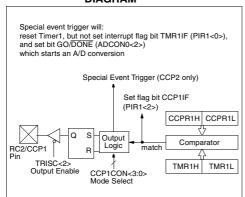

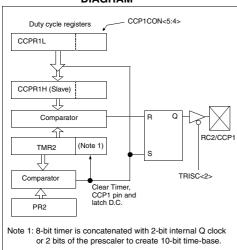

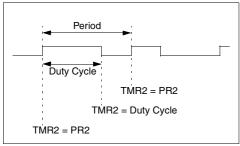

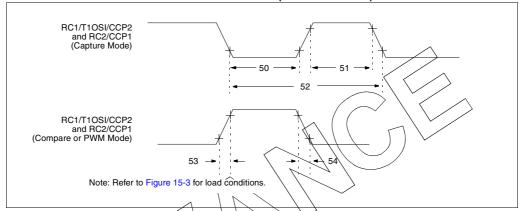

- Two Capture, Compare, PWM modules

- Capture is 16-bit, max. resolution is 12.5 ns, Compare is 16-bit, max. resolution is 200 ns, PWM max. resolution is 10-bit

- ★ 12-bit multi-channel Analog-to-Digital converter

- ★ On-chip absolute bandgap voltage reference generator

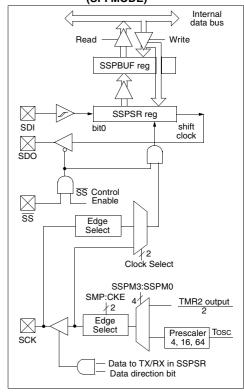

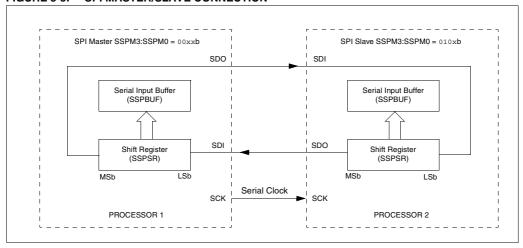

- ★ Synchronous Serial Port (SSP) with SPI<sup>™</sup> (Master Mode) and I<sup>2</sup>C<sup>™</sup>

- ★ Universal Synchronous Asynchronous Receiver Transmitter, supports high/low speeds and 9-bit address mode (USART/SCI)

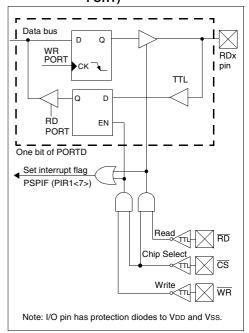

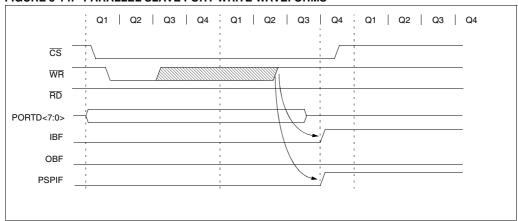

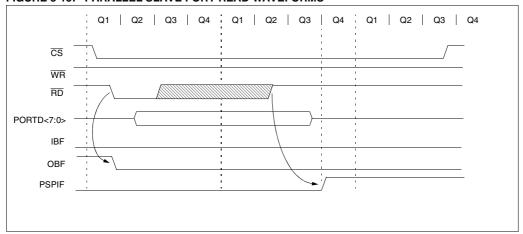

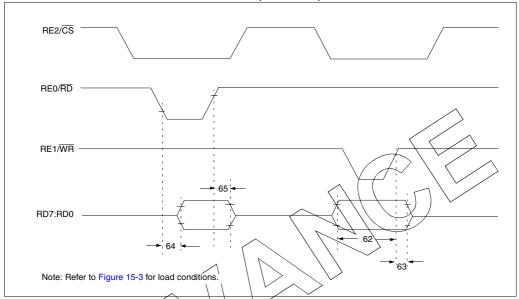

- Parallel Slave Port (PSP) 8-bits wide, with external RD, WR and CS controls

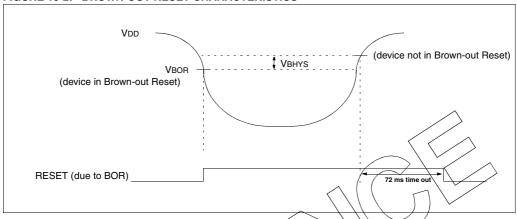

- ★ Programmable Brown-out detection circuitry for Brown-out Reset (BOR)

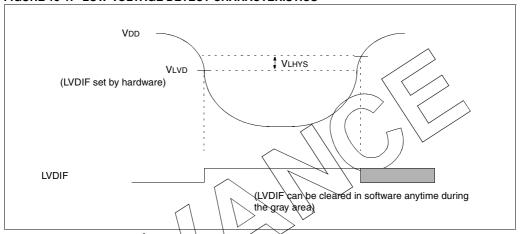

- \* Programmable Low-voltage detection circuitry

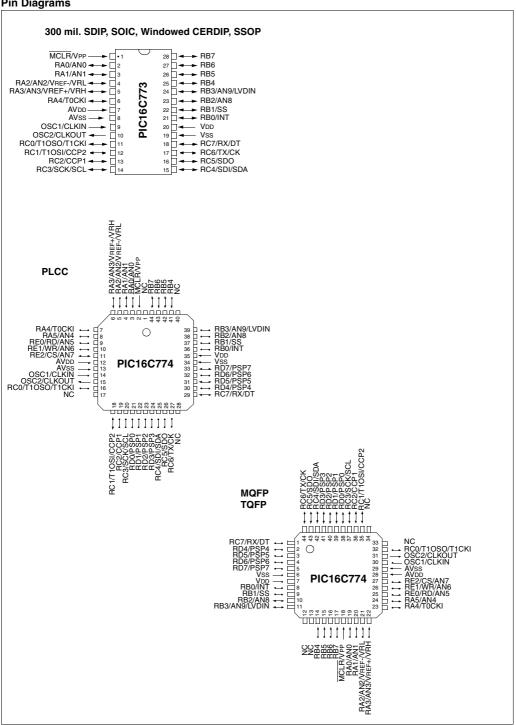

#### Pin Diagrams

| Key Features<br>PICmicro™ Mid-Range Reference Manual<br>(DS33023) | PIC16C773                          | PIC16C774                          |

|-------------------------------------------------------------------|------------------------------------|------------------------------------|

| Operating Frequency                                               | DC - 20 MHz                        | DC - 20 MHz                        |

| Resets (and Delays)                                               | POR, BOR, MCLR, WDT<br>(PWRT, OST) | POR, BOR, MCLR, WDT<br>(PWRT, OST) |

| Program Memory (14-bit words)                                     | 4K                                 | 4K                                 |

| Data Memory (bytes)                                               | 256                                | 256                                |

| Interrupts                                                        | 13                                 | 14                                 |

| I/O Ports                                                         | Ports A,B,C                        | Ports A,B,C,D,E                    |

| Timers                                                            | 3                                  | 3                                  |

| Capture/Compare/PWM modules                                       | 2                                  | 2                                  |

| Serial Communications                                             | MSSP, USART                        | MSSP, USART                        |

| Parallel Communications                                           | _                                  | PSP                                |

| 12-bit Analog-to-Digital Module                                   | 6 input channels                   | 10 input channels                  |

| Instruction Set                                                   | 35 Instructions                    | 35 Instructions                    |

#### **Table of Contents**

| 1.0 Device Overview                                                             | 5   |

|---------------------------------------------------------------------------------|-----|

| 2.0 Memory Organization                                                         | 11  |

| 3.0 I/O Ports                                                                   | 27  |

| 4.0 Timer0 Module                                                               | 39  |

| 5.0 Timer1 Module                                                               | 41  |

| 6.0 Timer2 Module                                                               | 45  |

| 7.0 Capture/Compare/PWM (CCP) Module(s)                                         | 47  |

| 8.0 Master Synchronous Serial Port (MSSP) Module                                | 53  |

| 9.0 Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 97  |

| 10.0 Voltage Reference Module and Low-voltage Detect                            | 113 |

| 11.0 Analog-to-Digital Converter (A/D) Module                                   | 117 |

| 12.0 Special Features of the CPU                                                | 127 |

| 13.0 Instruction Set Summary                                                    | 143 |

| 14.0 Development Support                                                        | 145 |

| 15.0 Electrical Characteristics                                                 | 151 |

| 16.0 DC and AC Characteristics Graphs and Tables                                | 173 |

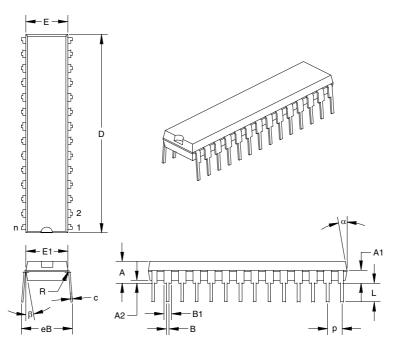

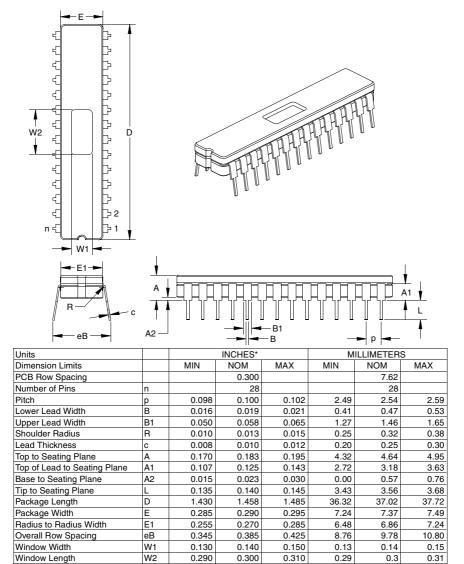

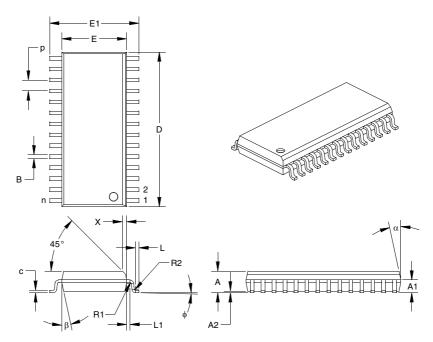

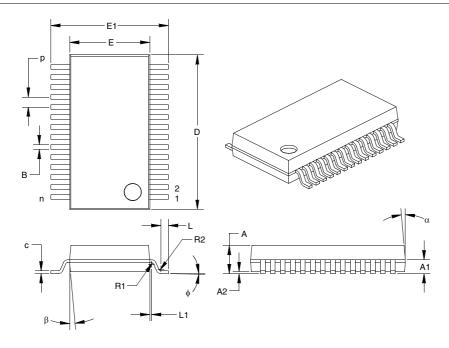

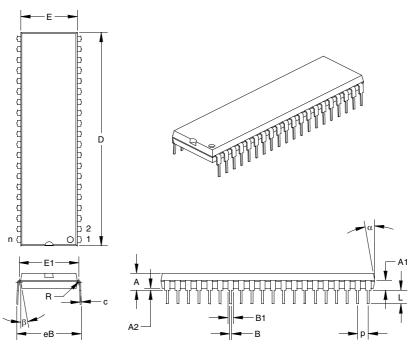

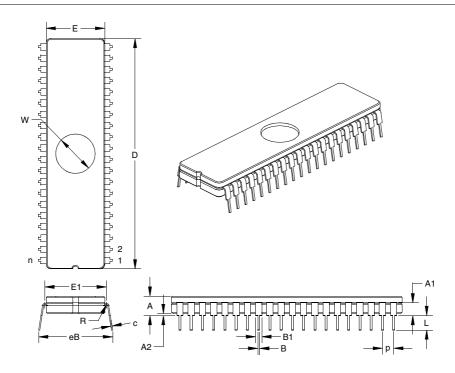

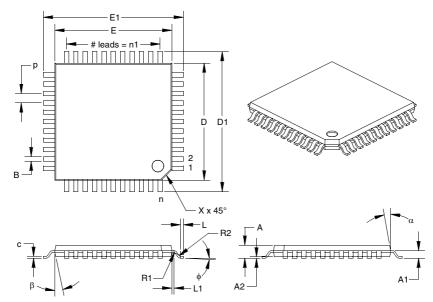

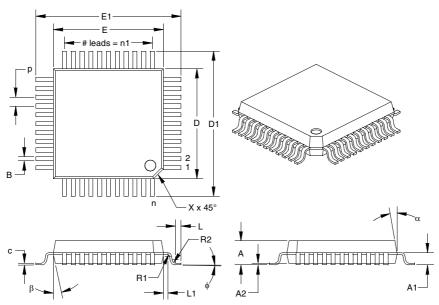

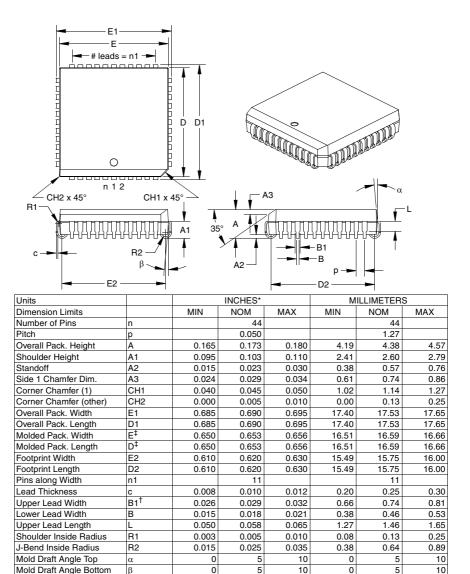

| 17.0 Packaging Information                                                      | 175 |

| Appendix A: Revision History                                                    | 187 |

| Appendix B: Device Differences                                                  | 187 |

| Appendix C: Conversion Considerations                                           | 187 |

| Index                                                                           | 189 |

| Bit/Register Cross-Reference List                                               | 196 |

| On-Line Support                                                                 | 197 |

| Reader Response                                                                 | 198 |

| PIC16C77X Product Identification System                                         | 199 |

#### To Our Valued Customers

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please check our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site: http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules

There a two devices (PIC16C773 and PIC16C774) covered by this datasheet. The PIC16C773 devices come in 28-pin packages and the PIC16C774 devices come in 40-pin packages. The 28-pin devices do not have a Parallel Slave Port implemented.

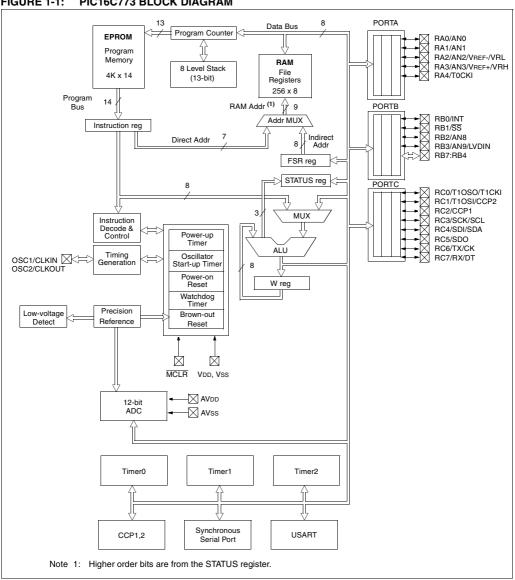

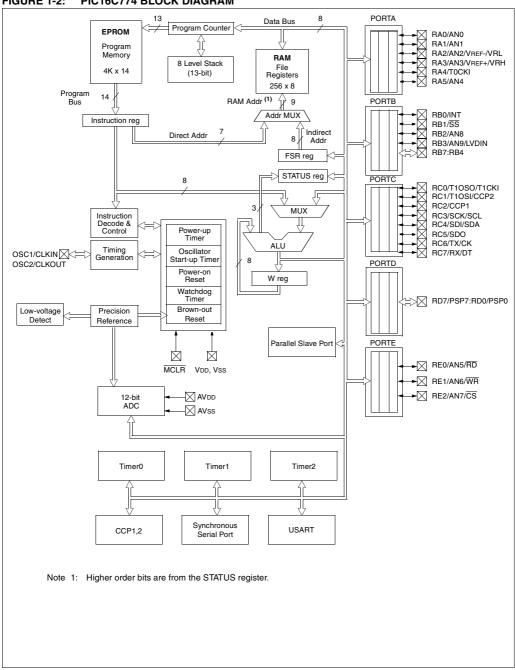

The following two figures are device block diagrams sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

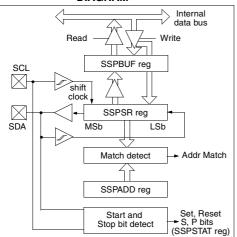

FIGURE 1-1: PIC16C773 BLOCK DIAGRAM

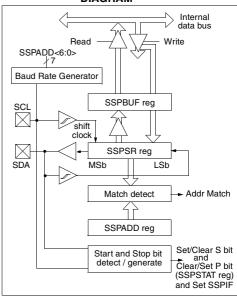

FIGURE 1-2: PIC16C774 BLOCK DIAGRAM

TABLE 1-1 **PIC16C773 PINOUT DESCRIPTION**

| Pin Name            | DIP,<br>SSOP, I/O/P Buffer<br>SOIC Type Type<br>Pin# |     |                        | Description                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------|------------------------------------------------------|-----|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

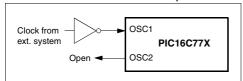

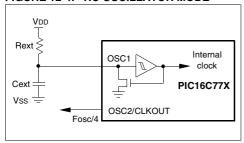

| OSC1/CLKIN          | 9                                                    | I   | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |  |  |  |  |  |

| OSC2/CLKOUT         | 10                                                   | 0   | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |  |  |  |

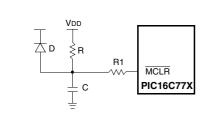

| MCLR/VPP            | 1                                                    | I/P | ST                     | Master clear (reset) input or programming voltage input. This pin is a active low reset to the device.                                                                                                       |  |  |  |  |  |

|                     |                                                      |     |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |  |  |  |  |  |

| RA0/AN0             | 2                                                    | I/O | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |  |  |  |  |  |

| RA1/AN1             | 3                                                    | I/O | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |  |  |  |  |  |

| RA2/AN2/VREF-/VRL   | 4                                                    | I/O | TTL                    | RA2 can also be analog input2 or negative analog reference voltage input or internal voltage reference low                                                                                                   |  |  |  |  |  |

| RA3/AN3/VREF+/VRH   | 5                                                    | I/O | TTL                    | RA3 can also be analog input3 or positive analog reference voltage input or internal voltage reference high                                                                                                  |  |  |  |  |  |

| RA4/T0CKI           | 6                                                    | I/O | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |  |  |  |  |  |

|                     |                                                      |     |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |  |  |  |  |  |

| RB0/INT             | 21                                                   | I/O | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |  |  |  |  |  |

| RB1/SS              | 22                                                   | I/O | TTL/ST <sup>(1)</sup>  | RB1 can also be the SSP slave select                                                                                                                                                                         |  |  |  |  |  |

| RB2/AN8             | 23                                                   | I/O | TTL                    | RB2 can also be analog input8                                                                                                                                                                                |  |  |  |  |  |

| RB3/AN9/LVDIN       | 24                                                   | I/O | TTL                    | RB3 can also be analog input9 or the low voltage detect input reference                                                                                                                                      |  |  |  |  |  |

| RB4                 | 25                                                   | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |  |  |  |

| RB5                 | 26                                                   | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |  |  |  |

| RB6                 | 27                                                   | I/O | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |  |  |  |  |  |

| RB7                 | 28                                                   | I/O | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |  |  |  |  |  |

|                     |                                                      |     |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |  |  |  |  |  |

| RC0/T1OSO/T1CKI     | 11                                                   | I/O | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |  |  |  |  |  |

| RC1/T1OSI/CCP2      | 12                                                   | I/O | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output.                                                                                                               |  |  |  |  |  |

| RC2/CCP1            | 13                                                   | I/O | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                              |  |  |  |  |  |

| RC3/SCK/SCL         | 14                                                   | I/O | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |  |  |  |  |  |

| RC4/SDI/SDA         | 15                                                   | I/O | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |  |  |  |  |  |

| RC5/SDO             | 16                                                   | I/O | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |  |  |  |  |  |

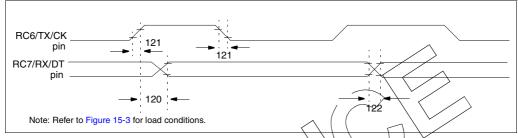

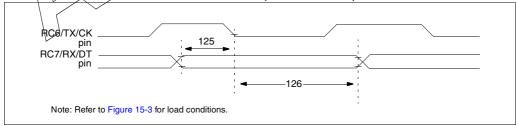

| RC6/TX/CK           | 17                                                   | I/O | ST                     | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |  |  |  |  |  |

| RC7/RX/DT           | 18                                                   | I/O | ST                     | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |  |  |  |  |  |

| AVss                | 8                                                    | Р   |                        | Ground reference for A/D converter                                                                                                                                                                           |  |  |  |  |  |

| AVDD                | 7                                                    | P   |                        | Positive supply for A/D converter                                                                                                                                                                            |  |  |  |  |  |

| Vss                 | 19                                                   | P   | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |  |  |  |  |  |

| VDD                 | 20                                                   | Р   | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |  |  |  |  |  |

| Legend: I = input ( | ) = output                                           |     | I/O = input            | /output P = power                                                                                                                                                                                            |  |  |  |  |  |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

**TABLE 1-2 PIC16C774 PINOUT DESCRIPTION**

| Pin Name            | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|---------------------|-------------|--------------|-------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN          | 13          | 14           | 30          | -             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT         | 14          | 15           | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP            | 1           | 2            | 18          | I/P           | ST                     | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                               |

|                     |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0             | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1             | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2/VREF-/VRL   | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input2 or negative analog reference voltage input or internal voltage reference low                                                                                               |

| RA3/AN3/VREF+/VRH   | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input3 or positive analog<br>reference voltage input or internal voltage reference<br>high                                                                                        |

| RA4/T0CKI           | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                  |

| RA5/AN4             | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input4                                                                                                                                                                            |

|                     |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT             | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1/SS              | 34          | 37           | 9           | I/O           | TTL/ST <sup>(1)</sup>  | RB1 can also be the SSP slave select                                                                                                                                                                     |

| RB2/AN8             | 35          | 38           | 10          | I/O           | TTL                    | RB2 can also be analog input8                                                                                                                                                                            |

| RB3/AN9/LVDIN       | 36          | 39           | 11          | I/O           | TTL                    | RB3 can also be analog input9 or input reference for low voltage detect                                                                                                                                  |

| RB4                 | 37          | 41           | 14          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB5                 | 38          | 42           | 15          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB6                 | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7                 | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Legend: I = input ( | ) = outp    | ut           | I/O         | = input       | output/                | P = power                                                                                                                                                                                                |

— = Not used

I/O = input/output TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

<sup>2:</sup> This buffer is a Schmitt Trigger input when used in serial programming mode.

<sup>3:</sup> This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

<sup>4:</sup> This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

**TABLE 1-2** PIC16C774 PINOUT DESCRIPTION (Cont.'d)

| Pin Name             | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type                                 | Description                                                                                        |

|----------------------|-------------|----------------|-----------------|---------------|------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                      |             |                |                 |               |                                                | PORTC is a bi-directional I/O port.                                                                |

| RC0/T1OSO/T1CKI      | 15          | 16             | 32              | I/O           | ST                                             | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                           |

| RC1/T1OSI/CCP2       | 16          | 18             | 35              | I/O           | ST                                             | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.      |

| RC2/CCP1             | 17          | 19             | 36              | I/O           | ST                                             | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                    |

| RC3/SCK/SCL          | 18          | 20             | 37              | I/O           | ST                                             | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA          | 23          | 25             | 42              | I/O           | ST                                             | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                    |

| RC5/SDO              | 24          | 26             | 43              | I/O           | ST                                             | RC5 can also be the SPI Data Out (SPI mode).                                                       |

| RC6/TX/CK            | 25          | 27             | 44              | I/O           | ST                                             | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                              |

| RC7/RX/DT            | 26          | 29             | 1               | I/O           | ST                                             | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                |

|                      |             |                |                 |               |                                                | PORTD is a bi-directional I/O port or parallel slave port                                          |

|                      |             |                |                 |               | (3)                                            | when interfacing to a microprocessor bus.                                                          |

| RD0/PSP0             | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup><br>ST/TTL <sup>(3)</sup> |                                                                                                    |

| RD1/PSP1             | 20          | 22             | 39<br>40        | 1/0           | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| RD2/PSP2             | 21<br>22    | 23             |                 | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| RD3/PSP3<br>RD4/PSP4 | 27          | 24<br>30       | 41<br>2         | I/O<br>I/O    | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| RD5/PSP5             | 28          | 31             | 3               | 1/0           | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| RD6/PSP6             | 28          | 32             | 4               | 1/0           | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| RD7/PSP7             | 30          | 33             | 5               | 1/0           | ST/TTL <sup>(3)</sup>                          |                                                                                                    |

| ND//P3P/             | 30          | 33             | 5               | 1/0           | SI/IIL                                         | PORTE is a bi-directional I/O port.                                                                |

| RE0/RD/AN5           | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup>                          | RE0 can also be read control for the parallel slave port, or analog input5.                        |

| RE1/WR/AN6           | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup>                          | RE1 can also be write control for the parallel slave port, or analog input6.                       |

| RE2/CS/AN7           | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup>                          | RE2 can also be select control for the parallel slave port, or analog input7.                      |

| AVss                 | 12          | 13             | 29              | Р             |                                                | Ground reference for A/D converter                                                                 |

| AVDD                 | 11          | 12             | 28              | Р             |                                                | Positive supply for A/D converter                                                                  |

| Vss                  | 31          | 34             | 6               | Р             | _                                              | Ground reference for logic and I/O pins.                                                           |

| VDD                  | 32          | 35             | 7               | P             | _                                              | Positive supply for logic and I/O pins.                                                            |

| NC                   | -           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | _                                              | These pins are not internally connected. These pins should be left unconnected.                    |

TTL = TTL input

I/O = input/output P = power ST = Schmitt Trigger input

— = Not used Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

- 2: This buffer is a Schmitt Trigger input when used in serial programming mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

NOTES:

#### 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PICmicro® microcontrollers. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the  $PICmicro^{TM}$  Mid-Range Reference Manual, (DS33023).

#### 2.1 Program Memory Organization

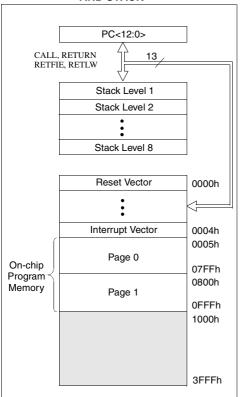

The PIC16C77X PICmicros have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

#### 2.2 <u>Data Memory Organization</u>

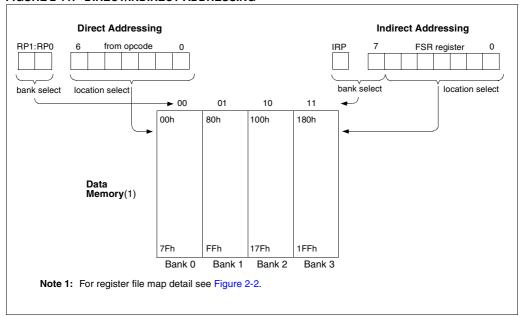

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1 | RP0 | (STATUS<6:5>) |

|-----|-----|---------------|

|     |     |               |

$= 00 \rightarrow Bank0$

$= 01 \rightarrow Bank1$

$= 10 \rightarrow Bank2$

= 11 → Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR.

FIGURE 2-2: REGISTER FILE MAP

| А                                          | File<br>ddress | А                                          | File<br>ddress |                                            | File<br>Address | F                     | File<br>Address |

|--------------------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|-----------------------|-----------------|

| Indirect addr.(*)                          | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)     | 180h            |

| TMR0                                       | 01h            | OPTION REG                                 | 81h            | TMR0                                       | 101h            | OPTION REG            | 181h            |

| PCL                                        | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                   | 182h            |

| STATUS                                     | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                | 183h            |

| FSR                                        | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                   | 184h            |

| PORTA                                      | 05h            | TRISA                                      | 85h            |                                            | 105h            |                       | 185h            |

| PORTB                                      | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                 | 186h            |

| PORTC                                      | 07h            | TRISC                                      | 87h            |                                            | 107h            |                       | 187h            |

| PORTD (1)                                  | 08h            | TRISD (1)                                  | 88h            |                                            | 108h            |                       | 188h            |

| PORTE (1)                                  | 09h            | TRISE (1)                                  | 89h            |                                            | 109h            |                       | 189h            |

| PCLATH                                     | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                | 18Ah            |

| INTCON                                     | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                | 18Bh            |

| PIR1                                       | 0Ch            | PIE1                                       | 8Ch            |                                            | 10Ch            |                       | 18Ch            |

| PIR2                                       | 0Dh            | PIE2                                       | 8Dh            |                                            | 10Dh            |                       | 18Dh            |

| TMR1L                                      | 0Eh            | PCON                                       | 8Eh            |                                            | 10Eh            |                       | 18Eh            |

| TMR1H                                      | 0Fh            |                                            | 8Fh            |                                            | 10Fh            |                       | 18Fh            |

| T1CON                                      | 10h            |                                            | 90h            | 1                                          | 110h            |                       | 190h            |

| TMR2                                       | 11h            | SSPCON2                                    | 91h            |                                            | 111h            |                       | 191h            |

| T2CON                                      | 12h            | PR2                                        | 92h            |                                            | 112h            |                       | 192h            |

| SSPBUF                                     | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                       | 193h            |

| SSPCON                                     | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                       | 194h            |

| CCPR1L                                     | 15h            |                                            | 95h            |                                            | 115h            |                       | 195h            |

| CCPR1H                                     | 16h            |                                            | 96h            |                                            | 116h            |                       | 196h            |

| CCP1CON                                    | 17h            |                                            | 97h            |                                            | 117h            |                       | 197h            |

| RCSTA                                      | 18h            | TXSTA                                      | 98h            |                                            | 118h            |                       | 198h            |

| TXREG                                      | 19h            | SPBRG                                      | 99h            |                                            | 119h            |                       | 199h            |

| RCREG                                      | 1Ah            |                                            | 9Ah            |                                            | 11Ah            |                       | 19Ah            |

| CCPR2L                                     | 1Bh            | REFCON                                     | 9Bh            |                                            | 11Bh            |                       | 19Bh            |

| CCPR2H                                     | 1Ch            | LVDCON                                     | 9Ch            |                                            | 11Ch            |                       | 19Ch            |

| CCP2CON                                    | 1Dh            |                                            | 9Dh            |                                            | 11Dh            |                       | 19Dh            |

| ADRESH                                     | 1Eh            | ADRESL                                     | 9Eh            |                                            | 11Eh            |                       | 19Eh            |

| ADCON0                                     | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                       | 19Fh            |

|                                            | 20h            |                                            | A0h            |                                            | 120h            |                       | 1A0h            |

| General<br>Purpose<br>Register<br>96 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes | EFh            | General<br>Purpose<br>Register<br>80 Bytes | 6Fh             |                       | 1EFh            |

|                                            | 7Fh            | accesses<br>70h-7Fh                        | F0h<br>FFh     | accesses<br>70h - 7Fh                      | 70h<br>17Fh     | accesses<br>70h - 7Fh | 1F0h            |

| Bank 0                                     | <i>i</i> FII   | Bank 1                                     | EFII           | Bank 2                                     | 17FII           | Bank 3                | 1FFh            |

<sup>(1)</sup> Not implemented on PIC16C773.

Unimplemented data memory locations, read as '0'. Not a physical register.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                                                                          | Bit 6                                                     | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1        | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|----------------------|---------|--------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|-----------------|--------------|--------------|--------------|-----------|--------------------------|-------------------------------|

| Bank 0               |         |                                                                                |                                                           |                |                 |              |              |              |           |                          |                               |

| 00h <sup>(4)</sup>   | INDF    | Addressing                                                                     | this location                                             | uses content   | s of FSR to ad  | dress data m | emory (not a | physical req | gister)   | 0000 0000                | 0000 0000                     |

| 01h                  | TMR0    | Timer0 mod                                                                     | dule's registe                                            | r              |                 |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 02h <sup>(4)</sup>   | PCL     | Program Co                                                                     | ounter's (PC)                                             | Least Signific | cant Byte       |              |              |              |           | 0000 0000                | 0000 0000                     |

| 03h <sup>(4)</sup>   | STATUS  | IRP                                                                            | RP1                                                       | RP0            | TO              | PD           | Z            | DC           | С         | 0001 1xxx                | 000q quuu                     |

| 04h <sup>(4)</sup>   | FSR     | Indirect data                                                                  | a memory ac                                               | Idress pointer |                 |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 05h                  | PORTA   | PORTA5 <sup>(5)</sup> PORTA Data Latch when written: PORTA<4:0> pins when read |                                                           |                |                 |              |              |              | when read | 0x 0000                  | 0u 0000                       |

| 06h                  | PORTB   | PORTB Dat                                                                      | ta Latch whe                                              | n written: PO  | RTB pins wher   | n read       |              |              |           | xxxx 11xx                | uuuu 11uu                     |

| 07h                  | PORTC   | PORTC Dat                                                                      | ta Latch whe                                              | n written: PO  | RTC pins whe    | n read       |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Dat                                                                      | ta Latch whe                                              | n written: PO  | RTD pins whe    | n read       |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 09h <sup>(5)</sup>   | PORTE   | _                                                                              | _                                                         | _              | _               | _            | RE2          | RE1          | RE0       | 000                      | 000                           |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                                                                              | Write Buffer for the upper 5 bits of the Program Counter0 |                |                 |              |              |              | 0 0000    | 0 0000                   |                               |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                                                                            | PEIE                                                      | TOIE           | INTE            | RBIE         | TOIF         | INTF         | RBIF      | 0000 000x                | 0000 000u                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup>                                                           | ADIF                                                      | RCIF           | TXIF            | SSPIF        | CCP1IF       | TMR2IF       | TMR1IF    | 0000 0000                | 0000 0000                     |

| 0Dh                  | PIR2    | LVDIF                                                                          | _                                                         | _              | -               | BCLIF        | _            | -            | CCP2IF    | 0 00                     | 0 00                          |

| 0Eh                  | TMR1L   | Holding reg                                                                    | ister for the L                                           | east Significa | ant Byte of the | 16-bit TMR1  | register     |              |           | xxxx xxxx                | uuuu uuuu                     |

| 0Fh                  | TMR1H   | Holding reg                                                                    | ister for the N                                           | Most Significa | nt Byte of the  | 16-bit TMR1  | register     |              |           | xxxx xxxx                | uuuu uuuu                     |

| 10h                  | T1CON   | _                                                                              | _                                                         | T1CKPS1        | T1CKPS0         | T10SCEN      | T1SYNC       | TMR1CS       | TMR10N    | 00 0000                  | uu uuuu                       |

| 11h                  | TMR2    | Timer2 mod                                                                     | dule's registe                                            | r              |                 |              |              |              |           | 0000 0000                | 0000 0000                     |

| 12h                  | T2CON   | _                                                                              | TOUTPS3                                                   | TOUTPS2        | TOUTPS1         | TOUTPS0      | TMR2ON       | T2CKPS1      | T2CKPS0   | -000 0000                | -000 0000                     |

| 13h                  | SSPBUF  | Synchronou                                                                     | ıs Serial Port                                            | Receive Buf    | fer/Transmit Re | egister      | •            |              | •         | xxxx xxxx                | uuuu uuuu                     |

| 14h                  | SSPCON  | WCOL                                                                           | SSPOV                                                     | SSPEN          | CKP             | SSPM3        | SSPM2        | SSPM1        | SSPM0     | 0000 0000                | 0000 0000                     |

| 15h                  | CCPR1L  | Capture/Co                                                                     | mpare/PWM                                                 | Register1 (L   | SB)             |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 16h                  | CCPR1H  | Capture/Co                                                                     | mpare/PWM                                                 | Register1 (M   | ISB)            |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 17h                  | CCP1CON | _                                                                              | _                                                         | CCP1X          | CCP1Y           | CCP1M3       | CCP1M2       | CCP1M1       | CCP1M0    | 00 0000                  | 00 0000                       |

| 18h                  | RCSTA   | SPEN                                                                           | RX9                                                       | SREN           | CREN            | ADDEN        | FERR         | OERR         | RX9D      | 0000 000x                | 0000 000x                     |

| 19h                  | TXREG   | USART Trai                                                                     | nsmit Data R                                              | legister       |                 |              |              |              |           | 0000 0000                | 0000 0000                     |

| 1Ah                  | RCREG   | USART Red                                                                      | ceive Data R                                              | egister        |                 |              |              |              |           | 0000 0000                | 0000 0000                     |

| 1Bh                  | CCPR2L  | Capture/Co                                                                     | mpare/PWM                                                 | Register2 (L   | SB)             |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 1Ch                  | CCPR2H  | Capture/Co                                                                     | mpare/PWM                                                 | Register2 (N   | ISB)            |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 1Dh                  | CCP2CON | _                                                                              | _                                                         | CCP2X          | CCP2Y           | ССР2М3       | CCP2M2       | CCP2M1       | CCP2M0    | 00 0000                  | 00 0000                       |

| 1Eh                  | ADRESH  | A/D High By                                                                    | yte Result Re                                             | egister        |                 |              |              |              |           | xxxx xxxx                | uuuu uuuu                     |

| 1Fh                  | ADCON0  | ADCS1                                                                          | ADCS0                                                     | CHS2           | CHS1            | CHS0         | GO/DONE      | CHS3         | ADON      | 0000 0000                | 0000 0000                     |

$\label{eq:Legends} \begin{tabular}{ll} Legends & $x=$ unknown, $u=$ unchanged, $q=$ value depends on condition, $-=$ unimplemented read as '0'. \\ Shaded locations are unimplemented, read as '0'. \\ \end{tabular}$

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

<sup>2:</sup> Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

<sup>3:</sup> Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

These registers can be addressed from any bank.

<sup>5:</sup> These registers/bits are not implemented on the 28-pin devices read as '0'.

#### TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

|                      |             |                      |                   |                         |                 |              |                 | •             | ,       |                          |                               |

|----------------------|-------------|----------------------|-------------------|-------------------------|-----------------|--------------|-----------------|---------------|---------|--------------------------|-------------------------------|

| Address              | Name        | Bit 7                | Bit 6             | Bit 5                   | Bit 4           | Bit 3        | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

| Bank 1               |             |                      |                   |                         |                 |              |                 |               |         |                          | <u>-</u>                      |

| 80h <sup>(4)</sup>   | INDF        | Addressing           | this location     | uses content            | s of FSR to add | dress data n | nemory (not a   | physical rec  | gister) | 0000 0000                | 0000 0000                     |

| 81h                  | OPTION_REG  | RBPU                 | INTEDG            | TOCS                    | TOSE            | PSA          | PS2             | PS1           | PS0     | 1111 1111                | 1111 1111                     |

| 82h <sup>(4)</sup>   | PCL         | Program Co           | ounter's (PC)     | Least Signifi           | cant Byte       |              |                 |               |         | 0000 0000                | 0000 0000                     |

| 83h <sup>(4)</sup>   | STATUS      | IRP                  | RP1               | RP0                     | TO              | PD           | Z               | DC            | С       | 0001 1xxx                | 000q quuu                     |

| 84h <sup>(4)</sup>   | FSR         | Indirect data        | a memory ad       | dress pointer           | r               |              | •               |               | •       | xxxx xxxx                | uuuu uuuu                     |

| 85h                  | TRISA       | _                    | _                 | bit5 <sup>(5)</sup>     | PORTA Data I    | Direction Re | gister          |               |         | 11 1111                  | 11 11111                      |

| 86h                  | TRISB       | PORTB Dat            | a Direction F     | Register                |                 |              |                 |               |         | 1111 1111                | 1111 1111                     |

| 87h                  | TRISC       | PORTC Dat            | a Direction F     | Register                |                 |              |                 |               |         | 1111 1111                | 1111 1111                     |

| 88h <sup>(5)</sup>   | TRISD       | PORTD Dat            | a Direction F     | Register                |                 |              |                 |               |         | 1111 1111                | 1111 1111                     |

| 89h <sup>(5)</sup>   | TRISE       | IBF                  | OBF               | IBOV                    | PSPMODE         | _            | PORTE Dat       | a Direction E | Bits    | 0000 -111                | 0000 -111                     |

| 8Ah <sup>(1,4)</sup> | PCLATH      | _                    | _                 | _                       | Write Buffer fo | r the upper  | 5 bits of the I | Program Cou   | inter   | 0 0000                   | 0 0000                        |

| 8Bh <sup>(4)</sup>   | INTCON      | GIE                  | PEIE              | TOIE                    | INTE            | RBIE         | TOIF            | INTF          | RBIF    | 0000 000x                | 0000 000u                     |

| 8Ch                  | PIE1        | PSPIE <sup>(3)</sup> | ADIE              | RCIE                    | TXIE            | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE  | 0000 0000                | 0000 0000                     |

| 8Dh                  | PIE2        | LVDIE                | _                 | _                       | _               | BCLIE        | _               | _             | CCP2IE  | 0 00                     | 0 00                          |

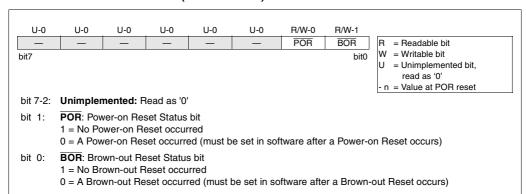

| 8Eh                  | PCON        | _                    | _                 | _                       | _               | _            | _               | POR           | BOR     | qq                       | uu                            |

| 8Fh                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 90h                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 91h                  | SSPCON2     | GCEN                 | AKSTAT            | AKDT                    | AKEN            | RCEN         | PEN             | RSEN          | SEN     | 0000 0000                | 0000 0000                     |

| 92h                  | PR2         | Timer2 Peri          | od Register       |                         |                 |              |                 |               |         | 1111 1111                | 1111 1111                     |

| 93h                  | SSPADD      | Synchronou           | s Serial Port     | (I <sup>2</sup> C mode) | Address Regist  | er           |                 |               |         | 0000 0000                | 0000 0000                     |

| 94h                  | SSPSTAT     | SMP                  | CKE               | D/A                     | Р               | S            | R/W             | UA            | BF      | 0000 0000                | 0000 0000                     |

| 95h                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 96h                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 97h                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 98h                  | TXSTA       | CSRC                 | TX9               | TXEN                    | SYNC            | _            | BRGH            | TRMT          | TX9D    | 0000 -010                | 0000 -010                     |

| 99h                  | SPBRG       | Baud Rate            | Generator Re      | egister                 |                 |              | '               |               |         | 0000 0000                | 0000 0000                     |

| 9Ah                  | _           | Unimpleme            | Unimplemented — — |                         |                 |              |                 |               | _       |                          |                               |

| 9Bh                  | REFCON      | VRHEN                | VRLEN             | VRHOEN                  | VRLOEN          | _            | _               | _             | _       | 0000                     | 0000                          |

| 9Ch                  | LVDCON      | _                    | _                 | BGST                    | LVDEN           | LV3          | LV2             | LV1           | LV0     | 00 0101                  | 00 0101                       |

| 9Ah                  | _           | Unimpleme            | nted              |                         |                 |              |                 |               |         | _                        | _                             |

| 9Eh                  | ADRESL      | A/D Low By           | te Result Re      | gister                  |                 |              |                 |               |         | xxxx xxxx                | uuuu uuuu                     |

| 9Fh                  | ADCON1      | ADFM                 | VCFG2             | VCFG1                   | VCFG0           | PCFG3        | PCFG2           | PCFG1         | PCFG0   | 0000 0000                | 0000 0000                     |

| edend.               | x = unknown |                      |                   |                         |                 |              |                 | d.            |         |                          |                               |

x= unknown, u= unchanged, q= value depends on condition, -= unimplemented read as '0'. Legend:

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

<sup>3:</sup> Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear. These registers can be addressed from any bank.

These registers/bits are not implemented on the 28-pin devices read as '0'.

#### TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address               | Name       | Bit 7                                  | Bit 6             | Bit 5          | Bit 4           | Bit 3        | Bit 2           | Bit 1       | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|-----------------------|------------|----------------------------------------|-------------------|----------------|-----------------|--------------|-----------------|-------------|-----------|--------------------------|-------------------------------|

| Bank 2                |            |                                        |                   |                |                 | 1            |                 |             |           | -                        | -                             |

| 100h <sup>(4)</sup>   | INDF       | Addressing                             | this location     | uses content   | s of FSR to ad  | dress data m | emory (not a    | physical re | gister)   | 0000 0000                | 0000 0000                     |

| 101h                  | TMR0       | Timer0 mod                             | lule's register   | r              |                 |              |                 |             |           | xxxx xxxx                | uuuu uuuu                     |

| 102h <sup>(4)</sup>   | PCL        | Program Co                             | ounter's (PC)     | Least Signific | cant Byte       |              |                 |             |           | 0000 0000                | 0000 0000                     |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                    | RP1               | RP0            | TO              | PD           | Z               | DC          | С         | 0001 1xxx                | 000q quuu                     |

| 104h <sup>(4)</sup>   | FSR        | Indirect data                          | a memory ad       | dress pointer  |                 |              |                 |             |           | xxxx xxxx                | uuuu uuuu                     |

| 105h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 106h                  | PORTB      | PORTB Dat                              | a Latch whe       | n written: PO  | RTB pins wher   | n read       |                 |             |           | xxxx 11xx                | uuuu 11uu                     |

| 107h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 108h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 109h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 10Ah <sup>(1,4)</sup> | PCLATH     | 1                                      | 1                 | 1              | Write Buffer fo | or the upper | 5 bits of the F | Program Cou | unter     | 0 0000                   | 0 0000                        |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE PEIE TOIE INTE RBIE TOIF INTF RBIF |                   |                |                 |              |                 |             | 0000 000x | 0000 000u                |                               |

| 10Ch-<br>10Fh         | -          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| Bank 3                |            |                                        |                   |                |                 |              |                 |             |           |                          |                               |

| 180h <sup>(4)</sup>   | INDF       | Addressing                             | this location     | uses content   | s of FSR to ad  | dress data m | emory (not a    | physical re | gister)   | 0000 0000                | 0000 0000                     |

| 181h                  | OPTION_REG | RBPU                                   | INTEDG            | T0CS           | T0SE            | PSA          | PS2             | PS1         | PS0       | 1111 1111                | 1111 1111                     |

| 182h <sup>(4)</sup>   | PCL        | Program Co                             | ounter's (PC)     | Least Signif   | icant Byte      |              |                 |             |           | 0000 0000                | 0000 0000                     |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                    | RP1               | RP0            | TO              | PD           | z               | DC          | С         | 0001 1xxx                | 000q quuu                     |

| 184h <sup>(4)</sup>   | FSR        | Indirect data                          | a memory ad       | dress pointer  |                 |              |                 |             |           | xxxx xxxx                | uuuu uuuu                     |

| 185h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 186h                  | TRISB      | PORTB Dat                              | a Direction F     | Register       |                 |              |                 |             |           | 1111 1111                | 1111 1111                     |

| 187h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 188h                  | _          | Unimpleme                              | nted              |                |                 |              |                 |             |           | _                        | _                             |

| 189h                  | _          | Unimpleme                              | Unimplemented — — |                |                 |              |                 |             | _         |                          |                               |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                                      | _                 | _              | Write Buffer fo | or the upper | 5 bits of the F | Program Cou | unter     | 0 0000                   | 0 0000                        |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                    | PEIE              | TOIE           | INTE            | RBIE         | TOIF            | INTF        | RBIF      | 0000 000x                | 0000 000u                     |

| 18Ch-<br>18Fh         | _          | Unimplemen                             | nted              |                |                 |              |                 |             |           | _                        | _                             |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

<sup>4:</sup> These registers can be addressed from any bank.

5: These registers/bits are not implemented on the 28-pin devices read as '0'.

#### 2.2.2.1 STATUS REGISTER

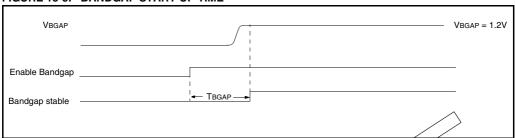

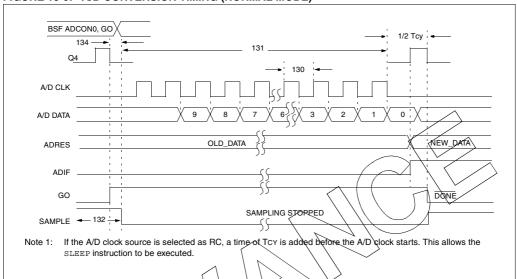

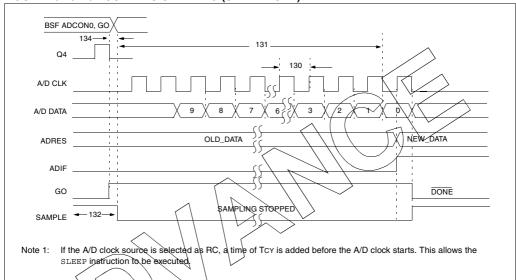

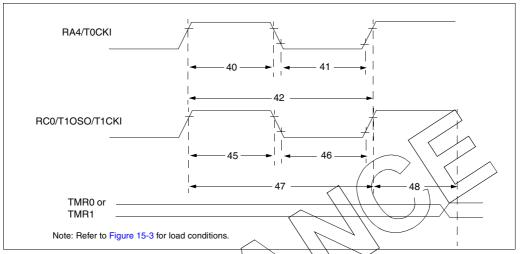

The STATUS register, shown in Figure 2-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.