# 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Eight Outputs

Data Sheet AD9510

### **FEATURES**

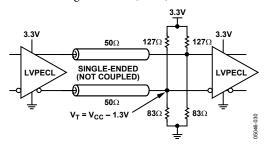

Low phase noise phase-locked loop core Reference input frequencies to 250 MHz Programmable dual modulus prescaler Programmable charge pump (CP) current Separate CP supply (VCPs) extends tuning range Two 1.6 GHz, differential clock inputs 8 programmable dividers, 1 to 32, all integers Phase select for output-to-output coarse delay adjust 4 independent 1.2 GHz LVPECL outputs Additive output jitter of 225 fs rms 4 independent 800 MHz low voltage differential signaling (LVDS) or 250 MHz complementary metal oxide conductor (CMOS) clock outputs Additive output jitter of 275 fs rms Fine delay adjust on 2 LVDS/CMOS outputs Serial control port Space-saving 64-lead LFCSP

#### **APPLICATIONS**

Low jitter, low phase noise clock distribution

Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, and

mixed-signal front ends (MxFEs)

High performance wireless transceivers

High performance instrumentation

Broadband infrastructure

### **GENERAL DESCRIPTION**

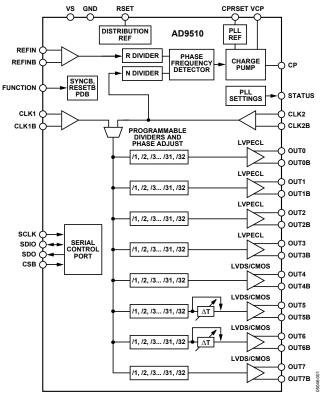

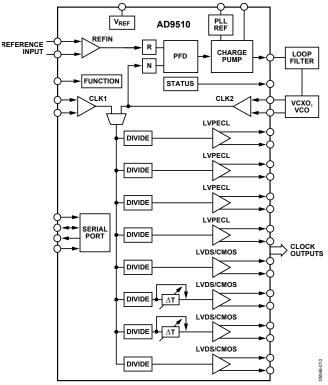

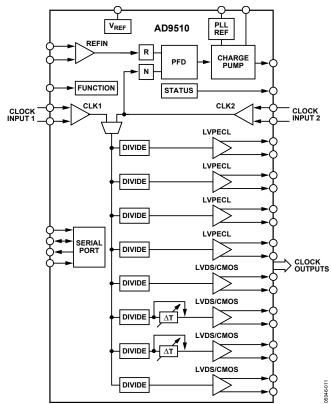

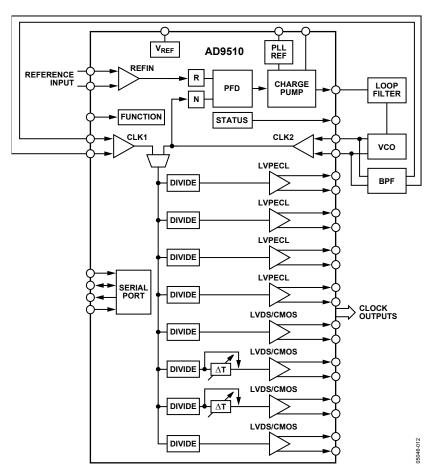

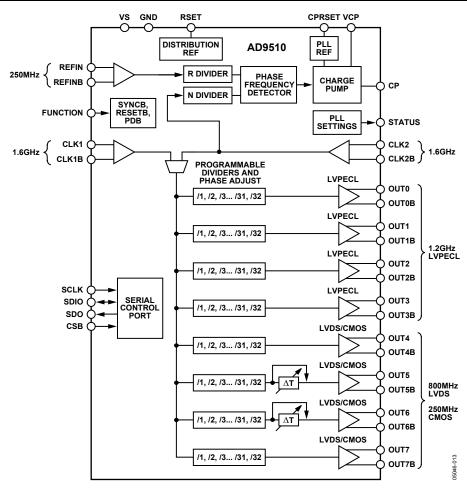

The AD9510 provides a multi-output clock distribution function along with an on-chip phase-locked loop (PLL) core. The design emphasizes low jitter and phase noise to maximize data converter performance. Other applications with demanding phase noise and jitter requirements also benefit from this device.

The PLL section consists of a programmable reference divider (R); a low noise, phase frequency detector (PFD); a precision charge pump (CP); and a programmable feedback divider (N). By connecting an external voltage-controlled crystal oscillator (VCXO) or voltage-controlled oscillator (VCO) to the CLK2 and CLK2B pins, frequencies of up to 1.6 GHz can be synchronized to the input reference.

There are eight independent clock outputs. Four outputs are low voltage positive emitter-coupled logic (LVPECL) at 1.2 GHz, and four are selectable as either LVDS (800 MHz) or CMOS (250 MHz) levels.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

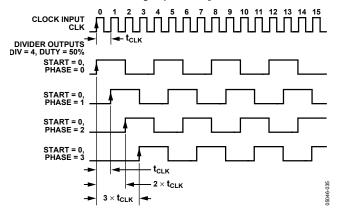

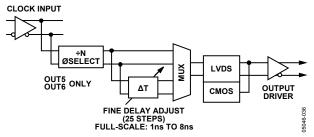

Each output has a programmable divider that can be bypassed or set to divide by any integer up to 32. The phase of one clock output relative to another clock output can be varied by means of a divider phase select function that serves as a coarse timing adjustment. Two of the LVDS/CMOS outputs feature programmable delay elements with full-scale ranges up to 8 ns of delay. This fine tuning delay block has 5-bit resolution, giving 25 possible delays from which to choose for each full-scale setting (Register 0x36 and Register 0x3A = 00000b to 11000b).

The AD9510 is ideally suited for data converter clocking applications where maximum converter performance is achieved by encode signals with subpicosecond jitter.

The AD9510 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply (VCP) to 5.5 V. The temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# **TABLE OF CONTENTS**

| Features                                               | Overall                                                                      |

|--------------------------------------------------------|------------------------------------------------------------------------------|

| Applications1                                          | PLL Section                                                                  |

| Functional Block Diagram1                              | FUNCTION Pin32                                                               |

| General Description1                                   | Distribution Section                                                         |

| Revision History                                       | CLK1 and CLK2 Clock Inputs32                                                 |

| Specifications4                                        | Dividers                                                                     |

| PLL Characteristics                                    | Delay Block                                                                  |

| Clock Inputs                                           | Outputs                                                                      |

| Clock Outputs                                          | Power-Down Modes                                                             |

| Timing Characteristics                                 | Reset Modes                                                                  |

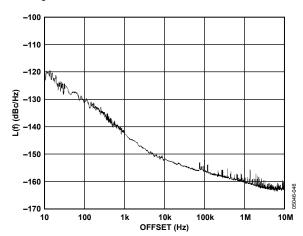

| Clock Output Phase Noise                               | Single-Chip Synchronization39                                                |

| Clock Output Additive Time Jitter11                    | Multichip Synchronization                                                    |

| PLL and Distribution Phase Noise and Spurious          | Serial Control Port                                                          |

| Serial Control Port                                    | Serial Control Port Pin Descriptions                                         |

| FUNCTION Pin                                           | General Operation of Serial Control Port                                     |

| STATUS Pin                                             | The Instruction Word (16 Bits)41                                             |

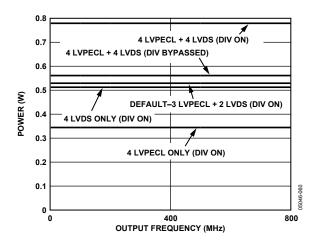

| Power                                                  |                                                                              |

|                                                        | MSB/LSB First Transfers                                                      |

| Fiming Diagrams                                        | Register Map and Description                                                 |

| Absolute Maximum Ratings                               | Summary Table                                                                |

| Thermal Characteristics                                | Register Map Description                                                     |

| ESD Caution                                            | Power Supply53                                                               |

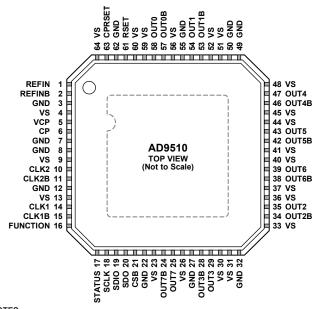

| Pin Configuration and Function Descriptions18          | Power Management                                                             |

| Typical Performance Characteristics                    | Applications Information                                                     |

| Гerminology24                                          | Using the AD9510 Outputs for ADC Clock Applications 54                       |

| Typical Modes of Operation25                           | CMOS Clock Distribution54                                                    |

| PLL with External VCXO/VCO Followed by Clock           | LVPECL Clock Distribution55                                                  |

| Distribution25                                         | LVDS Clock Distribution55                                                    |

| Clock Distribution Only25                              | Power and Grounding Considerations and Power Supply                          |

| PLL with External VCO and Band-Pass Filter Followed by | Rejection                                                                    |

| Clock Distribution                                     | Outline Dimensions                                                           |

| Functional Description28                               | Ordering Guide56                                                             |

| REVISION HISTORY                                       |                                                                              |

| 0/2016—Rev. B to Rev. C                                | Added EPAD Row, Table 1419                                                   |

| Changes to STATUS Pin Section                          | Changes to Figure 21                                                         |

| Changes to Ordering Guide56                            | Changes to Delay Block Section, Figure 40, and Calculating the Delay Section |

| 0/2013—Rev. A to Rev. B                                | Changes to Address 0x36[5:1] and Address 0x3A[5:1],                          |

| Changes to General Description Section                 | Table 24                                                                     |

| Changes to Table 4                                     | Changes to Address 0x36 and Address 0x3A, Table 25 49                        |

| Changes to Table 611                                   | Updated Outline Dimensions                                                   |

| Added Table 13; Renumbered Sequentially                | Changes to Ordering Guide                                                    |

| nanges to Highire 6                                    |                                                                              |

| 5/2005—Rev. 0 to Rev. A                             |    |

|-----------------------------------------------------|----|

| Changes to Features                                 |    |

| Changes to Table 1 and Table 2                      | 5  |

| Changes to Table 4                                  | 8  |

| Changes to Table 5                                  |    |

| Changes to Table 6                                  | 14 |

| Changes to Table 8 and Table 9                      | 15 |

| Changes to Table 11                                 | 16 |

| Changes to Table 13                                 | 20 |

| Changes to Figure 7 and Figure 10                   | 22 |

| Changes to Figure 19 to Figure 23                   | 24 |

| Changes to Figure 30 and Figure 31                  | 26 |

| Changes to Figure 32                                | 27 |

| Changes to Figure 33                                | 28 |

| Changes to VCO/VCXO Clock Input—CLK2 Section        | 29 |

| Changes to A and B Counters Section                 | 30 |

| Changes to PLL Digital Lock Detect Section          |    |

| Changes to PLL Analog Lock Detect Section           | 32 |

| Changes to Loss of Reference Section                | 32 |

| Changes to FUNCTION Pin Section                     | 33 |

| Changes to RESETB: 58h<6:5> = 00b (Default) Section | 33 |

| Changes to SYNCB: 58h<6:5> = 01b Section            |    |

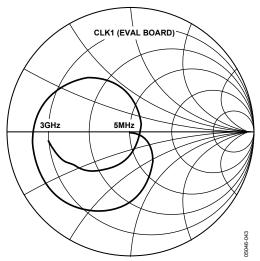

| Changes to CLK1 and CLK2 Clock Inputs Section       | 33 |

|                                                     |    |

| Changes to Calculating the Delay Section                | 38 |

|---------------------------------------------------------|----|

| Changes to Soft Reset via the Serial Port Section       | 41 |

| Changes to Multichip Synchronization Section            | 41 |

| Changes to Serial Control Port Section                  | 42 |

| Changes to Serial Control Port Pin Descriptions Section | 42 |

| Changes to General Operation of Serial                  |    |

| Control Port Section                                    | 42 |

| Added Framing a Communication Cycle with CSB Section    | 42 |

| Added Communication Cycle—Instruction Plus              |    |

| Data Section                                            | 42 |

| Changes to Write Section                                | 42 |

| Changes to Read Section                                 | 42 |

| Changes to The Instruction Word (16 Bits) Section       |    |

| Changes to Table 20                                     |    |

| Changes to MSB/LSB First Transfers Section              | 43 |

| Changes to Table 21                                     | 44 |

| Added Figure 52; Renumbered Sequentially                | 45 |

| Changes to Table 23                                     | 46 |

| Changes to Table 24                                     | 49 |

| Changes to Using the AD9510 Outputs for ADC Clock       |    |

| Applications                                            | 57 |

|                                                         |    |

4/2005—Revision 0: Initial Version

# **SPECIFICATIONS**

Typical (typ) is given for  $V_S = 3.3 \text{ V} \pm 5\%$ ,  $V_S \leq VCP_S \leq 5.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $R_{SET} = 4.12 \text{ k}\Omega$ ,  $CPR_{SET} = 5.1 \text{ k}\Omega$ , unless otherwise noted. Minimum (min) and maximum (max) values are given over full  $V_S$  and  $T_A$  ( $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ) variation.

### **PLL CHARACTERISTICS**

Table 1.

| Parameter                                 | Min  | Тур    | Max  | Unit   | Test Conditions/Comments                                                                                       |

|-------------------------------------------|------|--------|------|--------|----------------------------------------------------------------------------------------------------------------|

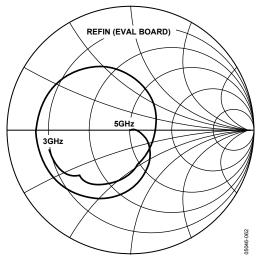

| REFERENCE INPUTS (REFIN)                  |      |        |      |        |                                                                                                                |

| Input Frequency                           | 0    |        | 250  | MHz    |                                                                                                                |

| Input Sensitivity                         |      | 150    |      | mV p-p |                                                                                                                |

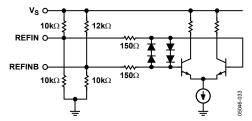

| Self-Bias Voltage, REFIN                  | 1.45 | 1.60   | 1.75 | V      | Self-bias voltage of REFIN <sup>1</sup>                                                                        |

| Self-Bias Voltage, REFINB                 | 1.40 | 1.50   | 1.60 | V      | Self-bias voltage of REFINB <sup>1</sup>                                                                       |

| Input Resistance, REFIN                   | 4.0  | 4.9    | 5.8  | kΩ     | Self-biased <sup>1</sup>                                                                                       |

| Input Resistance, REFINB                  | 4.5  | 5.4    | 6.3  | kΩ     | Self-biased <sup>1</sup>                                                                                       |

| Input Capacitance                         |      | 2      |      | pF     |                                                                                                                |

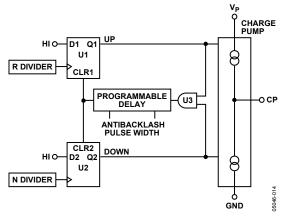

| PHASE FREQUENCY DETECTOR (PFD)            |      |        |      | -      |                                                                                                                |

| PFD Input Frequency                       |      |        | 100  | MHz    | Antibacklash pulse width, Register 0x0D[1:0] = 00b                                                             |

| PFD Input Frequency                       |      |        | 100  | MHz    | Antibacklash pulse width, Register 0x0D[1:0] = 01b                                                             |

| PFD Input Frequency                       |      |        | 45   | MHz    | Antibacklash pulse width, Register 0x0D[1:0] = 10b                                                             |

| Antibacklash Pulse Width                  |      | 1.3    |      | ns     | Register 0x0D[1:0] = 00b (this is the default setting)                                                         |

| Antibacklash Pulse Width                  |      | 2.9    |      | ns     | Register 0x0D[1:0] = 01b                                                                                       |

| Antibacklash Pulse Width                  |      | 6.0    |      | ns     | Register 0x0D[1:0] = 10b                                                                                       |

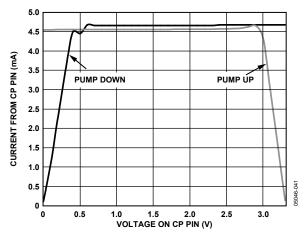

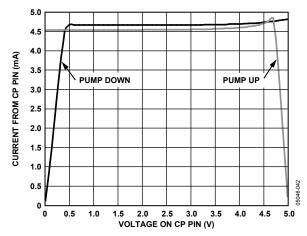

| CHARGE PUMP (CP)                          |      |        |      |        |                                                                                                                |

| I <sub>CP</sub> Sink/Source               |      |        |      |        | Programmable                                                                                                   |

| High Value                                |      | 4.8    |      | mA     | With $CPR_{SET} = 5.1 \text{ k}\Omega$                                                                         |

| Low Value                                 |      | 0.60   |      | mA     |                                                                                                                |

| Absolute Accuracy                         |      | 2.5    |      | %      | $V_{CP} = VCP_S/2$                                                                                             |

| CPR <sub>SET</sub> Range                  |      | 2.7/10 |      | kΩ     |                                                                                                                |

| Icp Three-State Leakage                   |      | 1      |      | nA     |                                                                                                                |

| Sink-and-Source Current Matching          |      | 2      |      | %      | $0.5 < V_{CP} < VCP_S - 0.5 V$                                                                                 |

| ICP VS. VCP                               |      | 1.5    |      | %      | $0.5 < V_{CP} < VCP_S - 0.5 V$                                                                                 |

| I <sub>CP</sub> vs. Temperature           |      | 2      |      | %      | $V_{CP} = VCP_s/2 V$                                                                                           |

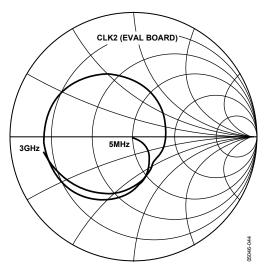

| RF CHARACTERISTICS (CLK2) <sup>2</sup>    |      |        |      | ,,,    | 10.32                                                                                                          |

| Input Frequency                           |      |        | 1.6  | GHz    | Frequencies > 1200 MHz (LVPECL) or 800 MHz (LVDS) require a minimum divide-by-2 (see the Distribution Section) |

| Input Sensitivity                         |      | 150    |      | mV p-p |                                                                                                                |

| Input Common-Mode Voltage, $V_{CM}$       | 1.5  | 1.6    | 1.7  | V      | Self-biased, enables ac coupling                                                                               |

| Input Common-Mode Range, V <sub>CMR</sub> | 1.3  |        | 1.8  | V      | With 200 mV p-p signal applied                                                                                 |

| Input Sensitivity, Single-Ended           |      | 150    |      | mV p-p | CLK2 ac-coupled, CLK2B capacitively bypassed to RF ground                                                      |

| Input Resistance                          | 4.0  | 4.8    | 5.6  | kΩ     | Self-biased                                                                                                    |

| Input Capacitance                         |      | 2      |      | pF     |                                                                                                                |

| CLK2 VS. REFIN DELAY                      |      | 500    |      | ps     | Difference at PFD                                                                                              |

| PRESCALER (PART OF N DIVIDER)             |      |        |      |        | See the VCO/VCXO Feedback Divider—N (P, A, B) section                                                          |

| Prescaler Input Frequency                 |      |        |      |        |                                                                                                                |

| P = 2 DM (2/3)                            |      |        | 600  | MHz    |                                                                                                                |

| P = 4 DM (4/5)                            |      |        | 1000 | MHz    |                                                                                                                |

| P = 8 DM (8/9)                            |      |        | 1600 | MHz    |                                                                                                                |

| P = 16 DM (16/17)                         |      |        | 1600 | MHz    |                                                                                                                |

| P = 32 DM (32/33)                         |      |        | 1600 | MHz    |                                                                                                                |

| CLK2 Input Frequency for PLL              |      |        | 300  | MHz    | A, B counter input frequency                                                                                   |

| Parameter                                                                                                  | Min | Тур                               | Max | Unit   | Test Conditions/Comments                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

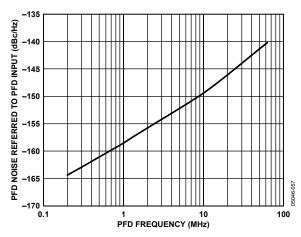

| NOISE CHARACTERISTICS                                                                                      |     |                                   |     |        |                                                                                                                                                                                  |

| In-Band Noise of the Charge Pump/<br>Phase Frequency Detector (In-Band<br>Means Within the LBW of the PLL) |     |                                   |     |        | Synthesizer phase noise floor estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20logN (where N is the N divider value)                    |

| At 50 kHz PFD Frequency                                                                                    |     | -172                              |     | dBc/Hz |                                                                                                                                                                                  |

| At 2 MHz PFD Frequency                                                                                     |     | -156                              |     | dBc/Hz |                                                                                                                                                                                  |

| At 10 MHz PFD Frequency                                                                                    |     | -149                              |     | dBc/Hz |                                                                                                                                                                                  |

| At 50 MHz PFD Frequency                                                                                    |     | -142                              |     | dBc/Hz |                                                                                                                                                                                  |

| PLL Figure of Merit                                                                                        |     | $-218 + 10 \times \log (f_{PFD})$ |     | dBc/Hz | Approximation of the PFD/CP phase noise floor (in the flat region) inside the PLL loop bandwidth; when running closed loop this phase noise is gained up by $20 \times log(N)^3$ |

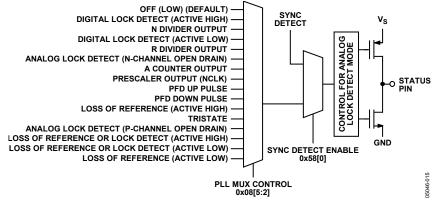

| PLL DIGITAL LOCK DETECT WINDOW <sup>4</sup>                                                                |     |                                   |     |        | Signal available at STATUS pin when selected by Register 0x08[5:2]                                                                                                               |

| Required to Lock (Coincidence of Edges)                                                                    |     |                                   |     |        | Selected by Register 0x0D                                                                                                                                                        |

| Low Range (ABP 1.3 ns, 2.9 ns)                                                                             |     | 3.5                               |     | ns     | Bit[5] = 1b.                                                                                                                                                                     |

| High Range (ABP 1.3 ns, 2.9 ns)                                                                            |     | 7.5                               |     | ns     | Bit[5] = 0b.                                                                                                                                                                     |

| High Range (ABP 6 ns)                                                                                      |     | 3.5                               |     | ns     | Bit[5] = 0b.                                                                                                                                                                     |

| To Unlock After Lock (Hysteresis) <sup>4</sup>                                                             |     |                                   |     |        | Selected by Register 0x0D                                                                                                                                                        |

| Low Range (ABP 1.3 ns, 2.9 ns)                                                                             |     | 7                                 |     | ns     | Bit[5] = 1b.                                                                                                                                                                     |

| High Range (ABP 1.3 ns, 2.9 ns)                                                                            |     | 15                                |     | ns     | Bit[5] = 0b.                                                                                                                                                                     |

| High Range (ABP 6 ns)                                                                                      |     | 11                                |     | ns     | Bit[5] = 0b.                                                                                                                                                                     |

### **CLOCK INPUTS**

Table 2.

| Parameter                              | Symbol    | Min | Тур              | Max            | Unit   | Test Conditions/Comments                                                       |

|----------------------------------------|-----------|-----|------------------|----------------|--------|--------------------------------------------------------------------------------|

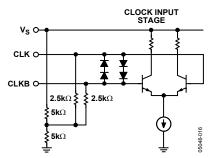

| CLOCK INPUTS (CLK1, CLK2) <sup>1</sup> |           |     |                  |                |        |                                                                                |

| Input Frequency                        |           | 0   |                  | 1.6            | GHz    |                                                                                |

| Input Sensitivity                      |           |     | 150 <sup>2</sup> |                | mV p-p | Jitter performance can be improved with higher slew rates (greater swing)      |

| Input Level                            |           |     |                  | 2 <sup>3</sup> | V p-p  | Larger swings turn on the protection diodes and can degrade jitter performance |

| Input Common-Mode Voltage              | $V_{CM}$  | 1.5 | 1.6              | 1.7            | V      | Self-biased; enables ac coupling                                               |

| Input Common-Mode Range                | $V_{CMR}$ | 1.3 |                  | 1.8            | V      | With 200 mV p-p signal applied; dc-coupled                                     |

| Input Sensitivity, Single-Ended        |           |     | 150              |                | mV p-p | CLK2 ac-coupled, CLK2B ac-bypassed to RF ground                                |

| Input Resistance                       |           | 4.0 | 4.8              | 5.6            | kΩ     | Self-biased                                                                    |

| Input Capacitance                      |           |     | 2                |                | pF     |                                                                                |

<sup>&</sup>lt;sup>1</sup> CLK1 and CLK2 are electrically identical; each can be used as either a differential or a single-ended input.

<sup>&</sup>lt;sup>1</sup> REFIN and REFINB self-bias points are offset slightly to avoid chatter on an open input condition.

<sup>2</sup> CLK2 is electrically identical to CLK1; the distribution-only input can be used as differential or single-ended input (see the Clock Inputs section).

<sup>3</sup> Example: –218 + 10 × log(f<sub>PFD</sub>) + 20 × log(N) gives the values for the in-band noise at the VCO output.

<sup>4</sup> For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.

<sup>&</sup>lt;sup>2</sup> With a 50 Ω termination, this is -12.5 dBm.

$<sup>^3</sup>$  With a 50  $\Omega$  termination, this is +10 dBm.

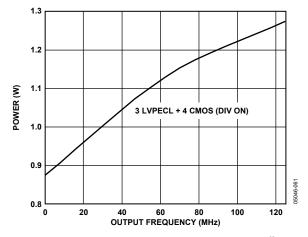

# **CLOCK OUTPUTS**

Table 3.

| Parameter                   | Symbol                            | Min           | Тур                 | Max                   | Unit | Test Conditions/Comments                         |

|-----------------------------|-----------------------------------|---------------|---------------------|-----------------------|------|--------------------------------------------------|

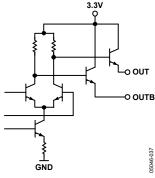

| LVPECL CLOCK OUTPUTS        |                                   |               |                     |                       |      | Termination = $50 \Omega$ to $V_s - 2 V$         |

| OUT0, OUT1, OUT2, OUT3;     |                                   |               |                     |                       |      | Output level Register 0x3C, Register 0x3D,       |

| Differential                |                                   |               |                     |                       |      | Register 0x3E, Register 0x3F[3:2] = 10b          |

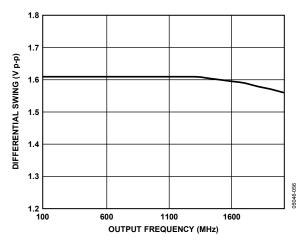

| Output Frequency            |                                   |               |                     | 1200                  | MHz  | See Figure 21                                    |

| Output High Voltage         | V <sub>OH</sub>                   | $V_S - 1.22$  | $V_{\text{S}}-0.98$ | $V_{\text{S}} - 0.93$ | V    |                                                  |

| Output Low Voltage          | $V_{OL}$                          | $V_s - 2.10$  | $V_{s} - 1.80$      | $V_{s} - 1.67$        | V    |                                                  |

| Output Differential Voltage | V <sub>OD</sub>                   | 660           | 810                 | 965                   | mV   |                                                  |

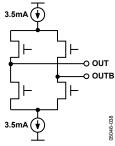

| LVDS CLOCK OUTPUTS          |                                   |               |                     |                       |      | Termination = $100 \Omega$ differential; default |

| OUT4, OUT5, OUT6, OUT7;     |                                   |               |                     |                       |      | Output level Register 0x40, Register 0x41,       |

| Differential                |                                   |               |                     |                       |      | Register 0x42, Register 0x43[2:1] = 01b          |

|                             |                                   |               |                     |                       |      | 3.5 mA termination current                       |

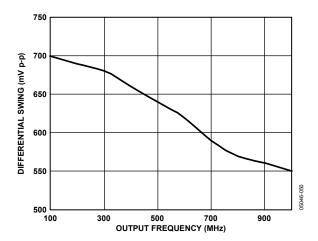

| Output Frequency            |                                   |               |                     | 800                   | MHz  | See Figure 22                                    |

| Differential Output Voltage | $V_{OD}$                          | 250           | 360                 | 450                   | mV   |                                                  |

| Delta V <sub>OD</sub>       |                                   |               |                     | 25                    | mV   |                                                  |

| Output Offset Voltage       | Vos                               | 1.125         | 1.23                | 1.375                 | V    |                                                  |

| Delta V <sub>os</sub>       |                                   |               |                     | 25                    | mV   |                                                  |

| Short-Circuit Current       | I <sub>SA</sub> , I <sub>SB</sub> |               | 14                  | 24                    | mA   | Output shorted to GND                            |

| CMOS CLOCK OUTPUTS          |                                   |               |                     |                       |      |                                                  |

| OUT4, OUT5, OUT6, OUT7      |                                   |               |                     |                       |      | Single-ended measurements, B outputs:            |

|                             |                                   |               |                     |                       |      | inverted, termination open                       |

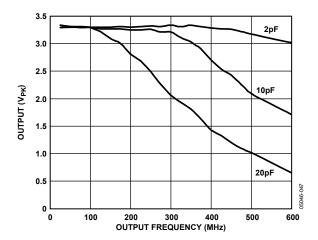

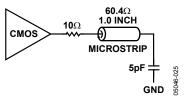

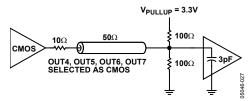

| Output Frequency            |                                   |               |                     | 250                   | MHz  | With 5 pF load each output, see Figure 23        |

| Output Voltage High         | $V_{OH}$                          | $V_{s} - 0.1$ |                     |                       | V    | At 1 mA load                                     |

| Output Voltage Low          | V <sub>OL</sub>                   |               |                     | 0.1                   | V    | At 1 mA load                                     |

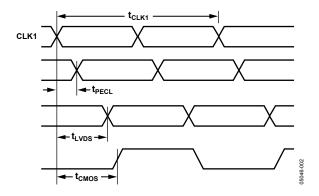

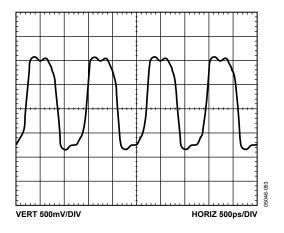

### **TIMING CHARACTERISTICS**

Table 4.

| Parameter                                             | Symbol              | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                                                                                         |

|-------------------------------------------------------|---------------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

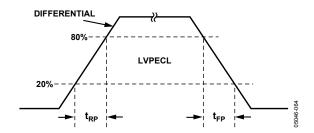

| LVPECL                                                |                     |     |     |     |       | Termination = $50 \Omega$ to $V_s - 2 V$ ; output level<br>Register 0x3C, Register 0x3D, Register 0x3E,<br>Register 0x3F[3:2] = $10b$                            |

| Output Rise Time                                      | t <sub>RP</sub>     |     | 130 | 180 | ps    | 20% to 80%, measured differentially                                                                                                                              |

| Output Fall Time                                      | t <sub>FP</sub>     |     | 130 | 180 | ps    | 80% to 20%, measured differentially                                                                                                                              |

| PROPAGATION DELAY, CLK-TO-LVPECL OUT <sup>1</sup>     | t <sub>PECL</sub>   |     |     |     |       |                                                                                                                                                                  |

| Divide = Bypass                                       |                     | 335 | 490 | 635 | ps    |                                                                                                                                                                  |

| Divide = $2 - 32$                                     |                     | 375 | 545 | 695 | ps    |                                                                                                                                                                  |

| Variation with Temperature                            |                     |     | 0.5 |     | ps/°C |                                                                                                                                                                  |

| OUTPUT SKEW, LVPECL OUTPUTS                           |                     |     |     |     |       |                                                                                                                                                                  |

| OUT1 to OUT0 on Same Part <sup>2</sup>                | t <sub>SKP</sub>    | -5  | +30 | +85 | ps    |                                                                                                                                                                  |

| OUT2 to OUT3 on Same Part <sup>2</sup>                | t <sub>SKP</sub>    | 15  | 45  | 80  | ps    |                                                                                                                                                                  |

| All LVPECL OUTs on Same Part <sup>2</sup>             | t <sub>SKP</sub>    | 90  | 130 | 180 | ps    |                                                                                                                                                                  |

| All LVPECL OUTs Across Multiple Parts <sup>3</sup>    | t <sub>SKP_AB</sub> |     |     | 275 | ps    |                                                                                                                                                                  |

| Same LVPECL OUT Across Multiple<br>Parts <sup>3</sup> | t <sub>SKP_AB</sub> |     |     | 130 | ps    |                                                                                                                                                                  |

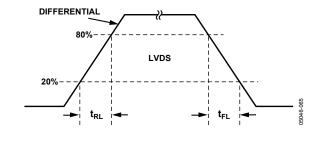

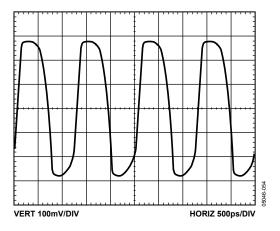

| LVDS                                                  |                     |     |     |     |       | Termination = $100 \Omega$ differential; output level<br>Register 0x40, Register 0x41, Register 0x42,<br>Register 0x43[2:1] = 01b; 3.5 mA termination<br>current |

| Output Rise Time                                      | t <sub>RL</sub>     |     | 200 | 350 | ps    | 20% to 80%, measured differentially                                                                                                                              |

| Output Fall Time                                      | t <sub>FL</sub>     |     | 210 | 350 | ps    | 80% to 20%, measured differentially                                                                                                                              |

| Parameter                                        | Symbol              | Min  | Тур   | Max  | Unit  | Test Conditions/Comments                   |

|--------------------------------------------------|---------------------|------|-------|------|-------|--------------------------------------------|

| PROPAGATION DELAY, CLK-TO-LVDS OUT <sup>1</sup>  | t <sub>LVDS</sub>   |      |       |      |       | Delay off on OUT5 and OUT6                 |

| OUT4, OUT5, OUT6, OUT7                           |                     |      |       |      |       |                                            |

| Divide = Bypass                                  |                     | 0.99 | 1.33  | 1.59 | ns    |                                            |

| Divide = $2 - 32$                                |                     | 1.04 | 1.38  | 1.64 | ns    |                                            |

| Variation with Temperature                       |                     |      | 0.9   |      | ps/°C |                                            |

| OUTPUT SKEW, LVDS OUTPUTS                        |                     |      |       |      |       | Delay off on OUT5 and OUT6                 |

| OUT4 to OUT7 on Same Part <sup>2</sup>           | t <sub>SKV</sub>    | -85  |       | +270 | ps    |                                            |

| OUT5 to OUT6 on Same Part <sup>2</sup>           | t <sub>SKV</sub>    | -175 |       | +155 | ps    |                                            |

| All LVDS OUTs on Same Part <sup>2</sup>          | tskv                | -175 |       | +270 | ps    |                                            |

| All LVDS OUTs Across Multiple Parts <sup>3</sup> | t <sub>SKV_AB</sub> |      |       | 450  | ps    |                                            |

| Same LVDS OUT Across Multiple Parts <sup>3</sup> | t <sub>SKV_AB</sub> |      |       | 325  | ps    |                                            |

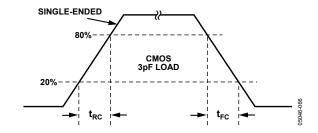

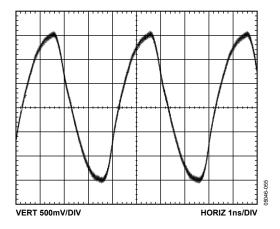

| CMOS                                             |                     |      |       |      |       | B outputs are inverted, termination = open |

| Output Rise Time                                 | t <sub>RC</sub>     |      | 681   | 865  | ps    | 20% to 80%; C <sub>LOAD</sub> = 3 pF       |

| Output Fall Time                                 | t <sub>FC</sub>     |      | 646   | 992  | ps    | 80% to 20%; C <sub>LOAD</sub> = 3 pF       |

| PROPAGATION DELAY, CLK-TO-CMOS OUT <sup>1</sup>  | t <sub>CMOS</sub>   |      |       |      |       | Delay off on OUT5 and OUT6                 |

| Divide = Bypass                                  |                     | 1.02 | 1.39  | 1.71 | ns    |                                            |

| Divide = $2 - 32$                                |                     | 1.07 | 1.44  | 1.76 | ns    |                                            |

| Variation with Temperature                       |                     |      | 1     |      | ps/°C |                                            |

| OUTPUT SKEW, CMOS OUTPUTS                        |                     |      |       |      |       | Delay off on OUT5 and OUT6                 |

| All CMOS OUTs on Same Part <sup>2</sup>          | tskc                | -140 | +145  | +300 | ps    |                                            |

| All CMOS OUTs Across Multiple Parts <sup>3</sup> | t <sub>SKC_AB</sub> |      |       | 650  | ps    |                                            |

| Same CMOS OUT Across Multiple Parts <sup>3</sup> | t <sub>SKC_AB</sub> |      |       | 500  | ps    |                                            |

| LVPECL-TO-LVDS OUT                               |                     |      |       |      |       | Everything the same; different logic type  |

| Output Skew                                      | t <sub>SKP_V</sub>  | 0.74 | 0.92  | 1.14 | ns    | LVPECL to LVDS on same part                |

| LVPECL-TO-CMOS OUT                               |                     |      |       |      |       | Everything the same; different logic type  |

| Output Skew                                      | t <sub>SKP_C</sub>  | 0.88 | 1.14  | 1.43 | ns    | LVPECL to CMOS on same part                |

| LVDS-TO-CMOS OUT                                 |                     |      |       |      |       | Everything the same; different logic type  |

| Output Skew                                      | t <sub>SKV_C</sub>  | 158  | 353   | 506  | ps    | LVDS to CMOS on same part                  |

| DELAY ADJUST <sup>4</sup>                        |                     |      |       |      |       | OUT5 (OUT6); LVDS and CMOS                 |

| Shortest Delay Range⁵                            |                     |      |       |      |       | Register 0x35, Register 0x39[5:1] = 11111b |

| Zero Scale                                       |                     | 0.05 | 0.36  | 0.68 | ns    | Register 0x36, Register 0x3A[5:1] = 00000b |

| Full Scale                                       |                     | 0.57 | 0.95  | 1.32 | ns    | Register 0x36, Register 0x3A[5:1] = 11000b |

| Linearity, DNL                                   |                     |      | 0.5   |      | LSB   |                                            |

| Linearity, INL                                   |                     |      | 0.8   |      | LSB   |                                            |

| Longest Delay Range⁵                             |                     |      |       |      |       | Register 0x35, Register 0x39[5:1] = 00000b |

| Zero Scale                                       |                     | 0.20 | 0.57  | 0.95 | ns    | Register 0x36, Register 0x3A[5:1] = 00000b |

| Full Scale                                       |                     | 7.0  | 8.0   | 9.2  | ns    | Register 0x36, Register 0x3A[5:1] = 11000b |

| Linearity, DNL                                   |                     |      | 0.3   |      | LSB   | _                                          |

| Linearity, INL                                   |                     |      | 0.6   |      | LSB   |                                            |

| Delay Variation with Temperature                 |                     |      |       |      |       |                                            |

| Long Delay Range, 8 ns <sup>6</sup>              |                     |      |       |      |       |                                            |

| Zero Scale                                       |                     |      | 0.35  |      | ps/°C |                                            |

| Full Scale                                       |                     |      | -0.14 |      | ps/°C |                                            |

| Short Delay Range, 1 ns <sup>6</sup>             |                     |      |       |      |       |                                            |

| Zero Scale                                       |                     |      | 0.51  |      | ps/°C |                                            |

| Full Scale                                       |                     |      | 0.67  |      | ps/°C |                                            |

<sup>&</sup>lt;sup>1</sup> These measurements are for CLK1. For CLK2, add approximately 25 ps.

<sup>2</sup> This is the difference between any two similar delay paths within a single device operating at the same voltage and temperature.

<sup>3</sup> This is the difference between any two similar delay paths across multiple devices operating at the same voltage and temperature.

<sup>4</sup> The maximum delay that can be used is a little less than one half the period of the clock. A longer delay disables the output.

<sup>5</sup> Incremental delay; does not include propagation delay.

<sup>6</sup> All delays between zero scale and full scale can be estimated by linear interpolation.

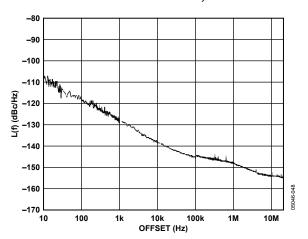

# **CLOCK OUTPUT PHASE NOISE**

Table 5.

| Parameter                           | Min Typ | Max Unit | Test Conditions/Comments                                             |

|-------------------------------------|---------|----------|----------------------------------------------------------------------|

| CLK1-TO-LVPECL ADDITIVE PHASE NOISE |         |          | Distribution Section only, does not include PLL or external VCO/VCXO |

| CLK1 = 622.08 MHz, OUT = 622.08 MHz |         |          | Input slew rate > 1 V/ns                                             |

| Divide Ratio = 1                    |         |          |                                                                      |

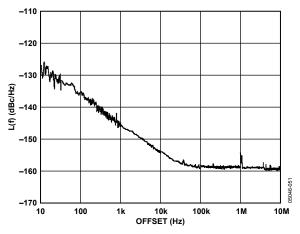

| At 10 Hz Offset                     | -125    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -132    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -140    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -148    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -153    | dBc/Hz   |                                                                      |

| >1 MHz Offset                       | -154    | dBc/Hz   |                                                                      |

| CLK1 = 622.08 MHz, OUT = 155.52 MHz |         |          |                                                                      |

| Divide Ratio = 4                    |         |          |                                                                      |

| At 10 Hz Offset                     | -128    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -140    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -148    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -155    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -161    | dBc/Hz   |                                                                      |

| >1 MHz Offset                       | -161    | dBc/Hz   |                                                                      |

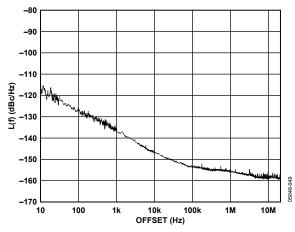

| CLK1 = 622.08 MHz, OUT = 38.88 MHz  |         |          |                                                                      |

| Divide Ratio = 16                   |         |          |                                                                      |

| At 10 Hz Offset                     | -135    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -145    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -158    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -165    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -165    | dBc/Hz   |                                                                      |

| >1 MHz Offset                       | -166    | dBc/Hz   |                                                                      |

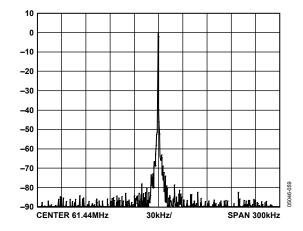

| CLK1 = 491.52 MHz, OUT = 61.44 MHz  |         |          |                                                                      |

| Divide Ratio = 8                    |         |          |                                                                      |

| At 10 Hz Offset                     | -131    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -142    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -153    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -160    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -165    | dBc/Hz   |                                                                      |

| > 1 MHz Offset                      | -165    | dBc/Hz   |                                                                      |

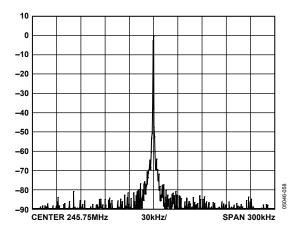

| CLK1 = 491.52 MHz, OUT = 245.76 MHz |         |          |                                                                      |

| Divide Ratio = 2                    |         |          |                                                                      |

| At 10 Hz Offset                     | -125    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -132    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -140    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -151    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -157    | dBc/Hz   |                                                                      |

| >1 MHz Offset                       | -158    | dBc/Hz   |                                                                      |

| CLK1 = 245.76 MHz, OUT = 61.44 MHz  |         |          |                                                                      |

| Divide Ratio = 4                    |         |          |                                                                      |

| At 10 Hz Offset                     | -138    | dBc/Hz   |                                                                      |

| At 100 Hz Offset                    | -144    | dBc/Hz   |                                                                      |

| At 1 kHz Offset                     | -154    | dBc/Hz   |                                                                      |

| At 10 kHz Offset                    | -163    | dBc/Hz   |                                                                      |

| At 100 kHz Offset                   | -164    | dBc/Hz   |                                                                      |

| >1 MHz Offset                       | -165    | dBc/Hz   |                                                                      |

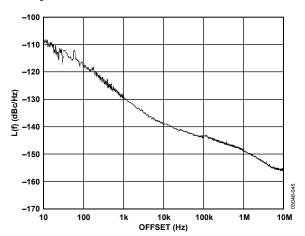

| Parameter                           | Min Typ      | Max | Unit    | Test Conditions/Comments                    |

|-------------------------------------|--------------|-----|---------|---------------------------------------------|

| CLK1-TO-LVDS ADDITIVE PHASE NOISE   |              |     |         | Distribution Section only; does not include |

|                                     |              |     |         | PLL or external VCO/VCXO                    |

| CLK1 = 622.08 MHz, OUT= 622.08 MHz  |              |     |         |                                             |

| Divide Ratio = 1                    |              |     |         |                                             |

| At 10 Hz Offset                     | -100         |     | dBc/Hz  |                                             |

| At 100 Hz Offset                    | -110         |     | dBc/Hz  |                                             |

| At 1 kHz Offset                     | -118         |     | dBc/Hz  |                                             |

| At 10 kHz Offset                    | -129         |     | dBc/Hz  |                                             |

| At 100 kHz Offset                   | -135         |     | dBc/Hz  |                                             |

| At 1 MHz Offset                     | -140         |     | dBc/Hz  |                                             |

| >10 MHz Offset                      | -148         |     | dBc/Hz  |                                             |

| CLK1 = 622.08 MHz, OUT = 155.52 MHz |              |     |         |                                             |

| Divide Ratio = 4                    |              |     |         |                                             |

| At 10 Hz Offset                     | -112         |     | dBc/Hz  |                                             |

| At 100 Hz Offset                    | -122         |     | dBc/Hz  |                                             |

| At 1 kHz Offset                     | -132         |     | dBc/Hz  |                                             |

| At 10 kHz Offset                    | -142         |     | dBc/Hz  |                                             |

| At 100 kHz Offset                   | -148         |     | dBc/Hz  |                                             |

| At 1 MHz Offset                     | -152         |     | dBc/Hz  |                                             |

| >10 MHz Offset                      | -155         |     | dBc/Hz  |                                             |

| CLK1 = 491.52 MHz, OUT = 245.76 MHz |              |     |         |                                             |

| Divide Ratio = 2                    |              |     |         |                                             |

| At 10 Hz Offset                     | -108         |     | dBc/Hz  |                                             |

| At 100 Hz Offset                    | -118         |     | dBc/Hz  |                                             |

| At 1 kHz Offset                     | -128         |     | dBc/Hz  |                                             |

| At 10 kHz Offset                    | -138         |     | dBc/Hz  |                                             |

| At 100 kHz Offset                   | -145         |     | dBc/Hz  |                                             |

| At 1 MHz Offset                     | -148         |     | dBc/Hz  |                                             |

| >10 MHz Offset                      | -154         |     | dBc/Hz  |                                             |

| CLK1 = 491.52 MHz, OUT = 122.88 MHz |              |     |         |                                             |

| Divide Ratio = 4                    |              |     |         |                                             |

| At 10 Hz Offset                     | -118         |     | dBc/Hz  |                                             |

| At 100 Hz Offset                    | -129         |     | dBc/Hz  |                                             |

| At 1 kHz Offset                     | -136         |     | dBc/Hz  |                                             |

| At 10 kHz Offset                    | -147         |     | dBc/Hz  |                                             |

| At 100 kHz Offset                   | -153         |     | dBc/Hz  |                                             |

| At 1 MHz Offset                     | -156         |     | dBc/Hz  |                                             |

| >10 MHz Offset                      | -158         |     | dBc/Hz  |                                             |

| CLK1 = 245.76 MHz, OUT = 245.76 MHz | 130          |     | 450,112 |                                             |

| Divide Ratio = 1                    |              |     |         |                                             |

| At 10 Hz Offset                     | -108         |     | dBc/Hz  |                                             |

| At 100 Hz Offset                    | -118         |     | dBc/Hz  |                                             |

| At 1 kHz Offset                     | -128         |     | dBc/Hz  |                                             |

| At 10 kHz Offset                    | -138         |     | dBc/Hz  |                                             |

| At 100 kHz Offset                   | -138<br>-145 |     | dBc/Hz  |                                             |

| At 1 MHz Offset                     | -148         |     | dBc/Hz  |                                             |

| >10 MHz Offset                      | -148<br>-155 |     | dBc/Hz  |                                             |

| / IO IVII IZ OTISEL                 | -133         |     | UDC/FIZ |                                             |

| Parameter                             | Min | Тур  | Max | Unit   | Test Conditions/Comments                                             |

|---------------------------------------|-----|------|-----|--------|----------------------------------------------------------------------|

| CLK1 = 245.76 MHz, OUT = 122.88 MHz   |     |      |     |        |                                                                      |

| Divide Ratio = 2                      |     |      |     |        |                                                                      |

| At 10 Hz Offset                       |     | -118 |     | dBc/Hz |                                                                      |

| At 100 Hz Offset                      |     | -127 |     | dBc/Hz |                                                                      |

| At 1 kHz Offset                       |     | -137 |     | dBc/Hz |                                                                      |

| At 10 kHz Offset                      |     | -147 |     | dBc/Hz |                                                                      |

| At 100 kHz Offset                     |     | -154 |     | dBc/Hz |                                                                      |

| At 1 MHz Offset                       |     | -156 |     | dBc/Hz |                                                                      |

| >10 MHz Offset                        |     | -158 |     | dBc/Hz |                                                                      |

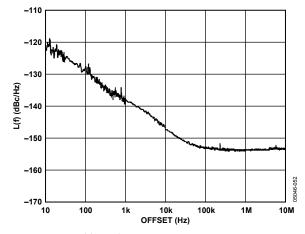

| CLK1-TO-CMOS ADDITIVE PHASE NOISE     |     |      |     |        | Distribution Section only, does not include PLL or external VCO/VCXO |

| CLK1 = 245.76 MHz, OUT = 245.76 MHz   |     |      |     |        | PLE or external VCO/VCXO                                             |

| Divide Ratio = 1                      |     |      |     |        |                                                                      |

| At 10 Hz Offset                       |     | -110 |     | dBc/Hz |                                                                      |

| At 100 Hz Offset                      |     | -121 |     | dBc/Hz |                                                                      |

| At 1 kHz Offset                       |     | -130 |     | dBc/Hz |                                                                      |

| At 10 kHz Offset                      |     | -140 |     | dBc/Hz |                                                                      |

| At 100 kHz Offset                     |     | -145 |     | dBc/Hz |                                                                      |

| At 1 MHz Offset                       |     | -149 |     | dBc/Hz |                                                                      |

| >10 MHz Offset                        |     | -156 |     | dBc/Hz |                                                                      |

| CLK1 = 245.76 MHz, OUT = 61.44 MHz    |     |      |     |        |                                                                      |

| Divide Ratio = 4                      |     |      |     |        |                                                                      |

| At 10 Hz Offset                       |     | -122 |     | dBc/Hz |                                                                      |

| At 100 Hz Offset                      |     | -132 |     | dBc/Hz |                                                                      |

| At 1 kHz Offset                       |     | -143 |     | dBc/Hz |                                                                      |

| At 10 kHz Offset                      |     | -152 |     | dBc/Hz |                                                                      |

| At 100 kHz Offset                     |     | -158 |     | dBc/Hz |                                                                      |

| At 1 MHz Offset                       |     | -160 |     | dBc/Hz |                                                                      |

| >10 MHz Offset                        |     | -162 |     | dBc/Hz |                                                                      |

| CLK1 = 78.6432 MHz, OUT = 78.6432 MHz |     |      |     |        |                                                                      |

| Divide Ratio = 1                      |     |      |     |        |                                                                      |

| At 10 Hz Offset                       |     | -122 |     | dBc/Hz |                                                                      |

| At 100 Hz Offset                      |     | -132 |     | dBc/Hz |                                                                      |

| At 1 kHz Offset                       |     | -140 |     | dBc/Hz |                                                                      |

| At 10 kHz Offset                      |     | -150 |     | dBc/Hz |                                                                      |

| At 100 kHz Offset                     |     | -155 |     | dBc/Hz |                                                                      |

| At 1 MHz Offset                       |     | -158 |     | dBc/Hz |                                                                      |

| >10 MHz Offset                        |     | -160 |     | dBc/Hz |                                                                      |

| CLK1 = 78.6432 MHz, OUT = 39.3216 MHz |     |      |     |        |                                                                      |

| Divide Ratio = 2                      |     |      |     |        |                                                                      |

| At 10 Hz Offset                       |     | -128 |     | dBc/Hz |                                                                      |

| At 100 Hz Offset                      |     | -136 |     | dBc/Hz |                                                                      |

| At 1 kHz Offset                       |     | -146 |     | dBc/Hz |                                                                      |

| At 10 kHz Offset                      |     | -155 |     | dBc/Hz |                                                                      |

| At 100 kHz Offset                     |     | -161 |     | dBc/Hz |                                                                      |

| >1 MHz Offset                         |     | -162 |     | dBc/Hz |                                                                      |

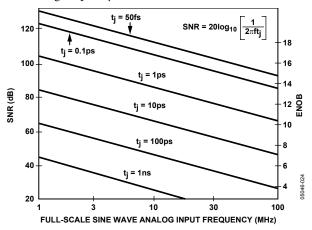

## **CLOCK OUTPUT ADDITIVE TIME JITTER**

Table 6.

| Parameter                                               | Min | Тур | Max | Unit   | Test Conditions/Comments                                                                           |

|---------------------------------------------------------|-----|-----|-----|--------|----------------------------------------------------------------------------------------------------|

| LVPECL OUTPUT ADDITIVE TIME JITTER                      |     |     |     |        | Distribution Section only, does not include PLL or external VCO/VCXO                               |

| CLK1 = 622.08 MHz                                       |     | 40  |     | fs rms | Bandwidth = 12 kHz – 20 MHz (OC-12)                                                                |

| Any LVPECL (OUT0 to OUT3) = 622.08 MHz                  |     |     |     |        |                                                                                                    |

| Divide Ratio = 1                                        |     |     |     |        |                                                                                                    |

| CLK1 = 622.08 MHz                                       |     | 55  |     | fs rms | Bandwidth = 12 kHz – 20 MHz (OC-3)                                                                 |

| Any LVPECL (OUT0 to OUT3) = 155.52 MHz                  |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| CLK1 = 400 MHz                                          |     | 215 |     | fs rms | Calculated from signal-to-noise ratio (SNR) of ADC method, $f_C = 100$ MHz with $A_{IN} = 170$ MHz |

| Any LVPECL (OUT0 to OUT3) = 100 MHz                     |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| CLK1 = 400 MHz                                          |     | 215 |     | fs rms | Calculated from SNR of ADC method, $f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$         |

| Any LVPECL (OUT0 to OUT3) = 100 MHz                     |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        | lataria and a                                                                                      |

| All Other LVPECL = 100 MHz                              |     |     |     |        | Interferer(s)                                                                                      |

| All LVDS (OUT4 to OUT7) = 100 MHz                       |     | าาา |     | f      | Interferer(s)                                                                                      |

| CLK1 = 400 MHz                                          |     | 222 |     | fs rms | Calculated from SNR of ADC method,<br>$f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$      |

| Any LVPECL (OUT0 to OUT3) = 100 MHz                     |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| All Other LVPECL = 50 MHz                               |     |     |     |        | Interferer(s)                                                                                      |

| All LVDS (OUT4 to OUT7) = 50 MHz                        |     |     |     |        | Interferer(s)                                                                                      |

| CLK1 = 400 MHz                                          |     | 225 |     | fs rms | Calculated from SNR of ADC method;<br>$f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$      |

| Any LVPECL (OUT0 to OUT3) = 100 MHz<br>Divide Ratio = 4 |     |     |     |        |                                                                                                    |

| All Other LVPECL = 50 MHz                               |     |     |     |        | Interferer(s)                                                                                      |

| All CMOS (OUT4 to OUT7) = 50 MHz (B Outputs Off)        |     |     |     |        | Interferer(s)                                                                                      |

| CLK1 = 400 MHz                                          |     | 225 |     | fs rms | Calculated from SNR of ADC method,<br>$f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$      |

| Any LVPECL (OUT0 to OUT3) = 100 MHz                     |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| All Other LVPECL = 50 MHz                               |     |     |     |        | Interferer(s)                                                                                      |

| All CMOS (OUT4 to OUT7) = 50 MHz (B Outputs On)         |     |     |     |        | Interferer(s)                                                                                      |

| LVDS OUTPUT ADDITIVE TIME JITTER                        |     |     |     |        | Distribution Section only, does not include PLL or external VCO/VCXO                               |

| CLK1 = 400 MHz                                          |     | 264 |     | fs rms | Calculated from SNR of ADC method,<br>$f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$      |

| LVDS (OUT4, OUT7) = 100 MHz                             |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| CLK1 = 400 MHz                                          |     | 319 |     | fs rms | Calculated from SNR of ADC method,<br>f <sub>C</sub> = 100 MHz with A <sub>IN</sub> = 170 MHz      |

| LVDS (OUT5, OUT6) = 100 MHz                             |     |     |     |        |                                                                                                    |

| Divide Ratio = 4                                        |     |     |     |        |                                                                                                    |

| Parameter                                       | Min | Тур | Max | Unit   | Test Conditions/Comments                                                                      |

|-------------------------------------------------|-----|-----|-----|--------|-----------------------------------------------------------------------------------------------|

| CLK1 = 400 MHz                                  |     | 395 |     | fs rms | Calculated from SNR of ADC method, $f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$    |

| LVDS (OUT4, OUT7) = 100 MHz                     |     |     |     |        |                                                                                               |

| Divide Ratio = 4                                |     |     |     |        |                                                                                               |

| All Other LVDS = 50 MHz                         |     |     |     |        | Interferer(s)                                                                                 |

| All LVPECL = 50 MHz                             |     |     |     |        | Interferer(s)                                                                                 |

| CLK1 = 400 MHz                                  |     | 395 |     | fs rms | Calculated from SNR of ADC method,<br>$f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |

| LVDS (OUT5, OUT6) = $100 \text{ MHz}$           |     |     |     |        |                                                                                               |

| Divide Ratio = 4                                |     |     |     |        |                                                                                               |

| All Other LVDS = 50 MHz                         |     |     |     |        | Interferer(s)                                                                                 |

| All LVPECL = 50 MHz                             |     |     |     |        | Interferer(s)                                                                                 |

| CLK1 = 400 MHz                                  |     | 367 |     | fs rms | Calculated from SNR of ADC method, $f_C = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$    |

| LVDS (OUT4, OUT7) = 100 MHz                     |     |     |     |        |                                                                                               |

| Divide Ratio = 4                                |     |     |     |        | list of a self-                                                                               |

| All Other CMOS = 50 MHz (B Outputs Off)         |     |     |     |        | Interferer(s)                                                                                 |

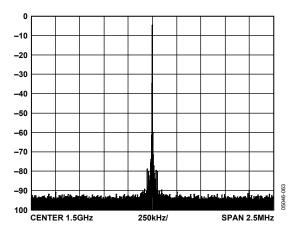

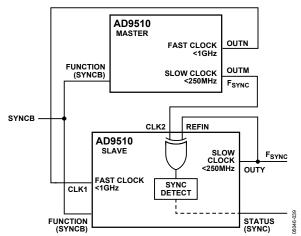

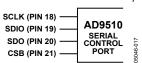

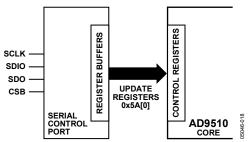

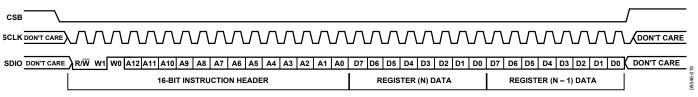

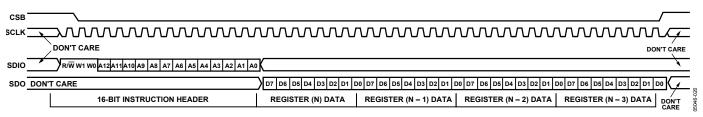

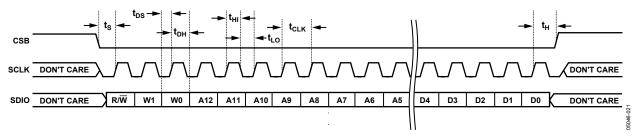

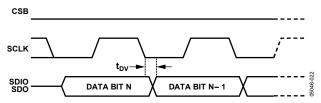

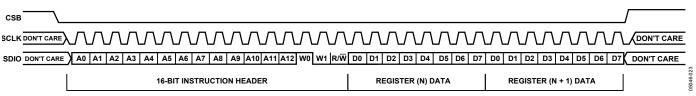

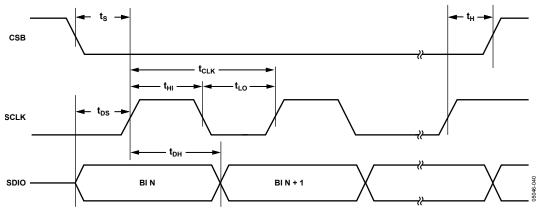

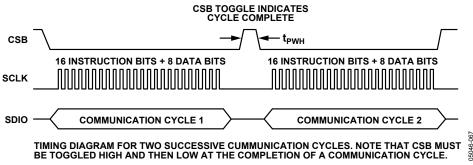

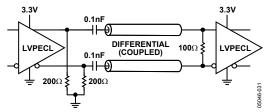

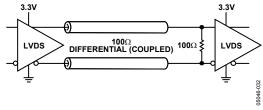

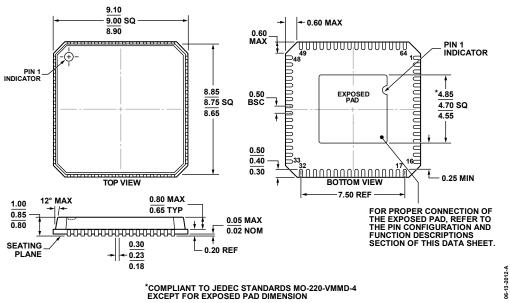

| All LVPECL = 50 MHz<br>CLK1 = 400 MHz           |     | 267 |     | fa     | Interferer(s)                                                                                 |