## HIGH VOLTAGE LED LIGHTING DRIVER WITH THREE LEVEL POWER SEQUENCING

#### May 2015

### **GENERAL DESCRIPTION**

IS31LT3938 LED driver IC is a peak current detection buck converter which operates in constant off time mode. It operates over a very wide input voltage supply range of 10VDC to 450VDC or 110VAC/220VAC.

IS31LT3938 incorporates the special feature of three power sequencing levels by detecting OFF-ON cycles of the main power switch. When the switch is cycled within a 4 second period (typical) the device automatically switches the power level to the next step. As a result, the input and output power of the luminaire may be adjusted depending on the desired amount of illumination and/or power consumption. There are multiple power levels that the engineer may configure, 2 steps or 3 steps, via the external pins DIM1 and DIM2.

IS31LT3938 can also realize LED dimming using an external PWM signal. It can accept a PWM signal from 0% to 100% duty cycle. The LED current may also be adjusted linearly by applying an analog input voltage in the range of 0.5V to 2.5V.

IS31LT3938 adopts a peak current mode control architecture, which eliminates the need for any additional loop compensation while maintaining a good degree of constant output current regulation.

### FEATURES

- User configurable power sequencing levels

- 3% output current accuracy

- Over current, temperature protection and short circuit protection

- High efficiency (typical up to 95%)

- Higher MOS drive capability

- Wide input voltage range: 10VDC~450VDC or 85VAC~ 265VAC

- Linear and PWM dimming

- Very few external components

#### **APPLICATIONS**

- DC/DC or AC/DC constant current LED driver

- Signal and decorative lighting

- Backlight LED driver

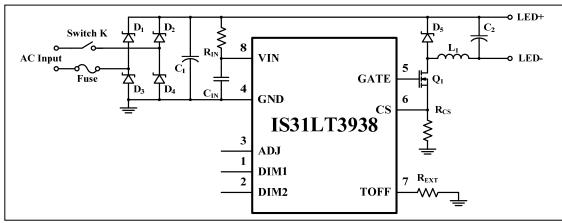

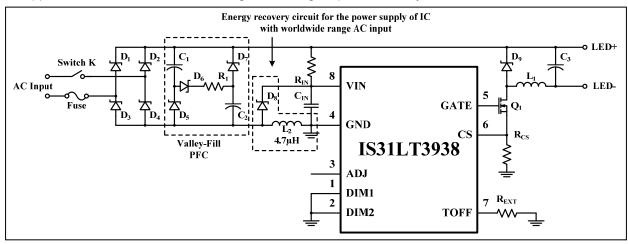

## TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

### **PIN CONFIGURATION**

| Package | Pin Configurations                                          |

|---------|-------------------------------------------------------------|

| SOP-8   | DIM1 1 8 VIN<br>DIM2 2 7 TOFF<br>ADJ 3 6 CS<br>GND 4 5 GATE |

#### PIN DESCRIPTION

| No. | Pin  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DIM1 | These two pins configure the power sequencing levels as follows:<br>DIM1="floating"DIM2="floating", no dimming (100% only);<br>DIM1="floating"DIM2="GND", 100%-30%-100%                                                                                                                                                                                                                                                                                                                                       |

| 2   | DIM2 | DIM1= "GND"DIM2="floating", 100%-50%-100%<br>DIM1="GND"DIM2="GND", 100%-50%-20%-100%                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3   | ADJ  | Linear and PWM dimming input pin.<br>Linear dimming range: 0.5V to 2.5V.<br>If $V_{ADJ} < 0.5V$ , GATE output is off.<br>If $0.5V \le V_{ADJ} \le 2.5V$ , $V_{CS_TH} = V_{ADJ}/10$ .<br>If $V_{ADJ} > 2.5V$ , $V_{CS_TH} = 0.25V$ .<br>When the pin is floating, there is an internal pull up to 4.0V (Typ.) and $V_{CS_TH} = 0.25V$ .<br>Recommended PWM dimming frequency range: 200Hz~1kHz.<br>Note: During the start up (VIN voltage is rising), ADJ must not be connected to low (recommended floating). |

| 4   | GND  | Ground pin. All internal currents return through this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | GATE | This pin connects to the external NMOS's gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6   | CS   | Current detect pin, uses an external resistor to sense the peak inductor current.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | TOFF | This pin sets the off time for the switch by connecting a resistor between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8   | VIN  | 10V~450V supply voltage is connected to this pin via an external resistor. It is internally clamped and must be bypassed using a capacitor to GND.                                                                                                                                                                                                                                                                                                                                                            |

#### ORDERING INFORMATION INDUSTRIAL RANGE: -40°C TO +85°C

| Order Part No.      | Package          | QTY/Reel |

|---------------------|------------------|----------|

| IS31LT3938–GRLS2-TR | SOP-8, Lead-free | 2500     |

Copyright © 2015 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the

product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that: a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| -0.3V ~ 13.0V  |

|----------------|

| -0.3V ~ 6.0V   |

| 10mA           |

| -40°C ~ +125°C |

| -40°C ~ +150°C |

| -65°C ~ +150°C |

| 4kV            |

| 1kV            |

|                |

Note 1: Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Note 2: Beyond the input current range, VIN pin may not clamp at 9V (Typ.).

#### **ELECTRICAL CHARACTERISTICS**

The specifications are at  $T_A=25^{\circ}$ C and  $V_{IN}=20V$  (Note 3),  $R_{IN}=1.5k\Omega$ ,  $C_{IN}=10\mu$ F unless otherwise noted. (Note 4)

| Symbol                 | Parameter                                                             | Conditions                                                        | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>        | Input DC supply voltage range                                         | Supply voltage connected to<br>VIN via an appropriate<br>resistor | 10   |      | 450  | V    |

| $V_{\text{CLAMP}}$     | VIN pin clamp voltage                                                 |                                                                   | 8    | 9    | 10   | V    |

| UVLO                   | Undervoltage lockout                                                  | V <sub>IN</sub> falling                                           |      | 7    |      | V    |

| riangleUVLO            | UVLO hysteresis                                                       |                                                                   |      | 1.6  |      | V    |

| I <sub>IN</sub>        | Quiescent current                                                     | $V_{IN}=V_{CLAMP}$ , Gate floating                                |      | 450  | 700  | μA   |

| I <sub>IN,UV</sub>     | Input current in UVLO                                                 | V <sub>IN</sub> = UVLO                                            |      | 200  | 350  | μA   |

| V <sub>CS_TH</sub>     | Peak current sense threshold                                          |                                                                   | 245  | 250  | 255  | mV   |

| t <sub>BLANK</sub>     | Current sense blanking time                                           | V <sub>CS</sub> =V <sub>CS_TH</sub> +50mV                         |      | 500  |      | ns   |

| t <sub>OFF</sub>       | Off time                                                              | R <sub>EXT</sub> =250kΩ                                           | 9.8  | 10   | 10.2 | μs   |

|                        | PWM input voltage high threshold                                      |                                                                   |      | 2.5  |      | V    |

| V <sub>ADJ</sub>       | PWM input voltage low threshold                                       |                                                                   |      | 0.5  |      | V    |

| (Note 5)               | Linear dimming off output threshold                                   |                                                                   |      | 0.5  |      | V    |

|                        | Linear dimming full output threshold                                  |                                                                   |      | 2.5  |      | V    |

| t <sub>R</sub>         | GATE rises from 0.1×V <sub>CLAMP</sub> to 0.9×V <sub>CLAMP</sub>      | C <sub>GATE</sub> =1nF                                            |      | 60   | 80   | ns   |

| t <sub>f</sub>         | GATE falls from 0.9× V <sub>CLAMP</sub> to 0.1×<br>V <sub>CLAMP</sub> | C <sub>GATE</sub> =1nF                                            |      | 50   | 80   | ns   |

| Τ <sub>Ρ</sub>         | Over temperature protection threshold                                 |                                                                   |      | 150  |      | °C   |

| $\triangle T_{P}$      | Over temperature protection hysteresis                                |                                                                   |      | 20   |      | °C   |

| V <sub>OCP</sub>       | Over current protection CS voltage threshold                          |                                                                   |      | 0.4  |      | V    |

| t <sub>OFF_RESET</sub> | Over current protection t <sub>OFF</sub> delay time                   |                                                                   | 2.5  | 4    | 6    | ms   |

| t <sub>MAX</sub>       | Maximum switch off time for power sequencing                          |                                                                   |      | 4    |      | s    |

Note 3: V<sub>IN</sub> is the input voltage. When V<sub>IN</sub>>9V, input voltage connected to VIN pin should via a appropriate resistor.

Note 4: Production testing of the chip is performed at 25°C. Functional operation of the chip and parameters specified are guaranteed by design, characterization and process control in other temperature

Note 5: When  $V_{ADJ}$ >2.5V,  $I_{OUT}$  is 100% output current. When  $V_{ADJ}$ <0.5V,  $I_{OUT}$  is shutdown. When 0.5V  $\leq V_{ADJ} \leq 2.5V$ ,  $I_{OUT}$  is linear dimming.

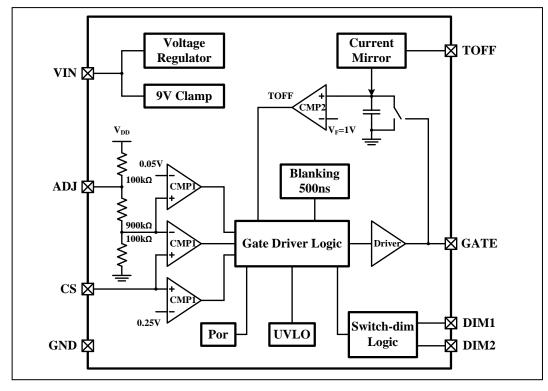

## FUNCTIONAL BLOCK DIAGRAM

### APPLICATION INFORMATION

IS31LT3938 is a peak current control LED driver IC. It does not require any high side current sensing nor the design of any closed loop control, yet provides a very accurate constant LED drive current. IS31LT3938 includes an input allowing either a PWM or an analog dimming signal.

An external resistor connected to the TOFF pin determines the internal oscillator's constant off time. The off time adds to the on time, controlled by the internal switching control logic, to set the oscillation frequency. The inductor current increases when the switch is on. This current also flows through the external current sense resistor R<sub>CS</sub>, and when the voltage across R<sub>CS</sub> reaches the current sense threshold, V<sub>CS TH</sub> or 1/10 of the ADJ input voltage, whichever is lower, the switch turns off. The current through the inductor will continue to flow through the LEDs, but will decrease linearly during the switch off time. After the programmed off-time, the switch will turn on again. A short blanking time of 500ns (typical) is implemented to block the voltage spike encountered across R<sub>CS</sub>, caused by the parasitic capacitance of the switch discharging. After the blanking time the control logic again compares the CS input voltage to the current sense threshold.

Choose the acceptable level of ripple current coefficient, K, and then calculate the value of the current sense resistor:

$$R_{CS} = \frac{V_{CS\_TH}}{(1 + K/2) \times I_{LED}}$$

V<sub>CS TH</sub>: If V<sub>ADJ</sub> < 0.5V, GATE output is off.

If  $0.5V \le V_{ADJ} \le 2.5V$ ,  $V_{CS TH} = V_{ADJ}/10$ .

If

$$V_{ADJ} > 2.5V$$

,  $V_{CS_{TH}} = 0.25V$ .

When ADJ pin is floating, there is an internal pull up to 4.0V (Typ.) and V\_{CS\_TH} = 0.25V.

K: acceptable current ripple coefficient, the recommended value range is 1~1.8.

A constant off-time peak current control scheme can easily operate at duty cycles greater than 0.5 and also gives inherent input voltage rejection making the LED current almost insensitive to input voltage variations.

### INPUT VOLTAGE REGULATION

The VIN pin is internally clamped to 9V (Typ.). When supplying a voltage larger than 9V, an external resistor must be used between the input voltage and the VIN pin. Bypass the VIN pin using a low ESR capacitor to provide a high frequency path to GND. The current required by the device is 0.45mA plus the switching current of the external switch. The switching frequency of the external NMOS affects the amount of current required, as does the NMOS's gate charge

requirement (found on the NMOS data sheet).

$$I_{IN} \approx 0.45 mA + Q_G \times f_S$$

In the above equation,  $f_{\rm S}$  is the switching frequency,  $Q_{\rm G}$  is the external NMOS gate charge (from the NMOS datasheet).

#### **CURRENT DETECTION**

The CS pin input voltage is internally provided to 2 comparators. One of the comparators uses an internal 250mV reference, while the other uses a scaled value of the ADJ pin voltage. The outputs of the comparators are ORed, thus causing the lower of the 2 thresholds to trigger the switch control logic. At the moment the switch control logic changes the gate signal to low, the t<sub>OFF</sub> timer is started. The external switch will remain off for the length of time programmed, and once the tOFF time is expired, the switch control logic again toggles the gate signal, this time from low to high, and the external switch turns on. As the external switch turns on, the parasitic capacitance on the drain of the switch must discharge through the switch channel causing a spike of current which can be guite large, but only lasts for a very short period of time. To prevent this current from causing a false triggering of the current sense comparators, the signal is blocked from the internal comparators for 500ns (Typ.). In some special cases, the 500ns blanking time may not be sufficient to prevent false triggering of the CS threshold logic. Under these circumstances, an additional RC filter may be added to the CS input pin to help filter the voltage spike. Careful layout of the PCB to minimize parasitic capacitance, trace resistance and inductance greatly aid in the elimination of false triggering.

#### OSCILLATOR

IS31LT3938's TOFF pin controls the off time of the internal oscillator. Oscillator off time is determined by the following equation:

$$t_{OFF}(s) = 40 \times 10^{-12} \times R_{EXT}$$

R<sub>EXT</sub>: Resistor connected between TOFF and GND.

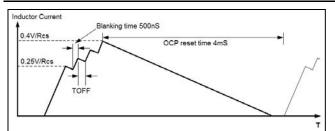

#### SHORT CIRCUIT PROTECTION

As the output is shorted, the inductor peak current will increase cycle-by-cycle because of the blanking time and the low output voltage. When the voltage of the current sense resistor exceeds  $V_{OCP}$  (0.4V), the OCP reset time will be triggered and the gate will keep low for 4ms to prevent the damage of the unlimited peak current increasing. The typical short circuit protection waveform as below:

## SWITCHABLE POWER LEVELS

IS31LT3938 detects the external switch action of the main power switch, and can automatically adjust the level of the output current based on the action of the main power switch.

|                     | L Switch K | L |                     | LED+ |              |

|---------------------|------------|---|---------------------|------|--------------|

| Input<br>AC85V~265V |            | N | IS31LT3938<br>Board | LED- | LED<br>Array |

The action of the external power switch can be divided into two types. The first is "normal switch operation" wherein the switch is toggled from ON to OFF, remaining OFF for longer than 4 seconds (Typ.). The other is "power sequencing action" wherein the switch is toggled from ON to OFF and back ON within 4 seconds (Typ.).

When the device experiences normal switch operation, it merely powers on in the first state, 100%, when the power switch is toggled to ON, and the device turns off when the external power switch is changed to OFF.

Power sequencing output current levels are configured by connecting the DIM1 and DIM2 pins as indicated in the table below:

| DIM1     | DIM2     | Power sequencing levels    |

|----------|----------|----------------------------|

| Floating | Floating | No Power Sequencing        |

| Floating | GND      | 2 levels:100%-30%-100%     |

| GND      | Floating | 2 levels:100%-50%-100%     |

| GND      | GND      | 3 levels:100%-50%-20%-100% |

When operating the power switch normally the device will always power up at 100% output current.

The operation of the power switch and the configuration of the DIM1 and DIM2 pins control the power sequencing process as follows:

- 1. When DIM1 and DIM2 pins are both floating, there are no switchable power levels, and the output current is 100% of the programmed value when the power is on.

- 2. When DIM1 is floating and DIM2 is GND, the output current is:

- a) 100% at power on.

- b) The first power sequencing action causes the current to change to 30%.

- c) A second power sequencing action causes the current to return to 100%.

- d) A third power sequencing action has the same effect as the first power sequencing action.

- e) Subsequent power sequencing actions causes the cycle to continue.

- 3. When DIM1 is GND and DIM2 is floating, the power sequence is as described in (2) above, except that the current sequence is 100%-50%-100%.

- When both DIM1 and DIM2 are connected to GND, the power sequence is as described in (2) above, except that the current sequence is 100%-50%-20%-100%.

If the switch is operated normally, that is, switched on once after being in the OFF position for a long time, or if both the DIM1 and DIM2 pins are floating, then the output current always starts up at the initial value of 100%.

Note: Because the main power switch is used to initiate the power sequencing function, the device must have a large enough external capacitor on VIN to maintain device operation for 4 seconds.

#### LINEAR DIMMING

An external voltage, 0.5V to 2.5V, connected to the ADJ pin can adjust the LED current. Two possible situations where this might be used are:

If it is not possible to change the value of  $R_{CS}$  to obtain the desired value of LED current, an external voltage reference can be connected to the ADJ pin to adjust the voltage sense level across  $R_{CS}$ , equivalent to changing the value of  $R_{CS}$ .

Connecting a resistor between the VIN and ADJ pin, then connecting a thermistor from the ADJ pin to GND can adjust the LED current based on temperature, thus realizing the temperature compensation feature.

### **PWM DIMMING**

PWM dimming may be realized by applying a low frequency PWM waveform to the ADJ pin. When the PWM signal is low, less than 0.5V, the IS31LT3938 remains off; When the PWM signal is high, greater than 2.5V, the driver is enabled and operates normally. The PWM signal does not shut down other circuit blocks of the device, thus the response to the PWM signal is relatively fast and primarily determined by the rise and fall time of the inductor current.

To disable PWM dimming, leave the ADJ pin floating.

#### APPLICATION EXAMPLE

DC Input Voltage: V<sub>in</sub> =220VAC

Output:  $V_0$ = 40V (12,1W LEDs in series,  $V_F$ =3.3V) I<sub>LED</sub>=0.35A

#### 1. V<sub>IN</sub> Power Supply Circuit

V<sub>IN</sub> supply current is given by:

$$I_{IN} \approx 0.45 mA + Q_G \times f_s$$

Assuming I<sub>IN</sub>=1mA,

Then,  $R_{IN} = \frac{V_{in} - V_{IN}}{I_{IN}} \approx \frac{220 - 9}{1} = 211 k\Omega$

Choose two  $430k\Omega/0.5W$  in parallel for the resistor lifetime consideration.

Choose C<sub>IN</sub>: 10µF/25V ceramic capacitor.

#### 2. Constant Off Time (toff)

Off time is given by:

$$t_{OFF}(s) = 40 \times 10^{-12} \times R_{FXT}$$

To decide the off time, assume the desired switching frequency is 50kHz (period time t= $20\mu$ s), and the duty

cycle:

$$D = \frac{Vo}{Vin} = \frac{40}{220} = 18.18\%$$

The duty cycle is decided by the ratio of the output voltage and input voltage, then  $t_{\mbox{\scriptsize OFF}}$ :

$$t_{OFF} = t \times (1 - D) = 20 \mu s \times (1 - 18.18\%) = 16.36 \mu s$$

So  $R_{EXT}$  =409k $\Omega$ , choose the closest resistor,  $R_{EXT}$ =390k $\Omega$ , the actual  $t_{OFF}$ =15.6µs (Because the actual  $t_{OFF}$  is smaller than theoretical  $t_{OFF}$ , the operating frequency will be little higher than 50kHz).

#### 3. Current Sense Resistor (R<sub>cs</sub>)

The ripple current is:

$$I_{RIPPLE} = K \times I_{LED}$$

K is the ripple current coefficient, the recommended value range is 1~1.8.

The peak current:

$$I_{PEAK} = I_{LED} + \frac{I_{RIPPLE}}{2} = \left(1 + \frac{K}{2}\right) \times I_{LED}$$

Because of ADJ pin floating,  $V_{\text{CS}_{\text{TH}}}\text{=}0.25\text{V}.$  Assuming a typical value for K of 1.8.

The current sense resistor is given by:

$$R_{CS} = \frac{V_{CS_{TH}}}{I_{PEAK}} = \frac{V_{CS_{TH}}}{\left(1 + \frac{K}{2}\right)}I_{LED} = \frac{0.25}{\left(1 + \frac{1.8}{2}\right) \times 0.35} = 0.376\Omega$$

Choose  $R_{CS}$ =0.38 $\Omega$  and 1% precision.

#### 4. Inductor (L1)

The inductance of inductor L1 is dependent on the LED current, in this case 350mA. We have already chosen  $t_{OFF}$ =15.6µs, thus:

$$L = \frac{V_{O} \times t_{OFF}}{I_{Ripple}} = \frac{V_{O} \times t_{OFF}}{K \times I_{LED}} = \frac{40 \times 15.6 \times 10^{-6}}{1.8 \times 0.35} \approx 1 mH$$

Where I<sub>RIPPLE</sub> is the design target for ripple current.

Note: The saturation of inductor must be higher than the peak current.

#### 5. Freewheeling Diode (D5) and NMOS (Q1)

Choose Q1 to have a voltage rating at least as large as the peak voltage of the maximum input voltage with approximately 50% margin.

$$V_{NMOS} = 150\% \times \sqrt{2} \times V_{in}$$

The current through the NMOS is based on the peak LED current, choose FET current rating with 50% margin.

$$I_{NMOS} = 150\% \times I_{PEAK}$$

Thus, choose 600V, 2A, NMOS, such as: 2N60

The diode ratings are equal to that of the NMOS, Q1.

Note: The diode must be a superfast recovery diode and the Reverse Recovery Time ( $t_{RR}$ ) should be less than 50ns. Thus, choose 600V, 1A, superfast recovery diode, such as: ES1J, SF18.

## APPENDIX

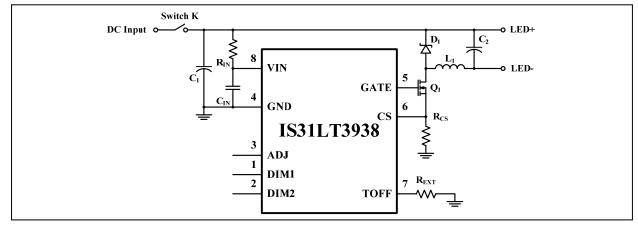

Typical Application Circuit of DC Voltage Input

Typical Application Circuit of Worldwide Range AC Voltage Input with Valley-Fill PFC

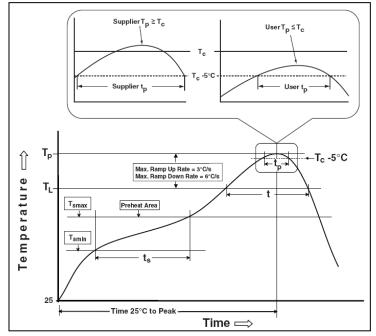

## **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                    | Pb-Free Assembly                 |  |  |

|----------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Preheat & Soak<br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |  |  |

| Average ramp-up rate (Tsmax to Tp)                                                                 | 3°C/second max.                  |  |  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                               | 217°C<br>60-150 seconds          |  |  |

| Peak package body temperature (Tp)*                                                                | Max 260°C                        |  |  |

| Time (tp)** within 5°C of the specified<br>classification temperature (Tc)                         | Max 30 seconds                   |  |  |

| Average ramp-down rate (Tp to Tsmax)                                                               | 6°C/second max.                  |  |  |

| Time 25°C to peak temperature                                                                      | 8 minutes max.                   |  |  |

Figure 2 Classification Profile

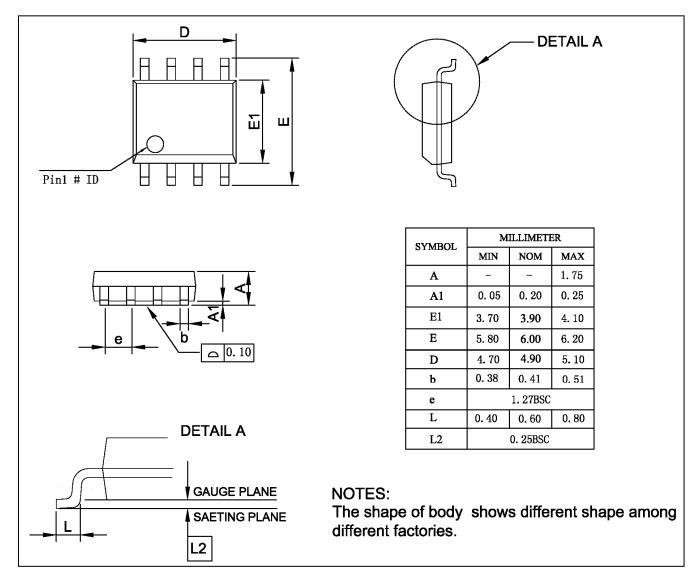

#### SOP-8

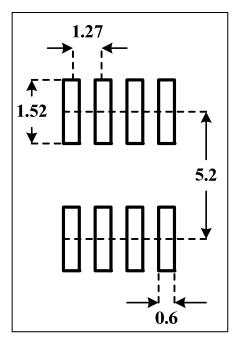

## **RECOMMENDED LAND PATTERN**

#### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

## **REVISION HISTORY**

| Revision | Detail Information                                                                                                                                                                                                     |            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| А        | Initial release                                                                                                                                                                                                        | 2012.07.05 |

| В        | <ol> <li>Add the description of short circuit protection.</li> <li>Add a note to the ADJ pin (Note: During the start up (VIN voltage is rising), ADJ must not be connected to low (recommended floating).).</li> </ol> | 2013.01.05 |

| С        | 1. Separate $V_{ADJ}$ (Linear dimming input voltage range) into two parameters 2. Add land pattern                                                                                                                     | 2015.05.20 |

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331