# Intel® Ethernet Network Connection I347-AT4 Datasheet

May 2012

Revision 2.2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

This document contains information on products in the design phase of development.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{\textcircled{C}}$  2012, Intel Corporation. All Rights Reserved.

*Note:* This page intentionally left blank.

# **Revision History**

| Rev              | Date                                                 | ate Comments                                                                                                                                   |  |  |  |

|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2.2              | May 2012                                             | dded Thermal Design Recommendations.                                                                                                           |  |  |  |

| 2.1              | March 2012                                           | Added power consumption table to section 5.2.                                                                                                  |  |  |  |

| 2.0 <sup>1</sup> | December 2011                                        | December 2011 Changed 1.8V power rail to 1.9V.<br>Updated the pin interface section (added RCLK1, RCLK2, and SCLK).<br>Initial public release. |  |  |  |

| 0.75             | April 2011                                           | Added clocking source descriptions (Recovered Clock and Reference Clock Select).                                                               |  |  |  |

| 0.7              | February 2011                                        | Added I347-AT4 SGMII-to-copper dual-port mode details.                                                                                         |  |  |  |

| 0.6              | November 2010                                        | Major revision (all sections).                                                                                                                 |  |  |  |

| 0.5              | September 2010 Initial Release (Intel Confidential). |                                                                                                                                                |  |  |  |

1. No releases between revision 0.75 and 2.0.

*Note:* This page intentionally left blank.

# Contents

| 1.0 | Introdu    | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                         |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

|     | 1.1        | I347-AT4 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                         |  |  |  |

| 2.0 | Pin Int    | rface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                         |  |  |  |

| 2.0 | 2.1        | Pin Assignment       2         2.1.1       Signal Type Definitions       2         2.1.2       Media Dependent Interface       2         2.1.3       SGMI       2         2.1.4       Reserved Pins       2         2.1.5       Management/Control       2         2.1.6       LED       2         2.1.7       JTAG       2         2.1.8       Master Clock/Reset       2         2.1.9       Test       2         2.1.10       References       10         2.1.11       Power and Ground       10 | 4<br>5<br>6<br>7<br>8<br>8<br>9<br>9<br>0 |  |  |  |

|     | 2.2        | 2.1.12       Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1<br>1<br>1<br>2                          |  |  |  |

| 3.0 | Device     | Functionality14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                         |  |  |  |

|     | 3.1<br>3.2 | I347-AT4 Operation and Major Interfaces16Copper Media Interface163.2.1Transmit Side Network Interface173.2.2Encoder173.2.3Receive Side Network Interface183.2.4Decoder183.2.5Electrical Interface203.2.6SGMII Speed and Link273.2.7SGMII TRR Blocking27                                                                                                                                                                                                                                             | 6<br>7<br>8<br>9<br>0                     |  |  |  |

|     | 3.3        | Loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1<br>1<br>2                               |  |  |  |

|     | 3.4        | Synchronizing FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |  |  |  |

|     | 3.5        | Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |  |  |  |

|     | 3.6        | Power Management263.6.1Manual Power Down263.6.2MAC Interface Power Down263.6.3Copper Detect Mode273.6.4Low Power Modes283.6.5Low Power Operating Modes28                                                                                                                                                                                                                                                                                                                                            | 6<br>6<br>7<br>8                          |  |  |  |

|     |            | 3.6.6 SGMII Effect on Low Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |  |  |  |

|     | 3.7        | Auto-Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |  |  |  |

|      | 3.7.1 10/100/1000BASE-T Auto-Negotiation                |    |

|------|---------------------------------------------------------|----|

| 3.8  | Downshift Feature                                       |    |

| 3.9  | Fast 1000BASE-T Link Down Indication                    | 31 |

| 3.10 | Cable Tester                                            | 32 |

|      | 3.10.1 Maximum Peak                                     | 33 |

|      | 3.10.2 First Peak                                       |    |

|      | 3.10.3 Offset                                           | 35 |

|      | 3.10.4 Sample Point                                     | 35 |

|      | 3.10.5 Pulse Amplitude and Pulse Width                  |    |

|      | 3.10.6 Drop Link                                        |    |

|      | 3.10.7 Cable Test with Link Up                          |    |

| 3.11 | Data Terminal Equipment (DTE) Detect                    |    |

| 3.12 | CRC Error Counter and Frame Counter                     |    |

|      | 3.12.1 Enabling The CRC Error Counter and Frame Counter |    |

| 3.13 | Packet Generator                                        |    |

| 3.14 | RX ER Byte Capture                                      |    |

| 3.15 | MDI/MDIX Crossover                                      |    |

| 3.16 | Unidirectional Transmit                                 |    |

| 3.17 | Polarity Correction                                     |    |

| 3.18 | FLP Exchange Complete with No Link                      |    |

| 0.10 | 3.18.1 Behavior in Various Low Power States             |    |

|      | 3.18.2 Serial LED                                       |    |

| 3.19 | IEEE 1149.1 and 1149.6 Controller                       |    |

| 0.10 | 3.19.1 BYPASS Instruction                               |    |

|      | 3.19.2 SAMPLE/PRELOAD Instruction                       |    |

|      | 3.19.3 EXTEST Instruction                               |    |

|      | 3.19.4 The CLAMP Instruction                            |    |

|      | 3.19.5 The HIGH-Z Instruction                           |    |

|      | 3.19.6 ID CODE Instruction                              |    |

|      | 3.19.7 EXTEST_PULSE Instruction                         |    |

|      | 3.19.8 EXTEST_TRAIN Instruction                         |    |

|      | 3.19.9 AC-JTAG Fault Detection                          |    |

| 3.20 | Interrupt                                               |    |

| 3.21 | Configuring The I347-AT4                                |    |

| 0.21 | 3.21.1 Hardware Configuration                           |    |

|      | 3.21.2 Configuration Mapping                            |    |

|      | 3.21.3 Software Configuration - Management Interface    |    |

| 3.22 | Reference Clock                                         |    |

| 3.23 | Temperature Sensor                                      |    |

| 3.24 | Power Supplies                                          |    |

| 0.21 | 3.24.1 AVDDH                                            |    |

|      | 3.24.2 VDDC                                             |    |

|      | 3.24.3 DVDD                                             |    |

|      | 3.24.4 VDDOL                                            |    |

|      | 3.24.5 VDDOR                                            |    |

|      | 3.24.6 VDDOM                                            |    |

|      | 3.24.7 Power Supply Sequencing                          |    |

| 3.25 | Clocking Support                                        |    |

| 0.20 | 3.25.1 Recovered Clock                                  |    |

|      | 3.25.2 Reference Clock Select                           |    |

|      |                                                         |    |

4.0

| Progra |         | Visible State                                                   |      |

|--------|---------|-----------------------------------------------------------------|------|

| 4.1    | Registe | er Map                                                          |      |

|        | 4.1.1   | Copper Control Register - Page 0, Register 0                    |      |

|        | 4.1.2   | Copper Status Register - Page 0, Register 1                     |      |

|        | 4.1.3   | PHY Identifier 1 - Page 0, Register 2                           |      |

|        | 4.1.4   | PHY Identifier 2 - Page 0, Register 3                           |      |

|        | 4.1.5   | Copper Auto-Negotiation                                         |      |

|        |         | Advertisement Register - Page 0, Register 4                     |      |

|        | 4.1.6   | Copper Link Partner Ability                                     |      |

|        |         | Register - Base Page - Page 0, Register 5                       |      |

|        | 4.1.7   | Copper Auto-Negotiation Expansion Register - Page 0, Register 6 |      |

|        | 4.1.8   | Copper Next Page Transmit Register - Page 0, Register 7         |      |

|        | 4.1.9   | Copper Link Partner Next Page Register - Page 0, Register 8     |      |

|        | 4.1.10  | 1000BASE-T Control Register - Page 0, Register 9                |      |

|        | 4.1.11  | 1000BASE-T Status Register - Page 0, Register 10                |      |

|        |         | Extended Status Register - Page 0, Register 15                  |      |

|        |         | Copper Specific Control Register 1 - Page 0, Register 16        |      |

|        | 4.1.14  |                                                                 |      |

|        |         | Copper Specific Interrupt Enable Register - Page 0, Register 18 |      |

|        |         | Copper Interrupt Status Register - Page 0, Register 19          |      |

|        | 4.1.17  |                                                                 |      |

|        | 4.1.17  |                                                                 | •••• |

|        | 4.1.10  | Error Counter Register - Page 0, Register 21                    |      |

|        | 1 1 10  | Page Address Register - Any Page, Register 22                   |      |

|        |         | Global Interrupt Status - Page 0, Register 23                   |      |

|        |         | Copper Specific Control Register 3 - Page 0, Register 26        |      |

|        |         |                                                                 |      |

|        |         | PHY Identifier Register - Page 1, Register                      |      |

|        |         | PHY Identifier Register - Page 1, Register 3                    |      |

|        |         | Extended Status Register - Page 1, Register 15                  |      |

|        |         | PRBS Control - Page 1, Register 23                              |      |

|        |         | PRBS Error Counter LSB - Page 1, Register 24                    |      |

|        | 4.1.27  |                                                                 |      |

|        | 4.1.28  |                                                                 |      |

|        | 4.1.29  |                                                                 |      |

|        | 4.1.30  |                                                                 |      |

|        | 4.1.31  |                                                                 |      |

|        | 4.1.32  |                                                                 |      |

|        | 4.1.33  | LED[3:0] Function Control Register - Page 3, Register 16        |      |

|        | 4.1.34  | LED[3:0] Polarity Control Register - Page 3, Register 17        |      |

|        | 4.1.35  | LED Timer Control Register - Page 3, Register 18                |      |

|        | 4.1.36  | LED[5:4] Function Control and Polarity - Page 3, Register 19    |      |

|        | 4.1.37  | SGMII Link Partner Ability Register - SGMII                     |      |

|        |         | (Media mode) Mode (Register 16_4.0 = 1b) - Page 4, Register 5   |      |

|        | 4.1.38  |                                                                 |      |

|        | 4.1.39  |                                                                 |      |

|        | 4.1.40  |                                                                 |      |

|        | 4.1.41  |                                                                 |      |

|        | 4.1.42  |                                                                 |      |

|        | 4.1.43  | 1000BASE-T Pair Swap and Polarity - Page 5, Register 21         |      |

|        | 4.1.44  |                                                                 |      |

|        |              | able Tester Sample Point Distance - Page 5, Register 24                                    |       |

|--------|--------------|--------------------------------------------------------------------------------------------|-------|

|        |              | Cable Tester Cross Pair Positive Threshold - Page 5, Register 25<br>Cable Tester Same Pair | 95    |

|        | -            | pedance Positive Threshold 0 and 1 - Page 5, Register 26                                   | 95    |

|        |              | Cable Tester Same Pair                                                                     |       |

|        |              | mpedance Positive Threshold 2 and 3 - Page 5, Register 27                                  | 96    |

|        | 4.1.49 C     | Cable Tester Same Pair Impedance Positive                                                  |       |

|        |              | hreshold 4 and Transmit Pulse Control - Page 5, Register 28                                |       |

|        |              | Packet Generation - Page 6, Register 16                                                    |       |

|        |              | RC Counters - Page 6, Register 17                                                          |       |

|        |              | Checker Control - Page 6, Register 18                                                      |       |

|        |              | General Control Register - Page 6, Register 20                                             |       |

|        |              | ate Collision Counters 1 & 2 - Page 6, Register 23                                         |       |

|        |              | ate Collision Counters 3 & 4 - Page 6, Register 24                                         |       |

|        |              | ate Collision Window Adjust/Link Disconnect - Page 6, Register 25                          |       |

|        |              | lisc Test - Page 6, Register 26                                                            |       |

| Electr | ical and Tim | ning Specifications                                                                        | . 102 |

| 5.1    | Recomme      | ended Operating Conditions                                                                 | . 102 |

| 5.2    |              | Consumption                                                                                |       |

| 5.3    |              | ating Conditions                                                                           |       |

|        | 5.3.1 D      | Digital Pins                                                                               | . 104 |

|        | 5.3.2 IE     | EEE DC Transceiver Parameters                                                              | . 105 |

|        | 5.3.3 S      | GMII Interface                                                                             | . 105 |

| 5.4    |              | ical Specifications                                                                        |       |

|        | 5.4.1 R      | Reset Timing                                                                               | .110  |

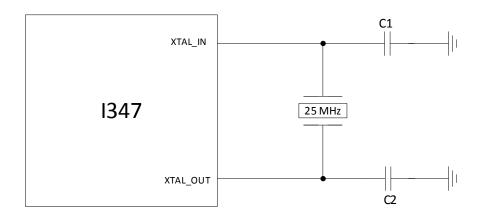

|        |              | TAL_IN/XTAL_OUT (CLK_SEL[1:0] = 10b or 11b) Timing                                         |       |

|        |              | ED to CONFIG Timing                                                                        |       |

|        |              | erial LED Timing                                                                           |       |

| 5.5    |              | erface Timing                                                                              |       |

|        |              | GMII Output AC Characteristics                                                             |       |

|        |              | GMII Input AC Characteristics                                                              |       |

| 5.6    |              | IO Timing                                                                                  |       |

| 5.7    |              | ning                                                                                       |       |

| 5.8    |              | Transceiver Parameters                                                                     |       |

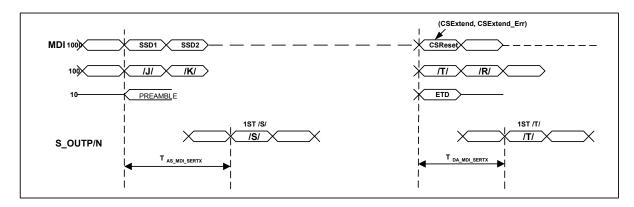

| 5.9    |              | Timing<br>0/100/1000BASE-T to SGMII Latency Timing                                         |       |

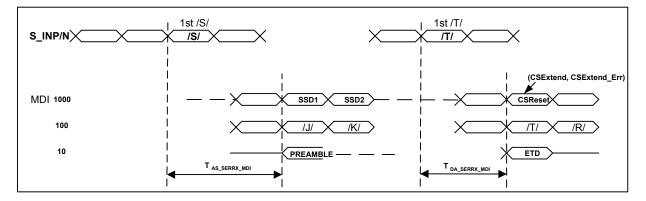

|        |              | GMII to 10/100/1000BASE-T Latency Timing                                                   |       |

| 5.10   |              | pecifications                                                                              |       |

|        |              |                                                                                            |       |

| Packa  | age          |                                                                                            | . 122 |

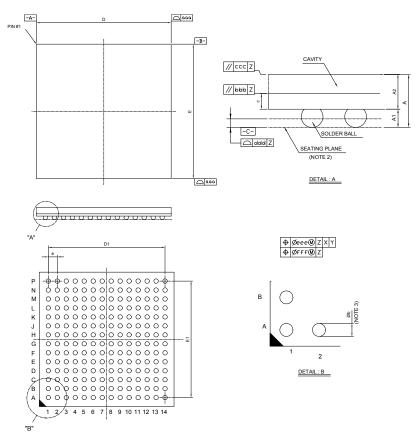

| 6.1    | 196-Pin T    | FBGA Package                                                                               | . 123 |

| Thern  | nal Design R | Recommendations                                                                            | . 125 |

| 7.1    | Introducti   | on                                                                                         | . 125 |

| 7.2    | Intended     | Audience                                                                                   | . 125 |

| 7.3    | Thermal (    | Considerations                                                                             | . 125 |

| 7.4    | Thermal N    | Management Importance                                                                      | . 126 |

| 7.5    |              | bgy and Definitions                                                                        |       |

| 7.6    |              | Thermal/Mechanical Specifications and Limits                                               |       |

|        | 7.6.1 T      | hermal Limits - Max Junction/Case                                                          | . 127 |

|      | 7.6.2                 | Thermal Specifications                              | 128 |  |  |  |  |

|------|-----------------------|-----------------------------------------------------|-----|--|--|--|--|

|      | 7.6.3                 | Mechanical Limits - Maximum Static Normal Load      | 128 |  |  |  |  |

|      | 7.6.4                 | Mechanical Specifications                           |     |  |  |  |  |

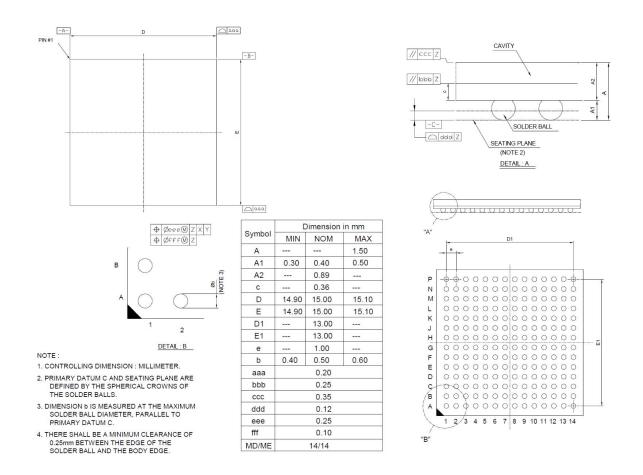

| 7.7  | Therma                | al Solutions                                        |     |  |  |  |  |

|      | 7.7.1                 | Extruded Heat Sinks                                 |     |  |  |  |  |

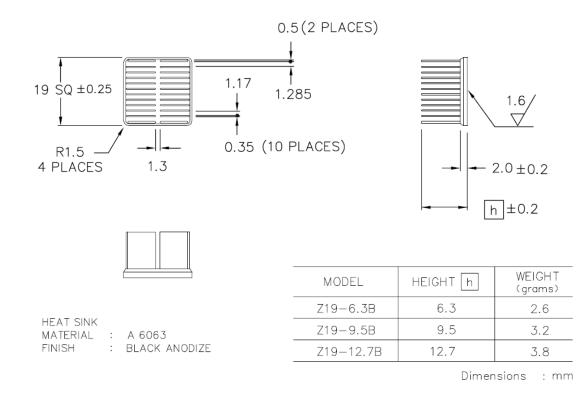

|      | 7.7.2                 | Thermal Interface Materials for Heat Sink Solutions |     |  |  |  |  |

|      | 7.7.3                 | Attaching the Extruded Heat Sink                    | 133 |  |  |  |  |

| 7.8  | Reliabil              | ity                                                 |     |  |  |  |  |

| 7.9  | JEDEC                 | Simulation Results                                  |     |  |  |  |  |

|      | 7.9.1                 | Designing for Thermal Performance                   |     |  |  |  |  |

|      | 7.9.2                 | Simulation Setup                                    |     |  |  |  |  |

|      | 7.9.3                 | Simulation Results                                  |     |  |  |  |  |

| 7.10 | Compo                 | nent Measurement Methodology                        |     |  |  |  |  |

|      | 7.10.1                | Case Temperature Measurements                       |     |  |  |  |  |

| 7.11 | Conclu                | sion                                                |     |  |  |  |  |

| 7.12 |                       | leat Sink and Attach Suppliers138                   |     |  |  |  |  |

| 7.13 | PCB Layout Guidelines |                                                     |     |  |  |  |  |

|      |                       |                                                     |     |  |  |  |  |

### **1.0** Introduction

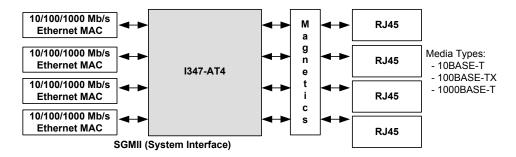

The Intel<sup>®</sup> Ethernet Network Connection I347-AT4 (I347-AT4) quad, single-chip device contains four independent Gigabit Ethernet (GbE) transceivers on a single monolithic Integrated Circuit (IC) that supports SGMII on the MAC interface in an SGMII-to-copper application. Each transceiver performs all the Physical Layer (PHY) functions for 100BASE-TX and 1000BASE-T full- or half-duplex Ethernet on a CAT 5 twisted pair cable, and 10BASE-T full- or half-duplex Ethernet on a CAT 3, 4, and 5 cable.

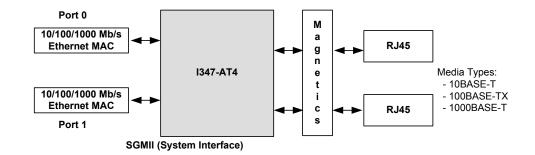

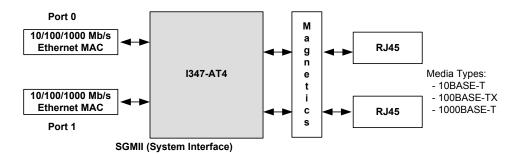

*Note:* The I347-AT4 can also operate in dual-port mode. When set by the MAC, the I347-AT4 uses two independent GbE transceivers (Port 0 and Port 1) in an SGMII-to-copper application.

The I347-AT4 integrates MDI interface termination resistors and capacitors into the PHY. This resistor integration simplifies board layout and lowers board cost by reducing the number of external components. The new calibrated resistor scheme achieves and exceeds the accuracy requirements of the IEEE 802.3 return loss specifications.

The I347-AT4 consumes less than 500 mW per port; thereby, reducing overall system cost by eliminating heat-sink and reducing air-flow requirements.

The I347-AT4 is fully compliant with the IEEE 802.3 standard. It includes the PMD, PMA, and PCS sublayers and performs:

- PAM5, 8B/10B, 4B/5B, MLT-3, NRZI, and Manchester encoding/decoding

- Digital clock/data recovery

- Stream cipher scrambling/descrambling

- Digital adaptive equalization for the receiver data path as well as digital filtering for pulse-shaping for the line transmitter

- Auto-negotiation and management functions.

The I347-AT4 also supports auto-MDI/MDIX at all three speeds to enable easier installation and reduce installation costs.

The I347-AT4 uses advanced mixed-signal processing to perform equalization, echo and crosstalk cancellation, data recovery, and error correction at a gigabit-per-second data rate. The I347-AT4 dissipates very low power while achieving robust performance in noisy environments.

In addition, the I347-AT4 supports a cable tester feature that enables fault detection and advanced cable performance monitoring.

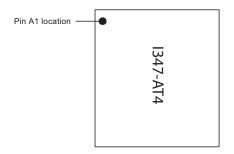

The I347-AT4 is available in a 15 mm x 15 mm, 196-pin TFBGA package.

### 1.1 I347-AT4 Features

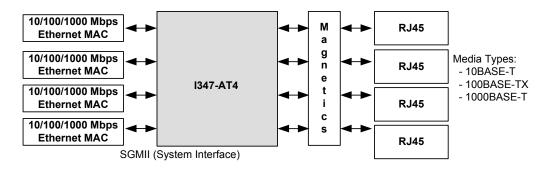

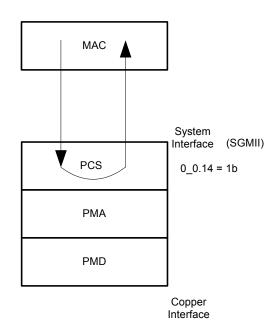

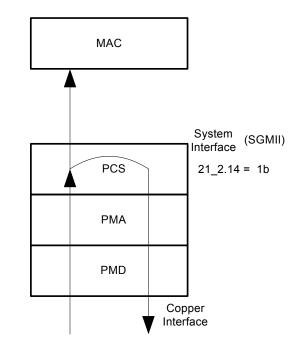

- Two or four ports SGMII-to-copper (see Figure 1 and Figure 2)

- Integrated MDI interface termination resistors and capacitors

- Low power consumption (< 500 mW per port)

- Integrated cable diagnostic feature

- Downshift mode for two-pair cable installations

- Supports up to four LEDs per port programmable to indicate link, speed, duplex, and activity functions

- Supports Advance Power Management (APM) modes for significant power savings

- Automatic MDI/MDIX crossover for all three speeds of operation (10/100/ 1000BASE-T)

- Automatic polarity correction

- 25 MHz clock input option

- Loopback mode for diagnostics

- Supports IEEE 1149.1 JTAG and 1149.6 AC JTAG

- Available in RoHS 6 and Halogen Free packages

- Manufactured in a 15 x 15 mm 196-pin TFBGA package

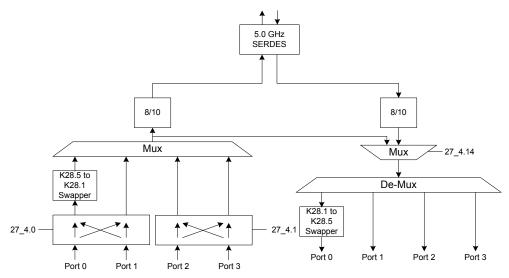

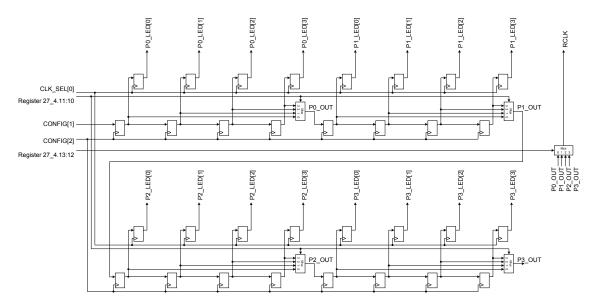

#### Figure 1. SGMII (System) to Copper – Dual Port Mode

Figure 2. SGMII (System) to Copper – Quad Port Mode

# 2.0 Pin Interface

## 2.1 Pin Assignment

The I347-AT4 is manufactured in a 15 x 15 mm 196-pin TFBGA package.

### 2.1.1 Signal Type Definitions

| Signal Type | Definition            |  |  |  |

|-------------|-----------------------|--|--|--|

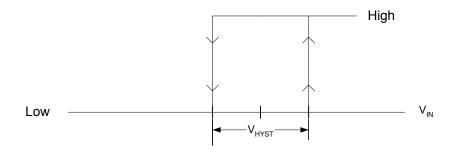

| Н           | input with hysteresis |  |  |  |

| I/O         | nput/output           |  |  |  |

| I           | Input only            |  |  |  |

| 0           | Output only           |  |  |  |

| PU          | Internal pull-up      |  |  |  |

| PD          | Internal pull-down    |  |  |  |

| D           | Open-drain output     |  |  |  |

| Z           | Tri-state output      |  |  |  |

| mA          | DC sink capability    |  |  |  |

## 2.1.2 Media Dependent Interface

#### Table 1. Media Dependent Interface Port 0

| Pin #    | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N3<br>P3 | P0_MDIP[0]<br>P0_MDIN[0] | I/O         | Media Dependent Interface[0].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[0] correspond to BI_DA±.<br>In MDIX configuration, MDIP/N[0] correspond to BI_DB±.<br>In 100BASE-TX and 10BASE-T modes in MDI configuration, MDIP/N[0] are used<br>for the transmit pair. In MDIX configuration, MDIP/N[0] are used for the receive<br>pair.<br>Unused MDI pins must be left floating.<br>The I347-AT4 contains an internal 100 $\Omega$ resistor between the MDIP/N[0] pins. |

| N4<br>P4 | P0_MDIP[1]<br>P0_MDIN[1] | I/O         | Media Dependent Interface[1].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[1] correspond to BI_DB±. In<br>MDIX configuration, MDIP/N[1] correspond to BI_DA±.<br>In 100BASE-TX and 10BASE-T modes in MDI configuration, MDIP/N[1] are used<br>for the receive pair. In MDIX configuration, MDIP/N[1] are used for the transmit<br>pair.<br>Unused MDI pins must be left floating.<br>The I347-AT4 contains an internal 100 $\Omega$ resistor between the MDIP/N[1] pins. |

| P5<br>N5 | P0_MDIP[2]<br>P0_MDIN[2] | I/O         | Media Dependent Interface[2].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[2] correspond to BI_DC±. In<br>MDIX configuration, MDIP/N[2] correspond to BI_DD±.<br>In 100BASE-TX and 10BASE-T modes, MDIP/N[2] are not used.<br>Unused MDI pins must be left floating.<br>The I347-AT4 contains an internal 100 $\Omega$ resistor between the MDIP/N[2] pins.                                                                                                              |

| M5<br>M6 | P0_MDIP[3]<br>P0_MDIN[3] | I/O         | Media Dependent Interface[3].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[3] correspond to BI_DD±.<br>In MDIX configuration, MDIP/N[3] correspond to BI_DC±.<br>In 100BASE-TX and 10BASE-T modes, MDIP/N[3] are not used.<br>Unused MDI pins must be left floating.<br>The I347-AT4 contains an internal 100 $\Omega$ resistor between the MDIP/N[3] pins.                                                                                                              |

#### Table 2. Media Dependent Interface Port 1

| Pin # | Pin Name   | Pin<br>Type | Description                              |

|-------|------------|-------------|------------------------------------------|

| M8    | P1_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 1. |

| M7    | P1_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| N8    | P1_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 1. |

| P8    | P1_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| N7    | P1_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 1. |

| P7    | P1_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| N6    | P1_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 1. |

| P6    | P1_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

### Table 3. Media Dependent Interface Port 2

| Pin # | Pin Name   | Pin<br>Type | Description                              |

|-------|------------|-------------|------------------------------------------|

| P9    | P2_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 2. |

| N9    | P2_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| P10   | P2_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 2. |

| N10   | P2_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| P11   | P2_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 2. |

| N11   | P2_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| M9    | P2_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 2. |

| M10   | P2_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

#### Table 4. Media Dependent Interface Port 3

| Pin # | Pin Name   | Pin<br>Type | Description                              |

|-------|------------|-------------|------------------------------------------|

| N14   | P3_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 3. |

| P14   | P3_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| M12   | P3_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 3. |

| M11   | P3_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| N13   | P3_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 3. |

| P13   | P3_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| N12   | P3_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 3. |

| P12   | P3_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

### 2.1.3 SGMI

#### Table 5.SGMII Interface Port 0

| Pin #    | Pin Name               | Pin<br>Type | Description                                                                                                               |

|----------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

| B1<br>A1 | P0_S_INP<br>P0_S_INN   | I           | SGMII Transmit Data. 1.25 GBaud input - Positive and Negative.                                                            |

| B2<br>A2 | P0_S_OUTP<br>P0_S_OUTN | 0           | SGMII Receive Data. 1.25 GBaud output - Positive and Negative.<br>Output amplitude can be adjusted via register 26_1.2:0. |

#### Table 6.SGMII Interface Port 1

| Pin #    | Pin Name               | Pin<br>Type | Description                                                                                                               |  |

|----------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|--|

| A4<br>B4 | P1_S_INP<br>P1_S_INN   | Ι           | SGMII Transmit Data. 1.25 GBaud input - Positive and Negative.                                                            |  |

| A3<br>B3 | P1_S_OUTP<br>P1_S_OUTN | 0           | SGMII Receive Data. 1.25 GBaud output - Positive and Negative.<br>Output amplitude can be adjusted via register 26_1.2:0. |  |

| Table 7. | SCMTT | Interface | Port 2 |

|----------|-------|-----------|--------|

| Table 7. | SGMIT | Interface | FUIL Z |

| Pin #      | Pin Name               | Pin<br>Type | Description                                                                                                               |  |

|------------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|--|

| A11<br>B11 | P2_S_INP<br>P2_S_INN   | I           | SGMII Transmit Data. 1.25 GBaud input - Positive and Negative.                                                            |  |

| A12<br>B12 | P2_S_OUTP<br>P2_S_OUTN | 0           | SGMII Receive Data. 1.25 GBaud output - Positive and Negative.<br>Output amplitude can be adjusted via register 26_1.2:0. |  |

#### Table 8.SGMII Interface Port 3

| Pin #      | Pin Name               | Pin<br>Type | Description                                                                                                               |  |

|------------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|--|

| B14<br>A14 | P3_S_INP<br>P3_S_INN   | Ι           | SGMII Transmit Data. 1.25 GBaud input - Positive and Negative.                                                            |  |

| B13<br>A13 | P3_S_OUTP<br>P3_S_OUTN | 0           | SGMII Receive Data. 1.25 GBaud output - Positive and Negative.<br>Output amplitude can be adjusted via register 26_1.2:0. |  |

### 2.1.4 Reserved Pins

| Pin #    | Pin Name           | Pin<br>Type | Description               |  |

|----------|--------------------|-------------|---------------------------|--|

| B9<br>A9 | RSVD_NC<br>RSVD_NC | Ι           | Reserved, do not connect. |  |

| A8<br>B8 | RSVD_NC<br>RSVD_NC | 0           | Reserved, do not connect. |  |

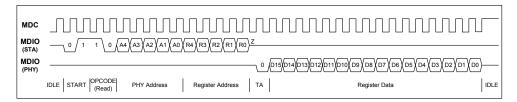

## 2.1.5 Management/Control

| Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                            |  |

|-------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| В6    | MDC      | I           | Management Clock pin.<br>MDC is the management data clock reference for the serial management<br>interface. A continuous clock stream is not expected. The maximum frequency<br>supported is 12 MHz.                   |  |

| A6    | MDIO     | I/O         | Management Data pin. MDIO is the management data. MDIO transfers management data in and out of the device synchronously to MDC. This pin requires a pull-up resistor in a range from 1.5 K $\Omega$ to 10 K $\Omega$ . |  |

| D2    | INTn     | OD          | Interrupt pin.<br>The pull-up resistor used for the INTn must be connected to the VDDOL level.<br>The pull-up resistor should not be connected to voltage higher than VDDOL.                                           |  |

### 2.1.6 LED

| Pin #                | Pin Name                                         | Pin<br>Type | Description                                                                                          |  |  |  |

|----------------------|--------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------|--|--|--|

| F2<br>E1<br>E2<br>D1 | P0_LED[3]<br>P0_LED[2]<br>P0_LED[1]<br>P0_LED[0] | 0           | Parallel LED Output port 0.                                                                          |  |  |  |

| H1<br>G1<br>G2<br>F1 | P1_LED[3]<br>P1_LED[2]<br>P1_LED[1]<br>P1_LED[0] | 0           | Parallel LED Output port 1.                                                                          |  |  |  |

| K2<br>K1<br>J1<br>H2 | P2_LED[3]<br>P2_LED[2]<br>P2_LED[1]<br>P2_LED[0] | 0           | Parallel LED Output port 2.                                                                          |  |  |  |

| M2<br>M1<br>L2<br>L1 | P3_LED[3]<br>P3_LED[2]<br>P3_LED[1]<br>P3_LED[0] | 0           | Parallel LED Output port 3.                                                                          |  |  |  |

| L3<br>K3<br>P1<br>N1 | CONFIG[3]<br>CONFIG[2]<br>CONFIG[1]<br>CONFIG[0] | I           | Global hardware configuration.<br>See Section 3.21 for details.                                      |  |  |  |

| 32                   | V18_L                                            | I           | VDDOL voltage control.<br>Tie to VSS = VDDOL operating at 3.3V<br>Floating = VDDOL operating at 1.9V |  |  |  |

| E13                  | V18_R                                            | I           | VDDOR voltage control.<br>Tie to VSS = VDDOR operating at 3.3V<br>Floating = VDDOR operating at 1.9V |  |  |  |

| C7                   | V12_EN                                           | I           | VDDOM voltage control.<br>Tie to VSS = VDDOM operating at 3.3V<br>Floating = VDDOM operating at 1.9V |  |  |  |

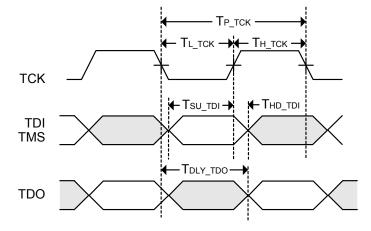

### 2.1.7 JTAG

| Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                             |  |

|-------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| G14   | TDI      | I, PU       | Boundary scan test data input. TDI contains an internal 150 K $\Omega$ pull-up resistor.                                                                                                                |  |

| G13   | TMS      | I, PU       | Boundary scan test mode select input. TMS contains an internal 150 $\mbox{K}\Omega$ pull-up resistor.                                                                                                   |  |

| G12   | тск      | I, PU       | Boundary scan test clock input. TCK contains an internal 150 K ${\rm \Omega}$ pull-up resistor.                                                                                                         |  |

| E12   | TRSTn    | I, PU       | Boundary scan test reset input. Active low.<br>TRSTn contains an internal 150 K $\Omega$ pull-up resistor. For normal operation, TRST<br>should be pulled low with a 4.7 K $\Omega$ pull-down resistor. |  |

| D12   | TDO      | 0           | Boundary scan test data output.                                                                                                                                                                         |  |

## 2.1.8 Master Clock/Reset

| Pin #      | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| J13        | XTAL_IN                  | I           | 25 MHz Clock Input<br>25 MHz ± 50 ppm tolerance crystal reference or oscillator input.<br>XTAL_IN should be left floating when it is not used. When XTAL_IN is driven<br>directly from the oscillator or clock buffer, this pin should be ac-coupled with a<br>0.1 nF capacitor.<br>No additional AC capacitor is needed if a capacitor divider is already used for<br>level shifting. |  |  |

| J14        | XTAL_OUT                 | 0           | 25 MHz Crystal Output.<br>25 MHz $\pm$ 50 ppm tolerance crystal reference. XTAL_OUT should be left floating when it is not used.                                                                                                                                                                                                                                                       |  |  |

| D13<br>D14 | REF_CLKP<br>REF_CLKN     | I           | 125 MHz/156.25 MHz Reference Clock Input Positive and Negative ± 50 ppm tolerance differential clock inputs.<br>REF_CLKP/N are LVDS differential inputs with a 100 Ω differential internal termination resistor.<br>If not used, REF_CLKP must be pulled high with a 1 KΩ resistor to 1.9V.<br>If not used, REF_CLKN must be pulled to GND with a 1 KΩ resistor.                       |  |  |

| H13<br>H14 | CLK_SEL[1]<br>CLK_SEL[0] | I           | Reference Clock Selection<br>00b = Reserved.<br>01b = Reserved.<br>10b = Use 25 MHz XTAL_IN/XTAL_OUT <sup>1</sup> .<br>11b = Use 25 MHz XTAL_IN/XTAL_OUT.<br>CLK_SEL[1:0] must be connected to VDDOR for configuration high.                                                                                                                                                           |  |  |

| E3         | RESETn                   | I           | Hardware reset. XTAL_IN must be active for a minimum of 10 clock cycles before<br>the rising edge of RESETn. RESETn must be in inactive state for normal<br>operation.<br>1b = Normal operation<br>0b = Reset                                                                                                                                                                          |  |  |

1. See Section 3.21 for details.

### 2.1.9 Test

| Pin #      | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                                                                                                                     |  |

|------------|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L14<br>L13 | HSDACP<br>HSDACN   | 0           | AC Test Point. Positive and Negative.<br>These pins are also used to bring out a differential TX_TCLK. Connect these pins with a 50 $\Omega$ termination resistor to VSS for IEEE testing and debug purposes. If debug and IEEE testing are not of importance, these pins can be left floating. |  |

| K13        | TSTPT              | 0           | DC Test Point. The TSTPT pin should be left floating.                                                                                                                                                                                                                                           |  |

| C8         | TSTPTF             | 0           | DC test point. The TSTPTF pin should be left floating.                                                                                                                                                                                                                                          |  |

| A5<br>B5   | TEST[1]<br>TEST[0] | I, PD       | Test Control. This pin should be left floating.                                                                                                                                                                                                                                                 |  |

#### 2.1.10 References

| Pin # | Pin Name | Pin<br>Type | Description                                                                 |  |

|-------|----------|-------------|-----------------------------------------------------------------------------|--|

| K12   | RSET     | I           | Resistor Reference External 5.0 K $\Omega$ 1% resistor connected to ground. |  |

#### **Power and Ground** 2.1.11

| Pin #                                                                                                                                                                                                                                                              | Pin<br>Name | Pin Type | Description                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|----------------------------------------|

| E6, E7, E8, E9, F4, F11, F12, G4, G11, H4, J4                                                                                                                                                                                                                      | DVDD        | Power    | 1.0V Digital Supply                    |

| D4, D5, D8, D9, D10, D11, E4, E5, E10, E11,<br>K11, L4, L5, L6, L7, L8, L9, L10, L11                                                                                                                                                                               | AVDDH       | Power    | 1.9V Analog Supply.                    |

| H12                                                                                                                                                                                                                                                                | VDDC        | Power    | 1.9V Supply <sup>1</sup> .             |

| D6, D7                                                                                                                                                                                                                                                             | VDDOM       | Power    | 1.9V or 3.3V I/O Supply <sup>2</sup> . |

| F13                                                                                                                                                                                                                                                                | VDDOR       | Power    | 1.9V or 3.3V I/O Supply <sup>3</sup> . |

| F3, G3, H3, J3                                                                                                                                                                                                                                                     | VDDOL       | Power    | 1.9V or 3.3V I/O Supply <sup>4</sup> . |

| A7, A10, B7, B10, C1, C2, C3, C4, C5, C6, C9,<br>C10, C11, C12, C13, C14, D3, F5, F6, F7, F8,<br>F9, F10, G5, G6, G7, G8, G9, G10, H5, H6, H7,<br>H8, H9, H10, H11, J5, J6, J7, J8, J9, J10, J11,<br>K4, K5, K6, K7, K8, K9, K10, L12, M3, M4, M13,<br>M14, N2, P2 | VSS         | Ground   | Ground.                                |

| J12                                                                                                                                                                                                                                                                | VSSC        | Ground   | Ground.                                |

VDDC supplies XTAL\_IN/OUT.

VDDOM supplies digital I/O pins for MDC, MDIO, and TEST.

VDDOR supplies digital I/O pins for TDO, TDI, TMS, TCK, TRSTn, REF\_CLKP/N, and CLK\_SEL[1:0].

VDDOL supplies digital I/O pins for RESETn, LED, CONFIG, and INTn.

#### Clocking 2.1.12

| Pin # | Pin Name | Pin<br>Type | Description                                                                                                             |

|-------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| E14   | RCLK1    | 0           | 25/125 MHz Gigabit Recovered Clock1. If not used pins must be left unconnected.                                         |

| F14   | RCLK2    | 0           | 25/125 MHz Gigabit Recovered Clock2. If not used pins must be left unconnected.                                         |

| K14   | SCLK     | I           | 25 MHz input reference clock. Do not electrically short the SCLK to XTAL_IN. If not used pins must be left unconnected. |

## 2.1.13 Pins I/O State at Various Test or Reset Modes

| Pin(s)      | Loopback | Software Reset                                                   | Hardware Reset                                      | Power Down                                                                                    |

|-------------|----------|------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|

| MDI[3:0]P/N | Active   | Tri-state                                                        | Tri-state                                           | Tri-state                                                                                     |

| S_OUTP/N    | Active   | Internally pulled up by terminations of 50 $\boldsymbol{\Omega}$ | Internally pulled up by terminations of 50 $\Omega$ | Reg. 16.3 state<br>Ob = Internally pulled up by<br>terminations of 50 $\Omega$<br>1b = Active |

| MDIO        | Active   | Active                                                           | Tri-state                                           | Active                                                                                        |

| INTn        | Active   | Tri-state                                                        | Tri-state                                           | Tri-state                                                                                     |

| LED         | Active   | See Section 2.27.5                                               | Tri-state                                           | See Section 2.27.5                                                                            |

| TDO         | Active   | Active                                                           | Active                                              | Active                                                                                        |

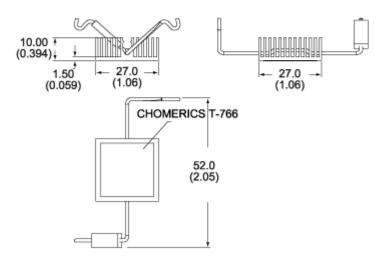

## 2.2 Pinouts (Top View)

### 2.2.1 Pin A1 Location

## 2.2.2 Pinouts (A1 Through P7)

|   | 1         | 2         | 3          | 4          | 5          | 6          | 7          |   |

|---|-----------|-----------|------------|------------|------------|------------|------------|---|

| A | P0_S_INN  | P0_S_OUTN | P1_S_OUTP  | P1_S_INP   | TEST[1]    | MDIO       | VSS        | A |

| В | P0_S_INP  | P0_S_OUTP | P1_S_OUTN  | P1_S_INN   | TEST[0]    | MDC        | VSS        | В |

| С | VSS       | VSS       | VSS        | VSS        | VSS        | VSS        | V12_EN     | С |

| D | P0_LED[0] | INTn      | VSS        | AVDDH      | AVDDH      | VDDOM      | VDDOM      | D |

| Е | P0_LED[2] | P0_LED[1] | RESETn     | AVDDH      | AVDDH      | DVDD       | DVDD       | Е |

| F | P1_LED[0] | P0_LED[3] | VDDOL      | DVDD       | VSS        | VSS        | VSS        | F |

| G | P1_LED[2] | P1_LED[1] | VDDOL      | DVDD       | VSS        | VSS        | VSS        | G |

| н | P1_LED[3] | P2_LED[0] | VDDOL      | DVDD       | VSS        | VSS        | VSS        | Н |

| J | P2_LED[1] | V18_L     | VDDOL      | DVDD       | VSS        | VSS        | VSS        | J |

| К | P2_LED[2] | P2_LED[3] | CONFIG[2]  | VSS        | VSS        | VSS        | VSS        | к |

| L | P3_LED[0] | P3_LED[1] | CONFIG[3]  | AVDDH      | AVDDH      | AVDDH      | AVDDH      | L |

| М | P3_LED[2] | P3_LED[3] | VSS        | VSS        | P0_MDIP[3] | P0_MDIN[3] | P1_MDIN[0] | М |

| Ν | CONFIG[0] | VSS       | P0_MDIP[0] | P0_MDIP[1] | P0_MDIN[2] | P1_MDIP[3] | P1_MDIP[2] | Ν |

| Ρ | CONFIG[1] | VSS       | P0_MDIN[0] | P0_MDIN[1] | P0_MDIP[2] | P1_MDIN[3] | P1_MDIN[2] | Ρ |

|   | 1         | 2         | 3          | 4          | 5          | 6          | 7          |   |

## 2.2.3 Pinouts (A8 Through P14)

|   | 8          | 9          | 10         | 11         | 12         | 13         | 14         |   |

|---|------------|------------|------------|------------|------------|------------|------------|---|

| A | RSVD_NC    | RSVD_NC    | VSS        | P2_S_INP   | P2_S_OUTP  | P3_S_OUTN  | P3_S_INN   | А |

| В | RSVD_NC    | RSVD_NC    | VSS        | P2_S_INN   | P2_S_OUTN  | P3_S_OUTP  | P3_S_INP   | В |

| С | TSTPTF     | VSS        | VSS        | VSS        | VSS        | VSS        | VSS        | С |

| D | AVDDH      | AVDDH      | AVDDH      | AVDDH      | TDO        | RSVD_NC    | RSVD_NC    | D |

| Е | DVDD       | DVDD       | AVDDH      | AVDDH      | TRSTn      | V18_R      | RCLK1      | Е |

| F | VSS        | VSS        | VSS        | DVDD       | DVDD       | VDDOR      | RCLK2      | F |

| G | VSS        | VSS        | VSS        | DVDD       | ТСК        | TMS        | TDI        | G |

| н | VSS        | VSS        | VSS        | VSS        | VDDC       | CLK_SEL[1] | CLK_SEL[0] | н |

| J | VSS        | VSS        | VSS        | VSS        | VSSC       | XTAL_IN    | XTAL_OUT   | J |

| к | VSS        | VSS        | VSS        | AVDDH      | RSET       | TSTPT      | SCLK       | к |

| L | AVDDH      | AVDDH      | AVDDH      | AVDDH      | VSS        | HSDACN     | HSDACP     | L |

| М | P1_MDIP[0] | P2_MDIP[3] | P2_MDIN[3] | P3_MDIN[1] | P3_MDIP[1] | VSS        | VSS        | М |

| Ν | P1_MDIP[1] | P2_MDIN[0] | P2_MDIN[1] | P2_MDIN[2] | P3_MDIP[3] | P3_MDIP[2] | P3_MDIP[0] | Ν |

| Ρ | P1_MDIN[1] | P2_MDIP[0] | P2_MDIP[1] | P2_MDIP[2] | P3_MDIN[3] | P3_MDIN[2] | P3_MDIN[0] | Ρ |

|   | 8          | 9          | 10         | 11         | 12         | 13         | 14         |   |

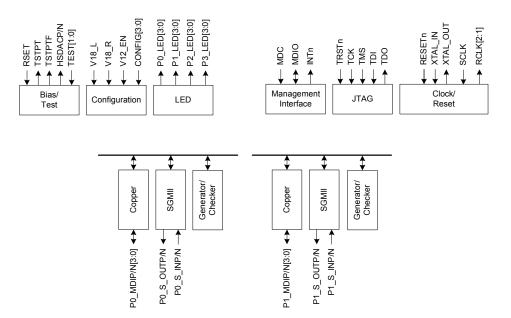

## 3.0 Device Functionality

The I347-AT4 is a 2- or 4-port 10/100/1000BASE-T Gigabit Ethernet transceiver. Each port of the I347-AT4 can operate completely independent of each other, but they are identical in performance and functionality. The functional description and electrical specifications for the I347-AT4 are applicable to each port. For simplicity, the functional description in this document describes the operation of a single transceiver.

Port numbers have been omitted from many diagrams and descriptive text indicating that the functionality applies to all ports. In this document, the pins for each port are specified by the port number, pin name, and signal number, respectively.

For example, LED 1 pin for Port 0 shown in Figure 3 (P0\_LED[1]):

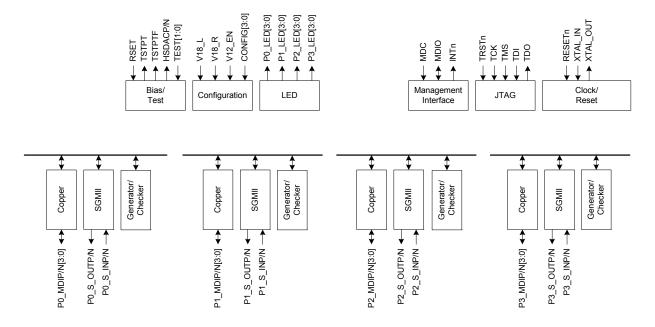

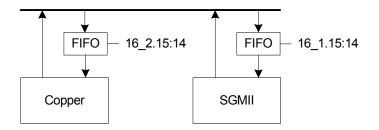

However, the MDIO pin supported by the I347-AT4 are global to the chip and do not have port numbers. Figure 3 and Figure 4 show the functional block diagram of the I347-AT4.

Figure 3. Functional Block Diagram – Dual-Port Mode

### 3.1 I347-AT4 Operation and Major Interfaces

The I347-AT4 supports an MDI interface-to-copper cable interface.

The MDI Interface is always a media interface. (The system interface is also known as MAC interface. It is typically the connection between the PHY and the MAC or the system ASIC.) For example:

#### Figure 5. SGMII System Interface Example – Quad-Port Mode

#### Figure 6. SGMII System Interface Example – Dual-Port Mode

As can be seen from this example, the SGMII interface acts as a system interface.

The I347-AT4 supports one mode of operation: SGMII (system)-to-copper (Register 20\_6.2:0 (001b).

### 3.2 Copper Media Interface

The copper interface consists of the MDIP/N[3:0] pins that connect to the physical media for 1000BASE-T, 100BASE-TX, and 10BASE-T modes of operation.

The I347-AT4 integrates MDI interface termination resistors. The IEEE 802.3 specification requires that both sides of a link have termination resistors to prevent reflections. Traditionally, these resistors and additional capacitors are placed on the board between a PHY device and the magnetics. The resistors have to be very accurate to meet the strict IEEE return loss requirements. Typically,  $\pm 1\%$  accuracy resistors are used on the board. These additional components between the PHY and the magnetics complicate board layout. Integrating the resistors has many advantages including component cost savings, better ICT yield, board reliability improvements, board area savings, improved layout, and signal integrity improvements.

#### **3.2.1** Transmit Side Network Interface

#### 3.2.1.1 Multi-mode TX Digital-to-Analog Converter

The I347-AT4 incorporates a multi-mode transmit DAC to generate filtered 4D PAM 5, MLT3, or Manchester coded symbols. The transmit DAC performs signal wave shaping to reduce EMI. The transmit DAC is designed for very low parasitic loading capacitances to improve the return loss requirement, which allows the use of low cost transformers.

#### 3.2.1.2 Slew Rate Control and Waveshaping

In 1000BASE-T mode, partial response filtering and slew rate control is used to minimize high frequency EMI. In 100BASE-TX mode, slew rate control is used to minimize high frequency EMI. In 10BASE-T mode, the output waveform is preequalized via a digital filter.

#### 3.2.2 Encoder

#### 3.2.2.1 **1000BASE-T**

In 1000BASE-T mode, the transmit data bytes are scrambled to 9-bit symbols and encoded into 4D PAM 5 symbols. Upon initialization, the initial scrambling seed is determined by the PHY address. This prevents multiple the I347-AT4 from outputting the same sequence during idle, which helps to reduce EMI.

#### 3.2.2.2 **100BASE-TX**

In 100BASE-TX mode, the transmit data stream is 4B/5B encoded, serialized, and scrambled.

#### 3.2.2.3 **10BASE-T**

In 10BASE-T mode, the transmit data is serialized and converted to Manchester encoding.

#### 3.2.3 Receive Side Network Interface

#### 3.2.3.1 Analog-to-Digital Converter

The I347-AT4 incorporates an advanced high speed ADC on each receive channel with greater resolution than the ADC used in the reference model of the 802.3ab standard committee. Higher resolution ADC results in better SNR, and therefore, lower error rates. Proprietary architectures and design techniques result in high differential and integral linearity, high power supply noise rejection, and low metastability error rate. The ADC samples the input signal at 125 MHz.

#### 3.2.3.2 Active Hybrid

The I347-AT4 employs a sophisticated on-chip hybrid to substantially reduce the nearend echo, which is the super-imposed transmit signal on the receive signal. The hybrid minimizes the echo to reduce the precision requirement of the digital echo canceller. The on-chip hybrid allows both the transmitter and receiver to use the same transformer for coupling to the twisted pair cable, which reduces the cost of the overall system.

#### 3.2.3.3 Echo Canceller

Residual echo not removed by the hybrid and echo due to patch cord impedance mismatch, patch panel discontinuity, and variations in cable impedance along the twisted pair cable result in drastic SNR degradation on the receive signal. The I347-AT4 employs a fully developed digital echo canceller to adjust for echo impairments from more than 100 meters of cable. The echo canceller is fully adaptive to compensate for the time varying nature of channel conditions.

#### 3.2.3.4 NEXT Canceller

The 1000BASE-T physical layer uses all 4 pairs of wires to transmit data to reduce the baud rate requirement to only 125 MHz. This results in significant high frequency crosstalk between adjacent pairs of cable in the same bundle. The I347-AT4 employs 3 parallel NEXT cancellers on each receive channel to cancel any high frequency crosstalk induced by the adjacent 3 transmitters. A fully adaptive digital filter is used to compensate for the time varying nature of channel conditions.

#### 3.2.3.5 Baseline Wander Canceller

Baseline wander is more problematic in the 1000BASE-T environment than in the traditional 100BASE-TX environment due to the DC baseline shift in both the transmit and receive signals. The I347-AT4 employs an advanced baseline wander cancellation circuit to automatically compensate for this DC shift. It minimizes the effect of DC baseline shift on the overall error rate.

#### 3.2.3.6 Digital Adaptive Equalizer

The digital adaptive equalizer removes inter-symbol interference at the receiver. The digital adaptive equalizer takes unequalized signals from ADC output and uses a combination of Feed Forward Equalizer (FFE) and decision feedback equalizer (DFE) for the best-optimized signal-to-noise (SNR) ratio.

#### 3.2.3.7 Digital Phase Lock Loop

In 1000BASE-T mode, the slave transmitter must use the exact receive clock frequency it sees on the receive signal. Any slight long-term frequency phase jitter (frequency drift) on the receive signal must be tracked and duplicated by the slave transmitter; otherwise, the receivers of both the slave and master physical layer devices have difficulty canceling the echo and NEXT components. In the I347-AT4, an advanced DPLL is used to recover and track the clock timing information from the receive signal. This DPLL has very low long-term phase jitter of its own, thereby maximizing the achievable SNR.

#### 3.2.3.8 Link Monitor

The link monitor is responsible for determining if link is established with a link partner. In 10BASE-T mode, link monitor function is performed by detecting the presence of valid link pulses (NLPs) on the MDIP/N pins.

In 100BASE-TX and 1000BASE-T modes, link is established by scrambled idles.

If Force Link Good register 16\_0.10 is set high, the link is forced to be good and the link monitor is bypassed for 100BASE-TX and 10BASE-T modes. In the 1000BASE-T mode, register 16\_0.10 has no effect.

#### 3.2.3.9 Signal Detection

In 1000BASE-T mode, signal detection is based on whether the local receiver has acquired lock to the incoming data stream.

In 100BASE-TX mode, the signal detection function is based on the receive signal energy detected on the MDIP/N pins that is continuously qualified by the squelch detect circuit, and the local receiver acquiring lock.

### 3.2.4 Decoder

#### 3.2.4.1 1000BASE-T

In 1000BASE-T mode, the receive idle stream is analyzed so that the scrambler seed, the skew among the 4 pairs, the pair swap order, and the polarity of the pairs can be accounted for. Once calibrated, the 4D PAM 5 symbols are converted to 9-bit symbols that are then descrambled into 8-bit data values. If the descrambler loses lock for any reason, the link is brought down and calibration is restarted after the completion of auto-negotiation.

#### 3.2.4.2 **100BASE-TX**

In 100BASE-TX mode, the receive data stream is recovered and converted to NRZ. The NRZ stream is descrambled and aligned to the symbol boundaries. The aligned data is put in parallel and then 5B/4B decoded. The receiver does not attempt to decode the data stream unless the scrambler is locked. The descrambler "locks" to the *scrambler* state after detecting a sufficient number of consecutive idle code-groups. Once locked, the descrambler continuously monitors the data stream to make sure that it has not lost synchronization. The descrambler is always forced into the *unlocked* state when a link failure condition is detected, or when insufficient idle symbols are detected.

#### 3.2.4.3 **10BASE-T**

In 10BASE-T mode, the recovered 10BASE-T signal is decoded from Manchester to NRZ, and then aligned. The alignment is necessary to insure that the start of frame delimiter (SFD) is aligned to the nibble boundary.

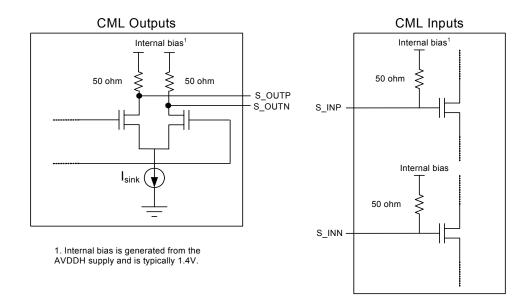

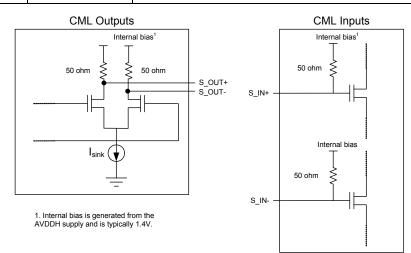

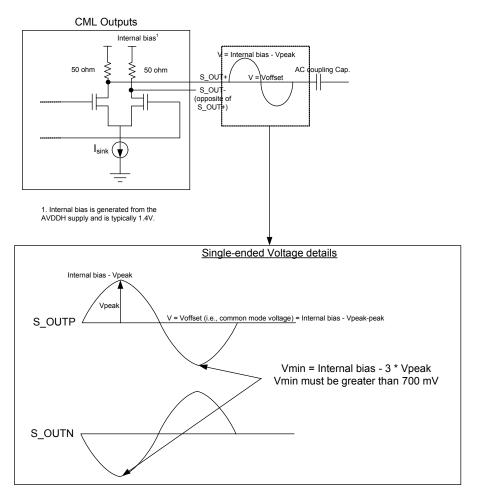

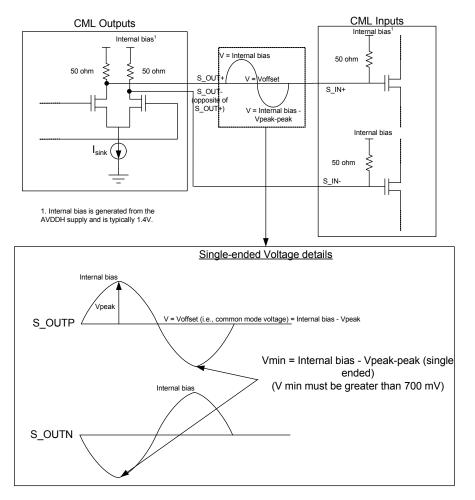

### 3.2.5 Electrical Interface

The input and output buffers are internally terminated to 50  $\Omega$  impedance. The output swing can be adjusted by programming register 26\_1.2:0.

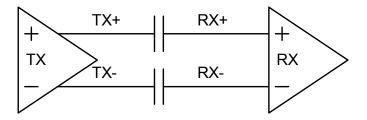

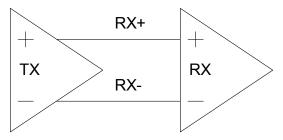

#### Figure 7. CML I/Os

#### 3.2.6 SGMII Speed and Link

When the SGMII MAC interface is used, the interface is copper . The operational speed of the SGMII MAC interface is determined according to Table 9 media interface status and/or loopback mode.

#### Table 9. SGMII (MAC Interface) Operational Speed

| Link Status or Media Interface Status | SGMII (MAC Interface) Speed             |

|---------------------------------------|-----------------------------------------|

| No Link                               | Determined by speed setting of 21_2.2:0 |

| MAC Loopback                          | Determined by speed setting of 21_2.2:0 |

#### 3.2.7 SGMII TRR Blocking

When the SGMII receives a packet with odd number of bytes, a single symbol of carrier extension will be passed on and transmitted onto 1000BASE-T. This carrier extension may cause problems with full-duplex MACs that incorrectly handle the carrier extension symbols. When register 16\_1.13 is set to 1, all carrier extend and carrier extend with error symbols received by the SGMII will be converted to idle symbols when operating in full-duplex. Carrier extend and carrier extend with error symbols will not be blocked when operating in half-duplex, or if register 16\_1.13 is set to 0b. Note that symbol errors will continue to be propagated regardless of the setting of register 16\_1.13.

This function is on by default as the SGMII rev 1.8 standard requires this function to be implemented.

### 3.3 Loopback

The I347-AT4 implements various different loopback paths.

#### 3.3.1 System Interface Loopback

The functionality, timing, and signal integrity of the system interface can be tested by placing the I347-AT4 in system interface loopback mode. This can be accomplished by setting register  $0_{0.14} = 1b$ ,  $0_{1.14} = 1b$ , or  $0_{4.14} = 1b$ . In loopback mode, the data received from the MAC is not transmitted out on the media interface. Instead, the data is looped back and sent to the MAC. During loopback, link will be lost and packets will not be received.

If loopback is enabled while auto-negotiating, FLP auto-negotiation codes will be transmitted. If loopback is enabled in forced 10BASE-T mode, 10BASE-T idle link pulses will be transmitted on the copper side. If loopback is enabled in forced 100BASE-T mode, 100BASE-T idles will be transmitted on the copper side.

The speed of the SGMII interface is determined by register  $21_2.2:0$  during loopback.  $21_2.2:0$  is 100b = 10 Mb/s, 101b = 100 Mb/s, 110b = 1000 Mb/s.

#### Figure 8. MAC Interface Loopback Diagram - Copper Media Interface

#### **3.3.2** Line Loopback

Line loopback allows a link partner to send frames into the I347-AT4 to test the transmit and receive data path. Frames from a link partner into the PHY, before reaching the MAC interface pins, are looped back and sent out on the line. They are also sent to the MAC. The packets received from the MAC are ignored during line loopback. Refer to Figure 9. This allows the link partner to receive its own frames.

Before enabling the line loopback feature, the PHY must first establish link to another PHY link partner. If auto-negotiation is enabled, both link partners should advertise the same speed and full-duplex. If auto-negotiation is disabled, both link partners need to be forced to the same speed and full-duplex. Once link is established, the line loopback mode can be enabled.

Register 21\_2.14 = 1b enables the line loopback on the copper interface.

#### Figure 9. Copper Line Loopback Data Path

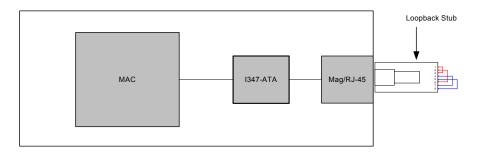

#### 3.3.3 External Loopback

For production testing, an external loopback stub allows testing of the complete data path.

For 10BASE-T and 100BASE-TX modes, the loopback test requires no register writes. For 1000BASE-T mode, register 18\_6.3 must be set to 1b to enable the external loopback. All copper modes require an external loopback stub.

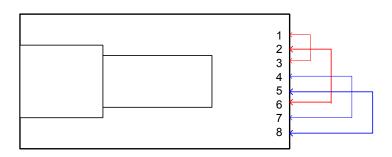

The loopback stub consists of a plastic RJ-45 header, connecting RJ-45 pair 1, 2 to pair 3, 6 and connecting pair 4, 5 to pair 7, 8, as seen in Figure 10.

Figure 10. Loopback Stub (Top View With Tab Up)

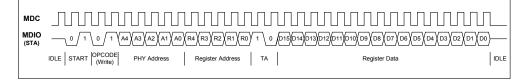

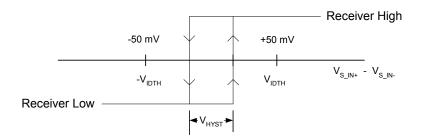

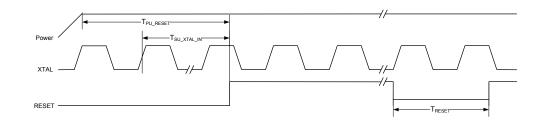

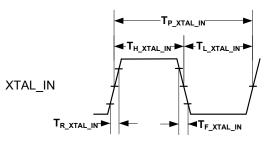

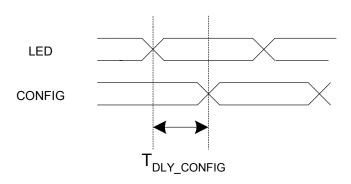

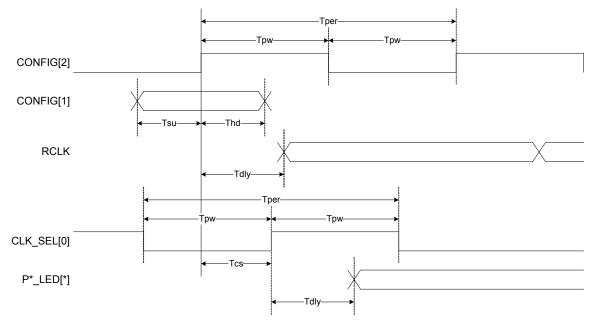

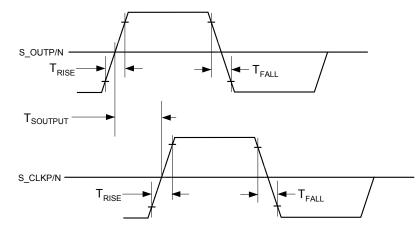

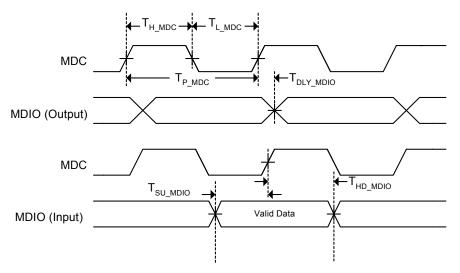

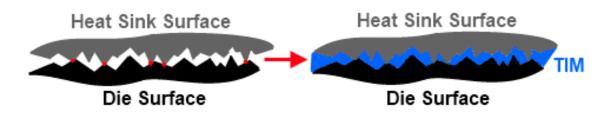

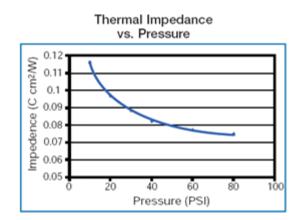

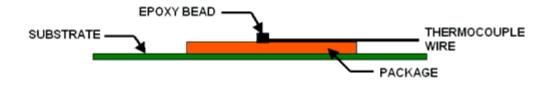

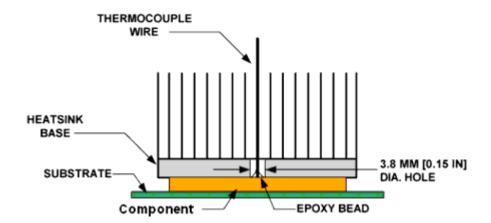

The external loopback test setup requires the presence of a MAC that will originate the frames to be sent out through the PHY. Instead of a normal RJ-45 cable, the loopback stubs allows the PHY to self-link at 1000 Mb/s. It also allows the actual external loopback. See Figure 11. The MAC should see the same packets it sent, looped back to it.