# MIC3001

FOM Management IC with Internal Calibration

### Consider MIC3003 for New Designs

### **General Description**

The MIC3001 enables the implementation of sophisticated, hot-pluggable fiber optic transceivers with intelligent laser control and an internally calibrated digital diagnostic monitoring interface per SFF-8472. It essentially integrates all non-data path functions of an SFP transceiver into a tiny (4mm  $\times$  4mm) QFN package.

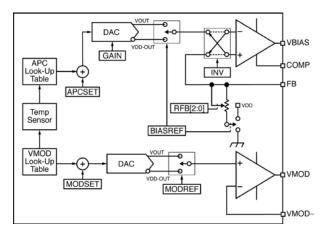

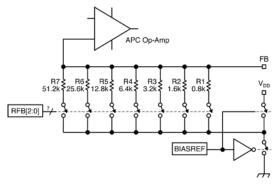

A highly-configurable automatic power control (APC) circuit controls laser bias. Bias and modulation are temperature compensated using dual DACs, an on-chip temperature sensor, and NVRAM look-up tables. A programmable internal feedback resistor provides unprecedented dynamic range for APC. Controlled laser turn-on facilitates hot plugging.

An analog-to-digital converter converts the measured temperature, voltage, bias current, transmit power, and received power from analog to digital. An EEPOT provides front-end adjustment of RX power. Each parameter is compared against user-programmed warning and alarm thresholds. Analog comparators and DACs provide highspeed monitoring of received power and critical laser operating parameters. Data can be reported as either internally calibrated or externally calibrated.

An interrupt output, power-on hour meter, and data-ready bits add user friendliness beyond SFF-8472. The interrupt output and data-ready bits reduce overhead in the host system. The power-on hour meter logs operating hours using an internal real-time clock and stores the result in NVRAM.

Communication with the MIC3001 is via an industry standard 2-wire serial interface. Nonvolatile memory is provided for serial ID, configuration, and separate OEM and user scratchpad spaces. Two-level password protection guards against data corruption.

Data sheets and support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

#### Features

- APC or constant-current laser bias

- Turbo mode for APC loop start-up and shorter laser turn on time

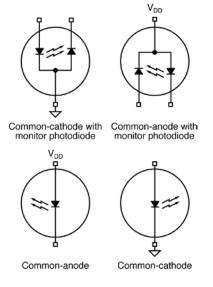

- Supports multiple laser types and bias circuit topologies

- Drives external low-cost BJT for laser bias

- Integrated digital temperature sensor

- Temperature compensation of modulation, bias, and fault levels via NVRAM look-up tables

- Direct interface to SY88932, SY88982, SY89307 and other drivers

- NVRAM to support GBIC/SFP serial ID function

- User writable EEPROM scratchpad

- Diagnostic monitoring interface per SFF-8472

- Monitors and reports critical parameters: temperature, bias current, TX and RX optical power, and supply voltage

- S/W control and monitoring of TXFAULT, RXLOS, RATESELECT, and TXDISABLE

- Internal or external calibration

- EEPOT for adjusting RX power measurement

- Power-on hour meter

- Interrupt capability

- Extensive test and calibration features

- 2-wire, I<sup>2</sup>C-compatible serial interface

- SFP MSA and SFF-8472 compliant

- 3.0V to 3.6V power supply range

- 5V-tolerant I/O

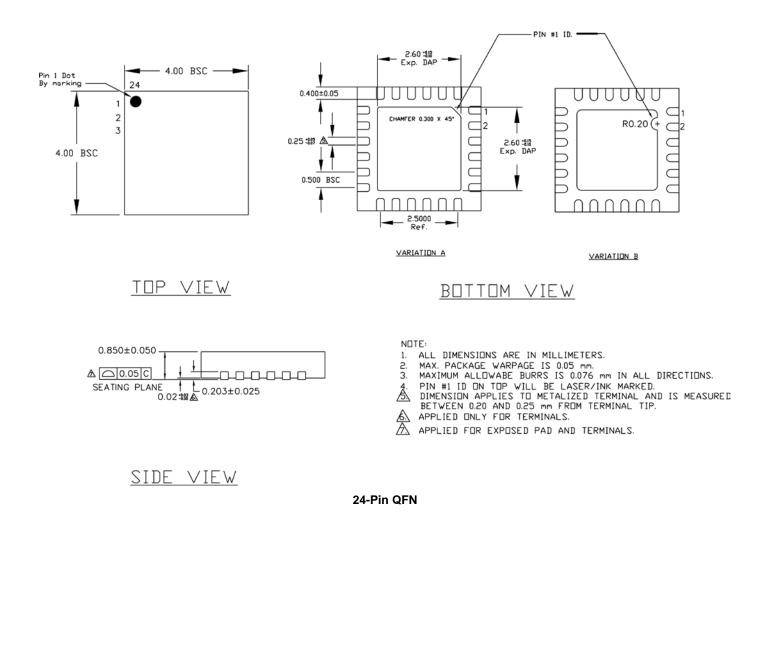

- 4mm × 4mm 24-pin QFN package

### **Applications**

- SFF/SFP optical transceivers

- SONET/SDH transceivers and transponders

- Fibre channel transceivers

- 10Gbps transceivers

- Free space optical communications

- Proprietary optical links

MLF and *Micro*LeadFrame are registered trademarks of Amkor Technology

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

# **Ordering Information**

| Part Number                 | Package Type | Junction Temperature Range | Package Marking                         | Lead<br>Finish     |

|-----------------------------|--------------|----------------------------|-----------------------------------------|--------------------|

| MIC3001BML                  | 24-Pin QFN   | -45°C to +105°C            | 3001                                    | Sn-Pb or<br>NiPdAu |

| MIC3001BMLTR <sup>(1)</sup> | 24-Pin QFN   | -45°C to +105°C            | 3001                                    | Sn-Pb or<br>NiPdAu |

| MIC3001GML                  | 24-Pin QFN   | -45°C to +105°C            | 3001 with Pb-Free Bar-Line<br>Indicator | NiPdAu             |

| MIC3001GMLTR <sup>(1)</sup> | 24-Pin QFN   | -45°C to +105°C            | 3001 with Pb-Free Bar-Line<br>Indicator | NiPdAu             |

Note:

1. Tape and Reel.

### Contents

| General Description                           | 1  |

|-----------------------------------------------|----|

| Applications                                  | 1  |

| Ordering Information                          | 2  |

| Pin Configuration                             | 7  |

| Pin Description                               | 7  |

| Absolute Maximum Ratings                      | 9  |

| Operating Ratings                             | 9  |

| Electrical Characteristics                    | 9  |

| Timing Diagram                                | 14 |

| Address Map                                   | 15 |

| Block Diagram                                 | 17 |

| MIC3000 Capability                            | 17 |

| Analog-to-Digital Converter/Signal Monitoring | 17 |

| Internal/External Calibration                 | 19 |

| A/ External Calibration                       | 19 |

| Voltage                                       | 19 |

| Temperature                                   | 19 |

| Bias Current                                  | 19 |

| TX Power                                      | 19 |

| RX Power                                      | 20 |

| B/ Internal Calibration                       |    |

| C/ ADC Result Registers Reading               | 22 |

| RXPOT                                         | 22 |

| Laser Diode Bias Control                      |    |

| Laser Modulation Control                      |    |

| Power ON and Laser Start-Up                   |    |

| Fault Comparators                             | 25 |

| SHDN and TXFIN                                |    |

| Temperature Measurement                       |    |

| Diode Faults                                  |    |

| Temperature Compensation                      |    |

| Alarms and Warning Flags                      |    |

| Control and Status I/O                        |    |

| System Timing                                 |    |

| Warm Resets                                   |    |

| Power-On Hour Meter                           |    |

| Test and Calibration Features                 |    |

| Serial Port Operation                         |    |

| Page Writes                                   |    |

| Acknowledge Polling                           |    |

| Write Protection and Data Security            |    |

| OEM Password                                  |    |

| User Password                                 |    |

| Detailed Register Descriptions                |    |

| Alarm Threshold Registers                     |    |

| Warning Threshold Registers                   |    |

| ADC Result Registers                          | 49 |

| Alarm Flags                                        | 52 |

|----------------------------------------------------|----|

|                                                    |    |

| Warning Flags                                      |    |

| Applications Information                           |    |

| Controlling Laser Diode Bias                       |    |

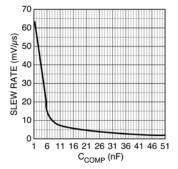

| Choosing C <sub>COMP</sub>                         | 70 |

| Measuring Laser Bias Current                       | 70 |

| Interfacing To Laser Drivers                       |    |

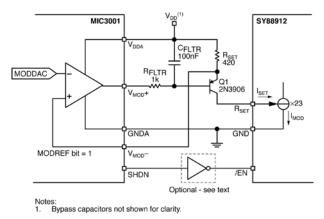

| SY88912 3.3V 3.2Gbps SONET/SDH Laser Driver        | 71 |

| Modulation Current                                 | 71 |

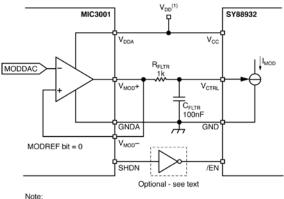

| SY88932 3.3V 3.2Gbps SONET/SDH Laser Driver        | 71 |

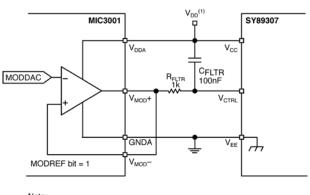

| SY89307 5.0V/ 3.3V 2.5Gbps VCSEL Driver            | 72 |

| Laser Drivers Programmed via a Sink Current        | 72 |

| Drivers with Monitor Outputs                       | 72 |

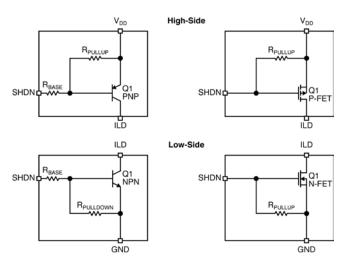

| Shutdown Output                                    | 72 |

| Temperature Sensing                                | 73 |

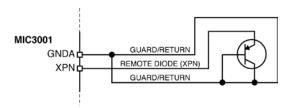

| Remote Sensing                                     | 73 |

| Minimizing Errors                                  |    |

| Self-Heating                                       |    |

| Series Resistance with External Temperature Sensor | 74 |

| XPN Filter Capacitor Selection                     |    |

| XPN Layout Considerations                          |    |

| Layout Considerations                              |    |

| Small Form-Factor Pluggable (SFP) Transceivers     |    |

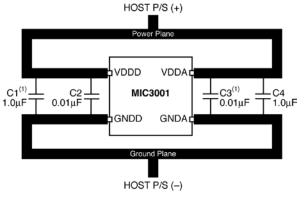

| Power Supplies                                     |    |

| Using the MIC3001 In a 5V System                   |    |

| Package Information                                |    |

|                                                    |    |

# List of Figures

| Figure 1. MIC3001 Block Diagram                                             | 17 |

|-----------------------------------------------------------------------------|----|

| Figure 2. Analog-to-Digital Converter Block Diagram                         | 18 |

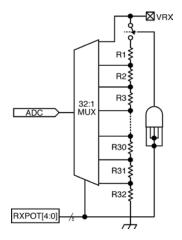

| Figure 3. RXPOT Block Diagram                                               | 22 |

| Figure 4. MIC3001 APC and Modulation Control Block Diagram                  | 22 |

| Figure 5. Programmable Feedback Resistor                                    |    |

| Figure 6. Transmitter Configurations Supported by MIC3001                   | 23 |

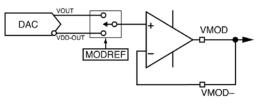

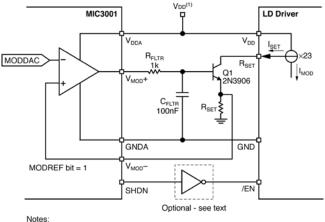

| Figure 7. V <sub>MOD</sub> Configured as Voltage Output with Gain           | 23 |

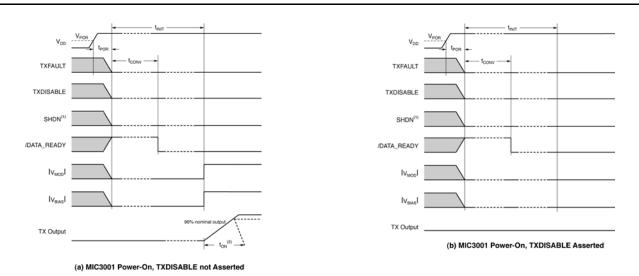

| Figure 9. Fault Comparator Logic                                            | 25 |

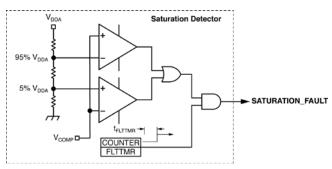

| Figure 10. Saturation Detector                                              | 26 |

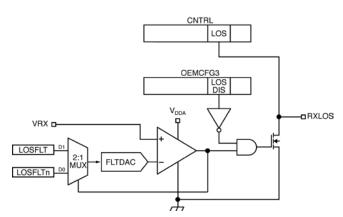

| Figure 11. RXLOS Comparator Logic                                           | 26 |

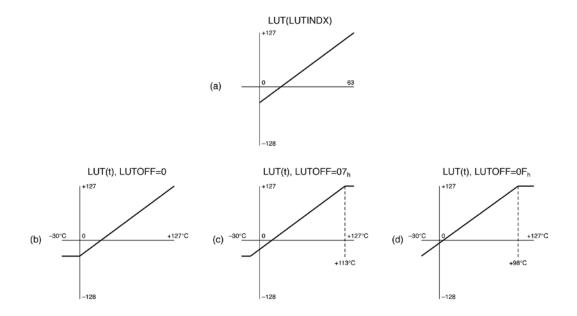

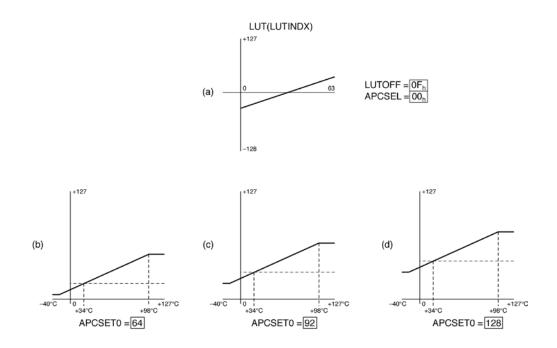

| Figure 12. Examples of LUTOFF Operation                                     |    |

| Figure 13. Temperature Compensation Examples                                |    |

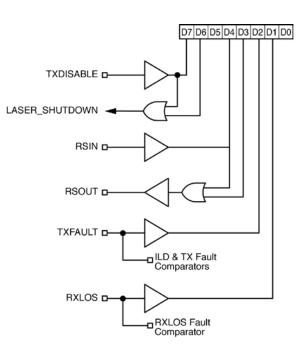

| Figure 14. Control and Status I/O Logic                                     | 32 |

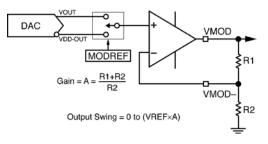

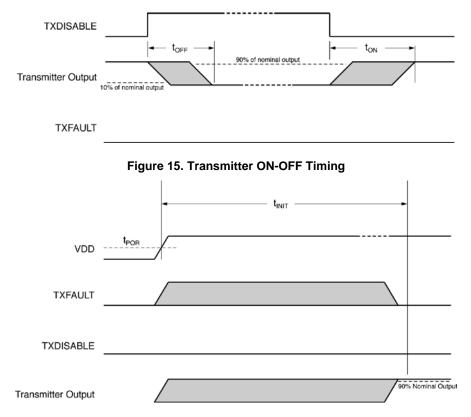

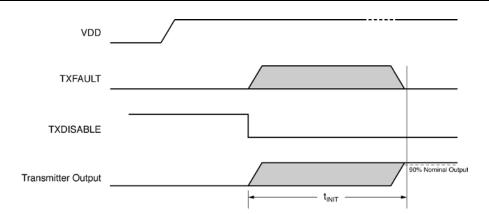

| Figure 15. Transmitter ON-OFF Timing                                        | 32 |

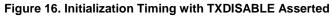

| Figure 16. Initialization Timing with TXDISABLE Asserted                    | 32 |

| Figure 17. Initialization Timing with TXDISABLE Not Asserted                | 33 |

| Figure 18. Loss-of-Signal (LOS) Timing                                      | 33 |

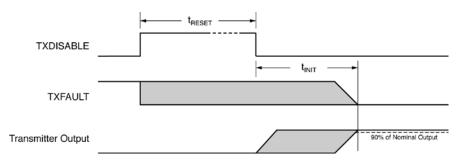

| Figure 20. Successfully Clearing a Fault Condition                          | 34 |

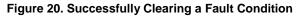

| Figure 21. Unsuccessful Attempt to Clear a Fault                            | 34 |

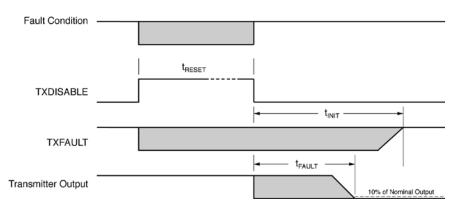

| Figure 22. Write Byte Protocol                                              | 36 |

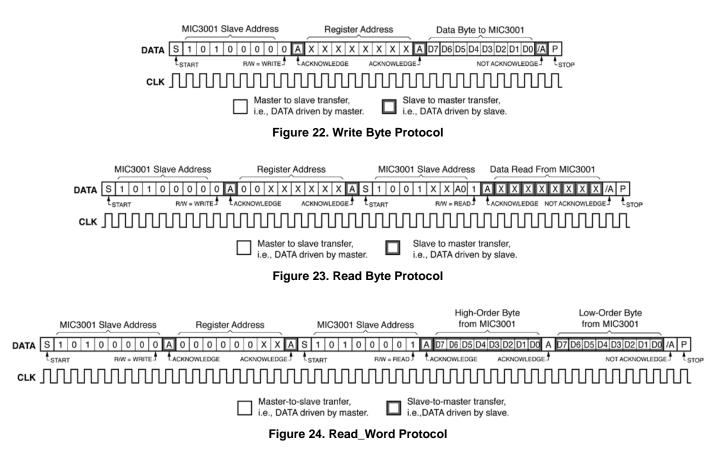

| Figure 23. Read Byte Protocol                                               | 36 |

| Figure 24. Read_Word Protocol                                               | 36 |

| Figure 25. Four-Byte Page_White Protocol                                    | 37 |

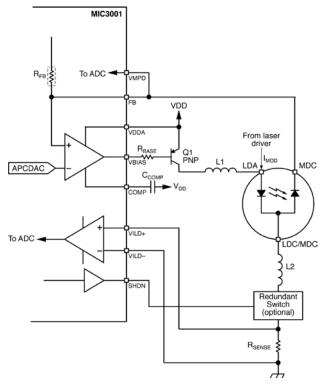

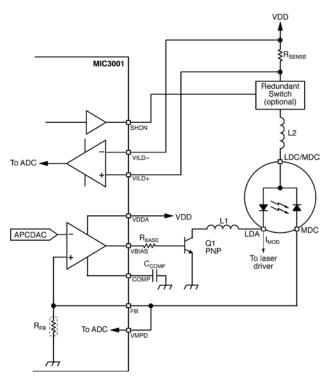

| Figure 26. Example APC Circuit for Common-Cathode TOSA                      |    |

| Figure 27. Example APC Circuit for Common Anode TOSA                        |    |

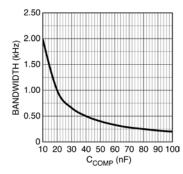

| Figure 28. Slew Rate vs. C <sub>COMP</sub> Value                            | 70 |

| Figure 29. Open Loop Unity-Gain Bandwidth vs. C <sub>COMP</sub>             | 70 |

| Figure 31. Controlling the SY88932 Modulation Current                       |    |

| Figure 32. Controlling the SY89307 Modulation Current                       | 72 |

| Figure 33. Controlling the Modulation Current via a Sink Current            | 72 |

| Figure 34. Redundant Switch Circuits                                        | 73 |

| Figure 35. Guard Traces and Kelvin Return for Remote Thermal Diode          |    |

| Figure 36. Typical SFP Control and Status I/O Signal Routing (not to scale) | 75 |

| Figure 37. Power Supply Routing and Bypassing                               | 75 |

# List of Tables

| Table 1. MIC3001 Address Map, Serial Address = A0 <sub>h</sub>                                           | 15 |

|----------------------------------------------------------------------------------------------------------|----|

| Table 2. MIC3001 Address Map, Serial Address = A2 <sub>h</sub>                                           | 15 |

| Table 3. Temperature Compensation Tables, Serial Address = A4 <sub>h</sub>                               | 15 |

| Table 4. OEM Configuration Registers, Serial Address = A6 <sub>h</sub>                                   | 16 |

| Table 5. A/D Input Signal Ranges and Resolutions                                                         | 18 |

| Table 6. V <sub>AUX</sub> Input Signal Ranges and Resolutions                                            | 18 |

| Table 7. LSB Values of Offset Coefficients                                                               |    |

| Table 8. Internal Calibration Coefficient Memory Map – Part I                                            | 21 |

| Table 9. Internal Calibration Coefficient Memory Map – Part II                                           | 21 |

| Table 10. Shutdown State of SHDN vs. Configuration Bits                                                  | 24 |

| Table 11. Shutdown State of V <sub>BIAS</sub> vs. Configuration Bits                                     |    |

| Table 12. Shutdown State of V <sub>MOD</sub> vs. Configuration Bits                                      |    |

| Table 13. Temperature Compensation Look-up Tables, Serial Address I2CADR + 4h                            | 27 |

| Table 14. APC Temperature Compensation Look-Up Table, Serial Address 12C ADR+4h                          | 28 |

| Table 15. V <sub>MOD</sub> Temperature Compensation Look-Up Table, Serial Address 12C ADR+4 <sub>h</sub> | 28 |

| Table 16. IBIAS Comparator Temperature Compensation Look-Up Table, Serial Address 12C ADR+4h             | 28 |

| Table 17. BIAS Current High Alarm Temperature Compensation Table, Serial Address 12C ADR+4h              | 28 |

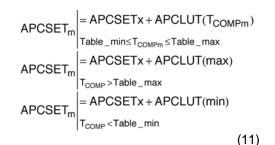

| Table 18. Range of Temperature Compensation Table vs. LUTOFF                                             | 29 |

| Table 19. MIC3001 Events                                                                                 | 31 |

| Table 20. Power-On Hour Meter Result Format                                                              | 35 |

| Table 21. Test and Diagnostic Features                                                                   | 35 |

| Table 22. Typical Values for C <sub>COMP</sub>                                                           | 70 |

| Table 23. Control Range of SY88912 Modulation Control Circuit                                            | 71 |

| Table 24. Transistors Suitable for Use as Remote Diodes                                                  |    |

| Table 25. Contributors to Self-Heating                                                                   | 74 |

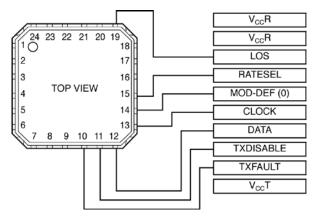

### **Pin Configuration**

### **Pin Description**

| Pin Number | Pin Name     | Pin Function                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB           | Analog Input. Feedback voltage for the APC loop op-amp. Polarity and scale are programmable via the APC configuration bits. Connect to $V_{BIAS}$ if APC is not used.                                                                                                                                                                                                                              |

| 2          | VMPD         | Analog Input. Multiplexed A/D converter input for monitoring transmitted optical power via a monitor photodiode. In most applications, VMPD will be connected directly to FB. The input range is 0 - $V_{REF}$ or 0 - $V_{REF}/4$ depending on the setting of the APC configuration bits                                                                                                           |

| 3          | GNDA         | Ground return for analog functions.                                                                                                                                                                                                                                                                                                                                                                |

| 4          | VDDA         | Power supply input for analog functions.                                                                                                                                                                                                                                                                                                                                                           |

| 5          | VILD-        | Analog Input. Reference terminal for the multiplexed pseudo-differential A/D converter inputs for monitoring laser bias current via a sense resistor (VILD+ is the sensing input). Tie to V <sub>DD</sub> or GND to reference the voltage sensed on VILD+ to V <sub>DD</sub> or GND                                                                                                                |

|            |              | respectively. Limited common-mode voltage range, see "Applications Information" section for more details.                                                                                                                                                                                                                                                                                          |

| 6          | VILD+        | Analog Input. Multiplexed A/D input for monitoring laser bias current via a sense resistor (signal input); accommodates inputs referenced to V <sub>DD</sub> or GND (see pin 5 description). Limited common-mode voltage range, see "Applications Information" section for more                                                                                                                    |

|            |              | details.                                                                                                                                                                                                                                                                                                                                                                                           |

| 7          | SHDN (TXFIN) | Digital output; Programmable polarity. When used as shutdown output (SHDN), asserted at the detection of a fault condition that can be used to activate a second series transistor in the laser current path, enhancing protection against single-point failures. When programmed as TXFIN, it is an input for external fault signals to be ORed with the internal fault sources to drive TXFAULT. |

| 8          | SHDN (TXFIN) | Analog Input. Multiplexed A/D converter input for monitoring received optical power. The input range is 0 to $V_{REF}$ . A 5-bit programmable EEPOT on this pin provides for coarse calibration and ranging of the RX power measurement.                                                                                                                                                           |

| 9          | XPN          | Analog Input/Output. Optional connection to an external PN junction for sensing temperature at a remote location. The Zone bit in OEMCFG1 determines whether temperature is measured using the on-chip sensor or the remote PN junction.                                                                                                                                                           |

| 10         | TXFAULT      | Digital Output; Open-Drain. A high level indicates a hardware fault impeding transmitter operation. The state of this input is always reflected in the TXFLT bit.                                                                                                                                                                                                                                  |

# **Pin Description**

| Pin Number | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | TXDISABLE   | Digital Input; Active High. The transmitter is disabled when this line is high or the STXDIS bit is set. The state of this input is always reflected in the TXDIS bit.                                                                                                                                                                                                                                                                                                           |

| 12         | DATA        | Digital I/O; Open-drain. Bi-directional serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13         | CLK         | Digital Input; Serial bit clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14         | VIN         | If bit 4 (IE) in USRCTL register is set to 0 (default), this pin is configured as analog input. If IE bit is set to 1, this pin is configured as open-drain output. Analog Input: Multiplexed A/D input for monitoring supply voltage. 0V to 5.5V input range. Open-drain output: outputs the internally generated interrupt signal /INT.                                                                                                                                        |

| 15         | RSIN        | Digital Input; Rate Select Input; ORed with rate select bit to determine the state of the RSOUT pin. The state of this pin is always reflected in the RSEL bit.                                                                                                                                                                                                                                                                                                                  |

| 16         | GNDD        | Ground return for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17         | NC          | No connection. This pin is used for test purposes and must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18         | VDDD        | Power supply input for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19         | RXLOS       | Digital Output; Active-High/Open-Drain. Indicates the loss of the received signal as indicated by a level of received optical power below the programmed RXLOS comparator threshold; may be wire-ORed with external signals. Low indicates normal operation. RXLOS is de-asserted when VRX > LOSFLTn. The LOS bit reflects the state of RXLOS whether driven by the MIC3001 or an external circuit.                                                                              |

| 20         | RSOUT (GPO) | Digital Output. Open-Drain or push-pull. When used as rate select output, this output is controlled by the SRSEL bit ORed with RSIN input and is open drain only. When used as a general-purpose, non-volatile output, it is controlled by the GPO configuration bits in OEMCFG3.                                                                                                                                                                                                |

| 21         | COMP        | Analog Output, compensation terminal. Connect a capacitor between this pin and GNDA or $V_{\mbox{DDA}}$ with appropriate value to tune the APC loop time constant to a desirable value.                                                                                                                                                                                                                                                                                          |

| 22         | VBIAS       | Analog Output. Buffered DAC output capable of sourcing or sinking up to 10mA under control of the APC function to drive an external transistor for laser diode D.C. bias. The output and feedback polarity are programmable to accommodate either a NPN or an PNP transistor to drive a common-anode or common-cathode laser diode.                                                                                                                                              |

| 23         | VMOD-       | Analog Input. Inverting terminal of VMOD buffer op-amp. Connect to $V_{MOD}$ + (gain = 1) or feedback resistors network to set a different gain                                                                                                                                                                                                                                                                                                                                  |

| 24         | VMOD+       | Analog Output. Buffered DAC output to set the modulation current on the laser driver IC. Operates with either a 0– $V_{REF}$ or a ( $V_{DD}-V_{REF}$ ) – $V_{DD}$ output swing so as to generate either a ground-referenced or a $V_{DD}$ referenced programmed voltage. A simple external circuit can be used to generate a programmable current for those drivers that require a current rather than a voltage input. See "Applications Information" section for more details. |

### Absolute Maximum Ratings<sup>(1)</sup>

| Power Supply Voltage, V <sub>DD</sub>          | +3.8V              |

|------------------------------------------------|--------------------|

| Voltage on CLK, DATA, TXFAULT, VIN, RXLOS      |                    |

| DISABLE, RSIN –0.3V to                         | o +6.0V            |

| Voltage On Any Other Pin0.3V to V <sub>D</sub> | <sub>D</sub> +0.3V |

| Power Dissipation, T <sub>A</sub> = 85°C       | 1.5W               |

| Junction Temperature (T <sub>J</sub> )         | . 150°C            |

| Storage Temperature (T <sub>S</sub> )65°C to   | +150°C             |

| ESD Ratings <sup>(3)</sup>                     |                    |

| Human Body Model                               | 2kV                |

| Machine Model                                  |                    |

| Soldering (20sec)                              |                    |

|                                                |                    |

# Operating Ratings<sup>(2)</sup>

Power Supply Voltage,  $V_{DDA}/V_{DDD}$  ..... +3.0V to +3.6V Ambient Temperature Range (T<sub>A</sub>) ... -40°C to +105°C Package Thermal Resistance

QFN (θ<sub>JA</sub>).....43°C/W

# **Electrical Characteristics**

For typical values,  $T_A = 25^{\circ}C$ ,  $V_{DDA} = V_{DDD} = +3.3V$ , unless otherwise noted. **Bold** values are guaranteed for  $+3.0V \le (V_{DDA} = V_{DDD}) \le 3.6V$ ,  $T_{(min)} \le T_A \le T_{(max)}^{(8)}$

| Symbol                            | Parameter                                | Condition                                                                                                                             | Min   | Тур   | Max       | Units |

|-----------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------|-------|

| Power Sup                         | ply                                      |                                                                                                                                       |       |       |           |       |

| I <sub>DD</sub>                   | Supply Current                           | CLK = DATA = $V_{DDD} = V_{DDA}$ ;<br>TXDISABLE low; all DACs at full-scale;<br>all A/D inputs at full-scale; all other pins<br>open. |       | 2.3   | 3.5       | mA    |

|                                   |                                          | $CLK = DATA = V_{DDD} = V_{DDA};$<br>TXDISABLE high; FLTDAC at full-scale;<br>all A/D inputs at full-scale; all other pins<br>open.   |       | 2.3   | 3.5       | mA    |

| V <sub>POR</sub>                  | Power-on Reset Voltage                   | All registers reset to default values;<br>A/D conversions initiated.                                                                  |       | 2.9   | 2.98      | V     |

| V <sub>UVLO</sub>                 | Under-Voltage Lockout Threshold          | Note 5                                                                                                                                | 2.5   | 2.73  |           | V     |

| V <sub>HYST</sub>                 | Power-on Reset Hysteresis Voltage        |                                                                                                                                       |       | 170   |           | mV    |

| t <sub>POR</sub>                  | Power-on Reset Time                      | $V_{DD} > V_{POR}^{(4)}$                                                                                                              |       | 50    |           | μs    |

| $V_{REF}$                         | Reference Voltage                        |                                                                                                                                       | 1.210 | 1.225 | 1.24<br>0 | V     |

| $\Delta V_{REF} / \Delta V_{DDA}$ | Voltage Reference Line Regulation        |                                                                                                                                       |       | 1.7   |           | mV/V  |

| Temperatu                         | re-to-Digital Converter Characteristic   | CS                                                                                                                                    |       |       |           |       |

|                                   | Local Temperature Measurement<br>Error   | $-40^{\circ}C \le T_{A} \le +105^{\circ}C^{(6)}$                                                                                      |       | ±1    | ±3        | °C    |

|                                   | Remote Temperature<br>Measurement Error  | $-40^{\circ}C \le T_{A} \le +105^{\circ}C^{(6)}$                                                                                      |       | ±1    | ±3        | °C    |

| t <sub>CONV</sub>                 | Conversion Time                          | Note 4                                                                                                                                |       |       | 60        | ms    |

| tSAMPLE                           | Sample Period                            |                                                                                                                                       |       |       | 100       | ms    |

| Remote Te                         | mperature Input, XPN                     |                                                                                                                                       |       |       |           |       |

| I <sub>F</sub>                    | Current to External Diode <sup>(4)</sup> | XPN at high level, clamped to 0.6V.                                                                                                   |       | 192   | 400       | μA    |

|                                   |                                          | XPN at low level, clamped to 0.6V.                                                                                                    | 7     | 12    |           | μA    |

### $\label{eq:Voltage-to-Digital Converter Characteristics} (V_{RX}, V_{AUX}, V_{BIAS}, V_{MPD}, V_{ILD} \pm)$

| Symbol              | Parameter                 | Condition                                        | Min | Тур | Max  | Units |

|---------------------|---------------------------|--------------------------------------------------|-----|-----|------|-------|

|                     | Voltage Measurement Error | $-40^{\circ}C \le T_{A} \le +105^{\circ}C^{(6)}$ |     | ±1  | ±2.0 | %fs   |

| t <sub>CONV</sub>   | Conversion Time           | Note 4                                           |     |     | 10   | ms    |

| t <sub>SAMPLE</sub> | Sample Period             | Note 4                                           |     |     | 100  | ms    |

#### Voltage Input, $V_{IN}$ (Pin 14 used as an ADC Input)

| V <sub>IN</sub>   | Input Voltage Range | $-0.3 \le V_{\text{DD}} \le 3.6 \text{V}$    | GNDA |    | 5.5 | V  |

|-------------------|---------------------|----------------------------------------------|------|----|-----|----|

| I <sub>LEAK</sub> | Input Current       | $V_{IN} = V_{DD}$ or GND; $V_{AUX} = V_{IN}$ |      | 55 |     | μA |

| C <sub>IN</sub>   | nput Capacitance    |                                              |      | 10 |     | pF |

### Digital-to-Voltage Converter Characteristics (V<sub>MOD</sub>, V<sub>BIAS</sub>)

|                   | Accuracy                         | $-40^{\circ}C \le T_{A} \le +105^{\circ}C^{(6)}$ | ±1   | 2.0 | %fs |

|-------------------|----------------------------------|--------------------------------------------------|------|-----|-----|

| t <sub>CONV</sub> | Conversion Time                  | Note 4                                           |      | 20  | ms  |

| DNL               | Differential Non-linearity Error | Note 4                                           | ±0.5 | ±1  | LSB |

#### Bias Current Sense Inputs, $V_{ILD}$ +, $V_{ILD}$ -

| V <sub>ILD</sub> | Differential Input Signal Range,<br>  V <sub>ILD</sub> + – V <sub>ILD</sub> - |                                                            | 0 |      | V <sub>REF</sub> /4 | mV |

|------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|---|------|---------------------|----|

| I <sub>IN+</sub> | V <sub>ILD</sub> + input current                                              |                                                            |   |      | ±1                  | μΑ |

| I <sub>IN-</sub> | V <sub>ILD</sub> <sup>-</sup> input current                                   | V <sub>ILD</sub> <sup>-</sup> referred to V <sub>DDA</sub> |   | +150 |                     | μA |

|                  | $ V_{ILD}^{+} - V_{ILD}^{-}  = 0.3V$                                          | V <sub>ILD</sub> <sup>-</sup> referred to GND              |   | -150 |                     | μΑ |

| C <sub>IN</sub>  | Input Capacitance                                                             |                                                            |   | 10   |                     | pF |

#### APC Op Amp, FB, V<sub>BIAS</sub>, COMP

| GBW                          | Gain Bandwidth Product                                         | C <sub>COMP</sub> = 20pF; Gain = 1         |                        | 1     |                  | MHz   |

|------------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------|-------|------------------|-------|

| $\mathrm{TC}_{\mathrm{VOS}}$ | Input Offset Voltage Temperature<br>Coefficient <sup>(4)</sup> |                                            |                        | 1     |                  | µV/°C |

| V <sub>OUT</sub>             | Output Voltage Swing                                           | I <sub>OUT</sub> = 10mA, SRCE bit = 1      | GNDA                   |       | 1.25             | V     |

|                              |                                                                | I <sub>OUT</sub> = -10mA, SRCE bit = 0     | V <sub>DDA</sub> -1.25 |       | V <sub>DDA</sub> | V     |

| I <sub>SC</sub>              | Output Short-Circuit Current                                   |                                            |                        | 55    |                  | mA    |

| t <sub>SC</sub>              | Short Circuit Withstand Time                                   | $T_{\rm J} \le 150^{\circ} {\rm C}^{(4)}$  |                        |       |                  | sec   |

| PSRR                         | Power Supply Rejection Ratio                                   | C <sub>COMP</sub> = 20pF; Gain = 1, to GND |                        | 55    |                  | dB    |

|                              |                                                                | $C_{COMP} = 20pF; Gain = 1, to V_{DD}$     |                        | 40    |                  |       |

| A <sub>MIN</sub>             | Minimum Stable Gain                                            | C <sub>COMP</sub> = 20pF, Note 4           |                        |       | 1                | V/V   |

| $\Delta V / \Delta t$        | Slew Rate                                                      | C <sub>COMP</sub> = 20pF; Gain = 1         |                        | 3     |                  | V/µs  |

| ΔRFB                         | Internal Feedback Resistor Tolerance                           |                                            |                        | ±20   |                  | %     |

| $\Delta RFB/\Delta t$        | Internal Feedback Resistor<br>Temperature Coefficient          |                                            |                        | 25    |                  | ppm/C |

| I <sub>START</sub>           | Laser Start-up Current Magnitude                               | START = 01 <sub>h</sub>                    |                        | 0.375 |                  | mA    |

|                              |                                                                | START = 02 <sub>h</sub>                    |                        | 0.750 |                  | mA    |

|                              |                                                                | START = 04 <sub>h</sub>                    |                        | 1.500 |                  | mA    |

|                              |                                                                | START = 08 <sub>h</sub>                    |                        | 3.000 |                  | mA    |

| C <sub>IN</sub>              | Pin Capacitance                                                |                                            |                        | 10    |                  | pF    |

### **Electrical Characteristics**

| Symbol                    | Parameter                                         | Condition                                 | Min                                | Тур  | Мах                   | Units    |

|---------------------------|---------------------------------------------------|-------------------------------------------|------------------------------------|------|-----------------------|----------|

| V <sub>MOD</sub> Buffe    | er Op-Amp, V <sub>MOD</sub> +, V <sub>MOD</sub> - | ·                                         |                                    |      |                       |          |

| GBW                       | Gain Bandwidth                                    | C <sub>COMP</sub> = 20pF; Gain = 1        |                                    | 1    |                       | MHz      |

| TC <sub>VOS</sub>         | Input Offset Voltage<br>Temperature Coefficient   |                                           |                                    | 1    |                       | µV/°C    |

| I <sub>BIAS</sub>         | V <sub>MOD</sub> - Input Current                  |                                           |                                    | ±0.1 | ±1                    | μA       |

| V <sub>OUT</sub>          | Output Voltage Swing                              | I <sub>OUT</sub> = ±1mA                   | GNDA+75                            |      | V <sub>DDA</sub> -75  | mV       |

| I <sub>SC</sub>           | Output Short-Circuit Current                      |                                           |                                    | 35   |                       | mA       |

| t <sub>SC</sub>           | Short Circuit Withstand Time                      | $T_{\rm J} \le 150^{\circ} {\rm C}^{(4)}$ |                                    |      |                       | sec      |

| PSRR                      | Power Supply Rejection Ratio                      | $C_{COMP} = 20pF; Gain = 1, to GND$       |                                    | 65   |                       | dB       |

|                           |                                                   | $C_{COMP} = 20pF; Gain = 1, to V_{DD}$    |                                    | 44   |                       | dB       |

| A <sub>MIN</sub>          | Minimum Stable Gain                               | C <sub>COMP</sub> = 20pF                  |                                    |      | 1                     | V/V      |

| $\Delta V / \Delta T$     | Slew Rate                                         | C <sub>COMP</sub> = 20pF; Gain = 1        |                                    | 1    |                       | V/µs     |

| C <sub>IN</sub>           | Pin Capacitance                                   |                                           |                                    | 10   |                       | pF       |

| Control and               | Status I/O, TXDISABLE, TXFAU                      | LT, RSIN, RSOUT(GPO), SHDN(TXI            | FIN), RXLOS, /                     | /INT | <u> </u>              | 1        |

| V <sub>IL</sub>           | Low Input Voltage                                 |                                           |                                    |      | 0.8                   | V        |

| V <sub>IH</sub>           | High Input Voltage                                |                                           | 2.0                                |      |                       | V        |

| V <sub>OL</sub>           | Low Output Voltage                                | I <sub>OL</sub> ≤ 3mA                     |                                    |      | 0.3                   | V        |

| V <sub>OH</sub>           | High Output Voltage<br>(applies to SHDN only)     | I <sub>OH</sub> ≤ 3mA                     |                                    |      | V <sub>DDD</sub> -0.3 | V        |

| I <sub>LEAK</sub>         | Input Current                                     |                                           |                                    |      | ±1                    | μA       |

| C <sub>IN</sub>           | Input Capacitance                                 |                                           |                                    | 10   |                       | pF       |

| Transmit Op               | otical Power Input, V <sub>MPD</sub>              |                                           | 1                                  |      | _1                    | I        |

| V <sub>IN</sub>           | Input Voltage Range                               | Note 4                                    | GNDA                               |      | V <sub>DDA</sub>      | V        |

| V <sub>RX</sub>           | Input Signal Range                                | BIASREF=0                                 |                                    |      | V <sub>REF</sub>      | V        |

|                           |                                                   | BIASREF=1                                 | V <sub>DDA</sub> -V <sub>REF</sub> |      | V <sub>DDA</sub>      | V        |

| C <sub>IN</sub>           | Input Capacitance                                 | Note 4                                    |                                    | 10   |                       | pF       |

| I <sub>LEAK</sub>         | Input Current                                     |                                           |                                    |      | ±1                    | μA       |

|                           | ptical Power Input, VRX, RXPOT                    |                                           |                                    |      | -1                    | <u> </u> |

|                           | Input Voltage Range                               | Note 4                                    | GNDA                               |      | V <sub>DDA</sub>      | V        |

| V <sub>RX</sub>           | Valid Input Signal Range<br>(ADC Input Range)     |                                           | 0                                  |      | V <sub>REF</sub>      | V        |

| R <sub>RXPOT(32)</sub>    | End-to-End Resistance                             | RXPOT = 1F <sub>h</sub>                   |                                    | 32   |                       | KΩ       |

| ∆RXPOT                    | Resistor Tolerance                                |                                           |                                    | ±20  |                       | %        |

| ∆RXPOT/∆T                 | Resistor Temperature<br>Coefficient               |                                           |                                    | 25   |                       | ppm/C    |

| $\Delta V_{RX} V_{RXPOT}$ | Divider Ratio Accuracy                            | $00 \le \text{RXPOT} \le 1\text{F}_{h}$   | -5                                 |      | +5                    | %        |

| I <sub>LEAK</sub>         | Input Current                                     | RXPOT = 0 (disconnected)                  |                                    |      | ±1                    | μA       |

| C <sub>IN</sub>           | Input Capacitance                                 | Note 4                                    |                                    | 10   | 1                     | pF       |

| I <sub>LEAK</sub>         | Input Current                                     |                                           |                                    |      | ±1                    | μA       |

### **Electrical Characteristics**

| Symbol                                 | Parameter                                                                                                                                   | Condition                                                                                                               | Min   | Тур | Max   | Units |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|--|--|

| Control and                            | Control and Status I/O Timing, TXFAULT, TXDISABLE, RSIN, RSOUT, and RXLOS                                                                   |                                                                                                                         |       |     |       |       |  |  |

| t <sub>OFF</sub>                       | TXDISABLE Assert Time                                                                                                                       | From input asserted to optical output at 10% of nominal, $C_{COMP} = 10nF$ .                                            |       |     | 10    | μs    |  |  |

| t <sub>ON</sub>                        | TXDISABLE De-assert Time       From input de-asserted to optical output at 90% of nominal, C <sub>COMP</sub> = 10nF.                        |                                                                                                                         |       |     |       | ms    |  |  |

| t <sub>INIT</sub>                      | Initialization Time                                                                                                                         | From power on or transmitter enabled<br>to optical output at 90% of nominal<br>and TX_FAULT de-asserted. <sup>(4)</sup> |       |     | 300   | ms    |  |  |

| t <sub>INIT2</sub>                     | Power-on Initialization Time                                                                                                                | From power on to APC loop enabled.                                                                                      |       |     | 200   | ms    |  |  |

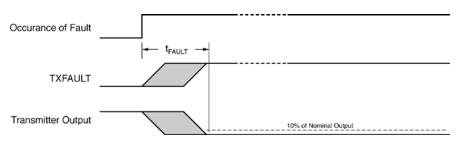

| t <sub>FAULT</sub> TXFAULT Assert Time |                                                                                                                                             | From fault condition to TXFAULT assertion. <sup>(4)</sup>                                                               |       |     | 95    | μs    |  |  |

| t <sub>RESET</sub>                     | Fault Reset Time                                                                                                                            | Length of time TXDISABLE must be asserted to reset fault condition.                                                     | 10    |     |       | μs    |  |  |

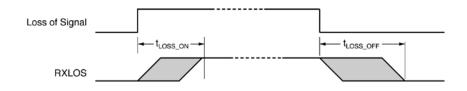

| t <sub>LOSS_ON</sub>                   | RXLOS Assert Time                                                                                                                           | From loss of signal to RXLOS asserted.                                                                                  |       |     | 95    | μs    |  |  |

| t <sub>LOSS_OFF</sub>                  | RXLOS De-assert Time                                                                                                                        | From signal acquisition to LOS de-<br>asserted.                                                                         |       |     | 100   | μs    |  |  |

| t <sub>DATA</sub>                      | Analog Parameter Data Ready                                                                                                                 | From power on to valid analog parameter data available. <sup>(4)</sup>                                                  |       |     | 400   | ms    |  |  |

| t <sub>PROP_IN</sub>                   | TXFAULT, TXDISABLE, RXLOS,<br>RSIN Input Propagation Time                                                                                   | Time from input change to corresponding internal register bit set or cleared. <sup>(4)</sup>                            |       |     | 1     | μs    |  |  |

| t <sub>PROP_OUT</sub>                  | UT TXFAULT, RSOUT, /INT Output Propagation Time From an internal register bit set or cleared to corresponding output change. <sup>(4)</sup> |                                                                                                                         |       |     | 1     | μs    |  |  |

| Fault Com                              | parators                                                                                                                                    | •                                                                                                                       | •     |     | •     | •     |  |  |

| $\phi_{FLTTMR}$                        | Fault Suppression Timer Clock<br>Period                                                                                                     | Note 4                                                                                                                  | 0.475 | 0.5 | 0.525 | ms    |  |  |

|                                        |                                                                                                                                             |                                                                                                                         | 2     |     |       |       |  |  |

|                     | Fellou                         |                                                                                 |     |    |    |        |

|---------------------|--------------------------------|---------------------------------------------------------------------------------|-----|----|----|--------|

|                     | Accuracy                       |                                                                                 | -3  |    | +3 | %/F.S. |

| t <sub>REJECT</sub> | Glitch Rejection               | Maximum length pulse that will not cause output to change state. <sup>(4)</sup> | 4.5 |    |    | μs     |

| V <sub>SAT</sub>    | Saturation Detection Threshold | High level                                                                      |     | 95 |    | %VDDA  |

|                     |                                | Low level                                                                       |     | 5  |    | %VDDA  |

#### Power-On Hour Meter

| Timebase Accuracy | $0^{\circ}C \le T_{A} \le +70^{\circ}C^{(4)}$ | +5  |    | -5  | %     |

|-------------------|-----------------------------------------------|-----|----|-----|-------|

|                   | $-40^{\circ}C \le T_A \le +105^{\circ}C$      | +10 |    | -10 | %     |

| Resolution        | Note 4                                        |     | 10 |     | hours |

#### Non-Volatile (FLASH) Memory

| t <sub>wR</sub> | Write Cycle Time(7)                      | From STOP of a one to four-byte write transaction.(4) |        | 13 | ms     |

|-----------------|------------------------------------------|-------------------------------------------------------|--------|----|--------|

|                 | Data Retention                           |                                                       | 100    |    | years  |

| Endurance       | Minimum Permitted Number<br>Write Cycles |                                                       | 10,000 |    | cycles |

V V µA pF

#### Serial Data I/O Pin, Data

| Symbol            | Parameter          | Condition             | Min | Тур | Max | Units |

|-------------------|--------------------|-----------------------|-----|-----|-----|-------|

| V <sub>OL</sub>   | Low Output Voltage | I <sub>OL</sub> = 3mA |     |     | 0.4 | V     |

|                   |                    | $I_{OL} = 6mA$        |     |     | 0.6 | V     |

| VIL               | Low Input Voltage  |                       |     |     | 0.8 | V     |

| VIH               | High Input Voltage |                       | 2.1 |     |     | V     |

| I <sub>LEAK</sub> | Input Current      |                       |     |     | ±1  | μA    |

| CIN               | Input Capacitance  | Note 4                |     | 10  |     | pF    |

| Serial Ciu        |                    |                            |     |    |     |   |  |  |

|-------------------|--------------------|----------------------------|-----|----|-----|---|--|--|

| VIL               | Low Input Voltage  | $2.7V \le V_{DD} \le 3.6V$ |     |    | 0.8 |   |  |  |

| V <sub>IH</sub>   | High Input Voltage | $2.7V \le V_{DD} \le 3.6V$ | 2.1 |    |     |   |  |  |

| I <sub>LEAK</sub> | Input Current      |                            |     |    | ±1  | ł |  |  |

| CIN               | Input Capacitance  | Note 4                     |     | 10 |     | ł |  |  |

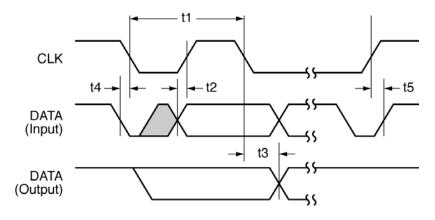

#### Serial Interface Timing<sup>(4)</sup>

|                   | 0                                     |                                                                                                        |     |     |    |

|-------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|----|

| t <sub>1</sub>    | CLK (clock) Period                    |                                                                                                        | 2.5 |     | μs |

| t <sub>2</sub>    | Data In Setup Time to CLK High        |                                                                                                        | 100 |     | ns |

| t <sub>3</sub>    | Data Out Stable After CLK Low         |                                                                                                        | 300 |     | ns |

| t <sub>4</sub>    | Data Low Setup Time to CLK<br>Low     | Start Condition                                                                                        | 100 |     | ns |

| t <sub>5</sub>    | Data High Hold Time After CLK<br>High | Stop Condition                                                                                         | 100 |     | ns |

| t <sub>DATA</sub> | Data Ready Time                       | From power on to completion of one set of ADC conversions; analog data available via serial interface. |     | 400 | ms |

Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling

- 4. precautions recommended.

- 5. Guaranteed by designing and/or testing of related parameters. Not 100% tested in production.

- The MIC3000 will attempt to enter its shutdown state when V<sub>DD</sub> falls below V<sub>UVLO</sub>. This operation requires time to complete. If the supply voltage falls too rapidly, the operation may not be completed.

- 7. Does not include quantization error.

- 8. The MIC3001 will not respond to serial bus transactions during an EEPROM write-cycle. The host will receive a NACK during twee

- 9. Final test on outgoing product is performed at  $T_A = +25^{\circ}C$ .

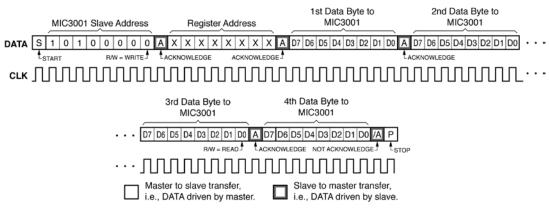

### **Timing Diagram**

Serial Interface Timing

### Address Map

| Address(s) | Field Size<br>(Bytes) | Name                         | Description                                                       |

|------------|-----------------------|------------------------------|-------------------------------------------------------------------|

| 0 –95      | 96                    | Serial ID defined by SEP MSA | G-P NVRAM; R/W under valid OEM password.                          |

| 96 – 127   | 32                    | Vendor Specific              | Vendor specific EEPROM                                            |

| 128 – 255  | 128                   | Reserved                     | Reserved for future use. G-P NVRAM; R/W under valid OEM password. |

#### Table 1. MIC3001 Address Map, Serial Address = A0<sub>h</sub>

| Address(s) Field Size |         |         |                                |                                                                                             |

|-----------------------|---------|---------|--------------------------------|---------------------------------------------------------------------------------------------|

| HEX                   | DEC     | (Bytes) | Name                           | Description                                                                                 |

| 00-27                 | 0-39    | 40      | Alarm and Warning<br>Threshold | High/low limits for warning and alarms; writeable using OEM p/w; read-only otherwise.       |

| 28-37                 | 40-55   | 16      | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 38-5B                 | 56-91   | 36      | Calibration Constants          | Numerical constants for external calibration; writeable using OEM p/w; read-only otherwise. |

| 5C-5E                 | 92-94   | 3       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 5F                    | 95      | 1       | Checksum                       | G-P NVRAM; writeable using OEM p/w; ready only otherwise.                                   |

| 60-69                 | 96-105  | 10      | Analog Data                    | Real time analog parameter data.                                                            |

| 6A-6D                 | 106-109 | 4       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 6E                    | 110     | 1       | Control/Status Bits            | Control and status bits.                                                                    |

| 6F                    | 111     | 1       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 70-71                 | 112-113 | 2       | Alarm Flags                    | Alarm status bits; read only.                                                               |

| 72-73                 | 114-115 | 2       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 74-75                 | 116-117 | 2       | Warning Flags                  | Warning status bits; read only.                                                             |

| 76-77                 | 118-119 | 2       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| 78-7B                 | 120-123 | 4       | OEMPW                          | OEM password entry field.                                                                   |

| 7C-7F                 | 124-127 | 4       | Vendor Specific                | Vendor specific. Reserved – do not write; reads undefined.                                  |

| 80-F7                 | 128-247 | 120     | User Scratchpad                | User writeable EEPROM. G-P NVRAM; R/W using any valid password.                             |

| F8-F9                 | 248-249 | 2       | Reserved                       | Reserved – do not write; reads undefined.                                                   |

| FA                    | 250     | 1       | USRPWSET                       | User password setting; read/write using any p/w; returns zero otherwise.                    |

| FB                    | 251     | 1       | USRPW                          | Entry field for user password.                                                              |

| FC-FD                 | 252-253 | 2       | РОН                            | Power-on hour meter result; ready only.                                                     |

| FE                    | 254     | 1       | Data Ready Flags               | Data ready bits for each measured parameter; read only.                                     |

| FF                    | 255     | 1       | User Control                   | End-user control and status bits.                                                           |

#### Table 2. MIC3001 Address Map, Serial Address = A2<sub>h</sub>

| Address(s) |         | Field Size |         |                                                                   |

|------------|---------|------------|---------|-------------------------------------------------------------------|

| HEX        | DEC     | (Bytes)    | Name    | Description                                                       |

| 00-3F      | 0-63    | 64         | APCLUTn | A.P.C temperature compensation L.U.T.                             |

| 40-7F      | 64-127  | 64         | MODLUTn | VMOD temperature compensation L.U.T.                              |

| 80-BF      | 128-191 | 64         | IFLTUT  | Bias current fault threshold temperature compensation L.U.T.      |

| C0-FF      | 192-255 | 64         | EOLLUTn | Bias current high alarm threshold temperature compensation L.U.T. |

#### Table 3. Temperature Compensation Tables, Serial Address = $A4_h$

| Address(s) |         | Field Size |          |                                                 |

|------------|---------|------------|----------|-------------------------------------------------|

| HEX        | DEC     | (Bytes)    | Name     | Description                                     |

| 00         | 0       | 40         | OEMCFG0  | Control/status bits                             |

| 01         | 1       | 16         | OEMCFG1  | Control/status bits                             |

| 02         | 2       | 36         | OEMCFG2  | Control/status bits                             |

| 03         | 3       | 3          | APCSET0  | APC setpoint 0                                  |

| 04         | 4       | 1          | APCSET1  | APC setpoint 1                                  |

| 05         | 5       | 10         | APCSET2  | APC setpoint 2                                  |

| 06         | 6       | 4          | MODSET   | Nominal modulation DAC setpoint                 |

| 07         | 7       | 1          | IBFLT    | Bias current fault-comparator threshold         |

| 08         | 8       | 1          | TXPFLT   | TX power fault threshold                        |

| 09         | 9       | 2          | LOSFLT   | RX LOS fault-comparator threshold               |

| 0A         | 10      | 2          | FLTTMR   | Fault comparator masking interval timer setting |

| 0B         | 11      | 2          | FLTMSK   | Fault source mask bits                          |

| 0C-0F      | 12-15   | 2          | OEMPWSET | Password for access to OEM areas                |

| 10         | 16      | 4          | OEMCAL0  | OEM calibration register 0                      |

| 11         | 17      | 4          | OEMCAL1  | OEM calibration register 1                      |

| 12         | 18      | 120        | LUTINDX  | Look-up table index read-back                   |

| 13         | 19      | 2          | RESERVED | Reserved – do not write; reads undefined.       |

| 14         | 20      | 1          | APCDAC   | Reads back current APC DAC setting              |

| 15         | 21      | 1          | MODDAC   | Reads back current modulation DAC setting       |

| 16         | 22      | 2          | OEMREAD  | Reads back OEM calibration data                 |

| 17         | 23      | 1          | LOSFLTn  | LOS De-assert threshold                         |

| 18         | 24      | 1          | RXPOT    | RXPOT tap selection                             |

| 19         | 25      | 1          | OEMCFG4  | I START selection bits                          |

| 1A-1F      | 26-31   | 6          | RESERVED | Reserved – do not write; reads undefined.       |

| 20-27      | 32-39   | 8          | POHDATA  | Power-on hour meter scratchpad                  |

| 28-47      | 40-71   | 32         | RXLUT    | RX power calibration look-up table              |

| 48-49      | 72-73   | 2          | RESERVED | Reserved – do not write; reads undefined.       |

| 4A-57      | 74-87   | 18         | CAL      | Internal calibration slope/offset data          |

| 59-7D      | 88-125  | 37         | RESERVED | Reserved – do not write; reads undefined.       |

| 7E-FD      | 126-253 | 128        | SCRATCH  | OEM scratchpad area                             |

| FE         | 254     | 1          | MFG_ID   | Manufacturer identification (Micrel = 42)       |

| FF         | 255     | 1          | DEV_ID   | Device and die revision                         |

Table 4. OEM Configuration Registers, Serial Address = A6<sub>h</sub>

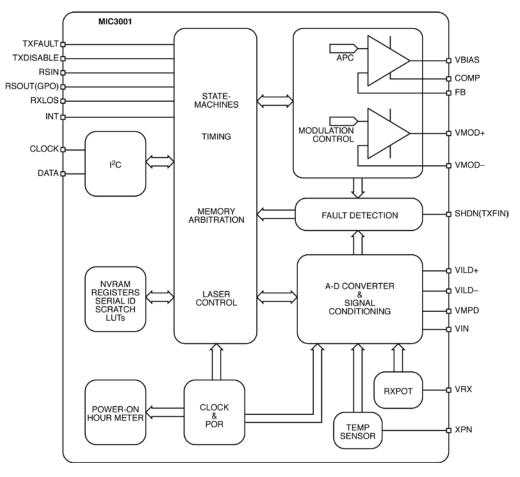

### **Block Diagram**

Figure 1. MIC3001 Block Diagram

### **MIC3000** Capability

In general, the MIC3001 is completely hardware and software backward compatible with the MIC3000. Every feature available in the MIC3000 is still present in the MIC3001. New features have, of course, been added. The following differences between the MIC3000 and MIC3001 would be evident to host software:

- 1. Faults do not set alarm or warning bits as in the MIC3000.

- RXOPI at register address 69<sub>h</sub> at serial address x2<sub>h</sub> now contains four bits of data rather then being fixed at zero as in the MIC3000.

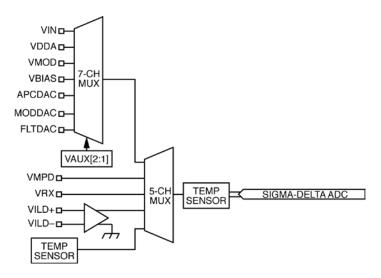

#### Analog-to-Digital Converter/Signal Monitoring

A block diagram of the monitoring circuit is shown below. Each of the five analog parameters monitored by the MIC3001 are sampled in sequence. All five parameters are sampled and the results updated within the  $t_{CONV}$  internal given in the "Electrical Characteristics" section. In OEM, Mode, the channel that is normally used to measure  $V_{IN}$  may be assigned to measure the level of the  $V_{DDA}$  pin or one of five other nodes. This provides a kind of analog loopback for debug and test purposes. The  $V_{AUX}$  bits in OEMCFG0 control which voltage source is being sampled. The various  $V_{AUX}$  channels are level-shifted differently depending on the signal source, resulting in different LSB values and signal ranges. See Table 5.

| Channel | ADC Resolution<br>(bits) | Conditions            | Input Range (V)                     | LSB <sup>(1)</sup> |

|---------|--------------------------|-----------------------|-------------------------------------|--------------------|

| TEMP    | 8                        |                       | N/A                                 | 1°C                |

| VAUX    | 8                        |                       | See Table 6                         |                    |

| VMPD    | 8                        | GAIN = 0; BIASREF = 0 | GNDA - V <sub>REF</sub>             | 4.77mV             |

|         |                          | GAIN = 0; BIASREF = 1 | $V_{DDA} - (V_{DDA} - V_{REF})$     |                    |

|         |                          | GAIN = 1; BIASREF = 0 | GNDA - V <sub>REF</sub> /4          | 1.17mV             |

|         |                          | GAIN = 1; BIASREF = 1 | $V_{DDA} - (V_{DDA} - V_{REF}^{4})$ |                    |

| VILD    | 8                        | VILD- = VDDA          | $V_{DDA} - (V_{DDA} - V_{REF})$     | 4.77mV             |

|         |                          | VILD- = GNDA          | GNDA - V <sub>REF</sub>             |                    |

| VRX     | 12                       | RXPOT = 00            | 0 - V <sub>REF</sub>                | 0.298mV            |

Table 5. A/D Input Signal Ranges and Resolutions

#### Note:

1. Assumes typical VREF value of 1.22V.

| Channel           | VAUX [2:0]      | Input Range (V)        | LSB <sup>(1)</sup> (mV) |

|-------------------|-----------------|------------------------|-------------------------|

| V <sub>IN</sub>   | $000 = 00_{h}$  | 0.5V to 5.5V           | 25.6mV                  |

| V <sub>DDA</sub>  | $0001 = 01_{h}$ | 0.5V to 5.5V           | 25.6mV                  |

| V <sub>BIAS</sub> | $010 = 02_{h}$  | 0.5V to 5.5V           | 25.6mV                  |

| V <sub>MOD</sub>  | $011 = 03_{h}$  | 0.5V to 5.5V           | 25.6mV                  |

| APCDAC            | $100 = 04_{h}$  | 0V to $V_{\text{REF}}$ | 4.77mV                  |

| MODDAC            | $101 = 05_{h}$  | 0V to V <sub>REF</sub> | 4.77mV                  |

| FLTDAC            | $110 = 06_{h}$  | 0V to $V_{\text{REF}}$ | 4.77mV                  |

#### Table 6. V<sub>AUX</sub> Input Signal Ranges and Resolutions

#### Note:

1. Assumes typical  $V_{\text{REF}}$  value of 1.22V.

#### Internal/External Calibration

The default mode of calibration in the MIC3001 is external calibration, for which INTCAL bit (bit 0 in OEMCF3 register) is set to 0. This mode is backward compatible with MIC3000. The internal calibration mode is selected by setting INTCAL bit to 1.

#### A/ External Calibration

The voltage and temperature values returned by the MIC3001's A/D converter are internally calibrated. The binary values of TEMPh:TEMPI and VOLTh:VOLTI are in the format called for by SFF-8472 under Internal Calibration.

SFF-8472 calls for a set of calibration constants to be stored by the transceiver OEM at specific non-volatile memory locations, refer to SFF-8472 specifications for memory map of calibration coefficient. The MIC3001 provides the non-volatile memory required for the storage of these constants. The Digital Diagnostic Monitoring Interface specification should be consulted for full details. Slopes and offsets are stored for use with voltage, temperature, bias current, and transmitted power measurements. Coefficients for a fourth-order polynomial are provided for use with received power measurements. The host system can retrieve these constants and use them to process the measured data. Since voltage and temperature require no calibration, the corresponding slopes should generally be set to unity and the offsets to zero.

#### Voltage

The voltage values returned by the MIC3001's A/D converter are internally calibrated. The binary values of VOLTh:VOLTI are in the format called for by SFF-8472 under Internal Calibration. Since VINh:VINI requires no processing, the corresponding slope should be set to unity and the offset to zero.

#### Temperature

The temperature values returned by the MIC3001's A/D converter are internally calibrated. The binary values of TEMPh:TEMPI are in the format called for by SFF-8472 under Internal Calibration. Since TEMPh:TEMPI requires no processing, the corresponding slope should be set to unity and the offset to zero.

#### Bias Current

Bias current is sensed via an external sense resistor as a voltage appearing at VILD+ and VILD-. The value returned by the A/D is therefore a voltage analogous to bias current. Bias current, IBIAS, is simply VVILD/R<sub>SENSE</sub>. The binary value in IBIASh (IBIASI is always zero) is related to bias current by:

$$I_{BIAS} = \frac{(0.300V) \left( \frac{IBIASh}{255} \right)}{R_{SENSE}}$$

(1)

The value of the least significant bit (LSB) of IBIASh is given by:

$$LSB(IBIASh) = \frac{0.300V}{255 \times R_{SENSE}} Amps = \frac{300mV}{255 \times R_{SENSE}} mA = \frac{11914}{R_{SENSE}} \mu A$$