## LCD Segment Driver series

# For 128~140 Segment type LCD

# **LCD Segment Driver**

# BU9728AKV, BU9795AKV/FV/GUW

## Outline

This is LCD segment driver for 126 to 140 segment type display. There is a lineup which is suitable for multi function display and is integrated display RAM and power supply circuit for LCD driving with 4 common output type: BU9728AKV and BU9795AKV/FV/GUW.

| 0 | 128Segment (SEG32×COM4) Driver | BU9728AKV        | ••••••P.1  |

|---|--------------------------------|------------------|------------|

| 0 | 140Segment (SEG35×COM4) Driver | BU9795AKV/FV/GUW | ••••••P.10 |

#### **BU9728AKV** 128Segment (SEG32×COM4) Driver

## • Feature (BU9728AKV)

- 1) 4wire serial interface (SCK, SD,  $\overline{C/D}$ ,  $\overline{CS}$ )

- 2) Integrated RAM for display data (DDRAM): 32 × 4bit (Max 128 Segment)

- 3) LCD driving port: 4 Common output, 32 Segment output

- 4) Display duty: 1/4 duty

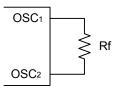

- 5) Integrated Oscillator circuit (external resister type)

- 6) Integrated Power supply circuit for LCD driving (1/3 bias)

- 7) Low voltage / low power consumption design: +2.5~5.5V

- Uses (BU9728AKV)

DVC, Car audio, Telephone

## Absolute Maximum Ratings (Ta=25degree, VSS=0V) (BU9728AKV)

| , aboolato maximani ratingo   |        |                 | 0001207 |                                                         |  |  |

|-------------------------------|--------|-----------------|---------|---------------------------------------------------------|--|--|

| Parameter                     | Symbol | Limits          | Unit    | Remarks                                                 |  |  |

| Power Supply Voltage1         | VDD    | -0.3 ~ +7.0     | V       | Power supply                                            |  |  |

| Power Supply Voltage2         | VLCD   | -0.3 ~ +7.0     | V       | LCD drive voltage                                       |  |  |

| Allowable loss                | Pd     | 400             | mW      | When use more than Ta=25°C, subtract<br>4mW per degree. |  |  |

| Operational temperature range | Topr   | -40 ~ +85       | degree  |                                                         |  |  |

| Storage temperature range     | Tstg   | -55 ~ +125      | degree  |                                                         |  |  |

| Input voltage range           | VIN    | -0.3 to VDD+0.3 | V       |                                                         |  |  |

| Output voltage range          | VOUT   | -0.3 to VDD+0.3 | V       |                                                         |  |  |

|                               |        |                 |         |                                                         |  |  |

\*This product is not designed against radioactive ray.

## Recommend operating conditions (Ta=25degree, VSS=0V) (BU9728AKV)

| Parameter             | Symbol | MIN | TYP | MAX | Unit | Remarks          |

|-----------------------|--------|-----|-----|-----|------|------------------|

| Power Supply Voltage1 | VDD    | 2.5 | -   | 5.5 | V    |                  |

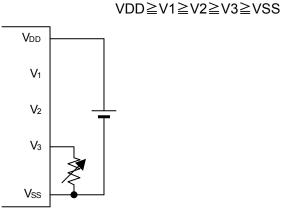

| Power Supply Voltage2 | VLCD   | 0   | -   | VDD | V    | VDD≧V1≧V2≧V3≧VSS |

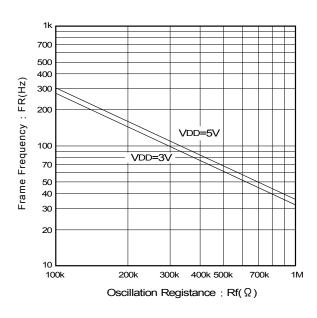

| Oscillator frequency  | fOSC   | -   | 36  | -   | KHz  | Rf=470kΩ         |

\*This document is not delivery specifications.

Jul. 2008

#### • Electrical Characteristics (BU9728AKV)

DC Characteristics (VDD=2.5~5.5V, VSS=0V, Ta=25degree, unless otherwise specified)

|                          | Symbo |         | Limit | •       | Uni | Condition                 | <b>-</b>                                                   |  |

|--------------------------|-------|---------|-------|---------|-----|---------------------------|------------------------------------------------------------|--|

| Parameter                | Î     | Min.    | Тур.  | Max.    | t   | Condition                 | Terminal                                                   |  |

| "H" level input voltage  | VIH1  | 0.8×VDD | -     | VDD     | V   | VO=0.9×VDD<br>or 0.1×VDD  | SC1, SD, SCK,                                              |  |

| "L" level input voltage  | VIL1  | 0       | -     | 0.2×VDD | V   | VO=0.1×VDD<br>or 0.9×VDD  | C/D, CS, RESET                                             |  |

| LCD Driver on resistance | RON   | -       | -     | 30      | kΩ  | ∆VON =0.1V                | SEG0~31, COM0~3                                            |  |

| "L" level Input current1 | IIL1  | -       | -     | 100     | μA  | VIN=0                     | RESET                                                      |  |

| "L" level Input current2 | IIL2  | -       | -     | 2       | μA  | VIN=0                     | $\frac{\text{OSC1, SD, SCK,}}{\text{C / D, } \text{ C S}}$ |  |

| "H" level Input current  | ΠΗ    | -2      | -     | -       | μA  | VIN=VDD                   | $\frac{OSC1, SD, SCK,}{C/D, CS, RESET}$                    |  |

| Input capacitance        | CI    | -       | 5     | -       | pF  |                           | SD, SCK, C / D, CS                                         |  |

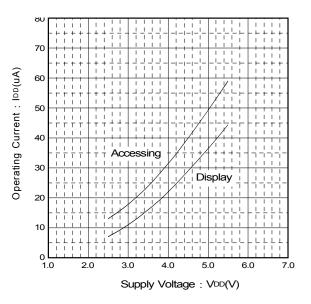

|                          |       | -       | 0.05  | 1       | μA  | <sup>*2</sup> Display OFF |                                                            |  |

| Power consumption        | IDD   | -       | 40    | 80      | μA  | *3 Display ON             | VDD                                                        |  |

|                          |       | -       | 100   | 250     | μA  | <sup>*4</sup> MPU Access  |                                                            |  |

\*1: LCD Driver on resistance is not included internal power supply impedance

\*2: V3=0V, All input terminal are connected to VDD or VSS.

\*3: V3=0V, Rf=470k $\Omega$ , except of OSC1 terminals are connected to VDD or VSS.

\*4: V3=0V, Rf=470kΩ, fSCK=200kHz

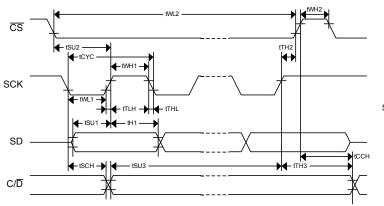

#### AC Characteristics (VDD=2.5~5.5V, VSS=0V, Ta=25degree, unless otherwise specified)

| Parameter             | Symbo |      | Limit |      | Unit | Condition                                 |  |

|-----------------------|-------|------|-------|------|------|-------------------------------------------|--|

| Falametei             | Î.    | Min. | Тур.  | Max. | Unit | Condition                                 |  |

| SCK rise time         | tTLH  | -    | -     | 100  | ns   |                                           |  |

| SCK fall time         | tTHL  | -    | -     | 100  | ns   |                                           |  |

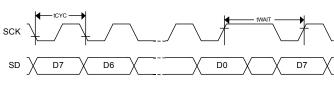

| SCK cycle time        | tCYC  | 800  | -     | -    | ns   |                                           |  |

| Wait time for command | tWAIT | 800  | -     | -    | ns   |                                           |  |

| SCK pulse width "H"   | tWH1  | 300  | -     | -    | ns   |                                           |  |

| SCK pulse width "L"   | tWL1  | 300  | -     | -    | ns   |                                           |  |

| SD setup time         | tSU1  | 100  | -     | -    | ns   |                                           |  |

| SD hold time          | tH1   | 100  | -     | -    | ns   |                                           |  |

| CS pulse width "H"    | tWH2  | 300  | -     | -    | ns   |                                           |  |

| CS pulse width "L"    | tWL2  | 6400 | -     | -    | ns   |                                           |  |

| CS setup time         | tSU2  | 100  | -     | -    | ns   |                                           |  |

| CS hold time          | tH2   | 100  | -     | -    | ns   |                                           |  |

| C/D setup time        | tSU3  | 100  | -     | -    | ns   |                                           |  |

| C/D hold time         | tH3   | 100  | -     | -    | ns   | Based on SCK 8 <sup>th</sup> clock rising |  |

| C/D – CS time *5      | tCCH  | 100  | -     | -    | ns   | Based on CS rising                        |  |

| C/D – SCK time *5     | tSCH  | 100  | -     | -    | ns   | Based o SCK 8 <sup>th</sup> clock falling |  |

\*5: Should satisfy either one condition

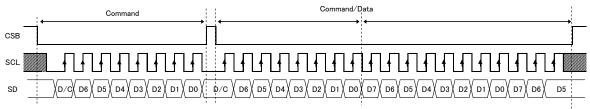

Fig. BU9728AKV-1 Interface timing

Reference data (BU9728AKV)

Fig. BU9728AKV-2 Command cycle

Fig. BU9728AKV-3 Frame frequency vs. Resister value

Fig. BU9728AKV-4 Power consumption vs. Power supply

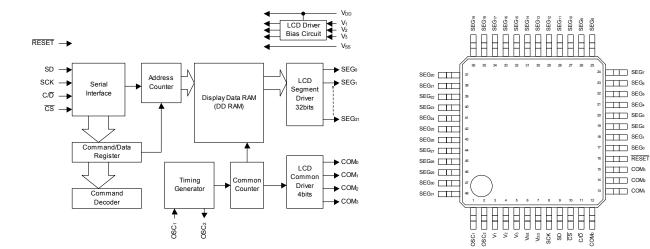

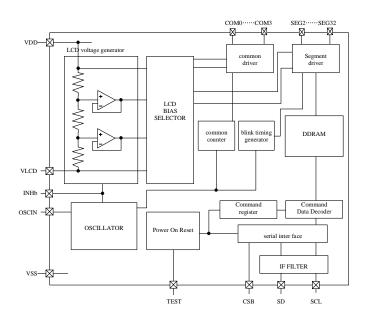

Block Diagram (BU9728AKV)

•Pin Arrangement (BU9728AKV)

Fig. BU9728AKV-5 Block diagram arrangement

Fig. BU9728AKV-6 Pin

## Terminal description (BU9728AKV)

| Terminal    | No.   | Туре | Function                                                                                                                |  |  |  |  |  |  |

|-------------|-------|------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

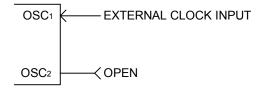

| OSC1        | 1     | I    | Int clock use mode, connect resister between OSC1 and OSC2.                                                             |  |  |  |  |  |  |

| OSC2        | 2     | 0    | Ext clock use mode, input clock from OSC1, OSC2 keep OPEN.                                                              |  |  |  |  |  |  |

| V1~V3       | 3~5   |      | Power supply for LCD driving.<br>Keep $VDD \ge V1 \ge V2 \ge V3 \ge VSS$ condition.                                     |  |  |  |  |  |  |

| VSS         | 6     |      | VSS terminal                                                                                                            |  |  |  |  |  |  |

| VDD         | 7     |      | VDD terminal                                                                                                            |  |  |  |  |  |  |

| SCK         | 8     | I    | Serial clock input                                                                                                      |  |  |  |  |  |  |

| SD          | 9     | I    | Serial data input                                                                                                       |  |  |  |  |  |  |

| CS          | 10    | I    | Chip select input "L": active                                                                                           |  |  |  |  |  |  |

| C/D         | 11    | I    | Command data judgment input<br>"L": display data, "H": command                                                          |  |  |  |  |  |  |

| COM0~3      | 12~15 | О    | LCD COMMON output                                                                                                       |  |  |  |  |  |  |

| RESET       | 16    | I    | Reset input terminal.<br>It will be initialized with "L" level input.<br>Reset address counter, Set display off status. |  |  |  |  |  |  |

| SEG0~<br>31 | 17~48 | Ο    | LCD SEGMENT output                                                                                                      |  |  |  |  |  |  |

Block Description (BU9728AKV)

## ○ ADDRESS COUNTER

An address counter shows the address of DDRAM. Address data are transferred to the address counter automatically when an address set is written in the command/data register.

After data are written in DDRAM, +1 or +2 is done automatically with an address counter. The choice of +1 or +2 is done automatically by the next condition.

DDRAM 8bit writing (in the 8 clock of SCK, C/ $\overline{D}$ = "L")  $\rightarrow$  +2

DDRAM 4bit rewriting (in the 8 clock of SCK, C/D= "H")  $\rightarrow$  +1

And, when it is counted to 1FH, an address becomes 00H with an address counter by the next count up.

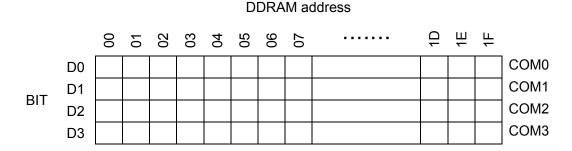

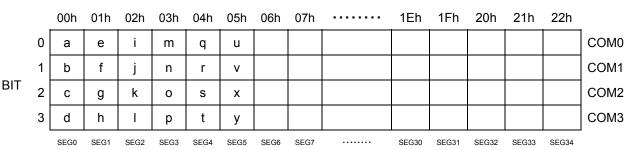

#### O DISPLAY DATA RAM (DDRAM)

A display data RAM (DDRAM) is used to store display data. That capacity is 32 address × 4 bits. DDRAM and the relations of the display position are as the following.

## ○ TIMING GENERATER

It will be started to oscillate by connecting Rf between OSC1, OSC2, and generated display timing signal. Also it will be able to do by external clock input.

(It is possible that Oscillating Frequency is changed with Rf. )

Fig. BU9728AKV-7 Rf Oscillator Circuit

Fig. BU9728AKV-8 External Clock Input

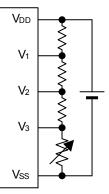

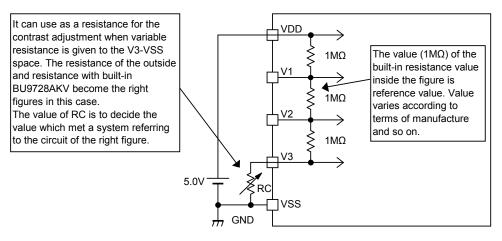

## ○ LCD DRIVE POWER SUPPLY

LCD drive power supply occurs by BU9728AKV. LCD voltage is given by VDD- V3, and it causes V1=2·VLCD/3, V2=VLCD/3. When input LCD power supply by using external breeder register etc.

Please keep below condition.

Fig. BU9728AKV-9 Internal Power supply use

Fig. BU9728AKV-10 External Power supply use

### • DETAIL OF COMMANDS (BU9728AKV)

There is the following thing in the command (The 8×n clock of SCK is C/D= "H".) of BU9728AKV.

|                         | S SET  | -       |          |         |         |         |        |         |                                                   |

|-------------------------|--------|---------|----------|---------|---------|---------|--------|---------|---------------------------------------------------|

|                         | MSB    |         |          |         |         |         |        |         | LSB                                               |

|                         | 0      | 0       | 0        | Α       | Α       | А       | А      | А       |                                                   |

|                         |        |         |          |         | •       | •       | •      |         | et on the address counter.<br>t) completes input. |

| O DISPLAY               | ON     |         |          |         |         |         |        |         |                                                   |

|                         | MSB    |         |          |         |         |         |        |         | LSB                                               |

|                         | 0      | 0       | 1        | *       | *       | *       | *      | *       |                                                   |

|                         |        |         |          |         |         |         |        |         | *:Don't Care                                      |

|                         |        |         |          |         |         |         | -      | -       | ta RAM (DDRAM).<br>DDRAM don't change.            |

| O DISPLAY               | OFF    |         |          |         |         |         |        |         |                                                   |

|                         | MSB    |         |          |         |         |         |        |         | LSB                                               |

|                         | 0      | 1       | 0        | *       | *       | *       | *      | *       |                                                   |

|                         |        |         |          |         |         |         |        |         | *:Don't Care                                      |

| There and<br>In this ca |        |         |          |         |         |         | -      | -       | ta RAM (DDRAM).                                   |

| O DISPLAY               | STAR   | T       |          |         |         |         |        |         |                                                   |

|                         | MSB    | 5       | 1        |         | 1       | 1       | 1      | 1       | LSB                                               |

|                         | 0      | 1       | 1        | *       | *       | *       | *      | *       |                                                   |

|                         |        |         |          |         |         |         |        |         | *:Don't Care                                      |

| It will be              | starte | ed to o | scillate | e and t | to disp | olay in | accord | dance   | with the contents of DDRAM.                       |

|                         | NG O   | F THE   | DISP     | LAY D   | ATA F   | ram (e  | DRA    | M)      |                                                   |

|                         | MSB    |         |          |         |         | ,       |        |         | LSB                                               |

|                         | 1      | 0       | 0        | *       | D       | D       | D      | D       | ]                                                 |

|                         |        |         |          |         |         |         |        |         | :Don't Care                                       |

| -                       | addre  | ess is  | addre    | ss ord  | ered b  | y the a | addres | s set o | command.<br>s + 1 automatically.                  |

| ○ RESET                 |        |         |          |         |         |         |        |         |                                                   |

|                         | MSB    |         |          |         | 1       |         |        |         | LSB                                               |

|                         | 1      | 1       | 0        | *       | *       | *       | *      | *       |                                                   |

|                         |        |         |          |         |         |         |        |         | *:Don't Care                                      |

Please execute this command first after Power on. It will be initialized as follow conditions;

- Display OFF

- Address counter reset

## Recommendation circuit example (BU9728AKV)

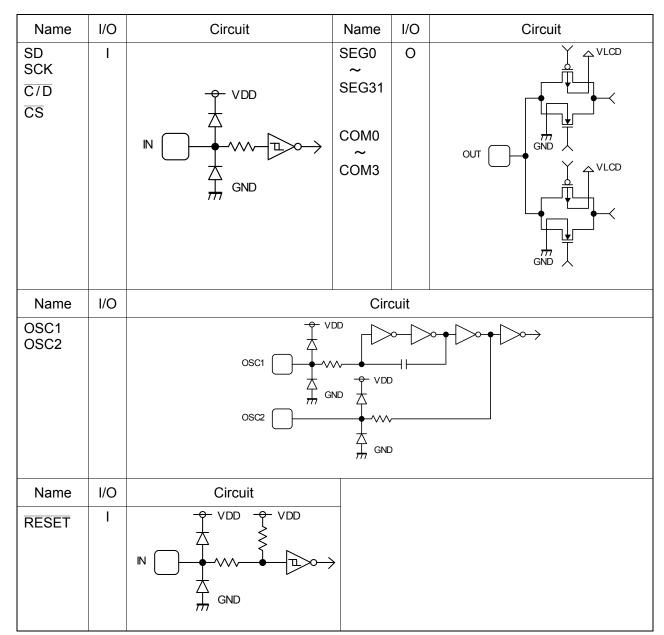

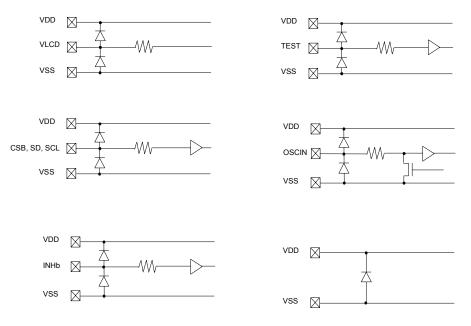

## INPUT OUTPUT CIRCUIT (BU9728AKV)

Fig. BU9728AKV-14 INPUT OUTPUT circuit

#### Cautions on use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines. In this regard, or the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner. Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

#### (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) No Connecting input terminals

In terms of extremely high impedance of CMOS gate, to open the input terminals causes unstable state. And unstable state brings the inside gate voltage of p-channel or n-channel transistor into active. As a result, battery current may increase. And unstable state can also causes unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or GND line.

#### (13) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special condition to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

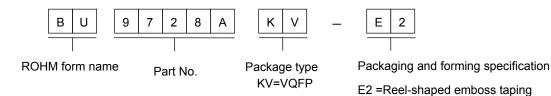

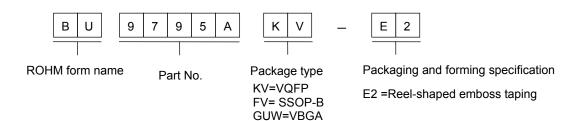

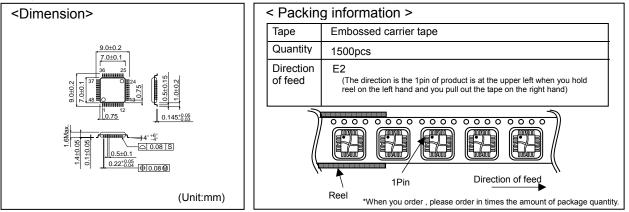

#### Order form name selection

## VQFP48C

# BU9795AKV/FV/GUW

MAX140Segment (SEG35×COM4) Driver

- Feature (BU9795AKV/AFV/AGUW)

- 1) 3wire serial interface (CSB, SD, SCL)

- 2) Integrated RAM for display data (DDRAM): 35 × 4bit (Max 140 Segment)

- 3) LCD driving port: 4 Common output, Segment: 35output (BU9795AKV), 31output (BU9795AGUW), 27output (BU9795AFV)

- 4) Display duty: 1/4 duty

- 5) Integrated Buffer AMP for LCD driving power supply

- 6) 1/2bias, 1/3bias selectable

- 7) No external components

- 8) Low power/ Ultra low power consumption design: +2.5~5.5V

- Uses (BU9795AKV/AFV/AGUW)

Telephone, FAX, Portable equipment (POS, ECR, PDA etc.), DSC, DVC, Car audio, Home electrical appliance, Meter equipment etc.

• Line-up

| Parameter      | BU9795AKV | BU9795AFV | BU9795AGUW |

|----------------|-----------|-----------|------------|

| Segment output | 35        | 27        | 31         |

| Common output  | 4         | 4         | 4          |

| Package        | VQFP48C   | SSOP-B40  | VBGA48W040 |

#### • Absolute Maximum Ratings (Ta=25degree, VSS=0V) (BU9795AKV/AFV/AGUW)

|                               | <u> </u> |                   |        |                                                                    |  |  |  |

|-------------------------------|----------|-------------------|--------|--------------------------------------------------------------------|--|--|--|

| Parameter                     | Symbol   | Limits            | Unit   | Remark                                                             |  |  |  |

| Power supply voltage1         | VDD      | -0.5 ~ +7.0       | V      | Power supply                                                       |  |  |  |

| Power supply voltage2         | VLCD     | -0.5 ~ VDD        | V      | LCD drive voltage                                                  |  |  |  |

|                               |          | 0.6               | W      | When use more than Ta=25°C, subtract 6mW per degree.(BU9795AKV)    |  |  |  |

| Allowable loss                | Pd       | 0.7               | W      | When use more than Ta=25°C, subtract 7mW per degree (BU9795AFV)    |  |  |  |

|                               |          | 0.27              | W      | When use more than Ta=25°C, subtract 2.7mW per degree (BU9795AGUW) |  |  |  |

| Input voltage range           | VIN      | -0.5 ~<br>VDD+0.5 | V      |                                                                    |  |  |  |

| Operational temperature range | Topr     | -40 ~ +85         | degree |                                                                    |  |  |  |

| Storage temperature range     | Tstg     | -55 ~ +125        | degree |                                                                    |  |  |  |

\*This product is not designed against radioactive ray.

• Recommend operating conditions (Ta=25degree,VSS=0V) (BU9795AKV/AFV/AGUW)

| Parameter             | Symbol | Min. | Тур. | Max.    | Unit | Remark            |  |  |  |

|-----------------------|--------|------|------|---------|------|-------------------|--|--|--|

| Power Supply voltage1 | VDD    | 2.5  | -    | 5.5     | V    | Power supply      |  |  |  |

| Power Supply voltage2 | VLCD   | 0    | -    | VDD-2.4 | V    | LCD drive voltage |  |  |  |

|                       |        |      |      |         |      |                   |  |  |  |

\* Please use VDD-VLCD $\geq$ 2.4V condition.

## • Electrical Characteristics(BU9795AKV/AFV/AGUW)

DC Characteristics (VDD=2.5~5.5V, VSS=0V, Ta=-40~85degree, unless otherwise specified)

| · · · · ·               | Symb  |        | Limit | <u>_</u> |      |                                                                            |

|-------------------------|-------|--------|-------|----------|------|----------------------------------------------------------------------------|

| Parameter               | ol    | MIN    | TYP   | MAX      | Unit | Condition                                                                  |

| "H" level input voltage | VIH   | 0.7VDD | -     | VDD      | V    |                                                                            |

| "L" level input voltage | VIL   | VSS    | -     | 0.3VDD   | V    |                                                                            |

| "H" level input current | IIH   | -      | -     | 1        | uA   |                                                                            |

| "L" level input current | IIL   | -1     | -     | -        | uA   |                                                                            |

| LCD Driver on SEG       | RON   | -      | 3.5   | -        | kΩ   | lload=±10uA                                                                |

| resistance COM          | I RON | -      | 3.5   | -        | kΩ   |                                                                            |

| VLCD supply voltage     | VLCD  | 0      | -     | VDD -2.4 | V    | VDD-VLCD≧2.5V                                                              |

| Standby current         | Ist   | -      | -     | 5        | uA   | Display off, Oscillator off                                                |

| Power consumption 1     | IDD1  | -      | 12.5  | 30       | uA   | VDD=3.3[V], Ta=25,<br>Power save mode1, FR=70Hz<br>1/3 bias, Frame inverse |

| Power consumption 2     | IDD2  | -      | 20    | 40       | uA   | VDD=3.3[V], Ta=25,<br>Normal mode, FR=80Hz<br>1/3 bias, Line inverse       |

Oscillation Characteristics (BU9795AKV/AFV/AGUW)

## (VDD=2.5~5.5V,VSS=0V, Ta=-40~85degree)

| Parameter             | Symb         |     | Limit |     | Unit | Condition          |

|-----------------------|--------------|-----|-------|-----|------|--------------------|

| Parameter             | ol           | MIN | TYP   | MAX | Unit | Condition          |

| Frame frequency       | <b>f</b> clk | 56  | 80    | 104 | Hz   | FR = 80Hz setting  |

| rame frequency1 fclk1 |              | 70  | 80    | 90  | Hz   | VDD=3.5V, 25degree |

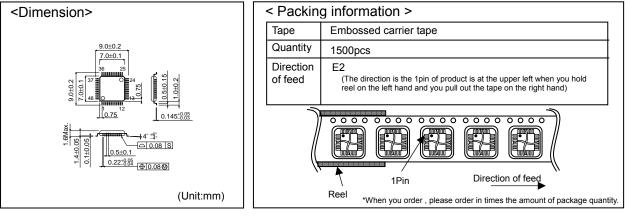

## • MPU interface Characteristics (BU9795AKV/AFV/AGUW)

(VDD=2.5V~5.5V,VSS=0V, Ta=-40~85degree)

| Parameter           | Symb | Limit |     |     | Linit | Condition |

|---------------------|------|-------|-----|-----|-------|-----------|

| Parameter           | ol   | MIN   | TYP | MAX | Unit  | Condition |

| Input rise time     | tr   | -     | -   | 80  | ns    |           |

| Input fall time     | tf   | -     | -   | 80  | ns    |           |

| SCL cycle time      | tSCY | 400   | -   | -   | ns    |           |

| "H" SCL pulse width | tSHW | 100   | -   | -   | ns    |           |

| "L" SCL pulse width | tSLW | 100   | -   | -   | ns    |           |

| SD setup time       | tSDS | 20    | -   | -   | ns    |           |

| SD hold time        | tSDH | 50    | -   | -   | ns    |           |

| CSB setup time      | tCSS | 50    | -   | -   | ns    |           |

| CSB hold time       | tCSH | 50    | -   | -   | ns    |           |

| "H" CSB pulse width | tCHW | 50    | -   | -   | ns    |           |

\* BU9795AKV

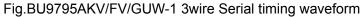

#### Block Diagram

Fig. BU9795AKV /AFV /AGUW-2A BU9795AKV Block diagram

• Terminal description

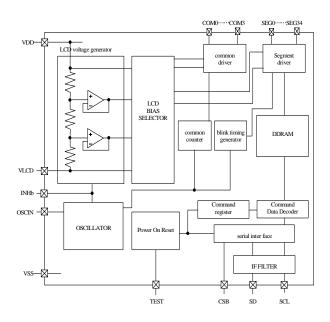

• Pin Arrangement

Fig. BU9795AKV /AFV /AGUW-3A BU9795AKV Pin arrangement

| Terminal | Terminal<br>No. | I/O | Function                                                                                                                                   |

|----------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| INHb     | 48              | Ι   | Input terminal for turn off display<br>H: turn on display L: turn off display                                                              |

| TEST     | 47              | Ι   | Test input (ROHM use only)<br>Must be connect to VSS                                                                                       |

| OSCIO    | 43              | Ι   | External clock input<br>Ex clock and Int clock can be changed by command.<br>Must be connect to VSS when use internal oscillation circuit. |

| SD       | 46              | Ι   | serial data input                                                                                                                          |

| SCL      | 45              | Ι   | serial data transfer clock                                                                                                                 |

| CSB      | 44              | Ι   | Chip select : "L" active                                                                                                                   |

| VSS      | 42              |     | GND                                                                                                                                        |

| VDD      | 41              |     | Power supply                                                                                                                               |

| VLCD     | 40              |     | Power supply for LCD driving                                                                                                               |

| SEG0-34  | 1-35            | 0   | SEGMENT output for LCD driving                                                                                                             |

| COM0-3   | 36-39           | 0   | COMMON output for LCD driving                                                                                                              |

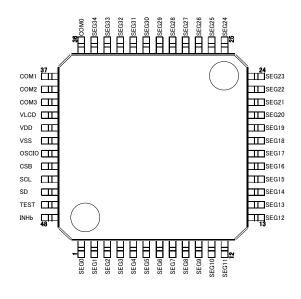

\* BU9795AFV • Block Diagram

#### ···сомз SEG4· ··seg30 COM0·· VDD-X LCD voltage generator common driver Segment LCD BIAS SELECTOR Гŀ blink timing generator common counter DDRAM [ŀ VLCD -INHb -Command Command Data Decoder OSCIN register OSCILLATOR Power On Reset serial inter face IF FILTER 肉 vss 肉 -肉 倅 TEST CSB SD SCL

Fig. BU9795AKV /AFV /AGUW-2B BU9795AFV Block diagram

## • Pin Arrangement

Fig. BU9795AKV /AFV /AGUW-3B BU9795AFV Pin arrangement

• Terminal description

| Terminal | Terminal<br>No. | I/O | Function                                                                                                                                   |

|----------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| INHb     | 36              | Ι   | Input terminal for turn off display<br>H: turn on display L: turn off display                                                              |

| TEST     | 35              | Ι   | Test input (ROHM use only)<br>Must be connect to VSS                                                                                       |

| OSCIO    | 31              | Ι   | External clock input<br>Ex clock and Int clock can be changed by command.<br>Must be connect to VSS when use internal oscillation circuit. |

| SD       | 34              | Ι   | serial data input                                                                                                                          |

| SCL      | 33              | Ι   | serial data transfer clock                                                                                                                 |

| CSB      | 32              | Ι   | Chip select : "L" active                                                                                                                   |

| VSS      | 30              |     | GND                                                                                                                                        |

| VDD      | 29              |     | Power supply                                                                                                                               |

| VLCD     | 28              | I   | Power supply for LCD driving                                                                                                               |

| SEG4-30  | 1-23,<br>37-40  | 0   | SEGMENT output for LCD driving                                                                                                             |

| COM0-3   | 24-27           | 0   | COMMON output for LCD driving                                                                                                              |

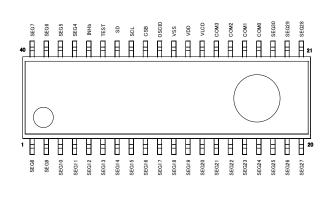

\* BU9795AGUW

## Block Diagram

Fig. BU9795AKV /AFV /AGUW-2C BU9795AGUW Block diagram

## • Pin Arrangement

|   | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

|---|-------|-------|-------|-------|-------|-------|-------|

| G | (NC)  | SEG13 | SEG15 | SEG18 | SEG20 | SEG22 | (NC)  |

| F | SEG11 | SEG12 | SEG16 | SEG17 | SEG21 | SEG23 | SEG24 |

| E | SEG9  | SEG10 | SEG14 | SEG19 | SEG25 | SEG27 | SEG26 |

| D | SEG7  | SEG6  | SEG8  | SEG5  | SEG30 | SEG28 | SEG29 |

| С | SEG4  | SEG3  | SEG2  | CSB   | сомз  | SEG32 | SEG31 |

| в | imes  | INHb  | SD    | VSS   | VDD   | COM1  | СОМО  |

| A | (NC)  | TEST2 | SCL   | oscio | VLCD  | COM2  | (NC)  |

#### Fig. BU9795AKV /AFV /AGUW-3C BU9795AGUW Pin arrangement

• Terminal description

| Terminal | I/O | Function                                                                                                                                   |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| INHb     | Ι   | Input terminal for turn off display<br>H: turn on display L: turn off display                                                              |

| TEST     | Ι   | Test input (ROHM use only)<br>Must be connect to VSS                                                                                       |

| OSCIO    | Ι   | External clock input<br>Ex clock and Int clock can be changed by command.<br>Must be connect to VSS when use internal oscillation circuit. |

| SD       | Ι   | serial data input                                                                                                                          |

| SCL      | Ι   | serial data transfer clock                                                                                                                 |

| CSB      | Ι   | Chip select : "L" active                                                                                                                   |

| VSS      |     | GND                                                                                                                                        |

| VDD      |     | Power supply                                                                                                                               |

| VLCD     | Ι   | Power supply for LCD driving                                                                                                               |

| SEG2-32  | 0   | SEGMENT output for LCD driving                                                                                                             |

| COM0-3   | 0   | COMMON output for LCD driving                                                                                                              |

(Caution) About terminal number, please refer to above pin arrangement

• Command Description (BU9795AKV/AFV/AGUW)

D7 (MSB) is bit for command or data judgment. Refer to Command and data transfer method.

### C: 0: Next byte is RAM write data.

1: Next byte is command.

### $\circ$ Mode Set (MODE SET)

| MSB |    |    |    |    |    |    | LSB |                |

|-----|----|----|----|----|----|----|-----|----------------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |                |

| С   | 1  | 0  | *  | P3 | P2 | *  | *   | (*:Don't care) |

## Set display ON and OFF

| Setting               | P3 | Reset initialize condition |

|-----------------------|----|----------------------------|

| Display OFF (DISPOFF) | 0  | 0                          |

| Display ON (DISPON)   | 1  |                            |

#### Set bias level

| Setting  | P2 | Reset initialize condition |

|----------|----|----------------------------|

| 1/3 Bias | 0  | 0                          |

| 1/2 Bias | 1  |                            |

#### • Address set (ADSET)

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| С   | 0  | 0  | P4 | P3 | P2 | P1 | P0  |

Address data is specified in P[4:0] and P2 (ICSET command) as follows.

|                     |             | LSB         |       |             |

|---------------------|-------------|-------------|-------|-------------|

| Internal register   | Address [5] | Address [4] | • • • | Address [0] |

| Bit of each command | ICSET [P2]  | ADSET [P4]  | • • • | ADSET [P0]  |

## • Display control (DISCTL)

| MSB |   |   |    |    |    |    | LSB |

|-----|---|---|----|----|----|----|-----|

|     |   |   |    |    |    |    | D0  |

| С   | 0 | 1 | P4 | P3 | P2 | P1 | P0  |

## Set Frame frequency

| Setting | P4 | P3 | Reset initialize condition |

|---------|----|----|----------------------------|

| 80Hz    | 0  | 0  | 0                          |

| 71Hz    | 0  | 1  |                            |

| 64Hz    | 1  | 0  |                            |

| 53Hz    | 1  | 1  |                            |

#### Set LCD drive waveform

| Setting         | P2 | Reset initialize condition |

|-----------------|----|----------------------------|

| Line inversion  | 0  | 0                          |

| Frame inversion | 1  |                            |

#### Set Power save mode

| Setting           | P1 | P0 | Reset initialize condition |

|-------------------|----|----|----------------------------|

| Power save mode 1 | 0  | 0  |                            |

| Power save mode 2 | 0  | 1  |                            |

| Normal mode       | 1  | 0  | 0                          |

| High power mode   | 1  | 1  |                            |

\* VDD-VLCD>=3.0V is required for High power mode.

## • Set IC Operation (ICSET)

| MSB | MSB |   |   |    |    |    |    |  |  |  |

|-----|-----|---|---|----|----|----|----|--|--|--|

| D7  |     |   |   | D3 |    |    |    |  |  |  |

| С   | 1   | 1 | 0 | 1  | P2 | P1 | P0 |  |  |  |

P2: MSB data of DDRAM address. Please refer to "ADSET" command.

| Setting        | P2 | Reset initialize condition |

|----------------|----|----------------------------|

| Address MSB'0' | 0  | 0                          |

| Address MSB'1' | 1  |                            |

Set Software Reset condition

| Setting        | P1 |

|----------------|----|

| No operation   | 0  |

| Software Reset | 1  |

#### Switch between internal clock and external clock.

| Setting              | P0 | Reset initialize condition |

|----------------------|----|----------------------------|

| Internal clock       | 0  | 0                          |

| External clock input | 1  |                            |

• Blink control (BLKCTL)

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| С   | 1  | 1  | 1  | 0  | *  | P1 | P0  |

Set blink condition

| Setting | P1 | P0 | Reset initialize condition |

|---------|----|----|----------------------------|

| OFF     | 0  | 0  | 0                          |

| 0.5 Hz  | 0  | 1  |                            |

| 1 Hz    | 1  | 0  |                            |

| 2 Hz    | 1  | 1  |                            |

• All pixel control (APCTL)

| MSB |   |   |   |    |   |    | LSB |

|-----|---|---|---|----|---|----|-----|

| D7  |   |   |   | D3 |   |    | D0  |

| С   | 1 | 1 | 1 | 1  | 1 | P1 | P0  |

All display set ON. OFF

•

| Setting      | P1 | Reset initialize condition |

|--------------|----|----------------------------|

| Normal       | 0  | 0                          |

| All pixel ON | 1  |                            |

| Setting       | P0 | Reset initialize condition |

|---------------|----|----------------------------|

| Normal        | 0  | 0                          |

| All pixel OFF | 1  |                            |

- Function description (BU9795AKV/AFV/AGUW)

- Command and data transfer method

- o 3-SPI (3wire Serial interface)

This device is controlled by 3-wire signal (CSB, SCL, and SD). First, Interface counter is initialized with CSB="H", and CSB="L" makes SD and SCL input enable. The protocol of 3-SPI transfer is as follows. Each command starts with Command or Data judgment bit (D/C) as MSB data, and continuously in order of D6 to D0 are followed after CSB ="L". (Internal data is latched at the rising edge of SCL, it converted to 8bits parallel data at the falling edge of 8<sup>th</sup> CLK.)

D/C = "H" : Command D/C = "L" : Data Fig. BU9795AKV /AFV /AGUW-10 3-SPI Command/Data transfer format

$\circ \text{Write}$  display data and transfer method

\* BU9795AKV

This LSI have Display Data RAM (DDRAM) of 35×4=140bit.

The relationship between data input and display data, DDRAM data and address are as follows.

8 bit data will be stored in DDRAM. The address to be written is the address specified by Address set command, and the address is automatically incremented in every 4bit data.

Data can be continuously written in DDRAM by transmitting Data continuously. (When RAM data is written successively after writing RAM data to 22h (SEG34), the address is returned to 00h (SEG0) by the auto-increment function.

#### DDRAM address

As data transfer to DDRAM happens every 4bit data, it will be cancelled if it changes  $CSB="L" \rightarrow "H"$  before 4bits data transfer.

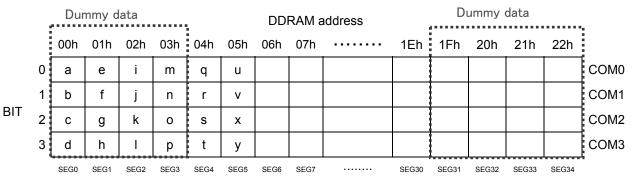

## \* BU9795AFV

As SEG0, SEG1, SEG2, SEG3, SEG31, SEG32, SEG33, SEG34 are not output, these address will be dummy address.

As data transfer to DDRAM happens every 4bit data, it will be cancelled if it changes  $CSB="L" \rightarrow "H"$  before 4bits data transfer.

## \* BU9795AGUW

As SEG0, SEG1, SEG33, SEG34 are not output, these address will be dummy address.

|        | Dummy data |      |      |      |      |      | DDRAM address |      |      |  |       | Dummy data |       |       |       |      |

|--------|------------|------|------|------|------|------|---------------|------|------|--|-------|------------|-------|-------|-------|------|

|        |            | 00h  | 01h  | 02h  | 03h  | 04h  | 05h           | 06h  | 07h  |  | 1Eh   | 1Fh        | 20h   | 21h   | 22h   |      |

| 0<br>1 | 0          | а    | е    | i    | m    | q    | u             |      |      |  |       |            |       |       |       | COM0 |

|        | 1          | b    | f    | j    | n    | r    | v             |      |      |  |       |            |       |       |       | COM1 |

| BIT    | 2          | с    | g    | k    | 0    | s    | х             |      |      |  |       |            |       |       |       | COM2 |

|        | 3          | d    | h    | I    | р    | t    | у             |      |      |  |       |            |       |       |       | СОМЗ |

|        |            | SEG0 | SEG1 | SEG2 | SEG3 | SEG4 | SEG5          | SEG6 | SEG7 |  | SEG30 | SEG31      | SEG32 | SEG33 | SEG34 | -    |

As data transfer to DDRAM happens every 4bit data, it will be cancelled if it changes  $CSB="L" \rightarrow "H"$  before 4bits data transfer.

## • Reset (initial) condition

Initial condition after execute Software Reset is as follows.

- · Display is OFF.

- DDRAM address is initialized (DDRAM Data is not initialized).

- Refer to Command Description about initialize value of register.

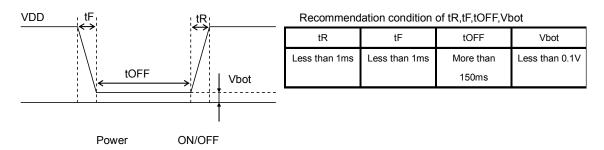

### • Cautions of Power-On condition (BU9795AKV /AFV /AGUW)

This LSI has "P.O.R" (Power-On Reset) circuit and Software Reset function. Please keep the following recommended Power-On conditions in order to power up properly.

1. Please set power up conditions to meet the recommended tR, tF, tOFF, and Vbot spec below in order to ensure P.O.R operation.

Fig. BU9795AKV /AFV /AGUW-18 Power on-off waveform

- If it is difficult to meet above conditions, execute the following sequence after Power-On. Because it doesn't accept the command in power off, it is necessary to care that correspondence by software reset doesn't become alternative to POR function completely.

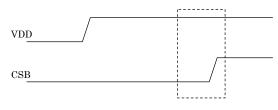

- (1) CSB="L" $\rightarrow$ "H" condition

Fig. BU9795AKV-19 CSB Timing

(2) After CSB"H" $\rightarrow$ "L", execute Software Reset (ICSET command).

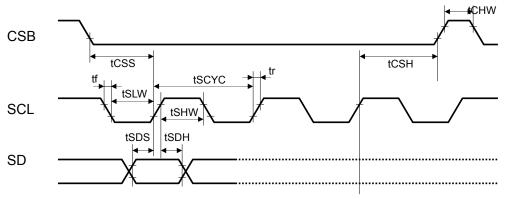

## ● IO Circuit (BU9795AKV /AFV /AGUW)

Fig. BU9795AKV /AFV /AGUW-20 IO circuit

#### Cautions on use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines. In this regard, or the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner. Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

#### (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) No Connecting input terminals

In terms of extremely high impedance of CMOS gate, to open the input terminals causes unstable state. And unstable state brings the inside gate voltage of p-channel or n-channel transistor into active. As a result, battery current may increase. And unstable state can also causes unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or GND line.

#### (13) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special condition to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

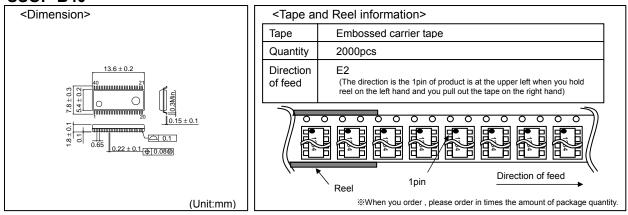

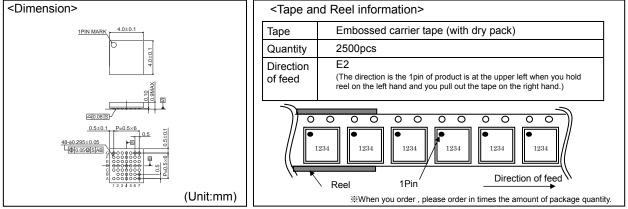

Order form name selection

## VQFP48C

## SSOP-B40

## VBGA048W040

The contents described herein are correct as of July, 2008

The products described herein utilize silicon as the main material. The products described herein are not designed to be X ray proof.

infringement, or arising from or connected with or related to the use of such devices.

proprietary rights owned or controlled by ROHM CO., LTD. is granted to any such buyer.

upon circuit constants in the set.

Excellence in Electronics

ROHM CO., LTD.

TEL: +81-75-311-2121 FAX: +81-75-315-0172

21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto

Published by KTC LSI Development Headquarters LSI Business Pomotion Group

URL http://www.rohm.com

615-8585, Japan

San Diego Atlanta

Boston Chicago Dallas

Denver

Munich

Stuttgart

Denmark

Barcelona

Hungary Poland

Russia

Seoul

Masan

Dalian

Beijing

Espoo

Salo

Oulu

France United Kingdom

Deriver Detroit Nashville Mexico Düsseldorf

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding

Any data, including, but not limited to application circuit diagrams and information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO. LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such

Oupon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, implied right or license to practice or commercially exploit any intellectual property rights or other

The products listed in this catalog are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment,

FAX: +1-858-625-3670 FAX: +1-770-754-0691 FAX: +1-928-438-7164

FAX: +1-847-368-1008

FAX: +1-469-362-7973

FAX: +1-469-362-7973 FAX: +1-303-708-0858 FAX: +1-248-348-9942 FAX: +1-615-620-6702 FAX: +52-33-3123-2002 FAX: +49-2154-921400

FAX: +49-899-216176

FAX: +49-711-72723720

FAX: +49-711-72723720 FAX: +33-1-5697-3080 FAX: +41-908-235788 FAX: +45-3694-4789 FAX: +358-9-7255-4499 FAX: +358-9-7232237

FAX: +358-8-5372931

FAX: +34-9375-24410 FAX: +34-5375-24410 FAX: +36-1-4719339 FAX: +48-22-5757001 FAX: +7-95-937-8290 FAX: +82-2-8182-715

FAX: +82-55-240-6236

TEL: +86-411-8230-8549 FAX: +86-411-8230-8537

TEL: +86-10-8525-2483 FAX: +86-10-8525-2489

TEL: +86-22-23029181 FAX: +86-22-23029183 TEL: +86-21-6279-2727 FAX: +86-21-6247-2066 TEL: +86-571-87658072 FAX: +86-571-87658071 TEL: +86-25-8689-0015 FAX: +86-25-8689-0393

TEL: +86-574-87654201 FAX: +86-574-87654208

TEL: +86-53/43/054201 FAX: +86-5/43/054208 TEL: +86-532-6779-312 TEL: +86-512-6807-1300 FAX: +86-512-6807-2300 TEL: +86-510-82702693 FAX: +86-510-82702992 TEL: +86-75-8307-3008 FAX: +86-755-8307-3003 TEL: +86-755-8307-3008 FAX: +86-755-8307-3003 TEL: +86-769-8393-3320 FAX: +86-769-8398-4140

TEL: +86-591-8801-8698 FAX: +86-591-8801-8690

FAX: +86-20-3825-5965

FAX: +86-752-205-1059 FAX: +86-752-205-1059 FAX: +86-756-3232-460 FAX: +852-2-375-8971

FAX: +886-2-2503-2869

FAX: +886-7-238-7332

FAX: +886-7-238-7332 FAX: +65-6332-5662 FAX: +63-2-809-1422 FAX: +66-2-256-6334 FAX: +60-3-7958-8377 FAX: +60-4-2286452 FAX: +81-75-365-1228

FAX: +81-45-476-2295

Catalog No.08T313A '08.7 ROHM ©

TEL: +86-591-8801-8698 TEL: +86-20-3878-8100 TEL: +86-752-205-1054 TEL: +86-592-238-5705 TEL: +86-756-3232-480 TEL: +852-2-740-6262

TEL: +886-2-2500-6956

TEL: +886-7-237-0881

TEL: +65-632-232 TEL: +65-632-2322 TEL: +63-2-807-6872 TEL: +66-2-254-4890 TEL: +60-3-7958-8355

TEL: +60-4-2286453 TEL: +81-75-365-1218

TEL: +81-45-476-2290

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers,

> Tianjin Shanghai Hangzhou

Nanjing Ningbo

Qingdao Suzhou

Fuzhou

Guangzhou Huizhou Xiamen Zhuhai

Hong Kong

Taipei Kaohsiung

Singapore Philippines Thailand

Kuala Lumpu

Penang

Yokohama

Kvoto

Wuxi Shenzhen Dongguan

office-automation equipment, communications devices, electrical appliances and electronic toys).

fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

TEL: +1-858-625-3630 TEL: +1-770-754-5972 TEL: +1-978-371-0382

TEL: +1-847-368-1006

TEL: +1-469-287-5366

TEL: +1-303-708-0908

TEL: +1-303-708-0908 TEL: +1-248-348-9920 TEL: +1-615-620-6700 TEL: +52-33-3123-2001 TEL: +49-2154-9210

TEL: +49-899-216168

TEL: +49-899-216168 TEL: +49-711-72723710 TEL: +43-1-5697-3060 TEL: +44-1-908-306700 TEL: +45-3694-4739 TEL: +558-9725-54491

TEL: +358-2-7332234

TEL: +358-8-5372930

TEL: +358-8-5372930 TEL: +34-9375-24320 TEL: +36-1-4719338 TEL: +48-22-5757213 TEL: +7-95-980-6755 TEL: +82-2-8182-700

TEL: +82-55-240-6234

Contact us for further information about the products.

- The contents described herein are subject to change without notice. For updates of the latest information, please contact and confirm with ROHM CO.,LTD. Any part of this application note must not be duplicated or copied without our permission.

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM CO.,LTD.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact your nearest sales office.

## ROHM Customer Support System

www.rohm.com

THE AMERICAS / EUROPE / ASIA / JAPAN

Contact us : webmaster@rohm.co.jp

Copyright © 2009 ROHM CO.,LTD.

ROHM Co., Ltd. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

TEL : +81-75-311-2121 FAX : +81-75-315-0172

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331