# **ANALOG DEVICES**

# 16-Bit, 10 MHz Bandwidth, 30 MSPS to 160 MSPS Continuous Time Sigma-Delta ADC

# AD9261

#### FEATURES

SNR: 83 dB (85 dBFS) to 10 MHz input SFDR: 87 dBc to 10 MHz input Noise figure: 15 dB Input impedance: 1 kΩ Power: 340 mW 1.8 V analog supply operation 1.8 V to 3.3 V output supply Selectable bandwidth 2.5 MHz/5 MHz/10 MHz Output data rate: 30 MSPS to 160 MSPS **Integrated decimation filters** Integrated sample rate converter **On-chip PLL clock multiplier On-chip voltage reference** Offset binary, Gray code, or twos complement data format Serial control interface (SPI)

#### **APPLICATIONS**

Data acquisition Automated test equipment Instrumentation Medical imaging

### **GENERAL DESCRIPTION**

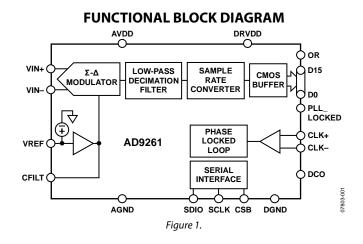

The AD9261 is a single 16-bit analog-to-digital converter (ADC) based on a continuous time (CT) sigma-delta ( $\Sigma$ - $\Delta$ ) architecture that achieves 87 dBc of dynamic range over a 10 MHz input bandwidth. The integrated features and characteristics unique to the continuous time  $\Sigma$ - $\Delta$  architecture significantly simplify its use and minimize the need for external components.

The AD9261 has a resistive input impedance that relaxes the requirements of the driver amplifier. In addition, a 32× oversampled fifth-order continuous time loop filter significantly attenuates out-of-band signals and aliases, reducing the need for external filters at the input.

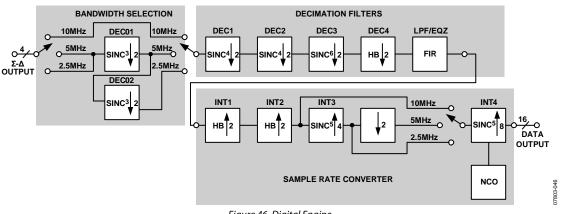

An external clock input or the integrated integer-N PLL provides the 640 MHz internal clock needed for the oversampled continuous time  $\Sigma$ - $\Delta$  modulator. On-chip decimation filters and sample rate converters reduce the modulator data rate from 640 MSPS to a user-defined output data rate from 30 MSPS to 160 MSPS, enabling a more efficient and direct interface.

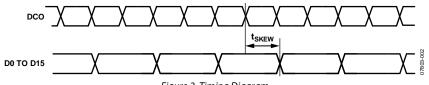

The digital output data is presented in offset binary, Gray code, or twos complement format. A data clock output (DCO) is provided to ensure proper timing with the receiving logic.

The AD9261 operates on a 1.8 V analog supply and a 1.8 V to 3.3 V digital supply, consuming 340 mW. The AD9261 is available in a 48-lead LFCSP and is specified over the industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C).

### **PRODUCT HIGHLIGHTS**

- 1. Continuous time  $\Sigma$ - $\Delta$  architecture efficiently achieves high dynamic range and wide bandwidth.

- 2. Passive input structure reduces or eliminates the requirements for a driver amplifier.

- 3. An oversampling ratio of 32× and high order loop filter provide excellent alias rejection reducing or eliminating the need for antialiasing filters.

- 4. An integrated decimation filter, sample rate converter, PLL clock multiplier, and voltage reference provide ease of use.

- 5. This part operates from a single 1.8 V analog power supply and 1.8 V to 3.3 V output supply.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2010 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram 1                   |

| General Description                          |

| Product Highlights 1                         |

| Revision History                             |

| Specifications                               |

| DC Specifications                            |

| AC Specifications                            |

| Digital Decimation Filtering Characteristics |

| Digital Specifications                       |

| Switching Specifications                     |

| Absolute Maximum Ratings7                    |

| Thermal Resistance                           |

| ESD Caution7                                 |

| Pin Configuration and Function Descriptions  |

| Typical Performance Characteristics | 9  |

|-------------------------------------|----|

| Equivalent Circuits                 | 13 |

| Theory of Operation                 | 14 |

| Analog Input Considerations         | 14 |

| Clock Input Considerations          | 16 |

| Power Dissipation and Standby Mode  | 18 |

| Digital Engine                      | 19 |

| Digital Outputs                     | 21 |

| Timing                              | 21 |

| Serial Port Interface (SPI)         | 23 |

| Configuration Using the SPI         | 23 |

| Hardware Interface                  | 24 |

| Memory Map                          | 25 |

| Memory Map Definitions              | 25 |

| Outline Dimensions                  | 27 |

| Ordering Guide                      | 27 |

### **REVISION HISTORY**

4/10—Revision 0: Initial Version

# **SPECIFICATIONS**

### DC SPECIFICATIONS

All power supplies set to 1.8 V, 640 MHz sample rate, 0.5 V internal reference, PLL disabled, 40 MSPS output data rate, AIN<sup>1</sup> = -2.0 dBFS, unless otherwise noted.

| Parameter                                   | Temp | Min | Тур      | Max   | Unit       |

|---------------------------------------------|------|-----|----------|-------|------------|

| RESOLUTION                                  | Full |     | 16       |       | Bits       |

| ANALOG INPUT BANDWIDTH                      |      |     |          | 10    | MHz        |

| ACCURACY                                    |      |     |          |       |            |

| No Missing Codes                            | Full |     | Guarante | ed    |            |

| Offset Error                                | Full |     | ±0.02    | ±0.15 | % FSR      |

| Gain Error                                  | Full |     | ±0.7     | ±3.0  | % FSR      |

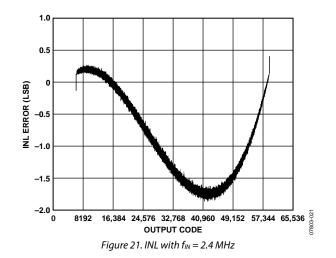

| Integral Nonlinearity (INL) <sup>2</sup>    | Full |     | ±1.5     |       | LSB        |

| TEMPERATURE DRIFT                           |      |     |          |       |            |

| Offset Error                                | Full |     | ±1.5     |       | ppm/°C     |

| Gain Error                                  | Full |     | ±50      |       | ppm/°C     |

| INTERNAL VOLTAGE REFERENCE                  |      | 490 | 500      | 510   | mV         |

| ANALOG INPUT                                |      |     |          |       |            |

| Input Span, VREF = 0.5 V                    | Full |     | 2        |       | V p-p diff |

| Common-Mode Voltage                         | Full | 1.7 | 1.8      | 1.9   | V          |

| Input Resistance                            | Full |     | 1        |       | kΩ         |

| POWER SUPPLIES                              |      |     |          |       |            |

| Supply Voltage                              |      |     |          |       |            |

| AVDD                                        | Full | 1.7 | 1.8      | 1.9   | V          |

| CVDD                                        | Full | 1.7 | 1.8      | 1.9   | V          |

| DVDD                                        | Full | 1.7 | 1.8      | 1.9   | V          |

| DRVDD                                       | Full | 1.7 | 1.8      | 3.6   | V          |

| Supply Current                              |      |     |          |       |            |

| AVDD <sup>2</sup>                           | Full |     | 74       | 83    | mA         |

| I <sub>CVDD</sub> <sup>2</sup> PLL Enabled  | Full |     | 57       | 654   | mA         |

| I <sub>CVDD</sub> <sup>2</sup> PLL Disabled | Full |     | 8.0      | 8.8   | mA         |

| lovdd <sup>2</sup>                          | Full |     | 100      | 108   | mA         |

| $I_{DRVDD}^2$ (1.8 V)                       | Full |     | 5.5      | 5.8   | mA         |

| I <sub>DRVDD</sub> <sup>2</sup> (3.3 V)     | Full |     | 10       |       | mA         |

| POWER CONSUMPTION                           |      |     |          |       |            |

| Sine Wave Input <sup>2</sup> PLL Disabled   | Full |     | 340      | 370   | mW         |

| Sine Wave Input <sup>2</sup> PLL Enabled    | Full |     | 425      | 465   | mW         |

| Power-Down Power                            | Full |     | 20       |       | mW         |

| Standby Power <sup>2</sup>                  | Full |     | 7        |       | mW         |

| Sleep Power                                 | Full |     | 3        | 4     | mW         |

<sup>1</sup> Input power is referenced to full scale. Therefore, all measurements were taken with a 2 dB signal below full scale, unless otherwise noted. <sup>2</sup> Measured with a low input frequency, full-scale sine wave.

### AC SPECIFICATIONS

All power supplies set to 1.8 V, 640 MHz sample rate, 0.5 V internal reference, PLL disabled, 40 MSPS output data rate, AIN = -2.0 dBFS, unless otherwise noted.

| Parameter <sup>1</sup>                                                                                   | Temp | Min | Тур  | Max    | Unit   |

|----------------------------------------------------------------------------------------------------------|------|-----|------|--------|--------|

| SIGNAL-TO-NOISE RATIO (SNR)                                                                              |      |     |      |        |        |

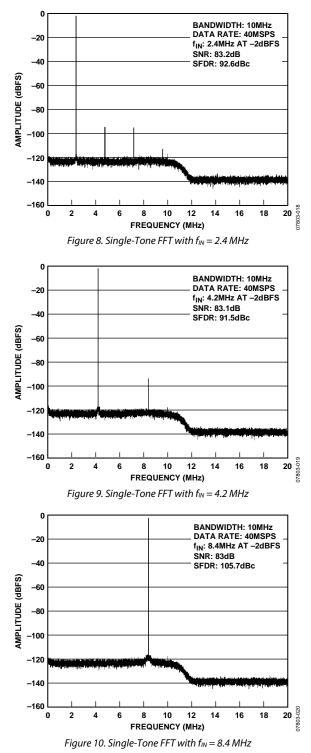

| $f_{IN} = 2.4 \text{ MHz}$                                                                               | Full | 81  | 83   |        | dB     |

| $f_{IN} = 4.2 \text{ MHz}$                                                                               | 25°C |     | 83   |        | dB     |

| $f_{IN} = 8.4 \text{ MHz}$                                                                               | 25°C |     | 83   |        | dB     |

| EFFECTIVE NUMBER OF BITS (ENOB)                                                                          |      |     |      |        |        |

| $f_{IN} = 2.4 \text{ MHz}$                                                                               | 25°C |     | 13.5 |        | Bits   |

| $f_{IN} = 4.2 \text{ MHz}$                                                                               | 25°C |     | 13.5 |        | Bits   |

| $f_{IN} = 8.4 \text{ MHz}$                                                                               | 25°C |     | 13.5 |        | Bits   |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                                                       |      |     |      |        |        |

| $f_{IN} = 2.4 \text{ MHz}$                                                                               | Full |     | 87   | 80     | dBc    |

| $f_{IN} = 4.2 \text{ MHz}$                                                                               | 25°C |     | 87   |        | dBc    |

| $f_{IN} = 8.4 \text{ MHz}$                                                                               | 25°C |     | <120 |        | dBc    |

| NOISE SPECTRAL DENSITY (NSD)                                                                             |      |     |      |        |        |

| AIN = -2 dBFS                                                                                            | Full |     | -155 | -153   | dB/Hz  |

| AIN = -40  dBFS                                                                                          | Full |     | -156 | -154.5 | dB/Hz  |

| NOISE FIGURE <sup>2</sup>                                                                                | 25°C |     | 15   |        | dB     |

| TWO-TONE SFDR                                                                                            |      |     |      |        |        |

| $f_{\text{IN1}}$ = 2.1 MHz at $-8$ dBFS, $f_{\text{IN2}}$ = 2.4 MHz at $-8$ dBFS                         | 25°C |     | 93   |        | dBc    |

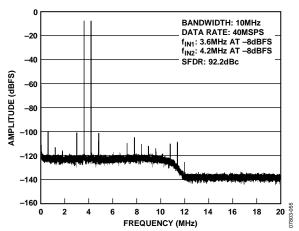

| $f_{\text{IN1}}=3.6~\text{MHz}$ at $-8~\text{dBFS},~f_{\text{IN2}}=4.2~\text{MHz}$ at $-8~\text{dBFS}$   | 25°C |     | 92.5 |        | dBc    |

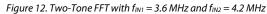

| $f_{\text{IN1}}=7.2~\text{MHz}$ at $-8~\text{dBFS},$ $f_{\text{IN2}}=8.4~\text{MHz}$ at $-8~\text{dBFS}$ | 25°C |     | 92.5 |        | dBc    |

| ANALOG INPUT BANDWIDTH                                                                                   | 25°C |     |      | 10     | MHz    |

| APERTURE JITTER                                                                                          | 25°C |     |      | 1      | ps rms |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

$^2$  Noise figure with respect to 50  $\Omega$ . AD9261 internal impedance is 1000  $\Omega$  differential. See the AN-835 Application Note for a definition.

### DIGITAL DECIMATION FILTERING CHARACTERISTICS

All power supplies set to 1.8 V, 640 MHz sample rate, 0.5 V internal reference, PLL disabled, AIN = -2.0 dBFS, unless otherwise noted.

#### Table 3.

|                        |     | 2.5 MHz BW      |      |     | 5 MHZ BW       |     |     | 10 MHz BW     |     |      |

|------------------------|-----|-----------------|------|-----|----------------|-----|-----|---------------|-----|------|

| Parameter <sup>1</sup> | Min | Тур             | Max  | Min | Тур            | Max | Min | Тур           | Max | Unit |

| Pass-Band Transition   | 2.5 |                 | 3.75 | 5   |                | 6.5 | 10  |               | 13  | MHz  |

| Pass-Band Ripple       |     | <0.1            |      |     | <0.1           |     |     | <0.1          |     | dB   |

| Stop Band              |     | 3.75 MHz – fs/2 |      |     | 6.5 MHz – fs/2 |     |     | 13 MHz – fs/2 |     | MHz  |

| Stop Band Attenuation  |     | >85             |      |     | >85            |     |     | >85           |     | dB   |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

### **DIGITAL SPECIFICATIONS**

All power supplies set to 1.8 V, 640 MHz sample rate, 0.5 V internal reference, PLL disabled, 40 MSPS output data rate, AIN = -2.0 dBFS, unless otherwise noted.

| Parameter <sup>1</sup>                                                     | Temp | Min  | Тур   | Max         | Unit  |

|----------------------------------------------------------------------------|------|------|-------|-------------|-------|

| DIFFERENTIAL CLOCK INPUTS (CLK+, CLK-)                                     |      |      |       |             |       |

| Logic Compliance                                                           |      |      | CMOS  | 5/LVPECL    |       |

| Differential Input Voltage                                                 | Full | 0.4  | 0.8   | 2           | V p-р |

| Input Common-Mode Range                                                    | Full | 0.3  | 0.450 | 0.5         | V     |

| High Level Input Current                                                   | Full | -60  |       | +60         | μΑ    |

| Low Level Input Current                                                    | Full | -60  |       | +60         | μΑ    |

| Input Resistance                                                           | Full |      | 20    |             | kΩ    |

| Input Capacitance                                                          | Full |      | 1     |             | pF    |

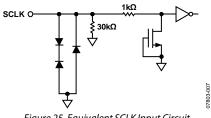

| LOGIC INPUTS (SCLK)                                                        |      |      |       |             |       |

| High Level Input Voltage                                                   | Full | 1.2  |       | DRVDD + 0.3 | V     |

| Low Level Input Voltage                                                    | Full | 0    |       | 0.8         | V     |

| High Level Input Current                                                   | Full | -50  |       | -75         | μΑ    |

| Low Level Input Current                                                    | Full | -10  |       | +10         | μΑ    |

| Input Resistance                                                           | Full |      | 30    |             | kΩ    |

| Input Capacitance                                                          | Full |      | 2     |             | pF    |

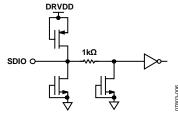

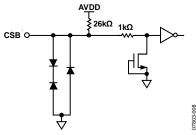

| LOGIC INPUTS (SDIO, CSB, RESET)                                            |      |      |       |             |       |

| High Level Input Voltage                                                   | Full | 1.2  |       | DRVDD + 0.3 | V     |

| Low Level Input Voltage                                                    | Full | 0    |       | 0.8         | V     |

| High Level Input Current                                                   | Full | -10  |       | +10         | μΑ    |

| Low Level Input Current                                                    | Full | +40  |       | +135        | μΑ    |

| Input Resistance                                                           | Full |      | 26    |             | kΩ    |

| Input Capacitance                                                          | Full |      | 5     |             | pF    |

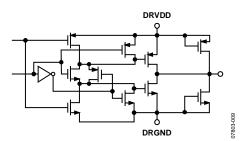

| DIGITAL OUTPUTS                                                            |      |      |       |             |       |

| DRVDD = 3.3 V                                                              |      |      |       |             |       |

| High Level Output Voltage (V <sub>OH</sub> , $I_{OH}$ = 50 µA)             | Full | 3.29 |       |             | V     |

| High Level Output Voltage ( $V_{OH}$ , $I_{OH}$ = 0.5 mA)                  | Full | 3.25 |       |             | V     |

| Low Level Output Voltage ( $V_{OL}$ , $I_{OL}$ = 1.6 mA)                   | Full |      |       | 0.2         | V     |

| Low Level Output Voltage (V <sub>OL</sub> , $I_{OL} = 50 \mu A$ )          | Full |      |       | 0.05        | V     |

| DRVDD = 1.8 V                                                              |      |      |       |             |       |

| High Level Output Voltage (V <sub>OH</sub> , I <sub>OH</sub> = 50 $\mu$ A) | Full | 1.79 |       |             | V     |

| High Level Output Voltage (V <sub>OH</sub> , $I_{OH}$ = 0.5 mA)            | Full | 1.75 |       |             | V     |

| Low Level Output Voltage ( $V_{OL}$ , $I_{OL}$ = 1.6 mA)                   | Full |      |       | 0.2         | V     |

| Low Level Output Voltage ( $V_{OL}$ , $I_{OL}$ = 50 $\mu$ A)               | Full |      |       | 0.05        | V     |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

### SWITCHING SPECIFICATIONS

All power supplies set to 1.8 V, 640 MHz sample rate, 0.5 V internal reference, PLL disabled, 40 MSPS output data rate, AIN = -2.0 dBFS, unless otherwise noted.

| Parameter <sup>1</sup>                             | Temp | Min  | Тур    | Max  | Unit   |

|----------------------------------------------------|------|------|--------|------|--------|

| CLOCK INPUT (USING CLOCK MULTIPLIER)               |      |      |        |      |        |

| Conversion Rate                                    | Full | 30   |        | 160  | MSPS   |

| CLK± Period                                        | Full | 6.25 |        | 33   | ns     |

| CLK± Duty Cycle                                    | Full | 40   | 50     | 60   | %      |

| CLOCK INPUT (DIRECT CLOCKING)                      |      |      |        |      |        |

| Conversion Rate                                    | Full | 608  | 640    | 672  | MSPS   |

| CLK± Period                                        | Full | 1.49 | 1.5625 | 1.64 | ns     |

| CLK± Duty Cycle                                    | Full | 40   | 50     | 60   | %      |

| DATA OUTPUT PARAMETERS                             |      |      |        |      |        |

| Output Data Rate                                   | Full | 20   |        | 168  | MSPS   |

| DCO to Data Skew (t <sub>SKEW</sub> ) <sup>2</sup> | Full | 3    |        |      | ns     |

| Sample Latency                                     | Full |      | 960    |      | Cycles |

| WAKE-UP TIME <sup>3</sup>                          | Full |      |        |      |        |

| Power Down Power                                   | Full |      | 3      |      | μs     |

| Standby Power                                      | Full |      | 9      |      | μs     |

| Sleep Power                                        | Full |      | 15     |      | μs     |

| OUT-OF-RANGE RECOVERY TIME                         | Full |      | 960    |      | Cycles |

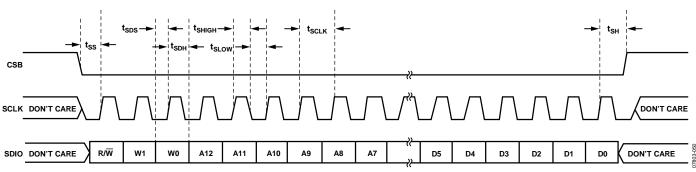

| SERIAL PORT INTERFACE <sup>4</sup>                 |      |      |        |      |        |

| SCLK Period                                        | Full | 40   |        |      | ns     |

| SCLK Pulse Width High Time (tshigh)                | Full | 16   |        |      | ns     |

| SCLK Pulse Width Low Time (t <sub>sLOW</sub> )     | Full | 16   |        |      | ns     |

| SDIO to SCLK Setup Time (tsds)                     | Full | 5    |        |      | ns     |

| SDIO to SCLK Hold Time (t <sub>SDH</sub> )         | Full | 2    |        |      | ns     |

| CSB to SCLK Setup Time (t <sub>ss</sub> )          | Full | 5    |        |      | ns     |

| CSB to SCLK Hold Time (t <sub>sH</sub> )           | Full | 2    |        |      | ns     |

<sup>1</sup> See the AN-83 5 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

<sup>2</sup> Data skew is measured from DCO 50% transition to data (D0 to D15) 50% transition, with 5 pF load.

<sup>3</sup> Wake-up time is dependent on the value of the decoupling capacitors. Values are shown with 10  $\mu$ F capacitor on VREF and CFILT. <sup>4</sup> See Figure 50 and the Serial Port Interface (SPI) section.

#### **Timing Diagram**

Figure 2. Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Parameter         Rating           Electrical         -0.3 V to +2.0 V           AVDD to AGND         -0.3 V to +2.0 V           DVDD to DGND         -0.3 V to +2.0 V           DRVDD to DGND         -0.3 V to +3.9 V           AGND to DGND         -0.3 V to +0.3 V           AVDD to DGND         -0.3 V to +0.3 V           AGND to DGND         -0.3 V to +0.3 V           AVDD to DRVDD         -3.9 V to +2.0 V           CVDD to CGND         -0.3 V to +2.0 V           CQND to DGND         -0.3 V to +2.0 V           D0 to D15 to DGND         -0.3 V to +2.0 V           DCO to DGND         -0.3 V to +2.0 V           DCO to DGND         -0.3 V to +2.0 V           PDWN to GND         -0.3 V to +2.0 V           PDWN to GND         -0.3 V to +2.0 V           PDWN to GND         -0.3 V to +2.0 V           SDIO to DGND         -0.3 V to +3.9 V           SDIO to DGND         -0.3 V to +3.9 V           SCLK to AGND         -0.3 V to +3.9 V           VIN+, VIN- to AGND         -0.3 V to +2.0 V           Environmental         -0.3 V to +2.0 V           Storage Temperature Range         -65°C to +125°C           Operating Temperature Range         -65°C to +125°C           Operating T | Table 0.                             |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|

| AVDD to AGND-0.3 V to +2.0 VDVDD to DGND-0.3 V to +2.0 VDRVDD to DGND-0.3 V to +3.9 VAGND to DGND-0.3 V to +3.9 VAGND to DGND-0.3 V to +0.3 VAVDD to DRVDD-3.9 V to +2.0 VCVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +2.0 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Parameter                            | Rating           |

| InterferenceOut of the factorDVDD to DGND-0.3 V to +2.0 VDRVDD to DGND-0.3 V to +3.9 VAGND to DGND-0.3 V to +0.3 VAVDD to DRVDD-3.9 V to +2.0 VCVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +2.0 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Electrical                           |                  |

| DRVDD to DGND-0.3 V to +3.9 VAGND to DGND-0.3 V to +0.3 VAVDD to DRVDD-3.9 V to +2.0 VCVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +0.3 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AVDD to AGND                         | –0.3 V to +2.0 V |

| AGND to DGND-0.3 V to +0.3 VAVDD to DRVDD-3.9 V to +2.0 VCVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +0.3 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDUN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DVDD to DGND                         | –0.3 V to +2.0 V |

| AVDD to DRVDD-3.9 V to +2.0 VCVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +2.0 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VOR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDUT to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DRVDD to DGND                        | –0.3 V to +3.9 V |

| CVDD to CGND-0.3 V to +2.0 VCGND to DGND-0.3 V to +0.3 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VOR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AGND to DGND                         | –0.3 V to +0.3 V |

| CGND to DGND-0.3 V to +0.3 VD0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VOR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AVDD to DRVDD                        | -3.9 V to +2.0 V |

| D0 to D15 to DGND-0.3 V to +2.0 VDCO to DGND-0.3 V to +2.0 VOR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +3.9 VVLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-40°C to +125°COperating Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CVDD to CGND                         | –0.3 V to +2.0 V |

| DCO to DGND-0.3 V to +2.0 VOR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CGND to DGND                         | –0.3 V to +0.3 V |

| OR to DGND-0.3 V to +2.0 VPDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D0 to D15 to DGND                    | –0.3 V to +2.0 V |

| PDWN to GND-0.3 V to +2.0 VPLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DCO to DGND                          | –0.3 V to +2.0 V |

| PLLMULTx to DGND-0.3 V to +2.0 VSDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OR to DGND                           | –0.3 V to +2.0 V |

| SDIO to DGND-0.3 V to +3.9 VCSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PDWN to GND                          | –0.3 V to +2.0 V |

| CSB to AGND-0.3 V to +3.9 VSCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-0.3 V to +2.0 VStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PLLMULTx to DGND                     | –0.3 V to +2.0 V |

| SCLK to AGND-0.3 V to +3.9 VVIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SDIO to DGND                         | –0.3 V to +3.9 V |

| VIN+, VIN- to AGND-0.3 V to +2.5 VCLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CSB to AGND                          | –0.3 V to +3.9 V |

| CLK+, CLK- to CGND-0.3 V to +2.0 VEnvironmental-65°C to +125°CStorage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SCLK to AGND                         | –0.3 V to +3.9 V |

| Environmental-65°C to +125°CStorage Temperature Range-40°C to +85°COperating Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VIN+, VIN- to AGND                   | –0.3 V to +2.5 V |

| Storage Temperature Range-65°C to +125°COperating Temperature Range-40°C to +85°CLead Temperature (Soldering, 10 Sec)300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK+, CLK– to CGND                   | –0.3 V to +2.0 V |

| Operating Temperature Range $-40^{\circ}$ C to $+85^{\circ}$ CLead Temperature (Soldering, 10 Sec) $300^{\circ}$ C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Environmental                        |                  |

| Lead Temperature (Soldering, 10 Sec) 300°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Storage Temperature Range            | –65°C to +125°C  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operating Temperature Range          | –40°C to +85°C   |

| Junction Temperature 150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Lead Temperature (Soldering, 10 Sec) | 300°C            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Junction Temperature                 | 150℃             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

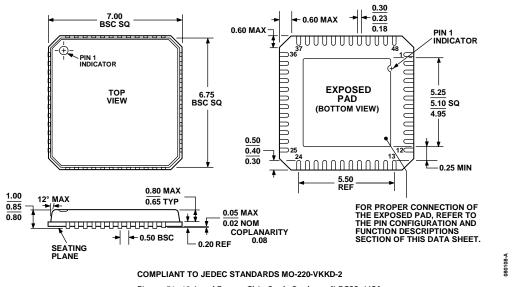

### THERMAL RESISTANCE

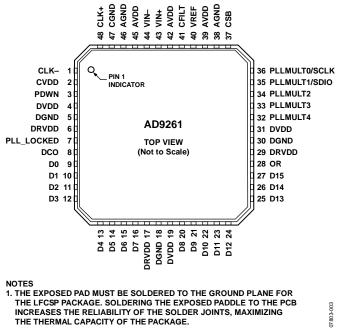

The exposed paddle must be soldered to the ground plane for the LFCSP package. Soldering the exposed paddle to the PCB increases the reliability of the solder joints, maximizing the thermal capability of the package.

#### Table 7. Thermal Resistance

| Package Type            | θ」Α  | θյβ  | θıc | Unit |

|-------------------------|------|------|-----|------|

| 48-Lead LFCSP (CP-48-1) | 27.7 | 11.8 | 1.1 | °C/W |

Typical  $\theta_{JA}$  and  $\theta_{JC}$  are specified for a 4-layer board in still air. Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{JA}$ .

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

07803-003

Figure 3. Pin Configuration

#### **Table 8. Pin Function Descriptions**

| Pin No.           | Mnemonic                     | Description                                                                    |

|-------------------|------------------------------|--------------------------------------------------------------------------------|

| 1                 | CLK–                         | Clock Input (–).                                                               |

| 2                 | CVDD                         | Clock Supply (1.8 V).                                                          |

| 3                 | PDWN                         | External Power-Down Pin.                                                       |

| 4, 19, 31         | DVDD                         | Digital Supply (1.8 V).                                                        |

| 5, 18, 30         | DGND                         | Digital Ground.                                                                |

| 6, 17, 29         | DRVDD                        | Digital Output Driver Supply (1.8 V to 3.3 V).                                 |

| 7                 | PLL_LOCKED                   | PLL Lock Indicator.                                                            |

| 8                 | DCO                          | Data Clock Output.                                                             |

| 9 to 16, 20 to 27 | D0 to D15                    | Data Output Bits. D0 is the LSB and D15 is the MSB.                            |

| 28                | OR                           | Overrange Indicator.                                                           |

| 32, 33, 34        | PLLMULT4, PLLMULT3, PLLMULT2 | PLL Mode Selection Pins.                                                       |

| 35                | PLLMULT1/SDIO                | PLL Mode Selection Pin/Serial Port Interface Data Input/Output.                |

| 36                | PLLMULT0/SCLK                | PLL Mode Selection Pin/Serial Port Interface Clock.                            |

| 37                | CSB                          | Serial Port Interface Chip Select. Active low.                                 |

| 38, 46            | AGND                         | Analog Ground.                                                                 |

| 39, 42, 45        | AVDD                         | Analog Supply (1.8 V).                                                         |

| 40                | VREF                         | Voltage Reference Input/Output.                                                |

| 41                | CFILT                        | Noise Limiting Filter Capacitor.                                               |

| 43                | VIN+                         | Analog Input (+).                                                              |

| 44                | VIN–                         | Analog Input (–).                                                              |

| 47                | CGND                         | Clock Ground.                                                                  |

| 48                | CLK+                         | Clock Input (+).                                                               |

| 49                | EPAD                         | Analog Ground. Pin 49 is the exposed thermal pad on the bottom of the package. |

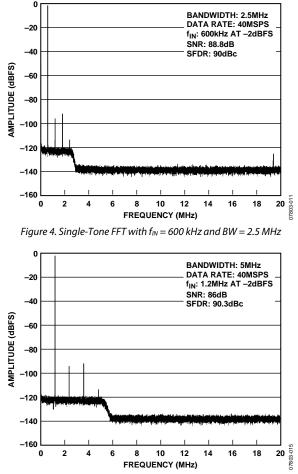

### **TYPICAL PERFORMANCE CHARACTERISTICS**

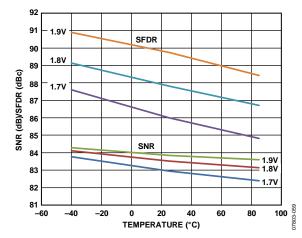

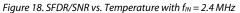

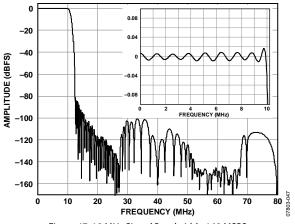

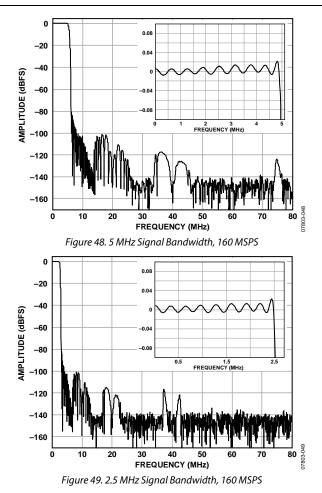

All power supplies set to 1.8 V, 640 MHz sample rate, 2 V p-p differential input, 0.5 V internal reference, PLL disabled, AIN = -2.0 dBFS, T<sub>A</sub> = 25°C, unless otherwise noted.

Figure 5. Single-Tone FFT with  $f_{IN} = 1.2 \text{ MHz}$  and BW = 5 MHz

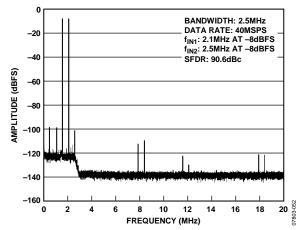

Figure 6. Two-Tone FFT with  $f_{IN1} = 2.1$  MHz,  $f_{IN2} = 2.5$  MHz, and BW = 2.5 MHz

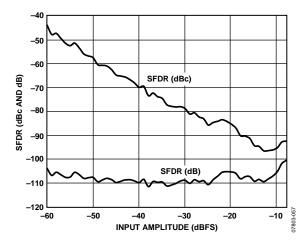

Figure 7. Two-Tone FFT with  $f_{IN1} = 2.1$  MHz,  $f_{IN2} = 2.4$  MHz and BW = 5 MHz

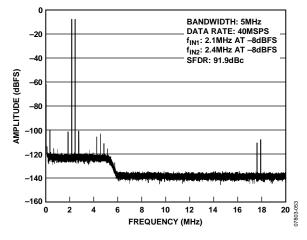

All power supplies set to 1.8 V, 640 MHz sample rate, 2 V p-p differential input, 0.5 V internal reference, PLL disabled, AIN = -2.0 dBFS, 10 MHz bandwidth, output data rate 40 MSPS,  $T_A = 25^{\circ}$ C, unless otherwise noted.

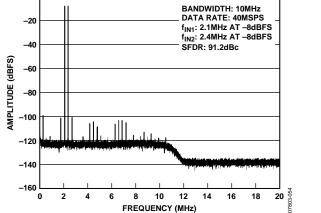

Figure 11. Two-Tone FFT with  $f_{IN1} = 2.1$  MHz and  $f_{IN2} = 2.4$  MHz

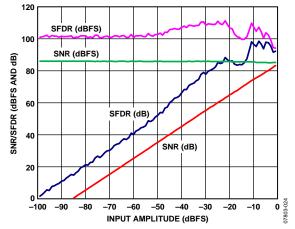

Figure 14. Single-Tone SNR and SFDR vs. Input Amplitude with  $f_{IN} = 2.4 \text{ MHz}$

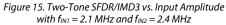

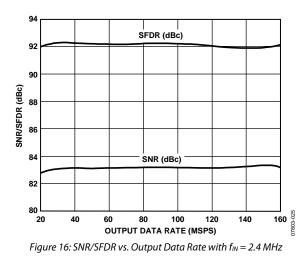

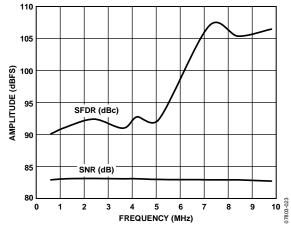

Figure 17. SNR/SFDR vs. Input Frequency

# **EQUIVALENT CIRCUITS**

Figure 23. Equivalent Clock Input Circuit

Figure 24. Equivalent SDIO Input Circuit

Figure 25. Equivalent SCLK Input Circuit

Figure 26. Equivalent CSB Input Circuit

Figure 27. Equivalent Digital Output Circuit

### THEORY OF OPERATION

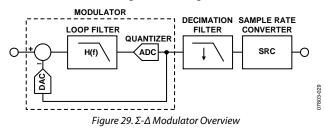

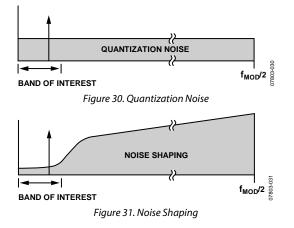

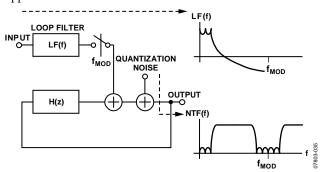

The AD9261 uses a continuous time  $\Sigma$ - $\Delta$  modulator to convert the analog input to a digital word. The digital word is processed by the decimation filter and rate-adjusted by the sample rate converter (see Figure 29). The modulator consists of a continuous time loop filter preceding a quantizer that samples at f<sub>MOD</sub> = 640 MSPS. This produces an oversampling ratio (OSR) of 32 for a 10 MHz input bandwidth. The output of the quantizer is fed back to a DAC that ideally cancels the input signal. The incomplete input cancellation residue is filtered by the loop filter and is used to form the next quantizer sample.

The quantizer produces a nine-level digital word. The quantization noise is spread uniformly over the Nyquist band (see Figure 30), but the feedback loop causes the quantization noise present in the nine-level output to have a nonuniform spectral shape. This noise-shaping technique (see Figure 31) pushes the in-band noise out of band; therefore, the amount of quantization noise in the frequency band of interest is minimal.

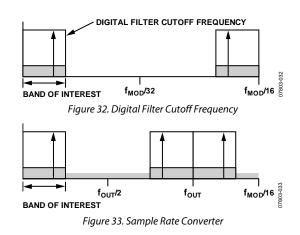

The digital decimation filter that follows the modulator removes the large out-of-band quantization noise (see Figure 32), while also reducing the data rate from  $f_{MOD}$  to  $f_{MOD}/16$ . If the internal PLL is enabled, the sample rate converter generates samples at the same frequency as the input clock frequency. If the internal PLL is disabled, the sample rate converter can be programmed to give an output frequency that is a divide ratio of the modulator clock. The sample rate converter is designed to attenuate images outside the band of interest (see Figure 33).

### **ANALOG INPUT CONSIDERATIONS**

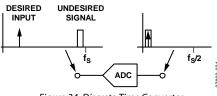

The continuous time modulator removes the need for an antialias filter at the input to the AD9261. A discrete time converter aliases signals around the sample clock frequency and its multiples to the band of interest (see Figure 34). Therefore, an external antialias filter is needed to reject these signals.

Figure 34. Discrete Time Converter

In contrast, the continuous time  $\Sigma$ - $\Delta$  modulator used within the AD9261 has inherent antialiasing. The antialiasing property results from sampling occurring at the output of the loop filter (see Figure 35), and thus aliasing occurs at the same point in the loop as quantization noise is injected; aliases are shaped by the same mechanism as quantization noise. The quantization noise transfer function, NTF(f), has zeros in the band of interest and in all alias bands because NTF(f) is a discrete time transfer function, whereas the loop filter transfer function, LF(f), is a continuous time transfer function, which introduces poles only in the band of interest. The signal transfer function, being the product of NTF(f) and LF(f), only has zeros in alias bands and therefore suppresses all aliases.

*Figure 35. Continuous Time Converter*

#### Input Common Mode

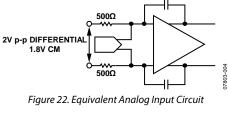

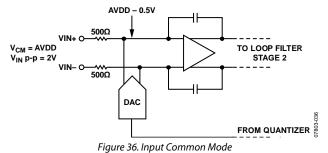

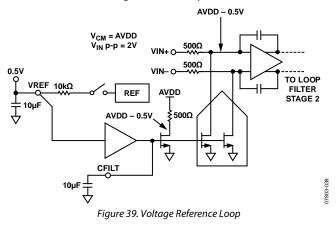

The analog inputs of the AD9261 are not internally dc biased. In ac-coupled applications, the user must provide this bias externally. Setting the device such that  $V_{CM} = AVDD$  is recommended for optimum performance. The analog inputs are 500  $\Omega$  resistors, and the internal reference loop aims to develop 0.5 V across each input resistor (see Figure 36). With 0 V differential input, the driver sources 1 mA into each analog input.

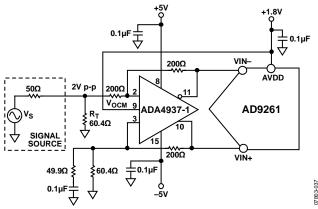

### Differential Input Configurations

The AD9261 can also be configured for differential inputs. The ADA4937-1 differential driver provides excellent performance and a flexible interface to the ADC. The output common-mode voltage of the ADA4937-1 is easily set by connecting AVDD to the  $V_{OCM}$  pin of the ADA4937-1 (see Figure 37). The noise and linearity of the ADA4937-1 needs important consideration because the system performance may be limited by the ADA4937-1.

Figure 37. Differential Input Configuration Using the ADA4937-1

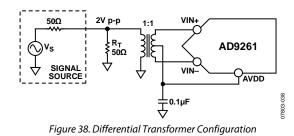

For frequencies offset from dc, where SNR is a key parameter, differential transformer coupling is the recommended input configuration. An example is shown in Figure 38. The center tap of the secondary winding of the transformer is connected to AVDD to bias the analog input.

The signal characteristics must be considered when selecting a transformer. Most RF transformers saturate at frequencies below a couple of megahertz (MHz), and excessive signal power can cause core saturation, which leads to distortion.

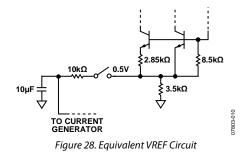

#### Voltage Reference

A stable and accurate 0.5 V voltage reference is built into the AD9261. The reference voltage should be decoupled to minimize the noise bandwidth using a 10  $\mu$ F capacitor. The reference is used to generate a bias current into a matched resistor such that, when used to bias the current in the feedback DAC, a voltage of AVDD – 0.5 V is developed at the internal side of the input resistors (see Figure 39). The current bias circuit should also be decoupled on the CFILT pin with a 10  $\mu$ F capacitor. For this reason, the VREF voltage should always be 0.5 V.

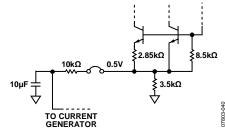

#### Internal Reference Connection

To minimize thermal noise, the internal reference on the AD9261 is an unbuffered 0.5 V. It has an internal 10 k $\Omega$  series resistor, which, when externally decoupled with a 10  $\mu$ F capacitor, limits the noise (see Figure 40). The unbuffered reference should not be used to drive any external circuitry. The internal reference is used by default.

Figure 40. Internal Reference Configuration

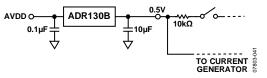

### **External Reference Operation**

If an external reference is desired, the internal reference can be disabled by setting Register 0x18[6] high. Figure 41 shows an application using the ADR130B as a stable external reference.

Figure 41. External Reference Configuration

### **CLOCK INPUT CONSIDERATIONS**

The AD9261 offers two modes of sourcing the ADC sample clock (CLK+ and CLK-). The first mode uses an on-chip clock multiplier that accepts a reference clock operating at the lower input frequency. The on-chip phase-locked loop (PLL) then multiplies the reference clock up to a higher frequency, which is then used to generate all the internal clocks required by the ADC

The clock multiplier provides a high quality clock that meets the performance requirements of most applications. Using the on-chip clock multiplier removes the burden of generating and distributing the high speed clock.

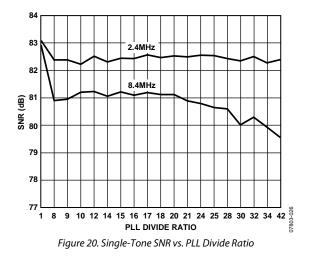

The second mode bypasses the clock multiplier circuitry and allows the clock to be directly sourced. This mode enables the user to source a very high quality clock directly to the  $\Sigma$ - $\Delta$ modulator. Sourcing the ADC clock directly may be necessary in demanding applications that require the lowest possible ADC output noise. Refer to Figure 20, which shows the degradation in SNR performance for the various PLL settings.

In either case, when using the on-chip clock multiplier or sourcing the high speed clock directly, it is necessary that the clock source have low jitter to maximize the ADC noise performance. High speed, high resolution ADCs are sensitive to the quality of the clock input. As jitter increases, the SNR performance of the AD9261 degrades from that specified in Table 2. The jitter inherent to the part due to the PLL root sum squares with any external clock jitter, thereby degrading performance. To prevent jitter from dominating the performance of the AD9261, the input clock source should be no greater than 1 ps rms of jitter.

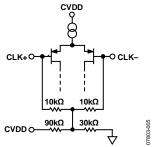

The CLK± inputs are self-biased to 450 mV (see Figure 23); if dc-coupled, it is important to maintain the specified 450 mV input common-mode voltage. Each input pin can safely swing from 200 mV p-p to 1 V p-p single-ended about the 450 mV common-mode voltage. The recommended clock inputs are CMOS or LVPECL.

The specified clock rate of the  $\Sigma$ - $\Delta$  modulator, f<sub>MOD</sub>, is 640 MHz. The clock rate possesses a direct relationship with the available input bandwidth of the ADC.

$Bandwidth = f_{MOD} \div 64$

In either case, using the on-chip clock multiplier to generate the  $\Sigma$ - $\Delta$  modulator clock rate or directly sourcing the clock, any deviation from 640 MHz results in a change in input bandwidth. The input range of the clock is limited to  $640 \text{ MHz} \pm 5\%$ .

### **Direct Clocking**

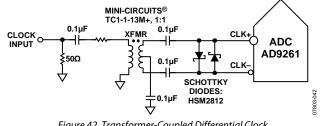

The default configuration of the AD9261 is for direct clocking where the PLL is bypassed. Figure 42 shows one preferred method for clocking the AD9261. A low jitter clock source is converted from a single-ended signal to a differential signal using an RF transformer. The back-to-back Schottky diodes across the secondary side of the transformer limits clock excursions into the AD9261 to approximately 0.8 V p-p differential. This helps prevent the large voltage swings of the clock from feeding through to other portions of the AD9261 while preserving the fast rise and fall times of the signal, which are critical to achieving low jitter.

Figure 42. Transformer-Coupled Differential Clock

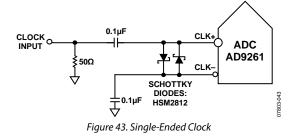

If a differential clock is not available, the AD9261 can be driven by a single-ended signal into the CLK+ terminal with the CLKterminal ac-coupled to ground. Figure 43 shows the circuit configuration.

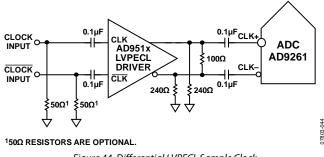

Another option is to ac couple a differential LVPECL signal to the sample clock input pins, as shown in Figure 44. The AD951x family of clock drivers is recommended because it offers excellent jitter performance.

Figure 44. Differential LVPECL Sample Clock

#### Internal PLL Clock Distribution

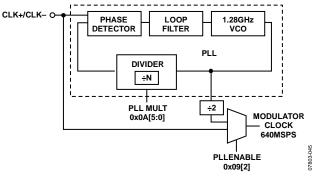

The alternative clocking option available on the AD9261 is to apply a low frequency reference clock and use the on-chip clock multiplier to generate the high frequency  $f_{MOD}$  rate. The internal clock architecture is shown in Figure 45.

Figure 45. Internal Clock Architecture

The clock multiplication circuit operates such that the VCO outputs a frequency,  $f_{VCO}$ , equal to the reference clock input multiplied by N

$\mathbf{f}_{VCO} = (CLK\pm) \times (N)$

where N is the PLL multiplication (PLLMULT) factor.

The  $\Sigma\text{-}\Delta$  modulator clock frequency,  $f_{\text{MOD}}\text{,}$  is equal to

$f_{MOD} = f_{VCO} \div 2$

The reference clock, CLK $\pm$ , is limited to 30 MHz to 160 MHz when configured to use the on-chip clock multiplier. Given the input range of the reference clock and the available multiplication factors, the f<sub>VCO</sub> is approximately 1280 MHz. This results in the desired f<sub>MOD</sub> rate of 640 MHz with a 50% duty cycle.

Before the PLL enable (PLLENABLE) register bit is set, the PLL multiplication factor should be programmed into Register 0x0A[5:0]. After setting the PLLENABLE bit, the PLL locks and reports a locked state in Register 0x0A[7]. If the PLL multiplication factor is changed, the PLL enable bit should be reset and set again. Some common clock multiplication factors are shown in Table 11.

The recommended sequence for enabling and programming the on-chip clock multiplier is summarized in Table 9.

Table 9. Sequence for Enabling and Programming the PLL

| Step | Procedure                                                                  |

|------|----------------------------------------------------------------------------|

| 1    | Apply a reference clock to the CLK± pins.                                  |

| 2    | Program the PLL multiplication factor in Register 0x0A[5:0]. See Table 10. |

| 3    | Enable the PLL; Register $0x09 = 04$ (decimal).                            |

| 4    | Enable the PLL autoband select.                                            |

| 5    | Initiate an SRC reset; Register 0x101[5:0] = 0.                            |

| 6    | Set SRC to the desired value via Register 0x101[5:0].                      |

| Table 10. Internal PLL Multiplication Fac | tors |

|-------------------------------------------|------|

|                                           |      |

| 0x0A[5:0] | PLLMULT (N) | 0x0A[5:0] | PLLMULT (N) |

|-----------|-------------|-----------|-------------|

| 1         | 8           | 33        | 32          |

| 2         | 8           | 34        | 34          |

| 3         | 8           | 35        | 34          |

| 4         | 8           | 36        | 34          |

| 5         | 8           | 37        | 34          |

| 6         | 8           | 38        | 34          |

| 7         | 8           | 39        | 34          |

| 8         | 8           | 40        | 34          |

| 9         | 9           | 41        | 34          |

| 10        | 10          | 42        | 42          |

| 11        | 10          | 43        | 42          |

| 12        | 12          | 44        | 42          |

| 13        | 12          | 45        | 42          |

| 14        | 14          | 46        | 42          |

| 15        | 15          | 47        | 42          |

| 16        | 16          | 48        | 42          |

| 17        | 17          | 49        | 42          |

| 18        | 18          | 50        | 42          |

| 19        | 18          | 51        | 42          |

| 20        | 20          | 52        | 42          |

| 21        | 21          | 53        | 42          |

| 22        | 21          | 54        | 42          |

| 23        | 21          | 55        | 42          |

| 24        | 24          | 56        | 42          |

| 25        | 25          | 57        | 42          |

| 26        | 25          | 58        | 42          |

| 27        | 25          | 59        | 42          |

| 28        | 28          | 60        | 42          |

| 29        | 28          | 61        | 42          |

| 30        | 30          | 62        | 42          |

| 31        | 30          | 63        | 42          |

| 32        | 32          | 64        | 42          |

#### **External PLL Control**

At power-up, the serial interface is disabled until the first serial port access. If the serial interface is disabled, the PLLMULTx pins control the PLL multiplication factor. The five PLLMULTx pins (Pin 32 to Pin 36) offer all the available multiplication factors. If all PLLMULTx pins are tied high, the PLL is disabled and the AD9261 assumes the high frequency modulator clock rate that is applied to the CLK± pins. Table 12 shows the relationship between PLLMULTx pins and the PLL multiplication factor.

### **PLL Autoband Select**

The PLL VCO has a wide operating range that is covered by overlapping frequency bands. For any desired VCO output frequency, there are multiple valid PLL band select values. The AD9261 possesses an automatic PLL band select feature on chip that determines the optimal PLL band setting. This feature can be enabled by writing to Register 0x0A[6] and is the recommended configuration with the PLL clocking option. Follow the sequence shown in Table 9 for enabling the autoband select and configuring the PLL.

When the device is taken out of sleep or standby mode, Register 0x0A[6] must be toggled to reinitiate the autoband detect.

| Table 11. Common Modulator Clock Multiplication Factors |                        |                        |                           |             |  |

|---------------------------------------------------------|------------------------|------------------------|---------------------------|-------------|--|

| CLK±<br>(MHz)                                           | 0x0A[5:0]<br>(PLLMULT) | f <sub>vco</sub> (MHz) | f <sub>мор</sub><br>(MHz) | BW<br>(MHz) |  |

| 30.72                                                   | 42                     | 1290.24                | 645.12                    | 10.08       |  |

| 39.3216                                                 | 32                     | 1258.29                | 629.15                    | 9.83        |  |

| 52.00                                                   | 25                     | 1300.00                | 650.00                    | 10.16       |  |

| 61.44                                                   | 21                     | 1290.24                | 645.12                    | 10.08       |  |

| 76.80                                                   | 17                     | 1305.60                | 652.80                    | 10.20       |  |

| 78.00                                                   | 17                     | 1326.00                | 663.00                    | 10.36       |  |

| 78.6432                                                 | 16                     | 1258.29                | 629.15                    | 9.83        |  |

| 89.60                                                   | 15                     | 1344.00                | 672.00                    | 10.50       |  |

| 92.16                                                   | 14                     | 1290.24                | 645.12                    | 10.08       |  |

| 122.88                                                  | 10                     | 1228.80                | 614.40                    | 9.60        |  |

| 134.40                                                  | 10                     | 1344.00                | 672.00                    | 10.50       |  |