Freescale Semiconductor, Inc. Datasheet: Technical Data

Document Number: MC13201

Rev. 2, 04/2015

## MC13201 Datasheet with Addendum

Rev. 2 of the MC13201 datasheet has two parts:

- The addendum to revision 1.3 of the datasheet immediately following this cover page.

- Revision 1.3 of the datasheet, following the addendum. The changes described in the addendum have not been implemented in the specified pages.

## Freescale Semiconductor, Inc. Datasheet Addendum

Document Number: MC13201AD

Rev. 0, 04/2015

# Addendum to Rev. 1.3 of the MC13201 Datasheet

This addendum identifies changes to Rev. 1.3 of the MC13201 datasheet. The changes described in this addendum have not been implemented in the specified pages.

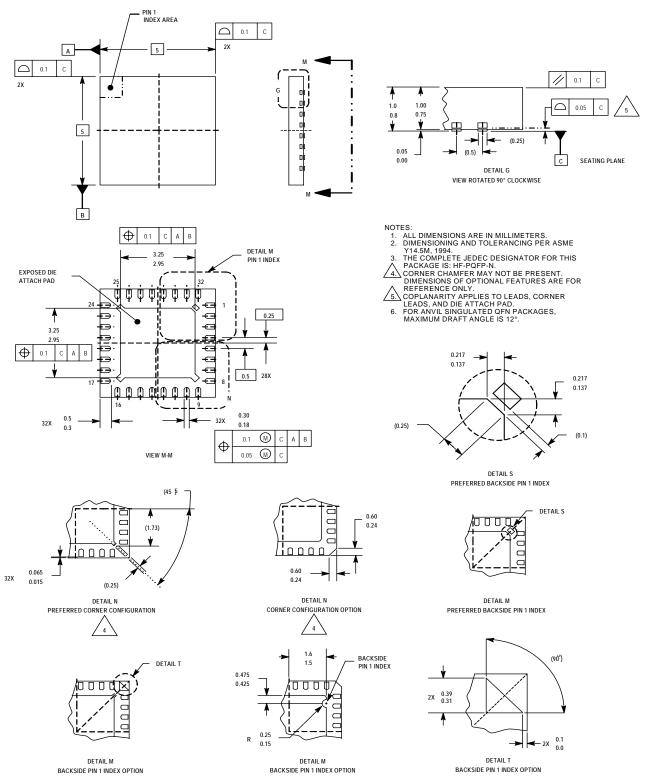

## 1 Case outline drawing change for new QFN-32 package migration

| Location: | Section 9, Page 27 |

|-----------|--------------------|

The case outline was changed because of migration from gold wireto copper wire for QFN-32 packages.

The case outline details in Section 9 Packaging Information, should be replaced with package document #98ASA00473D case outline details.

To view the new case outine details, go to freescale.com and perform a keyword særch for the drawing's document number.

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| QFN-32                                   | 98ASA00473D                   |

#### NOTE

For more information about QFN package use, see EB806 Electrical Connection Recommendations for Exposed Pad on QFN and DFN Packages.

## 2 References to case 1311-03

Location: Section 1, Page 1 Section 9, Page 27

Remove the references to case 1311-03.

## **Freescale Semiconductor**

## **Technical Data**

Document Number: MC13201

Rev. 1.3, 04/2008

## MC13201

#### **Package Information**

Plastic Package Case 1311-03 QFN -32

#### Ordering Information

| Device                         | Device Marking | Package |

|--------------------------------|----------------|---------|

| MC13201FC                      | 13201          | QFN-32  |

| MC13201FCR2<br>(Tape and Reel) | 13201          | QFN-32  |

## MC13201

2.4 GHz Low Power Transceiver for the IEEE<sup>®</sup> 802.15.4 Standard

## 1 Introduction

The MC13201 is a short range, low power, 2.4 GHz Industrial, Scientific, and Medical (ISM) band transceivers. The MC13201 contains a complete packet data modem which is compliant with the IEEE<sup>®</sup> 802.15.4 Standard PHY (Physical) layer. This allows the development of proprietary point-to-point and star networks based on the 802.15.4 packet structure and modulation format. For full 802.15.4 Standard compliance, the MC13202 and Freescale's 802.15.4 MAC software are required.

When combined with an appropriate microcontroller (MCU), the MC13201 provides a cost-effective solution for short-range data links and networks. Interface with the MCU is accomplished using a four wire serial peripheral interface (SPI) connection and an interrupt request output which allows for the use of a variety of processors. The software and processor can be scaled to fit applications ranging from simple point-to-point systems to star networks.

#### **Contents**

| 1 | Introduction 1                            |

|---|-------------------------------------------|

| 2 | Features 2                                |

| 3 | Block Diagrams4                           |

| 4 | Data Transfer Mode 5                      |

| 5 | Electrical Characteristics 7              |

| 6 | Functional Description                    |

| 7 | Pin Connections 14                        |

| 8 | Crystal Oscillator Reference Frequency 18 |

| 9 | Packaging Information 27                  |

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2005, 2006, 2007, 2008. All rights reserved.

For more detailed information about MC13201 operation, refer to the *MC13201 Reference Manual*, (MC13201RM).

Applications include, but are not limited to, the following:

- Residential and commercial automation

- Lighting control

- Security

- Access control

- Heating, ventilation, air-conditioning (HVAC)

- Automated meter reading (AMR)

- Industrial Control

- Asset tracking and monitoring

- Homeland security

- Process management

- Environmental monitoring and control

- HVAC

- Automated meter reading

- Health Care

- Patient monitoring

- Fitness monitoring

- Consumer

- Human interface devices (keyboard, mice, etc.)

- Remote control

- Wireless toys

The transceiver includes a low noise amplifier, 1.0 mW power amplifiers (PA), onboard RF transmit/receive (T/R) switch for single port use, PLL with internal voltage controlled oscillator (VCO), on-board power supply regulation, and full spread-spectrum encoding and decoding. The device supports 250 kbps Offset-Quadrature Phase Shift Keying (O-QPSK) data in 2.0 MHz channels with 5.0 MHz channel spacing per the 802.15.4 Standard. The SPI port and interrupt request output are used for receive (RX) and transmit (TX) data transfer and control.

## 2 Features

- Recommended power supply range: 2.0 to 3.4 V

- Fully compliant 802.15.4 Standard transceiver supports 250 kbps O-QPSK data in 5.0 MHz channels and full spread-spectrum encode and decode

- Operates on one of 16 selectable channels in the 2.4 GHz band

- -1 to 0 dBm nominal output power, programmable from -27 dBm to +3 dBm typical

- Receive sensitivity of <-91 dBm (typical) at 1% PER, 20-byte packet, much better than the 802.15.4 Standard of -85 dBm

- Integrated transmit/receive switch

- Dual PA output pairs which can be programmed for full differential single port or dual port operation that supports an external LNA and/or PA

- Three power down modes for increased battery life

- $--<1 \,\mu A$  Off current

- 1.0 μA Typical Hibernate current

- 35 µA Typical Doze current (no CLKO)

- Programmable frequency clock output (CLKO) for use by MCU

- Onboard trim capability for 16 MHz crystal reference oscillator eliminates need for external variable capacitors and allows for automated production frequency calibration

- Four internal timer comparators available to supplement MCU timer resources

- Buffered transmit and receive data packets for simplified use with low cost MCUs

- Seven GPIO to supplement MCU GPIO

- Operating temperature range: -40 °C to 85 °C

- Small form factor QFN-32 Package

- Meets moisture sensitivity level (MSL) 3

- 260 °C peak reflow temperature

- Meets lead-free requirements

## 2.1 Software Support

Freescale provides a software suite to complement the MC13201 hardware which is called the Freescale Simple MAC (SMAC):

- Simple proprietary wireless connectivity.

- Small memory footprint (about 3 Kbytes typical)

- Supports point-to-point and star network configurations

- Proprietary networks

- Source code and application examples provided

## 3 Block Diagrams

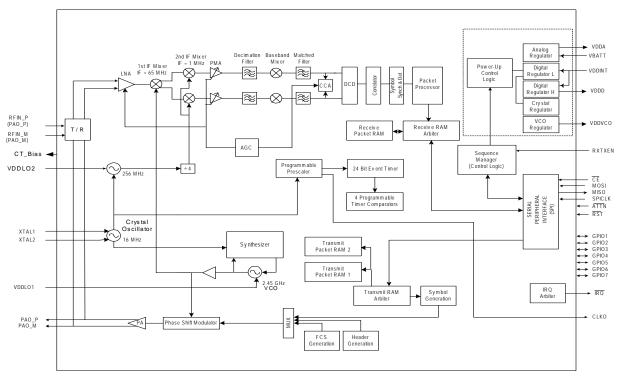

Figure 1 shows a simplified block diagram of the MC13201 which is an 802.15.4 Standard compatible transceiver that provides the functions required in the physical layer (PHY) specification.

Figure 1. 802.15.4 modem Simplified Block Diagram

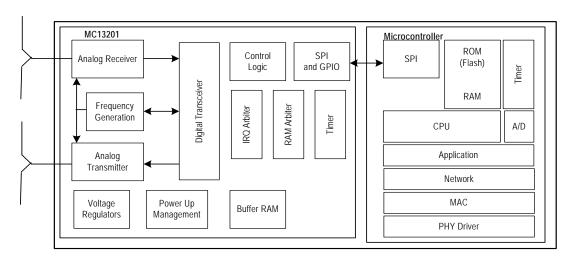

Figure 2 shows the basic system block diagram for the MC13201 in an application. Interface with the transceiver is accomplished through a 4-wire SPI port and interrupt request line. The media access control (MAC), drivers, and network and application software (as required) reside on the host processor. The host can vary from a simple 8-bit device up to a sophisticated 32-bit processor depending on application requirements.

Figure 2. System Level Block Diagram

MC13201 Technical Data, Rev. 1.3,

## 4 Data Transfer Mode

The MC13201 has a data transfer mode called Packet Mode where data is buffered in on-chip Packet RAMs. There is a TX Packet RAM and an RX Packet RAM, each of which are 64 locations by 16 bits wide.

#### 4.1 Packet Structure

Figure 3 shows the packet structure of the MC13201 which is consistent with the 802.15.4 Standard. Payloads of up to 125 bytes are supported. The MC13201 adds a four-byte preamble, a one-byte Start of Frame Delimiter (SFD), and a one-byte Frame Length Indicator (FLI) before the data. A Frame Check Sequence (FCS) is calculated and appended to the end of the data.

| 4 bytes  | 1 byte | 1 byte | 125 bytes maximum | 2 bytes |  |

|----------|--------|--------|-------------------|---------|--|

| Preamble | SFD    | FLI    | Payload Data      | FCS     |  |

Figure 3. MC13201 Packet Structure

## 4.2 Receive Path Description

In the receive signal path, the RF input is converted to low IF In-phase and Quadrature (I & Q) signals through two down-conversion stages. A Clear Channel Assessment (CCA) can be performed based upon the baseband energy integrated over a specific time interval. The digital backend performs Differential Chip Detection (DCD), the correlator "de-spreads" the Direct Sequence Spread Spectrum (DSSS) Offset QPSK (O-QPSK) signal, determines the symbols and packets, and detects the data.

The preamble, SFD, and FLI are parsed and used to detect the payload data and FCS which are stored in RAM. A two-byte FCS is calculated on the received data and compared to the FCS value appended to the transmitted data, which generates a Cyclical Redundancy Check (CRC) result. Link Quality is measured over a 64 µs period after the packet preamble and stored in RAM.

The MC13201 uses a packet mode where the data is processed as an entire packet and stored in Rx Packet RAM. The MCU is notified that an entire packet has been received via an interrupt.

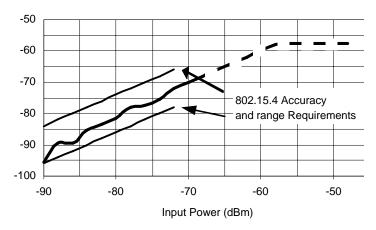

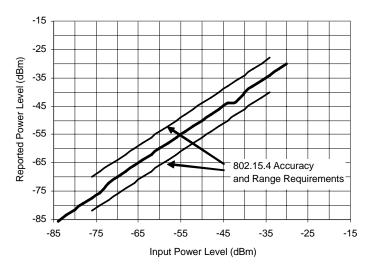

Figure 4 shows CCA reported power level versus input power. Note that CCA reported power saturates at about -57 dBm input power which is well above 802.15.4 Standard requirements. Figure 5 shows energy detection/LQI reported level versus input power.

#### NOTE

For both graphs, the required 802.15.4 Standard accuracy and range limits are shown. A 3.5 dBm offset has been programmed into the CCA reporting level to center the level over temperature in the graphs.

Figure 4. Reported Power Level versus Input Power in CCA Mode

Figure 5. Reported Power Level Versus Input Power for Energy Detect or Link Quality Indicator

## 4.3 Transmit Path Description

For the transmit path, the TX data that was previously stored in TX Packet RAM is retrieved, formed into packets per the 802.15.4 PHY, spread, and then up-converted to the transmit frequency.

Because the MC13201 is used in packet mode, data is processed as an entire packet. The data is first loaded into the TX buffer. The MCU then requests that the MC13201 transmit the data. The MCU is notified via an interrupt when the whole packet has successfully been transmitted.

## 5 Electrical Characteristics

## 5.1 Maximum Ratings

**Table 1. Maximum Ratings**

| Rating                    | Symbol                                | Value                              | Unit |

|---------------------------|---------------------------------------|------------------------------------|------|

| Power Supply Voltage      | V <sub>BATT,</sub> V <sub>DDINT</sub> | -0.3 to 3.6                        | Vdc  |

| Digital Input Voltage     | Vin                                   | -0.3 to (V <sub>DDINT</sub> + 0.3) |      |

| RF Input Power            | P <sub>max</sub>                      | 10                                 | dBm  |

| Junction Temperature      | T <sub>J</sub>                        | 125                                | °C   |

| Storage Temperature Range | T <sub>stg</sub>                      | -55 to 125                         | °C   |

**Note:** Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics or Recommended Operating Conditions tables.

**Note:** Meets Human Body Model (HBM) = 2 kV. RF input/output pins have no ESD protection.

## 5.2 Recommended Operating Conditions

**Table 2. Recommended Operating Conditions**

| Characteristic                                                                                            | Symbol                                   | Min                       | Тур | Max                       | Unit |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|-----|---------------------------|------|

| Power Supply Voltage (V <sub>BATT</sub> = V <sub>DDINT</sub> ) <sup>1</sup>                               | V <sub>BATT,</sub><br>V <sub>DDINT</sub> | 2.0                       | 2.7 | 3.4                       | Vdc  |

| Input Frequency                                                                                           | f <sub>in</sub>                          | 2.405                     | -   | 2.480                     | GHz  |

| Ambient Temperature Range                                                                                 | T <sub>A</sub>                           | -40                       | 25  | 85                        | °C   |

| Logic Input Voltage Low                                                                                   | V <sub>IL</sub>                          | 0                         | -   | 30%<br>V <sub>DDINT</sub> | V    |

| Logic Input Voltage High                                                                                  | V <sub>IH</sub>                          | 70%<br>V <sub>DDINT</sub> | -   | V <sub>DDINT</sub>        | V    |

| SPI Clock Rate                                                                                            | f <sub>SPI</sub>                         | -                         | -   | 8.0                       | MHz  |

| RF Input Power                                                                                            | P <sub>max</sub>                         | -                         | -   | 10                        | dBm  |

| Crystal Reference Oscillator Frequency (±40 ppm over operating conditions to meet the 802.15.4 Standard.) | f <sub>ref</sub>                         | 16 MHz Only               |     |                           |      |

<sup>&</sup>lt;sup>1</sup> If the supply voltage is produced by a switching DC-DC converter, ripple should be less than 100 mV peak-to-peak.

## 5.3 DC Electrical Characteristics

#### **Table 3. DC Electrical Characteristics**

(V<sub>BATT</sub>, V<sub>DDINT</sub> = 2.7 V, T<sub>A</sub> = 25 °C, unless otherwise noted)

| Characteristic                                                                                                                                                                                    | Symbol                                                                                                    | Min                       | Тур                                 | Max                                  | Unit                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------|--------------------------------------|----------------------------------|

| Power Supply Current (V <sub>BATT</sub> + V <sub>DDINT</sub> ) Off <sup>1</sup> Hibernate <sup>1</sup> Doze (No CLKO) <sup>1 2</sup> Idle Transmit Mode (0 dBm nominal output power) Receive Mode | I <sub>leakage</sub> I <sub>CCH</sub> I <sub>CCD</sub> I <sub>CCI</sub> I <sub>CCT</sub> I <sub>CCR</sub> | -<br>-<br>-<br>-          | 0.2<br>1.0<br>35<br>500<br>30<br>37 | 2.5<br>22<br>154<br>1500<br>38<br>45 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>mA<br>mA |

| Input Current (V <sub>IN</sub> = 0 V or V <sub>DDINT</sub> ) (All digital inputs)                                                                                                                 | I <sub>IN</sub>                                                                                           | -                         | -                                   | ±1                                   | μA                               |

| Input Low Voltage (All digital inputs)                                                                                                                                                            | V <sub>IL</sub>                                                                                           | 0                         | -                                   | 30%<br>V <sub>DDINT</sub>            | V                                |

| Input High Voltage (all digital inputs)                                                                                                                                                           | V <sub>IH</sub>                                                                                           | 70%<br>V <sub>DDINT</sub> | -                                   | V <sub>DDINT</sub>                   | V                                |

| Output High Voltage (I <sub>OH</sub> = -1 mA) (All digital outputs)                                                                                                                               | V <sub>OH</sub>                                                                                           | 80%<br>V <sub>DDINT</sub> | -                                   | V <sub>DDINT</sub>                   | V                                |

| Output Low Voltage (I <sub>OL</sub> = 1 mA) (All digital outputs)                                                                                                                                 | V <sub>OL</sub>                                                                                           | 0                         | -                                   | 20%<br>V <sub>DDINT</sub>            | V                                |

To attain specified low power current, all GPIO and other digital IO must be handled properly. See Section 8.3, "Low Power Considerations.

<sup>&</sup>lt;sup>2</sup> CLKO frequency at default value of 32.786 kHz.

## 5.4 AC Electrical Characteristics

#### **Table 4. Receiver AC Electrical Characteristics**

( $V_{BATT}$ ,  $V_{DDINT}$  = 2.7 V,  $T_{A}$  = 25 °C,  $f_{ref}$  = 16 MHz, unless otherwise noted.)

| Characteristic                                                                                                                                                              | Symbol              | Min | Тур                        | Max              | Unit                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|----------------------------|------------------|----------------------------|

| Sensitivity for 1% Packet Error Rate (PER) (-40 to +85 °C)                                                                                                                  | SENS <sub>per</sub> | -   | -91                        | -                | dBm                        |

| Sensitivity for 1% Packet Error Rate (PER) (+25 °C)                                                                                                                         |                     | -   | -91                        | -82              | dBm                        |

| Saturation (maximum input level)                                                                                                                                            | SENS <sub>max</sub> | -   | 10                         | -                | dBm                        |

| Channel Rejection for 1% PER (desired signal -82 dBm) +5 MHz (adjacent channel) -5 MHz (adjacent channel) +10 MHz (alternate channel) -10 MHz (alternate channel) >= 15 MHz |                     |     | 31<br>30<br>43<br>41<br>53 | -<br>-<br>-<br>- | dB<br>dB<br>dB<br>dB<br>dB |

| Frequency Error Tolerance                                                                                                                                                   |                     | -   | -                          | 200              | kHz                        |

| Symbol Rate Error Tolerance                                                                                                                                                 |                     | -   | -                          | 80               | ppm                        |

#### **Table 5. Transmitter AC Electrical Characteristics**

(V<sub>BATT</sub>, V<sub>DDINT</sub> = 2.7 V,  $T_A$  = 25 °C,  $f_{ref}$  = 16 MHz, unless otherwise noted.)

| Characteristic                                        | Symbol           | Min | Тур | Max | Unit |

|-------------------------------------------------------|------------------|-----|-----|-----|------|

| Power Spectral Density (-40 to +85 °C) Absolute limit |                  | -   | -47 | -   | dBm  |

| Power Spectral Density (-40 to +85 °C) Relative limit |                  | -   | 47  | -   |      |

| Nominal Output Power <sup>1</sup>                     | P <sub>out</sub> | -5  | -1  | -   | dBm  |

| Maximum Output Power <sup>2</sup>                     |                  |     | 4   |     | dBm  |

| Error Vector Magnitude                                | EVM              | -   | 20  | 45  | %    |

| Output Power Control Range                            |                  | -   | 30  | -   | dB   |

| Over the Air Data Rate                                |                  | -   | 250 | -   | kbps |

| 2nd Harmonic                                          |                  | -   | TBD | -   | dBc  |

| 3rd Harmonic                                          |                  | -   | TBD | -   | dBc  |

<sup>1</sup> SPI Register 12 programmed to 0x00BC which sets output power to nominal (-1 dBm typical).

<sup>&</sup>lt;sup>2</sup> SPI Register 12 programmed to 0x00FF which sets output power to maximum.

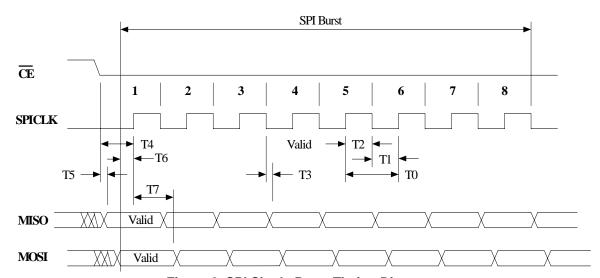

#### **Table 6. Digital Timing Specifications**

(VBATT, VDDINT = 2.7 V, TA = 25 °C, frequency = 16 MHz, unless otherwise noted. SPI timing parameters are referenced to Figure 8.

| Symbol | Parameter                                       | Min | Тур | Max | Unit |

|--------|-------------------------------------------------|-----|-----|-----|------|

| T0     | SPICLK period                                   | 125 |     |     | nS   |

| T1     | Pulse width, SPICLK low                         | 50  |     |     | nS   |

| T2     | Pulse width, SPICLK high                        | 50  |     |     | nS   |

| Т3     | Delay time, MISO data valid from falling SPICLK |     | 15  |     | nS   |

| T4     | Setup time, CE low to rising SPICLK             |     | 15  |     | nS   |

| T5     | Delay time, MISO valid from CE low              |     | 15  |     | nS   |

| T6     | Setup time, MOSI valid to rising SPICLK         |     | 15  |     | nS   |

| T7     | Hold time, MOSI valid from rising SPICLK        |     | 15  |     | nS   |

|        | RST minimum pulse width low (asserted)          | 250 |     |     | nS   |

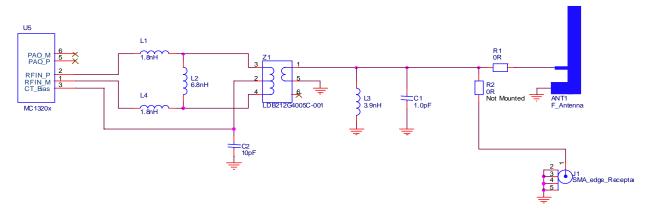

Figure 6 shows a typical AC parameter evaluation circuit.

Figure 6. RF Parametric Evaluation Circuit

## 6 Functional Description

The following sections provide a detailed description of the MC13201 functionality, including operating modes, and the Serial Peripheral Interface (SPI).

## 6.1 MC13201 Operational Modes

The MC13201 has a number of operational modes that allow for low-current operation. Transition from the Off to Idle mode occurs when  $\overline{RST}$  is negated. Once in Idle, the SPI is active and is used to control the IC. Transition to Hibernate and Doze modes is enabled via the SPI. These modes are summarized, along with the transition times, in Table 7. Current drain in the various modes is listed in Table 3, DC Electrical Characteristics.

Table 7. MC13201 Mode Definitions and Transition Times

| Mode      | Definition                                                                                                                                                                                                                                      | Transition Time<br>To or From Idle |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Off       | All IC functions Off, Leakage only. $\overline{\rm RST}$ asserted. Digital outputs are tri-stated including $\overline{\rm IRQ}$                                                                                                                | 10 - 25 ms to Idle                 |

| Hibernate | Crystal Reference Oscillator Off. (SPI not functional.) IC Responds to $\overline{\text{ATTN}}$ . Data is retained.                                                                                                                             | 7 - 20 ms to Idle                  |

| Doze      | Crystal Reference Oscillator On but CLKO output available only if Register 7, Bit 9 = 1 for frequencies of 1 MHz or less. (SPI not functional.) Responds to ATTN and can be programmed to enter Idle Mode through an internal timer comparator. | (300 + 1/CLKO) μs to Idle          |

| Idle      | Crystal Reference Oscillator On with CLKO output available. SPI active.                                                                                                                                                                         |                                    |

| Receive   | Crystal Reference Oscillator On. Receiver On.                                                                                                                                                                                                   | 144 µs from Idle                   |

| Transmit  | Crystal Reference Oscillator On. Transmitter On.                                                                                                                                                                                                | 144 µs from Idle                   |

## 6.2 Serial Peripheral Interface (SPI)

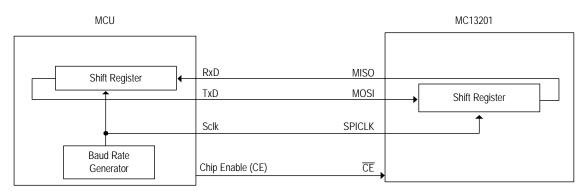

The host microcontroller directs the MC13201, checks its status, and reads/writes data to the device through the 4-wire SPI port. The transceiver operates as a SPI slave device only. A transaction between the host and the MC13201 occurs as multiple 8-bit bursts on the SPI. The SPI signals are:

- 1. Chip Enable ( $\overline{CE}$ ) A transaction on the SPI port is framed by the active low  $\overline{CE}$  input signal. A transaction is a minimum of 3 SPI bursts and can extend to a greater number of bursts.

- 2. SPI Clock (SPICLK) The host drives the SPICLK input to the MC13201. Data is clocked into the master or slave on the leading (rising) edge of the return-to-zero SPICLK and data out changes state on the trailing (falling) edge of SPICLK.

#### NOTE

For Freescale microcontrollers, the SPI clock format is the clock phase control bit CPHA = 0 and the clock polarity control bit CPOL = 0.

- 3. Master Out/Slave In (MOSI) Incoming data from the host is presented on the MOSI input.

- 4. Master In/Slave Out (MISO) The MC13201 presents data to the master on the MISO output.

A typical interconnection to a microcontroller is shown in Figure 7.

Figure 7. SPI Interface

Although the SPI port is fully static, internal memory, timer and interrupt arbiters require an internal clock (CLK<sub>core</sub>), derived from the crystal reference oscillator, to communicate from the SPI registers to internal registers and memory.

## 6.2.1 SPI Burst Operation

The SPI port of an MCU transfers data in bursts of 8 bits with most significant bit (MSB) first. The master (MCU) can send a byte to the slave (transceiver) on the MOSI line and the slave can send a byte to the master on the MISO line. Although an MC13201 transaction is three or more SPI bursts long, the timing of a single SPI burst is shown in Figure 8.

Figure 8. SPI Single Burst Timing Diagram

SPI digital timing specifications are shown in Table 6.

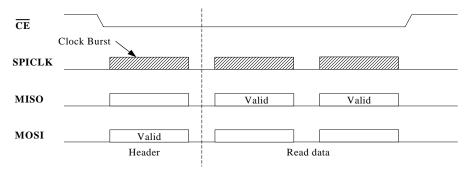

## 6.2.2 SPI Transaction Operation

Although the SPI port of an MCU transfers data in bursts of 8 bits, the MC13201 requires that a complete SPI transaction be framed by  $\overline{\text{CE}}$ , and there will be three (3) or more bursts per transaction. The assertion of  $\overline{\text{CE}}$  to low signals the start of a transaction. The first SPI burst is a write of an 8-bit header to the transceiver (MOSI is valid) that defines a 6-bit address of the internal resource being accessed and identifies the access as being a read or write operation. In this context, a write is data written to the MC13201 and a read is data written to the SPI master. The following SPI bursts will be either the write data (MOSI is valid) to the transceiver or read data from the transceiver (MISO is valid).

Although the SPI bus is capable of sending data simultaneously between master and slave, the MC13201 never uses this mode. The number of data bytes (payload) will be a minimum of 2 bytes and can extend to a larger number depending on the type of access. The number of payload bytes sent will always be an even integer. After the final SPI burst,  $\overline{CE}$  is negated to high to signal the end of the transaction. Refer to the MC13201 Reference Manual, (MC13201RM) for more details on SPI registers and transaction types.

An example SPI read transaction with a 2-byte payload is shown in Figure 9.

Figure 9. SPI Read Transaction Diagram

## 7 Pin Connections

**Table 8. Pin Function Description**

| Pin# | Pin Name           | Туре                  | Description                                                                                                                                                                          | Functionality                                                                                                                                                                                 |  |

|------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | RFIN_M             | RF Input              | RF input/output negative.                                                                                                                                                            | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                              |  |

| 2    | RFIN_P             | RF Input              | RF input/output positive.                                                                                                                                                            | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                              |  |

| 3    | CT_Bias            | Control voltage       | Bias voltage/control signal for external RF components                                                                                                                               | When used with internal T/R switch, provides RX ground reference and TX VDDA reference for use with external balun. Can also be used as a control signal for external LNA, PA, or T/R switch. |  |

| 4    | NC                 |                       | Tie to Ground.                                                                                                                                                                       |                                                                                                                                                                                               |  |

| 5    | PAO_P              | RF Output /DC Input   | RF Power Amplifier Output Positive.                                                                                                                                                  | Open drain. Connect to VDDA through a bias network when used with an external balun. Not used when internal T/R switch is used.                                                               |  |

| 6    | PAO_M              | RF Output/DC Input    | RF Power Amplifier Output Negative.                                                                                                                                                  | Open drain. Connect to VDDA through a bias network when used with an external balun. Not used when internal T/R switch is used.                                                               |  |

| 7    | SM                 | Input                 | Test mode pin.                                                                                                                                                                       | Must be grounded for normal operation.                                                                                                                                                        |  |

| 8    | GPIO4 <sup>1</sup> | Digital Input/ Output | General Purpose Input/Output 4.                                                                                                                                                      | See Footnote 1.                                                                                                                                                                               |  |

| 9    | GPIO3 <sup>1</sup> | Digital Input/ Output | General Purpose Input/Output 3.                                                                                                                                                      | See Footnote 1.                                                                                                                                                                               |  |

| 10   | GPIO2 <sup>1</sup> | Digital Input/ Output | General Purpose Input/Output 2. When gpio_alt_en, Register 9, Bit 7 = 1, GPIO2 functions as a "CRC Valid" indicator.                                                                 | See Footnote 1.                                                                                                                                                                               |  |

| 11   | GPIO1 <sup>1</sup> | Digital Input/ Output | General Purpose Input/Output 1.<br>When gpio_alt_en, Register 9, Bit 7 = 1, GPIO1 functions as an "Out of Idle" indicator.                                                           | See Footnote 1.                                                                                                                                                                               |  |

| 12   | RST                | Digital Input         | Active Low Reset. While held low, the IC is in Off Mode and all internal information is lost from RAM and SPI registers. When high, IC goes to IDLE Mode, with SPI in default state. |                                                                                                                                                                                               |  |

## **Table 8. Pin Function Description (continued)**

| Pin# | Pin Name            | Туре                 | Description                                                                                                                                                                                                                                                                                      | Functionality                                                                                                                                                                 |

|------|---------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | RXTXEN <sup>2</sup> | Digital Input        | Active High. Low to high transition initiates RX or TX sequence depending on SPI setting. Should be taken high after SPI programming to start RX or TX sequence and should be held high through the sequence. After sequence is complete, return RXTXEN to low. When held low, forces Idle Mode. | See Footnote 2                                                                                                                                                                |

| 14   | ATTN <sup>2</sup>   | Digital Input        | Active Low Attention. Transitions IC from either Hibernate or Doze Modes to Idle.                                                                                                                                                                                                                | See Footnote 2                                                                                                                                                                |

| 15   | CLKO                | Digital Output       | Clock output to host MCU. Programmable frequencies of: 16 MHz, 8 MHz, 4 MHz, 2 MHz, 1 MHz, 62.5 kHz, 32.786+ kHz (default), and 16.393+ kHz.                                                                                                                                                     |                                                                                                                                                                               |

| 16   | SPICLK <sup>2</sup> | Digital Clock Input  | External clock input for the SPI interface.                                                                                                                                                                                                                                                      | See Footnote 2                                                                                                                                                                |

| 17   | MOSI <sup>2</sup>   | Digital Input        | Master Out/Slave In. Dedicated SPI data input.                                                                                                                                                                                                                                                   | See Footnote 2                                                                                                                                                                |

| 18   | MISO <sup>3</sup>   | Digital Output       | Master In/Slave Out. Dedicated SPI data output.                                                                                                                                                                                                                                                  | See Footnote 3                                                                                                                                                                |

| 19   | CE <sup>2</sup>     | Digital Input        | Active Low Chip Enable. Enables SPI transfers.                                                                                                                                                                                                                                                   | See Footnote 2                                                                                                                                                                |

| 20   | ĪRQ                 | Digital Output       | Active Low Interrupt Request.                                                                                                                                                                                                                                                                    | Open drain device. Programmable 40 k $\Omega$ internal pull-up. Interrupt can be serviced every 6 $\mu$ s with <20 pF load. Optional external pull-up must be >4 k $\Omega$ . |

| 21   | VDDD                | Power Output         | Digital regulated supply bypass.                                                                                                                                                                                                                                                                 | Decouple to ground.                                                                                                                                                           |

| 22   | VDDINT              | Power Input          | Digital interface supply & digital regulator input. Connect to Battery.                                                                                                                                                                                                                          | 2.0 to 3.4 V. Decouple to ground.                                                                                                                                             |

| 23   | GPIO5 <sup>1</sup>  | Digital Input/Output | General Purpose Input/Output 5.                                                                                                                                                                                                                                                                  | See Footnote 1                                                                                                                                                                |

| 24   | GPIO6 <sup>1</sup>  | Digital Input/Output | General Purpose Input/Output 6.                                                                                                                                                                                                                                                                  | See Footnote 1                                                                                                                                                                |

| 25   | GPIO7 <sup>1</sup>  | Digital Input/Output | General Purpose Input/Output 7.                                                                                                                                                                                                                                                                  | See Footnote 1                                                                                                                                                                |

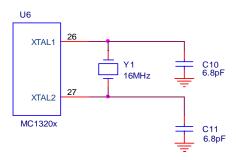

| 26   | XTAL1               | Input                | Crystal Reference oscillator input.                                                                                                                                                                                                                                                              | Connect to 16 MHz crystal and load capacitor.                                                                                                                                 |

#### **Table 8. Pin Function Description (continued)**

| Pin # | Pin Name | Туре         | Description                                                                                                                                                                                                 | Functionality                                 |

|-------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 27    | XTAL2    | Input/Output | Crystal Reference oscillator output  Note: Do not load this pin by using it as a 16 MHz source. Measure 16 MHz output at Pin 15, CLKO, programmed for 16 MHz. See the MC13201 Reference Manual for details. | Connect to 16 MHz crystal and load capacitor. |

| 28    | VDDLO2   | Power Input  | LO2 VDD supply. Connect to VDDA externally.                                                                                                                                                                 |                                               |

| 29    | VDDLO1   | Power Input  | LO1 VDD supply. Connect to VDDA externally.                                                                                                                                                                 |                                               |

| 30    | VDDVCO   | Power Output | VCO regulated supply bypass.                                                                                                                                                                                | Decouple to ground.                           |

| 31    | VBATT    | Power Input  | Analog voltage regulators Input.<br>Connect to Battery.                                                                                                                                                     | Decouple to ground.                           |

| 32    | VDDA     | Power Output | Analog regulated supply Output. Connect to directly VDDLO1 and VDDLO2 externally and to PAO± through a bias network. Note: Do not use this pin to supply circuitry external to the chip.                    | Decouple to ground.                           |

| EP    | Ground   |              | External paddle / flag ground.                                                                                                                                                                              | Connect to ground.                            |

The transceiver GPIO pins default to inputs at reset. There are no programmable pullups on these pins. Unused GPIO pins should be tied to ground if left as inputs, or if left unconnected, they should be programmed as outputs set to the low state.

<sup>&</sup>lt;sup>2</sup> During low power modes, input must remain driven by MCU.

<sup>&</sup>lt;sup>3</sup> By default MISO is tri-stated when  $\overline{\text{CE}}$  is <u>neg</u>ated. For low power operation, miso\_hiz\_en (Bit 11, Register 07) should be set to zero so that MISO is driven low when  $\overline{\text{CE}}$  is negated.

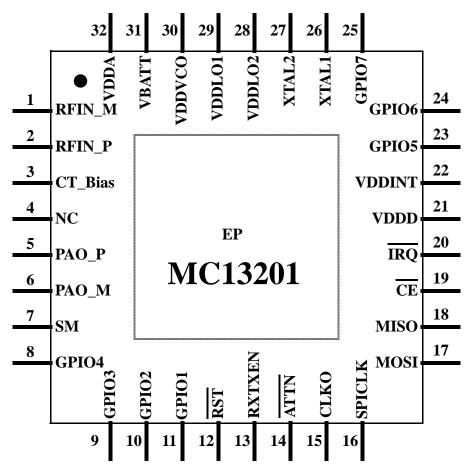

Figure 10. Pin Connections (Top View)

## 8 Crystal Oscillator Reference Frequency

This section provides application specific information regarding crystal oscillator reference design and recommended crystal usage.

## 8.1 Crystal Oscillator Design Considerations

The 802.15.4 Standard requires that several frequency tolerances be kept within  $\pm$  40 ppm accuracy. This means that a total offset up to 80 ppm between transmitter and receiver will still result in acceptable performance. The MC13201 transceiver provides onboard crystal trim capacitors to assist in meeting this performance.

The primary determining factor in meeting this specification is the tolerance of the crystal oscillator reference frequency. A number of factors can contribute to this tolerance and a crystal specification will quantify each of them:

- 1. The initial (or make) tolerance of the crystal resonant frequency itself.

- 2. The variation of the crystal resonant frequency with temperature.

- 3. The variation of the crystal resonant frequency with time, also commonly known as aging.

- 4. The variation of the crystal resonant frequency with load capacitance, also commonly known as pulling. This is affected by:

- a) The external load capacitor values initial tolerance and variation with temperature.

- b) The internal trim capacitor values initial tolerance and variation with temperature.

- c) Stray capacitance on the crystal pin nodes including stray on-chip capacitance, stray package capacitance and stray board capacitance; and its initial tolerance and variation with temperature.

- 5. Whether or not a frequency trim step will be performed in production

Freescale requires the use of a 16 MHz crystal with a <9 pF load capacitance. The MC13201 does not contain a reference divider, so 16 MHz is the only frequency that can be used. A crystal requiring higher load capacitance is prohibited because a higher load on the amplifier circuit may compromise its performance. The crystal manufacturer defines the load capacitance as that total external capacitance seen across the two terminals of the crystal. The oscillator amplifier configuration used in the MC13201 requires two balanced load capacitors from each terminal of the crystal to ground. As such, the capacitors are seen to be in series by the crystal, so each must be <18 pF for proper loading.

In the Figure 11 crystal reference schematic, the external load capacitors are shown as 6.8 pF each, used in conjunction with a crystal that requires an 8 pF load capacitance. The default internal trim capacitor value (2.4 pF) and stray capacitance total value (6.8 pF) sum up to 9.2 pF giving a total of 16 pF. The value for the stray capacitance was determined empirically assuming the default internal trim capacitor value and for a specific board layout. A different board layout may require a different external load capacitor value. The on-chip trim capability may be used to determine the closest standard value by adjusting the trim value via the SPI and observing the frequency at CLKO. Each internal trim load capacitor has a trim range of approximately 5 pF in 20 fF steps.

Initial tolerance for the internal trim capacitance is approximately  $\pm 15\%$ .

Since the MC13201 contains an on-chip reference frequency trim capability, it is possible to trim out virtually all of the initial tolerance factors and put the frequency within 0.12 ppm on a board-by-board basis. Individual trimming of each board in a production environment allows use of the lowest cost crystal, but requires that each board go through a trimming procedure. This step can be avoided by using/specifying a crystal with a tighter stability tolerance, but the crystal will be slightly higher in cost.

A tolerance analysis budget may be created using all the previously stated factors. It is an engineering judgment whether the worst case tolerance will assume that all factors will vary in the same direction or if the various factors can be statistically rationalized using RSS (Root-Sum-Square) analysis. The aging factor is usually specified in ppm/year and the product designer can determine how many years are to be assumed for the product lifetime. Taking all of the factors into account, the product designer can determine the needed specifications for the crystal and external load capacitors to meet the 802.15.4 Standard.

Y1 = Daishinku KDS - DSX321G ZD00882

Figure 11. MC13201 Modem Crystal Circuit

## 8.2 Crystal Requirements

The suggested crystal specification for the MC13201 is shown in Table 10. A number of the stated parameters are related to desired package, desired temperature range and use of crystal capacitive load trimming. For more design details and suggested crystals, see application note AN3251, Reference Oscillator Crystal Requirements for MC1319x, MC1320x, and MC1321x.

| Parameter                                            | Value     | Unit | Condition                      |  |

|------------------------------------------------------|-----------|------|--------------------------------|--|

| Frequency                                            | 16.000000 | MHz  |                                |  |

| Frequency tolerance (cut tolerance) <sup>2</sup>     | ± 10      | ppm  | at 25 °C                       |  |

| Frequency stability (temperature drift) <sup>3</sup> | ± 15      | ppm  | Over desired temperature range |  |

| Aging <sup>4</sup>                                   | ± 2       | ppm  | max                            |  |

| Equivalent series resistance <sup>5</sup>            | 43        | Ω    | max                            |  |

| Load capacitance <sup>6</sup>                        | 5 - 9     | pF   |                                |  |

| Shunt capacitance                                    | <2        | pF   | max                            |  |

| Mode of oscillation                                  |           |      | fundamental                    |  |

Table 9. MC13201 Crystal Specifications<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> User must be sure manufacturer specifications apply to the desired package.

<sup>&</sup>lt;sup>2</sup> A wider frequency tolerance may acceptable if application uses trimming at production final test.

- <sup>3</sup> A wider frequency stability may be acceptable if application uses trimming at production final test.

- <sup>4</sup> A wider aging tolerance may be acceptable if application uses trimming at production final test.

- <sup>5</sup> Higher ESR may be acceptable with lower load capacitance.

- <sup>6</sup> Lower load capacitance can allow higher ESR and is better for low temperature operation in Doze mode.

#### 8.3 Low Power Considerations

- Program and use the modem IO pins properly for low power operation

- All unused modem GPIOx signals must be used one of 2 ways:

- If the Off mode is to be used as a long term low power mode, unused GPIO should be tied to ground. The default GPIO mode is an input and there will be no conflict.

- If only Hibernate and/or Doze modes are used as long term low power modes, the GPIO should programmed as outputs in the low state.

- When modem GPIO are used as outputs:

- Pullup resistors should be provided (can be provided by the MCU IO pin if tied to the MCU) if the modem Off condition is to be used as a long term low power mode.

- During Hibernate and/or Doze modes, the GPIO will retain its programmed output state.

- If the modem GPIO is used as an input, the GPIO should be driven by its source during all low power modes or a pullup resistor should be provided.

- Digital outputs  $\overline{IRQ}$ , MISO, and CLKO:

- MISO is always an output. During Hibernate, Doze, and active modes, the default condition is for the MISO output to go to tristate when \(\overline{CE}\) is de-asserted, and this can cause a problem with the MCU because one of its inputs can float. Program Control\_B Register 07, Bit 11, miso\_hiz\_en = 0 so that MISO is driven low when \(\overline{CE}\) is de-asserted. As a result, MISO will not float when Doze or Hibernate Mode is enabled.

- IRQ is an open drain output (OD) and should always have a pullup resistor (typically provided by the MCU IO). IRQ acts as the interrupt request output.

#### NOTE

It is good practice to have the  $\overline{IRQ}$  interrupt input to the MCU disabled during the hardware reset to the modem. After releasing the modem hardware reset, the interrupt request input to the MCU can then be enabled to await the  $\overline{IRQ}$  that signifies the modem is ready and in Idle mode; this can prevent a possible extraneous false interrupt request.

- CLKO is always an output. During Hibernate CLKO retains its output state, but does not toggle. During Doze, CLKO may toggle depending on whether it is being used.

- If the MCU is also going to be used in low power modes, be sure that all unused IO are programmed properly for low power operation (typically best case is as outputs in the low state). The MC13201 is commonly used with the Freescale MC9S08GT/GB 8-bit devices. For these MCUs:

- Use only STOP2 and STOP3 modes (not STOP1) with these devices where the GPIO states are retained. The MCU must retain control of the MC13201 IO during low power operation.

- As stated above all unused GPIO should be programmed as outputs low for lowest power and no floating inputs.

— MC9S08GT devices have IO signals that are not pinned-out on the package. These signals must also be initialized (even though they cannot be used) to prevent floating inputs.

## 8.4 Transceiver RF Configurations and External Connections

The MC13201 radio has features that allow for a flexible as well as low cost RF interface:

- Programmable output power 0 dBm nominal output power, programmable from -27 dBm to +4 dBm typical

- <-91 dBm (typical) receive sensitivity At 1% PER, 20-byte packet (well above 802.15.4 Standard of -85 dBm)

- Optional integrated transmit/receive (T/R) switch for low cost operation With internal PAs and LNA, the internal T/R switch allows a minimal part count radio interface using only a single balun to interface to a single-ended antenna

- Maximum flexibility There are full differential RF I/O pins for use with the internal T/R switch. Optionally, these pins become the RF\_IN signals and a separate set of full differential PA outputs are also provided. Separate inputs and outputs allow for a variety of RF configurations including external LNA and PA for increased range

- CT\_Bias Output The CT\_Bias signal provides a switched bias reference for use with the internal T/R switch, and alternatively can be programmed as an antenna switch signal for use with an external antenna switch

- Onboard trim capability for 16 MHz crystal reference oscillator The 802.15.4 Standard puts a +/- 40 ppm requirement on the carrier frequency. The onboard trim capability of the modem crystal oscillator eliminates need for external variable capacitors and allows for automated production frequency calibration. Also tighter tolerance can produce greater receive sensitivity

#### 8.5 RF Interface Pins

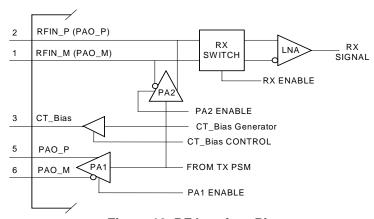

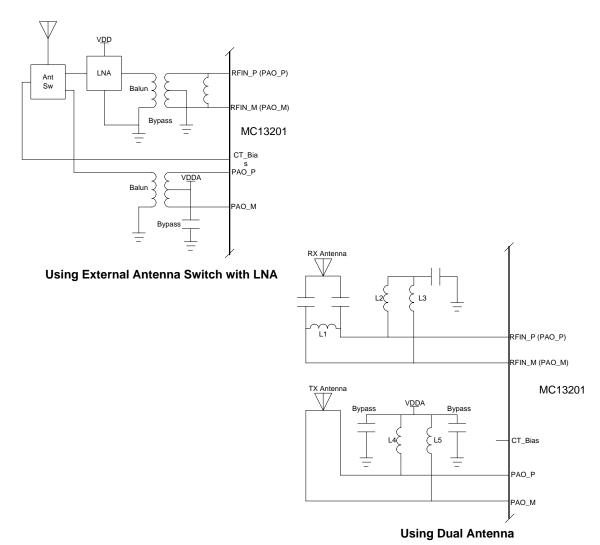

Figure 12 shows the RF interface pins and the associated analog blocks. Notice that separate PA blocks are associated with RFIN\_x and PAO\_x signal pairs. The RF interface allows both single port differential operation and dual port differential operation.

Figure 12. RF Interface Pins

### 8.5.1 Single Port Operation

The integrated RF switch allows users to operate in a single port configuration. In Single Port Mode, an internal RX switch and separate PA are used and pins RFIN\_P (PAO\_P) and RFIN\_M (PAO\_M) become bidirectional and connect both for TX and RX. When receiving, the RX switch is enabled to the internal LNA and the TX PA is disabled. When transmitting, the RX switch is disabled (isolating the LNA) and a TX PA is enabled. The optional CT\_Bias pin provides a reference or bias voltage which is at VDDA for transmit and is at ground for receive. This signal can be used to provide the proper bias voltage to a balun that converts a single-ended antenna to the differential interface required by the transceiver.

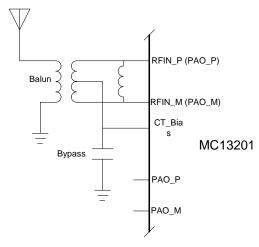

Figure 13. Single Port RF Operation with a Balun

Figure 13 shows a single port example with a balun. The CT\_Bias is connected to the balun center-tap providing the proper DC bias voltage to the balun depending on RX or TX.

## 8.5.2 **Dual Port Operation**

A second set of pins designated PAO\_P and PAO\_N allow operation in a dual port configuration. There are separate paths for transmit and receive with the optional CT\_Bias pin providing a signal that indicates if the radio is in TX or RX Mode which then can be used to drive an external low noise amplifier, power amplifier, or antenna switch.

In dual port operation, the RFIN\_P and RFIN\_N are inputs only, the internal RX switch to the LNA is enabled to receive, and the associated TX PA stays disabled. Pins PAO\_P and PAO\_N become the differential output pins and the associated TX PA is enabled for transmit.

Figure 14 shows two dual port configurations. First is a single antenna configuration with an external low noise amplifier (LNA) for greater range. An external antenna switch is used to multiplex the antenna between receive and transmit. An LNA is in the receive path to add gain for greater receive sensitivity. Two external baluns are required to convert the single-ended antenna switch signals to the differential signals required by the radio. Separate RFIN and PAO signals are provided for connection with the baluns, and the CT\_bias signal is programmed to provide the external switch control. The polarity of the external switch control is selectable.

Figure 14 also shows a dual antenna configuration where there is a RX antenna and a TX antenna. For the receive side, the RX antenna is ac-coupled to the differential RFIN inputs and these capacitors along with inductor L1 form a matching network. Inductors L2 and L3 are ac-coupled to ground to form a frequency trap. For the transmit side, the TX antenna is connected to the differential PAO outputs, and inductors L4 and L5 provide DC-biasing to VDDA but are ac-isolated. CT\_Bias is not required or used.

Figure 14. Dual Port RF Configuration Examples

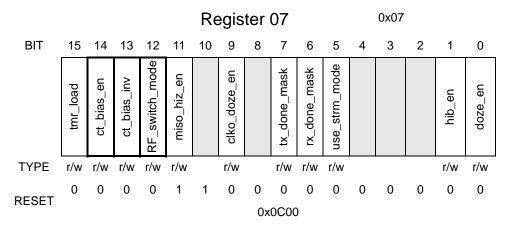

## 8.6 Controlling RF Modes of Operation

Use of the RF interface pins and RF modes of operation are controlled through several bits of modem Control\_B Register 07. Figure 15 shows the model for Register 07 with the RF interface control bits highlighted.

Figure 15. Control\_B Register 07 Model

The RF interface control bits include:

- RF\_switch\_mode (Bit 12) This bit selects Dual Port Mode versus Single Port Mode:

- The default condition (Bit 12 = 0) is Dual Port Mode where the RF inputs are RFIN\_M and RFIN\_P and the RF outputs are PAO\_M and PAO\_P, and operation is as described in Section 8.5.2, "Dual Port Operation. The use of CT\_Bias pin in Dual Port Mode is controlled by Bit 13 and Bit 12.

- When Bit = 1, the Single Port Mode is selected where RFIN\_M (PAO\_M) and RFIN\_P (PAO\_P) become bidirectional pins and operation is as described in Section 8.5.1, "Single Port Operation. The use of CT\_Bias pin in Dual Port Mode in controlled by Bit 13 and Bit 12.

- Ct\_bias\_en (Bit 14) This bit is the enable for the CT\_Bias output. When Bit 14 = 0 (default), the CT\_Bias is disabled and stays in a Hi-Z or tri-stated condition. When Bit 14 = 1, the CT\_Bias output is active and its state is controlled by the selected mode (Bit 12), ct\_bias\_inv, and operation of the radio.

- Ct\_bias\_inv (Bit 13) This bit only affects the state of CT\_Bias when Dual Port Mode is selected and CT\_bias is active. The CT\_Bias changes state in Dual Port Mode based on the TX or RX state of the radio. The ct\_bias\_inv bit causes the sense of the active state to change or invert based on Bit 13's setting. In this manner, the user can select the CT\_Bias as a control signal for external components and make the control signal active high or active low.

Table 10 summarizes the operation of the RF interface control bits.

**Table 10. RF Interface Control Bits**

| Bit | Designation    | Default | Operation                                                                                                                                                                                                                                          |

|-----|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | ct_bias_en     | 0       | 1 = CT_Bias enabled. Output state is defined by Table 11. 0 = CT_Bias disabled. Output state is tri-stated.                                                                                                                                        |

| 13  | ct_bias_inv    | 0       | The output state of CT_Bias under varying conditions is defined in Table 11. This bit only has effect for dual port operation.  1 = CT_Bias inverted.  0 = CT_Bias not inverted                                                                    |

| 12  | RF_switch_mode | 0       | 1= Single Port Mode selected where RF switch is active and RFIN_M and RFIN_P and bidirectional signals. 0 = Dual Port Mode selected where RFIN_M and RFIN_P are inputs only and PAO_P and PAO_N are separate outputs. (This is default operation). |

## 8.7 RF Control Output CT Bias

CT\_Bias is a useful signal for interface with external RF components. It must be enabled via the ct\_bias\_en control bit, and then its state is determined first by the selected RF mode and then by the active state of the radio, i.e., whether a TX or RX operation is active:

- Single Port Operation In this mode, the CT\_Bias can be used to establish the proper DC bias voltage to a balun depending on the RX state versus TX state as described in Section 8.5.1, "Single Port Operation. Note that in single port operation, the ct\_bias\_inv has no effect and CT\_Bias is at VDDA for TX and is at ground for RX.

- Dual Port Operation In this mode, the CT\_Bias can be used as a control signal to enable a LNA or PA or to determine the direction of an antenna switch as described in Section 8.5.2, "Dual Port Operation. In dual port operation, ct-bias\_inv is used to control the sense of the output control, i.e., CT\_Bias can be active high or active low for TX and vice-versa for RX.

Table 11 defines the CT\_Bias output state depending on control bits and operation mode of the modem. Note that the output state is also defined in Idle, Hibernate, and Doze state as well as RX and TX operation.

Table 11. CT\_Bias Output vs. Register Settings

| Mode | CT_Bias_en | RF_switch_mode | CT_Bias_inv | CT_Bias |

|------|------------|----------------|-------------|---------|

| RX   | 1          | 1              | 0           | 0       |

| RX   | 1          | 1              | 1           | 0       |

| RX   | 1          | 0              | 0           | 0       |

| RX   | 0          | Х              | Х           | Hi-Z    |

| RX   | 1          | 1              | 0           | 1       |

| TX   | 1          | 1              | 0           | 1       |

| TX   | 1          | 1              | 1           | 1       |

| TX   | 1          | 0              | 0           | 1       |

| Mode      | CT_Bias_en | RF_switch_mode | CT_Bias_inv | CT_Bias   |

|-----------|------------|----------------|-------------|-----------|

| TX        | 1          | 0              | 1           | 0         |

| TX        | 0          | Х              | Х           | Hi-Z      |

| Idle      | 1          | Х              | Х           | 0         |

| Idle      | 0          | Х              | Х           | Hi-Z      |

| Doze      | 1          | Х              | Х           | 0         |

| Doze      | 0          | Х              | Х           | Hi-Z      |

| Hibernate | 1          | Х              | Х           | 0 (Low-Z) |

| Hibernate | 0          | Х              | Х           | Hi-Z      |

| Off       | Х          | Х              | Х           | Unknown   |

Table 11. CT\_Bias Output vs. Register Settings (continued)

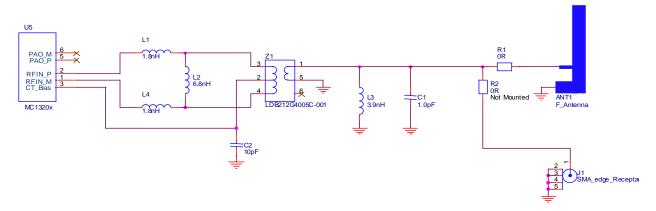

## 8.8 RF Single Port Application with an F Antenna

Figure 16 shows a typical single port RF application in which part count is minimized and a printed copper F antenna is used for low cost. Only the RFIN port of the MC13201 is required because the differential port is bi-directional and uses the on-chip T/R switch. Matching to near 50 Ohms is accomplished with L1, L2, L3, and the traces on the PCB. A balun transforms the differential signal to single-ended to interface with the F antenna.

The proper DC bias to the RFIN\_x (PAO\_x) pins is provided through the balun. The CT\_Bias pin provides the proper bias voltage point to the balun depending on operation, that is, CT\_Bias is at VDDA voltage for transmit and is at ground for receive. CT\_Bias is switched between these two voltages based on the operation. Capacitor C2 provides some high frequency bypass to the DC bias point. The L3/C1 network provides a simple bandpass filter to limit out-of-band harmonics from the transmitter.

Figure 16. RF Single Port Application with an F-Antenna

## 9 Packaging Information

Figure 17. Outline Dimensions for QFN-32, 5x5 mm (Case 1311-03, Issue E)

MC13201 Technical Data, Rev. 1.3,

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### F-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

**Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate

Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005, 2006, 2007, 2008. All rights reserved.

Document Number: MC13201 Rev. 1.3,

04/2008

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331