# P-Channel 30 V (D-S) MOSFET

| PRODUCT SUMMARY     |                                    |                                    |  |  |

|---------------------|------------------------------------|------------------------------------|--|--|

| V <sub>DS</sub> (V) | $R_{DS(on)}(\Omega)$ Max.          | I <sub>D</sub> (A) <sup>a, e</sup> |  |  |

|                     | 0.031 at V <sub>GS</sub> = - 10 V  | - 7.7                              |  |  |

| - 30                | 0.035 at V <sub>GS</sub> = - 4.5 V | - 7.3                              |  |  |

|                     | 0.045 at V <sub>GS</sub> = - 2.5 V | - 6.4                              |  |  |

#### **FEATURES**

- TrenchFET® Power MOSFET

- Low-on Resistance

- Ultra-Small 1.6 mm x 1.6 mm Maximum Outline

- Ultra-Thin 0.6 mm Maximum Height

- Pin Compatible to Si8409DB

- Material categorization: For definitions of compliance please see www.vishay.com/doc?99912

HALOGEN **FREE**

#### **APPLICATIONS**

- Mobile Computing, Smart Phones, Tablet PCs

- Load Switch

- Battery Switch

- Charger Switch

- OVP Switch

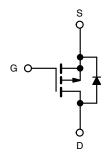

P-Channel MOSFET

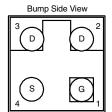

### MICRO FOOT®

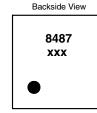

**Device Marking:**

xxx = Date/Lot Traceability Code

Ordering Information: Si8487DB-T1-E1 (Lead (Pb)-free and Halogen-free)

| Parameter                                          | Symbol                            | Limit                | Unit                |          |  |

|----------------------------------------------------|-----------------------------------|----------------------|---------------------|----------|--|

| Drain-Source Voltage                               |                                   | V <sub>DS</sub>      | - 30                |          |  |

| Gate-Source Voltage                                |                                   | V <sub>GS</sub> ± 12 |                     | V        |  |

|                                                    | T <sub>A</sub> = 25 °C            |                      | - 7.7 <sup>a</sup>  |          |  |

| Continuous Drain Current /T 150 °C)                | T <sub>A</sub> = 70 °C            |                      | - 6.2 <sup>a</sup>  |          |  |

| Continuous Drain Current (T <sub>J</sub> = 150 °C) | T <sub>A</sub> = 25 °C            | I <sub>D</sub>       | - 4.9 <sup>b</sup>  |          |  |

|                                                    | T <sub>A</sub> = 70 °C            |                      | - 4 <sup>b</sup>    | Α        |  |

| Pulsed Drain Current (t = 300 μs)                  |                                   | I <sub>DM</sub>      | - 25                |          |  |

| 0 11 0 0 0 1                                       | T <sub>A</sub> = 25 °C            | la la                | - 2.3 <sup>a</sup>  |          |  |

| Continuous Source-Drain Diode Current              | T <sub>A</sub> = 25 °C            | I <sub>S</sub>       | - 0.92 <sup>b</sup> |          |  |

|                                                    | T <sub>A</sub> = 25 °C            |                      | 2.7 <sup>a</sup>    |          |  |

| Maximum Daylar Dissination                         | T <sub>A</sub> = 70 °C            | P <sub>D</sub>       | 1.8 <sup>a</sup>    | $\Box$ w |  |

| Maximum Power Dissipation                          | T <sub>A</sub> = 25 °C            | ' b                  | 1.1 <sup>b</sup>    | - vv     |  |

|                                                    | T <sub>A</sub> = 70 °C            |                      | 0.73 <sup>b</sup>   | 7        |  |

| Operating Junction and Storage Temperature R       | T <sub>J</sub> , T <sub>stg</sub> | - 55 to 150          |                     |          |  |

| Package Reflow Conditions <sup>c</sup>             | $V_{PR}$                          |                      | 260                 | °C       |  |

| rackage nellow Collulions                          | IR/Convection                     |                      | 260                 |          |  |

- a. Surface mounted on 1" x 1" FR4 board with full copper, t = 5 s.

- b. Surface mounted on 1" x 1" FR4 board with minimum copper, t = 5 s.

- c. Refer to IPC/JEDEC (J-STD-020), no manual or hand soldering.

- d. In this document, any reference to case represents the body of the MICRO FOOT device and foot is the bump.

- e. Based on T<sub>A</sub> = 25 °C.

## **Si8487DB**

## Vishay Siliconix

| THERMAL RESISTANCE RATINGS                  |         |            |         |         |              |  |

|---------------------------------------------|---------|------------|---------|---------|--------------|--|

| Parameter                                   |         | Symbol     | Typical | Maximum | Unit         |  |

| Maximum Junction-to-Ambient <sup>a, b</sup> | t = 5 s | $R_{thJA}$ | 35      | 45      | °C/W         |  |

| Maximum Junction-to-Ambient <sup>c, d</sup> | t = 5 s | $R_{thJA}$ | 85      | 110     | C/ <b>VV</b> |  |

#### Notes:

- a. Surface mounted on 1" x 1" FR4 board with full copper, t = 5 s.

- b. Maximum under steady state conditions is 85 °C/W.

- c. Surface mounted on  $1^{\circ}$  x  $1^{\circ}$  FR4 board with minimum copper, t = 5 s.

- d. Maximum under steady state conditions is 175 °C/W.

| Parameter                                     | Symbol                  | Test Conditions                                                             | Min.  | Тур.   | Max.               | Unit  |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------------------|-------|--------|--------------------|-------|

| Static                                        |                         |                                                                             |       |        |                    |       |

| Drain-Source Breakdown Voltage                | V <sub>DS</sub>         | $V_{GS} = 0 \text{ V, } I_{D} = -250 \mu\text{A}$                           | - 30  |        |                    | V     |

| V <sub>DS</sub> Temperature Coefficient       | $\Delta V_{DS}/T_{J}$   | I <sub>D</sub> = - 250 μA                                                   |       | - 21   |                    | mV/°C |

| V <sub>GS(th)</sub> Temperature Coefficient   | $\Delta V_{GS(th)}/T_J$ | 1 <sub>D</sub> = - 250 μΑ                                                   |       | 3.3    |                    |       |

| Gate-Source Threshold Voltage                 | V <sub>GS(th)</sub>     | $V_{DS} = V_{GS}, I_{D} = -250 \mu A$                                       | - 0.6 |        | - 1.2              | V     |

| Gate-Source Leakage                           | I <sub>GSS</sub>        | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 12 \text{ V}$                           |       |        | ± 100              | nA    |

| Zara Cata Valtaga Drain Current               | 1                       | V <sub>DS</sub> = - 30 V, V <sub>GS</sub> = 0 V                             |       |        | - 1                |       |

| Zero Gate Voltage Drain Current               | I <sub>DSS</sub>        | V <sub>DS</sub> = - 30 V, V <sub>GS</sub> = 0 V, T <sub>J</sub> = 70 °C     |       |        | - 10               | μΑ    |

| On-State Drain Current <sup>a</sup>           | I <sub>D(on)</sub>      | $V_{DS} \le -5 \text{ V}, V_{GS} = -4.5 \text{ V}$                          | - 5   |        |                    | Α     |

|                                               | , ,                     | V <sub>GS</sub> = - 10 V, I <sub>D</sub> = - 2 A                            |       | 0.025  | 0.031              |       |

| Drain-Source On-State Resistance <sup>a</sup> | R <sub>DS(on)</sub>     | $V_{GS} = -4.5 \text{ V}, I_D = -2 \text{ A}$                               |       | 0.028  | 0.035              | Ω     |

|                                               | , ,                     | V <sub>GS</sub> = - 2.5 V, I <sub>D</sub> = - 1 A                           |       | 0.036  | 0.045              |       |

| Forward Transconductance <sup>a</sup>         | 9 <sub>fs</sub>         | V <sub>DS</sub> = - 10 V, I <sub>D</sub> = - 2 A                            |       | 16     |                    | S     |

| Dynamic <sup>b</sup>                          |                         |                                                                             |       |        |                    |       |

| Input Capacitance                             | C <sub>iss</sub>        |                                                                             |       | 2240   |                    | pF    |

| Output Capacitance                            | C <sub>oss</sub>        | V <sub>DS</sub> = - 15 V, V <sub>GS</sub> = 0 V, f = 1 MHz                  |       | 200    |                    |       |

| Reverse Transfer Capacitance                  | C <sub>rss</sub>        |                                                                             |       | 165    |                    |       |

| Total Gate Charge                             | Qg                      | $V_{DS} = -15 \text{ V}, V_{GS} = -10 \text{ V}, I_D = -2 \text{ A}$        |       | 52     | 80                 | nC    |

|                                               |                         | V <sub>DS</sub> = - 15 V, V <sub>GS</sub> = - 4.5 V, I <sub>D</sub> = - 2 A |       | 25     | 40                 |       |

| Gate-Source Charge                            | $Q_{gs}$                |                                                                             |       | 4.1    |                    |       |

| Gate-Drain Charge                             | $Q_{gd}$                |                                                                             |       | 5.7    |                    |       |

| Gate Resistance                               | $R_{q}$                 | V <sub>GS</sub> = - 0.1 V, f = 1 MHz                                        |       | 15     |                    | Ω     |

| Turn-On Delay Time                            | t <sub>d(on)</sub>      |                                                                             |       | 25     | 50                 |       |

| Rise Time                                     | t <sub>r</sub>          | $V_{DD} = -15 \text{ V}, R_1 = 15 \Omega$                                   |       | 22     | 45                 |       |

| Turn-Off Delay Time                           | t <sub>d(off)</sub>     | $I_D \cong -2 \text{ A}, V_{GEN} = -4.5 \text{ V}, R_g = 1 \Omega$          |       | 195    | 390                |       |

| Fall Time                                     | t <sub>f</sub>          |                                                                             |       | 60     | 120                |       |

| Turn-On Delay Time                            | t <sub>d(on)</sub>      |                                                                             |       | 7      | 15                 | ns    |

| Rise Time                                     | t <sub>r</sub>          | $V_{DD} = -15 \text{ V}, R_{L} = 15 \Omega$                                 |       | 10     | 20                 | 1     |

| Turn-Off Delay Time                           | t <sub>d(off)</sub>     | $I_D \cong -2 \text{ A}, V_{GEN} = -10 \text{ V}, R_g = 1 \Omega$           |       | 290    | 580                |       |

| Fall Time                                     | t <sub>f</sub>          |                                                                             |       | 60     | 120                |       |

| <b>Drain-Source Body Diode Characteris</b>    | stics                   |                                                                             |       |        |                    |       |

| Continuous Source-Drain Diode                 | I <sub>S</sub>          | T <sub>A</sub> = 25 °C                                                      |       |        | - 2.3 <sup>c</sup> |       |

| Pulse Diode Forward Current                   | I <sub>SM</sub>         |                                                                             |       |        | - 25               | A     |

| Body Diode Voltage                            | V <sub>SD</sub>         | I <sub>S</sub> = - 2 A, V <sub>GS</sub> = 0 V                               |       | - 0.75 | - 1.2              | V     |

| Body Diode Reverse Recovery Time              | t <sub>rr</sub>         |                                                                             |       | 86     | 170                | ns    |

| Body Diode Reverse Recovery Charge            | Q <sub>rr</sub>         | l <sub>F</sub> = - 2 A, dl/dt = 100 A/μs, T <sub>J</sub> = 25 °C            |       | 85     | 170                | nC    |

| Reverse Recovery Fall Time                    | Ic = - 2 A              |                                                                             |       | 23     |                    |       |

| Reverse Recovery Rise Time                    | t <sub>b</sub>          |                                                                             |       | 63     |                    | ns    |

#### Notes:

- a. Pulse test; pulse width  $\leq$  300  $\mu s,$  duty cycle  $\leq$  2 %.

- b. Guaranteed by design, not subject to production testing.

- c. Surface mounted on 1" x 1" FR4 board with full copper, t = 5 s.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

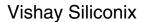

#### **Output Characteristics**

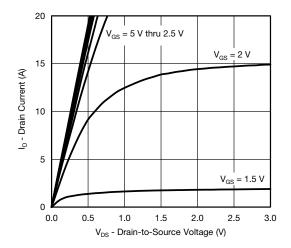

On-Resistance vs. Drain Current

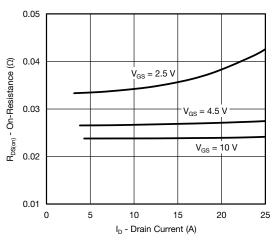

**Gate Charge**

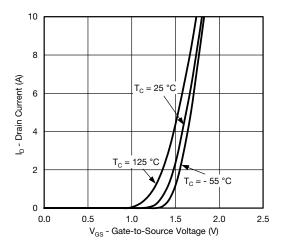

**Transfer Characteristics**

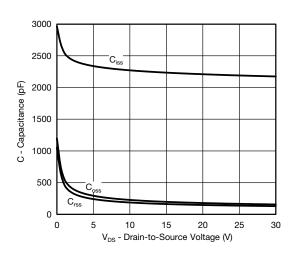

Capacitance

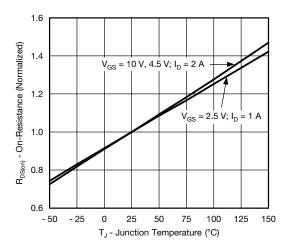

On-Resistance vs. Junction Temperature

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

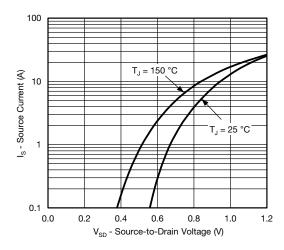

Source-Drain Diode Forward Voltage

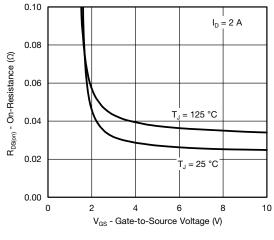

On-Resistance vs. Gate-to-Source Voltage

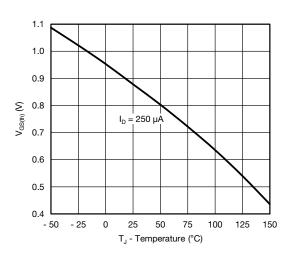

**Threshold Voltage**

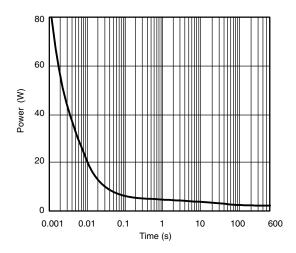

Single Pulse Power, Junction-to-Ambient

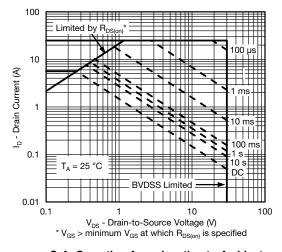

Safe Operating Area, Junction-to-Ambient

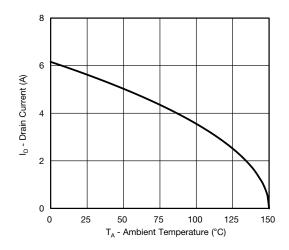

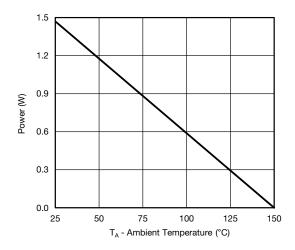

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

**Power Derating**

**Current Derating\***

Note:

When mounted on 1" x 1" FR4 with full copper.

<sup>\*</sup> The power dissipation  $P_D$  is based on  $T_{J(max.)}$  = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.

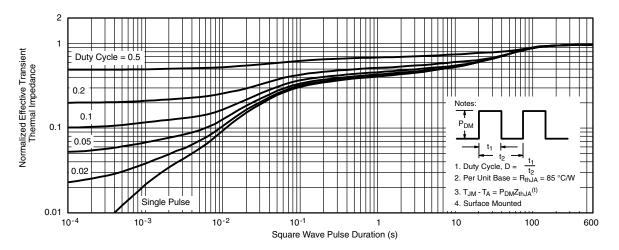

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

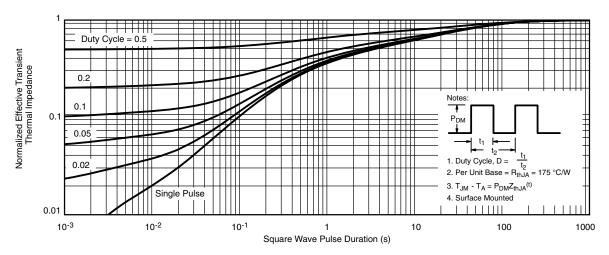

Normalized Thermal Transient Impedance, Junction-to-Ambient (1" x 1" FR4 Board with Full Copper)

Normalized Thermal Transient Impedance, Junction-to-Ambient (1" x 1" FR4 Board with Minimum Copper)

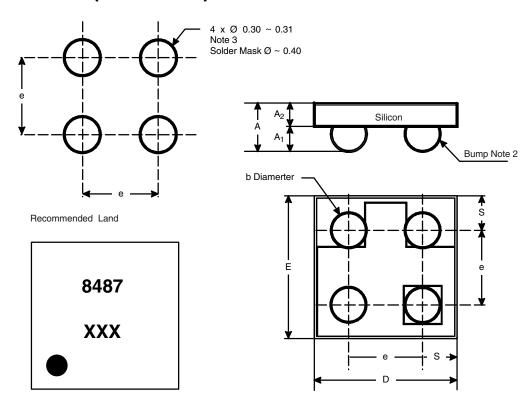

#### **PACKAGE OUTLINE**

### MICRO FOOT: 4-BUMP (0.8 mm PITCH)

Mark on Backside of Die

Notes (Unless otherwise specified):

- 1. Laser mark on the silicon die back, coated with a thin metal.

- 2. Bumps are 95.5 Sn/3.8 Ag/0.7 Cu.

- 3. Non-solder mask defined copper landing pad.

- 4. The flat side of wafers is oriented at the bottom.

| Dim.           | Millimeters <sup>a</sup> |       | Inches |        |  |

|----------------|--------------------------|-------|--------|--------|--|

| Dim.           | Min.                     | Max.  | Min.   | Max.   |  |

| Α              | 0.550                    | 0.600 | 0.0216 | 0.0236 |  |

| A <sub>1</sub> | 0.260                    | 0.290 | 0.0102 | 0.0114 |  |

| A <sub>2</sub> | 0.290                    | 0.310 | 0.0114 | 0.0122 |  |

| b              | 0.370                    | 0.410 | 0.0146 | 0.0161 |  |

| D              | 1.520                    | 1.600 | 0.0598 | 0.0630 |  |

| E              | 1.520                    | 1.600 | 0.0598 | 0.0630 |  |

| е              | 0.800                    |       | 0.0    | 315    |  |

| S              | 0.360                    | 0.400 | 0.0142 | 0.0157 |  |

#### Notes:

a. Use millimeters as the primary measurement.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg263483">www.vishay.com/ppg263483</a>.

# PCB Design and Assembly Guidelines For MICRO FOOT® Products

Johnson Zhao

#### INTRODUCTION

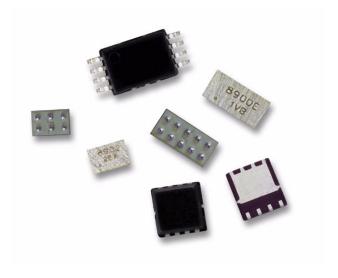

Vishay Siliconix's MICRO FOOT product family is based on a wafer-level chip-scale packaging (WL-CSP) technology that implements a solder bump process to eliminate the need for an outer package to encase the silicon die. MICRO FOOT products include power MOSFETs, analog switches, and power ICs.

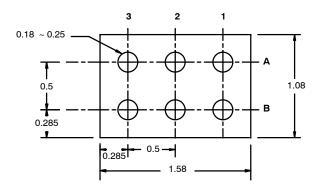

For battery powered compact devices, this new packaging technology reduces board space requirements, improves thermal performance, and mitigates the parasitic effect typical of leaded packaged products. For example, the 6-bump MICRO FOOT Si8902EDB common drain power MOSFET, which measures just 1.6 mm x 2.4 mm, achieves the same performance as TSSOP-8 devices in a footprint that is 80% smaller and with a 50% lower height profile (Figure 1). A MICRO FOOT analog switch, the 6-bump DG3000DB, offers low charge injection and 1.4 W on-resistance in a footprint measuring just 1.08 mm x 1.58 mm (Figure 2).

Vishay Siliconix MICRO FOOT products can be handled with the same process techniques used for high-volume assembly of packaged surface-mount devices. With proper attention to PCB and stencil design, the device will achieve reliable performance without underfill. The advantage of the device's small footprint and short thermal path make it an ideal option for space-constrained applications in portable devices such as battery packs, PDAs, cellular phones, and notebook computers.

This application note discusses the mechanical design and reliability of MICRO FOOT, and then provides guidelines for board layout, the assembly process, and the PCB rework process.

FIGURE 1. 3D View of MICRO FOOT Products Si8902DB and Si8900EDB

FIGURE 2. Outline of MICRO FOOT CSP & Analog Switch DG3000DB

| TABLE 1  Main Parameters of Solder Bumps in MICRO FOOT Designs       |                               |     |           |           |  |

|----------------------------------------------------------------------|-------------------------------|-----|-----------|-----------|--|

| MICRO FOOT CSP Bump Material Bump Pitch* Bump Diameter* Bump Height* |                               |     |           |           |  |

| MICRO FOOT CSP MOSFET                                                | 5 0.11                        | 0.8 | 0.37-0.41 | 0.26-0.29 |  |

| MICRO FOOT CSP Analog Switch                                         | Eutectic Solder:<br>63Sm/37Pb | 0.5 | 0.18-0.25 | 0.14-0.19 |  |

| MICRO FOOT UCSP Analog Switch                                        |                               | 0.5 | 0.32-0.34 | 0.21-0.24 |  |

<sup>\*</sup> All measurements in millimeters

### MICRO FOOT'S DESIGN AND RELIABILITY

As a mechanical, electrical, and thermal connection between the device and PCB, the solder bumps of MICRO FOOT products are mounted on the top active surface of the die. Table 1 shows the main parameters for solder bumps used in MICRO FOOT products. A silicon nitride passivation layer is applied to the active area as the last masking process in fabrication, ensuring that the device passes the pressure pot test. A green laser is used to mark the backside of the die without damaging it. Reliability results for MICRO FOOT products mounted on a FR-4 board without underfill are shown in Table 2.

| TABLE 2 MICRO FOOT Reliability Results |              |  |  |  |

|----------------------------------------|--------------|--|--|--|

| Test Condition C: −65° to 150°C        | >500 Cycles  |  |  |  |

| Test condition B: −40° to 125°C        | >1000 Cycles |  |  |  |

| 121°C @ 15PSI 100% Humidity Test       | 96 Hours     |  |  |  |

The main failure mechanism associated with wafer-level chip-scale packaging is fatigue of the solder joint. The results shown in Table 2 demonstrate that a high level of reliability can be achieved with proper board design and assembly techniques.

### **BOARD LAYOUT GUIDELINES**

**Board materials**. Vishay Siliconix MICRO FOOT products are designed to be reliable on most board types, including organic boards such as FR-4 or polyamide boards. The package qualification information is based on the test on 0.5-oz. FR-4 and polyamide boards with NSMD pad design.

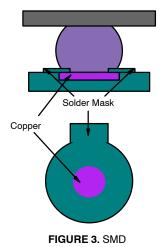

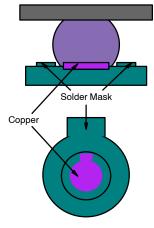

**Land patterns.** Two types of land patterns are used for surface-mount packages. Solder mask defined (SMD) pads have a solder mask opening smaller than the metal pad (Figure 3), whereas on-solder mask defined (NSMD) pads have a metal pad smaller than the solder-mask opening (Figure 4).

NSMD is recommended for copper etch processes, since it provides a higher level of control compared to SMD etch processes. A small-size NSMD pad definition provides more area (both lateral and vertical) for soldering and more room for escape routing on the PCB. By contrast, SMD pad definition introduces a stress -concentration point near the solder mask on the PCB side that may result in solder joint cracking under extreme fatigue conditions.

Copper pads should be finished with an organic solderability preservative (OSP) coating. For electroplated nickel-immersion gold finish pads, the gold thickness must be less than 0.5  $\mu$ m to avoid solder joint embrittlement.

FIGURE 4. NSMD

Document Number: 71990

**Board pad design.** The landing-pad size for MICRO FOOT products is determined by the bump pitch as shown in Table 3. The pad pattern is circular to ensure a symmetric, barrel-shaped solder bump.

| TABLE 3 Dimensions of Copper Pad and Solder Mask Opening in PCB and Stencil Aperture |                                      |                |                                     |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------------------------|--|--|

| Pitch                                                                                | Pitch Copper Pad Solder Mask Opening |                | Stencil<br>Aperture                 |  |  |

| 0.80 mm                                                                              | 0.30 ± 0.01 mm                       | 0.41 ± 0.01 mm | 0.33 ± 0.01 mm in ciircle aperture  |  |  |

| 0.50 mm                                                                              | 0.17 ± 0.01 mm                       | 0.27 ± 0.01 mm | $0.30\pm0.01$ mm in square aperture |  |  |

#### **ASSEMBLY PROCESS**

MICRO FOOT products' surface-mount-assembly operations include solder paste printing, component placement, and solder reflow as shown in the process flow chart (Figure 5).

FIGURE 5. SMT Assembly Process Flow

**Stencil design**. Stencil design is the key to ensuring maximum solder paste deposition without compromising the assembly yield from solder joint defects (such as bridging and extraneous solder spheres). The stencil aperture is dependent on the copper pad size, the solder mask opening, and the quantity of solder paste.

In MICRO FOOT products, the stencil is 0.125-mm (5-mils) thick. The recommended apertures are shown in Table 3 and are fabricated by laser cut.

**Solder-paste printing.** The solder-paste printing process involves transferring solder paste through pre-defined apertures via application of pressure.

In MICRO FOOT products, the solder paste used is UP78 No-clean eutectic 63 Sn/37Pb type3 or finer solder paste.

**Chip pick-and-placement.** MICRO FOOT products can be picked and placed with standard pick-and-place equipment. The recommended pick-and-place force is 150 g. Though the part will self-center during solder reflow, the maximum placement offset is 0.02 mm.

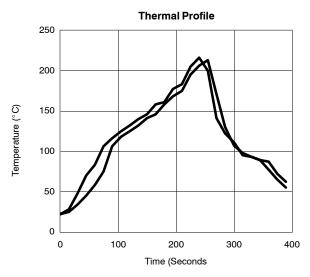

**Reflow Process.** MICRO FOOT products can be assembled using standard SMT reflow processes. Similar to any other package, the thermal profile at specific board locations must be determined. Nitrogen purge is recommended during reflow operation. Figure 6 shows a typical reflow profile.

FIGURE 6. Reflow Profile

### **PCB REWORK**

To replace MICRO FOOT products on PCB, the rework procedure is much like the rework process for a standard BGA or CSP, as long as the rework process duplicates the original reflow profile. The key steps are as follows:

- Remove the MICRO FOOT device using a convection nozzle to create localized heating similar to the original reflow profile. Preheat from the bottom.

- Once the nozzle temperature is +190°C, use tweezers to remove the part to be replaced.

- Resurface the pads using a temperature-controlled soldering iron.

- Apply gel flux to the pad.

- Use a vacuum needle pick-up tip to pick up the replacement part, and use a placement jig to placed it accurately.

- Reflow the part using the same convection nozzle, and preheat from the bottom, matching the original reflow profile.

# **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12 Document Number: 91000

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научно-исследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

**Телефон:** +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331