## CMOS 0 to 44 MHz Single Chip 8–bit Microntroller

## Description

TEMIC's 80C52 and 80C32 are high performance CMOS versions of the 8052/8032 NMOS single chip 8 bit  $\mu$ C.

The fully static design of the TEMIC 80C52/80C32 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The 80C52 retains all the features of the 8052 : 8 K bytes of ROM ; 256 bytes of RAM ; 32 I/O lines ; three 16 bit timers ; a 6-source, 2-level interrupt structure ; a full duplex serial port ; and on-chip oscillator and clock circuits. In addition, the 80C52 has 2 software-selectable

- 80C32 : Romless version of the 80C52

- 80C32/80C52-L16 : Low power version Vcc : 2.7 – 5.5 V Freq : 0-16 MHz

- 80C32/80C52-12 : 0 to 12 MHz

- 80C32/80C52-16 : 0 to 16 MHz

- 80C32/80C52-20 : 0 to 20 MHz

- 80C32/80C52-25 : 0 to 25 MHz

- 80C32/80C52-30 : 0 to 30 MHz

## Features

- Power control modes

- 256 bytes of RAM

- 8 Kbytes of ROM (80C52)

- 32 programmable I/O lines

- Three 16 bit timer/counters

- 64 K program memory space

- 64 K data memory space

## Optional

- Secret ROM : Encryption

- Secret TAG : Identification number

modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the RAM, the timers, the serial port and the interrupt system continue to function. In the power down mode the RAM is saved and all other functions are inoperative.

The 80C32 is identical to the 80C52 except that it has no on-chip ROM. TEMIC's 80C52/80C32 are manufactured using SCMOS process which allows them to run from 0 up to 44 MHz with Vcc = 5 V.

TEMIC's 80C52 and 80C32 are also available at 16 MHz with 2.7 V < V<sub>CC</sub> < 5.5 V.

- 80C32/80C52-36 : 0 to 36 MHz

- 80C32-40 : 0 to 40 MHz\*

- 80C32-42 : 0 to 42 MHz\*

- 80C32-44 : 0 to 44 MHz\*

\* 0 to 70°C temperature range. For other speed and temperature range availability please consult your sales office.

- Fully static design

- 0.8µ CMOS process

- Boolean processor

- 6 interrupt sources

- Programmable serial port

- Temperature range : commercial, industrial, automotive, military

## 80C32/80C52

## Interface

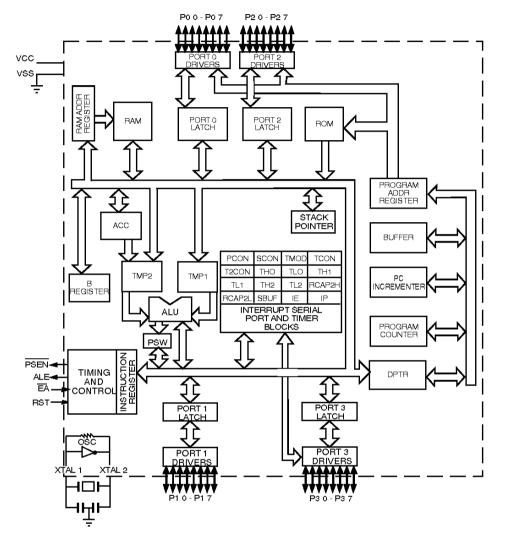

#### Figure 1. Block Diagram

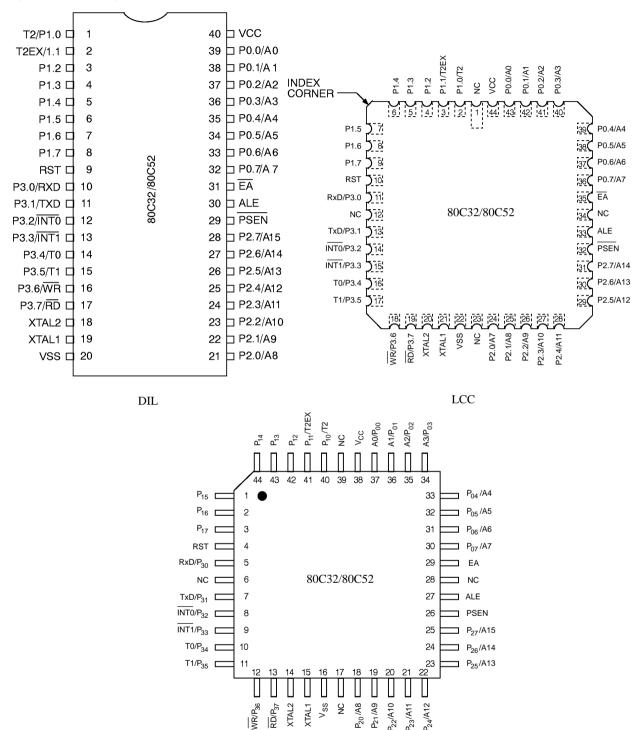

#### **Figure 2. Pin Configuration**

Flat Pack

RD/P<sub>37</sub> XTAL2 XTAL1  $^{\sf V}_{\sf SS}$ g

WR/P<sub>36</sub>

P<sub>22</sub>/A10

P<sub>23</sub>/A11

P<sub>24</sub>/A12

P<sub>21</sub>/A9

Diagrams are for reference only. Package sizes are not to scale.

## **Pin Description**

#### VSS

Circuit ground potential.

## VCC

Supply voltage during normal, Idle, and Power Down operation.

## Port 0

Port 0 is an 8 bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as high-impedance inputs.

Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pullups when emitting 1's. Port 0 also outputs the code bytes during program verification in the 80C52. External pullups are required during program verification. Port 0 can sink eight LS TTL inputs.

### Port 1

Port 1 is an 8 bit bi-directional I/O port with internal pullups. Port 1 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the internal pullups.

Port 1 also receives the low-order address byte during program verification. In the 80C52, Port 1 can sink/ source three LS TTL inputs. It can drive CMOS inputs without external pullups.

2 inputs of PORT 1 are also used for timer/counter 2 :

P1.0 [T2] : External clock input for timer/counter 2. P1.1 [T2EX] : A trigger input for timer/counter 2, to be reloaded or captured causing the timer/counter 2 interrupt.

### Port 2

Port 2 is an 8 bit bi-directional I/O port with internal pullups. Port 2 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (ILL, on the data sheet) because of the internal pullups. Port 2 emits the high-order address byte during fetches from external Program Memory and during accesses to external Data

Memory that use 16 bit addresses (MOVX @DPTR). In this application, it uses strong internal pullups when emitting 1's. During accesses to external Data Memory that use 8 bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 Special Function Register.

It also receives the high-order address bits and control signals during program verification in the 80C52. Port 2 can sink/source three LS TTL inputs. It can drive CMOS inputs without external pullups.

### Port 3

Port 3 is an 8 bit bi-directional I/O port with internal pullups. Port 3 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (ILL, on the data sheet) because of the pullups. It also serves the functions of various special features of the TEMIC 51 Family, as listed below.

| Port Pin | <b>Alternate Function</b>              |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | <b>INTO</b> (external interrupt 0)     |

| P3.3     | <b>INT1</b> (external interrupt 1)     |

| P3.4     | TD (Timer 0 external input)            |

| P3.5     | T1 (Timer 1 external input)            |

| P3.6     | WR (external Data Memory write strobe) |

| P3.7     | RD (external Data Memory read strobe)  |

Port 3 can sink/source three LS TTL inputs. It can drive CMOS inputs without external pullups.

### RST

A high level on this for two machine cycles while the oscillator is running resets the device. An internal pull-down resistor permits Power-On reset using only a capacitor connected to  $V_{CC}$ . As soon as the Reset is applied (Vin), PORT 1, 2 and 3 are tied to one. This operation is achieved asynchronously even if the oscillator does not start-up.

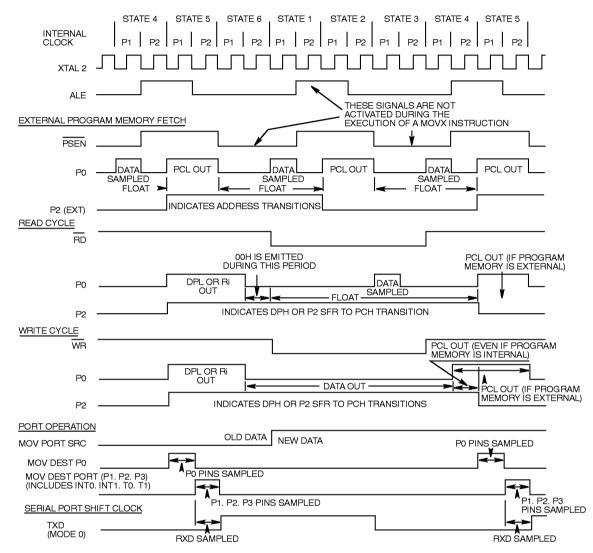

## ALE

Address Latch Enable output for latching the low byte of the address during accesses to external memory. ALE is activated as though for this purpose at a constant rate of 1/6 the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pullup.

## **PSEN**

Program Store Enable output is the read strobe to external Program Memory. PSEN is activated twice each machine cycle during fetches from external Program Memory. (However, when executing out of external Program Memory, two activations of PSEN are skipped during each access to external Data Memory). PSEN is not activated during fetches from internal Program Memory. PSEN can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pullup.

## EA

When EA is held high, the CPU executes out of internal Program Memory (unless the Program Counter exceeds

## **Idle And Power Down Operation**

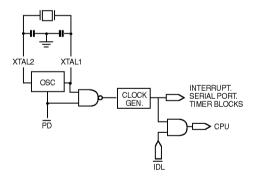

*Figure 3* shows the internal Idle and Power Down clock configuration. As illustrated, Power Down operation stops the oscillator. Idle mode operation allows the interrupt, serial port, and timer blocks to continue to function, while the clock to the CPU is gated off.

These special modes are activated by software via the Special Function Register, PCON. Its hardware address is 87H. PCON is not bit addressable.

#### Figure 3.Idle and Power Down Hardware.

PCON : Power Control Register

(MSB)

| (MDD) |   |   |   |     |     |    | (LSD) |

|-------|---|---|---|-----|-----|----|-------|

| SMOD  | - | - | - | GF1 | GF0 | PD | IDL   |

1 FFFH). When EA is held low, the CPU executes only out of external Program Memory. EA must not be floated.

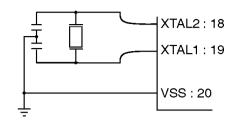

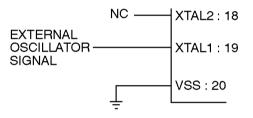

## XTAL1

Input to the inverting amplifier that forms the oscillator. Receives the external oscillator signal when an external oscillator is used.

## XTAL2

Output of the inverting amplifier that forms the oscillator. This pin should be floated when an external oscillator is used.

| Symbol | Position | Name and Function                                                                                                                      |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| SMOD   | PCON.7   | Double Baud rate bit. When set to<br>a 1, the baud rate is doubled when<br>the serial port is being used in<br>either modes 1, 2 or 3. |

| _      | PCON.6   | (Reserved)                                                                                                                             |

| _      | PCON.5   | (Reserved)                                                                                                                             |

| -      | PCON.4   | (Reserved)                                                                                                                             |

| GF1    | PCON.3   | General-purpose flag bit.                                                                                                              |

| GF0    | PCON.2   | General-purpose flag bit.                                                                                                              |

| PD     | PCON.1   | Power Down bit. Setting this bit activates power down operation.                                                                       |

| IDL    | PCON.0   | Idle mode bit. Setting this bit activates idle mode operation.                                                                         |

If 1's are written to PD and IDL at the same time. PD takes, precedence. The reset value of PCON is (000X0000).

#### **Idle Mode**

(I SB)

The instruction that sets PCON.0 is the last instruction executed before the Idle mode is activated. Once in the Idle mode the CPU status is preserved in its entirety : the Stack Pointer, Program Counter, Program Status Word, Accumulator, RAM and all other registers maintain their data during idle. *Table 1* describes the status of the external pins during Idle mode.

There are three ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating Idle mode. The interrupt is serviced, and following RETI, the next instruction to be executed will be the one following the instruction that wrote 1 to PCON.0.

The flag bits GF0 and GF1 may be used to determine whether the interrupt was received during normal execution or during the Idle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When Idle mode is terminated by an enabled interrupt, the service routine can examine the status of the flag bits.

The second way of terminating the Idle mode is with a hardware reset. Since the oscillator is still running, the hardware reset needs to be active for only 2 machine cycles (24 oscillator periods) to complete the reset operation.

#### **Power Down Mode**

The instruction that sets PCON.1 is the last executed prior to entering power down. Once in power down, the oscillator is stopped. The contents of the onchip RAM and the Special Function Register is saved during power down mode. The hardware reset initiates the Special Function Register. In the Power Down mode, VCC may be lowered to minimize circuit power consumption. Care must be taken to ensure the voltage is not reduced until the power down mode is entered, and that the voltage is restored before the hardware reset is applied which freezes the oscillator. Reset should not be released until the oscillator has restarted and stabilized.

Table 1 describes the status of the external pins while in the power down mode. It should be noted that if the power down mode is activated while in external program memory, the port data that is held in the Special Function Register P2 is restored to Port 2. If the data is a 1, the port pin is held high during the power down mode by the strong pullup, T1, shown in *Figure 4*.

| MODE       | PROGRAM MEMORY | ALE | <b>PSEN</b> | PORT0     | PORT1     | PORT2     | PORT3     |

|------------|----------------|-----|-------------|-----------|-----------|-----------|-----------|

| Idle       | Internal       | 1   | 1           | Port Data | Port Data | Port Data | Port Data |

| Idle       | External       | 1   | 1           | Floating  | Port Data | Address   | Port Data |

| Power Down | Internal       | 0   | 0           | Port Data | Port Data | Port Data | Port Data |

| Power Down | External       | 0   | 0           | Floating  | Port Data | Port Data | Port Data |

#### **Stop Clock Mode**

Due to static design, the TEMIC 80C32/C52 clock speed can be reduced until 0 MHz without any data loss in memory or registers. This mode allows step by step utilization, and permits to reduce system power consumption by bringing the clock frequency down to any value. At 0 MHz, the power consumption is the same as in the Power Down Mode.

#### **I/O Ports**

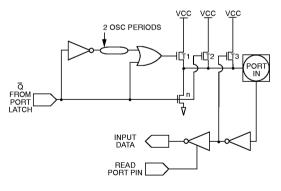

The I/O buffers for Ports 1, 2 and 3 are implemented as shown in *figure 4*.

#### Figure 4.I/O Buffers in the 80C52 (Ports 1, 2, 3).

When the port latch contains a 0, all pFETS in figure 4 are off while the nFET is turned on. When the port latch makes a 0-to-1 transition, the nFET turns off. The strong pFET, T1, turns on for two oscillator periods, pulling the output high very rapidly. As the output line is drawn high, pFET T3 turns on through the inverter to supply the IOH source current. This inverter and T form a latch which holds the 1 and is supported by T2.

When Port 2 is used as an address port, for access to external program of data memory, any address bit that contains a 1 will have his strong pullup turned on for the entire duration of the external memory access.

When an I/O pin on Ports 1, 2, or 3 is used as an input, the user should be aware that the external circuit must sink current during the logical 1-to-0 transition. The maximum sink current is specified as ITL under the D.C. Specifications. When the input goes below approximately 2 V, T3 turns off to save ICC current. Note, when returning to a logical 1, T2 is the only internal pullup that is on. This will result in a slow rise time if the user's circuit does not force the input line high.

#### **Oscillator Characteristics**

XTAL1 and XTAL2 are the input and output respectively, of an inverting amplifier which is configured for use as an on-chip oscillator, as shown in figure 5. Either a quartz crystal or ceramic resonator may be used.

## **Hardware Description**

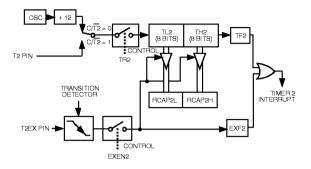

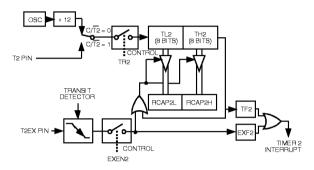

Same as for the 80C51, plus a third timer/counter :

#### **Timer/Event Counter 2**

Timer 2 is a 16 bit timer/counter like Timers 0 and 1, it can operate either as a timer or as an event counter. This is selected by bit C/T2 in the Special Function Register T2CON (Figure 1). It has three operating modes : "capture", "autoload" and "baud rate generator", which are selected by bits in T2CON as shown in *Table 2*.

In the capture mode there are two options which are selected by bit EXEN2 in T2CON; If EXEN2 = 0, then Timer 2 is a 16 bit timer or counter which upon overflowing sets bit TF2, the Timer 2 overflow bit, which can be used to generate an interrupt. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature

#### Figure 5. Crystal Oscillator.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected as shown in *figure 6*. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the Data Sheet must be observed.

#### Figure 6. External Drive Configuration.

that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively, (RCAP2L and RCAP2H are new Special Function Register in the 80C52). In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2, like TF2, can generate an interrupt.

Table 2. Timer 2 Operating Modes.

| RCLK +<br>TCLK | CP/RL2 | TR2 | MODE                |

|----------------|--------|-----|---------------------|

| 0              | 0      | 1   | 16 bit auto-reload  |

| 0              | 1      | 1   | 16 bit capture      |

| 1              | X      | 1   | baud rate generator |

| X              | X      | 0   | (off)               |

# 80C32/80C52

The capture mode is illustrated in Figure 7.

#### Figure 7. Timer 2 in Capture Mode.

In the auto-reload mode there are again two options, which are selected by bit EXEN2 in T2CON.If EXEN2 = 0, then when Timer 2 rolls over it does not only set TF2 but also causes the Timer 2 register to be reloaded

with the 16 bit value in registers RCAP2L and RCAP2H, which are preset by software. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX will also trigger the 16 bit reload and set EXF2.

The auto-reload mode is illustrated in *Figure 8*.

#### Figure 8. Timer in Auto-Reload Mode.

| (MSB) |      |      |      |       |     |                   | (LSB)  |

|-------|------|------|------|-------|-----|-------------------|--------|

| TF2   | EXF2 | RCLK | TCLK | EXEN2 | TR2 | $C/\overline{T2}$ | CP/RL2 |

The baud rate generator mode is selected by : RCLK = 1 and/or TCLK = 1.

| Symbol | Position | Name and Significance                                                                                                                                                                                                                                                                                                                         |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TF2    | T2CON.7  | Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either RCLK = 1 OR TCLK = 1.                                                                                                                                                                                                        |

| EXF2   | T2CON.6  | Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, $EXF2 = 1$ will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software.                                                                            |

| RCLK   | T2CON.5  | Receive clock flag. When set, causes the serial port to use Timer2 overflow pulses for its receive clock in modes 1 and 3. $RCLK = 0$ causes Timer 1 overflow to be used for the receive clock.                                                                                                                                               |

| TCLK   | T2CON.4  | Transmit clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.                                                                                                                                            |

| EXEN2  | T2CON.3  | Timer 2 external enable flag. When set, allows capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used to clock the serial port.<br>EXEN2 = 0 causes Timer 2 to ignore events at T2EX.                                                                                                           |

| TR2    | T2CON.2  | Start/stop control for Timer 2. A logic 1 starts the timer.                                                                                                                                                                                                                                                                                   |

| C/T2   | T2CON.1  | Timer or counter select. (Timer 2) $0 =$ Internal timer (OSC/12) $1 =$ External event counter (falling edge triggered).                                                                                                                                                                                                                       |

| CP/RL2 | T2CON.0  | Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN $2 = 1$ . When cleared, auto reloads will occur either with Timer 2 overflows or negative transition at T2EX when EXEN $2 = 1$ . When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. |

**TEMIC** Semiconductors

#### 80C52 with Secret ROM

TEMIC offers 80C52 with the encrypted secret ROM option to secure the ROM code contained in the 80C52 microcontrollers.

The clear reading of the program contained in the ROM is made impossible due to an encryption through several random keys implemented during the manufacturing process.

The keys used to do such encryption are selected randomwise and are definitely different from one microcontroller to another.

This encryption is activated during the following phases :

- Everytime a byte is addressed during a verify of the ROM content, a byte of the encryption array is selected.

- MOVC instructions executed from external program memory are disabled when fetching code bytes from internal memory.

- EA is sampled and latched on reset, thus all state modification are disabled.

For further information please refer to the application note (ANM053) available upon request.

#### 80C52 with Secret TAG

TEMIC offers special 64-bit identifier called "SECRET TAG" on the microcontroller chip.

The Secret Tag option is available on both ROMless and masked microcontrollers.

The Secret Tag feature allows serialization of each microcontroller for identification of a specific equipment. A unique number per device is implemented in the chip during manufacturing process. The serial number is a 64-bit binary value which is contained and addressable in the Special Function Registers (SFR) area.

This Secret Tag option can be read-out by a software routine and thus enables the user to do an individual identity check per device. This routine is implemented inside the microcontroller ROM memory in case of masked version which can be kept secret (and then the value of the Secret Tag also) by using a ROM Encryption.

For further information, please refer to the application note (ANM031) available upon request.

## **Electrical Characteristics**

#### **Absolute Maximum Ratings\***

Ambiant Temperature Under Bias :

| $C = commercial \dots 0^{\circ}C to 70^{\circ}C$                    |

|---------------------------------------------------------------------|

| $I = industrial \dots -40$ °C to 85 °C                              |

| Storage Temperature $-65^{\circ}C$ to $+150^{\circ}C$               |

| Voltage on VCC to VSS                                               |

| Voltage on Any Pin to VSS $\dots -0.5$ V to V <sub>CC</sub> + 0.5 V |

| Power Dissipation                                                   |

| * This value is based on the maximum allowable die temperature and  |

| the thermal resistance of the package                               |

\* Notice

Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

#### **DC Parameters**

TA = 0°C to 70°C ; VSS = 0 V ; VCC = 5 V  $\pm$  10 % ; F = 0 to 44 MHz TA = -40°C + 85°C ; VSS = 0 V ; VCC = 5 V  $\pm$  10 % ; F = 0 to 36 MHz

| SYMBOL | PARAMETER                                                                                                                                                                              | MIN           | MAX                 | UNIT                 | TEST CONDITIONS                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|----------------------|------------------------------------------------------------------------------|

| VIL    | Input Low Voltage                                                                                                                                                                      | - 0.5         | 0.2 Vcc - 0.1       | v                    |                                                                              |

| VIH    | Input High Voltage (Except XTAL and RST)                                                                                                                                               | 0.2 Vcc + 1.4 | Vcc + 0.5           | v                    |                                                                              |

| VIH1   | Input High Voltage (for XTAL and RST)                                                                                                                                                  | 0.7 Vcc       | Vcc + 0.5           | v                    |                                                                              |

| VOL    | Output Low Voltage (Port 1, 2 and 3)                                                                                                                                                   |               | 0.3<br>0.45<br>1.0  | V<br>V<br>V          | $IOL = 100 \ \mu A$ $IOL = 1.6 \ mA \ (note 2)$ $IOL = 3.5 \ mA$             |

| VOL1   | Output Low Voltage (Port 0, ALE, PSEN)                                                                                                                                                 |               | 0.3<br>0.45<br>1.0  | V<br>V<br>V          | $IOL = 200 \ \mu A$ $IOL = 3.2 \ mA \ (note 2)$ $IOL = 7.0 \ mA$             |

| VOH    | Output High Voltage Port 1, 2, 3                                                                                                                                                       | Vcc - 0.3     |                     | V                    | $IOH = -10 \ \mu A$                                                          |

|        |                                                                                                                                                                                        | Vcc - 0.7     |                     | v                    | $IOH = -30 \ \mu A$                                                          |

|        |                                                                                                                                                                                        | Vcc – 1.5     |                     | v                    | $\begin{split} IOH = &-60 \ \mu A \\ VCC = &5 \ V \pm &10 \ \% \end{split}$  |

| VOH1   | Output High Voltage (Port 0, ALE, PSEN)                                                                                                                                                | Vcc - 0.3     |                     | V                    | $IOH = -200 \ \mu A$                                                         |

|        |                                                                                                                                                                                        | Vcc - 0.7     |                     | V                    | IOH = -3.2  mA                                                               |

|        |                                                                                                                                                                                        | Vcc – 1.5     |                     | v                    | $\begin{array}{l} IOH = - \ 7.0 \ mA \\ VCC = 5 \ V \pm 10 \ \% \end{array}$ |

| IIL    | Logical 0 Input Current (Ports 1, 2 and 3)                                                                                                                                             |               | - 50                | μΑ                   | Vin = 0.45 V                                                                 |

| ILI    | Input leakage Current                                                                                                                                                                  |               | ± 10                | μΑ                   | 0.45 < Vin < Vcc                                                             |

| ITL    | Logical 1 to 0 Transition Current (Ports 1, 2 and 3)                                                                                                                                   |               | - 650               | μΑ                   | Vin = 2.0 V                                                                  |

| IPD    | Power Down Current                                                                                                                                                                     |               | 50                  | μΑ                   | Vcc = 2.0 V to 5.5 V (note 1)                                                |

| RRST   | RST Pulldown Resistor                                                                                                                                                                  | 50            | 200                 | KOhm                 |                                                                              |

| CIO    | Capacitance of I/O Buffer                                                                                                                                                              |               | 10                  | pF                   | $fc = 1 MHz$ , $Ta = 25^{\circ}C$                                            |

| ICC    | Power Supply Current<br>Freq = 1 MHz Icc op<br>Icc idle<br>Freq = 6 MHz Icc op<br>Icc idle<br>Freq $\ge$ 12 MHz Icc op = 1.25 Freq (MHz) + 5 mA<br>Icc idle = 0.36 Freq (MHz) + 2.7 mA |               | 1.8<br>1<br>10<br>4 | mA<br>mA<br>mA<br>mA | Vcc = 5.5 V                                                                  |

### **Absolute Maximum Ratings\***

Ambient Temperature Under Bias :

| A = Automotive $-40^{\circ}$ C to $+125^{\circ}$ C                            |

|-------------------------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}C$ to $+ 150^{\circ}C$                  |

| Voltage on VCC to VSS0.5 V to + 7 V                                           |

| Voltage on Any Pin to VSS $\ldots \ldots \ldots \ldots -0.5$ V to VCC + 0.5 V |

| Power Dissipation 1 W                                                         |

| * This value is based on the maximum allowable die temperature and            |

| the thermal resistance of the package                                         |

\* Notice

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Parameters**

$TA = -40^{\circ}C + 125^{\circ}C$ ; VSS = 0 V; VCC = 5 V  $\pm 10$  %; F = 0 to 36 MHz

| SYMBOL | PARAMETER                                                                                                                                                                               | MIN           | MAX                 | UNIT                 | TEST CONDITIONS                                                        |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|----------------------|------------------------------------------------------------------------|

| VIL    | Input Low Voltage                                                                                                                                                                       | - 0.5         | 0.2 Vcc - 0.1       | V                    |                                                                        |

| VIH    | Input High Voltage (Except XTAL and RST)                                                                                                                                                | 0.2 Vcc + 1.4 | Vcc + 0.5           | V                    |                                                                        |

| VIH1   | Input High Voltage (for XTAL and RST)                                                                                                                                                   | 0.7 Vcc       | Vcc + 0.5           | V                    |                                                                        |

| VOL    | Output Low Voltage (Port 1, 2 and 3)                                                                                                                                                    |               | 0.3<br>0.45<br>1.0  | V<br>V<br>V          | $IOL = 100 \ \mu A$ $IOL = 1.6 \ mA \ (note 2)$ $IOL = 3.5 \ mA$       |

| VOL1   | Output Low Voltage (Port 0, ALE, PSEN)                                                                                                                                                  |               | 0.3<br>0.45<br>1.0  | V<br>V<br>V          | $IOL = 200 \ \mu A$<br>$IOL = 3.2 \ mA \ (note 2)$<br>$IOL = 7.0 \ mA$ |

| VOH    | Output High Voltage Port 1, 2 and 3                                                                                                                                                     | Vcc - 0.3     |                     | v                    | $IOH = -10 \ \mu A$                                                    |

|        |                                                                                                                                                                                         | Vcc - 0.7     |                     | v                    | $IOH = -30 \mu A$                                                      |

|        |                                                                                                                                                                                         | Vcc – 1.5     |                     | v                    | $IOH = -60 \ \mu A$ $VCC = 5 \ V \pm 10 \ \%$                          |

| VOH1   | Output High Voltage (Port 0, ALE, PSEN)                                                                                                                                                 | Vcc - 0.3     |                     | v                    | $IOH = -200 \ \mu A$                                                   |

|        |                                                                                                                                                                                         | Vcc - 0.7     |                     | v                    | IOH = -3.2  mA                                                         |

|        |                                                                                                                                                                                         | Vcc – 1.5     |                     | v                    | IOH = - 7.0 mA<br>VCC = 5 V ± 10 %                                     |

| IIL    | Logical 0 Input Current (Ports 1, 2 and 3)                                                                                                                                              |               | - 75                | μΑ                   | Vin = 0.45 V                                                           |

| ILI    | Input leakage Current                                                                                                                                                                   |               | ±10                 | μΑ                   | 0.45 < Vin < Vcc                                                       |

| ITL    | Logical 1 to 0 Transition Current (Ports 1, 2 and 3)                                                                                                                                    |               | - 750               | μΑ                   | Vin = 2.0 V                                                            |

| IPD    | Power Down Current                                                                                                                                                                      |               | 75                  | μΑ                   | Vcc = 2.0 V to 5.5 V (note 1)                                          |

| RRST   | RST Pulldown Resistor                                                                                                                                                                   | 50            | 200                 | KOhm                 |                                                                        |

| CIO    | Capacitance of I/O Buffer                                                                                                                                                               |               | 10                  | pF                   | $fc = 1 MHz$ , $Ta = 25^{\circ}C$                                      |

| ICC    | Power Supply Current<br>Freq = 1 MHz Icc op<br>Icc idle<br>Freq = 6 MHz Icc op<br>Icc idle<br>Freq $\geq 12$ MHz Icc op = 1.25 Freq (MHz) + 5 mA<br>Icc idle = 0.36 Freq (MHz) + 2.7 mA |               | 1.8<br>1<br>10<br>4 | mA<br>mA<br>mA<br>mA | Vcc = 5.5 V                                                            |

### Absolute Maximum Ratings\*

Ambient Temperature Under Bias :

| Amblent Temperature Childer Dias .                                                                       |

|----------------------------------------------------------------------------------------------------------|

| $M = Military \dots -55^{\circ}C$ to $+125^{\circ}C$                                                     |

| Storage Temperature $\dots -65^{\circ}C$ to $+ 150^{\circ}C$                                             |

| Voltage on VCC to VSS0.5 V to + 7 V                                                                      |

| Voltage on Any Pin to VSS $\ldots \ldots \ldots \ldots -0.5$ V to VCC + 0.5 V                            |

| Power Dissipation 1 W                                                                                    |

| * This value is based on the maximum allowable die temperature and the thermal resistance of the package |

\* Notice

Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### **DC Parameters**

TA =  $-55^{\circ}C + 125^{\circ}C$ ; Vss = 0 V; Vcc = 5 V ± 10 %; F = 0 to 36 MHz

| SYMBOL | PARAMETER                                                                                                                                                                | MIN           | MAX                 | UNIT                 | TEST CONDITIONS                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|----------------------|---------------------------------------------------|

| VIL    | Input Low Voltage                                                                                                                                                        | - 0.5         | 0.2 Vcc - 0.1       | v                    |                                                   |

| VIH    | Input High Voltage (Except XTAL and RST)                                                                                                                                 | 0.2 Vcc + 1.4 | Vcc + 0.5           | v                    |                                                   |

| VIH1   | Input High Voltage (for XTAL and RST)                                                                                                                                    | 0.7 Vcc       | Vcc + 0.5           | v                    |                                                   |

| VOL    | Output Low Voltage (Port 1, 2 and 3)                                                                                                                                     |               | 0.45                | v                    | IOL = 1.6 mA (note 2)                             |

| VOL1   | Output Low Voltage (Port 0, ALE, PSEN)                                                                                                                                   |               | 0.45                | v                    | IOL = 3.2 mA (note 2)                             |

| VOH    | Output High Voltage (Port 1, 2 and 3)                                                                                                                                    | 2.4           |                     | v                    | $IOH = -60 \ \mu A$ $Vcc = 5 \ V \pm 10 \ \%$     |

|        |                                                                                                                                                                          | 0.75 Vcc      |                     | v                    | $IOH = -25 \ \mu A$                               |

|        |                                                                                                                                                                          | 0.9 Vcc       |                     | v                    | $IOH = -10 \ \mu A$                               |

| VOH1   | Output High Voltage<br>(Port 0 in External Bus Mode, ALE, PEN)                                                                                                           | 2.4           |                     | v                    | $IOH = -400 \ \mu A$<br>$Vcc = 5 \ V \pm 10 \ \%$ |

|        |                                                                                                                                                                          | 0.75 Vcc      |                     | v                    | $IOH = -150 \ \mu A$                              |

|        |                                                                                                                                                                          | 0.9 Vcc       |                     | v                    | $IOH = -40 \ \mu A$                               |

| IIL    | Logical 0 Input Current (Ports 1, 2 and 3)                                                                                                                               |               | - 75                | μΑ                   | Vin = 0.45 V                                      |

| ILI    | Input leakage Current                                                                                                                                                    |               | +/- 10              | μΑ                   | 0.45 < Vin < Vcc                                  |

| ITL    | Logical 1 to 0 Transition Current (Ports 1, 2 and 3)                                                                                                                     |               | - 750               | μΑ                   | Vin = 2.0 V                                       |

| IPD    | Power Down Current                                                                                                                                                       |               | 75                  | μΑ                   | Vcc = 2.0 V to 5.5 V (note 1)                     |

| RRST   | RST Pulldown Resistor                                                                                                                                                    | 50            | 200                 | ΚΩ                   |                                                   |

| CIO    | Capacitance of I/O Buffer                                                                                                                                                |               | 10                  | pF                   | $fc = 1 MHz$ , $Ta = 25^{\circ}C$                 |

| ICC    | Power Supply CurrentFreq = 1 MHzIcc op<br>Icc idleFreq = 6 MHzIcc op<br>Icc idleFreq $\geq$ 12 MHzIcc op = 1.25 Freq (MHz) + 5 mA<br>Icc idle = 0.36 Freq (MHz) + 2.7 mA |               | 1.8<br>1<br>10<br>4 | mA<br>mA<br>mA<br>mA | Vcc = 5.5 V                                       |

#### **Absolute Maximum Ratings\***

Ambient Temperature Under Bias :

| 1                                                                   |

|---------------------------------------------------------------------|

| $C = Commercial \dots 0^{\circ}C$ to 70°C                           |

| I = Industrial $\dots -40$ to $85^{\circ}C$                         |

| Storage Temperature $\qquad -65^{\circ}C$ to $+ 150^{\circ}C$       |

| Voltage on VCC to VSS0.5 V to + 7 V                                 |

| Voltage on Any Pin to VSS $\dots -0.5$ V to VCC + 0.5 V             |

| Power Dissipation 1 W**                                             |

| ** This value is based on the maximum allowable die temperature and |

| the thermal resistance of the package                               |

|                                                                     |

#### \* Notice

Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### **DC** Characteristics

TA = 0°C to 70°C ; Vcc = 2.7 V to 5.5 V ; Vss = 0 V ; F = 0 to 16 MHz TA = –40°C to 85°C ; Vcc = 2.7 V to 5.5 V

| SYMBOL | PARAMETER                                                              | MIN                 | MAX                       | UNIT | TEST CONDITIONS                                     |

|--------|------------------------------------------------------------------------|---------------------|---------------------------|------|-----------------------------------------------------|

| VIL    | Input Low Voltage                                                      | - 0.5               | 0.2 V <sub>CC</sub> - 0.1 | v    |                                                     |

| VIH    | Input High Voltage (Except XTAL and RST)                               | $0.2 V_{CC} + 1.4$  | V <sub>CC</sub> + 0.5     | V    |                                                     |

| VIH2   | Input High Voltage to RST for Reset                                    | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.5     | v    |                                                     |

| VIH1   | Input High Voltage to XTAL1                                            | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.5     | v    |                                                     |

| VPD    | Power Down Voltage to Vcc in PD Mode                                   | 2.0                 | 5.5                       | v    |                                                     |

| VOL    | Output Low Voltage (Ports 1, 2, 3)                                     |                     | 0.45                      | v    | IOL = 0.8 mA (note 2)                               |

| VOL1   | Output Low Voltage Port 0, ALE, PSEN                                   |                     | 0.45                      | v    | IOL = 1.6 mA (note 2)                               |

| VOH    | Output High Voltage Ports 1, 2, 3                                      | 0.9 Vcc             |                           | v    | $IOH = -10 \ \mu A$                                 |

| VOH1   | Output High Voltage (Port 0 in External Bus<br>Mode), ALE, <u>PSEN</u> | 0.9 Vcc             |                           | v    | $IOH = -40 \ \mu A$                                 |

| IIL    | Logical 0 Input Current Ports 1, 2, 3                                  |                     | - 50                      | μΑ   | Vin = 0.45 V                                        |

| ILI    | Input Leakage Current                                                  |                     | ± 10                      | μΑ   | $0.45 < Vin < V_{CC}$                               |

| ITL    | Logical 1 to 0 Transition Current<br>(Ports 1, 2, 3)                   |                     | - 650                     | μΑ   | Vin = 2.0 V                                         |

| IPD    | Power Down Current                                                     |                     | 50                        | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{ V (note 1)}$ |

| RRST   | RST Pulldown Resistor                                                  | 50                  | 200                       | kΩ   |                                                     |

| CIO    | Capacitance of I/O Buffer                                              |                     | 10                        | pF   | $fc = 1$ MHz, $T_A = 25^{\circ}C$                   |

#### Maximum Icc (mA)

|                               |                                                                                                                                                      | OPERATIN | G (NOTE 1) |        | IDLE (NOTE 1) |        |        |       |  |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|--------|---------------|--------|--------|-------|--|--|--|

| FREQUENCY/Vcc                 | 2.7 V                                                                                                                                                | 3 V      | 3.3 V      | 5.5 V  | 2.7 V         | 3 V    | 3.3 V  | 5.5 V |  |  |  |

| 1 MHz                         | 0.8 mA                                                                                                                                               | 1 mA     | 1.1 mA     | 1.8 mA | 400 µA        | 500 µA | 600 µA | 1 mA  |  |  |  |

| 6 MHz                         | 4 mA                                                                                                                                                 | 5 mA     | 6 mA       | 10 mA  | 1.5 mA        | 1.7 mA | 2 mA   | 4 mA  |  |  |  |

| 12 MHz                        | Hz 8 mA 10 mA 12 mA                                                                                                                                  |          |            |        |               | 3 mA   | 3.5 mA |       |  |  |  |

| 16 MHz                        | 10 mA                                                                                                                                                | 12 mA    | 14 mA      |        | 3 mA          | 3.8 mA | 4.5 mA |       |  |  |  |

| Freq > 12  MHz (Vcc = 5.5  V) | $Freq > 12 \text{ MHz } (Vcc = 5.5 \text{ V}) \qquad Icc (mA) = 1.25 \times Freq (MHz) + 5 \\ Icc \text{ Idle } (mA) = 0.36 \times Freq (MHz) + 2.7$ |          |            |        |               |        |        |       |  |  |  |

# 80C32/80C52

**TEMIC**

**Note 1 :** ICC is measured with all output pins disconnected ; XTAL1 driven with TCLCH, TCHCL = 5 ns, VIL = VSS + .5 V, VIH = VCC -.5 V ; XTAL2 N.C. ; EA = RST = Port 0 = VCC. ICC would be slightly higher if a crystal oscillator used.

Idle ICC is measured with all output pins disconnected; XTAL1 driven with TCLCH, TCHCL = 5 ns, VIL = VSS + 5 V, VIH = VCC -5 V; XTAL2 N.C; Port 0 = VCC; EA = RST = VSS.

Power Down ICC is measured with all output pins disconnected ; EA = PORT 0 = VCC ; XTAL2 N.C. ; RST = VSS.

**Note 2 :** Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the VOLS of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operations. In the worst cases (capacitive loading 100 pF), the noise pulse on the ALE line may exceed 0.45 V may exceed 0.45 V with maxi VOL peak 0.6 V. A Schmitt Trigger use is not necessary.

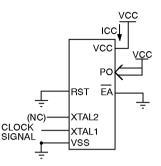

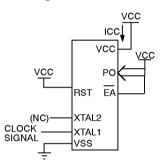

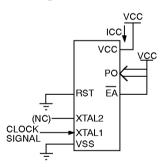

Figure 9. ICC Test Condition, Idle Mode. All other pins are disconnected.

Figure 10. ICC Test Condition, Active Mode. All other pins are disconnected.

Figure 11. ICC Test Condition, Power Down Mode. All other pins are disconnected.

#### **Explanation of the AC Symbol**

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

#### Example :

TAVLL = Time for Address Valid to ALE low.

TLLPL = Time for ALE low to  $\overline{\text{PSEN}}$  low.

|                                            |                                    | _ |

|--------------------------------------------|------------------------------------|---|

| A : Address.                               | Q : Output data.                   |   |

| C : Clock.                                 | R : READ signal.                   |   |

| D : Input data.                            | T : Time.                          |   |

| H : Logic level HIGH                       | V : Valid.                         |   |

| I : Instruction (program memory contents). | W : WRITE signal.                  |   |

| L : Logic level LOW, or ALE.               | X : No longer a valid logic level. |   |

| P:PSEN.                                    | Z : Float.                         |   |

|                                            |                                    |   |

#### **AC Parameters**

$$\begin{split} TA &= 0 \ to \ + \ 70^\circ C \ ; \ Vss = 0 \ V \ ; \ Vcc = 5 \ V \pm 10 \ \% \ ; \ F = 0 \ to \ 44 \ MHz \\ TA &= 0 \ to \ + \ 70^\circ C \ ; \ Vss = 0 \ V \ ; \ 2.7 \ V < Vcc < 5.5 \ V \ ; \ F = 0 \ to \ 16 \ MHz \\ TA &= -40^\circ \ to \ + \ 85^\circ C \ ; \ Vss = 0 \ V \ ; \ 2.7 \ V < Vcc < 5.5 \ V \ ; \ F = 0 \ to \ 16 \ MHz \\ TA &= -55^\circ \ + \ 125^\circ C \ ; \ Vss = 0 \ V \ ; \ Vcc = 5 \ V \pm 10 \ \% \ ; \ F = 0 \ to \ 36 \ MHz \\ (Load Capacitance \ for \ PORT \ 0, \ ALE \ and \ PSEN = 100 \ pF \ ; \ Load \ Capacitance \ for \ all \ other \ outputs = 80 \ pF) \end{split}$$

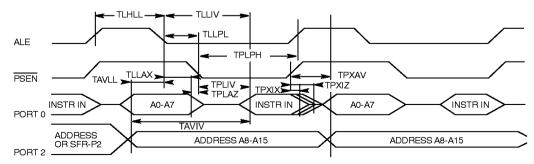

#### **External Program Memory Characteristics (values in ns)**

|             |                              | 16 N | MHz | 20 N | ΛHz | 25 N | ИHz | 30 N | ИHz | 36 N | ИHz | 40 N | ИHz | 42 N | ИHz | 44 N | MHz |

|-------------|------------------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|

| SYM-<br>BOL | PARAMETER                    | min  | max |

| TLHLL       | ALE Pulse Width              | 110  |     | 90   |     | 70   |     | 60   |     | 50   |     | 40   |     | 35   |     | 30   |     |

| TAVLL       | Address valid to ALE         | 40   |     | 30   |     | 20   |     | 15   |     | 10   |     | 9    |     | 8    |     | 7    |     |

| TLLAX       | Address Hold After ALE       | 35   |     | 35   |     | 35   |     | 35   |     | 35   |     | 30   |     | 25   |     | 17   |     |

| TLLIV       | ALE to valid instr in        |      | 185 |      | 170 |      | 130 |      | 100 |      | 80  |      | 70  |      | 65  |      | 65  |

| TLLPL       | ALE to PSEN                  | 45   |     | 40   |     | 30   |     | 25   |     | 20   |     | 15   |     | 13   |     | 12   |     |

| TPLPH       | PSEN pulse Width             | 165  |     | 130  |     | 100  |     | 80   |     | 75   |     | 65   |     | 60   |     | 54   |     |

| TPLIV       | PSEN to valid instr in       |      | 125 |      | 110 |      | 85  |      | 65  |      | 50  |      | 45  |      | 40  |      | 35  |

| TPXIX       | Input instr Hold After PSEN  | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     |

| TPXIZ       | Input instr Float After PSEN |      | 50  |      | 45  |      | 35  |      | 30  |      | 25  |      | 20  |      | 15  |      | 10  |

| TPXAV       | PSEN to Address Valid        | 55   |     | 50   |     | 40   |     | 35   |     | 30   |     | 25   |     | 20   |     | 15   |     |

| TAVIV       | Address to Valid instr in    |      | 230 |      | 210 |      | 170 |      | 130 |      | 90  |      | 80  |      | 75  |      | 70  |

| TPLAZ       | PSEN low to Address Float    |      | 10  |      | 10  |      | 8   |      | 6   |      | 5   |      | 5   |      | 5   |      | 5   |

### **External Program Memory Read Cycle**

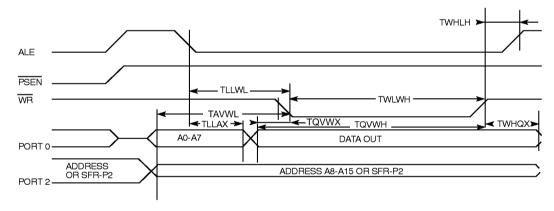

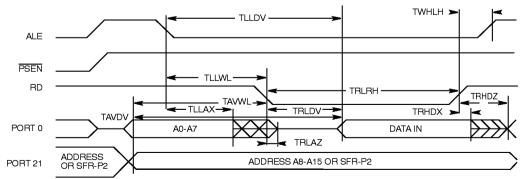

|             |                             | 16 N | AHz | 20 N | ИHz | 25 N | AHz | 30 N | ΛHz | 36 N | ΛHz | 40 N | ИНz | 42 N | ΛHz | 44 N | AHz |

|-------------|-----------------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|

| SYM-<br>BOL | PARAMETER                   | min  | max |

| TRLRH       | RD pulse Width              | 340  |     | 270  |     | 210  |     | 180  |     | 120  |     | 100  |     | 90   |     | 80   |     |

| TWLWH       | WR pulse Width              | 340  |     | 270  |     | 210  |     | 180  |     | 120  |     | 100  |     | 90   |     | 80   |     |

| TLLAX       | Address Hold After ALE      | 85   |     | 85   |     | 70   |     | 55   |     | 35   |     | 30   |     | 25   |     | 25   |     |

| TRLDV       | RD to Valid Data in         |      | 240 |      | 210 |      | 175 |      | 135 |      | 110 |      | 90  |      | 80  |      | 70  |

| TRHDX       | Data hold after RD          | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     |

| TRHDZ       | Data float after RD         |      | 90  |      | 90  |      | 80  |      | 70  |      | 50  |      | 45  |      | 40  |      | 35  |

| TLLDV       | ALE to Valid Data In        |      | 435 |      | 370 |      | 290 |      | 235 |      | 170 |      | 150 |      | 140 |      | 130 |

| TAVDV       | Address to Valid Data IN    |      | 480 |      | 400 |      | 320 |      | 260 |      | 190 |      | 180 |      | 175 |      | 170 |

| TLLWL       | ALE to WR or RD             | 150  | 250 | 135  | 170 | 120  | 130 | 90   | 115 | 70   | 100 | 60   | 95  | 55   | 90  | 50   | 85  |

| TAVWL       | Address to WR or RD         | 180  |     | 180  |     | 140  |     | 115  |     | 75   |     | 65   |     | 60   |     | 55   |     |

| TQVWX       | Data valid to WR transition | 35   |     | 35   |     | 30   |     | 20   |     | 15   |     | 10   |     | 8    |     | 6    |     |

| TQVWH       | Data Setup to WR transition | 380  |     | 325  |     | 250  |     | 215  |     | 170  |     | 160  |     | 150  |     | 140  |     |

| TWHQX       | Data Hold after WR          | 40   |     | 35   |     | 30   |     | 20   |     | 15   |     | 10   |     | 8    |     | 6    |     |

| TRLAZ       | RD low to Address Float     |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |

| TWHLH       | RD or WR high to ALE high   | 35   | 90  | 35   | 60  | 25   | 45  | 20   | 40  | 20   | 40  | 15   | 35  | 13   | 33  | 13   | 33  |

## **External Data Memory Characteristics (values in ns)**

## **External Data Memory Write Cycle**

## **External Data Memory Read Cycle**

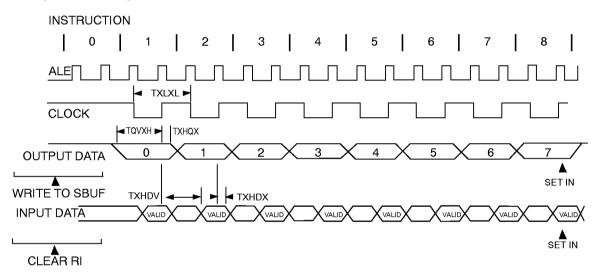

### Serial Port Timing – Shift Register Mode (values in ns)

|             |                                             | 16 N | ЛНz | 20 N | ΛHz | 25 N | ΛHz | 30 N | AHz | 36 N | /Hz | 40 N | ИHz | 42 N | AHz | 44 N | ΛHz |

|-------------|---------------------------------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|

| SYM-<br>BOL | PARAMETER                                   | min  | max |

| TXLXL       | Serial Port Clock Cycle Time                | 750  |     | 600  |     | 480  |     | 400  |     | 330  |     | 250  |     | 230  |     | 227  |     |

| TQVXH       | Output Data Setup to Clock<br>Rising Edge   | 563  |     | 480  |     | 380  |     | 300  |     | 220  |     | 170  |     | 150  |     | 140  |     |

| TXHQX       | Output Data Hold after Clock<br>Rising Edge | 63   |     | 90   |     | 65   |     | 50   |     | 45   |     | 35   |     | 30   |     | 25   |     |

| TXHDX       | Input Data Hold after Clock<br>Rising Edge  | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     | 0    |     |

| TXHDV       | Clock Rising Edge to Input<br>Data Valid    |      | 563 |      | 450 |      | 350 |      | 300 |      | 250 |      | 200 |      | 180 |      | 160 |

## Shift Register Timing Waveforms

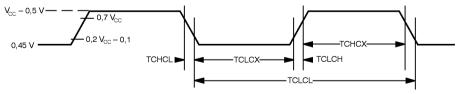

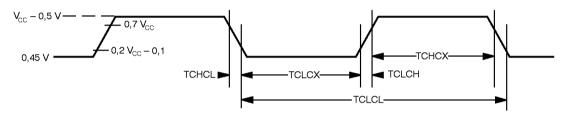

### **External Clock Drive Characteristics (XTAL1)**

| SYMBOL | PARAMETER            | MIN  | MAX | UNIT |

|--------|----------------------|------|-----|------|

| FCLCL  | Oscillator Frequency |      | 44  | MHz  |

| TCLCL  | Oscillator period    | 22.7 |     | ns   |

| TCHCX  | High Time            | 5    |     | ns   |

| TCLCX  | Low Time             | 5    |     | ns   |

| TCLCH  | Rise Time            |      | 5   | ns   |

| TCHCL  | Fall Time            |      | 5   | ns   |

### **External Clock Drive Waveforms**

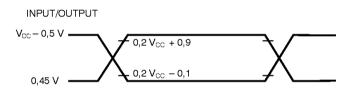

### AC Testing Input/Output Waveforms

AC inputs during testing are driven at Vcc - 0.5 for a logic "1" and 0.45 V for a logic "0". Timing measurements are made at VIH min for a logic "1" and VIL max for a logic "0".

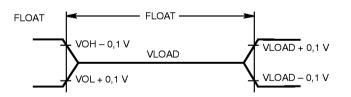

### **Float Waveforms**

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded VOH/VOL level occurs. Iol/IoH  $\ge \pm 20$  mA.

## TEMIC Semiconductors

### **Clock Waveforms**

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50 ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# 80C32/80C52

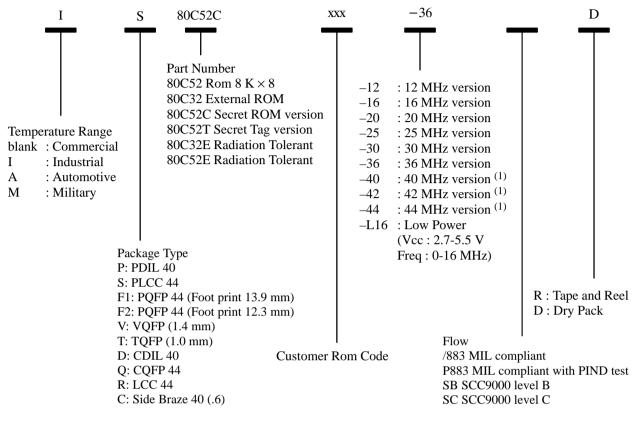

## **Ordering Information**

(1) Only for 80C31 at commercial range.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331