# PAC1932/3/4

### Multi-Channel DC Power/Energy Monitor with Accumulator

#### **Features**

- · High-Side Current Monitor with 2, 3 or 4 Channels

- 100 mV full scale range for current sense voltage,16 bit resolution

- Selectable bidirectional current sense capability, -100 mV to +100 mV range, 16 bit two's complement (signed) data format

- External sense resistor sets full scale current range

- Very low input current simplifies routing

- · Wide Bus Voltage Range for Voltage Monitor

- 0V to 32V input common-mode voltage

- 16 bit resolution for voltage measurements,

14 bits are used for power calculations

- Real Time Auto-Calibration of Offset and Gain Errors for Voltage and Current, No User Adjustment Required

- 1% Power Measurement Accuracy over a Wide Dynamic Range

- On-Chip Accumulation of 28-bit Power Results for Energy Measurement

- 48-bit power accumulator register for recording accumulated power data

- 24 bit Accumulator Count

- User programmable sampling rates of 8, 64, 256 and 1024 samples per second

- 17 minutes of power data accumulation minimum at 1024 S/s

- Over 36 hours of power data accumulation minimum at 8 S/s

- · 2.7V to 5.5V Supply Operation

- Separate V<sub>DD</sub> I/O pin for digital I/O

- 1.62-5.5V capable SMBus and digital I/O

- SMBus 3.0 and I<sup>2</sup>C Fast Mode Plus (1Mb/S)

- SMBus Address 16 Options, set with Resistor

- · No Input Filters Required

- · ALERT Features that can be Enabled:

- ALERT on accumulator overflow

- ALERT on Conversion Complete

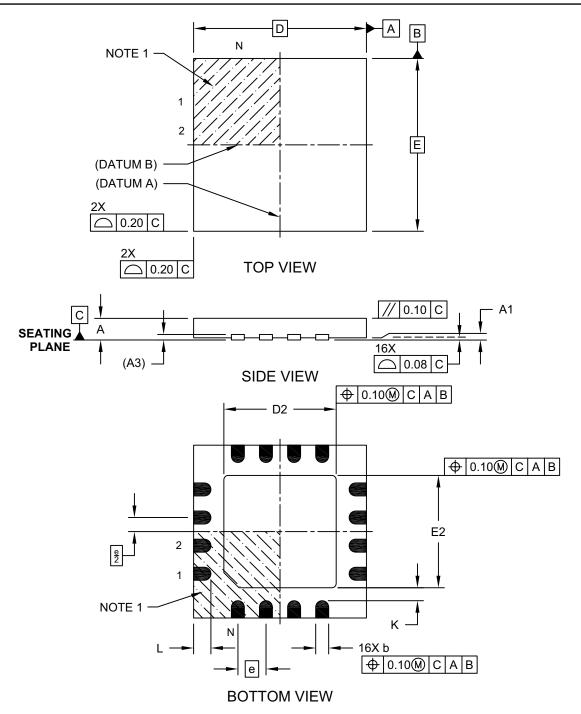

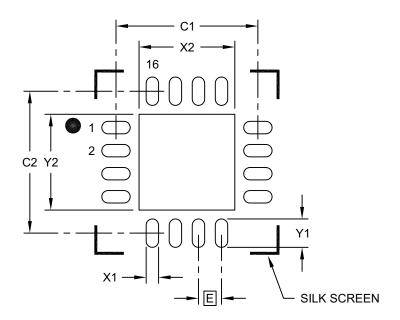

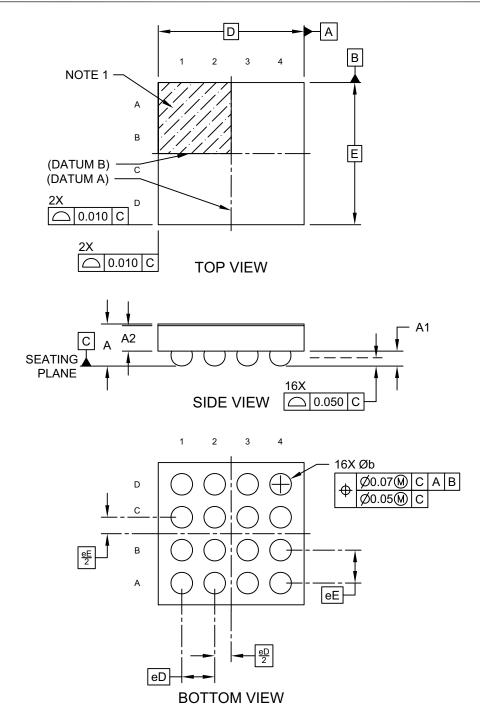

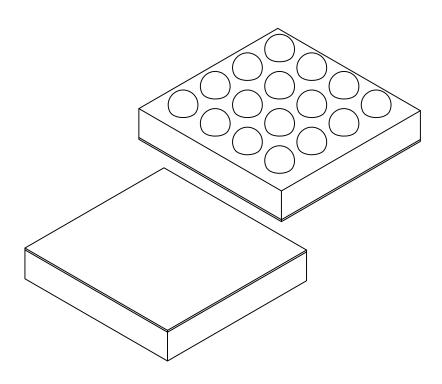

- 4x4x0.5 mm UQFN Package

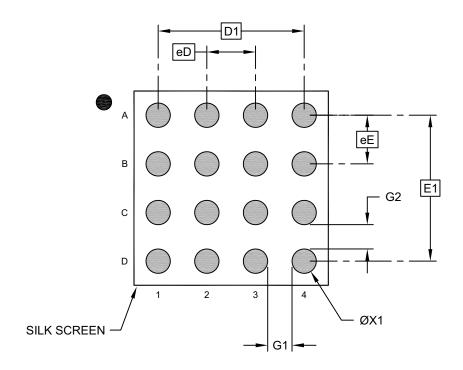

- · 2.225x2.17 mm WLCSP Package

- WLCSP available for PAC1934 only

- Contact Marketing for other options

#### **Applications**

- · Embedded Computing

- · Networking

- · FPGA Systems

- · Automotive

- · Low voltage/High Power AI, GPU

- Industrial

- Linux Applications

- · Notebook and Tablet Computing

- · Cloud, Linux and Server Computing

#### **Computing Platform Support**

- Windows<sup>®</sup> 10 Driver

- · Linux Driver

- · Python Script

#### **Description**

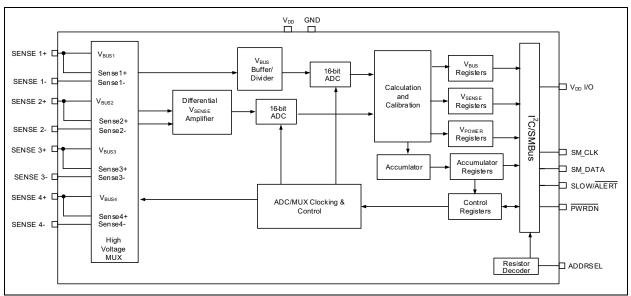

The PAC1932/3/4 are two, three and four-channel power and energy monitoring devices. A high-voltage multiplexer sequentially connects the inputs to a bus voltage monitor and current sense amplifier that feed high-resolution ADCs. Digital circuitry performs power calculations and energy accumulation.

This enables energy monitoring with integration periods from 1 ms up to 36 hours or longer. Bus voltage, sense resistor voltage and accumulated proportional power are stored in registers for retrieval by the system master or Embedded Controller.

The sampling rate and energy integration period can be controlled over SMBus or  $I^2C$ . Active channel selection, one-shot measurements and other controls are also configurable by SMBus or  $I^2C$ .

The PAC1932/3/4 device family uses real time calibration to minimize offset and gain errors. No input filters are required for this device.

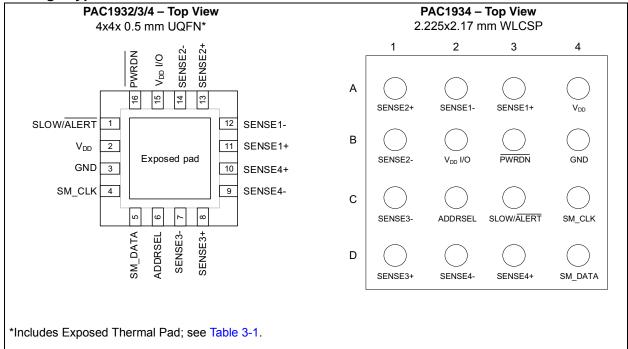

#### **Package Types**

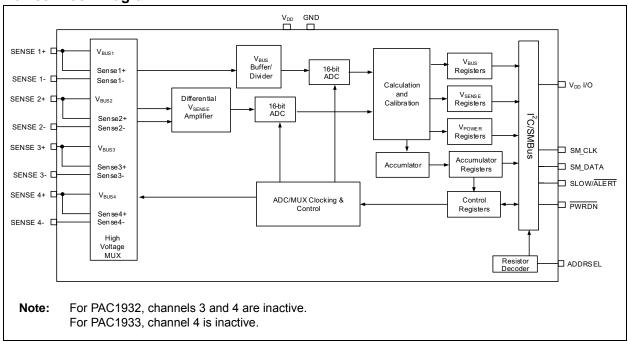

#### **Device Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Electrical Specifications

### Absolute Maximum Ratings(†)

| V <sub>DD</sub> pin                              | 0.3 to 6.0V       |

|--------------------------------------------------|-------------------|

| Voltage on SENSE- and SENSE+ pins                | 0.3 to 40V        |

| Voltage on any other pin to GND                  | GND -0.3 to +6.0V |

| Voltage between Sense pins ( (SENSE+ – SENSE-) ) | 500 mV            |

| Input current to any pin except V <sub>DD</sub>  | ±100 mA           |

| Output short-circuit current                     | Continuous        |

| Junction to Ambient (θ <sub>J-A</sub> )          | +78°C/W           |

| Operating Ambient Temperature Range              | -40 to +150°C     |

| Storage Temperature Range                        | 55 to +150°C      |

| ESD Rating – all pins – HBM                      | 4000V             |

| ESD Rating – all pins – CDM                      | 2000V             |

**† Notice**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

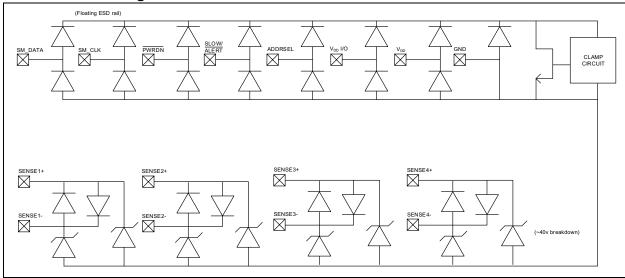

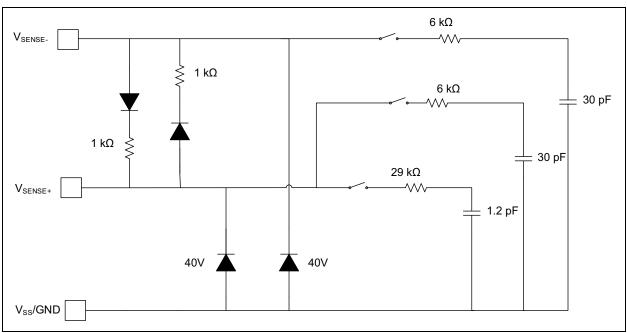

#### **ESD Protection Diagram**

This diagram represents the ESD protection circuitry on the PAC1934. The SENSE pins are allowed to be at 32V if  $V_{DD}$  is at zero. The back-to-back diodes between the Sense+ and Sense- pins have 1  $k\Omega$  resistors in series with them.

For PAC1932 and PAC1933, some of the SENSE pins are not electrically connected inside. These unconnected pins should be grounded.

TABLE 1-1: DC CHARACTERISTICS

**Electrical Characteristics**: Unless otherwise specified, maximum values are at  $T_A = -40^{\circ}C$  to +85°C,  $V_{DD} = 2.7V$  to 5.5V,  $V_{DD \ I/O} = 1.62V$  to 5.5V,  $V_{BUS} = 0V$  to 32V; typical values are at  $T_A = +25^{\circ}C$   $V_{DD} = V_{DD \ I/O} = 3.3V$ ,  $V_{BUS} = 32V$ ,  $V_{SENSE} = (SENSE+ - SENSE-) = 0V$

| Characteristic                                                |                                            | T     |               | Lle-14 | Conditions |                                                                                                                       |

|---------------------------------------------------------------|--------------------------------------------|-------|---------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                | Symbol                                     | Min.  | Тур.          | Max.   | Unit       | Conditions                                                                                                            |

| Power Supply                                                  |                                            |       | 1             | 1      | 1          |                                                                                                                       |

| V <sub>DD</sub> Range                                         | $V_{DD}$                                   | 2.7   | _             | 5.5    | V          |                                                                                                                       |

| V <sub>DD I/O</sub> Range                                     | V <sub>DD</sub> I/O                        | 1.62  | _             | 5.5    | V          |                                                                                                                       |

| V <sub>DD</sub> Pin Active<br>Current                         | I <sub>DD</sub>                            |       | 585           | 675    | μA         | 1024 Samples/s All IDD specifications are the same for PAC1932/3/4                                                    |

| V <sub>DD</sub> Pin Active<br>Current                         | I <sub>DD</sub> slow                       |       | 16            | _      | μA         | 4 channels enabled, 8 Samples/s                                                                                       |

| Minimum V <sub>DD</sub> Rise<br>Rate                          | V <sub>DD_RISE_MIN</sub>                   |       | 0.05          | _      | V/ms       | 0 to 5V in 100 ms                                                                                                     |

| Maximum V <sub>DD</sub> Rise<br>Rate                          | V <sub>DD_RISE</sub>                       | 1     | 1000          | _      | V/ms       | 0 to 5V in 5 μs                                                                                                       |

| V <sub>DD</sub> Sleep Current                                 | I <sub>DD_SLEEP</sub>                      |       | 5             | _      | μA         | Sleep State                                                                                                           |

| V <sub>DD</sub> Power-Down<br>Current                         | I <sub>DD_PWRDN</sub>                      | l     | 0.1           | _      | μA         | Power-Down State                                                                                                      |

| V <sub>DD I/O</sub> Current                                   | I <sub>DD I/O</sub>                        | _     | _             | 2      | μA         | All States                                                                                                            |

| Analog Input Characte                                         |                                            |       |               |        |            |                                                                                                                       |

| V <sub>BUS</sub> Voltage Range                                | V <sub>BUS</sub>                           | -0.2V | _             | 32     | V          | Common mode range for SENSE+<br>and SENSE- pins, referenced to<br>ground (negative range not tested<br>in production) |

| V <sub>SENSE</sub> Differential<br>Input Voltage Range        | V <sub>SENSE_DIF</sub>                     | -100  | _             | 100    | mV         |                                                                                                                       |

| SENSE+, SENSE-Pin<br>Input Current                            | I <sub>SENSE</sub> +, I <sub>SENSE</sub> - | -7    | 0             | 7      | μA         | V <sub>SENSE</sub> + = V <sub>SENSE</sub> - = 32V<br>(Input current is the combined<br>current for the two pins)      |

| SENSE+, SENSE-Pin<br>Input current                            | I <sub>SENSE</sub> +, I <sub>SENSE</sub> - | -1    | 0             | 1      | μA         | V <sub>SENSE</sub> + = 6V, V <sub>SENSE</sub> - = 5.9V                                                                |

| <b>V<sub>SENSE</sub> Measurement</b>                          | Accuracy                                   |       |               |        |            |                                                                                                                       |

| V <sub>SENSE</sub> Gain<br>Accuracy                           | V <sub>SENSE</sub><br>GAIN_ERR             |       | ±0.2<br>±1    | ±0.9   | %<br>%     | At +25°C<br>typical, -40 to +85°C                                                                                     |

| V <sub>SENSE</sub> Offset<br>Accuracy, referenced<br>to input | V <sub>BUS</sub> _<br>OFFSET_ERR           |       | ±0.02<br>±0.2 | ±0.1   | mV<br>mV   | At +25C°<br>typical, -40 to +85°C                                                                                     |

| V <sub>SENSE</sub> – Unidirection                             | al Currents                                |       |               |        |            |                                                                                                                       |

| V <sub>SENSE</sub><br>ADC Resolution                          | V <sub>SENSE_RES</sub>                     |       | _             | 16     | Bits       | Straight Binary for unidirectional currents                                                                           |

| V <sub>SENSE</sub><br>Full Scale Range                        | V <sub>SENSE_FSR</sub>                     | 0     | _             | 100    | mV         | Unidirectional currents                                                                                               |

| V <sub>SENSE</sub> LSB Step<br>Size                           | V <sub>SENSE_LSB</sub>                     | _     | 1.5           | _      | μV         | Unidirectional currents                                                                                               |

| V <sub>SENSE</sub> – Bidirectiona                             | l Currents                                 |       |               |        |            |                                                                                                                       |

| V <sub>SENSE</sub><br>ADC Resolution                          | V <sub>SENSE_RES</sub>                     | _     | _             | 16     | bits       | 16-bit two's complement (signed)                                                                                      |

| V <sub>SENSE</sub><br>Full Scale Range                        | V <sub>SENSE_FSR</sub>                     | -100  | _             | 100    | mV         | Bidirectional currents                                                                                                |

#### TABLE 1-1: DC CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise specified, maximum values are at T<sub>A</sub> = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{DD\ I/O}$ = 1.62V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C  $V_{DD}$  =  $V_{DD\ I/O}$  = 3.3V,  $V_{BUS}$  = 32V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V Characteristic **Symbol** Unit **Conditions** Min. Тур. Max. V<sub>SENSE</sub> LSB Step 3 Bidirectional currents μV V<sub>SENSE LSB</sub> Size **V<sub>BUS</sub>** Measurement Accuracy ±0.02 ±0.5 % At +25°C V<sub>BUS</sub> Gain Accuracy V<sub>BUS GAIN ERR</sub> ±0.2 % typical, -40 to +85°C V<sub>BUS</sub> Offset Accuracy, LSB At +25°C  $V_{BUS}_{\_}$ referenced to input ±2 LSB typical, -40 to +85°C OFFSET ERR V<sub>BUS</sub> - Unipolar Voltages  $V_{BUS}$ V<sub>BUS\_RES</sub> 16 bits Straight Binary for unidirectional ADC Resolution currents V<sub>BUS</sub> FSR V<sub>BUS</sub> Unipolar 0 32 V Unipolar voltage Full-Scale Range V<sub>BUS</sub> LSB Step Size V<sub>BUS</sub> LSB 488 μV FSR = 32V, 16-bit resolution V<sub>BUS</sub> - Bipolar Voltages V<sub>BUS</sub> ADC Resolution 16-bit two's complement (signed)  $V_{BUS\_RES}$ 16 numbers are reported for V<sub>BUS</sub> measurement result V<sub>BUS</sub> Bipolar  $V_{BUS}$  FSR ٧ Mathematical scaling. -32 32 Physics limits the negative input Full-Scale Range voltage to -0.2V 976 V<sub>BUS</sub> LSB Step Size V<sub>BUS</sub> LSB μV Bipolar voltages

### TABLE 1-1: DC CHARACTERISTICS (CONTINUED)

| DD                                                             | DOC OLIVOR          | <del>. '</del>               |         |                              |      |                                                                                                   |

|----------------------------------------------------------------|---------------------|------------------------------|---------|------------------------------|------|---------------------------------------------------------------------------------------------------|

| Characteristic                                                 | Symbol              | Min.                         | Тур.    | Max.                         | Unit | Conditions                                                                                        |

| Power Accumulator A                                            | ccuracy             |                              |         |                              |      |                                                                                                   |

| Accumulator Error                                              | ACC_Err             | _                            | 0.2     | _                            | %    | V <sub>SENSE</sub> = 97 mV                                                                        |

| Accumulator Error                                              | ACC_Err             | _                            | 0.2     | _                            | %    | V <sub>SENSE</sub> = 10 mV                                                                        |

| Accumulator Error                                              | ACC_Err             |                              | 1       | _                            | %    | V <sub>SENSE</sub> = 1 mV                                                                         |

| Accumulator Error                                              | ACC_Err             | _                            | 3       | _                            | %    | V <sub>SENSE</sub> = 100 μV                                                                       |

| Accumulator Error                                              | ACC_Err             | _                            | 5       | _                            | %    | V <sub>SENSE</sub> = 50 μV                                                                        |

| <b>Active Mode Timing</b>                                      |                     |                              |         |                              |      |                                                                                                   |

| Pull-Up Voltage<br>Range                                       | V <sub>PULLUP</sub> | 1.62                         | _       | 5.5                          | V    | Pull-up voltage for I <sup>2</sup> C/SMBus pins and digital I/O pins. Set by V <sub>DD</sub> I/O. |

| Time to First<br>Communications                                | t <sub>INT_T</sub>  | _                            | 14.25   | _                            | ms   |                                                                                                   |

| Transition From Sleep<br>State to Start of<br>Conversion Cycle | tSLEEP_TO_ACTIVE    | _                            | 3       | _                            | ms   |                                                                                                   |

| Digital I/O Pins (SM_C                                         | CLK, SM_DATA, SL    | OW/ALER                      | T, PWRD | N)                           |      |                                                                                                   |

| Input High Voltage                                             | V <sub>IH</sub>     | V <sub>DD</sub> I/O<br>x 0.7 | _       | _                            | V    |                                                                                                   |

| Input Low Voltage                                              | V <sub>IL</sub>     | _                            | _       | V <sub>DD</sub> I/O<br>x 0.3 | V    |                                                                                                   |

| Output Low Voltage                                             | V <sub>OL</sub>     | _                            | _       | 0.4                          | V    | Sinking 8 mA for the ALERT pin and 20 mA for the SMCLK pin                                        |

| Leakage Current                                                | I <sub>I EAK</sub>  | <b>–</b> 1                   | _       | +1                           | μA   |                                                                                                   |

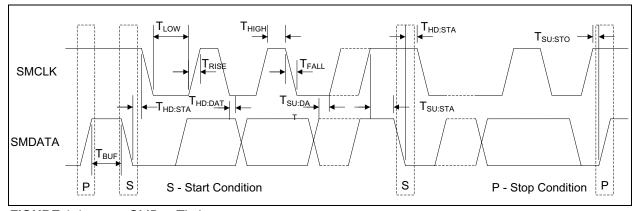

TABLE 1-2: SMBUS MODULE SPECIFICATIONS

**Electrical Characteristics**: Unless otherwise specified, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; Typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{BUS}$  = 32V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62V to 5.5V

| OLITOL (                                       |                     |      |      |      |       |                                                             |

|------------------------------------------------|---------------------|------|------|------|-------|-------------------------------------------------------------|

| Characteristic                                 | Sym.                | Min. | Тур. | Max. | Units | Conditions                                                  |

| SMBus Interface                                |                     |      |      |      |       |                                                             |

| Input Capacitance                              | C <sub>IN</sub>     | _    | 4    | 10   | pF    | Not tested in production                                    |

| SMBus Timing                                   |                     |      |      |      |       |                                                             |

| Clock Frequency                                | f <sub>SMB</sub>    | .010 |      | 1    | MHz   | No minimum if Time-Out is not enabled.                      |

| Spike Suppression                              | t <sub>SP</sub>     | 0    | _    | 50   | ns    |                                                             |

| Bus Free Time Stop to Start                    | t <sub>BUF</sub>    | 0.5  | _    | _    | μs    | Per SMBus 3.0                                               |

| Hold Time after<br>Repeated Start<br>Condition | t <sub>HD:STA</sub> | 0.26 | _    | _    | μs    | Per SMBus 3.0                                               |

| Repeated Start<br>Condition Setup Time         | t <sub>SU:STA</sub> | 0.26 | _    | _    | μs    | Per SMBus 3.0                                               |

| Setup Time: Stop                               | t <sub>SU:STO</sub> | 0.26 | _    | _    | μs    | Per SMBus 3.0                                               |

| Setup Time: Start                              | t <sub>SU:STA</sub> | 0.26 | _    | _    | μs    |                                                             |

| Data Hold Time                                 | t <sub>HD:DAT</sub> | 0    | _    | _    | μs    |                                                             |

| Data Setup Time                                | t <sub>SU:DAT</sub> | 50   | _    | _    | ns    | Per SMBus 3.0 (Note)                                        |

| Clock Low Period                               | $t_{LOW}$           | 0.5  | _    | _    | μs    | Per SMBus 3.0                                               |

| Clock High Period                              | t <sub>HIGH</sub>   | 0.26 | _    | 50   | μs    |                                                             |

| Clock/Data Fall Time                           | t <sub>FALL</sub>   |      | _    | 120  | ns    | Not tested in production                                    |

| Clock/Data Rise Time                           | t <sub>RISE</sub>   | _    | _    | 120  | ns    | Not tested in production                                    |

| Capacitive Load                                | C <sub>LOAD</sub>   | _    | _    | 550  | pF    | Per bus line,<br>C <sub>LOAD</sub> not tested in production |

| SLOW Pin Pulse Width                           | SLOWpw              |      | 100  | _    | μs    | Pulses narrower than 100 μS may not be detected             |

**Note:** A device must internally provide a hold time of at least 300 ns for the SM\_DATA signal (with respect to the V<sub>IH(min)</sub> of the SM\_CLK signal) to bridge the undefined region of the falling edge of SM\_CLK.

FIGURE 1-1: SMBus Timing.

| PA | <b>C1</b> | 93           | 2 | /3 | 14 |

|----|-----------|--------------|---|----|----|

|    |           | $\mathbf{v}$ |   |    |    |

NOTES:

#### 2.0 TYPICAL OPERATING CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62 to 5.5V.

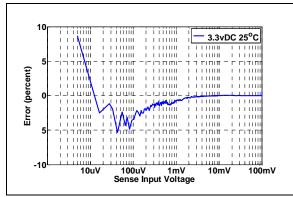

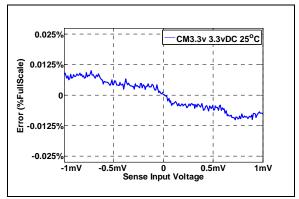

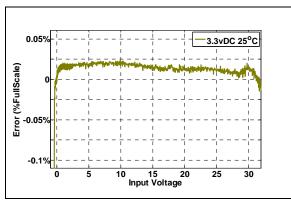

**FIGURE 2-1:**  $V_{SENSE}$  Error vs.  $V_{SENSE}$  Input Voltage.

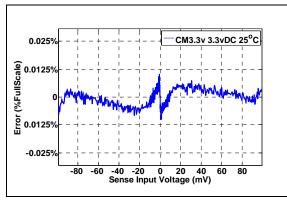

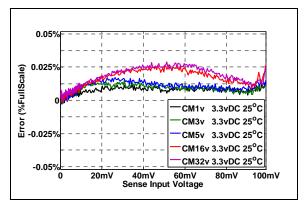

**FIGURE 2-2:** V<sub>SENSE</sub> Error vs. V<sub>SENSE</sub> Input Voltage Bidirectional Mode.

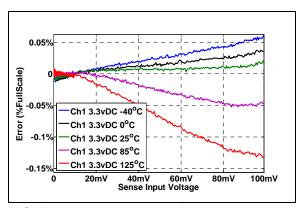

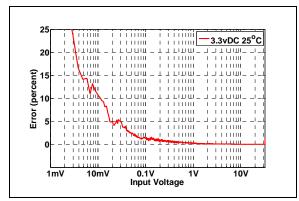

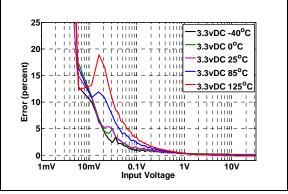

**FIGURE 2-3:** V<sub>SENSE</sub> Error vs. V<sub>SENSE</sub> Input Voltage vs. Temperature.

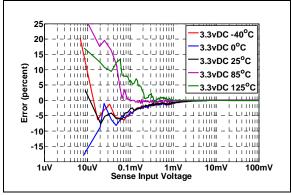

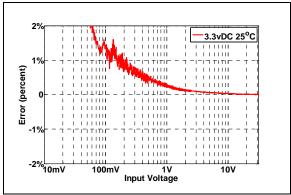

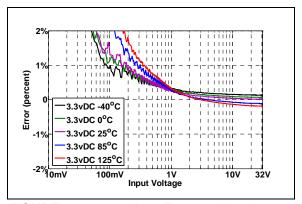

**FIGURE 2-4:** V<sub>SENSE</sub> Error vs. V<sub>SENSE</sub> Input Voltage and Temperature.

**FIGURE 2-5:** V<sub>SENSE</sub> Error vs. V<sub>SENSE</sub> Input Voltage Bidirectional Mode (Zoom View).

**FIGURE 2-6:** V<sub>SENSE</sub> Error vs. V<sub>SENSE</sub> and Common Mode.

**Note:** Unless otherwise indicated, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62 to 5.5V.

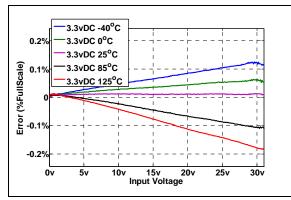

FIGURE 2-7: Voltage.

V<sub>BUS</sub> Error vs. V<sub>BUS</sub> Input

**FIGURE 2-8:**  $V_{BUS}$  Error vs.  $V_{BUS}$  Input Voltage (Zoom View).

FIGURE 2-9: Voltage.

V<sub>BUS</sub> Error vs. V<sub>BUS</sub> Input

**FIGURE 2-10:**  $V_{BUS}$  Error vs.  $V_{BUS}$  Input Voltage vs. Temperature.

**FIGURE 2-11:**  $V_{BUS}$  Error vs.  $V_{BUS}$  Input Voltage vs. Temperature (Zoom View).

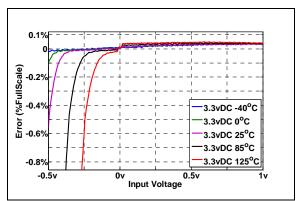

**FIGURE 2-12:** V<sub>BUS</sub> Error vs. V<sub>BUS</sub> Input Voltage vs. Temperature (Bipolar Voltage Mode).

**Note:** Unless otherwise indicated, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{BUS}$  = 3.3V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62 to 5.5V.

**FIGURE 2-13:**  $V_{BUS}$  Error vs.  $V_{BUS}$  Input Voltage vs. Temperature.

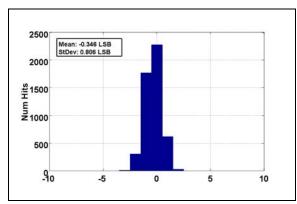

**FIGURE 2-14:** Zero Input Histogram for V<sub>BUS</sub> (LSBs, 8X Average Results, Total Population 5,000 devices).

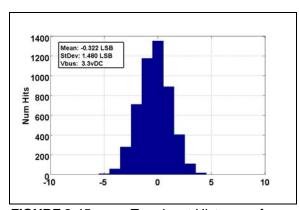

**FIGURE 2-15:** Zero Input Histogram for  $V_{SENSE}$  (LSBs, 8X Average Results, Total Population 5,000 Devices).

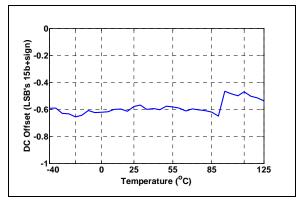

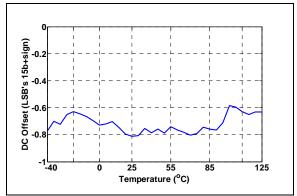

**FIGURE 2-16:** Input Offset for  $V_{BUS}$  Measurements vs. Temperature.

**FIGURE 2-17:** Input Offset for V<sub>SENSE</sub> Measurements vs. Temperature.

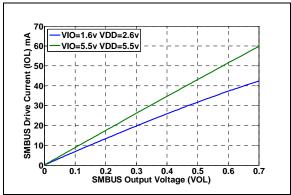

**FIGURE 2-18:**

I<sup>2</sup>C/SMBus Drive Current

vs. V<sub>OL</sub>.

**Note:** Unless otherwise indicated, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62 to 5.5V.

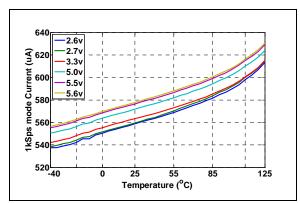

**FIGURE 2-19:** I<sub>DD</sub> vs. Temperature and Supply at 1024 Samples/Second.

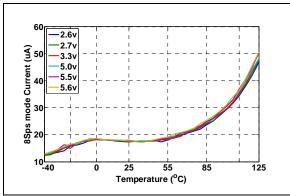

**FIGURE 2-20:**  $I_{DD}$  in SLOW Mode vs. Temperature and  $V_{DD}$ .

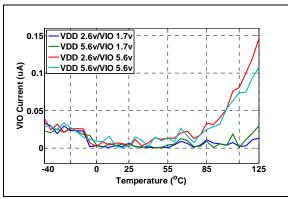

**FIGURE 2-21:**  $I_{DD}$  for  $V_{DD}$  I/O Pin vs. Temperature and  $V_{DD}$ .

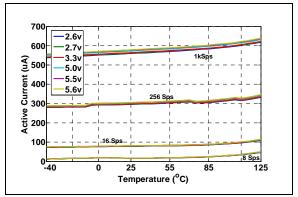

**FIGURE 2-22:**  $I_{DD}$  vs. Temperature,  $V_{DD}$ , and Sample Rate.

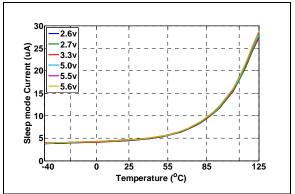

**FIGURE 2-23:**  $I_{DD}$  in SLEEP Mode vs. Temperature and  $V_{DD}$ .

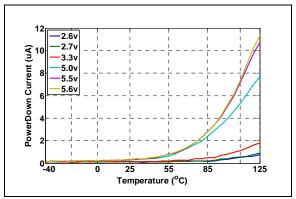

**FIGURE 2-24:**  $I_{DD}$  in Power Down Mode vs. Temperature and  $V_{DD}$ .

**Note:** Unless otherwise indicated, maximum values are at  $T_A$  = -40°C to +85°C,  $V_{DD}$  = 2.7V to 5.5V,  $V_{BUS}$  = 0V to 32V; typical values are at  $T_A$  = +25°C,  $V_{DD}$  = 3.3V,  $V_{BUS}$  = 3.3V,  $V_{SENSE}$  = (SENSE+ – SENSE-) = 0V,  $V_{DD}$  I/O = 1.62 to 5.5V.

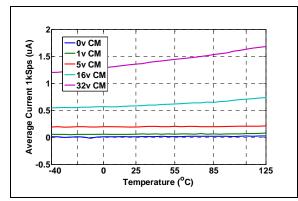

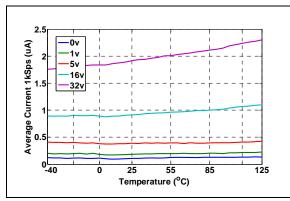

FIGURE 2-25: V<sub>SENSE</sub> Input Current – Active Mode, 1024 Samples/Second.

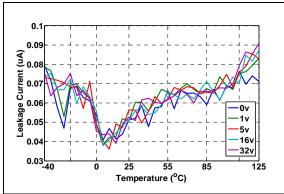

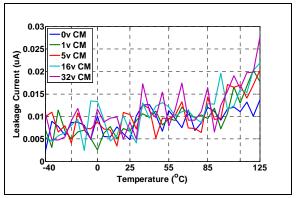

**FIGURE 2-26:**  $V_{BUS}$  Input Leakage Current vs.  $V_{DD}$  and Temperature.

**FIGURE 2-27:** V<sub>BUS</sub> Input Current – Active Mode, 1024 Samples/Second.

**FIGURE 2-28:** V<sub>SENSE</sub> Input Leakage Current vs. V<sub>DD</sub> and Temperature.

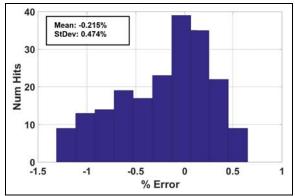

FIGURE 2-29: Clock Frequency Error -40°C to +85°C. Total Population 200 Devices.

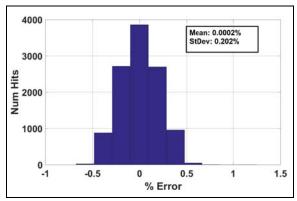

FIGURE 2-30: Clock Frequency Error at 30°C. Total Population 11,189 Devices.

Figure 2-31 shows the equivalent circuitry for the input channels of the PAC193X devices. ESD protection diodes include two 40V breakdown diodes. Input leakage current is very low (no DC bias current). The switched capacitor sampling circuits shown as a switch with equivalent series resistance and sampling capacitor. The switches work at 1024 samples per second (SPS) maximum, independent of sampling rate (at 8 SPS, the device is sleeping in between samples). Input impedance for each input is about 32  $\mbox{M}\Omega$ .

FIGURE 2-31: Equivalent Input Circuits for PAC193X Devices.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN DESCRIPTIONS

| QFN | WLCSP16 | Symbol                 | Pin Type                                       | Description                                                                                                                                                                                                         |

|-----|---------|------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | C3      | SLOW/ALERT             | Digital I/O pin                                | Voltage range is set by V <sub>DD</sub> I/O pin. Default function is SLOW, may be programmed to function as ALERT pin (Open Collector when functioning as ALERT, requires pull-up resistor to V <sub>DD</sub> I/O). |

| 2   | A4      | $V_{DD}$               | Power for IC                                   | Positive power supply voltage.                                                                                                                                                                                      |

| 3   | B4      | GND                    | Ground pin                                     | Ground for the IC.                                                                                                                                                                                                  |

| 4   | C4      | SM_CLK                 | SMBus clock input                              | Clock Input pin.                                                                                                                                                                                                    |

| 5   | D4      | SM_DATA                | SMBus data I/O                                 | Open drain requires pull-up resistor to V <sub>DD</sub> I/O.                                                                                                                                                        |

| 6   | C2      | ADDRSEL                | Analog I/O pin                                 | Address selection for the SMBus Slave address.                                                                                                                                                                      |

| 7   | C1      | SENSE3- <sup>(1)</sup> | 32V analog pin                                 | 0-32V range, connect to load side of sense resistor.                                                                                                                                                                |

| 8   | D1      | SENSE3+ <sup>(1)</sup> | 32V analog pin                                 | 0-32V range, connect to supply side of sense resistor.                                                                                                                                                              |

| 9   | D2      | SENSE4- <sup>(1)</sup> | 32V analog pin                                 | 0-32V range, connect to load side of sense resistor.                                                                                                                                                                |

| 10  | D3      | SENSE4+ <sup>(1)</sup> | 32V analog pin                                 | 0-32V range, connect to supply side of sense resistor.                                                                                                                                                              |

| 11  | A3      | SENSE1+                | 32V analog pin                                 | 0-32V range, connect to supply side of sense resistor.                                                                                                                                                              |

| 12  | A2      | SENSE1-                | 32V analog pin                                 | 0-32V range, connect to load side of sense resistor.                                                                                                                                                                |

| 13  | A1      | SENSE2+                | 32V analog pin                                 | 0-32V range, connect to supply side of sense resistor.                                                                                                                                                              |

| 14  | B1      | SENSE2-                | 32V analog pin                                 | 0-32V range, connect to load side of sense resistor.                                                                                                                                                                |

| 15  | B2      | V <sub>DD</sub> I/O    | Sets V <sub>IH</sub> reference for digital I/O | Digital power reference level for digital I/O.                                                                                                                                                                      |

| 16  | В3      | PWRDN                  | Digital input pin                              | Voltage range is set by $V_{DD}$ I/O pin. Active low puts the device in power-down state (all circuitry is powered down including SMBus).                                                                           |

| 17  | _       | EP                     | N/C                                            | The Exposed pad is not electrically connected.                                                                                                                                                                      |

**Note 1:** For PAC1932, pins 7,8,9,10 are not connected inside and should be grounded. For PAC1933, pins 9 and 10 are not connected inside and should be grounded.

#### 3.1 SenseN+/SenseN- (N=1,2,3,4)

These two pins form the differential input for measuring voltage across a sense resistor in the application. The positive input (SenseN+) also acts as the input pin for bus voltage.

#### 3.2 Ground (GND)

System ground.

#### 3.3 SMBus Data (SM\_DATA)

This is the bi-directional SMBus data pin. This pin is open drain, and requires a pull-up resistor to V<sub>DD</sub> I/O.

#### 3.4 SMBus Clock (SM\_CLK)

This is the SMBus clock input pin.

# 3.5 Positive Power Supply Voltage (V<sub>DD</sub>)

Power supply input pin for the device. 2.7-5.5V range, bypass with 100 nF ceramic capacitor to ground near the IC.

# 3.6 Digital Power Reference Voltage (V<sub>DD I/O</sub>)

Connect this pin to the power supply voltage for the digital controller driving the SMBus pins and digital input pins for the device, 1.62V-5.5V. Bypass with 100 nF ceramic capacitor to ground near the IC. This pin does not supply power, instead it acts as the  $V_{IH}$  reference.

#### 3.7 Address Selection (ADDR\_SEL)

Connect a resistor from this pin to ground to select SMBus address.

### PAC1932/3/4

### 3.8 Enable Pin (PWRDN)

Power down input pin for the device, active low.

### 3.9 SLOW/ALERT

In default mode, if this pin is forced high, sampling rate is forced to eight samples/second. When it is forced low, the sampling rate is 1024 samples/second unless a different sample rate has been programmed. This pin may be programmed to act as the  $\overline{\text{ALERT}}$  pin, in  $\overline{\text{ALERT}}$  mode the pin needs a pull-up resistor to  $V_{DD}$  I/O.

### 3.10 Exposed Thermal Pad Pin (EP)

The Exposed pad is not electrically connected. It is recommended that you connect it to ground.

#### 4.0 GENERAL DESCRIPTION

The PAC1934 is a four-channel, bidirectional, high-side current-sensing device with precision voltage measurement capabilities, DSP for power calculation and a power accumulator. PAC1932 and PAC1933 are two and three channel versions of the PAC1934. These devices measure the voltage developed across an external sense resistor ( $V_{\rm SENSE}$ ) to represent the high-side current of a battery or voltage regulator. The PAC1932/3/4 also measures the SENSE+ pin voltages ( $V_{\rm BUS}$ ). Both  $V_{\rm BUS}$  and  $V_{\rm SENSE}$  are converted to digital

results by a 16-bit ADC, and the digital results are multiplied to give  $V_{POWER}$ . The  $V_{POWER}$  results are accumulated on-chip, which enables energy measurement over the accumulation period.

The PAC1932/3/4 has an  $I^2$ C/SMBus interface for digital control and reading results. It also has digital supply reference  $V_{DD}$  I/O that is to be connected to the same supply as the digital master for the  $I^2$ C/SMBUS, enabling digital I/O voltages as low as 1.62V.

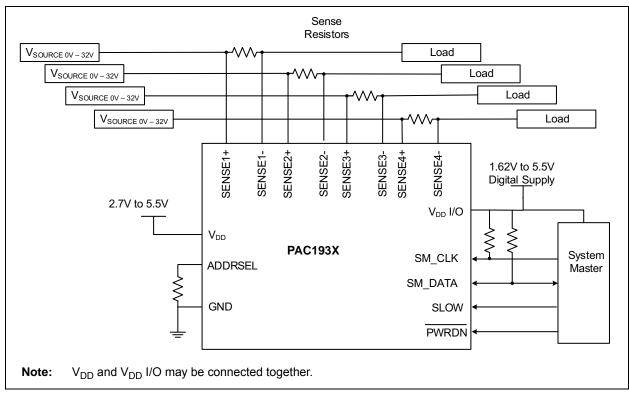

A system diagram is shown in Figure 4-1.

FIGURE 4-1: PAC1932/3/4 System Diagram.

FIGURE 4-2: PAC1932/3/4 Functional Block Diagram.

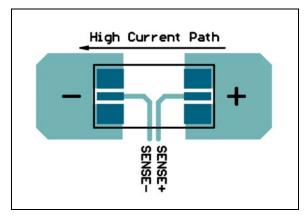

FIGURE 4-3: PCB Pattern for Sense Resistor.

**Figure 4-3** shows the recommended PCB pattern for sense resistor with wide metal for the high-current path. The drawing shows metal, solder paste openings and resistor outline.  $V_{SOURCE}$  connects to the +terminal of the high-current path, and the load connects to the -terminal of the high-current path. Sense+ and Sense- have a Kelvin connection to the current sense resistor to ensure that no metal with high current is included in the  $V_{SENSE}$  measurement path. Sense+ and Sense- are shown as a differential pair, route them as a differential pair to the Sense inputs at the chip.

#### 4.1 Detailed Description

A high-voltage multiplexer connects the input pins to the  $V_{BUS}$  and  $V_{SENSE}$  amplifiers. The amplifier outputs are sampled simultaneously for each channel, converted by 16 bit ADCs and processed for gain and offset error correction. After each conversion,  $V_{BUS}$  and  $V_{SENSE}$  are multiplied together to give  $V_{POWER}$ .

An internal oscillator and digital control signals control the two ADCs and the mux. The mux sequentially connects each channel's amplifiers to the ADC inputs.

The PAC1932/3/4 measures the source-side voltage,  $V_{BUS}$ , and the voltage  $V_{SENSE}$  across an external current sense resistor,  $R_{SENSE}$ .

### 4.1.1 INITIAL OPERATION AND ACTIVE STATE

After POR and a start-up sequence, the device is in the Active state and begins sampling the inputs sequentially. Voltage and current are sampled for all active channels and power is calculated and accumulated. All active channels are sampled at 1024 samples/second by default. Sample rates of 256, 64 or eight samples/second may be programmed over I<sup>2</sup>C or SMBus. If the SLOW pin is asserted the sample rate is eight samples per second. For sampling rates lower than 1024 samples/second, the device is in Sleep mode for a portion of the conversion cycle, which results in lower power dissipation. If fewer than four channels are active, power is also reduced.

To read accumulator data and reset the accumulators, the REFRESH command is used. To read the voltage, current, power and accumulator data without resetting the accumulators, the REFRESH\_V command is used. Changes to the Control register (01h) are activated by sending either REFRESH or REFRESH\_V. When a new value is written to the Control register (01h), the new values take effect at the end of the next round-robin sampling cycle following the next REFRESH\_V command.

#### 4.1.2 REFRESH COMMAND

The master sends the REFRESH command after changing the Control register and/or before reading accumulator data from the device. The master controls the accumulation period in this manner.

The readable registers for the  $V_{BUS}$ ,  $V_{SENSE}$ , Power, accumulator outputs and accumulator count are updated by the REFRESH command and the values will be static until the next REFRESH command. These readable registers will be stable within 1 mS from sending the REFRESH command, and may be read by the master at any time up until the next REFRESH command is sent. The internal accumulator values and accumulator count will be reset by the REFRESH command, but the sampling of the inputs,

data conversion and power integration is not interrupted and will continue as determined by the settings in the Control register.

Changes written to the control and configuration registers take effect 1 mS after a REFRESH command is sent. Any new commands written within this 1 mS window will be ignored and NACKed to indicate that they are ignored.

The values for  $V_{BUS}$  and  $V_{SENSE}$  measurement results and Power calculation results respond to the REFRESH command in the same fashion as the accumulators and accumulator count. The readable registers will be stable within 1 mS from sending the REFRESH command and may be read by the master at any time. The internal values continue to be updated according to the sampling plan determined by the settings in the Control register. The results that are sent to the readable registers for  $V_{BUS}$ ,  $V_{SENSE}$  and Power are the values from the most recent complete conversion cycle. See Register 6-1 REFRESH Command (Address 00h).

#### 4.1.3 REFRESH G COMMAND

The REFRESH\_G is identical in every respect to the REFRESH command, but it is used with the I<sup>2</sup>C General Call address (0000 000). This allows the system to issue a REFRESH command to all of the PAC1932/3/4 devices in the system with a single command. Then the data from this REFRESH G command may be read device-by-device to capture a snapshot of the system power and energy for all devices. See Register 6-12 REFRESH G Command (Address 1Eh). Note that the REFRESH G command can also be used with a valid Slave address but in this case only the device with this Slave address will receive the command. In other words it has the same properties as the REFRESH command with the possibility of being compatible with the I<sup>2</sup>C General Call address.

#### 4.1.4 REFRESH V COMMAND

If the user wants to read  $V_{SENSE}$  and  $V_{BUS}$  results, the most recent Power calculation, and/or the accumulator values and count without resetting the accumulators, the REFRESH\_V command may be sent. Sending the REFRESH\_V command and waiting 1 mS ensures that the  $V_{SENSE}$ ,  $V_{BUS}$ , Power, accumulator and accumulator count values will be stable when read by the master. The sampling of the inputs, data conversion and power integration are not interrupted and will continue as determined by the settings in the Control register. The data in these readable registers will remain stable until the next REFRESH or REFRESH\_V command. The internal accumulator values and accumulator count are unaffected by the REFRESH\_V command.

Note that the REFRESH\_V command may also be used to activate changes to the Control register, just like the REFRESH command, except with the REFRESH\_V command changes to the Control register will be enacted without resetting the accumulators or accumulator count. See Register 6-13 REFRESH\_V Command (Address 1Fh).

#### 4.1.5 SLEEP STATE

The SLEEP state is a lower power state than the Active state. While in this state, the device will draw a supply current of I<sub>SLEEP</sub> from the V<sub>DD</sub> pin. The device automatically goes to this state between conversion cycles when sampling rates lower than 1,024 samples/second are selected, or if fewer than four channels are active. All digital states and data are retained in the SLEEP state. The device can also be put in the Sleep state by setting the SLEEP bit followed by a REFRESH or REFRESH V command, and sampling will resume when the SLEEP bit is cleared followed by a REFRESH of REFRESH\_V command. The device does not go into SLEEP state based on any other condition such as static conditions on the SMBus pins. If SMBus Timeout is enabled, it is supported in SLEEP mode or ACTIVE mode.

#### 4.1.6 POWER-DOWN STATE

The Power-Down state is entered by pulling the PWRDN pin low. In this state, all circuits on the chip including the SMBus pins are inactive, and the device is in a state of minimum power dissipation.

In the Power-Down state, no data is retained in the chip (neither register configuration nor measurement data). When the PWRDN pin is pulled high, integration, measurement and accumulation will begin using the default register settings, as described in Section 4.1.1 "Initial Operation and Active State". The first measurement data may be requested by a REFRESH or REFRESH\_V command 20 ms after the PWRDN pin is pulled high.

### 4.1.7 PROGRAMMING THE SAMPLE RATE AND THE SLOW PIN

The default sampling rate after power-up is 1024 samples/second. Sampling rates of 256, 64 or 8 samples/second may be programmed in the Register 6-2 CTRL Register (Address 01h). Any time a new sample rate is programmed, it does not take effect until a REFRESH, REFRESH\_G, or REFRESH\_V command is received. When any of these REFRESH commands are received, any round-robin sampling cycle in progress will complete before the new sampling rate takes effect. For example, if the user is sampling at 8 SPS and program a new sample rate, it may take up to 125 mS for the

new sample rate to take effect and for all the sample rate related registers (like CTRL\_ACT) to show their updated values.

If one of these lower sample rates is used, power dissipation is reduced. The round-robin sampling and conversion cycle is exactly the same, but the device goes into the sleep state between conversion cycles. See Section 2.0 "Typical Operating Curves".

If the SLOW pin is pulled high, the device will sample at eight samples/second. No matter what the programmed sample rate, this new SLOW sample rate will take effect on the next conversion cycle (if a round-robin conversion cycle is in process when the SLOW pin goes high, that conversion cycle will complete before the SLOW sample rate takes effect.)

If the device is programmed for Single Shot mode, and the SLOW pin is asserted, the first sampling will begin within 125 ms after the SLOW pin is asserted.

If the device is in the Sleep state, asserting the SLOW pin will not cause sampling to start.

Whenever the SLOW pin changes state, a limited REFRESH or REFRESH\_V command may be executed by the chip hardware (default is REFRESH). Like any other REFRESH command, this resets the accumulators and accumulator count for a REFRESH command, and updates the readable registers for either REFRESH or REFRESH\_V. These are limited REFRESH commands because no programmed changes to the Control or Status registers take effect (Control and Status registers means registers 01h, 1Ch, 1Dh, and 20h-26h). The readable registers are stable with the new values within 1 ms of the SLOW pin transition.

The Slow register enables selection of REFRESH or REFRESH\_V on the SLOW pin transitions, which allows this function to be disabled for either edge, and also tracks both the state of the SLOW pin and transitions on the SLOW pin. See **Register 6-14**, SLOW (Address 20h).

This is the default functionality of the <u>SLOW</u> pin, but it may be reconfigured to function as an <u>ALERT</u> pin (see paragraph <u>Section 4.4 "Alert Functionality"</u>). If the SLOW pin is configured to serve as an <u>ALERT</u> pin, the slower sampling rate of eight samples/second is only available by programming the Control register 01h.

#### 4.2 Conversion Cycles

A conversion cycle for the device consists of analog-to-digital conversion being complete for all channels (including the real-time calibration that is part of each conversion cycle). Immediately following the data conversion, the power results are calculated for that channel and the power value is added to the accumulator. Averaged values for  $V_{\rm SENSE}$  and  $V_{\rm BUS}$  are also updated internally as part of each conversion cycle.

Data conversion and processing is performed for each active channel in sequential fashion until all active channels have been converted, completing the conversion cycle for the device. The sequential sampling of each channel, along with the calculation time and any sleep time needed to set the overall sampling rate, is referred to as a round-robin sampling period.

#### 4.3 Conversion Cycle Controls

# 4.3.1 REDUCING THE NUMBER OF CHANNELS TO BE SAMPLED

Program Register 6-10 CHANNEL\_DIS and SMBus (Address 1Ch) to reduce the number of channels that are active. The sample rate is unaffected, but power dissipation is reduced very slightly if some channels are disabled. Any or all channels may be disabled; if all channels are disabled, the device goes into Sleep mode. When a channel is disabled due to register programming in the PAC1934 or due to factory programming on the PAC1932 and PAC1933, the auto incrementing pointer will skip these channels by default (see Section 5.5 "Auto-Incrementing Pointer").

#### 4.3.2 SINGLE SHOT MODE

The Control register also allows the device to operate in Single Shot mode. In Single Shot mode, all active channels will sample and convert once, followed by results being calculated. The accumulator and accumulator count operate the same as for continuous conversion mode, accumulating each single shot power calculation and incrementing the accumulator count. The conversion cycle will start when the REFRESH command (or REFRESH\_V or REFRESH\_G) is sent.

After the single shot measurements and calculations are complete, the device will go into Sleep mode. A REFRESH, REFRESH\_G or REFRESH\_V command may be sent to read the data. The user needs to wait 3 ms after the REFRESH command before commanding another Single Shot conversion by means of sending one of the REFRESH commands. This is because a 1 ms delay is required between REFRESH commands, and coming out of Sleep requires 2 ms.

#### 4.4 Alert Functionality

The Alert functionality can serve two purposes: to notify the system that a conversion cycle for all active channels is complete, or to notify the system that the accumulator or accumulator count has overflowed.

#### 4.4.1 USING THE ALERT FUNCTION

To use the ALERT function, configure the SLOW pin to function as  $\overline{\text{ALERT}}$  using **Register 6-2** CTRL Register (Address 01h). For this configuration, the  $\overline{\text{ALERT}}$  pin must have a pull-up to  $V_{DD}$  I/O (it will function as an open drain output). If a pull-up resistor is attached to the pin for Alert functionality, the device will power up in Slow mode. Any of the four sample rates can be programmed using **Register 6-2** CTRL Register (Address 01h).

The Alert function for Accumulator Overflow can also be used without reconfiguring the SLOW pin, by monitoring the OVF bit in **Register 6-2** CTRL Register (Address 01h).

### 4.4.2 ALERT AFTER COMPLETE CONVERSION

Register 6-2 has an ALERT\_CC bit that can be used to enable the ALERT\_CC function. If this bit is set, the  $\overline{\text{ALERT}}$  pin will go low for 5  $\mu\text{S}$  after each complete conversion cycle is complete.

### 4.4.3 ALERT ON ACCUMULATOR OVERFLOW

If the ALERT function is enabled, and any of the accumulators or the accumulator count overflows, the ALERT pin may be used to notify the system. To enable this trigger for the ALERT pin, bit 1 in the Register 6-2 CTRL Register (Address 01h) must be set. Note that the OVF bit in the Register 6-2 CTRL Register (Address 01h) will be set when these overflows occur.

#### 4.4.4 CLEARING ALERT AND OVF

When the Alert function has been tripped by accumulator or accumulator count overflow, it will remain asserted until a REFRESH command is received. REFRESH\_G will also clear the OVF bit and the Alert function, but REFRESH\_V will not.

#### 4.5 Voltage Measurement

The  $V_{BUS}$  voltage for each channel is measured by the SENSE+ pin for each channel. A high-voltage multiplexer is connected to each SENSE+ pin, and the multiplexer sequentially connects each SENSE+ input to and ADC for conversion. The result is stored in a 16-bit  $V_{BUS}$  results register and the 14 MSBs are multiplied by the  $V_{SENSE}$  number for the  $V_{POWER}$  results value. The  $V_{POWER}$  results are accumulator

Full-Scale Voltage (FSV) is 32V by default. The device may be programmed for bipolar  $V_{BUS}$  measurements. in this bipolar mode, the mathematical range for negative  $V_{BUS}$  numbers is -32V, the actual range is limited to about -200mV due to physical factors. This bipolar capability for  $V_{BUS}$  enables accurate offset measurement and correction. For bipolar operation, the 16-bit  $V_{BUS}$  result is a two's complement (signed) number

The measured voltage at SENSE+ can be calculated using **Equation 4-1**.

#### **EQUATION 4-1:** BUS VOLTAGE

$V_{Source} = 32V \times \frac{V_{BUS}}{Denominator}$

Where:

$V_{SOURCE}$  = The measured voltage on the

SENSE+ pin

$V_{BUS}$  = The value read from the  $V_{BUS}$

results registers

Denominator =  $2^{16}$  for unipolar measurements

= 2<sup>15</sup> for bipolar measurements

#### 4.6 Current Measurement

The PAC1932/3/4 device family includes high-side current sensing circuits. These circuits measure the voltage ( $V_{SENSE}$ ) induced across a fixed external current sense resistor ( $R_{SENSE}$ ) and store the voltage as a 16-bit number in the  $V_{SENSE}$  Results registers.

The PAC1932/3/4 current sensing operates with a Full-Scale Range (FSR) of 100 mV in unidirectional mode (default).

When sensing unidirectional currents (the default mode), the ADC results are presented in straight binary format. For bidirectional current sensing, the ADC results are in two's complement (signed) format. For bipolar current measurements, the range is  $\pm 100$  mV, but use FSR = 100 mV in the equations that follow. For best accuracy on current values near zero, it is recommended to use the bidirectional current mode and 8x average current results.

#### 4.7 Selecting R<sub>SFNSF</sub> Values

R<sub>SENSE</sub> can easily be calculated if you know the maximum current you want to sense, as shown in **Equation 4-2**.

Consider that you may need to select a value for IMax that includes current peaks well beyond your nominal current.

### **EQUATION 4-2:** CALCULATING R<sub>SENSE</sub>

$$Rsense = \frac{FSR}{IMax}$$

Where:

$FSR = Full Scale V_{SENSE}$  voltage input  $S_{SENSE} = External R_{SENSE}$  resistor value

IMax = Maximum current to measure

Full-Scale Current (FSC) can be calculated from **Equation 4-3**.

#### **EQUATION 4-3: FULL-SCALE CURRENT**

$$FSC = \frac{100 \ mV}{R_{SENSE}}$$

Where:

FSC = Full-scale current

R<sub>SENSE</sub> = External sense resistor value

The actual current through  $R_{SENSE}$  can then be calculated using **Equation 4-4**.

#### **EQUATION 4-4:** SENSE CURRENT

$$I_{SENSE} = FSC \times \frac{V_{SENSE}}{Denominator}$$

Where:

I<sub>SENSE</sub> = Actual bus current

FSC = Full-scale current value (from

Equation 4-3)

$V_{SENSE}$  = The value read from the

V<sub>SENSE</sub> results registers

Denominator =  $2^{16}$  for unipolar measurements

2<sup>15</sup> for bipolar measurements

# 4.8 ADC Measurements, Offset, and 8x Averaging

The PAC1932/3/4 is primarily desired for energy measurements where many power readings are accumulated. This is inherently an averaging process. Individual voltage and current measurements can also benefit from averaging to reduce noise and offset. Averaged values are internally calculated for V<sub>BUS</sub> and V<sub>SENSE</sub>, with a rolling average of the most recent eight values present in the VBUSn\_AVG (Register 6-7) and VSENSEn\_AVG (Register 6-6) registers. The average is updated internally after every conversion cycle. The readable registers are updated with REFRESH, REFRESH\_V, or REFRESH\_G commands like all the other readable results registers. These averaged results may be used for the most accurate, lowest noise and lowest offset measurements.

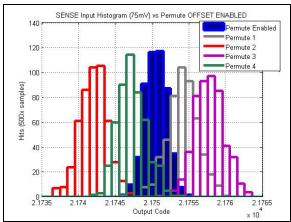

The ADC channels use a special offset canceling technique. If the user observes the unaveraged results for near-zero values of  $V_{BUS}$  and  $V_{SENSE}$ , they may observe a cyclical pattern of offset variation. The user may think this is noise, but in fact it is due to internal circuitry switching through different permutations of offset cancellation circuitry. This small variation in unaveraged offset is canceled in the 8x averaged result. It is also canceled in the Power Accumulator results. The overall effect is offset that is consistently very close to zero LSB over supply and temperature variations.

The offset canceling technique is illustrated in Figure 4-4. It is very difficult to accurately observe, as it is a challenge to read the data from every conversion cycle. The effect of capturing data points at a rate that does not correspond exactly to the internal sampling rate of the PAC1932/3/4 can make these permutations appear less periodic and deterministic than they are inside the chip. The data conversion uses one of the permute positions 1-4 for each input on each conversion, cycling through all four permutations in four conversions. When averaged the Permute Enabled result shown below is realized, evenly distributed around zero.

FIGURE 4-4: Illustration of the Four Permute Combinations that the ADC Cycles through and the Resulting Low Average Offset. Each Bin Represents One Code.

Results from both the  $V_{BUS}$  and  $V_{SENSE}$  ADCs are 17b two's complement (signed) internally. There is an additional bit of resolution that is not accessible from the results register. The NEG\_PWR (Address 1Dh) register determines whether the conversion results are reported in the readable registers as unipolar or bipolar numbers. Using bipolar numbers can give more accurate results for very small numbers that may actually be negative for some readings, in addition to measuring bidirectional currents (charging/discharging) and voltages that can dip below ground.

Averaged values are also calculated for  $V_{BUS}$  and  $V_{SENSE}$ . A rolling average of the most recent eight values is present in the VBUSn\_AVG (Register 6-7) and VSENSEn\_AVG (Register 6-6) registers. These registers require eight conversion cycles after POR before they represent an accurate value, they are updated after every conversion cycle. The readable registers are updated with REFRESH, REFRESH\_V or REFRESH\_G commands like all the other readable results registers.

#### 4.9 Power and Energy

The Full-Scale Range for Power depends on the external sense resistor used, as shown in **Equation 4-5**.

# EQUATION 4-5: POWER FSR CALCULATION

PowerFSR =

$$(100 \text{ mV/R}_{SENSE}\Omega) \times 32V$$

=  $3.2V^2/R_{SENSE}\Omega$

Where:

$R_{SENSE}\Omega$  = External  $R_{SENSE}$  resistor value 100 mV = Full-Scale  $V_{SENSE}$  voltage input 32V = Full-Scale  $V_{BUS}$  voltage input

The device implements Power measurements by multiplying  $V_{BUS}$  and the  $V_{SENSE}$  to give a result  $V_{POWER}$ .  $V_{POWER}$  values are used to calculate Proportional Power as shown in **Equation 4-6**. The Proportional Power is the fractional portion of Power FSR measured in one sample. Bipolar mode is where  $V_{BUS}$  is bipolar mode,  $V_{BUS}$  is bidirectional mode, or both  $V_{BUS}$  and  $V_{SENSE}$  are bipolar/bidirectional.

# EQUATION 4-6: PROPORTIONAL POWER CALCULATION

$$P_{PROP} = \frac{Vpower}{Denominator}$$

Where:

Denominator =  $2^{28}$  (unipolar mode) =  $2^{27}$  (bipolar mode)

To calculate the actual power from the Proportional Power, multiply by the Power FSR as shown in **Equation 4-7**. This Actual Power number is the power measured in one sample.

#### **EQUATION 4-7: POWER CALCULATION**

$$P_{actual} = PowerFSR \times P_{PROP}$$

These  $V_{\mbox{POWER}}$  results are digitally accumulated on chip, and stored in the VACCUM registers.

The energy calculation **Equations 4-8** and **4-9** use a different denominator term depending on unipolar or bipolar mode. Bipolar mode for energy applies when bipolar/bidirectional mode is used for  $V_{BUS}$  and/or  $V_{SENSE}$ . **Equation 4-8** shows how to realize this using the Accumulator results, Accumulator count and the

accumulation period, T. In this equation, T must be known from a system clock time stamp or other accurate indicator of the total accumulation period.

#### **EQUATION 4-8: ENERGY CALCULATION**

$$Energy = \frac{V(accum)}{Denominator} \times (PwrFSR) \times \frac{T}{AccCount}$$

Where:

Denominator =  $2^{28}$  (unipolar mode) =  $2^{27}$  (bipolar mode)

#### **EQUATION 4-9: ENERGY CALCULATION**

$$Energy = \frac{V(accum)}{Denominator} \times \frac{(PwrFSR)}{f_S}$$

Where:

Denominator =  $2^{28}$  (unipolar mode) =  $2^{27}$  (bipolar mode)

**Equation 4-9** shows how to calculate energy using the accumulated power and the sampling rate,  $f_s$ .

### 4.9.1 ADDITIONAL ACCUMULATOR INFORMATION

The math for the Power calculation and accumulation inside the chip is always done in two's complement math, no matter what the user sets the output registers to show.  $V_{BUS}$  and  $V_{SENSE}$  are 17-bit two's complement (signed) numbers internally.  $V_{POWER}$  is the product of  $V_{SENSE}$  multiplied by the 14 MSBs of  $V_{BUS}$ , and this is a 31 bit two's complement result (signed) internally. In some cases this results in a Power result that is not identical to the product of the  $V_{BUS}$  register multiplied by the  $V_{SENSE}$  register. However, the Power result from the Power results register is more accurate than the product of the  $V_{BUS}$  register multiplied by the  $V_{SENSE}$  register in these cases, as explained below.

If  $V_{SENSE}$  and  $V_{BUS}$  are both programmed to be unsigned (unipolar) in register NEG\_PWR (Address 1Dh), 16b without sign are exported to  $V_{BUS}$  and  $V_{SENSE}$  results registers.

If V<sub>BUS</sub> is programmed to be signed (bipolar) in Register 6-11 NEG\_PWR (Address 1Dh), the corresponding data is truncated to 16-bit two's complement (signed) for the readable results register.

If  $V_{SENSE}$  is programmed to be signed (bipolar) in register NEG\_PWR (Address 1Dh), the corresponding results register value is truncated to 16-bit two's complement (signed), but the power calculation uses 17-bit two's complement (signed). Therefore, a mismatch is possible between an externally calculated power value ( $V_{BUS}$  times  $V_{SENSE}$ ) and the actual power value calculated internally to the chip. The internally calculated (and accumulated) value is more accurate than the externally calculated value in every case.

The continuous power integration periods (also called the energy accumulation period) can range from ~1ms to many hours, depending on the number of samples per second selected via SMBus. The number of samples is limited by the size of the Accumulator Count register to 16,777,216 (2<sup>24</sup>). This count corresponds to about 273 minutes at 1024 samples/second, or 582 hours at eight samples/second. This Accumulator Count can overflow, and it will not reset when it overflows.

When the accumulation registers reach their maximum value, this is called accumulator overflow. The accumulator outputs remain at their maximum value; they do not roll over. The user can calculate the worst-case time to roll over and read them at or before that time or use the built in Alert functions to detect rollover and read them at that time.

Worst-case accumulator overflow time can be calculated assuming that every measurement that is accumulated is a full-scale number. Since the power numbers are 28 bits, and the accumulator is 48 bits, 2<sup>20</sup> samples can be accumulated before overflow if they are all full-scale values. For most applications, they will

not all be full-scale numbers; this is especially true if  $V_{BUS}$  is not 32V. If  $V_{BUS}$  is a lower number, the maximum number of full-scale samples that can be accumulated is scaled by 32V/ $V_{BUS}$ . This limitation can limit the accumulation period before overflow to 17 minutes at 1024 samples/second, or 36 hours at eight samples/second, if most values are near full-scale. The Accumulator Count limit described above will still limit the total number of samples to  $2^{24}$ .

# 5.0 SMBUS AND I<sup>2</sup>C COMMUNICATIONS PROTOCOL

The PAC1932/3/4 communicates over a two-wire bus with a controller using SMBus or I<sup>2</sup>C serial communication protocol. A detailed timing diagram is shown in Figure 1-1.

Stretching of the SMCLK signal is supported; however, the PAC1932/3/4 will not stretch the clock signal.

# 5.1 I<sup>2</sup>C/SMBus Addressing and Control Bits

#### 5.1.1 SMBUS ADDRESS AND RD/WR BIT

The SMBus Address Byte consists of the 7-bit slave address followed by a 1-bit RD /  $\overline{WR}$  indicator. If this RD /  $\overline{WR}$  bit is a logic '0', the SMBus master is writing data to the slave device. If this RD /  $\overline{WR}$  bit is a logic '1', the SMBus master is reading data from the slave device.

The PAC1932/3/4 I<sup>2</sup>C/SMBus address is determined by a single pull-down resistor connected between ground and the ADDRSEL pin as shown in Table 5-1. The chip translates the resistor value into an address on power-up, and the value is latched until another power-up event takes place. The address cannot be changed on the fly.

#### 5.1.2 SMBUS START BIT

The SMBus Start bit is defined as a transition of the SMBus data line from a logic '1' state to a logic '0' state while the SMBus Clock line is in a logic '1' state.

#### 5.1.3 SMBUS ACK AND NACK BITS

The SMBus slave will ACK (acknowledge) all data bytes that it receives. This is done by the slave device pulling the SMBus data line low after the eighth bit of each byte that is transmitted.

#### 5.1.4 SMBUS STOP BIT

The SMBus Stop bit is defined as a transition of the SMBus data line from a logic '0' state to a logic '1' state while the SMBus clock line is in a logic '1' state. When the PAC1932/3/4 detects an SMBus Stop bit, and it has been communicating with the SMBus protocol, it will reset its slave interface and prepare to receive further communications.

#### 5.1.5 SMBUS DATA BYTES

All SMBus data bytes are sent most significant bit first and composed of eight bits of information.

TABLE 5-1: ADDRESS SELECT RESISTOR

| Resistor (1%)          | SMBus Address |

|------------------------|---------------|

| 0 (Tie to GND)         | 0010_000(r/w) |

| 499                    | 0010_001(r/w) |

| 806                    | 0010_010(r/w) |

| 1,270                  | 0010_011(r/w) |

| 2,050                  | 0010_100(r/w) |

| 3,240                  | 0010_101(r/w) |

| 5,230                  | 0010_110(r/w) |

| 8,450                  | 0010_111(r/w) |

| 13,300                 | 0011_000(r/w) |

| 21,500                 | 0011_001(r/w) |

| 34,000                 | 0011_010(r/w) |

| 54,900                 | 0011_011(r/w) |

| 88,700                 | 0011_100(r/w) |

| 140,000                | 0011_101(r/w) |

| 226,000                | 0011_110(r/w) |

| Tie to V <sub>DD</sub> | 0011_111(r/w) |

#### 5.2 SMBus Time-Out

The PAC1932/3/4 can support the SMBus Time-Out functionality. This functionality is disabled by default, and can be enabled by writing to the Timeout bit (see **Register 6-10** CHANNEL\_DIS and SMBus (Address 1Ch).

If Time-Out is enabled and the clock is held at logic '0' for  $t_{\text{TIMEOUT}}$  = 25-43 ms, the device will time-out and reset the SMBus interface. Communication is restored with a start condition.

### 5.3 SMBus and I<sup>2</sup>C Compatibility

The PAC1932/3/4 is compatible with SMBus 3.0 1 MHz class and I $^2$ C Fast-mode Plus. The major differences between SMBus and I $^2$ C devices are highlighted here. For more information, refer to the SMBus 3.0 and I $^2$ C specifications.

- If Time-Out function is enabled, the minimum frequency for SMBus communications is 10 kHz. If Time-Out function is disabled (default condition), then there is no minimum frequency for SMBus communications.

- If SMBus Time-Out is enabled in Register 6-10: CHANNEL\_DIS and SMBus (Address 1Ch), the SMBus slave protocol will reset if the clock is held at a logic '0' for t<sub>TIMEOUT</sub>. I<sup>2</sup>C does not have a time-out, this is the default condition.

- 3. I<sup>2</sup>C devices do not support the Alert Response Address functionality (which is optional for SMBus). The PAC1932/3/4 does not support the Alert Response Address functionality; instead, the ALERT is a GPIO pin that may be monitored by the master or Embedded Controller.

- 4. I<sup>2</sup>C devices support Block Read and Block Write differently. I<sup>2</sup>C protocol allows for unlimited number of bytes to be sent in either direction. The SMBus protocol for Block Read and Block Write requires that an additional data byte indicating number of bytes to read/write is transmitted. PAC1932/3/4 devices support the I<sup>2</sup>C protocol for Block Read by default (no byte count information is sent). If the Byte Count bit is set (see Register 6-10: CHANNEL\_DIS and SMBus (Address 1Ch), it will be sent as the first data byte in response to the Block Read command, per SMBus protocol.

#### 5.4 I<sup>2</sup>C/SMBus Protocols

The PAC1932/3/4 supports Write Byte, Read Byte, Block Read, Send Byte and Receive Byte as valid protocols.

It will not respond to the Alert Response Address protocol. It will respond to the  $I^2C$  General Call Address.

All of the protocol charts listed below use the convention in **Table 5-2**.

TABLE 5-2: PROTOCOL FORMAT

| Data Sent to Device | Data Sent to the Master |

|---------------------|-------------------------|

| # of bits sent      | # of bits sent          |

#### 5.5 Auto-Incrementing Pointer

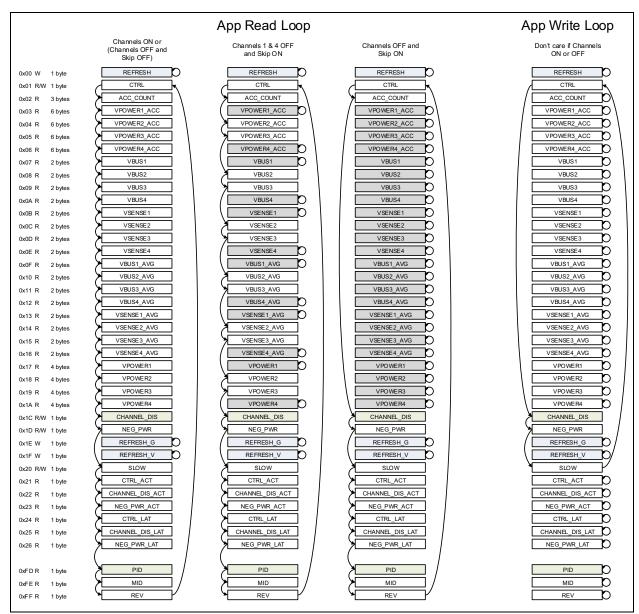

The PAC1932/3/4 has an auto-incrementing address pointer. The pointer has two loops for auto-incrementing, a read loop and a write loop.

The read loop includes all of the readable registers — all of the configuration and Control registers, the results registers, and the Product ID, Manufacturer ID and Revision ID registers.

The write loop includes only the writable control and configuration registers.

Neither loop includes the REFRESH commands.

The read loop will skip inactive channels, if some channels have been disabled. This automatic channel skipping feature can be disabled by setting the No Skip bit in **Register 6-10**: CHANNEL\_DIS and SMBus (Address 1Ch).

If the user elects to read disabled channels, they will return FFh and the register address will by NACKed.

See Figure 5-1 for a graphic representation.

FIGURE 5-1: READ and WRITE Auto Incrementing Loops.

**Figure 5-1** shows how the auto-incrementing READ loop works with SKIP option on and off, for reading. It also shows how the WRITE loop works with the REFRESH, REFRESH\_V, and REFRESH\_G commands.

#### 5.6 I<sup>2</sup>C/SMBus Commands

#### 5.6.1 REFRESH AND REFRESH V

REFRESH and REFRESH\_V commands are sent using the Send byte command, the Slave Address and the desired command (00h for REFRESH or 1Fh for REFRESH\_V. See **Table 5-3**.

TABLE 5-3: REFRESH AND REFRESH V COMMANDS

| START | Slave Address | WR | ACK | REFRESH or<br>REFRESH_V<br>Command | ACK | STOP  |

|-------|---------------|----|-----|------------------------------------|-----|-------|

| 1 → 0 | YYYY_YYY      | 0  | 0   | 00h or 1Fh                         | 0   | 0 → 1 |

# 5.6.2 GENERAL CALL ADDRESS RESPONSE

When the master sends the General Call address, the PAC1932/3/4 will be able to execute the REFRESH command by means of a second version of the REFRESH command called REFRESH\_G (see Register 6-12 REFRESH\_G Command (Address 1Eh)).

Just as the REFRESH command is sent using a Send Byte command with the slave address, and the REFRESH command (00h), the REFRESH\_G command is sent using Send Byte with the General Call address (0000 000) and the REFRESH\_G command (1Eh).

**Table 5-4** shows the response to the General Call command for REFRESH\_G.

TABLE 5-4: GENERAL CALL RESPONSE

| START | General Call<br>Address | WR | ACK | REFRESH_G<br>Command | ACK | STOP  |

|-------|-------------------------|----|-----|----------------------|-----|-------|

| 1 → 0 | 0000_000                | 0  | 0   | 1Eh                  | 0   | 0 → 1 |

#### 5.6.3 WRITE BYTE

The Write Byte is used to write one byte of data to the registers, as shown in **Table 5-5**.

TABLE 5-5: WRITE BYTE PROTOCOL

| START | Slave<br>Address | WR | ACK | Register<br>Address | ACK | Register<br>Data | ACK | STOP  |

|-------|------------------|----|-----|---------------------|-----|------------------|-----|-------|

| 1 → 0 | YYYY_YYY         | 0  | 0   | XXh                 | 0   | XXh              | 0   | 0 → 1 |

#### 5.6.4 READ BYTE

The Read Byte protocol is used to read one byte of data from the registers, as shown in **Table 5-6**.

If an invalid register address is specified, the slave will ACK its address but NACK (not acknowledge) the register address.

The master will NACK the data received from the slave by holding the SMBus data line high after the eighth data bit has been sent.

#### TABLE 5-6: READ BYTE PROTOCOL

| START | Slave<br>Address | WR | ACK | Register<br>Address | ACK | START | Slave Address | RD | ACK | Register Data | NACK | STOP  |

|-------|------------------|----|-----|---------------------|-----|-------|---------------|----|-----|---------------|------|-------|

| 1 → 0 | YYYY_YYY         | 0  | 0   | XXh                 | 0   | 1 → 0 | YYYY_YYY      | 1  | 0   | XXh           | 1    | 0 → 1 |

#### 5.6.5 SEND BYTE

The Send Byte protocol is used to set the internal address register pointer to the correct address location. No data is transferred during the Send Byte protocol, as shown in **Table 5-7**.

TABLE 5-7: SEND BYTE PROTOCOL

| START | Slave Address | WR | ACK | Register Address | ACK | STOP  |

|-------|---------------|----|-----|------------------|-----|-------|

| 1 → 0 | YYYY_YYY      | 0  | 0   | XXh              | 0   | 0 → 1 |

#### 5.6.6 RECEIVE BYTE

The Receive Byte protocol is used to read data from a register when the internal register address pointer is known to be at the right location (e.g., set via Send Byte). This is shown in **Table 5-8**.

When an ACK is received after the REGISTER DATA, then the address pointer automatically increments.

When a NACK is received after the REGISTER DATA, then the address pointer stays at the same position.

If the master wishes to continue clocking and read the next register, the master will ACK after the register data, instead of sending NACK followed by STOP.

If some channels are deactivated, their data registers will be skipped by the auto-incrementing pointer. Alternatively, you may set bit 0 in Register 6-10 CHANNEL\_DIS and SMBus (Address 1Ch) and the pointer will not skip the addresses associated with the inactive channels. The measurement data for these inactive channels will read FFh.

TABLE 5-8: RECEIVE BYTE PROTOCOL

| START | Slave Address | RD | ACK | Register Data | NACK | STOP  |

|-------|---------------|----|-----|---------------|------|-------|

| 1 → 0 | YYYY_YYY      | 1  | 0   | XXh           | 1    | 0 → 1 |

#### 5.6.7 BLOCK READ – I<sup>2</sup>C VERSION

Block Read is used to read multiple data bytes from a register that contains more than one byte of data, or from a group of contiguous registers, as shown in **Table 5-9**. The PAC1932/3/4 supports I<sup>2</sup>C Block Read by default, but the SMBus format can also be supported (see **Table 5-10**).

If an invalid register address is specified, the slave will ACK its address but NACK the register address.

The master will NACK the data received from the slave by holding the SMBus data line high after the 8<sup>th</sup> data bit has been sent.

TABLE 5-9: BLOCK READ PROTOCOL I<sup>2</sup>C VERSION (DEFAULT)

| START | Slave Address | WR  | ACK              | Register<br>Address | ACK              | START | Slave Address | RD               | ACK  | Register<br>Data |

|-------|---------------|-----|------------------|---------------------|------------------|-------|---------------|------------------|------|------------------|

| 1 → 0 | YYYY_YYY      | 0   | 0                | XXh                 | 0                | 1 → 0 | YYYY_YYY      | 1                | 0    | XXh              |

| ACK   | Register Data | ACK | Register<br>Data | ACK                 | Register<br>Data | ACK   |               | Register<br>Data | NACK | STOP             |

| 0     | XXh           | 0   | XXh              | 0                   | XXh              | 0     |               | XXh              | 1    | 0 → 1            |

#### 5.6.8 BLOCK READ – SMBUS VERSION