# CY14V116F7 CY14V116G7

# 16-Mbit nvSRAM with Asynchronous NAND Interface

### Features

- 16-Mbit nonvolatile static random access memory (nvSRAM)

Performance up to 33 MT/s per I/O

- □ Maximum data throughput using ×16 bus 528 Mbps

- Industry-standard asynchronous NAND Flash interface with reduced instruction set

- Shared address, data, and command bus

- Address and command bus is 8 bits

- Command is sent in one or two command cycles

- · Address is sent in five address cycles

- Data bus width is ×8 or ×16 bits

#### Modes of operation:

- Asynchronous NAND Interface I/O with 30-ns access time

Status Register with a software method for detecting the following:

- Nonvolatile STORE completion

- · Pass/Fail condition of previous command

- Write protect status

- Hands-off automatic STORE on power-down with only a small capacitor

- STORE to QuantumTrap nonvolatile elements is initiated by a software command, a dedicated hardware pin, or AutoStore on power-down

- RECALL to SRAM initiated by software or power-up

- High reliability

- Infinite read, write, and RECALL cycles

1 million STORE cycles to QuantumTrap

- Data retention: 20 years at 85 °C

- Operating voltage

Core V<sub>CC</sub> = 2.7 V to 3.6 V; I/O V<sub>CCQ</sub> = 1.70 V to 1.95 V

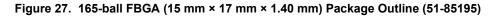

- 165-ball fine-pitch ball grid array (FBGA) package

- Industrial temperature: -40 °C to +85 °C

- Restriction of hazardous substances (RoHS) compliant

#### Overview

Cypress nvSRAM combines high-performance SRAM cells with nonvolatile elements in a monolithic integrated circuit. The embedded nonvolatile elements incorporate the Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) technology, producing the world's most reliable nonvolatile memory. The SRAM can be read and written an infinite number of times. The nonvolatile data resides in the nonvolatile elements and does not change when data is written to the SRAM.

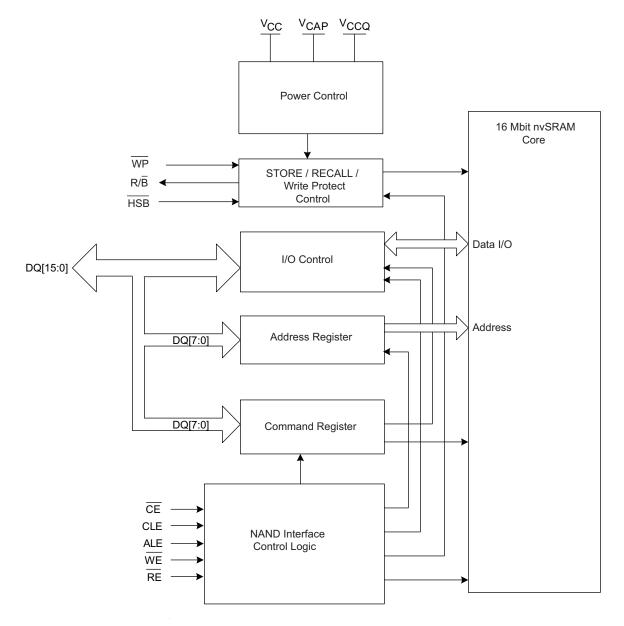

The CY14V116F7/CY14V116G7 nvSRAM provides access through a standard asynchronous NAND interface and supports the ×8 and ×16 interface options. In the case of ×16 interface, data bytes are transmitted over the DQ[15:0] lines and has double the throughput compared to the DQ[7:0] bus. The CY14V116F7/ CY14V116G7 uses a highly multiplexed DQ bus to transfer data, addresses, and instructions. All addresses and commands are always transmitted over the data bus DQ[7:0]. Therefore, in the case of the ×16 bus interface, the upper eight data bits DQ[15:8] become don't care bits during the address and command cycles. The <u>CY14V116F7/CY14V116F7/CY14V116F7</u> uses five control pins (CLE, ALE, CE, RE, and WE) to transfer command, address, and data during read and write operations. Additional I/O pins, such as write protect (WP), ready/busy (R/B), and HSB STORE, are used to support features in the device.

The asynchronous NAND interface nvSRAM is aligned to a majority of the ONFI 1.0 specifications and supports data access speed up to 33 MHz.

For a complete list of related documentation, click here.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised January 7, 2015

### **Block Diagram**

#### **Single-Channel Architecture**

# CY14V116F7 CY14V116G7

### Contents

| Pin Configurations                  | . 4 |

|-------------------------------------|-----|

| Pin Definitions                     | . 5 |

| Discovery and Initialization        | . 5 |

| nvSRAM Bus Operations               |     |

| Control Signals                     | . 5 |

| nvSRAM Bus Modes                    | . 6 |

| nvSRAM Enable/Standby               | . 6 |

| nvSRAM Bus Idle                     |     |

| nvSRAM Commands                     | . 6 |

| nvSRAM Address Input                | . 7 |

| nvSRAM Data Input                   | . 8 |

| nvSRAM Data Output                  | . 8 |

| Command Definition                  | . 9 |

| Basic Operations                    |     |

| Read ID (90h) Definition            |     |

| Read Parameter Page (ECh)           |     |

| Read Status (70h) Definition        |     |

| Status Field Definition             |     |

| nvSRAM Burst Mode Read (00h, 30h)   |     |

| nvSRAM Burst Write (80h, 10h)       |     |

| Reset (FFh) Definition              |     |

| nvSRAM Software RECALL (FCh)        |     |

| Software STORE (84h, A5h) in nvSRAM |     |

| nvSRAM AutoStore Disable (A3h)      |     |

| nvSRAM AutoStore Enable (ACh)       |     |

| Write Protect                       |     |

| nvSRAM Store Operations             |     |

| AutoStore Operation                 |     |

| Hardware STORE (HSB) Operation      |     |

| Software Store Operation            | 19  |

|                                     |     |

| nvSRAM RECALL Operations                | 19       |

|-----------------------------------------|----------|

| Hardware RECALL (Power Up)              | 19       |

| Software Recall                         | 19       |

| Maximum Ratings                         | 20       |

| Operating Range                         | 20       |

| DC Electrical Characteristics           |          |

| Data Retention and Endurance            | 21       |

| Capacitance                             | 21       |

| Thermal Resistance                      |          |

| AC Test Conditions                      | 22       |

| AC Switching Characteristics            | 23       |

| Timing Modes                            | 23       |

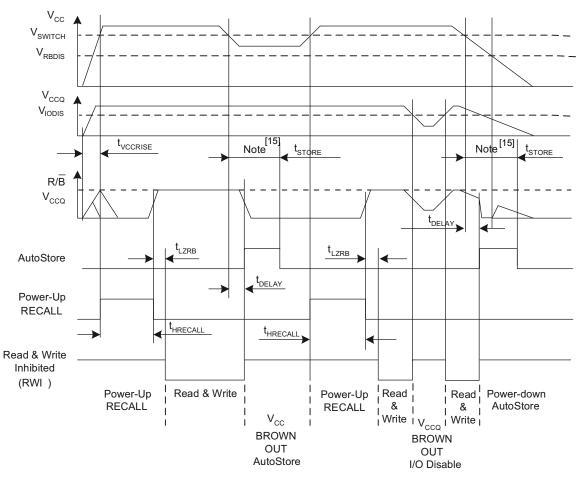

| nvSRAM AutoStore/Power-Up RECALL        |          |

| Characteristics                         |          |

| Hardware STORE Characteristics          |          |

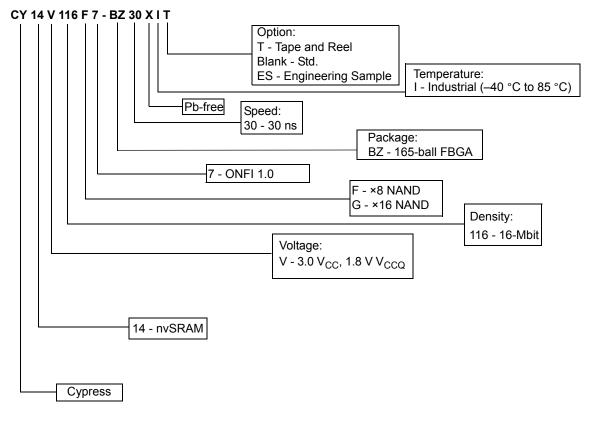

| Ordering Information                    | 26       |

| Ordering Code Definitions               | 26       |

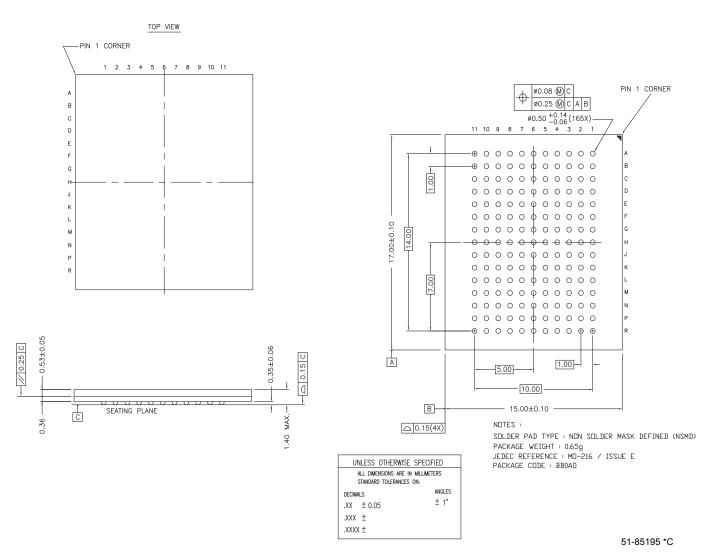

| Package Diagram                         | 27       |

| Acronyms                                |          |

| Document Conventions                    | 28       |

| Units of Measure                        | 28       |

| Document History Page                   | 29       |

| Sales, Solutions, and Legal Information | 31       |

| Worldwide Sales and Design Support      | 31       |

| Due du ete                              |          |

| Products                                | -        |

| Products<br>PSoC® Solutions             | -        |

|                                         | 31<br>31 |

# **Pin Configurations**

| Figure 1. | Single-Channel ( | (×8) Pin Diagra | am: 165-ball FBGA |

|-----------|------------------|-----------------|-------------------|

|           |                  |                 |                   |

|   | 1  | 2                | 3                | 4        | 5               | 6  | 7               | 8               | 9                | 10               | 11 |

|---|----|------------------|------------------|----------|-----------------|----|-----------------|-----------------|------------------|------------------|----|

| Α | R  | R                | R                | NC       | NC              | NC | NC              | NC              | R                | R                | R  |

| В | R  | R                | R                | NC       | NC              | NC | NC              | NC              | R                | R                | R  |

| С | R  | V <sub>CCQ</sub> | V <sub>CCQ</sub> | NC       | V <sub>SS</sub> | NC | V <sub>CC</sub> | NC              | V <sub>CCQ</sub> | V <sub>CCQ</sub> | R  |

| D | R  | $V_{SS}$         | NC               | $V_{SS}$ | NC              | NC | NC              | V <sub>SS</sub> | NC               | $V_{SS}$         | R  |

| E | NC | NC               | NC               | NC       | NC              | NC | NC              | NC              | NC               | NC               | NC |

| F | NC | $V_{SS}$         | V <sub>CCQ</sub> | NC       | NC              | NC | NC              | NC              | V <sub>CCQ</sub> | $V_{SS}$         | NC |

| G | NC | NC               | NC               | NC       | R               | NC | NC              | NC              | NC               | HSB              | NC |

| н | NC | $V_{SS}$         | V <sub>CC</sub>  | R/B      | NC              | NC | NC              | NC              | V <sub>CC</sub>  | $V_{SS}$         | NC |

| J | NC | V <sub>CAP</sub> | NC               | CE       | NC              | NC | NC              | WP              | R                | NC               | NC |

| К | NC | $V_{SS}$         | V <sub>CCQ</sub> | NC       | NC              | NC | CLE             | ALE             | V <sub>CCQ</sub> | $V_{SS}$         | NC |

| L | NC | DQ7              | DQ6              | NC       | WE              | NC | NC              | NC              | DQ1              | DQ0              | NC |

| М | R  | $V_{SS}$         | DQ5              | $V_{SS}$ | RE              | NC | NC              | V <sub>SS</sub> | DQ2              | $V_{SS}$         | R  |

| N | R  | V <sub>CCQ</sub> | V <sub>CCQ</sub> | DQ4      | V <sub>CC</sub> | NC | V <sub>SS</sub> | DQ3             | V <sub>CCQ</sub> | V <sub>CCQ</sub> | R  |

| Р | R  | R                | R                | NC       | NC              | NC | NC              | NC              | R                | R                | R  |

| R | R  | R                | R                | NC       | NC              | NC | NC              | NC              | R                | R                | R  |

Figure 2. Single-Channel (×16) Pin Diagram: 165-ball FBGA

|   | 1  | 2                | 3                | 4               | 5               | 6  | 7               | 8               | 9                | 10               | 11 |

|---|----|------------------|------------------|-----------------|-----------------|----|-----------------|-----------------|------------------|------------------|----|

| Α | R  | R                | R                | NC              | NC              | NC | NC              | NC              | R                | R                | R  |

| В | R  | R                | R                | NC              | NC              | NC | NC              | NC              | R                | R                | R  |

| С | R  | V <sub>CCQ</sub> | V <sub>CCQ</sub> | DQ11            | V <sub>SS</sub> | NC | V <sub>CC</sub> | DQ12            | V <sub>CCQ</sub> | V <sub>CCQ</sub> | R  |

| D | R  | V <sub>SS</sub>  | DQ10             | V <sub>SS</sub> | NC              | NC | NC              | V <sub>SS</sub> | DQ13             | V <sub>SS</sub>  | R  |

| Е | NC | DQ8              | DQ9              | NC              | NC              | NC | NC              | NC              | DQ14             | DQ15             | NC |

| F | NC | V <sub>SS</sub>  | V <sub>CCQ</sub> | NC              | NC              | NC | NC              | NC              | V <sub>CCQ</sub> | $V_{SS}$         | NC |

| G | NC | NC               | NC               | NC              | R               | NC | NC              | NC              | NC               | HSB              | NC |

| н | NC | V <sub>SS</sub>  | V <sub>CC</sub>  | R/B             | NC              | NC | NC              | NC              | V <sub>CC</sub>  | V <sub>SS</sub>  | NC |

| J | NC | V <sub>CAP</sub> | NC               | CE              | NC              | NC | NC              | WP              | R                | NC               | NC |

| к | NC | V <sub>SS</sub>  | V <sub>CCQ</sub> | NC              | NC              | NC | CLE             | ALE             | V <sub>CCQ</sub> | V <sub>SS</sub>  | NC |

| L | NC | DQ7              | DQ6              | NC              | WE              | NC | NC              | NC              | DQ1              | DQ0              | NC |

| м | R  | V <sub>SS</sub>  | DQ5              | V <sub>SS</sub> | RE              | NC | NC              | V <sub>SS</sub> | DQ2              | V <sub>SS</sub>  | R  |

| Ν | R  | V <sub>CCQ</sub> | V <sub>CCQ</sub> | DQ4             | V <sub>CC</sub> | NC | V <sub>SS</sub> | DQ3             | V <sub>CCQ</sub> | V <sub>CCQ</sub> | R  |

| Р | R  | R                | R                | NC              | NC              | NC | NC              | NC              | R                | R                | R  |

| R | R  | R                | R                | NC              | NC              | NC | NC              | NC              | R                | R                | R  |

### **Pin Definitions**

| Pin Name                | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/B                     | Output       | <b>Ready/Busy.</b> The ready/busy signal indicates the device status. When it is pulled LOW, the signal indicates that nvSRAM is busy doing either a STORE or a power-up RECALL or a Software RECALL/Software STORE/AutoStore Disable/AutoStore Enable operation. This signal is an open drain output and requires an external pull-up resistor. |

| RE                      | Input        | Read Enable. The read enable signal enables the data output during read operation.                                                                                                                                                                                                                                                               |

| CE                      | Input        | Chip Enable. The chip enable signal selects the device when pulled LOW. When chip enable is HIGH and the device is not busy doing a STORE operation, the device goes into a low-power standby state.                                                                                                                                             |

| CLE                     | Input        | <b>Command Latch Enable.</b> The command latch enable signal is used to latch the command byte. This is one of the signals used by the host to indicate the type of bus cycle (command, address, and data).                                                                                                                                      |

| ALE                     | Input        | Address Latch Enable. The address latch enable signal is used to latch the address byte. This is one of the signals used by the host to indicate the type of bus cycle (command, address, and data).                                                                                                                                             |

| WE                      | Input        | Write Enable. The write enable signal controls the latching of the input data on every rising edge.                                                                                                                                                                                                                                              |

| WP                      | Input        | Write Protect. The WP disables the SRAM write operation in nvSRAM if pulled LOW.                                                                                                                                                                                                                                                                 |

| DQ[7:0] <sup>[1]</sup>  | Input/Output | <b>I/O Port, 8 bits for the ×8 configuration.</b> The I/O port is an 8-bit wide bidirectional port for transferring address, command, and data to and from the device.                                                                                                                                                                           |

| DQ[15:0] <sup>[1]</sup> | Input/Output | <b>I/O Port, 16 bits for the ×16 configuration.</b> The I/O port is a 16-bit wide bidirectional bus to transfer data words to and from the device during write and read operations. Address and commands are always transmitted over the lower 8 bits DQ[7:0].                                                                                   |

| HSB                     | Input        | Hardware STORE. When pulled LOW external to the chip, it will initiate a nonvolatile STORE operation.                                                                                                                                                                                                                                            |

| V <sub>CAP</sub>        | Power supply | AutoStore capacitor: Supplies power to the nvSRAM during power loss to store data from SRAM to nonvolatile elements.                                                                                                                                                                                                                             |

| V <sub>CC</sub>         | Power supply | Power. Power supply inputs to the core of the device.                                                                                                                                                                                                                                                                                            |

| V <sub>CCQ</sub>        | Power supply | I/O Power. Power supply inputs for the inputs and outputs of the device.                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub>         | Power supply | Ground for the device. Must be connected to ground of the system.                                                                                                                                                                                                                                                                                |

| R                       | R            | Reserved. These pins are reserved, should be left unconnected by the host.                                                                                                                                                                                                                                                                       |

| NC                      | NC           | No Connect. Die pads are not connected to the package pin.                                                                                                                                                                                                                                                                                       |

### **Discovery and Initialization**

When the power-up cycle starts and V<sub>CC</sub> crosses the V<sub>SWITCH</sub> threshold, the device initializes an internal Power-up RECALL operation and pulls the R/ $\overline{B}$  pin LOW for t<sub>RECALL</sub> duration. When the power-up cycle is completed, the device releases the R/ $\overline{B}$  pin, which is then pulled HIGH by an external pull-up resistor connected to it. The R/ $\overline{B}$  HIGH indicates the device's ready status and allows the host controller to communicate with the device by executing opcodes. All supported opcodes are described in Table 3 on page 9.

### nvSRAM Bus Operations

The nvSRAM device I/Os are multiplexed. Data I/O, addresses, and commands all share the same I/O pins. DQ[15:8] are used only for data in the ×16 configuration. Addresses and commands

are always transmitted through DQ[7:0] and data through DQ[15:0] in the ×16 configuration.

The command sequence normally consists of a Command Latch cycle, Address Input cycles, and one or more Data cycles, either Read or Write.

### **Control Signals**

The <u>nvSRAM</u> control signals, such as  $\overline{CE}$ ,  $\overline{WE}$ ,  $\overline{RE}$ , CLE, ALE, and  $\overline{WP}$ , control the nvSRAM device read and write operations. The  $\overline{CE}$  is used to enable the device when pulled LOW and the device is not in the busy state. When the nvSRAM is selected, it accepts command, address, and data bytes. The nvSRAM will enter the standby mode if  $\overline{CE}$  goes HIGH while data is being transferred and the device is not busy.

A HIGH CLE signal, along with  $\overline{CE}$  and  $\overline{WE}$  LOW, indicates a command input cycle. Similarly, a HIGH ALE signal, along with  $\overline{CE}$  and  $\overline{WE}$  LOW, indicates an Address Input cycle.

#### Note

1. Data DQ[7:0] for the ×8 configuration and data DQ[15:0] for the ×16 configuration.

### nvSRAM Bus Modes

Depending upon the input control signals status, the nvSRAM takes any of the following bus states as defined in Table 1.

| Table 1. | Asynch | ronous NAN | D Interface | Bus Modes |

|----------|--------|------------|-------------|-----------|

|----------|--------|------------|-------------|-----------|

| CE | ALE | CLE | WE | RE | WP | Bus State             |

|----|-----|-----|----|----|----|-----------------------|

| 1  | Х   | Х   | Х  | Х  | Х  | Standby               |

| 0  | 0   | 0   | 1  | 1  | Х  | Bus Idle              |

| 0  | 0   | 1   | 0  | 1  | Х  | Command cycle         |

| 0  | 1   | 0   | 0  | 1  | Х  | Address cycle         |

| 0  | 0   | 0   | 0  | 1  | Н  | Write Cycle           |

| 0  | 0   | 0   | 1  | 0  | Х  | Read Cycle            |

| 0  | 1   | 1   | Х  | Х  | Х  | Undefined             |

| 0  | 0   | 0   | 0  | 1  | L  | Write protect to SRAM |

**Note** Signal with state 'X' can be either  $\geq$  V<sub>IH</sub> or  $\leq$  V<sub>IL</sub>.

#### nvSRAM Enable/Standby

A chip enable  $(\overline{CE})$  signal is used to enable or disable the device. When  $\overline{CE}$  is driven LOW, all nvSRAM input signals are enabled. With  $\overline{CE}$  LOW, the nvSRAM can accept commands, addresses, and data on its DQ lines. The nvSRAM is disabled when  $\overline{CE}$  is driven HIGH, even when the device is busy. The nvSRAM enters the low-power standby mode when the device status is ready and R/B is pulled HIGH by the external pull-up resistor. When  $\overline{CE}$  is disabled, all nvSRAM I/Os are disabled except  $\overline{WP}$ , R/B, and HSB.

#### nvSRAM Bus Idle

The nvSRAM goes to the bus idle state when  $\overline{CE}$ , ALE, CLE are LOW, and  $\overline{WE}$ , RE are HIGH. During bus idle, all the input signals are enabled but the commands, addresses, and data are not latched in the device and there is also no data output from the device.

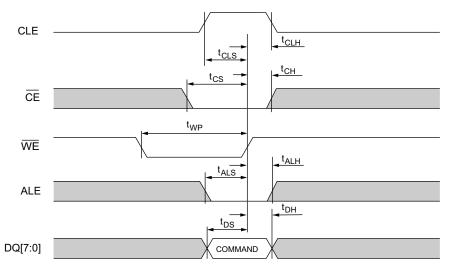

#### nvSRAM Commands

A command is written from DQ[7:0] to the command register on the rising edge of WE when CE is LOW, ALE is LOW, CLE is HIGH, and RE is HIGH. All commands except the status register read (70h) and reset (FFh) are ignored when the nvSRAM is busy (RDY bit is set to '0' in the status register).

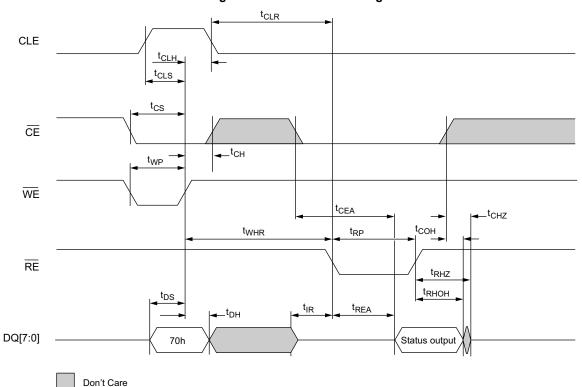

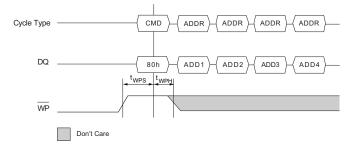

#### Figure 3. Command Latch Cycle

Don't Care

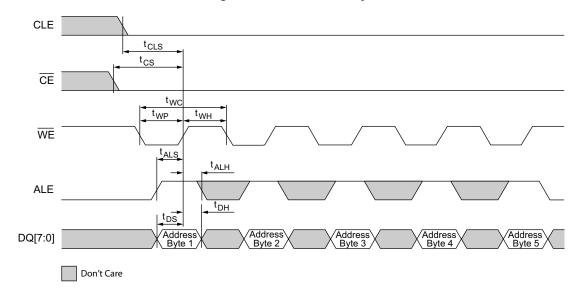

#### nvSRAM Address Input

During the nvSRAM address cycle, the host transmits the five consecutive address bytes through DQ[7:0] to the address register on every rising edge of WE toggle when CE is LOW, ALE is HIGH, CLE is LOW, and RE is HIGH. In five-byte addressing, the least significant address byte is sent in the first address cycle and the most significant address byte is sent in the fifth address cycle. nvSRAM requires only the first three address bytes to

address its entire 16-Mbit memory. Therefore, the two extra address bytes in the five-byte address are don't care bytes. All unused address bits, including the don't care bits, should be set to '0' by the host controller. The address cycle is ignored by the nvSRAM during the busy (RDY bit is set to '0' in the status register) period. Refer to Table 2 on page 9 for nvSRAM addressing.

#### Figure 4. Address Latch Cycle

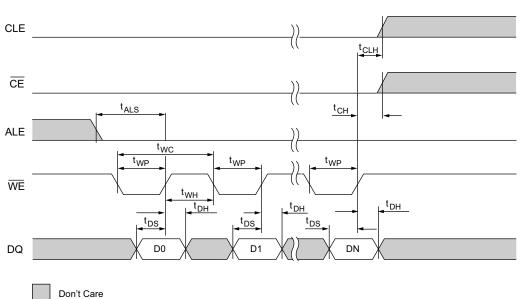

#### nvSRAM Data Input

Data is written from DQ (DQ[7:0] or DQ[15:0]) to the data register of the nvSRAM on the rising edge of  $\overline{WE}$  when  $\overline{CE}$  is LOW, ALE is LOW, CLE is LOW, and  $\overline{RE}$  is HIGH. Data inputs are ignored by the nvSRAM during device busy (RDY bit is set to '0' in the status register) state.

#### Figure 5. Data Input Cycle

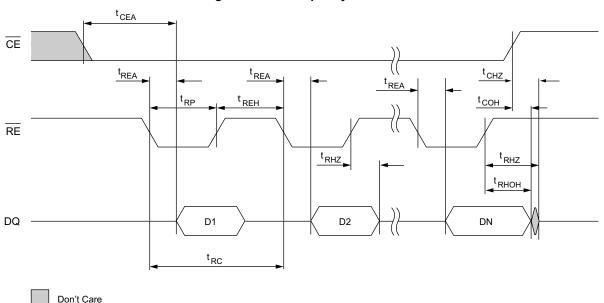

#### nvSRAM Data Output

Data is sent out (during read) on the DQ bus (DQ[7:0] or DQ[15:0]) by the nvSRAM if it is in the ready status. Data is output from the data register on every falling edge of  $\overline{RE}$  when  $\overline{CE}$  is LOW, ALE is LOW, CLE is LOW, and  $\overline{WE}$  is HIGH. nvSRAM ignores the read request if it is busy (RDY bit is set to '0' in the status register) during a STORE cycle.

#### Figure 6. Data Output Cycles

#### Table 2. nvSRAM Addressing

| Address Cycle | DQ7                       | DQ6 | DQ5 | DQ4                    | DQ3                 | DQ2 | DQ1 | DQ0 |  |  |

|---------------|---------------------------|-----|-----|------------------------|---------------------|-----|-----|-----|--|--|

| First         | A7                        | A6  | A5  | A4                     | A3                  | A2  | A1  | A0  |  |  |

| Second        | A15                       | A14 | A13 | A12                    | A11                 | A10 | A9  | A8  |  |  |

| Third         | Don't care <sup>[3]</sup> |     |     | A20/LOW <sup>[2]</sup> | A19                 | A18 | A17 | A16 |  |  |

| Fourth        | Don't care <sup>[3]</sup> |     |     |                        |                     |     |     |     |  |  |

| Fifth         |                           |     |     | Don't d                | care <sup>[3]</sup> |     |     |     |  |  |

#### **Command Definition**

The nvSRAM has address, command, and data multiplexed on its I/Os. All commands and addresses are written through the DQ bus DQ[7:0] by toggling  $\overline{WE}$  to LOW while  $\overline{CE}$  and CLE are LOW and ALE is HIGH for the address cycle and  $\overline{CE}$  and ALE are LOW and CLE is HIGH for the command cycle. The status of all the

input pins are latched on the rising edge of  $\overline{\text{WE}}$  after which the device determines whether the bus cycle is a command cycle, address cycle, data input cycle, or data output cycle. All the asynchronous NAND interface nvSRAM commands are listed in Table 3.

#### Table 3. nvSRAM Commands Table

| nvSRAM Function        | First Cycle | Second Cycle       | Description                                                                                                                                                                                               |

|------------------------|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read ID                | 90h         |                    | Identifies that the target supports the ONFI specification. If the target supports the ONFI specification, then the ONFI signature is returned.                                                           |

| Read Parameter<br>Page | ECh         |                    | The read parameter page function retrieves the data structure that describes the target's organization, features, timings and other behavioral parameters.                                                |

| Read Status            | 70h         |                    | Retrieves a status value for the last operation issued.                                                                                                                                                   |

| Read                   | 00h         | 30h                | The read function reads from the nvSRAM array location specified by the address bytes.                                                                                                                    |

| Write                  | 80h         | 10h <sup>[4]</sup> | Data is written to the SRAM array of nvSRAM. 10h is an optional command cycle for the nvSRAM write operation and a successful write will execute even without the host issuing this command.              |

| Reset                  | FFh         |                    | Aborts the current operation (all writes and reads) and puts the nvSRAM in its power-up state. If an NV operation is in progress, it will be completed first and then the reset request will be serviced. |

| Software RECALL        | FCh         |                    | Software RECALL                                                                                                                                                                                           |

| Software STORE         | 84h         | A5h                | Software STORE                                                                                                                                                                                            |

| AutoStore Disable      | A3h         |                    | Disables the AutoStore                                                                                                                                                                                    |

| AutoStore Enable       | ACh         |                    | Enables the AutoStore                                                                                                                                                                                     |

| Reserved               | EEh         |                    | Reserved                                                                                                                                                                                                  |

| Reserved               | EFh         |                    | Reserved                                                                                                                                                                                                  |

- Notes

- 2. A20 address bit should be set to LOW for the  $\times 16$  configuration.

- 3. Although these address bits are 'don't care', Cypress recommends that these bits are treated as 0s.

4. The 10h command at the end of the write cycle is optional and used only for flash compatibility.

### **Basic Operations**

The following sections describe the nvSRAM commands.

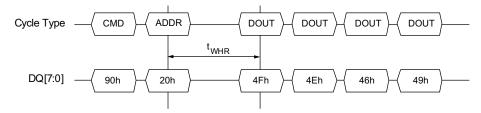

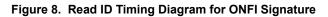

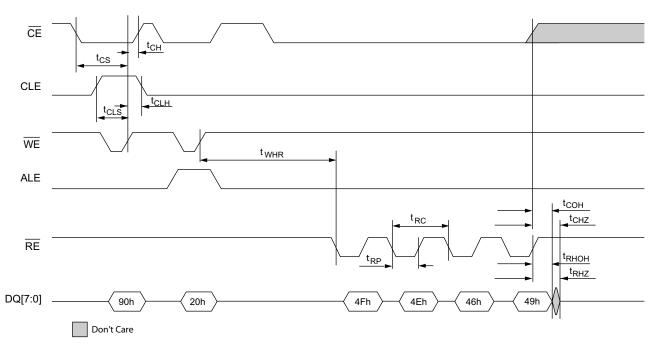

#### Read ID (90h) Definition

The read ID function identifies that the device supports the ONFI specification. If the nvSRAM supports the ONFI specification, the ONFI signature shall be returned. The ONFI signature is the ASCII encoding of 'ONFI' where 'O' = 4Fh, 'N' = 4Eh, 'F' = 46h, and 'I' = 49h. Reading beyond four bytes will yield indeterminate values. Figure 7 and Figure 8 define the read ID behavior and timings.

For the read ID command, only the addresses of 00h and 20h are valid. Any other addresses, except 00h and 20h, following the read ID command (90h) will return invalid data to the host. To retrieve the ONFI signature, an address of 20h shall be entered.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

#### Figure 7. Read ID Operation Diagram for ONFI Signature

The read ID function can also be used to determine the JEDEC manufacturer ID and the device ID for the particular NAND part by specifying an address of 00h. Figure 9 defines the read ID behavior and timings for retrieving the device ID. Reading beyond the first two bytes yields undetermined value.

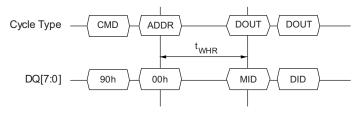

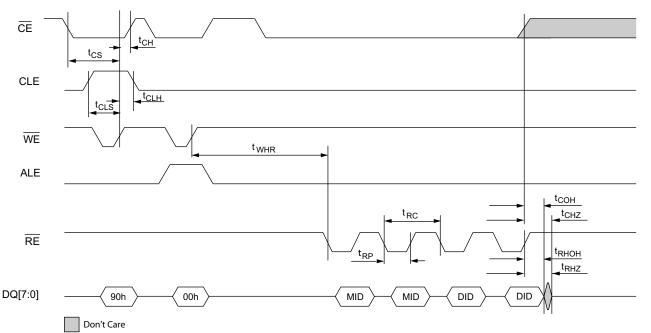

#### Figure 9. Read ID Operation Diagram for Manufacturer ID

Figure 10. Read ID Timing Diagram for Manufacturer ID

MID is a 2-byte code consisting of the assigned manufacturer ID. MID registers are set in factory and are read-only registers for the user. This is the JEDEC-assigned manufacturer ID for Cypress. JEDEC assigns the manufacturer ID in different banks. The first eight bits represents the bank in which the ID is assigned. The next eight bits represent the manufacturer ID. The Cypress manufacturer ID is 34h in bank 0. Therefore, the manufacturer ID for all Cypress NAND interface nvSRAM products is: DID is a 2-byte code consisting of the device ID for the part, assigned by Cypress. The device ID is 22h, 00h for the ×8 part and 22h, 40h for the ×16 part.

DID (×8): 0010\_0010\_0000\_0000 DID (×16): 0010\_0010\_0100\_0000

MID: 0000 0000 0011 0100

#### **Read Parameter Page (ECh)**

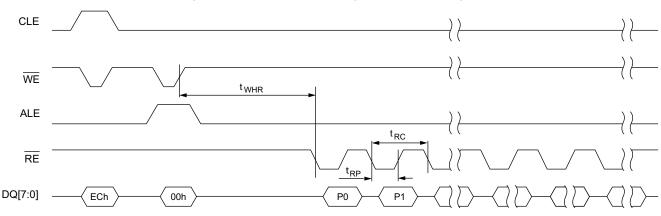

The read parameter page command (ECh) retrieves the data structure that describes the target's organization, features, timings, and other behavioral parameters. Figure 11 defines the read parameter page command. This command is accepted by the target only when the nvSRAM is idle. Writing ECh to the command register puts the target in the Read Parameter Page mode. The device stays in this mode until another valid command is issued.

When the ECh command is sent, followed by the 00h address cycle, the host should wait for at least  $t_{WHR}$  time before reading

the parameter page byte. The nvSRAM starts sending parameter bytes for every RE toggle.

The read parameter page (ECh) output data can be used by the host to configure its internal settings for properly using the nvSRAM device. The parameter page data is static for every part. However, the value can be changed through the product cycle of the device. The host should interpret the data and configure itself accordingly.

#### Figure 11. Read Parameter Page command timing

#### Parameter Page Data Structure Definition

Table 4 defines the parameter page data structure of nvSRAM. The parameter page spans into multiple bytes and the least significant byte of the parameter corresponds to the first byte in the parameter page data structure. Values are reported in the parameter page in units of bytes. For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

| Table 4. | Parameter | Page | Data | Structure | Definition |

|----------|-----------|------|------|-----------|------------|

|----------|-----------|------|------|-----------|------------|

| Byte | Parameter Description <sup>[5]</sup> | Value: (For SDR | Timing Mode - 3) | Value: (For SDR Timing Mode - 2) |          |  |

|------|--------------------------------------|-----------------|------------------|----------------------------------|----------|--|

| Dyte | Falameter Description-               | ×8              | ×16              | ×8                               | ×16      |  |

| 0–3  | Parameter page signature             |                 |                  |                                  |          |  |

|      | Byte 0: 4Fh, "O"                     | 4Fh             | 4Fh              | 4Fh                              | 4Fh      |  |

|      | Byte 1: 4Eh, "N"                     | 4Eh             | 4Eh              | 4Eh                              | 4Eh      |  |

|      | Byte 2: 46h, "F"                     | 46h             | 46h              | 46h                              | 46h      |  |

|      | Byte 3: 49h, "I"                     | 49h             | 49h              | 49h                              | 49h      |  |

| 4–5  | Revision number                      | 00h, 02h        | 00h, 02h         | 00h, 02h                         | 00h, 02h |  |

|      | Bits 15–2: Reserved (0)              |                 |                  |                                  |          |  |

|      | Bit 1: Supports ONFI version 1.0     |                 |                  |                                  |          |  |

|      | Bit 0: Reserved (0)                  |                 |                  |                                  |          |  |

| Table 4 | Parameter Page    | Data Structure | Definition | (continued) |   |

|---------|-------------------|----------------|------------|-------------|---|

|         | i urunicici i ugu |                | Deminion   | (continucu) | 1 |

| Durte   | Parameter Description <sup>[5]</sup>                                                        | Value: (For SDR | Timing Mode - 3) | Value: (For SDR Timing Mode - 2) |          |  |  |

|---------|---------------------------------------------------------------------------------------------|-----------------|------------------|----------------------------------|----------|--|--|

| Byte    | Parameter Description <sup>44</sup>                                                         | ×8              | ×16              | ×8                               | ×16      |  |  |

| 6–7     | Feature Supported                                                                           | 00h, 00h        | 00h, 01h         | 00h, 00h                         | 00h, 01h |  |  |

|         | Bits 15–1: Reserved (0)                                                                     |                 |                  |                                  |          |  |  |

|         | Bit 0: When set to '1', supports 16-bit data bus width                                      | _               |                  |                                  |          |  |  |

| 8–9     | Optional Command supported                                                                  | 00h, 00h        | 00h, 00h         | 00h, 00h                         | 00h, 00h |  |  |

|         | Bits 15–3: Reserved (0)                                                                     |                 |                  |                                  |          |  |  |

|         | Bit 2: Supports Get Feature and Set Feature                                                 |                 |                  |                                  |          |  |  |

|         | Bit 1–0: Reserved (0)                                                                       |                 |                  |                                  |          |  |  |

| 10–31   | Reserved (0)                                                                                | All bytes 00h   |                  |                                  |          |  |  |

| 32–43   | Device manufacturer (12 ASCII characters)                                                   | All bytes 00h   |                  |                                  |          |  |  |

| 44–63   | Device model (20 ASCII characters)                                                          | All bytes 00h   |                  |                                  |          |  |  |

| 64      | JEDEC manufacturer ID                                                                       | 34h             | 34h              | 34h                              | 34h      |  |  |

| 65–66   | Date Code (Optional)                                                                        | All bytes 00h   |                  |                                  |          |  |  |

| 67–79   | Reserved (0)                                                                                | All bytes 00h   |                  |                                  |          |  |  |

| 80–100  | Unused (0)                                                                                  |                 | All byt          | es 00h                           |          |  |  |

| 101     | Number of address cycles<br>Bits 7–4: Column address cycles<br>Bits 3–0: Row address cycles | 32h             | 32h              | 32h                              | 32h      |  |  |

| 102–127 | Unused (0)                                                                                  |                 | All byt          | es 00h                           |          |  |  |

| 128     | I/O pin capacitance                                                                         | 08h             | 08h              | 08h                              | 08h      |  |  |

| 129–130 | Timing mode support                                                                         | 00h, 08h        | 00h, 08h         | 00h, 04h                         | 00h, 04h |  |  |

|         | Bits 15–4: Reserved (0)                                                                     |                 |                  |                                  |          |  |  |

|         | Bit 3: When set to '1', supports timing mode 3                                              |                 |                  |                                  |          |  |  |

|         | Bit 2: When set to '1', supports timing mode 2                                              |                 |                  |                                  |          |  |  |

|         | Bits 1–0: Reserved(0)                                                                       |                 |                  |                                  |          |  |  |

| 131–140 | Unused (0)                                                                                  | All bytes 00h   |                  |                                  |          |  |  |

| 141–163 | Reserved (0)                                                                                |                 | All byt          | es 00h                           |          |  |  |

| 164–253 | Unused (0)                                                                                  | All bytes 00h   |                  |                                  |          |  |  |

| 254–255 | Integrity CRC                                                                               |                 | All byt          | es 00h                           |          |  |  |

| 256–768 | Reserved (0)                                                                                |                 | All byt          | es 00h                           |          |  |  |

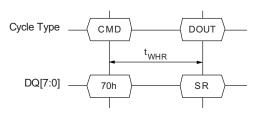

#### Read Status (70h) Definition

The read status command retrieves a status value for the last operation issued. See Table 5 on page 15 (Status field definition) for status register bit definitions. Figure 12 and Figure 13 define the read status behavior and timings. SR: Status register bits are defined in Table 6 on page 15.

#### Figure 12. Read Status Operation

Figure 13. Read Status Timing

#### Status Field Definition

The read status register command returns the status register byte value (SR). If the RDY bit is cleared to zero, all other bits in the status byte (except WP) are invalid and shall be ignored by the host. The RDY bit can be polled to check the ready or busy status while a nvSRAM STORE or Software RECALL cycle is in progress.

#### Table 5. Status Field Definition

| SR bit          | 7  | 6   | 5     | 4     | 3     | 2     | 1     | 0    |

|-----------------|----|-----|-------|-------|-------|-------|-------|------|

| Status Register | WP | RDY | X (0) | X (0) | X (0) | R (0) | X (0) | FAIL |

#### Table 6. Status Register Bit Definition

| SR Bit | SR Bit Definition | SR Bit Description                                                                                                                                                                                                                                                                                                                                                             |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0  | FAIL              | This shows the status of the last executed command by the nvSRAM. The FAIL bit is set to<br>'1' if the last command did not execute successfully. The nvSRAM sets the FAIL bit when the<br>last command sent by the host did not get registered properly, or the command did not receive<br>the associated address bytes, or an invalid command was sent by the host.          |

| Bit 1  | Don't care        | Reading this bit always returns a '0'.                                                                                                                                                                                                                                                                                                                                         |

| Bit 2  | Reserved          | Reading this bit always returns a '0'.                                                                                                                                                                                                                                                                                                                                         |

| Bit 3  | Don't care        | Reading this bit always returns a '0'.                                                                                                                                                                                                                                                                                                                                         |

| Bit 4  | Don't care        | Reading this bit always returns a '0'.                                                                                                                                                                                                                                                                                                                                         |

| Bit 5  | Don't care        | Reading this bit always returns a '0'.                                                                                                                                                                                                                                                                                                                                         |

| Bit 6  | RDY               | If set to '1', the nvSRAM is ready for another command and all other bits in the status value are valid. If cleared to '0', the last command issued is not yet complete and the SR bits 5:0 are invalid and shall be ignored by the host. This bit impacts the value of R/B accordingly. This bit is set to '0' by the device while a STORE or Software RECALL is in progress. |

| Bit 7  | WP                | If set to '1', the device is not write protected. If cleared to '0', the device is protected from writing. This bit shall always be valid regardless of the state of the RDY bit.                                                                                                                                                                                              |

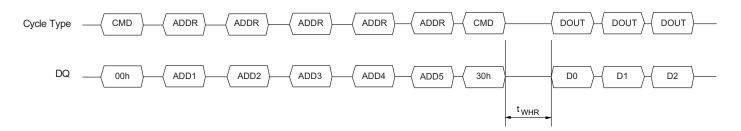

#### nvSRAM Burst Mode Read (00h, 30h)

The nvSRAM enters the Read mode when the host controller sends a 00h command, followed by five Address bytes, and the 30h second command cycle. After the read command is registered, the nvSRAM starts sending data out on its DQ bus after  $t_{REA}$  time from the falling edge of the  $\overline{RE}$  control signal on every  $\overline{RE}$  toggling. The nvSRAM allows reading in the Burst mode, where the host can continue reading the data from the device by repeatedly pulsing  $\overline{RE}$  at the maximum  $t_{RC}$  rate. The host controller can read the entire memory by initiating a single

read request. In the burst mode read, the internal address counter of the nvSRAM automatically increments to the next addressable location and the device continues sending data on its DQ bus. After the internal address counter reaches the last addressable memory location, the counter rolls over to the start address and continues sending data bytes. The device stays in the Read mode until the read is interrupted by another valid command. Refer to Figure 14 for the data output cycle timing.

Figure 14. Read Timing

#### nvSRAM Burst Write (80h, 10h)

The nvSRAM enters the Write mode when the host controller sends an 80h command, followed by five Address bytes, and data bytes to be written. After the write command is initiated, subsequent data bytes are written to the nvSRAM on every WE toggle. The Write mode terminates when the host sends a 10h command at the end of a write data cycle. The nvSRAM supports the burst mode write operation, in which the host initiates the Write command, once at the beginning of the write cycle, and continues sending data bytes to be written by pulsing the WE. The host should maintain the minimum write pulse width (t<sub>WP</sub>) of WE, and setup (t<sub>CS</sub>) and hold (t<sub>CH</sub>) criteria for the  $\overline{CE}$  signal.

When the burst mode write is in progress, the internal address counter of the nvSRAM advances automatically after every data word write. After the internal address counter reaches the last addressable memory location, the address counter rolls over to the starting address and continues writing data from the starting address location by overwriting the previously written data.

**Note** Command 10h is an optional command for the nvSRAM write operation and a successful write executes without the host issuing this command. If the host executes the 10h command when the write operation is in progress, the ongoing Write mode is terminated.

Refer to Figure 15 for the data input cycle timing.

Figure 15. Write Timing

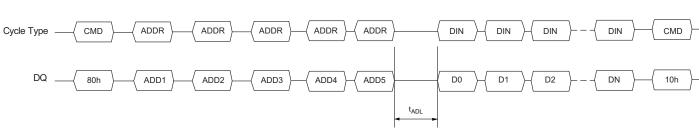

# Reset (FFh) Definition

The Reset function puts the nvSRAM in its power-up state. The reset command can be executed when the device is in any state, except when a power-up RECALL operation is in progress. When the power-up RECALL operation is in progress, the reset command is not issued and the host must wait for R/B to become HIGH after the device is ready. Figure 16 defines the Reset behavior and timings.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

Note If the Reset (FFh) command is issued when any NV operation is in progress, then the reset request is executed only

after the ongoing NV operation is completed. Depending upon the present state of the device, the t<sub>RST</sub> timing varies based on the following:

- If the reset command is executed when the device is ready, it takes t<sub>SS</sub> time to process the reset request.

- If the reset command is issued when the software RECALL cycle is in progress, it takes t<sub>RECALL</sub> time to process the reset request.

- If the reset command is issued when a software or HSB STORE cycle is in progress, it takes t<sub>STORE</sub> time to process the reset request.

#### Figure 16. Reset Timing Diagram

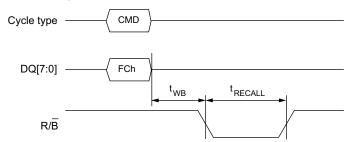

#### nvSRAM Software RECALL (FCh)

The software RECALL initiates a software RECALL operation in the nvSRAM. The command may be executed any time when the device is in the ready status. Figure 17 defines the nvSRAM Software RECALL behavior and timings. After the software RECALL command is registered by the nvSRAM, it takes  $t_{SS}$  time to process the software command before initiating the Software RECALL operation internally. All accesses to the

nvSRAM, except reset (FFh) and read status (70h), are inhibited during  $t_{RECALL}$  time. During the RECALL operation, the nvSRAM sets the RDY bit of the status register to '0' and pulls the R/ $\overline{B}$  pin to LOW for  $t_{RECALL}$  duration. After the RECALL completes, the RDY bit is set to '1' and R/ $\overline{B}$  is pulled to HIGH by an external pull-up resistor indicating the ready status.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

#### Figure 17. nvSRAM Software RECALL

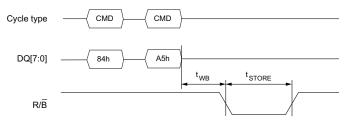

#### Software STORE (84h, A5h) in nvSRAM

Sending a software STORE command initiates a software STORE operation within the nvSRAM, regardless of whether there was an SRAM write or not. After the software STORE command is registered, the device takes  $t_{STORE}$  time to complete the STORE operation. All accesses to the nvSRAM, except Reset (FFh) and read status (70h), are inhibited during the STORE operation. After you initiate the STORE cycle, the nvSRAM pulls the R/B pin LOW for  $t_{STORE}$  duration. The RDY bit of the status register SR[6] transitions from '1' to '0' and remains at '0' until the STORE cycle is completed. Figure 18 defines the Software STORE behavior and timing. After the software STORE command is initiated, it pulls the R/B signal LOW for  $t_{STORE}$  time and all accesses, including FFh reset to the nvSRAM, are disabled.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

#### Figure 18. Software STORE Timing

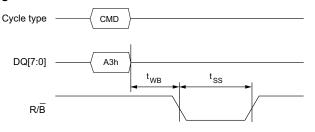

#### nvSRAM AutoStore Disable (A3h)

The AutoStore disable command (A3h) disables the nvSRAM AutoStore. All accesses to the nvSRAM, except Reset (FFh) and read status (70h), are inhibited during  $t_{SS}$  time. When the AutoStore Enable command is executing, the device pulls  $R/\overline{B}$

LOW for  $t_{SS}$  time. Because this setting is volatile, you must perform a manual software STORE operation if this is desired to survive subsequent power cycles. The command may be executed any time when the device is in the ready status. Figure 19 defines the nvSRAM AutoStore disable timing.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

#### Figure 19. nvSRAM AutoStore Disable

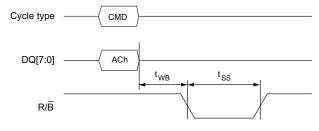

#### nvSRAM AutoStore Enable (ACh)

The AutoStore enable command (ACh) enables the nvSRAM AutoStore. All accesses to the nvSRAM, except reset (FFh) and read status (70h), are inhibited during  $t_{SS}$  time. When the AutoStore Enable command is executing, the device pulls R/B LOW for  $t_{SS}$  time. Because this setting is volatile, you must perform a manual software STORE operation if this is desired to survive subsequent power cycles. The command may be executed any time when the device is in the ready status. Figure 20 defines the nvSRAM AutoStore enable timing.

For a device that supports 16-bit data access, the upper 8 bits DQ[15:8] are not used and are "Don't Care" bits.

#### Figure 20. nvSRAM AutoStore Enable

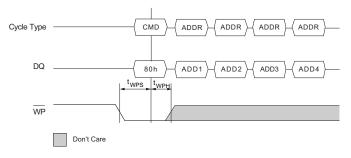

#### Write Protect

The write protect feature disables the write operation in the nvSRAM. When the WP pin is pulled LOW externally by the host before initiating the write command (80h), the nvSRAM clears the WP (SR[7]) status in the status register and disables the write into the SRAM memory. However, writing into the status register is not protected. The status of the write protect pin is latched by the device along with the write command (80h) on the rising edge of the WE signal. After the write protect status is latched, it is locked for the current write cycle. After modifying the value of the WP, the host shall not issue a new command to the device for at least  $t_{WW}$  time. The host must not toggle the WP pin during a command cycle. Figure 21 describes the tww timing requirement, which shows the start of an nvSRAM write command after toggling the  $\overline{WP}$ . The transition of the  $\overline{WP}$  signal is asynchronous. The bus shall be idle for t<sub>WW</sub> time after every WP transition from LOW to HIGH or HIGH to LOW before a new command is issued by the host.

#### Figure 21. Write Protect Disable Timing

#### Figure 22. Write Protect Enable Timing

#### **nvSRAM Store Operations**

The nvSRAM stores data in the nonvolatile memory cell using one of the three store operations. These three operations are: AutoStore, automatically triggered on device power-down; Hardware STORE, activated by the HSB; and Software STORE activated by issuing a software command.

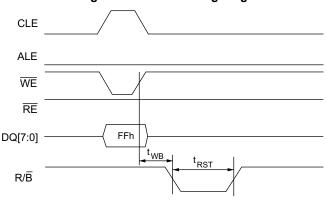

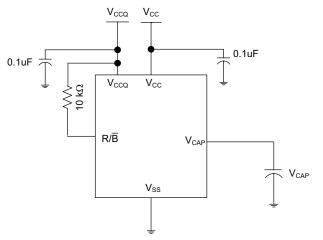

#### AutoStore Operation

The AutoStore operation is a unique feature of the SONOS technology and is enabled by default on the device. During normal operation, the device draws current from V<sub>CC</sub> to charge a capacitor connected to the V<sub>CAP</sub> pin. This stored charge is used by the chip to perform a STORE operation during power-down. If the voltage on the V<sub>CC</sub> pin drops below V<sub>SWITCH</sub>, the part automatically disconnects the V<sub>CAP</sub> pin from V<sub>CC</sub> and a STORE operation is initiated with power provided by the V<sub>CAP</sub> capacitor.

**Note** If the capacitor is not connected to the V<sub>CAP</sub> pin, disable AutoStore using the AutoStore disable command (A3h). If AutoStore is enabled without a capacitor on the V<sub>CAP</sub> pin, the device attempts an AutoStore operation without sufficient charge to complete the STORE. This corrupts the nvSRAM data.

#### Figure 23. AutoStore Mode

Figure 23 shows the proper connection of the storage capacitor (V<sub>CAP</sub>) for automatic STORE operation. Refer to DC Electrical Characteristics on page 20 for the size of the V<sub>CAP</sub>. The voltage on the V<sub>CAP</sub> pin is driven to V<sub>VCAP</sub> by a regulator on the chip. A pull-up resistor should be placed on R/B to hold it inactive during power-up. This pull-up resistor is only effective if the R/B signal is tristate during power-up. When the nvSRAM comes out of power-up RECALL, the host microcontroller must be active or the R/B held inactive until the host microcontroller comes out of reset. To reduce unnecessary nonvolatile STOREs, AutoStore and Hardware STORE operations are ignored unless at least one write operation has taken place since the most recent STORE or RECALL cycle.

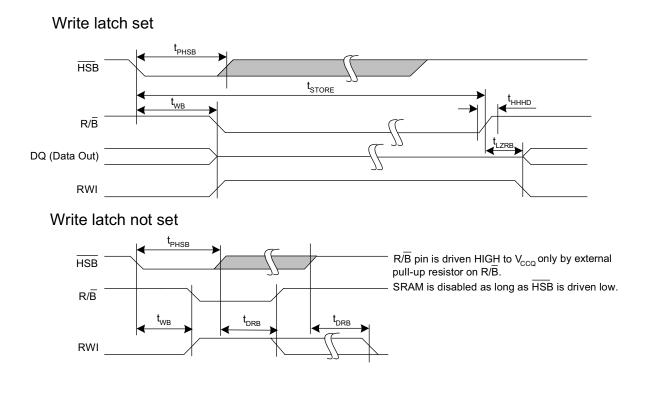

### Hardware STORE (HSB) Operation

The device provides the  $\overline{\text{HSB}}$  pin to control the Hardware STORE operation. The HSB pin is used to request a Hardware STORE cycle. When the HSB pin is driven LOW, the device conditionally initiates a STORE operation after t<sub>DELAY</sub>. An actual STORE cycle begins only if a write to the SRAM has taken place since the last STORE or RECALL cycle. SRAM write operations that are in progress when HSB is driven LOW by any means are given time (t<sub>DELAY</sub>) to complete before the STORE operation is initiated. However, any SRAM write cycles requested after HSB goes LOW are inhibited until R/B returns HIGH. R/B remains LOW by the device as long as HSB is LOW. Any SRAM read and write cycles are inhibited until HSB is returned HIGH by host microcontroller or any other external source. The HSB pin must be set to HIGH during the normal device operation. If HSB is not used in application, this pin should be pulled HIGH using an external pull-up resistor of value between 4.7 k $\Omega$  and 10 k $\Omega$ .

#### **Software Store Operation**

The software store operation is initiated by sending a Software STORE command (84h, A5h). The nvSRAM initiates a STORE cycle irrespective of whether the write latch is set or not. Refer to Software STORE (84h, A5h) in nvSRAM on page 17 for further details.

### **nvSRAM RECALL Operations**

The nvSRAM recalls data from the nonvolatile memory cell using one of the two recall operations. These two recall operations are: Hardware Recall, activated automatically by the device during a power cycle or brown out, and a software initiated RECALL cycle.

#### Hardware RECALL (Power Up)

During power-up or after any low-power condition ( $V_{CC} < V_{SWITCH}$ ), an internal RECALL request is latched. When  $V_{CC}$  again exceeds the  $V_{SWITCH}$  on power-up, a RECALL cycle is automatically initiated and takes  $t_{HRECALL}$  to complete. During this time, the R/B pin is driven LOW by the nvSRAM and all reads and writes to nvSRAM inhibited.

#### Software Recall

The software recall operation is initiated by sending a Software RECALL command (FCh). The nvSRAM initiates a RECALL cycle and overwrites the SRAM data with the recalled data from the nonvolatile cell. Refer to the nvSRAM Software RECALL (FCh) on page 17 for further details.

### **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

| Storage temperature65 °C to +150 °C                                      |

|--------------------------------------------------------------------------|

| Maximum accumulated storage time                                         |

| At 150 °C ambient temperature 1000h                                      |

| At 85 °C ambient temperature 20 Years                                    |

| Maximum Junction temperature 150 °C                                      |

| Supply voltage on $V_{CC}$ relative to $V_{SS}$ –0.5 V to +4.1 V         |

| Supply voltage on $V_{CCQ}$ relative to $V_{SS}$ –0.5 V to +2.4 V        |

| DC voltage applied to outputs in HIGH Z State–0.5 V to $V_{CCQ}$ + 0.5 V |

| Input voltage–0.5 V to $V_{CCQ}$ + 0.5 V                                 |

| Transient voltage (< 20 ns) on any pin to ground potential–2.0 V to $V_{CCQ}$ + 2.0 V |

|---------------------------------------------------------------------------------------|

| Package power dissipation<br>capability (T <sub>A</sub> = 25 °C)1.0 W                 |

| Package Pb soldering<br>temperature (3 seconds)+260 °C                                |

| DC output current (1 output at a time, 1s duration) 20 mA                             |

| Static discharge voltage<br>(per MIL-STD-883, Method 3015) > 2001 V                   |

| Latch up current > 140 mA                                                             |

### **Operating Range**

| Range      | Ambient<br>Temperature (T <sub>A</sub> ) | V <sub>cc</sub> | V <sub>CCQ</sub> |

|------------|------------------------------------------|-----------------|------------------|

| Industrial | –40 °C to +85 °C                         | 2.7 V to 3.6 V  | 1.70 V to 1.95 V |

### **DC Electrical Characteristics**

| Parameter            | Description                                                                                      | Test Conditio                                                                   | ns                                                                                         | Min                    | <b>Typ</b> <sup>[6]</sup> | Max                    | Unit |

|----------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------|---------------------------|------------------------|------|

| V <sub>CC</sub>      | Core power supply                                                                                |                                                                                 |                                                                                            | 2.7                    | 3.0                       | 3.6                    | V    |

| V <sub>CCQ</sub>     | I/O power supply                                                                                 |                                                                                 |                                                                                            | 1.70                   | 1.80                      | 1.95                   | V    |

| I <sub>CC1</sub>     | Average V <sub>CC</sub> current                                                                  | t <sub>RC</sub> ≥ 30 ns                                                         |                                                                                            | -                      | -                         | 100                    | mA   |

| I <sub>CCQ1</sub>    | Average V <sub>CCQ</sub> current                                                                 | t <sub>RC</sub> <u>&gt;</u> 30 ns                                               | CY14V116F7                                                                                 | _                      | _                         | 30                     | mA   |

|                      |                                                                                                  | Values obtained without output loads (I <sub>OUT</sub> = 0 mA)                  | CY14V116G7                                                                                 | -                      | _                         | 60                     | mA   |

| I <sub>CC2</sub>     | Average V <sub>CC</sub> current during STORE                                                     | All inputs don't care, V <sub>CC</sub> =<br>Average current for duratio         | All inputs don't care, $V_{CC} = V_{CC}$ (Max)<br>Average current for duration $t_{STORE}$ |                        | -                         | 10                     | mA   |

| I <sub>CC3</sub>     | Average $V_{CC}$ current<br>$t_{RC} \ge 200 \text{ ns};$<br>$V_{CC} = V_{CC}(Typ), 25 ^{\circ}C$ | All inputs cycling at CMOS levels.                                              |                                                                                            | -                      | -                         | 50                     | mA   |

| I <sub>CCQ3</sub>    | Average V <sub>CCQ</sub> current                                                                 | All inputs cycling at CMOS                                                      | CY14V116F7                                                                                 | -                      | -                         | 15                     | mA   |

|                      | t <sub>RC</sub> ≥ 200 ns;<br>V <sub>CCQ</sub> = V <sub>CCQ</sub> (Typ), 25 °C                    | levels Values obtained                                                          | CY14V116G7                                                                                 | -                      | _                         | 30                     | mA   |

| I <sub>CC4</sub> [7] | Average V <sub>CAP</sub> current during AutoStore cycle                                          | All inputs don't care. Average current for duration t <sub>STORE</sub>          |                                                                                            | -                      | -                         | 6                      | mA   |

| I <sub>SB</sub>      | V <sub>CC</sub> standby current                                                                  | $\overline{\text{CE}} \ge (\text{V}_{\text{CCQ}} - 0.2 \text{ V}).$             |                                                                                            | -                      | _                         | 5                      | mA   |

| I <sub>SB1</sub>     | V <sub>CCQ</sub> standby current                                                                 | $V_{IN} \le 0.2 \text{ V or} \ge (V_{CCQ} - 0.2 \text{ V or})$                  | 2 V)                                                                                       | _                      | _                         | 2                      | mA   |

| I <sub>IX</sub>      | Input leakage current                                                                            | $V_{CCQ} = V_{CCQ}$ (Max), $V_{SS} \leq$                                        | V <sub>IN</sub> ≤ V <sub>CCQ</sub>                                                         | -1                     | _                         | +1                     | μA   |

| I <sub>OZ</sub>      | Output leakage current                                                                           | $V_{CCQ} = V_{CCQ}$ (Max), $V_{SS} \le V_{IN} \le V_{CCQ}$ ;<br>output disabled |                                                                                            | -1                     | -                         | +1                     | μA   |

| V <sub>IH</sub>      | Input HIGH voltage                                                                               |                                                                                 |                                                                                            | $0.8 \times V_{CCQ}$   | _                         | V <sub>CCQ</sub> + 0.3 | V    |

| V <sub>IL</sub>      | Input LOW voltage                                                                                |                                                                                 |                                                                                            | V <sub>SS</sub> – 0.3  | -                         | $0.2 \times V_{CCQ}$   | V    |

| V <sub>OH</sub>      | Output HIGH voltage                                                                              | I <sub>OH</sub> = -100 μA                                                       |                                                                                            | V <sub>CCQ</sub> – 0.1 | -                         | V <sub>CCQ</sub>       | V    |

Notes

6. Typical values are at 25 °C,  $V_{CC} = V_{CC}(Typ)$  and  $V_{CCQ} = V_{CCQ}(Typ)$ . Not 100% tested.

7. This parameter is only guaranteed by design and is not tested.

### DC Electrical Characteristics (continued)

#### Over the Operating Range

| Parameter                            | Description                                           | Test Conditions                         | Min  | <b>Typ</b> <sup>[6]</sup> | Max  | Unit |

|--------------------------------------|-------------------------------------------------------|-----------------------------------------|------|---------------------------|------|------|

| V <sub>OL</sub>                      | Output LOW voltage<br>(except R/B)                    | I <sub>OL</sub> = 100 μA                | -    | -                         | 0.1  | V    |

|                                      | O <u>ut</u> put LOW voltage (for<br>R/B)              | I <sub>OL</sub> = 3 mA                  | -    | -                         | 0.2  | V    |

| V <sub>CAP</sub> <sup>[8]</sup>      | -                                                     | Between $V_{CAP}$ pin and $V_{SS}$      | 19.8 | 22.0                      | 82.0 | μF   |

| V <sub>VCAP</sub> <sup>[9, 10]</sup> | Maximum voltage driven on $V_{CAP}$ pin by the device | V <sub>CC</sub> = V <sub>CC</sub> (Max) | -    | -                         | 5.0  | V    |

### **Data Retention and Endurance**

Over the Operating Range

| Parameter         | Description                  | Min       | Unit   |

|-------------------|------------------------------|-----------|--------|

| DATA <sub>R</sub> | Data retention               | 20        | Years  |

| NV <sub>C</sub>   | Nonvolatile STORE operations | 1,000,000 | Cycles |

### Capacitance

| Parameter <sup>[10]</sup> | Description                               | Test Conditions                                                                         | Max | Unit |

|---------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|-----|------|

| C <sub>IN</sub>           | Input capacitance on clock and input pins | $T_A = 25 \degree C, f = 1 \text{ MHz}, V_{CC} = V_{CC} (Typ), V_{CCQ} = V_{CCQ} (Typ)$ | 10  | pF   |

| C <sub>IO</sub>           | Input capacitance on data and I/O pins    |                                                                                         | 10  | pF   |

| C <sub>OTHER</sub>        | Capacitance on all other control pins     |                                                                                         | 10  | pF   |

### **Thermal Resistance**

| Parameter <sup>[10]</sup> | Description                                 | Test Conditions                                                                              | 165-ball FBGA | Unit |

|---------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------|---------------|------|

| $\Theta_{JA}$             | Thermal resistance<br>(junction to ambient) | Test conditions follow standard test methods and procedures for measuring thermal impedance, | 15.6          | °C/W |

| $\Theta_{JC}$             | Thermal resistance<br>(junction to case)    | according to EIA / JESD51.                                                                   | 2.9           | °C/W |

Notes

- 8. Min V<sub>CAP</sub> value guarantees that there is a sufficient charge available to complete a successful AutoStore operation. Max V<sub>CAP</sub> value guarantees that the capacitor on V<sub>CAP</sub> is charged to a minimum voltage during a Power-Up RECALL cycle so that an immediate power-down cycle can complete a successful AutoStore. Therefore, it is always recommended to use a capacitor within the specified min and max limits.

- Maximum voltage on V<sub>CAP</sub> pin (V<sub>VCAP</sub>) is provided for guidance when choosing the V<sub>CAP</sub> capacitor. The voltage rating of the V<sub>CAP</sub> capacitor across the operating temperature range should be higher than the V<sub>VCAP</sub> voltage.

- 10. These parameters are guaranteed by design and are not tested.

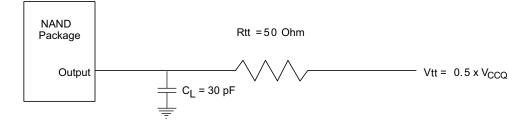

### **AC Test Conditions**

| Input pulse levels                       | V to V <sub>CCQ</sub> |

|------------------------------------------|-----------------------|

| Input rise and fall times (10% - 90%)    | 5 ns                  |

| Input and output timing reference levels | V <sub>CCQ</sub> /2   |

#### Figure 24. Driver Output Reference

### **AC Switching Characteristics**

#### **Timing Modes**

Over the Operating Range

|                                  | Description                                                  |     | Mode 2           |     | Mode 3           |      |

|----------------------------------|--------------------------------------------------------------|-----|------------------|-----|------------------|------|

| Parameter <sup>[11]</sup>        |                                                              |     | 35 ns            |     | 0 ns             | Unit |

|                                  |                                                              | Min | Max              | Min | Мах              |      |

| t <sub>ADL</sub>                 | Address cycle to data loading time                           | 100 | _                | 100 | -                | ns   |

| t <sub>ALH</sub>                 | ALE hold time                                                | 10  | _                | 5   | -                | ns   |

| t <sub>ALS</sub>                 | ALE setup time                                               | 15  | _                | 10  | _                | ns   |

| t <sub>AR</sub>                  | ALE to RE delay                                              | 10  | _                | 10  | _                | ns   |

| t <sub>CEA</sub>                 | CE access time                                               | _   | 30               | -   | 25               | ns   |

| t <sub>CH</sub>                  | CE hold time                                                 | 10  | _                | 5   | _                | ns   |

| t <sub>CHZ</sub> <sup>[12]</sup> | CE HIGH to output HIGH Z                                     | _   | 50               | -   | 50               | ns   |

| t <sub>CLH</sub>                 | CLE hold time                                                | 10  | _                | 5   | _                | ns   |

| t <sub>CLR</sub>                 | CLE to RE delay                                              | 10  | _                | 10  | _                | ns   |

| t <sub>CLS</sub>                 | CLE setup time                                               | 15  | -                | 10  | -                | ns   |

| t <sub>COH</sub>                 | CE HIGH to output hold                                       | 15  | _                | 15  | _                | ns   |

| t <sub>IR</sub>                  | Output HIGH Z to RE LOW                                      | 0   | -                | 0   | _                | ns   |

| t <sub>CS</sub>                  | CE setup time                                                | 25  | _                | 25  | _                | ns   |

| t <sub>DH</sub>                  | Data hold time                                               | 5   | -                | 5   | -                | ns   |

| t <sub>DS</sub>                  | Data setup time                                              | 15  | -                | 10  | _                | ns   |

| t <sub>RC</sub>                  | RE cycle time                                                | 35  | _                | 30  | _                | ns   |