# Low-Power SoC (System-on-Chip) with MCU, Memory, 2.4 GHz RF Transceiver, and USB Controller

### **Applications**

- 2400 2483.5 MHz ISM/SRD band systems

- Consumer electronics

- · Wireless keyboard and mouse

- Wireless voice-quality audio

- RF enabled remote controls

- · Wireless sports and leisure equipment

- Low power telemetry

- CC2511Fx: USB dongles

#### **Product Description**

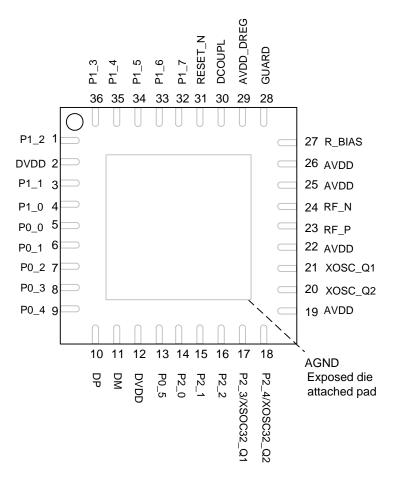

The *CC2510Fx/CC2511Fx* is a true low-cost 2.4 GHz system-on-chip (SoC) designed for low-power wireless applications. The *CC2510Fx/CC2511Fx* combines the excellent performance of the state-of-the-art RF transceiver *CC2500* with an industry-standard enhanced 8051 MCU, up to 32 kB of in-system programmable flash memory and 4 kB of RAM, and many other powerful features. The small 6x6 mm package makes it very suited for applications with size limitations.

The *CC2510Fx/CC2511Fx* is highly suited for systems where very low power consumption is required. This is ensured by several advanced low-power operating modes. The *CC2511Fx* adds a full-speed USB controller to the feature set of the *CC2510Fx*. Interfacing to a PC using the USB interface is quick and easy, and the high data rate (12 Mbps) of the USB interface avoids the bottlenecks of RS-232 or low-speed USB interfaces.

### **Key Features**

#### Radio

- High-performance RF transceiver based on the market-leading CC2500

- Excellent receiver selectivity and blocking performance

- High sensitivity (-103 dBm at 2.4 kBaud)

- o Programmable data rate up to 500 kBaud

- Programmable output power up to 1 dBm for all supported frequencies

- Frequency range: 2400 2483.5 MHz

- o Digital RSSI / LQI support

#### Current Consumption

- Low current consumption (RX: 17.1 mA @ 2.4 kBaud, TX: 16 mA @ -6 dBm output power)

- 0.3 µA in PM3 (the operating mode with the lowest power consumption)

#### MCU, Memory, and Peripherals

- High performance and low power 8051 microcontroller core.

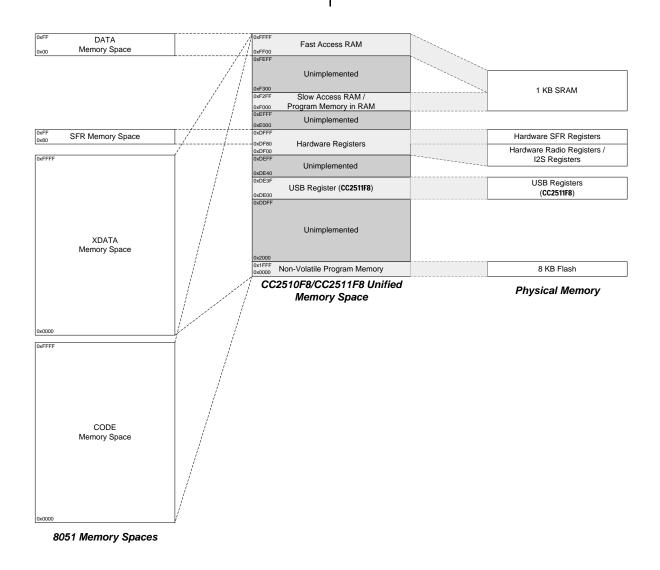

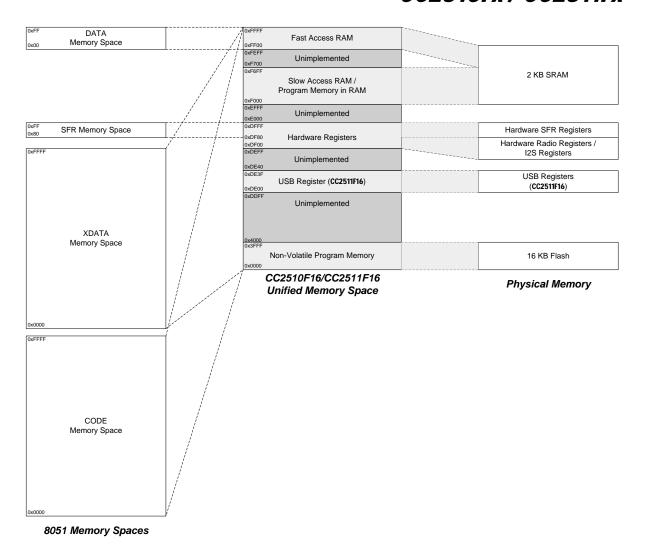

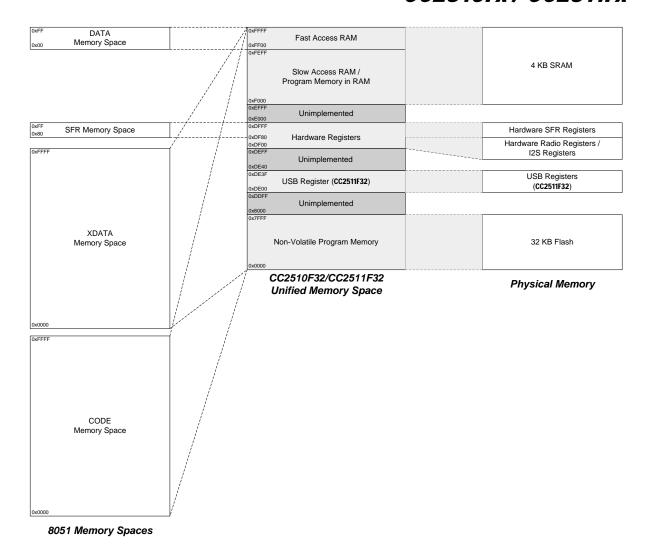

- 8/16/32 kB in-system programmable flash, and 1/2/4 kB RAM

- Full-Speed USB Controller with 1 kB USB FIFO (CC2511Fx)

- I<sup>2</sup>S interface

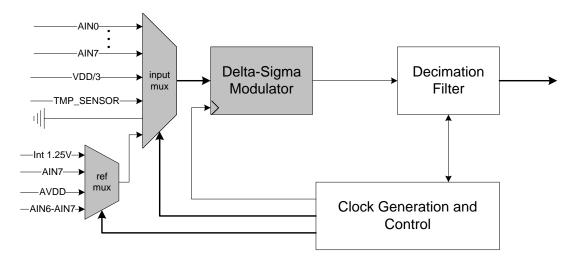

- o 7 12 bit ADC with up to eight inputs

- o 128-bit AES security coprocessor

- Powerful DMA functionality

- o Two USARTs

- o 16-bit timer with DSM mode

- o Three 8-bit timers

- Hardware debug support

- o 21 (*CC2510Fx*) or 19 (*CC2511Fx*) GPIO pins

#### General

- Wide supply voltage range (2.0V 3.6V)

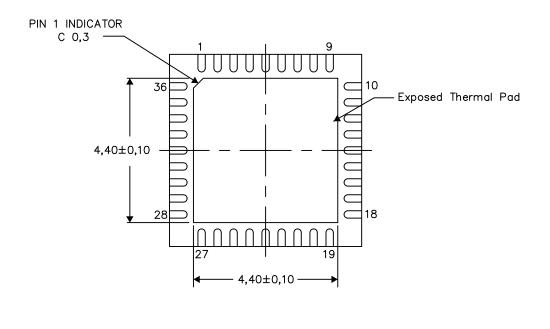

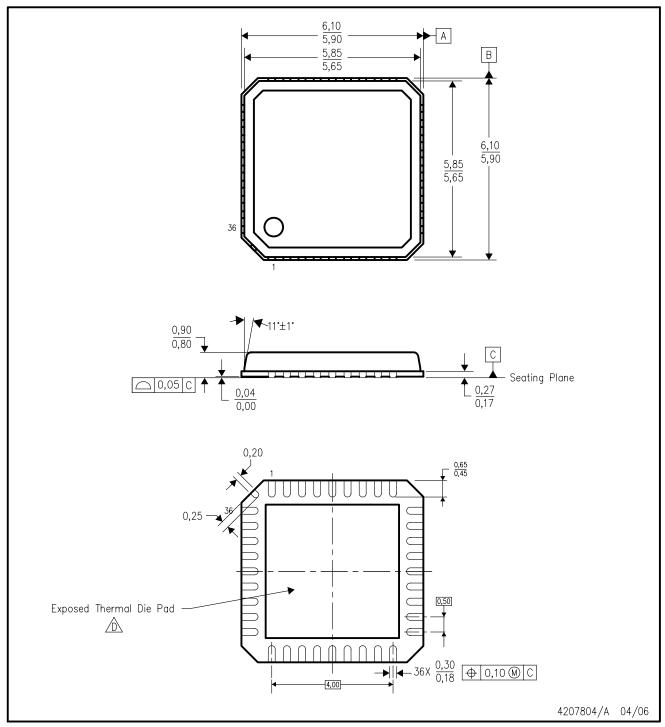

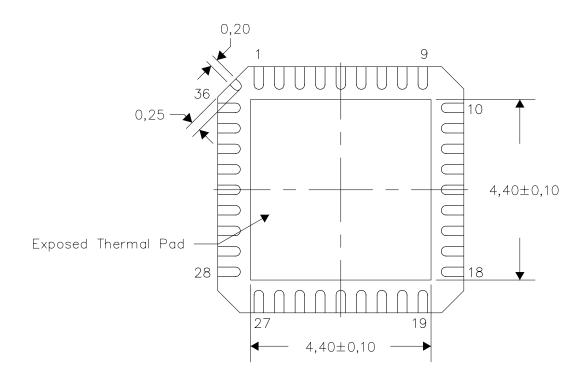

- Green package: RoHS compliant and no antimony or bromine, 6x6mm QFN 36

SWRS055G Page 1 of 236

### **Table of Contents**

| ABBI            | REVIATIONS                                                      |              |

|-----------------|-----------------------------------------------------------------|--------------|

| 1               | REGISTER CONVENTIONS                                            | 5            |

| 2               | KEY FEATURES (IN MORE DETAILS)                                  | 6            |

| 2.1             | HIGH-PERFORMANCE AND LOW-POWER 8051-COMPATIBLE MICROCONTROLLER  |              |

| 2.2             | 8/16/32 KB NON-VOLATILE PROGRAM MEMORY AND 1/2/4 KB DATA MEMORY | e            |

| 2.3             | FULL-SPEED USB CONTROLLER ( CC2511Fx)                           | <del>6</del> |

| 2.4             | I <sup>2</sup> S Interface                                      |              |

| 2.5             | HARDWARE AES ENCRYPTION/DECRYPTION                              |              |

| 2.6             | PERIPHERAL FEATURES                                             |              |

| 2.7             | Low Power                                                       |              |

| 2.8             | 2.4 GHz Radio with Baseband Modem                               | 7            |

| 3               | ABSOLUTE MAXIMUM RATINGS                                        | 8            |

| 4               | OPERATING CONDITIONS                                            |              |

| 4.1             | CC2510FX OPERATING CONDITIONS                                   |              |

| 4.2             | CC2511FX OPERATING CONDITIONS                                   | 9            |

| 5               | GENERAL CHARACTERISTICS                                         | 9            |

| 6               | ELECTRICAL SPECIFICATIONS                                       |              |

| 6.1             | CURRENT CONSUMPTION                                             |              |

| 6.2             | RF RECEIVE SECTION                                              |              |

| 6.3             | RF Transmit Section                                             |              |

| 6.4             | CRYSTAL OSCILLATORS                                             |              |

| 6.5             | 32.768 KHz Crystal Oscillator                                   | 17           |

| 6.6             | LOW POWER RC OSCILLATOR                                         |              |

| 6.7             | HIGH SPEED RC OSCILLATOR                                        |              |

| 6.8             | FREQUENCY SYNTHESIZER CHARACTERISTICS                           |              |

| 6.9             | ANALOG TEMPERATURE SENSOR                                       |              |

| 6.10            | 7 - 12 BIT ADC                                                  |              |

| 6.11            | CONTROL AC CHARACTERISTICS                                      |              |

| 6.12            | SPI AC CHARACTERISTICS                                          |              |

| 6.13<br>6.14    | DEBUG INTERFACE AC CHARACTERISTICS                              |              |

| 6.15            | TIMER INPUTS AC CHARACTERISTICS                                 |              |

| 6.16            | DC CHARACTERISTICS                                              |              |

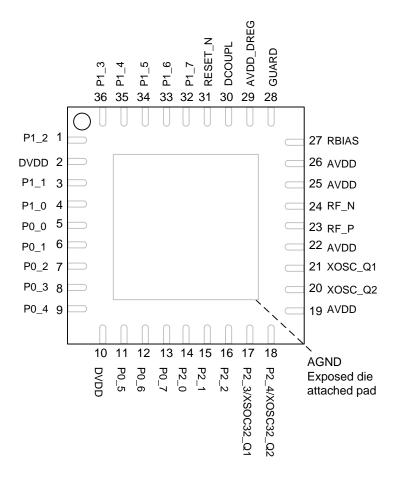

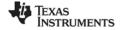

| 7               | PIN AND I/O PORT CONFIGURATION                                  |              |

|                 |                                                                 |              |

| 8               | CIRCUIT DESCRIPTION                                             |              |

| 8.1<br>8.2      | CPU AND PERIPHERALS                                             |              |

|                 |                                                                 |              |

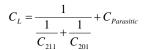

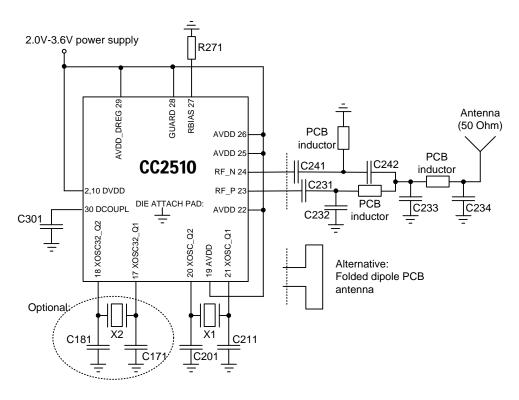

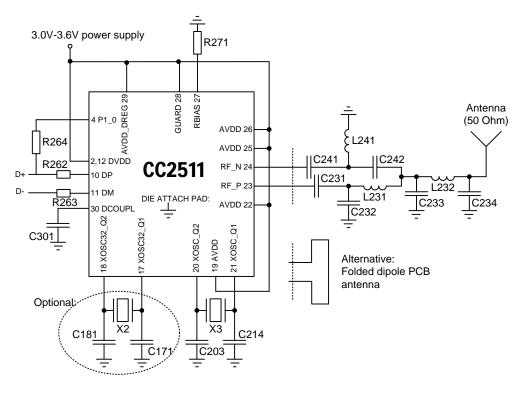

| 9               | APPLICATION CIRCUIT                                             |              |

| 9.1<br>9.2      | BIAS RESISTOR BALUN AND RF MATCHING                             |              |

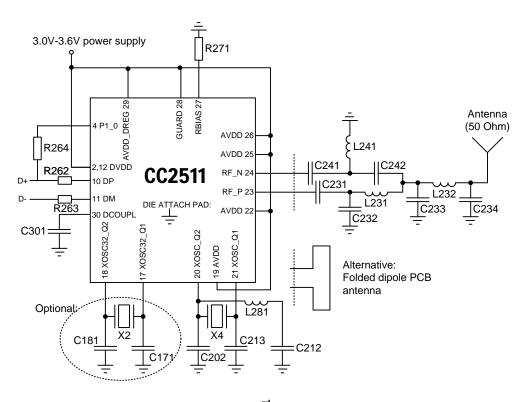

| 9.2             | CRYSTAL                                                         |              |

| 9.3<br>9.4      | REFERENCE SIGNAL                                                |              |

| 9. <del>5</del> | USB ( <i>CC2511Fx</i> )                                         |              |

| 9.6             | Power Supply Decoupling                                         |              |

| 9.7             | PCB LAYOUT RECOMMENDATIONS                                      |              |

| 10              | 8051 CPU                                                        |              |

| 10.1            | 8051 Introduction                                               |              |

| 10.1            | MEMORY                                                          |              |

| 10.2            | CPU REGISTERS                                                   |              |

| 10.4            | INSTRUCTION SET SUMMARY                                         |              |

| 10.5            | INTERRUPTS                                                      |              |

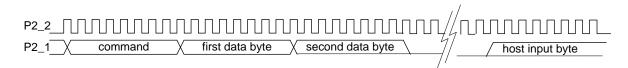

| 11              | DEBUG INTERFACE                                                 | 68           |

| 11.1            | DEBUG MODE                                                      |              |

| 11.2            | DEBUG COMMUNICATION                                             |              |

| 11.3            | DEBUG LOCK BIT                                                  | 68           |

| 11.4       | DEBUG COMMANDS                                          |     |

|------------|---------------------------------------------------------|-----|

| 12         | PERIPHERALS                                             | 73  |

| 12.1       | POWER MANAGEMENT AND CLOCKS                             | 73  |

| 12.2       | RESET                                                   | 80  |

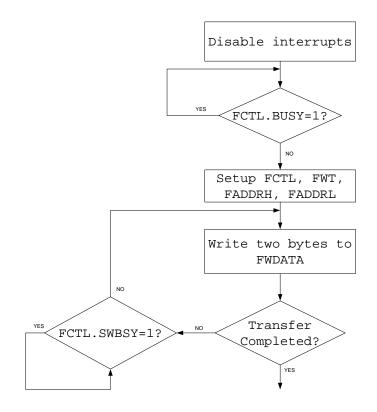

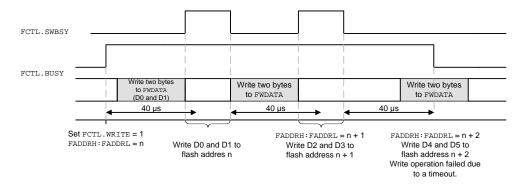

| 12.3       | FLASH CONTROLLER                                        | 81  |

| 12.4       | I/O PORTS                                               |     |

| 12.5       | DMA CONTROLLER                                          | 98  |

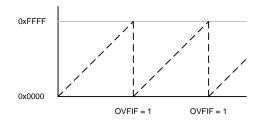

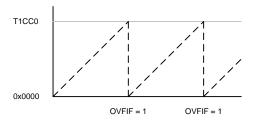

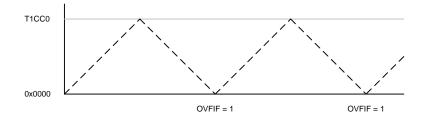

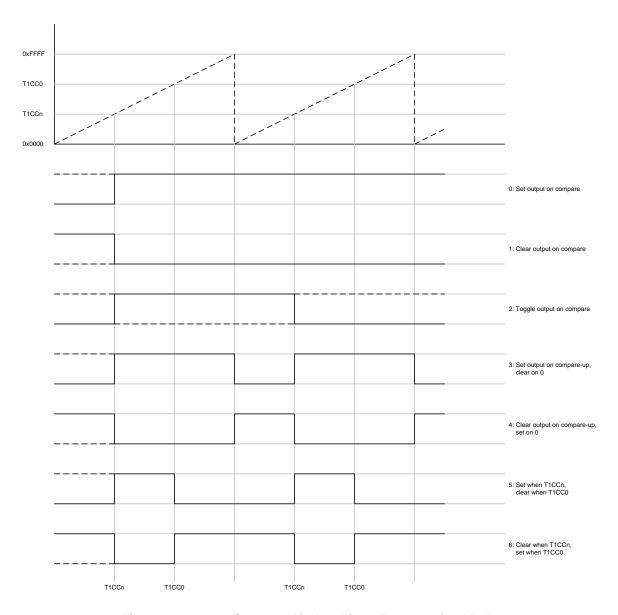

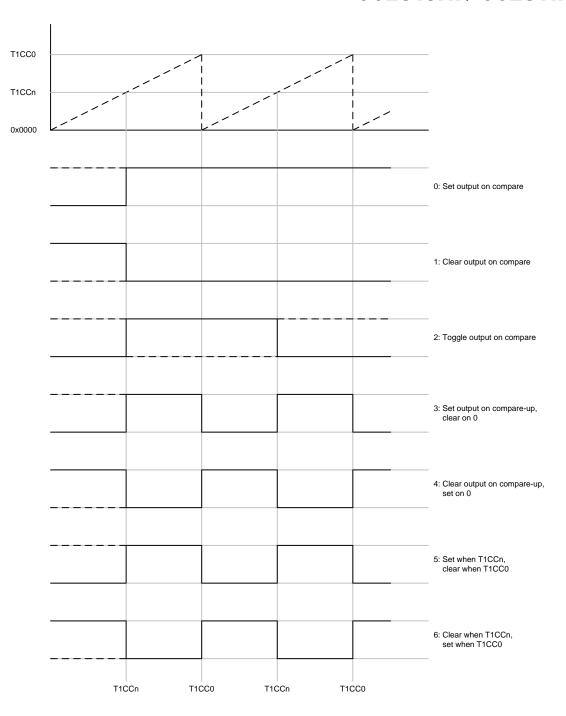

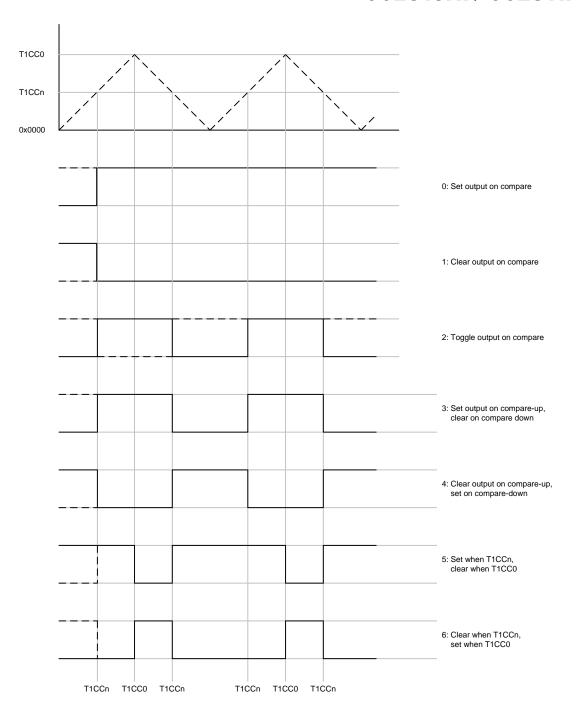

| 12.6       | 16-BIT TIMER, TIMER 1                                   | 109 |

| 12.7       | MAC TIMER (TIMER 2)                                     |     |

| 12.8       | SLEEP TIMER                                             |     |

| 12.9       | 8-BIT TIMERS, TIMER 3 AND TIMER 4                       |     |

| 12.10      |                                                         |     |

|            | RANDOM NUMBER GENERATOR                                 |     |

|            | AES COPROCESSOR                                         |     |

|            | WATCHDOG TIMER                                          |     |

|            | USART                                                   |     |

|            | I <sup>2</sup> S                                        |     |

| 12.16      | USB CONTROLLER                                          |     |

| 13         | RADIO                                                   | 183 |

| 13.1       | COMMAND STROBES                                         |     |

| 13.2       | RADIO REGISTERS                                         |     |

| 13.3       | INTERRUPTS                                              |     |

| 13.4       | TX/RX DATA TRANSFER                                     |     |

| 13.5       | Data Rate Programming                                   |     |

| 13.6       | RECEIVER CHANNEL FILTER BANDWIDTH                       |     |

| 13.7       | DEMODULATOR, SYMBOL SYNCHRONIZER, AND DATA DECISION     |     |

| 13.8       | PACKET HANDLING HARDWARE SUPPORT                        |     |

| 13.9       | MODULATION FORMATS                                      |     |

|            | RECEIVED SIGNAL QUALIFIERS AND LINK QUALITY INFORMATION |     |

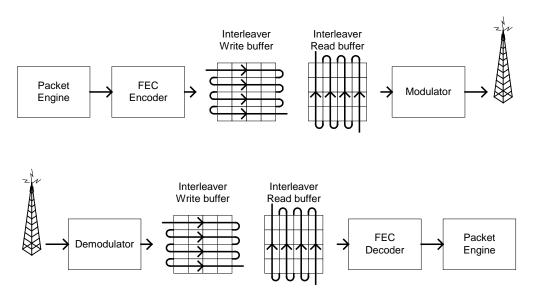

|            | FORWARD ERROR CORRECTION WITH INTERLEAVING              |     |

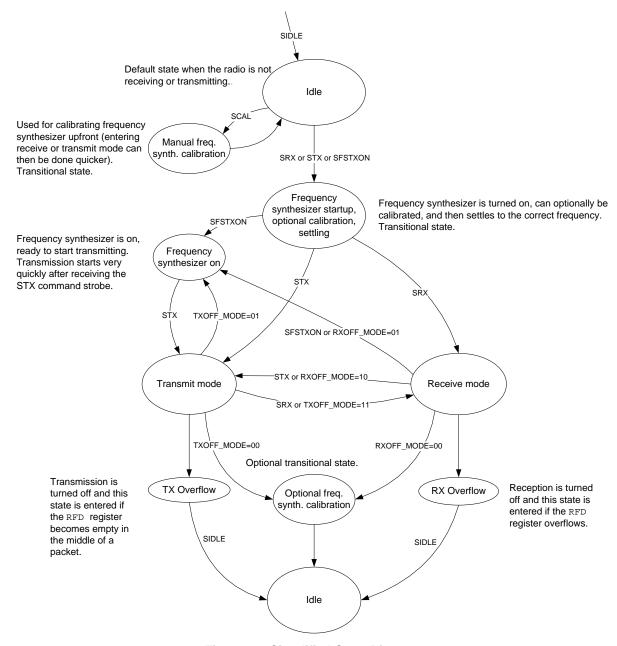

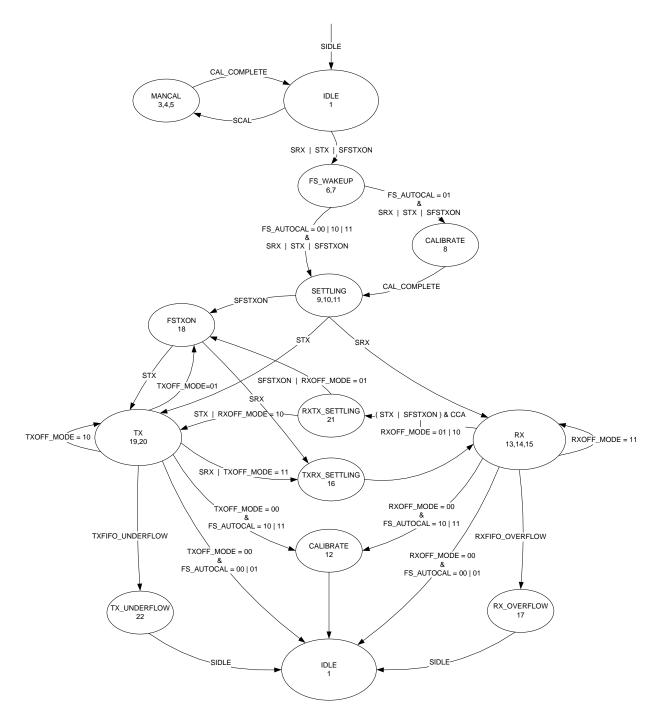

|            | RADIO CONTROL                                           |     |

|            | FREQUENCY PROGRAMMING                                   |     |

|            | VCO                                                     |     |

|            | OUTPUT POWER PROGRAMMING                                |     |

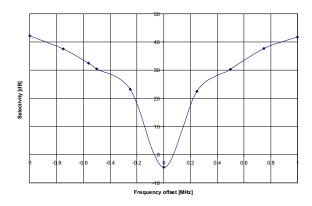

|            | SELECTIVITY                                             |     |

|            | SYSTEM CONSIDERATIONS AND GUIDELINES                    |     |

| 13.18      | RADIO REGISTERS                                         |     |

| 14         | VOLTAGE REGULATORS                                      |     |

| 14.1       | VOLTAGE REGULATOR POWER-ON                              |     |

| 15         | RADIO TEST OUTPUT SIGNALS                               |     |

| 16         | REGISTER OVERVIEW                                       |     |

| 17         | REFERENCES                                              | 232 |

| 18         | GENERAL INFORMATION                                     |     |

| 10<br>10 1 | DOCUMENT HISTORY                                        |     |

### **Abbreviations**

| $\Delta\Sigma$   | Delta-Sigma                                       | LNA       | Low-Noise Amplifier                          |

|------------------|---------------------------------------------------|-----------|----------------------------------------------|

| ADC              | Analog to Digital Converter                       | LO        | Local Oscillator                             |

| AES              | Advanced Encryption Standard                      | LQI       | Link Quality Indication                      |

| AGC              | Automatic Gain Control                            | LSB       | Least Significant Bit / Byte                 |

| ARIB             | Association of Radio Industries and               | MAC       | Medium Access Control                        |

|                  | Businesses                                        | MCU       | Microcontroller Unit                         |

| BCD              | Binary Coded Decimal                              | MISO      | Master In Slave Out                          |

| BER              | Bit Error Rate                                    | MOSI      | Master Out Slave In                          |

| BOD              | Brown Out Detector                                | MSB       | Most Significant Bit / Byte                  |

| CBC              | Cipher Block Chaining                             | NA        | Not Applicable                               |

| CBC-             | Cipher Block Chaining Message                     | OFB       | Output Feedback (encryption)                 |

| MAC              | Authentication Code                               | PA        | Power Amplifier                              |

| CCA              | Clear Channel Assessment                          | PCB       | Printed Circuit Board                        |

| CCM              | Counter mode + CBC-MAC                            | PER       | Packet Error Rate                            |

| CFB              | Cipher Feedback                                   | PLL       | Phase Locked Loop                            |

| CFR              | Code of Federal Regulations                       | PM{0 - 3} | Power Mode 0 - 3                             |

| CMOS             | Complementary Metal Oxide                         | PMC       | Power Management Controller                  |

| CDLI             | Semiconductor                                     | POR       | Power On Reset                               |

| CPU<br>CRC       | Central Processing Unit                           | PWM       | Pulse Width Modulator                        |

|                  | Cyclic Redundancy Check                           | Px_n      | Port x pin n ( $x = 0, 1, \text{ or } 2$ and |

| CTR              | Counter mode (encryption)                         | _         | n = 0, 1, 2,, 7)                             |

| DAC              | Digital to Analog Converter                       | QLP       | Quad Leadless Package                        |

| DMA              | Direct Memory Access                              | RAM       | Random Access Memory                         |

| DSM              | Delta-Sigma Modulator                             | RCOSC     | RC Oscillator                                |

| ECB              | Electronic Code Book                              | RF        | Radio Frequency                              |

| EM               | Evaluation Module                                 | RoHS      | Restriction on Hazardous Substances          |

| ENOB             | Effective Number of Bits                          | RSSI      | Receive Signal Strength Indicator            |

| EP{0 - 5}        | USB Endpoints 0 - 5                               | RX        | Receive                                      |

| ESD              | Electro Static Discharge                          | SCK       | Serial Clock                                 |

| ESR              | Equivalent Series Resistance                      | SFD       | Start of Frame Delimiter                     |

| ETSI             | European Telecommunications Standard<br>Institute | SFR       | Special Function Register                    |

| FCC              | Federal Communications Commission                 | SINAD     | Signal-to-noise and distortion ratio         |

| FIFO             | First In First Out                                |           |                                              |

| GPIO             | General Purpose Input / Output                    | SPI       | Serial Peripheral Interface                  |

| HSSD             | High Speed Serial Debug                           | SRAM      | Static Random Access Memory                  |

| HW               | Hardware                                          | SW        | Software                                     |

| I <sup>2</sup> S | Inter-IC Sound                                    | T/R       | Transmit / Receive                           |

| I/O              | Input / Output                                    | TX        | Transmit                                     |

| I/Q              | In-phase / Quadrature-phase                       | UART      | Universal Asynchronous                       |

| IF               | Intermediate Frequency                            |           | Receiver/Transmitter                         |

| IOC              | I/O Controller                                    | USART     | Universal Synchronous/Asynchronous           |

| ISM              | Industrial, Scientific and Medical                | HOD       | Receiver/Transmitter                         |

| ISR              | Interrupt Service Routine                         | USB       | Universal Serial Bus                         |

| IV               | Initialization Vector                             | VCO       | Voltage Controlled Oscillator                |

| JEDEC            | Joint Electron Device Engineering Council         | VGA       | Variable Gain Amplifier                      |

| kbps             | kilo bits per second                              | WDT       | Watchdog Timer                               |

| KB<br>KB         | Kilo Bytes (1024 bytes)                           | XOSC      | Crystal Oscillator                           |

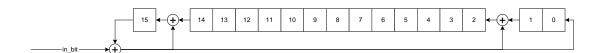

| LFSR             | Linear Feedback Shift Register                    |           |                                              |

| 21 01            | Emocal i Couback Offic Register                   |           |                                              |

SWRS055G Page 4 of 236

### 1 Register Conventions

Each SFR is described in a separate table. The table heading is given in the following format:

### **REGISTER NAME (SFR Address) - Register Description.**

Each RF register is described in a separate table. The table heading is given in the following format:

### **XDATA Address: REGISTER NAME - Register Description**

All register descriptions include a symbol denoted R/W describing the accessibility of each bit in the register. The register values are always given in binary notation unless prefixed by '0x', which indicates hexadecimal notation.

| Symbol | Access Mode    |

|--------|----------------|

| R/W    | Read/write     |

| R      | Read only      |

| R0     | Read as 0      |

| R1     | Read as 1      |

| W      | Write only     |

| W0     | Write as 0     |

| W1     | Write as 1     |

| H0     | Hardware clear |

| H1     | Hardware set   |

**Table 1: Register Bit Conventions**

SWRS055G Page 5 of 236

#### 2 **Key Features (in more details)**

#### 2.1 High-Performance and Low-Power **8051-Compatible Microcontroller**

- Optimized 8051 core which typically gives 8x the performance of a standard 8051

- Two data pointers

- In-circuit interactive debugging supported by the IAR Embedded Workbench through a simple two-wire serial interface

- SW compatible with CC1110Fx/CC1111Fx

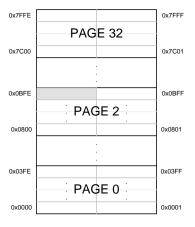

#### 2.2 8/16/32 kB Non-volatile Program Memory and 1/2/4 kB Data Memory

- 8, 16, or 32 kB of non-volatile flash programmable memory, in-system through a simple two-wire interface or by the 8051 core

- Minimum flash memory endurance: 1000 write/erase cycles

- Programmable read and write lock of portions of flash memory for software security

- 1, 2, or 4 kB of internal SRAM

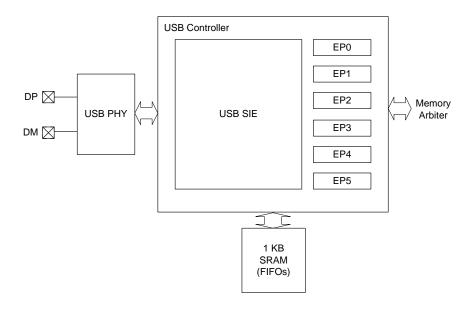

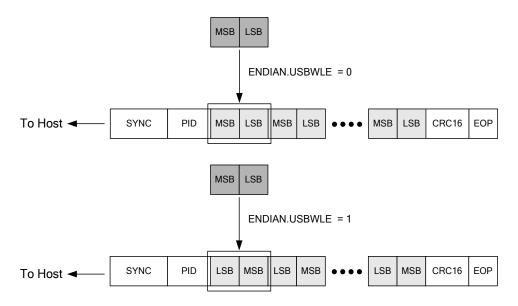

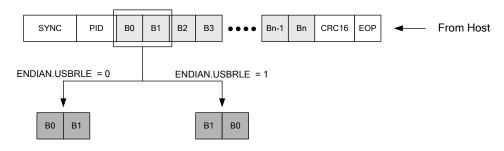

#### Full-Speed USB Controller (CC2511Fx) 2.3

- 5 bi-directional endpoints in addition to control endpoint 0

- Full-Speed, 12 Mbps transfer rate

- Support for Bulk, Interrupt, and Isochronous endpoints

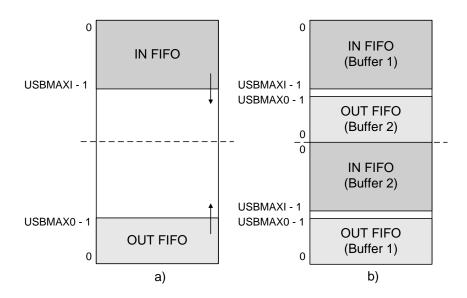

- 1024 bytes of dedicated endpoint FIFO memory

- 8 512 byte data packet size supported

- Configurable FIFO size for IN and OUT direction of endpoint

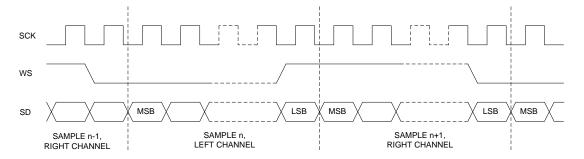

#### I<sup>2</sup>S Interface 2.4

- Industry standard I<sup>2</sup>S interface for transfer of digital audio data

- · Full duplex

- Mono and stereo support

- Configurable sample rate and sample size

- Support for µ-law compression and expansion

- Typically used to connect to external DAC or ADC

#### 2.5 Hardware AES Encryption/Decryption

128-bit AES supported in hardware coprocessor

#### **Peripheral Features** 2.6

- Powerful DMA Controller

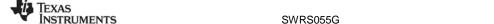

- Power On Reset/Brown-Out Detection

- ADC with eight individual input channels, single-ended or differential (*CC2511Fx* has six channels) configurable resolution

- Programmable watchdog timer

- Five timers: one general 16-bit timer with DSM mode, two general 8-bit timers, one MAC timer, and one sleep timer

- Two **USARTs** programmable for master/slave SPI or UART operation

- 21 configurable general-purpose digital I/O-pins (*CC2511Fx* has 19)

- Random number generator

#### **Low Power** 2.7

- Four flexible power modes for reduced power consumption

- System can wake up on external interrupt or when the Sleep Timer expires

- 0.5 µA current consumption in PM2, where external interrupts or the Sleep Timer can wake up the system

- 0.3 µA current consumption in PM3, where external interrupts can wake up the system

- Low-power fully static CMOS design

- System clock source is either a high speed crystal oscillator (24 - 27 MHz for CC2510Fx and 48 MHz for CC2511Fx) or a high speed RC oscillator (12 - 13.5 MHz for *CC2510Fx* and 12 MHz for *CC2511Fx*).

- The high speed crystal oscillator must be used when the radio is active.

- Clock source for ultra-low power operation can be either a low-power RC oscillator or an optional 32.768 kHz crystal oscillator

- Very fast transition to active mode from power modes enables ultra low average power consumption in low duty-cycle systems

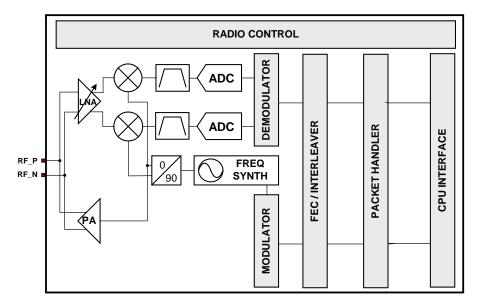

#### 2.8 2.4 GHz Radio with Baseband Modem

- Based on the industry leading *CC2500* radio core

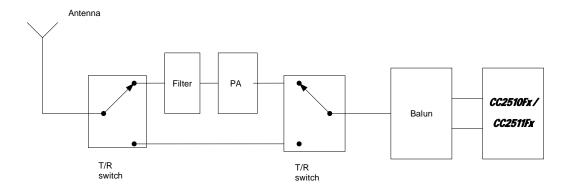

- Few external components: On-chip frequency synthesizer, no external filters or RF switch needed

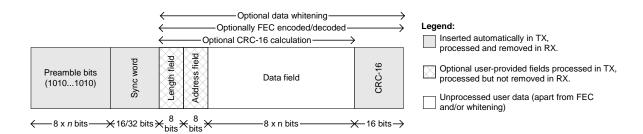

- Flexible support for packet oriented systems: On-chip support for sync word detection, address check, flexible packet length, and automatic CRC handling

- Supports use of DMA for both RX and TX resulting in minimal CPU intervention even on high data rates

- Programmable channel filter bandwidth

- · 2-FSK, GFSK and MSK supported

- Optional automatic whitening and dewhitening of data

- Programmable Carrier Sense (CS) indicator

- Programmable Preamble Quality Indicator for detecting preambles and improved protection against sync word detection in random noise

- Support for automatic Clear Channel Assessment (CCA) before transmitting (for listen-before-talk systems

- Support for per-package Link Quality Indication (LQI)

- Suited for systems targeting compliance with EN 300 328, EN 300 440, FCC CFR47 Part 15 and ARIB STD-T-66

- When transmitting in band 2480 -2483.5 MHz under FCC, duty-cycling or reducing output power might be needed

SWRS055G Page 7 of 236

### 3 Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 2 be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

| Parameter                                 | Min  | Max                   | Units | Condition                                                      |

|-------------------------------------------|------|-----------------------|-------|----------------------------------------------------------------|

| Supply voltage (VDD)                      | -0.3 | 3.9                   | V     | All supply pins must have the same voltage                     |

| Voltage on any digital pin                | -0.3 | VDD + 0.3,<br>max 3.9 | ٧     |                                                                |

| Voltage on the pins RF_P, RF_N and DCOUPL | -0.3 | 2.0                   | >     |                                                                |

| Voltage ramp-up rate                      |      | 120                   | kV/µs |                                                                |

| Input RF level                            |      | 10                    | dBm   |                                                                |

| Storage temperature range                 | -50  | 150                   | °C    | Device not programmed                                          |

| Solder reflow temperature                 |      | 260                   | °C    | According to IPC/JEDEC J-STD-020D                              |

| ESD <i>CC2510Fx</i>                       |      | 750                   | V     | According to JEDEC STD 22, method A114, Human Body Model (HBM) |

| ESD <i>CC2510Fx</i>                       |      | 500                   | ٧     | According to JEDEC STD 22, C101C, Charged Device Model (CDM)   |

| ESD <i>CC2511x</i>                        |      | 750                   | V     | According to JEDEC STD 22, method A114, Human Body Model (HBM) |

| ESD <i>CC2511x</i>                        |      | 500                   | V     | According to JEDEC STD 22, C101C, Charged Device Model (CDM)   |

**Table 2: Absolute Maximum Ratings**

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

SWRS055G Page 8 of 236

### 4 Operating Conditions

### 4.1 *CC2510Fx* Operating Conditions

The operating conditions for *CC2510Fx* are listed in Table 3 below.

| Parameter                                     | Min | Max | Unit | Condition                                  |

|-----------------------------------------------|-----|-----|------|--------------------------------------------|

| Operating ambient temperature, T <sub>A</sub> | -40 | 85  | °C   |                                            |

| Operating supply voltage (VDD)                | 2.0 | 3.6 | V    | All supply pins must have the same voltage |

Table 3: Operating Conditions for CC2510Fx

### 4.2 *CC2511Fx* Operating Conditions

The operating conditions for *CC2511Fx* are listed in Table 4 below.

| Parameter                                     | Min | Max | Unit | Condition                                  |

|-----------------------------------------------|-----|-----|------|--------------------------------------------|

| Operating ambient temperature, T <sub>A</sub> | 0   | 85  | °C   |                                            |

| Operating supply voltage (VDD)                | 3.0 | 3.6 | V    | All supply pins must have the same voltage |

Table 4: Operating Conditions for CC2511Fx

### **5** General Characteristics

$T_A = 25$ °C, VDD = 3.0 V if nothing else stated

| Parameter             | Min  | Тур | Max    | Unit  | Condition/Note                                                                                                                                                                                                                                                  |

|-----------------------|------|-----|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Radio part            |      |     |        |       |                                                                                                                                                                                                                                                                 |

| Frequency range       | 2400 |     | 2483.5 | MHz   | There will be spurious signals at n/2·crystal oscillator frequency (n is an integer number). RF frequencies at n/2·crystal oscillator frequency should therefore be avoided (e.g. 2405, 2418, 2431, 2444, 2457, 2470 and 2483 MHz when using a 26 MHz crystal). |

| Data rate             | 1.2  |     | 500    | kBaud | 2-FSK                                                                                                                                                                                                                                                           |

|                       | 1.2  |     | 250    | kBaud | GFSK                                                                                                                                                                                                                                                            |

|                       | 26   |     | 500    | kBaud | (Shaped) MSK (also known as differential offset QPSK)                                                                                                                                                                                                           |

|                       |      |     |        |       | Optional Manchester encoding (the data rate in kbps will be half the baud rate)                                                                                                                                                                                 |

| Wake-Up Timing        |      |     |        |       |                                                                                                                                                                                                                                                                 |

| PM1 → Active<br>Mode  |      | 4   |        | μs    | Digital regulator on. HS RCOSC and high speed crystal oscillator off. 32.768 kHz XOSC or low power RCOSC running.                                                                                                                                               |

|                       |      |     |        |       | SLEEP.OSC_PD=1 and CLKCON.OSC=1                                                                                                                                                                                                                                 |

| PM2/3→ Active<br>Mode |      | 100 |        | μs    | Digital regulator off. HS RCOSC and high speed crystal oscillator off. 32.768 kHz XOSC or low power RCOSC running (PM2). No crystal oscillators or RC oscillators are running in PM3.                                                                           |

|                       |      |     |        |       | SLEEP.OSC_PD=1 and CLKCON.OSC=1                                                                                                                                                                                                                                 |

**Table 5: General Characteristics**

SWRS055G Page 9 of 236

### 6 Electrical Specifications

#### 6.1 Current Consumption

$T_A = 25$ °C, VDD = 3.0 V if nothing else stated. All measurement results are obtained using the CC2510EM reference design ([1]).

| Parameter                                            | Min | Тур  | Max | Unit | Condition                                                                                                                                          |

|------------------------------------------------------|-----|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Active mode, full                                    |     | 4.8  |     | mA   | System clock running at 26 MHz.                                                                                                                    |

| speed (high speed crystal oscillator) <sup>1</sup> . |     | 4.6  |     | mA   | System clock running at 24 MHz.                                                                                                                    |

| Low CPU activity.                                    |     |      |     |      | Digital regulator on. High speed crystal oscillator and low power RCOSC running. No peripherals running.                                           |

|                                                      |     |      |     |      | Low CPU activity: No flash access (i.e. only cache hit), no RAM access                                                                             |

| Active mode, full                                    |     | 2.5  |     | mA   | System clock running at 13 MHz.                                                                                                                    |

| speed (HS<br>RCOSC) <sup>1</sup> .                   |     |      |     |      | Digital regulator on. HS RCOSC and low power RCOSC running. No peripherals running.                                                                |

| Low CPU activity.                                    |     |      |     |      | Low CPU activity: No flash access (i.e. only cache hit), no RAM access                                                                             |

| Active mode with radio in RX                         |     |      |     |      | Digital regulator on. High speed crystal oscillator and low power RCOSC running. Radio in RX mode (sensitivity optimized MDMCFG2.DEM_DCFILT_OFF=0) |

|                                                      |     | 19.8 |     | mA   | 2.4 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                             |

|                                                      |     | 20.6 |     | mA   | 2.4 kBaud, input at sensitivity limit, system clock running at 24 MHz.                                                                             |

|                                                      |     | 17.1 |     | mA   | 2.4 kBaud, input at sensitivity limit, system clock running at 203 kHz.                                                                            |

|                                                      |     | 19.8 |     | mA   | 2.4 kBaud, input well above sensitivity limit, system clock running at 26 MHz.                                                                     |

|                                                      |     | 21.5 |     | mA   | 10 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                              |

|                                                      |     | 22.1 |     | mA   | 10 kBaud, input at sensitivity limit, system clock running at 24 MHz.                                                                              |

|                                                      |     | 18.8 |     | mA   | 10 kBaud, input at sensitivity limit, system clock running at 203 kHz.                                                                             |

|                                                      |     | 19.0 |     | mA   | 10 kBaud, input well above sensitivity limit, system clock running at 26 MHz.                                                                      |

|                                                      |     | 22.9 |     | mA   | 250 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                             |

|                                                      |     | 22.7 |     | mA   | 250 kBaud, input at sensitivity limit, system clock running at 24 MHz.                                                                             |

|                                                      |     | 20.5 |     | mA   | 250 kBaud, input at sensitivity limit, system clock running at 1.625 MHz.                                                                          |

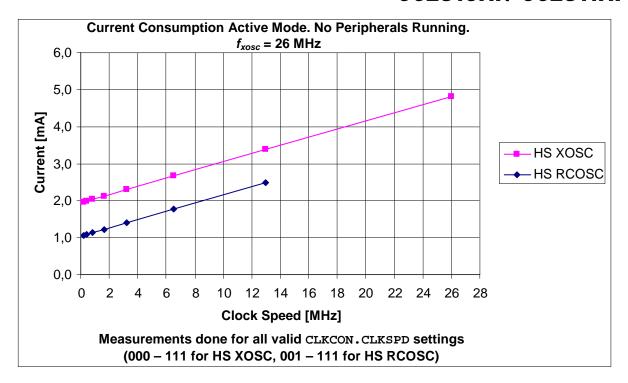

|                                                      |     | 19.6 |     | mA   | 250 kBaud, input well above sensitivity limit, system clock running at 26 MHz. See Figure 2 for typical variation over operating conditions        |

|                                                      |     | 19.7 |     | mA   | 500 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                             |

|                                                      |     | 20.8 |     | mA   | 500 kBaud, input at sensitivity limit, system clock running at 24 MHz.                                                                             |

|                                                      |     | 17.5 |     | mA   | 500 kBaud, input at sensitivity limit, system clock running at 3.25 MHz.                                                                           |

|                                                      |     | 16.7 |     | mA   | 500 kBaud, input well above sensitivity limit                                                                                                      |

|                                                      |     |      |     |      | Digital regulator on. High speed crystal oscillator and low power RCOSC running. Radio in RX mode (current optimized MDMCFG2.DEM_DCFILT_OFF=1)     |

|                                                      |     | 17.4 |     | mA   | 2.4 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                             |

|                                                      |     | 14.7 |     | mA   | 2.4 kBaud, input at sensitivity limit, system clock running at 203 kHz.                                                                            |

|                                                      |     | 17.4 |     | mA   | 2.4 kBaud, input well above sensitivity limit, system clock running at 26 MHz.                                                                     |

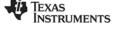

<sup>&</sup>lt;sup>1</sup> Note: In order to reduce the current consumption in active mode, the clock speed can be reduced by setting CLKCON.CLKSPD≠000 (see section 13.1 for details). Figure 1 shows typical current consumption in active mode for different clock speeds

SWRS055G Page 10 of 236

| Parameter                            | Min | Тур  | Max | Unit           | Condition                                                                                                                                   |

|--------------------------------------|-----|------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |     | 19.4 |     | mA             | 10 kBaud, input at sensitivity limit, system clock running at 26 MHz.                                                                       |

|                                      |     | 15.7 |     | mA             | 10 kBaud, input at sensitivity limit, system clock running at 203 kHz.                                                                      |

|                                      |     | 16.9 |     | mA             | 10 kBaud, input well above sensitivity limit, system clock running at 26 MHz.                                                               |

| Active mode with                     |     |      |     |                | System clock running at 26 MHz.                                                                                                             |

| radio in TX                          |     |      |     |                | Digital regulator on. High speed crystal oscillator and low power RCOSC running. Radio in TX mode                                           |

|                                      |     | 26   |     | mA             | 0 dBm output power (PA_TABLE0=0xFE). See Table 7 for typical variation over operating conditions                                            |

|                                      |     | 18.5 |     | mA             | -6 dBm output power (PA_TABLE0=0x7F)                                                                                                        |

|                                      |     | 15.5 |     | mA             | -12 dBm output power (PA_TABLE0=0x95)                                                                                                       |

|                                      |     | 26   |     | mA             | System clock running at 24 MHz.                                                                                                             |

|                                      |     |      |     |                | Digital regulator on. High speed crystal oscillator and low power RCOSC running. Radio in TX mode **/0 dBm output power (PA_TABLE0=0xFE)    |

| РМ0                                  |     | 4.3  |     | mA             | Same as active mode, but the CPU is not running (see 12.1.2.2 for details). System clock running at 26 MHz                                  |

| PM1                                  |     | 220  |     | μА             | Digital regulator on. HS RCOSC and high speed crystal oscillator off. 32.768 kHz XOSC or low power RCOSC running (see 12.1.2.3 for details) |

| PM2                                  |     | 0.5  | 1   | μА             | Digital regulator off. HS RCOSC and high speed crystal oscillator off. Low power RCOSC running (see 12.1.2.4 for details)                   |

| РМ3                                  |     | 0.3  | 1   | μА             | Digital regulator off. No crystal oscillators or RC oscillators are running (see 12.1.2.5 for details)                                      |

| Peripheral<br>Current<br>Consumption |     |      |     |                | Add to the figures above if the peripheral unit is activated                                                                                |

| Timer 1                              |     | 2.7  |     | μ <b>A/MHz</b> | When running                                                                                                                                |

| Timer 2                              |     | 1.3  |     | μ <b>A/MHz</b> | When running                                                                                                                                |

| Timer 3                              |     | 1.6  |     | μ <b>A/MHz</b> | When running                                                                                                                                |

| Timer 4                              |     | 2    |     | μ <b>A/MHz</b> | When running                                                                                                                                |

| ADC                                  |     | 1.2  |     | mA             | During conversion                                                                                                                           |

**Table 6: Current Consumption**

SWRS055G Page 11 of 236

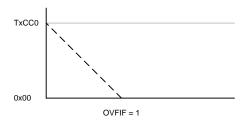

Figure 1: Current Consumption (Active Mode) vs. Clock Speed

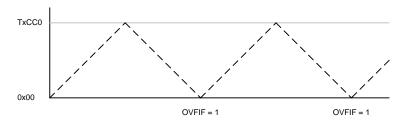

Figure 2: Typical Variation in RX Current Consumption over Temperature and Input Power Level.

Data Rate = 250 kBaud.

|                  | Supply | Voltage, VI | DD = 2 V | Supply Voltage, VDD = 3 V |    |      | Supply Voltage, VDD = 3.6 V |      |      |

|------------------|--------|-------------|----------|---------------------------|----|------|-----------------------------|------|------|

| Temperature [°C] | -40    | 25          | 85       | -40                       | 25 | 85   | -40                         | 25   | 85   |

| Current [mA]     | 26     | 25.6        | 26       | 26.3                      | 26 | 26.3 | 26.5                        | 26.2 | 26.6 |

Table 7: Typical Variation in TX Current Consumption over Temperature and Supply Voltage, 0 dBm Output Power

SWRS055G Page 12 of 236

### 6.2 RF Receive Section

$T_A = 25$  °C, VDD = 3.0 V if nothing else stated. All measurement results are obtained using the CC2510EM reference design ([1]).

| Parameter                        | Min        | Тур        | Max      | Unit     | Condition/Note                                                                                                                                                                            |  |

|----------------------------------|------------|------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Digital channel filter bandwidth | 58         |            | 812      | kHz      | User programmable (see Section 13.6). The bandwidth limits are proportional to crystal frequency (given values assume a 26.0 MHz crystal).                                                |  |

|                                  |            |            |          |          | CFG2.DEM_DCFILT_OFF=0 gth, 203 kHz digital channel filter bandwidth)                                                                                                                      |  |

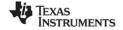

| Receiver sensitivity             |            | -103       |          | dBm      | The RX current consumption can be reduced by approximately 2.4 mA by setting MDMCFG2.DEM_DCFILT_OFF=1. The typical sensitivity is then -101 dBm.                                          |  |

|                                  |            |            |          |          | The sensitivity can be improved to typically -105 dBm with MDMCFG2.DEM_DCFILT_OFF=0 by changing registers TEST2 and TEST1 (see Page 222). The temperature range is then from 0°C to 85°C. |  |

| Saturation                       |            | -10        |          | dBm      |                                                                                                                                                                                           |  |

| Adjacent<br>channel<br>rejection |            | 23         |          | dB       | Desired channel 3 dB above the sensitivity limit. 250 kHz channel spacing                                                                                                                 |  |

| Alternate channel rejection      |            | 32         |          | dB       | Desired channel 3 dB above the sensitivity limit. 250 kHz channel spacing                                                                                                                 |  |

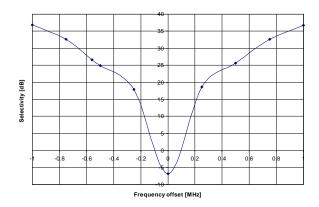

|                                  |            |            |          |          | See Figure 55 for plot of selectivity versus frequency offset                                                                                                                             |  |

| Blocking                         |            |            |          |          |                                                                                                                                                                                           |  |

| ±10 MHz offset                   |            | 64         |          | dB       | Wanted signal 3 dB above sensitivity level.                                                                                                                                               |  |

| ±20 MHz offset                   |            | 70         |          | dB       | Compliant with ETSI EN 300 440 class 2 receiver requirements.                                                                                                                             |  |

| ±50 MHz offset                   |            | 71         |          | dB       |                                                                                                                                                                                           |  |

| 10 kBaud data ra                 | ate, sen   | sitivity o | ptimize  | ed, MDM  | CFG2.DEM_DCFILT_OFF=0                                                                                                                                                                     |  |

| (2-FSK, 1% pack                  | et error ı | rate, 20 I | oytes pa | cket len | gth, 232 kHz digital channel filter bandwidth)                                                                                                                                            |  |

| Receiver sensitivity             |            | -98        |          | dBm      | The RX current consumption can be reduced by approximately 2.2 mA by setting MDMCFG2.DEM_DCFILT_OFF=1. The typical sensitivity is then -97 dBm.                                           |  |

|                                  |            |            |          |          | The sensitivity can be improved to typically -100 dBm with MDMCFG2.DEM_DCFILT_OFF=0 by changing registers TEST2 and TEST1 (see Page 222). The temperature range is then from 0°C to 85°C. |  |

| Saturation                       |            | -9         |          | dBm      |                                                                                                                                                                                           |  |

| Adjacent<br>channel<br>rejection |            | 19         |          | dB       | Desired channel 3 dB above the sensitivity limit. 250 kHz channel spacing                                                                                                                 |  |

| Alternate channel rejection      |            | 25         |          | dB       | Desired channel 3 dB above the sensitivity limit. 250 kHz channel spacing                                                                                                                 |  |

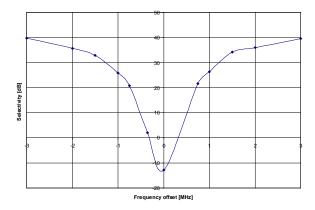

|                                  |            |            |          |          | See Figure 56 for plot of selectivity versus frequency offset                                                                                                                             |  |

| Blocking                         |            |            |          |          |                                                                                                                                                                                           |  |

|                                  | i          | 1          | 1        | -ID      | Wanted signal 3 dB above sensitivity level.                                                                                                                                               |  |

| ±10 MHz offset                   |            | 59         |          | dB       | Wanted Signal 3 db above Sensitivity level.                                                                                                                                               |  |

| _                                |            | 59<br>65   |          | dB       | Compliant with ETSI EN 300 440 class 2 receiver requirements.                                                                                                                             |  |

SWRS055G Page 13 of 236

| Parameter                         | Min      | Тур     | Max         | Unit | Condition/Note                                                                                                                                |

|-----------------------------------|----------|---------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |          |         |             |      | h, 540 kHz digital channel filter bandwidth)                                                                                                  |

| Receiver sensitivity              |          | -90     |             | dBm  | See Table 9 for typical variation over operating conditions                                                                                   |

| Saturation                        |          | -11     |             | dBm  |                                                                                                                                               |

| Adjacent<br>channel<br>rejection  |          | 21      |             | dB   | Desired channel 3 dB above the sensitivity limit. 750 kHz channel spacing                                                                     |

| Alternate<br>channel<br>rejection |          | 30      |             | dB   | Desired channel 3 dB above the sensitivity limit. 750 kHz channel spacing                                                                     |

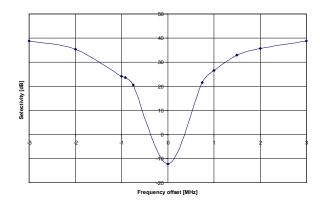

|                                   |          |         |             |      | See Figure 57 for plot of selectivity versus frequency offset                                                                                 |

| Blocking                          |          |         |             |      |                                                                                                                                               |

| ±10 MHz offset                    |          | 46      |             | dB   | Wanted signal 3 dB above sensitivity level.                                                                                                   |

| ±20 MHz offset                    |          | 53      |             | dB   | Compliant with ETSI EN 300 440 class 2 receiver requirements.                                                                                 |

| ±50 MHz offset                    |          | 55      |             | dB   |                                                                                                                                               |

| be used for data ra               | ates >10 | 00 kBau | d) •        | •    | MCFG2.DEM_DCFILT_OFF=0 (MDMCFG2.DEM_DCFILT_OFF=1 cannot h, 812 kHz digital channel filter bandwidth)                                          |

| Receiver sensitivity              |          | -82     |             | dBm  |                                                                                                                                               |

| Saturation                        |          | -15     |             | dBm  |                                                                                                                                               |

| Adjacent<br>channel<br>rejection  |          | 12      |             | dB   | Desired channel 3 dB above the sensitivity limit. 1 MHz channel spacing                                                                       |

| Alternate<br>channel<br>rejection |          | 23      |             | dB   | Desired channel 3 dB above the sensitivity limit. 1 MHz channel spacing                                                                       |

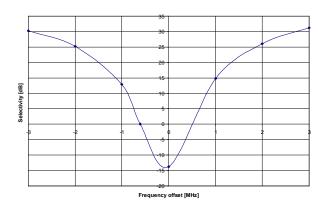

|                                   |          |         |             |      | See Figure 59 for plot of selectivity versus frequency offset                                                                                 |

| General                           |          |         | •           | •    |                                                                                                                                               |

| Spurious emissions                |          |         |             |      | Conducted measurement in a 50 $\Omega$ single ended load. Complies with EN 300 328, EN 300 440 class 2, FCC CFR47, Part 15 and ARIB STD-T-66. |

| 25 MHz -<br>1 GHz                 |          |         | <b>-</b> 57 | dBm  |                                                                                                                                               |

| Above 1 GHz                       |          |         | -47         | dBm  |                                                                                                                                               |

### **Table 8: RF Receive Section**

|                   | Supply V | oltage, VI | DD = 2 V | Supply            | Voltage, V | DD = 3 V | Supply Voltage, VDD = 3.6 V |       |       |

|-------------------|----------|------------|----------|-------------------|------------|----------|-----------------------------|-------|-------|

| Temperature [°C]  | -40      | 25         | 85       | <b>-</b> 40 25 85 |            |          | -40                         | 25    | 85    |

| Sensitivity [dBm] | -91.5    | -90.3      | -88.7    | -90               | -89.6      | -88.1    | -88.7                       | -89.3 | -88.4 |

Table 9: Typical Variation in Sensitivity over Temperature and Supply Voltage @ 2.44 GHz and 250 kBaud Data Rate

SWRS055G Page 14 of 236

### 6.3 RF Transmit Section

$T_A = 25$ °C, VDD = 3.0 V if nothing else stated. All measurement results are obtained using the CC2510EM reference designs ([1]).

| Parameter                                               | Min | Тур      | Max | Unit | Condition/Note                                                                                                                                                   |

|---------------------------------------------------------|-----|----------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential load impedance                             |     | 80 + j74 |     | Ω    | Differential impedance as seen from the RF-port (RF_P and RF_N) towards the antenna. Follow the CC2510EM reference design [1] available from TI's website.       |

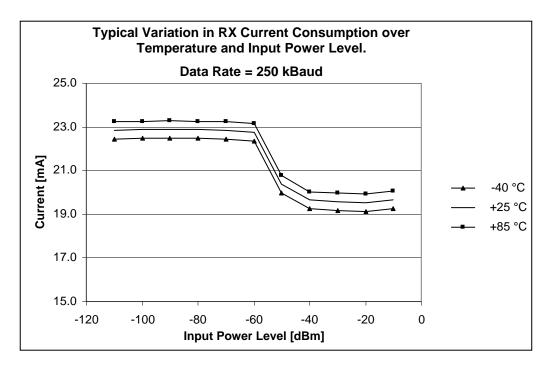

| Output power, highest setting                           |     | 1        |     | dBm  | Output power is programmable and is available across the entire frequency band. See Figure 3 typical variation over operating conditions (output power is 0 dBm) |

|                                                         |     |          |     |      | Delivered to a 50 $\Omega$ single-ended load via the CC2510EM reference design [1] RF matching network.                                                          |

| Output power, lowest setting                            |     | -30      |     | dBm  | Output power is programmable and is available across the entire frequency band                                                                                   |

|                                                         |     |          |     |      | Delivered to a 50 $\Omega$ single-ended load via the CC2510EM reference design [1] RF matching network.                                                          |

| Occupied bandwidth (99%)                                |     | -28      |     | dBc  | 2.4 kBaud, 38.2 kHz deviation, 2-FSK, 250 kHz channel spacing                                                                                                    |

|                                                         |     | -27      |     | dBc  | 10 kBaud, 38.2 kHz deviation, 2-FSK, 250 kHz channel spacing                                                                                                     |

|                                                         |     | -22      |     | dBc  | 250 kBaud, MSK, 750 kHz channel spacing                                                                                                                          |

|                                                         |     | -21      |     | dBc  | 500 kBaud, MSK, 1 MHz channel spacing                                                                                                                            |

| Spurious emissions                                      |     |          |     |      | 0 dBm output power.                                                                                                                                              |

| 25 MHz - 1 GHz                                          |     |          | -36 | dBm  |                                                                                                                                                                  |

| 47 - 74, 87.5 - 118,<br>174 - 230, and<br>470 - 862 MHz |     |          | -54 | dBm  |                                                                                                                                                                  |

| 1800 - 1900 MHz                                         |     |          | -47 | dBm  | Restricted band in Europe                                                                                                                                        |

| At 2·RF and 3·RF                                        |     |          | -41 | dBm  | Restricted bands in USA                                                                                                                                          |

| Otherwise above<br>1 GHz                                |     |          | -30 | dBm  |                                                                                                                                                                  |

**Table 10: RF Transmit Section**

## Typical Variation in Output Power (0 dBm) over Frequency and Temperature

Figure 3: Typical Variation in Output Power over Frequency and Temperature (0 dBm output power)

SWRS055G Page 15 of 236

### 6.4 Crystal Oscillators

### 6.4.1 CC2510Fx Crystal Oscillator

$T_A = 25$ °C, VDD = 3.0 V if nothing else is stated.

| Parameter                  | Min | Тур | Max | Unit | Condition/Note                                                                                                                                                                                                                                                                                                               |

|----------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal frequency          | 24  | 26  | 27  | MHz  | Referred to as $f_{\rm XOSC}$ . For operation below 26 MHz, please refer to Table 4 for Operating Conditions.                                                                                                                                                                                                                |

| Crystal frequency accuracy |     | ±40 |     | ppm  | This is the total tolerance including a) initial tolerance, b) crystal loading, c) aging, and d) temperature dependence.                                                                                                                                                                                                     |

| requirement                |     |     |     |      | The acceptable crystal tolerance depends on RF frequency and channel spacing / bandwidth.                                                                                                                                                                                                                                    |

| C <sub>0</sub>             | 1   | 5   | 7   | pF   | Simulated over operating conditions                                                                                                                                                                                                                                                                                          |

| Load capacitance           | 10  | 13  | 20  | pF   | Simulated over operating conditions                                                                                                                                                                                                                                                                                          |

| ESR                        |     |     | 100 | Ω    | Simulated over operating conditions                                                                                                                                                                                                                                                                                          |

| Start-up time              |     | 250 |     | μs   | $f_{XOSC} = 26 \text{ MHz}$                                                                                                                                                                                                                                                                                                  |

|                            |     |     |     |      | Note: A Ripple counter of 12 bit is included to ensure duty-cycle requirements. Start-up time includes ripple counter delay until SLEEP.XOSC_STB is asserted                                                                                                                                                                 |

| Power Down<br>Guard Time   | 3   |     |     | ms   | The crystal oscillator must be in power down for a guard time before it is used again. This requirement is valid for all modes of operation. The need for power down guard time can vary with crystal type and load. Minimum figure is valid for reference crystal NDK, AT-41CD2 and load capacitance according to Table 29. |

|                            |     |     |     |      | If power down guard time is violated, one of the consequences can be increased PER when using the radio immediately after the crystal oscillator has been reported stable.                                                                                                                                                   |

### Table 11: CC2510Fx Crystal Oscillator Parameters

### 6.4.2 CC2511Fx Crystal Oscillator

$T_A = 25$ °C, VDD = 3.0 V if nothing else is stated.

| Parameter                  | Min  | Тур | Max  | Unit | Condition/Note                                                                                                                                                |

|----------------------------|------|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal frequency          |      | 48  |      | MHz  | Referred to as f <sub>XOSC</sub>                                                                                                                              |

| Crystal frequency accuracy |      | ±40 |      | ppm  | This is the total tolerance including a) initial tolerance, b) crystal loading, c) aging, and d) temperature dependence.                                      |

| requirement                |      |     |      |      | The acceptable crystal tolerance depends on RF frequency and channel spacing / bandwidth.                                                                     |

| C <sub>0</sub>             |      |     |      |      |                                                                                                                                                               |

| Fundamental                | 0.85 | 1   | 1.15 | pF   | Simulated over operating conditions. Variation given by reference crystal NX2520SA from NDK                                                                   |

| 3 <sup>rd</sup> overtone   | 2    | 3   | 7    | pF   |                                                                                                                                                               |

| Load capacitance           | 15   | 16  | 17   | pF   | Simulated over operating conditions                                                                                                                           |

| ESR                        |      |     | 60   | Ω    | Simulated over operating conditions                                                                                                                           |

| Start-up time              |      |     |      |      | Note: A Ripple counter of 14 bit is included to ensure duty-cycle requirements. Start-up time includes ripple counter delay until SLEEP .XOSC_STB is asserted |

| Fundamental                |      | 650 |      | μs   |                                                                                                                                                               |

| 3 <sup>rd</sup> overtone   |      | 3   |      | ms   | Simulated value                                                                                                                                               |

Table 12: CC2511Fx Crystal Oscillator Parameters

SWRS055G Page 16 of 236

### 6.5 32.768 kHz Crystal Oscillator

$T_A = 25$ °C, VDD = 3.0V if nothing else is stated.

| Parameter         | Min | Тур    | Max | Unit | Condition/Note                      |

|-------------------|-----|--------|-----|------|-------------------------------------|

| Crystal frequency |     | 32.768 |     | kHz  |                                     |

| C <sub>0</sub>    |     | 0.9    | 2.0 | pF   | Simulated over operating conditions |

| Load capacitance  |     | 12     | 16  | pF   | Simulated over operating conditions |

| ESR               |     | 40     | 130 | kΩ   | Simulated over operating conditions |

| Start-up time     |     | 400    |     | ms   | Value is simulated                  |

Table 13: 32.768 kHz Crystal Oscillator Parameters

#### 6.6 Low Power RC Oscillator

$T_A = 25$ °C, VDD = 3.0 V if nothing else is stated.

| Parameter                            | Min  | Тур  | Max  | Unit | Condition/Note                                                                                                                                           |

|--------------------------------------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calibrated frequency <sup>2</sup>    | 32.0 | 34.7 | 36.0 | kHz  | CC2510Fx                                                                                                                                                 |

|                                      | 32.0 | 32.0 | 32.0 |      | CC2511Fx                                                                                                                                                 |

|                                      |      |      |      |      | Calibrated low power RC oscillator frequency is $f_{\rm Ref}/750$                                                                                        |

| Frequency accuracy after calibration |      |      | ±1   | %    |                                                                                                                                                          |

| Temperature coefficient              |      | +0.5 |      | %/°C | Frequency drift when temperature changes after calibration                                                                                               |

| Supply voltage coefficient           |      | +3   |      | %/V  | Frequency drift when supply voltage changes after calibration                                                                                            |

| Initial calibration time             |      | 2    |      | ms   | When the low power RC oscillator is enabled, calibration is continuously done in the background as long as the high speed crystal oscillator is running. |

**Table 14: Low Power RC Oscillator Parameters**

For *CC2510Fx* Min figures are given using  $f_{XOSC} = 24$  MHz. Typ figures are given using  $f_{XOSC} = 26$  MHz, and Max figures are given using  $f_{XOSC} = 27$  MHz. For *CC2511Fx*,  $f_{XOSC} = 48$  MHz

SWRS055G Page 17 of 236

$<sup>^2</sup>$   $f_{Ref} = f_{XOSC}$  for **CC2510Fx** and  $f_{Ref} = f_{XOSC}/2$  for **CC2511Fx**

### 6.7 High Speed RC Oscillator

$T_A = 25$ °C, VDD = 3.0 V if nothing else is stated.

| Parameter                         | Min | Тур | Max  | Unit   | Condition/Note                                                                                                                                                                                                                                                           |

|-----------------------------------|-----|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calibrated frequency <sup>2</sup> | 12  | 13  | 13.5 | MHz    | Calibrated HS RCOSC frequency is f <sub>XOSC</sub> / 2                                                                                                                                                                                                                   |

| Uncalibrated frequency accuracy   |     | ±15 |      | %      |                                                                                                                                                                                                                                                                          |

| Calibrated frequency accuracy     |     |     | ±1   | %      |                                                                                                                                                                                                                                                                          |

| Start-up time                     |     |     | 10   | μs     |                                                                                                                                                                                                                                                                          |

| Temperature coefficient           |     |     | -325 | ppm/°C | Frequency drift when temperature changes after calibration                                                                                                                                                                                                               |

| Supply voltage coefficient        |     |     | 28   | ppm/V  | Frequency drift when supply voltage changes after calibration                                                                                                                                                                                                            |

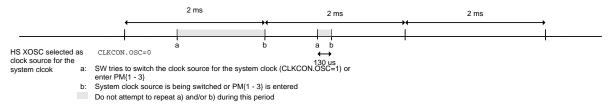

| Calibration time                  |     | 65  |      | μѕ     | The HS RCOSC will be calibrated once when the high speed crystal oscillator is selected as system clock source (CLKCON.OSC is set to 0), and also when the system wakes up from PM{1 - 3} if CLKCON.OSC was set to 0 when entering PM{1 - 3}. See 12.1.5.1 for details). |

**Table 15: High Speed RC Oscillator Parameters**

### 6.8 Frequency Synthesizer Characteristics

$T_A = 25$ °C, VDD = 3.0 V if nothing else stated. All measurement results are obtained using the CC2510EM reference designs ([1]).

| Parameter                       | Min | Тур  | Max | Unit   | Condition/Note                                                                                                                        |

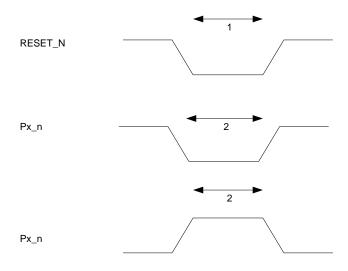

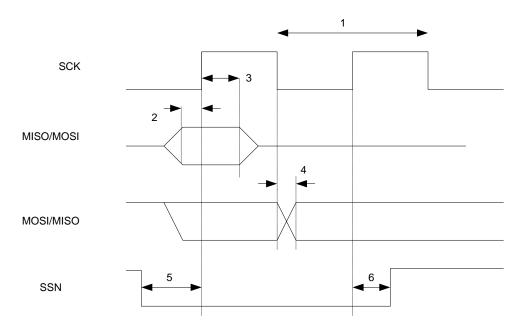

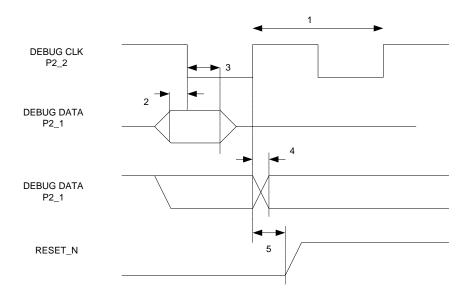

|---------------------------------|-----|------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------|