# ANALOG Integrated Dual RF Transmitter, Receiver, and Observation Pageiver

**ADRV9009 Data Sheet**

#### **FEATURES**

**Dual transmitters**

**Dual receivers**

**Dual input shared observation receiver** Maximum receiver bandwidth: 200 MHz

Maximum tunable transmitter synthesis bandwidth: 450 MHz

Maximum observation receiver bandwidth: 450 MHz Fully integrated fractional-N RF synthesizers

**Fully integrated clock synthesizer**

Multichip phase synchronization for RF LO and baseband clocks

JESD204B datapath interface

Tuning range (center frequency): 75 MHz to 6000 MHz

#### **APPLICATIONS**

3G, 4G, and 5G TDD macrocell base stations **TDD active antenna systems** Massive multiple input, multiple output (MIMO) Phased array radar **Electronic warfare** Military communications Portable test equipment

#### **GENERAL DESCRIPTION**

The ADRV9009 is a highly integrated, radio frequency (RF), agile transceiver offering dual transmitters and receivers, integrated synthesizers, and digital signal processing functions. The IC delivers a versatile combination of high performance and low power consumption demanded by 3G, 4G, and 5G macro cell time division duplex (TDD) base station applications.

The receive path consists of two independent, wide bandwidth, direct conversion receivers with state-of-the-art dynamic range. The device also supports a wide bandwidth, time shared observation path receiver (ORx) for use in TDD applications. The complete receive subsystem includes automatic and manual attenuation control, dc offset correction, quadrature error correction (QEC), and digital filtering, thus eliminating the need for these functions in the digital baseband. Several auxiliary functions, such as analog-to-digital converters (ADCs), digital-toanalog converters (DACs), and general-purpose inputs/outputs (GPIOs) for the power amplifier (PA), and RF front-end control are also integrated.

In addition to automatic gain control (AGC), the ADRV9009 also features flexible external gain control modes, allowing significant flexibility in setting system level gain dynamically.

The received signals are digitized with a set of four high dynamic range, continuous time  $\Sigma$ - $\Delta$  ADCs that provide inherent antialiasing. The combination of the direct conversion architecture, which does not suffer from out of band image mixing, and the lack of aliasing, relaxes the requirements of the RF filters when compared to traditional intermediate frequency (IF) receivers.

The transmitters use an innovative direct conversion modulator that achieves high modulation accuracy with exceptionally low noise.

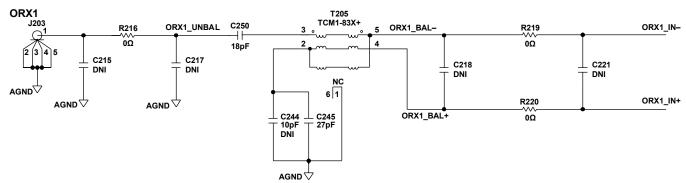

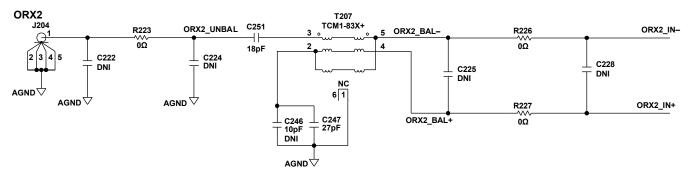

The observation receiver path consists of a wide bandwidth, direct conversion receiver with state-of-the-art dynamic range.

The fully integrated phase-locked loop (PLL) provides high performance, low power, fractional-N RF frequency synthesis for the transmitter (Tx) and receiver (Rx) signal paths. An additional synthesizer generates the clocks needed for the converters, digital circuits, and the serial interface. A multichip synchronization mechanism synchronizes the phase of the RF local oscillator (LO) and baseband clocks between multiple ADRV9009 chips. Precautions are taken to provide the isolation required in high performance base station applications. All voltage controlled oscillators (VCOs) and loop filter components are integrated.

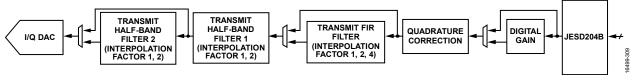

The high speed JESD204B interface supports up to 12.288 Gbps lane rates, resulting in two lanes per transmitter and a single lane per receiver in the widest bandwidth mode. The interface also supports interleaved mode for lower bandwidths, thus reducing the total number of high speed data interface lanes to one. Both fixed and floating point data formats are supported. The floating point format allows internal AGC to be invisible to the demodulator device.

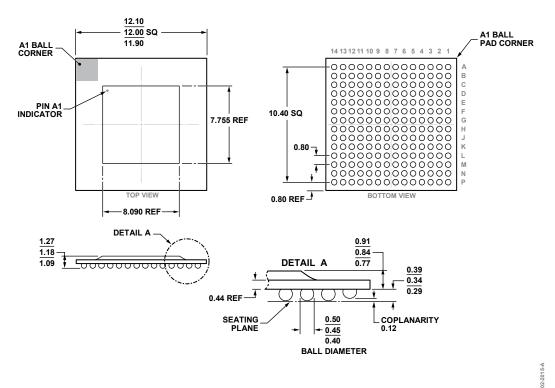

The core of the ADRV9009 can be powered directly from 1.3 V regulators and 1.8 V regulators, and is controlled via a standard 4-wire serial port. Comprehensive power-down modes are included to minimize power consumption in normal use. The ADRV9009 is packaged in a 12 mm × 12 mm, 196-ball chip scale ball grid array (CSP\_BGA).

Trademarks and registered trademarks are the property of their respective owners.

# **ADRV9009**

# **TABLE OF CONTENTS**

| reatures                                                           | Theory of Operation98                                                  |

|--------------------------------------------------------------------|------------------------------------------------------------------------|

| Applications1                                                      | Transmitter98                                                          |

| General Description1                                               | Receiver                                                               |

| Revision History                                                   | Observation Receiver98                                                 |

| Functional Block Diagram4                                          | Clock Input98                                                          |

| Specifications                                                     | Synthesizers                                                           |

| Current and Power Consumption Specifications14                     | SPI                                                                    |

|                                                                    |                                                                        |

| Timing Diagrams                                                    | JTAG Boundary Scan                                                     |

| Absolute Maximum Ratings                                           | Power Supply Sequence                                                  |

| Reflow Profile16                                                   | GPIO_x Pins                                                            |

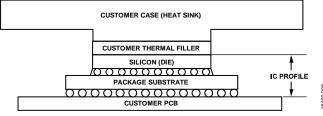

| Thermal Management                                                 | Auxiliary Converters                                                   |

| Thermal Resistance                                                 | JESD204B Data Interface                                                |

| ESD Caution16                                                      | Applications Information101                                            |

| Pin Configuration and Function Descriptions17                      | PCB Layout and Power Supply Recommendations 101                        |

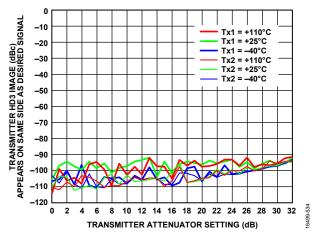

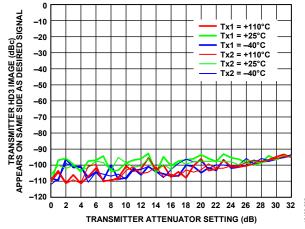

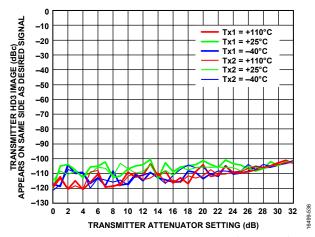

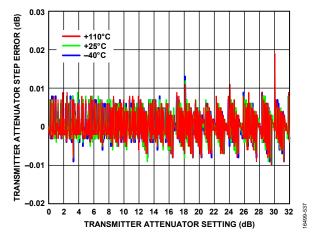

| Typical Performance Characteristics23                              | PCB Material and Stackup Selection                                     |

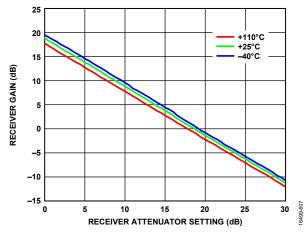

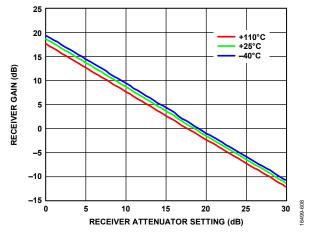

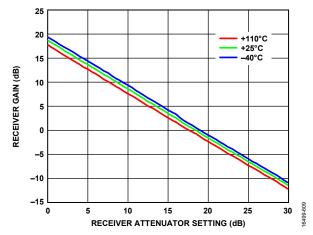

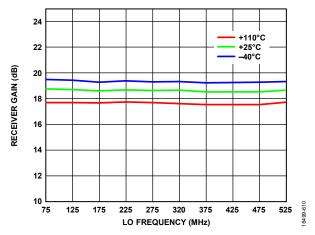

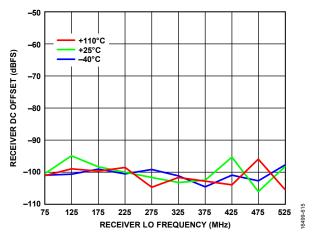

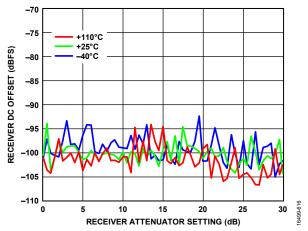

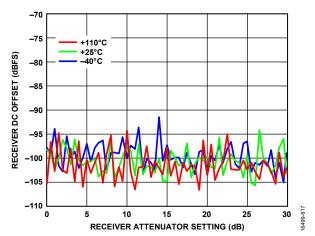

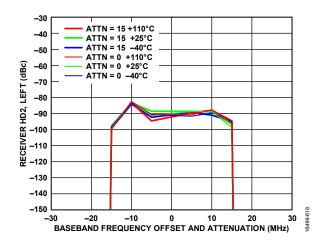

| 75 MHz to 525 MHz Band                                             | Fanout and Trace Space Guidelines                                      |

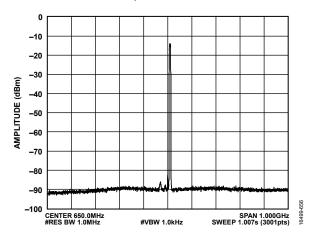

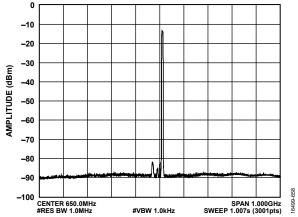

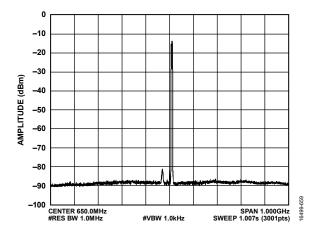

| 650 MHz to 3000 MHz Band                                           | Component Placement and Routing Guidelines                             |

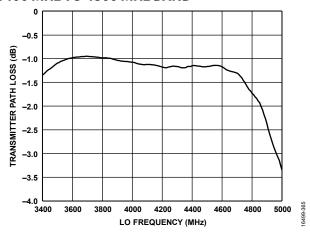

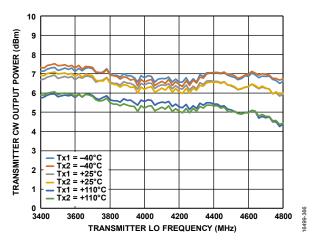

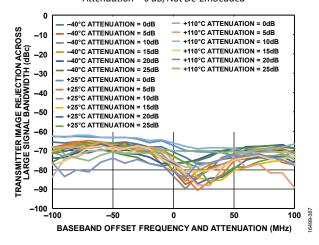

| 3400 MHz to 4800 MHz Band                                          | RF and JESD204B Transmission Line Layout                               |

|                                                                    |                                                                        |

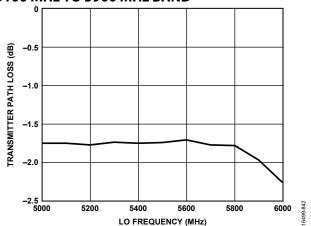

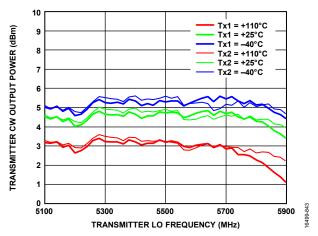

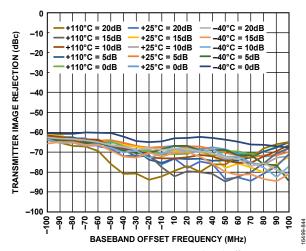

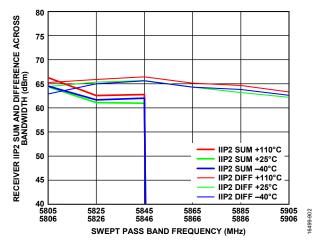

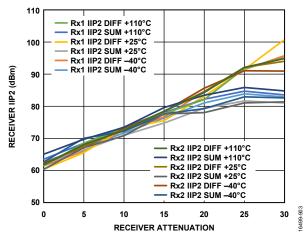

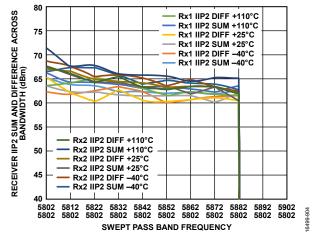

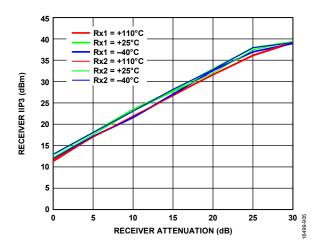

| 5100 MHz to 5900 MHz Band80                                        | Isolation Techniques Used on the ADRV9009-W/PCBZ 114                   |

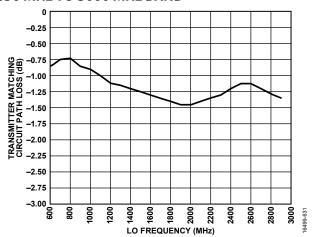

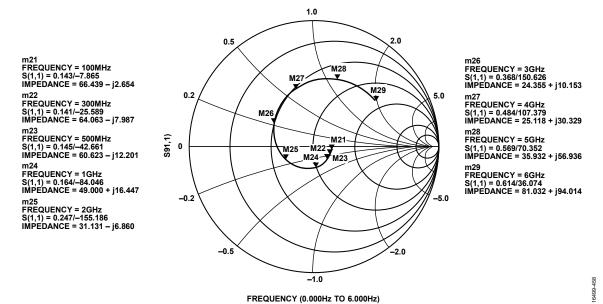

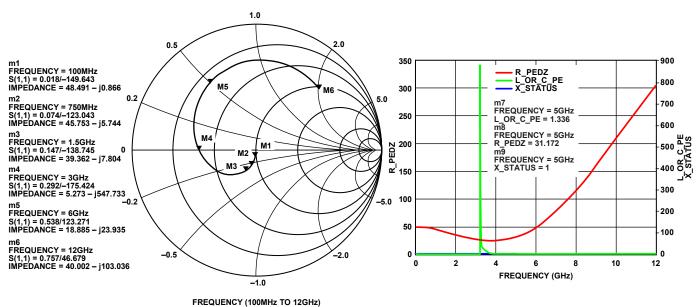

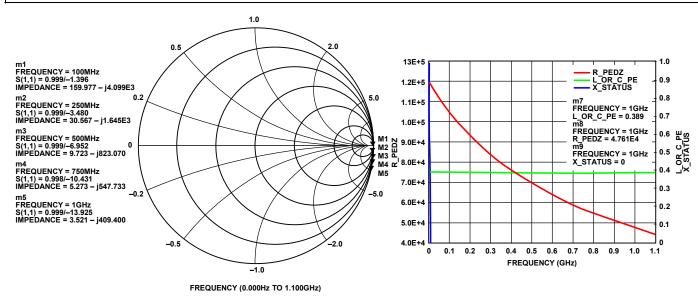

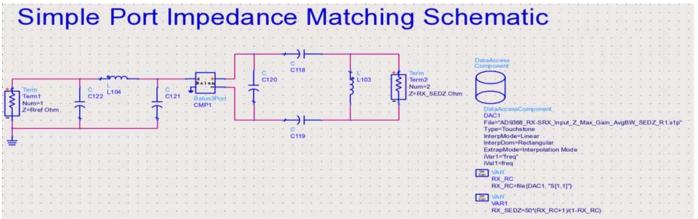

| Transmitter Output Impedance                                       | RF Port Interface Information                                          |

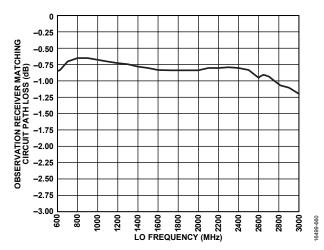

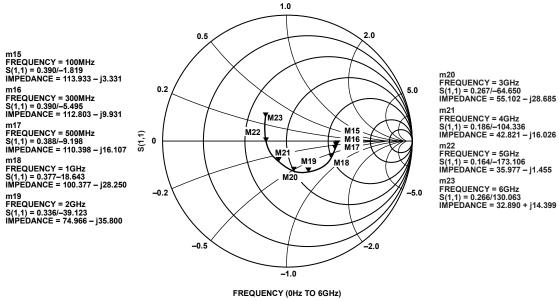

| Observation Receiver Input Impedance95                             | Outline Dimensions                                                     |

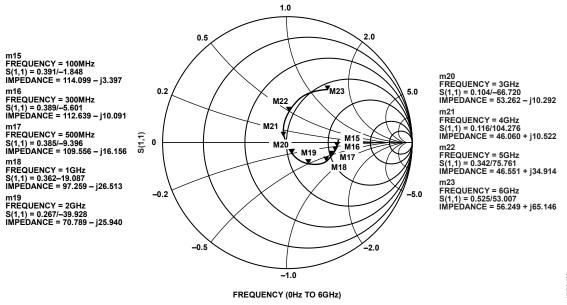

| Receiver Input Impedance96                                         | Ordering Guide                                                         |

| Terminology97                                                      |                                                                        |

| REVISION HISTORY                                                   |                                                                        |

| 5/2019—Rev. A to Rev B.                                            | Changes to Terminology Section97                                       |

| Replaced ADRV9009 Customer Card to                                 | Deleted Figure 432                                                     |

| ADRV9009-WPCBZThroughout                                           | Changes to Theory of Operation Section and Clock                       |

| Changes to Features Section1                                       | Input Section                                                          |

| Changes to Figure 14                                               | Changed Serial Peripheral Interface Section to SPI Section and         |

| Changes to Specifications Section and Table 15                     | AUX DAC_x Section to Auxiliary DAC x Section99                         |

| Change to Figure 2                                                 | Changes to Power Supply Sequence Section, GPIO_x Pins                  |

| Changes to Table 3 and Thermal Resistance Section                  | Section, Auxiliary DAC x Section, and JESD204B Data                    |

| Changes to 75 MHz to 525 MHz Band Section, Figures and             | Interface Section                                                      |

| Captions 23                                                        | Changes to Table 7 Title, Figure 430, and Figure 431                   |

| Deleted Figure 83 to Figure 85; Renumbered Sequentially 34         | Changes to Overview Section, PCB Material and Stackup                  |

| Added Figure 78, Figure 79, and Figure 80; Renumbered              | Selection Section, and Figure 432 Caption                              |

| Sequentially                                                       | Changes to Table 9 and Table 10                                        |

| Added Figure 90                                                    | Changes to Fanout and Trace Space Guidelines Section 103               |

| Added Figure 125 to Figure 127                                     | Changes to Signals with Highest Routing Priority Section and           |

| Changes to 650 MHz to 3000 MHz Band Section, Figures and           | Figure 434                                                             |

| Captions                                                           | Change to Signals with Second Pouting Priority Section and             |

| Changes to 3400 MHz to 4800 MHz Band Section, Figures and Captions | Changes to Signals with Second Routing Priority Section and Figure 436 |

| Changes to 5100 MHz to 5900 MHz Band Section, Figures and          | Changes to Figure 437                                                  |

| Captions80                                                         | Changes to Figure 437                                                  |

| Cap (101)                                                          | Changes to rigure 450                                                  |

| Changes to Signals with Lowest Routing Priority Section | and |

|---------------------------------------------------------|-----|

| Figure 439                                              | 109 |

| Changes to RF Routing Guidelines Section and            |     |

| Figure 440 Caption                                      | 110 |

| Change to Figure 441 Caption                            | 111 |

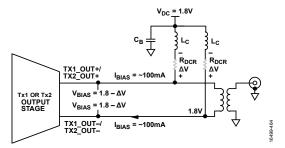

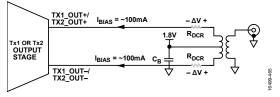

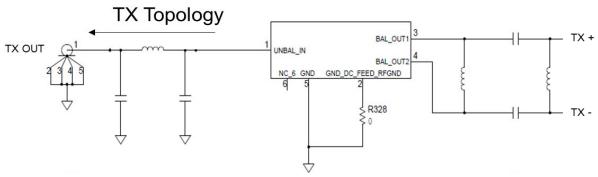

| Changes to Transmitter Balun DC Feed                    |     |

| Supplies Section                                        | 112 |

| Changes to Stripline Transmission Lines vs. Microstrip  |     |

| Transmission Lines Section                              | 113 |

| Moved Figure 444 to Isolation Techniques Used on the    |     |

| ADRV9009-W/PCBZ Section                                 | 114 |

| Moved Figure 446                                        | 115 |

| Changes to Isolation Between JESD204B Lines Section     |     |

| Changes to RF Port Interface Information Section        | 116 |

| Deleted KF Fort litterface Overview Section          | 1 1 / |

|------------------------------------------------------|-------|

| Changes to Figure 448 Caption                        | 117   |

| Moved Table 11                                       | 120   |

| Changes to Figure 456 Caption to Figure 459 Caption  | 121   |

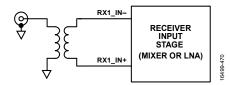

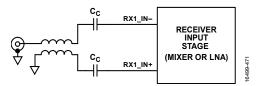

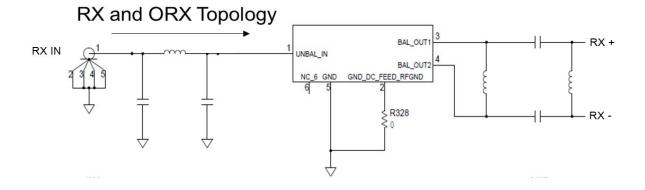

| Changes to General Receiver Path Interface Section   | 122   |

| Changes to Figure 463                                | 124   |

| Changes to Figure 464 and Figure 465                 | 125   |

| Deleted Endnote 1, Table 12 to Endnote 1, Table 15;  |       |

| Renumbered Sequentially, and Endnote 2, Table 16 and |       |

| Endnote 2, Table 17                                  | 126   |

| Changes to Table 15                                  | 126   |

|                                                      |       |

6/2018—Revision A: Initial Version

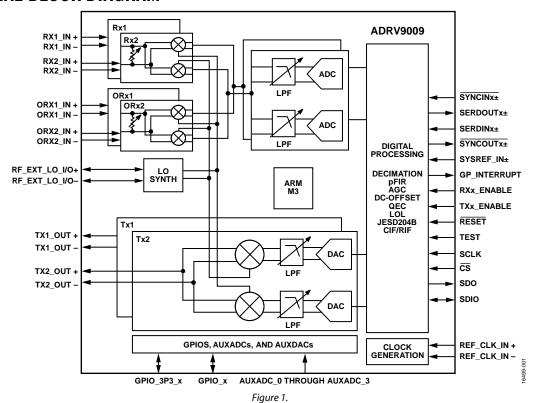

## **FUNCTIONAL BLOCK DIAGRAM**

## **SPECIFICATIONS**

Electrical characteristics at VDDA1P3 $^{1}$  = 1.3 V, VDDD1P3 $_{L}$ DIG = 1.3 V, VDDA1P8 $_{L}$ TX = 1.8 V, junction temperature ( $T_{L}$ ) = full operating temperature range. LO frequency ( $f_{LO}$ ) = 1800 MHz, unless otherwise noted. The specifications in Table 1 are not de-embedded. Refer to the Typical Performance Characteristics section for input and output circuit path loss. The device configuration profile for the 75 MHz to 525 MHz frequency range is as follows: receiver = 50 MHz bandwidth (inphase quadrature (IQ) rate = 61.44 MHz), transmitter = 50 MHz transmitter large signal bandwidth and 100 MHz transmitter synthesis bandwidth (IQ rate = 122.88 MHz), observation receiver = 100 MHz bandwidth (IQ rate = 122.88 MHz), JESD204B rate = 9.8304 GSPS, and device clock = 245.76 MHz. Unless otherwise specified, the device configuration for all other frequency ranges is as follows: receiver = 200 MHz bandwidth (IQ rate = 491.52 MHz), transmitter = 200 MHz transmitter large signal bandwidth and 450 MHz transmitter synthesis bandwidth (IQ rate = 491.52 MHz), observation receiver = 450 MHz bandwidth (IQ rate = 491.52 MHz), JESD204B rate = 9.8304 GSPS, and device clock = 245.76 MHz.

Table 1.

| Parameter                                                                  | Symbol                  | Min  | Тур  | Max  | Unit    | Test Conditions/Comments                                                                              |

|----------------------------------------------------------------------------|-------------------------|------|------|------|---------|-------------------------------------------------------------------------------------------------------|

| TRANSMITTERS                                                               |                         |      |      |      |         |                                                                                                       |

| Center Frequency                                                           |                         | 75   |      | 6000 | MHz     |                                                                                                       |

| Transmitter Synthesis<br>Bandwidth                                         |                         |      |      | 450  | MHz     |                                                                                                       |

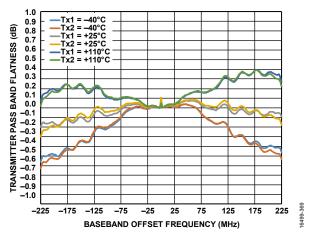

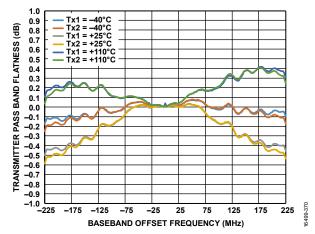

| Transmitter Large Signal<br>Bandwidth                                      |                         |      |      | 200  | MHz     |                                                                                                       |

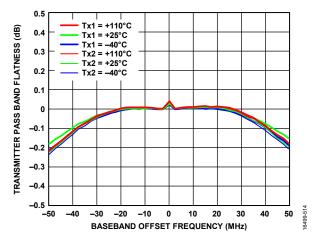

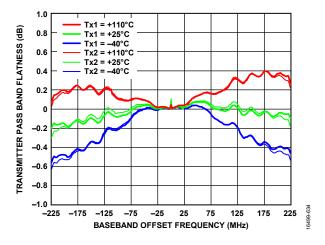

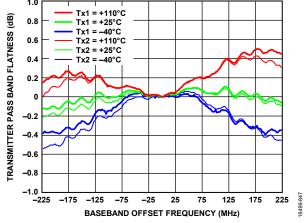

| Peak-to-Peak Gain<br>Deviation                                             |                         |      | 1.0  |      | dB      | 450 MHz bandwidth, compensated by programmable finite impulse response (FIR) filter                   |

| Gain Slope                                                                 |                         |      | ±0.1 |      | dB      | Any 20 MHz bandwidth span,<br>compensated by programmable FIR<br>filter                               |

| Deviation from Linear Phase                                                |                         |      | 1    |      | Degrees | 450 MHz bandwidth                                                                                     |

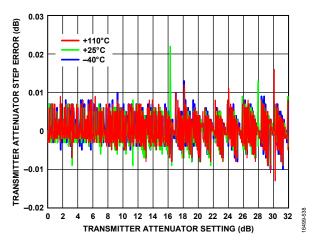

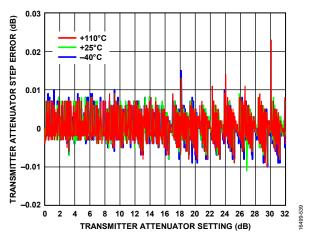

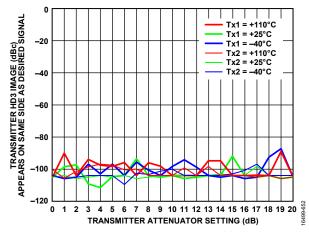

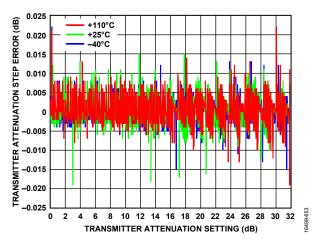

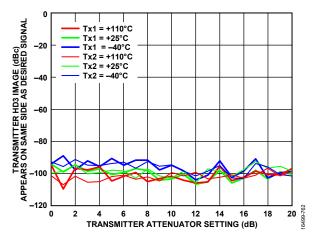

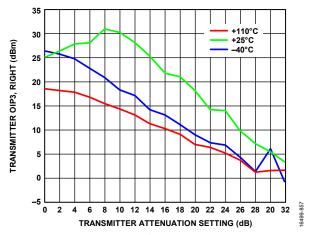

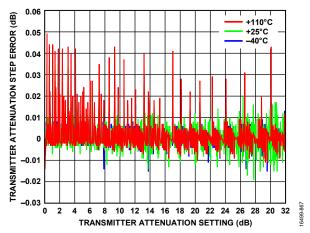

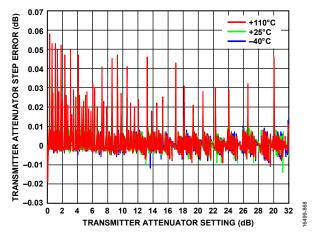

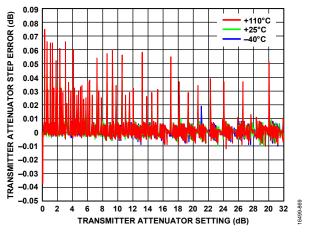

| Transmitter Attenuation<br>Power Control Range                             |                         | 0    |      | 32   | dB      | Signal-to-noise ratio (SNR) maintained for attenuation between 0 dB and 20 dB                         |

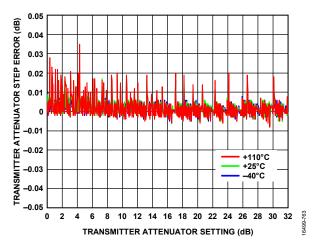

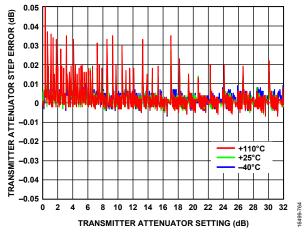

| Transmitter Attenuation Power Control Resolution                           |                         |      | 0.05 |      | dB      |                                                                                                       |

| Transmitter Attenuation<br>Integral Nonlinearity                           | INL                     |      | 0.1  |      | dB      | For any 4 dB step                                                                                     |

| Transmitter Attenuation Differential Nonlinearity                          | DNL                     |      | 0.04 |      | dB      | Monotonic                                                                                             |

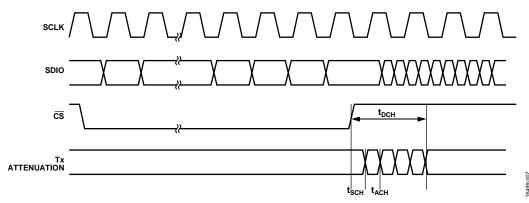

| Transmitter Attenuation<br>Serial Peripheral<br>Interface 2 (SPI 2) Timing |                         |      |      |      |         | See Figure 4                                                                                          |

| Time from CS Going High<br>to Change in Transmitter<br>Attenuation         | tscн                    | 19.5 |      | 24   | ns      |                                                                                                       |

| Time Between Consecutive<br>Microattenuation Steps                         | <b>t</b> ach            | 6.5  |      | 8.1  | ns      | A large change in attenuation can be broken up into a series of smaller attenuation changes           |

| Time Required to Reach<br>Final Attenuation Value                          | <b>t</b> <sub>DCH</sub> |      |      | 800  | ns      | Time required to complete the change in attenuation from start attenuation to final attenuation value |

| Maximum Attenuation<br>Overshoot During<br>Transition                      |                         | -1.0 |      | +0.5 | dB      |                                                                                                       |

| Change in Attenuation per<br>Microstep                                     |                         |      |      | 0.5  | dB      |                                                                                                       |

| Maximum Attenuation<br>Change when CS Goes<br>High                         |                         |      | 32   |      | dB      |                                                                                                       |

| Parameter                                                | Symbol | Min | Тур             | Max | Unit   | Test Conditions/Comments                                                                                                                                                                                           |

|----------------------------------------------------------|--------|-----|-----------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

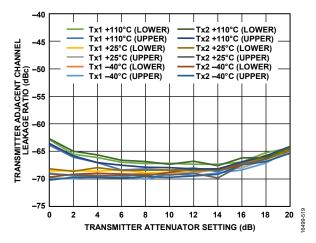

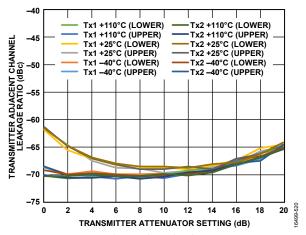

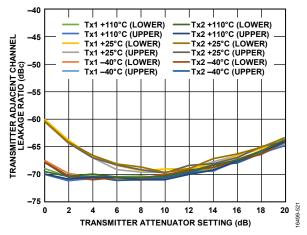

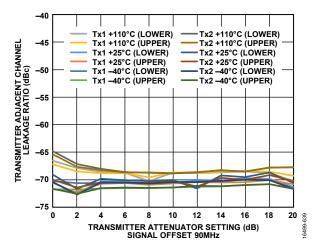

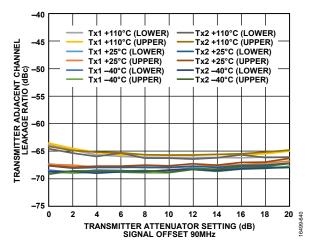

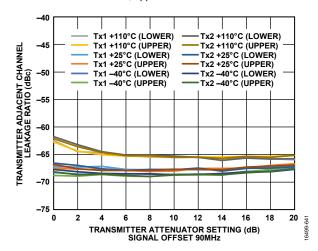

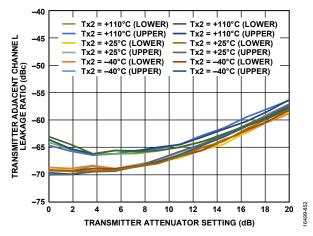

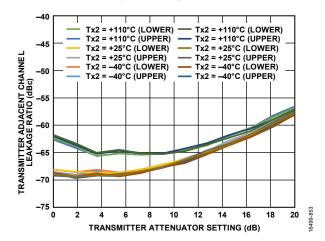

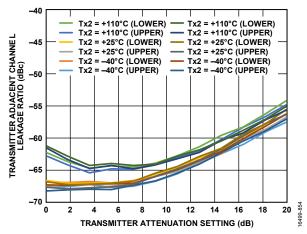

| Adjacent Channel Leakage                                 | ,      |     |                 |     |        | 20 MHz LTE at -12 dBFS                                                                                                                                                                                             |

| Ratio (ACLR) Long Term                                   |        |     |                 |     |        |                                                                                                                                                                                                                    |

| Evolution (LTE)                                          |        |     |                 |     |        |                                                                                                                                                                                                                    |

|                                                          |        |     | <del>-6</del> 7 |     | dB     | 75 MHz < f ≤ 2800 MHz                                                                                                                                                                                              |

|                                                          |        |     | -64             |     | dB     | 2800 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | -60             |     | dB     | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

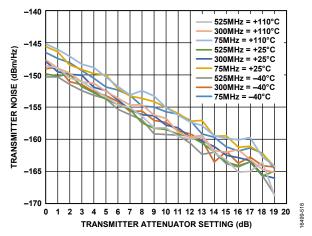

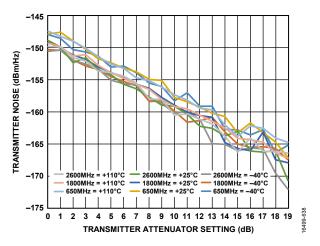

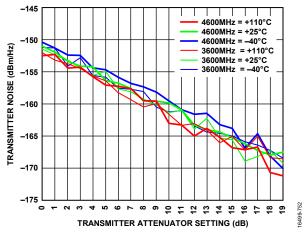

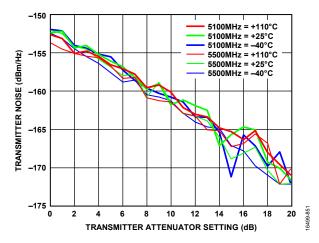

| In Band Noise Floor                                      |        |     |                 |     |        | 0 dB attenuation, in band noise falls<br>1 dB for each dB of attenuation for                                                                                                                                       |

|                                                          |        |     |                 |     |        | attenuation between 0 dB and 20 dB                                                                                                                                                                                 |

|                                                          |        |     | -147            |     | dBm/Hz | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | -148            |     | dBm/Hz | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                                             |

|                                                          |        |     | -149            |     | dBm/Hz | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | -150.5          |     | dBm/Hz | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

| Out of Band Noise Floor                                  |        |     |                 |     |        | 0 dB attenuation, $3 \times$ bandwidth/2 offset                                                                                                                                                                    |

|                                                          |        |     | -147            |     | dBm/Hz | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | -153            |     | dBm/Hz | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                                             |

|                                                          |        |     | -154            |     | dBm/Hz | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | -155.5          |     | dBm/Hz | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

| Interpolation Images                                     |        |     | -80             |     | dBc    | 1000 1111 12 11 2 0000 1111 12                                                                                                                                                                                     |

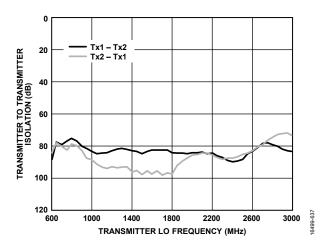

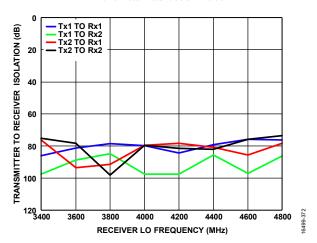

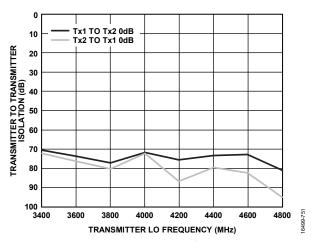

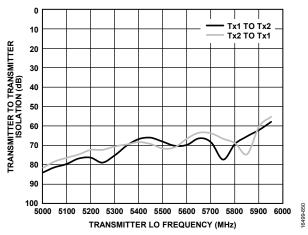

| Transmitter to Transmitter Isolation                     |        |     | 85              |     | dB     | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | 75              |     | dB     | 600 MHz < f ≤ 2800 MHz                                                                                                                                                                                             |

|                                                          |        |     | 70              |     | dB     | 2800 MHz < f < 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | 65              |     | dB     | 4800 MHz < f ≤ 5700 MHz                                                                                                                                                                                            |

|                                                          |        |     | 56              |     | dB     | 5700 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

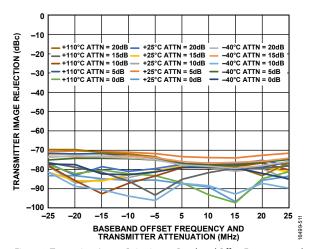

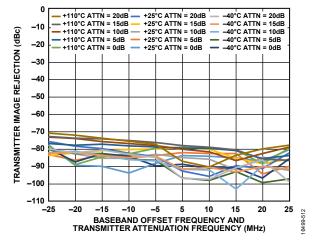

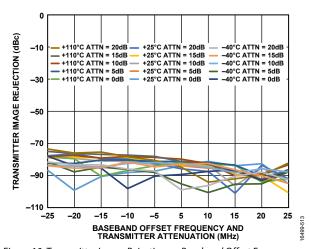

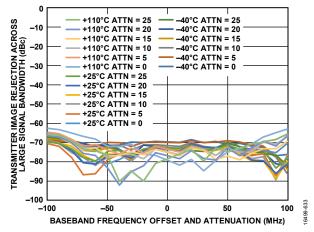

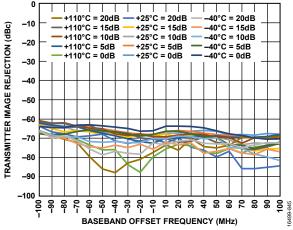

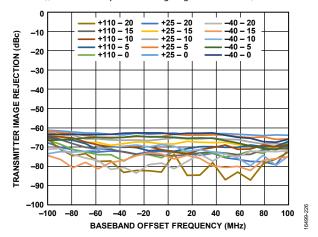

| Imaga Paiastian                                          |        |     | 30              |     | ub.    | 3700 WH 12 < 1 \le 0000 WH 12                                                                                                                                                                                      |

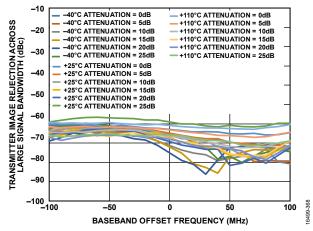

| Image Rejection<br>Within Large Signal<br>Bandwidth      |        |     |                 |     |        | QEC active                                                                                                                                                                                                         |

|                                                          |        |     | 70              |     | dB     | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | 65              |     | dB     | 600 MHz < f ≤ 4000 MHz                                                                                                                                                                                             |

|                                                          |        |     | 62              |     | dB     | 4000 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | 60              |     | dB     | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

| Beyond Large Signal<br>Bandwidth                         |        |     | 40              |     | dB     | Assumes that distortion power density is 25 dB below desired power density                                                                                                                                         |

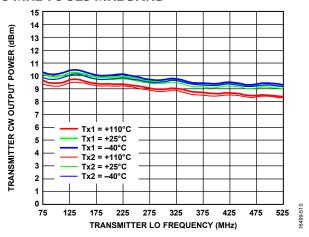

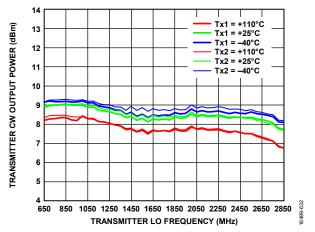

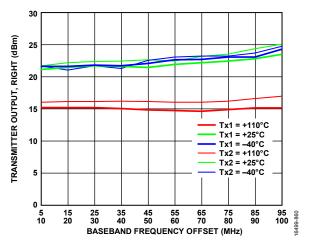

| Maximum Output Power                                     |        |     |                 |     |        | 0 dBFS, continuous wave (CW) tone into 50 $\Omega$ load, 0 dB transmitter attenuation                                                                                                                              |

|                                                          |        |     | 9               |     | dBm    | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | 7               |     | dBm    | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                                             |

|                                                          |        |     | 6               |     | dBm    | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

|                                                          |        |     | 4.5             |     | dBm    | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

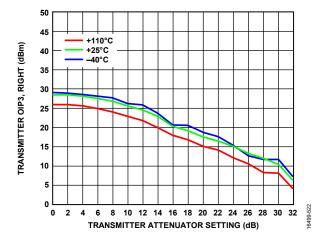

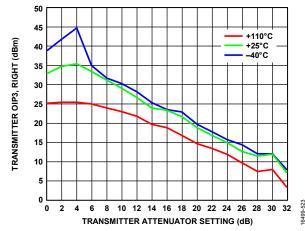

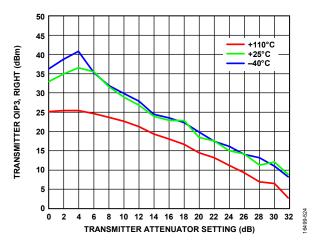

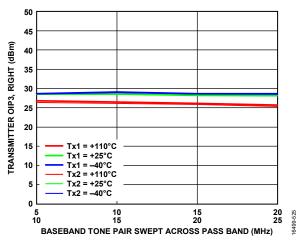

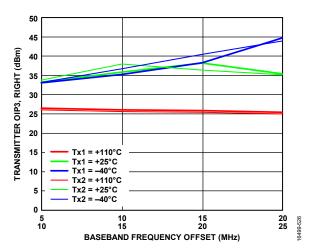

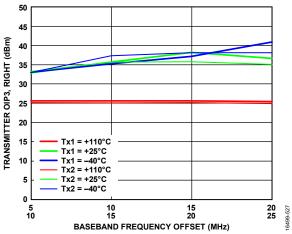

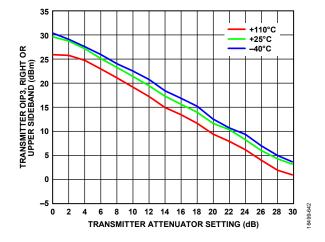

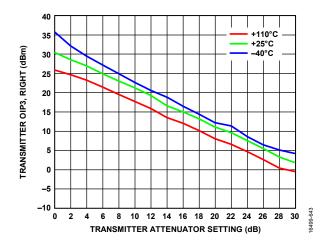

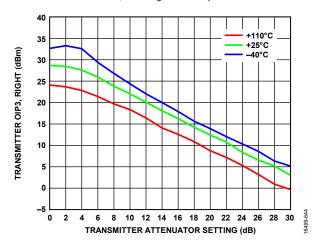

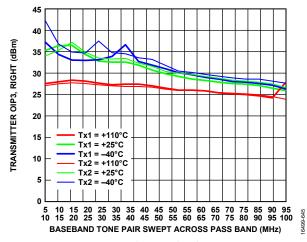

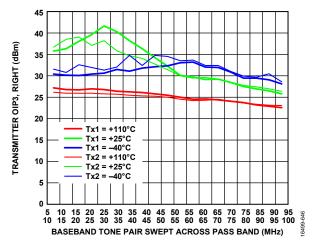

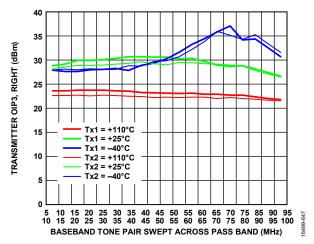

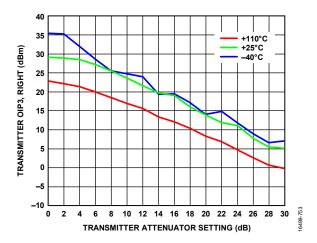

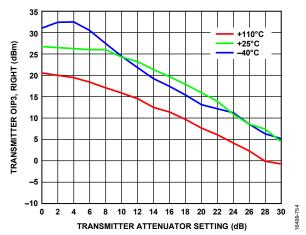

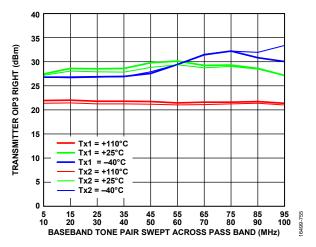

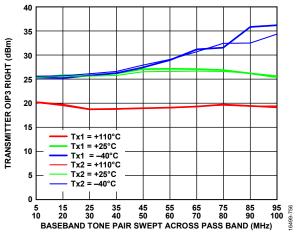

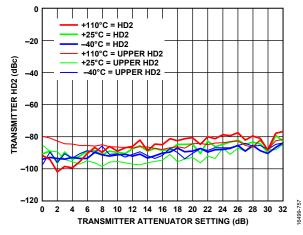

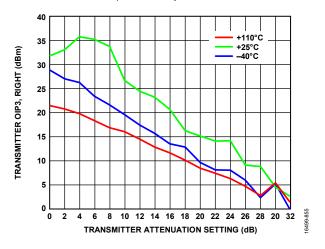

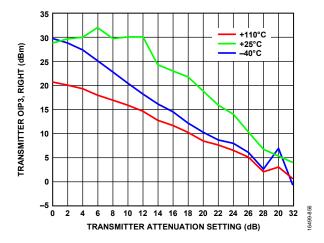

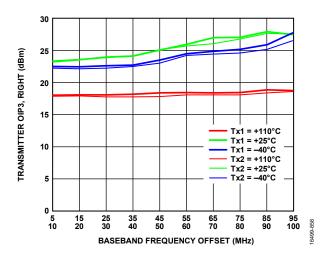

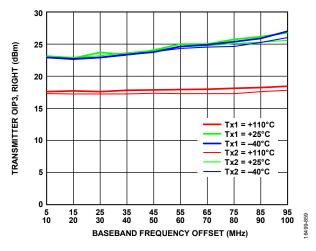

| Third-Order Output<br>Intermodulation<br>Intercept Point | OIP3   |     |                 |     |        | 0 dB transmitter attenuation                                                                                                                                                                                       |

| intercept i onit                                         |        |     | 29              |     | dBm    | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

|                                                          |        |     | 29<br>27        |     | dBm    | 600 MHz < f ≤ 4000 MHz                                                                                                                                                                                             |

|                                                          |        |     | 27              |     | dBm    | 4000 MHz < f ≤ 6000 MHz                                                                                                                                                                                            |

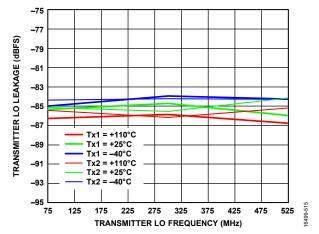

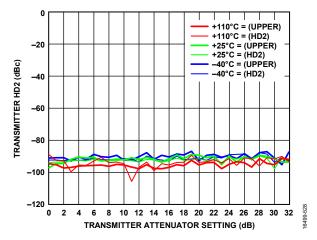

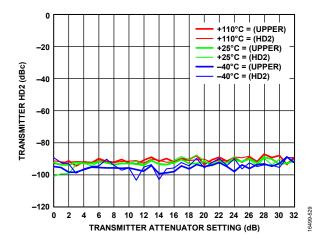

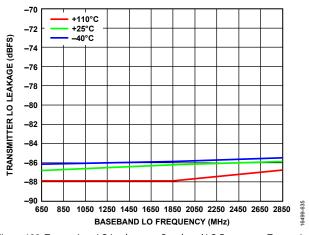

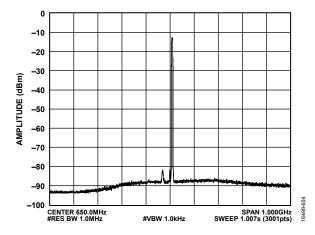

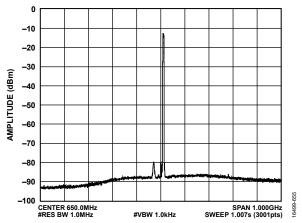

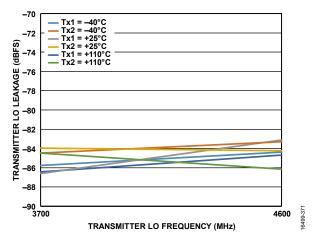

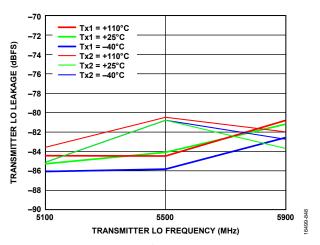

| Carrier Leakage                                          |        |     | 23              |     | авт    | With LO leakage correction active, 0 dB attenuation, scales decibel for decibel with attenuation, measured in 1 MHz bandwidth, resolution bandwidth and video bandwidth = 100 kHz, rms detector, 100 trace average |

| Carrier Offset from LO                                   |        |     | -84             |     | dBFS   | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                               |

| Carrier Offset IfOfff LO                                 |        |     | -84<br>-82      |     | dBFS   | 75 MHz < f ≤ 600 MHz<br>600 MHz < f ≤ 4800 MHz                                                                                                                                                                     |

|                                                          |        |     |                 |     | dBFS   | 4800 MHz < f ≤ 4800 MHz                                                                                                                                                                                            |

| Carrier and C                                            |        |     | -80<br>71       |     |        | 4000 IVI□Z < I ≤ 0000 IVI□Z                                                                                                                                                                                        |

| Carrier on LO                                            |        | 1   | <del>-</del> 71 |     | dBFS   |                                                                                                                                                                                                                    |

Rev. B | Page 6 of 127

| Parameter                                                          | Symbol            | Min | Тур   | Max  | Unit        | Test Conditions/Comments                                                                                                                                                                      |

|--------------------------------------------------------------------|-------------------|-----|-------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

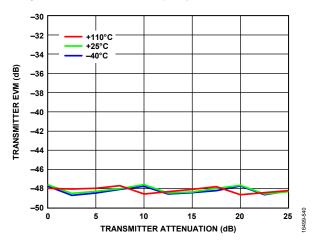

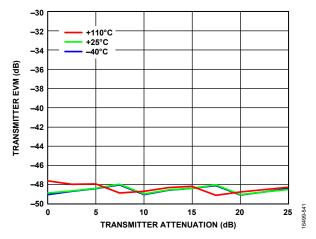

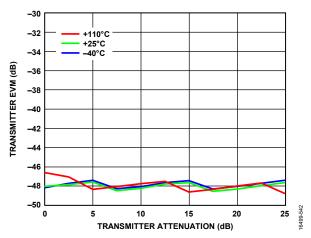

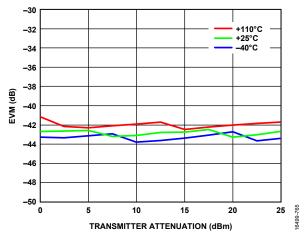

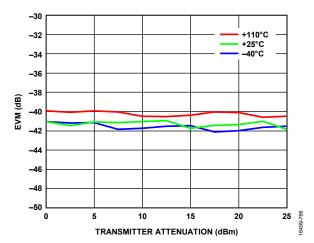

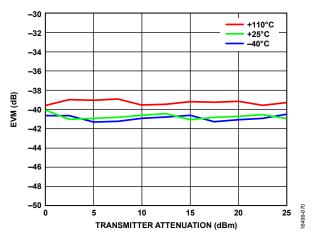

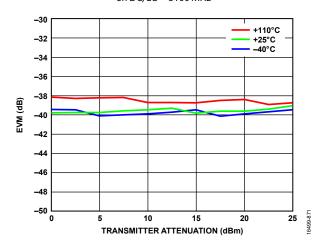

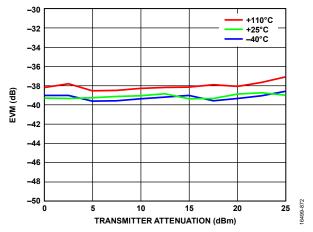

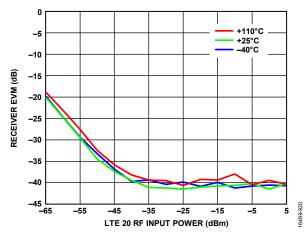

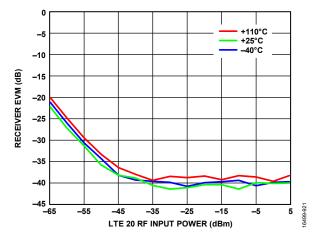

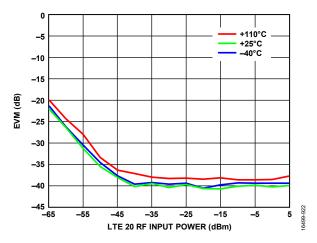

| Error Vector Magnitude<br>(Third Generation<br>Partnership Project | EVM               |     |       |      |             |                                                                                                                                                                                               |

| (3GPP) Test Signals)                                               |                   |     |       |      |             |                                                                                                                                                                                               |

| 75 MHz LO                                                          |                   |     | 0.5   |      | %           | 300 kHz RF PLL loop bandwidth, test equipment phase noise performance limited                                                                                                                 |

| 1900 MHz LO                                                        |                   |     | 0.7   |      | %           | 50 kHz RF PLL loop bandwidth                                                                                                                                                                  |

| 3800 MHz LO                                                        |                   |     | 0.7   |      | %           | 300 kHz RF PLL loop bandwidth                                                                                                                                                                 |

| 5900 MHz LO                                                        |                   |     | 1.1   |      | %           | 300 kHz RF PLL loop bandwidth                                                                                                                                                                 |

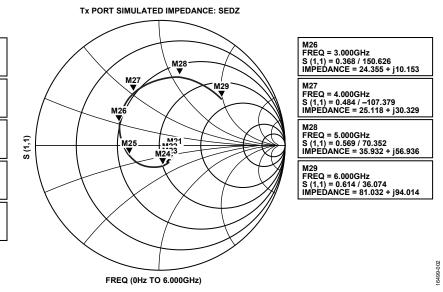

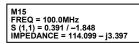

| Output Impedance                                                   | Zout              |     | 50    |      | Ω           | Differential (see Figure 427)                                                                                                                                                                 |

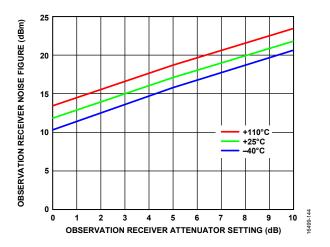

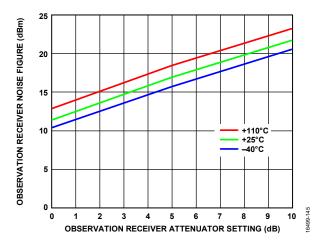

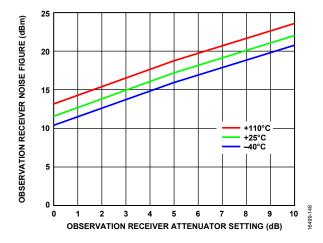

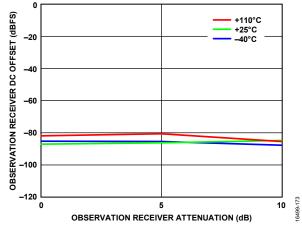

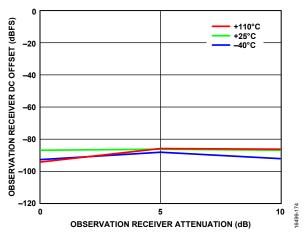

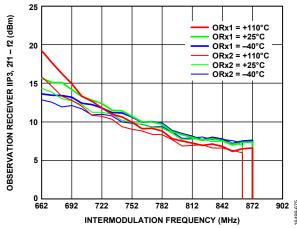

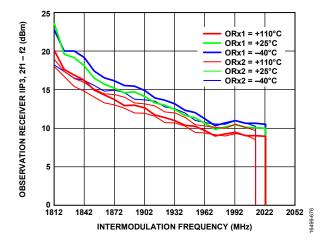

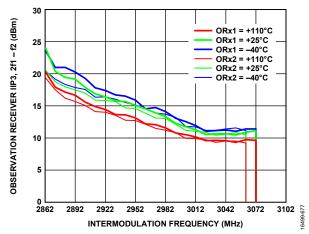

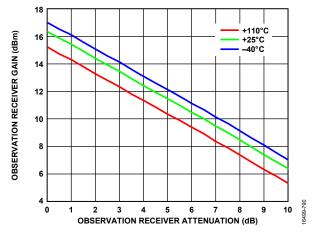

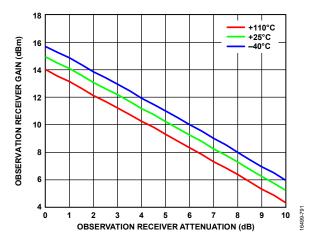

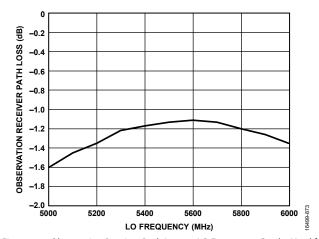

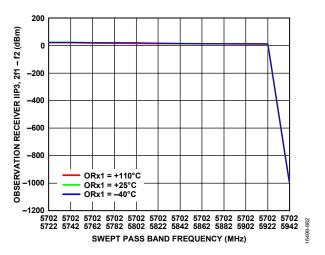

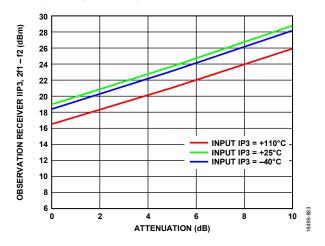

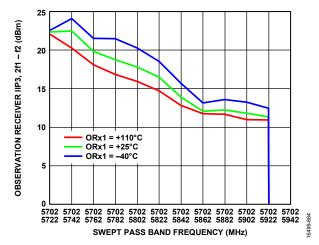

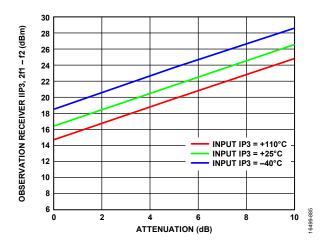

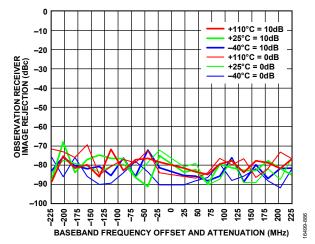

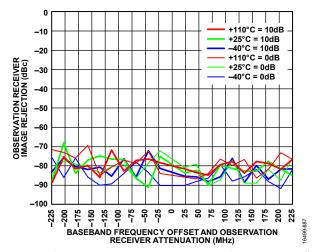

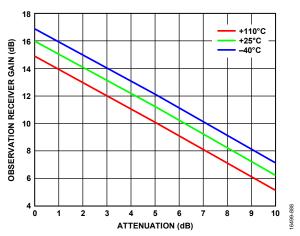

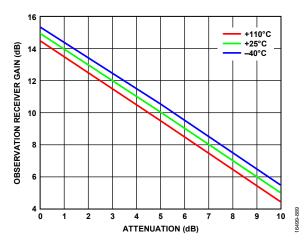

| OBSERVATION RECEIVER                                               | ORx               |     |       |      |             |                                                                                                                                                                                               |

| Center Frequency                                                   |                   | 75  |       | 6000 | MHz         |                                                                                                                                                                                               |

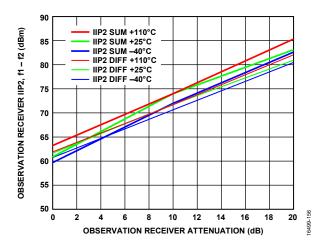

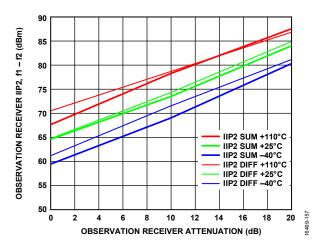

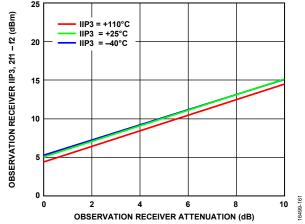

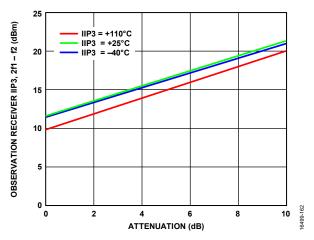

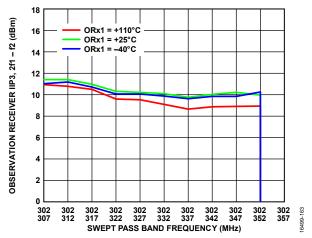

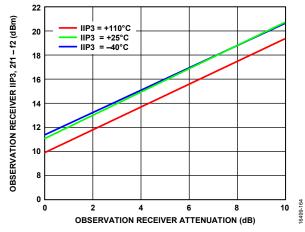

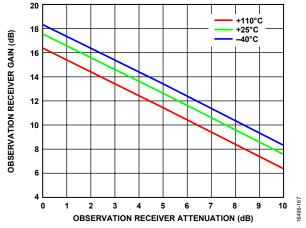

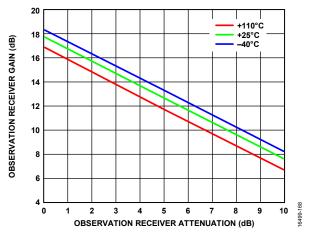

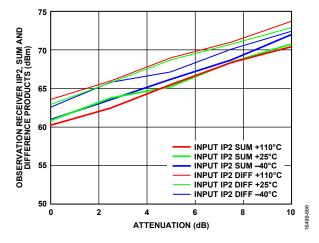

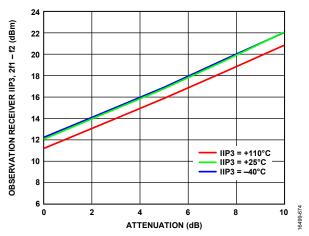

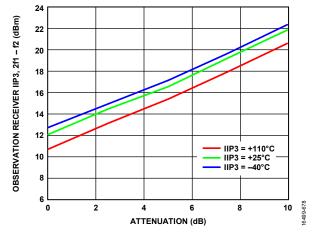

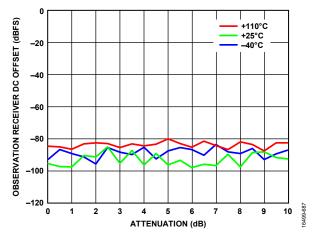

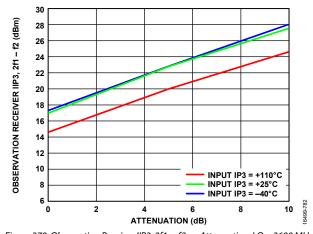

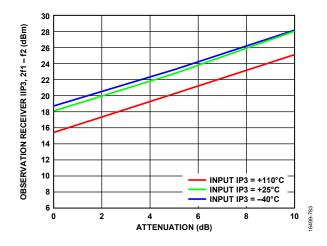

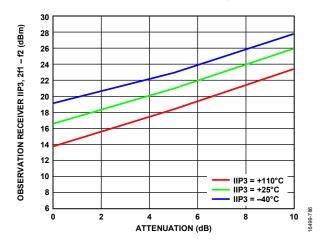

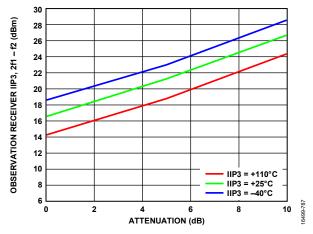

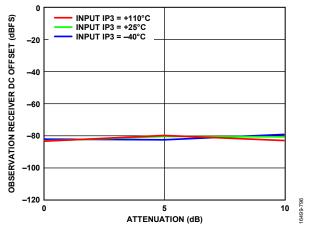

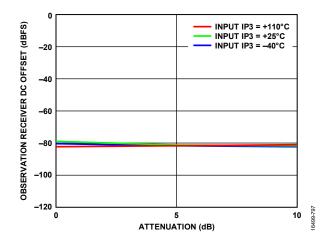

| Gain Range                                                         |                   |     | 30    |      | dB          | Third-order input intermodulation intercept point (IIP3) improves decibel for decibel for the first 18 dB of gain attenuation, QEC performance optimized for 0 dB to 6 dB of attenuation only |

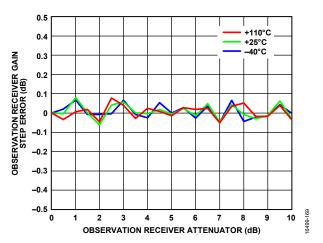

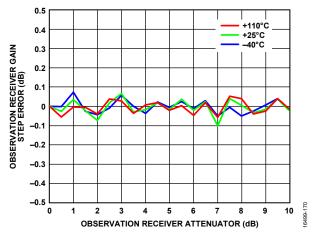

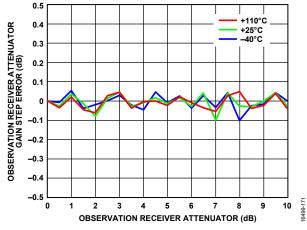

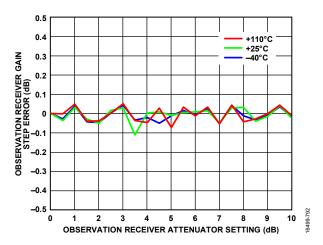

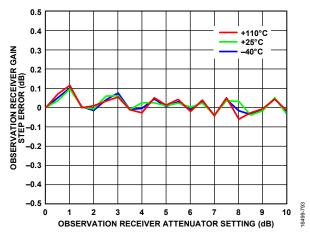

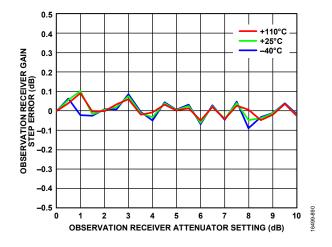

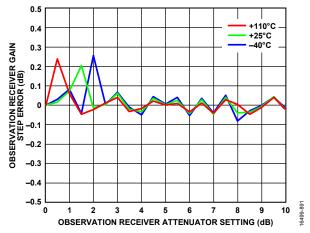

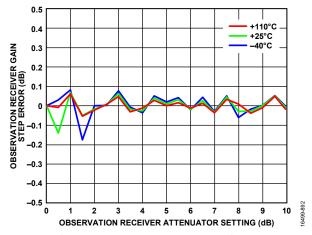

| Analog Gain Step                                                   |                   |     | 0.5   |      | dB          | For attenuator steps from 0 dB to 6 dB                                                                                                                                                        |

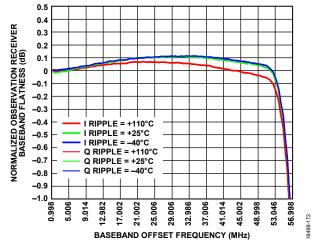

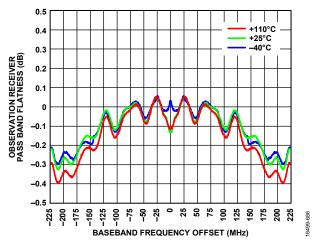

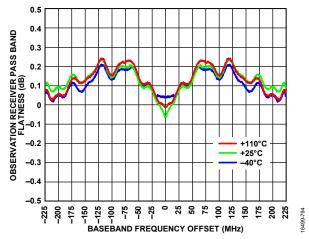

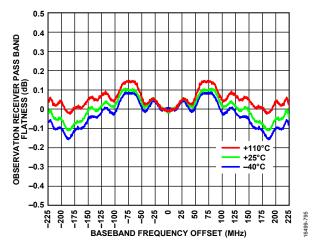

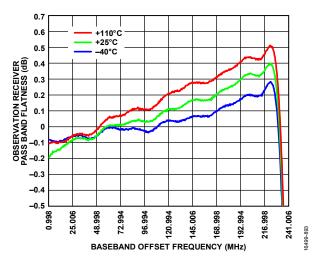

| Peak-to-Peak Gain<br>Deviation                                     |                   |     | 1     |      | dB          | 450 MHz bandwidth, compensated by programmable FIR filter                                                                                                                                     |

| Gain Slope                                                         |                   |     | ±0.1  |      | dB          | Any 20 MHz bandwidth span, compensated by programmable FIR filter                                                                                                                             |

| Deviation from Linear Phase                                        |                   |     | 1     |      | Degree<br>s | 450 MHz RF bandwidth                                                                                                                                                                          |

| Observation Receiver<br>Bandwidth                                  |                   |     |       | 450  | MHz         |                                                                                                                                                                                               |

| Observation Receiver Alias<br>Band Rejection                       |                   | 60  |       |      | dB          | Due to digital filters                                                                                                                                                                        |

| Maximum Useable Input<br>Level                                     | P <sub>HIGH</sub> |     |       |      |             | 0 dB attenuation, increases decibel for decibel with attenuation, CW corresponds to –1 dBFS at ADC                                                                                            |

|                                                                    |                   |     | -11   |      | dBm         | 75 MHz < f ≤ 3000 MHz                                                                                                                                                                         |

|                                                                    |                   |     | -9.5  |      | dBm         | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                       |

|                                                                    |                   |     | -8    |      | dBm         | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                       |

| Integrated Noise                                                   |                   |     | -58.5 |      | dBFS        | 450 MHz integration bandwidth                                                                                                                                                                 |

| 3                                                                  |                   |     | -57.5 |      | dBFS        | 491.52 MHz integration bandwidth                                                                                                                                                              |

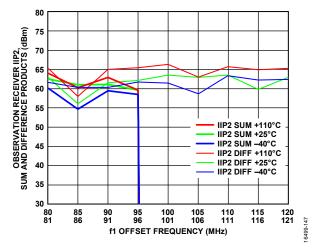

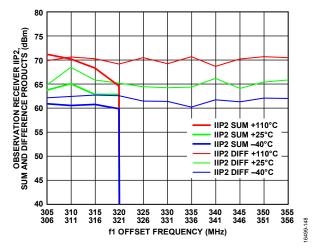

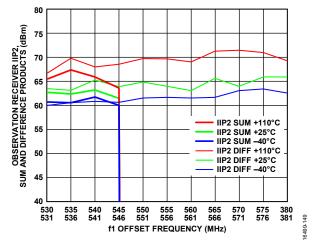

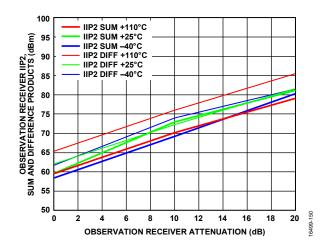

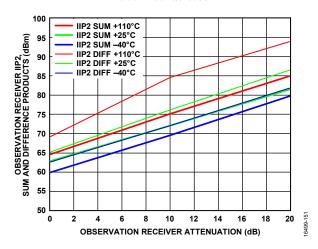

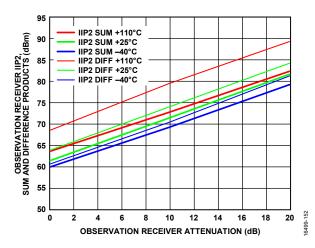

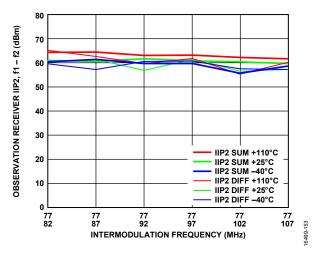

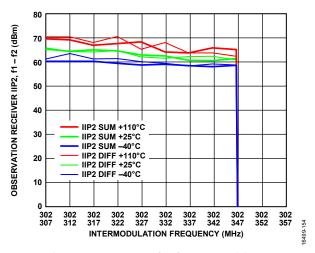

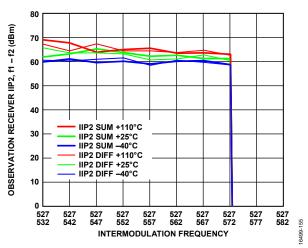

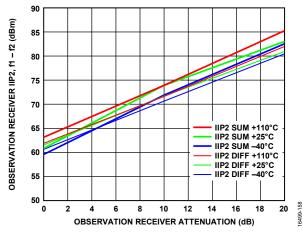

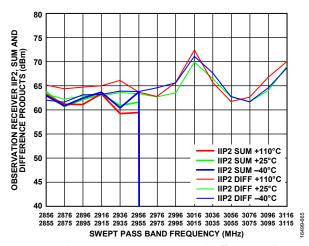

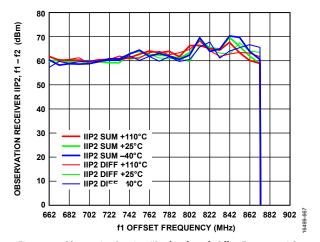

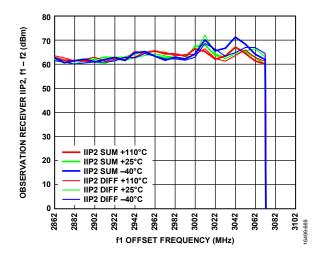

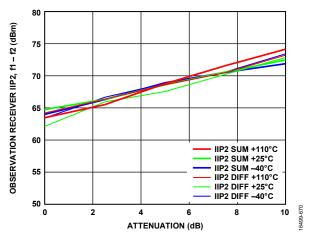

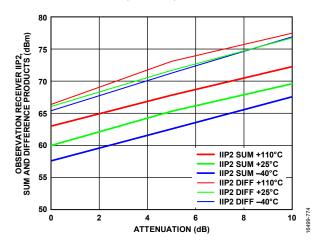

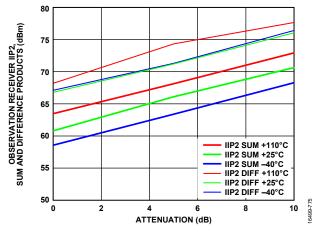

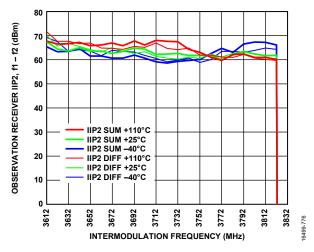

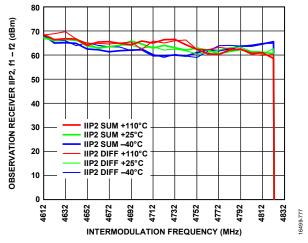

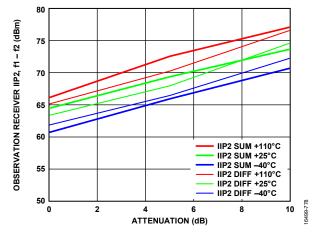

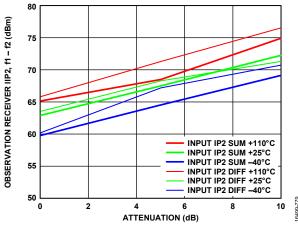

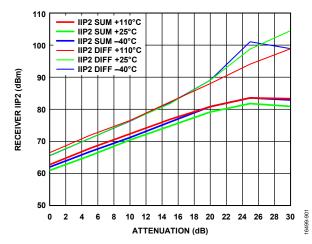

| Second-Order Input<br>Intermodulation<br>Intercept Point           | IIP2              |     | 62    |      | dBm         | Maximum observation receiver gain, ( $P_{HIGH}$ − 14 dB) per tone (see the Terminology section), 75 MHz < f ≤ 600 MHz                                                                         |

|                                                                    |                   |     | 62    |      | dBm         | Maximum observation receiver gain, $(P_{HIGH}-8\ dB)$ per tone (see the Terminology section), 600 MHz $< f \le 3000\ MHz$                                                                     |

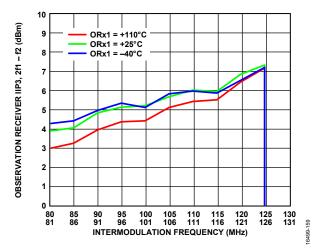

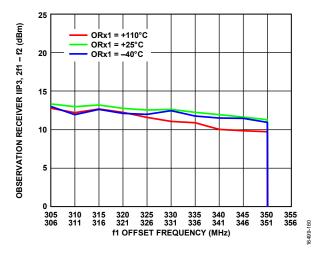

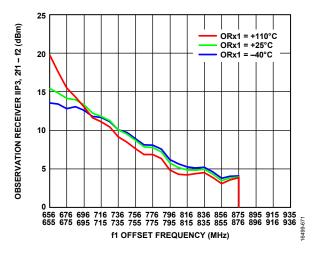

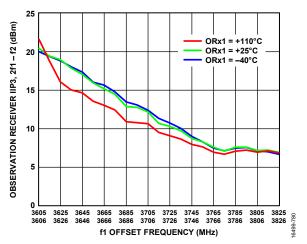

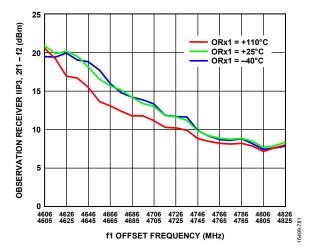

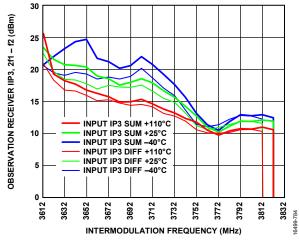

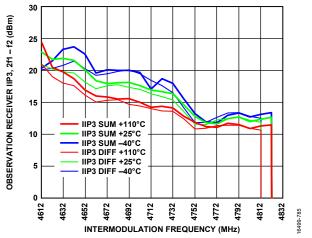

| Third-Order Input Intermodulation                                  | IIP3              |     |       |      |             |                                                                                                                                                                                               |

| Intercept Point<br>Narrow Band                                     |                   |     | 4     |      | dBm         | 75 MHz $<$ f $\le$ 300 MHz, test condition:<br>(P <sub>HIGH</sub> $-$ 14) dB per tone                                                                                                         |

|                                                                    |                   |     | 11    |      | dBm         | 300 MHz $<$ f $\le$ 600 MHz, (P <sub>HIGH</sub> $-$ 14) dB per tone                                                                                                                           |

|                                                                    |                   |     |       |      |             | Third-order intermodulation product (IM3) product < 130 MHz at baseband, (P <sub>HIGH</sub> – 8) dB per tone                                                                                  |

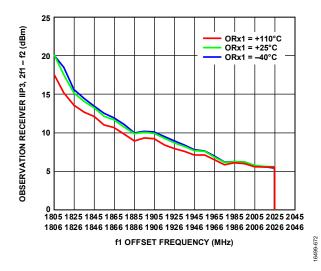

|                                                                    |                   |     | 12    |      | dBm         | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                        |

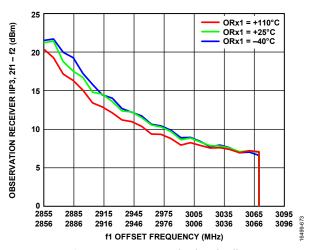

|                                                                    |                   |     | 12    |      | dBm         | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                       |

|                                                                    |                   |     | 11    |      | dBm         | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                                       |

Rev. B | Page 7 of 127

| Parameter                                                                                                     | Symbol | Min Typ | Max  | Unit | Test Conditions/Comments                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------|--------|---------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wide Band                                                                                                     |        |         |      |      |                                                                                                                                                                                 |

|                                                                                                               |        | 7       |      | dBm  | 600 MHz < f ≤ 3000 MHz                                                                                                                                                          |

|                                                                                                               |        | 7       |      | dBm  | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                         |

|                                                                                                               |        | 6       |      | dBm  | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                         |

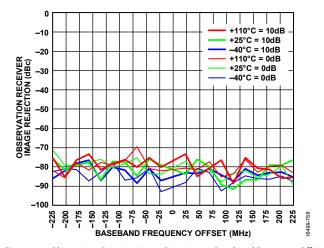

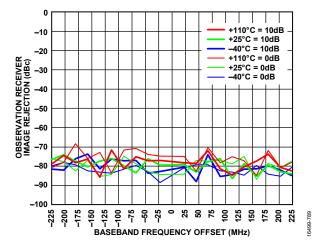

| Third-Order Intermodulation<br>Product                                                                        | IM3    |         |      |      | IM3 product < 130 MHz at baseband,<br>two tones, each at (P <sub>HIGH</sub> – 12) dB                                                                                            |

|                                                                                                               |        | -70     |      | dBc  | 600 MHz < f ≤ 3000 MHz                                                                                                                                                          |

|                                                                                                               |        | -67     |      | dBc  | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                         |

|                                                                                                               |        | -62     |      | dBc  | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                         |

| Fifth-Order Intermodulation<br>Product (1800 MHz)                                                             | IM5    | -80     |      | dBc  | IM5 product $<$ 50 MHz at baseband,<br>two tones, each at ( $P_{HIGH} - 12$ ) dB,<br>600 MHz $<$ f $\le$ 6000 MHz                                                               |

| Seventh-Order<br>Intermodulation Product<br>(1800 MHz)                                                        | IM7    | -80     |      | dBc  | IM7 product $<$ 50 MHz at baseband,<br>two tones, each at ( $P_{HIGH} - 12$ ) dB,<br>600 MHz $<$ f $\le$ 6000 MHz                                                               |

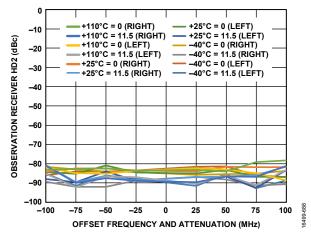

| Spurious-Free Dynamic<br>Range                                                                                | SFDR   | 70      |      | dB   | Non IMx related spurs, does not include HDx, $(P_{HIGH} - 9)$ dB input signal, 600 MHz $< f \le 6000$ MHz                                                                       |

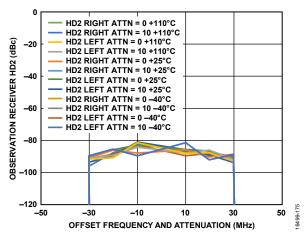

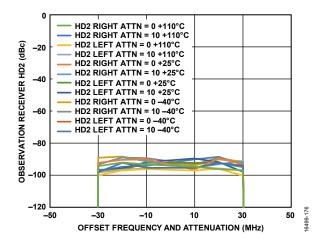

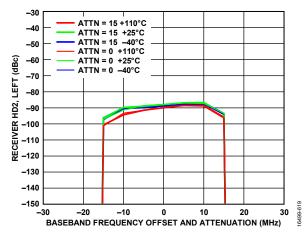

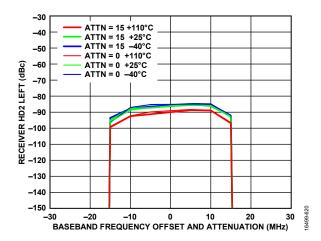

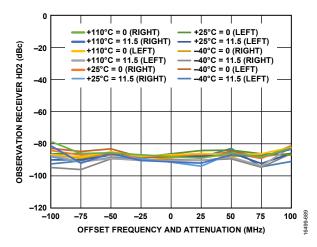

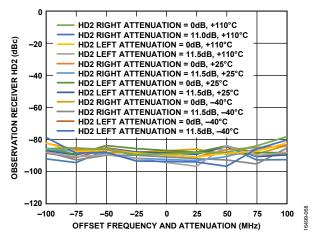

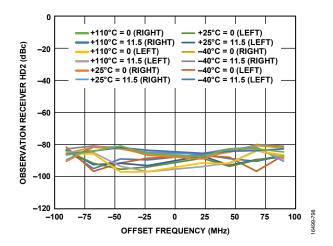

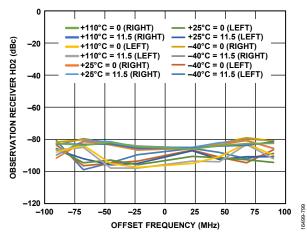

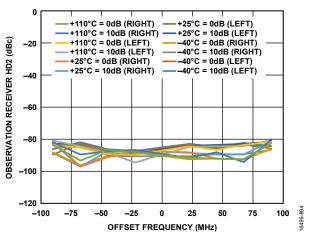

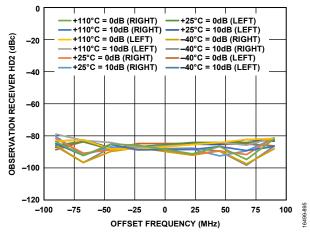

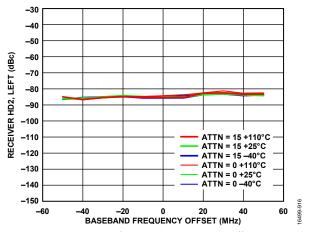

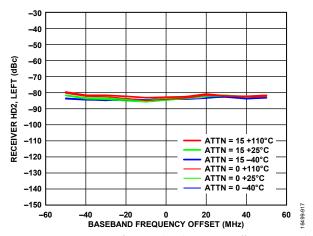

| Harmonic Distortion                                                                                           |        |         |      |      | (Р <sub>нібн</sub> — 11) dB input signal                                                                                                                                        |

| Second-Order Harmonic<br>Distortion Product                                                                   | HD2    | -80     |      | dBc  | $(P_{HIGH}-11)$ dB input signal 75 MHz $<$ f $\le$ 600 MHz, $(P_{HIGH}-9)$ dB input signal 600 MHz $<$ f $\le$ 6000 MHz, in band harmonic distortion falls within $\pm$ 100 MHz |

|                                                                                                               |        | -80     |      | dBc  | Out of band harmonic distortion falls within ±225 MHz                                                                                                                           |

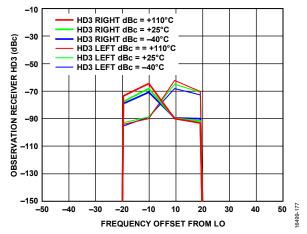

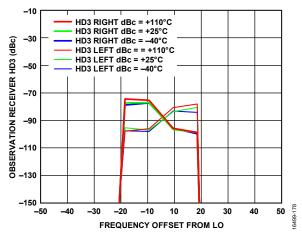

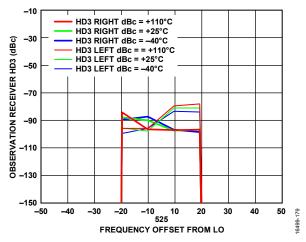

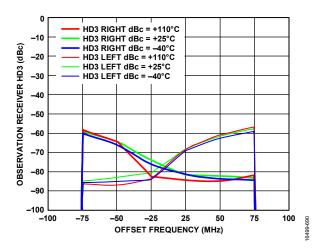

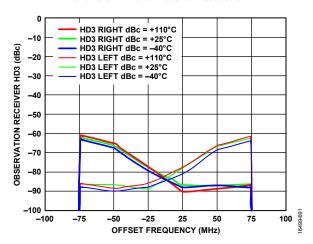

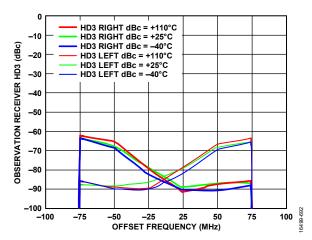

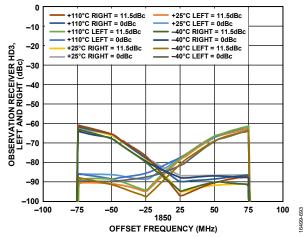

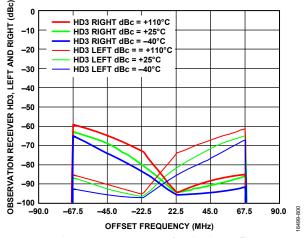

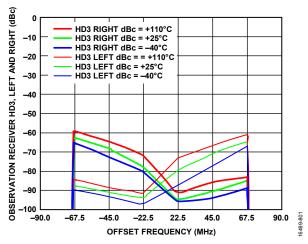

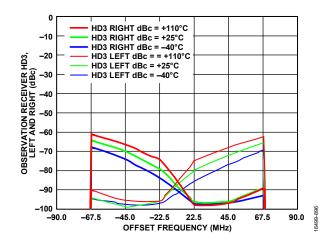

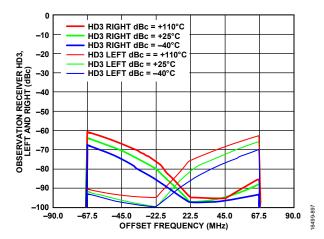

| Third-Order Harmonic<br>Distortion Product                                                                    | HD3    | -70     |      | dBc  | In band harmonic distortion falls within ±100 MHz                                                                                                                               |

|                                                                                                               |        | -60     |      | dBc  | Out of band harmonic distortion falls within ±225 MHz                                                                                                                           |

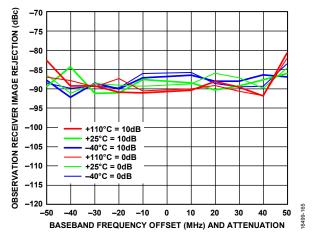

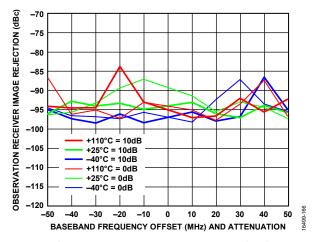

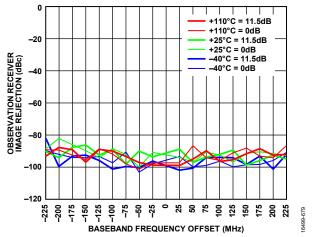

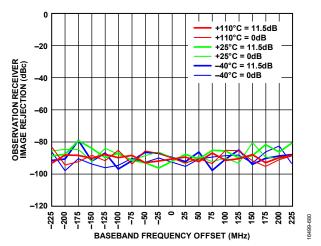

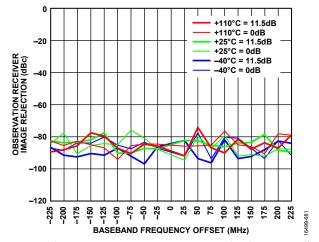

| Image Rejection<br>Within Large Signal                                                                        |        | 65      |      | dB   | QEC active                                                                                                                                                                      |

| Bandwidth Outside Large Signal                                                                                |        | 55      |      | dB   |                                                                                                                                                                                 |

| Bandwidth                                                                                                     |        | 100     |      | 0    | D:ff                                                                                                                                                                            |

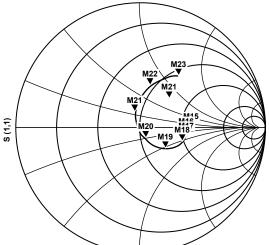

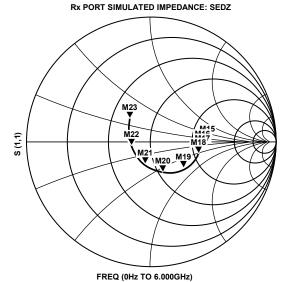

| Input Impedance<br>Isolation                                                                                  |        | 100     |      | Ω    | Differential (see Figure 428)                                                                                                                                                   |

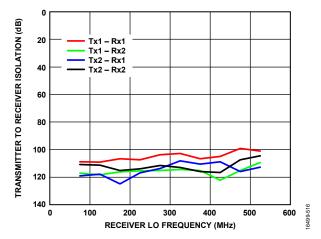

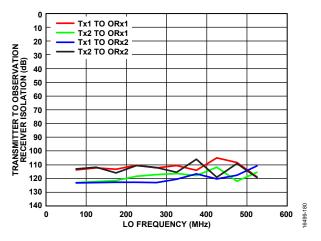

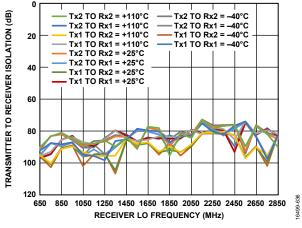

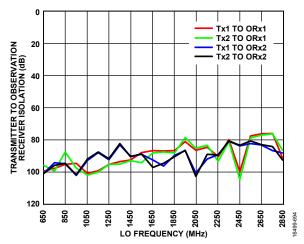

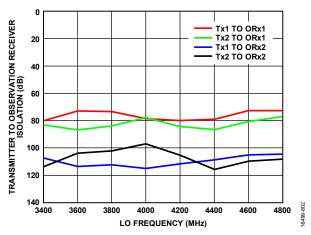

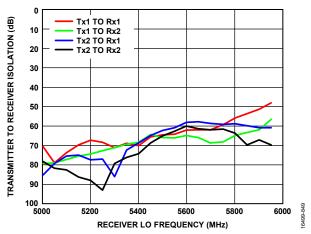

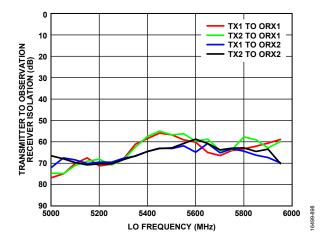

| Transmitter 1 (Tx1) to Observation Receiver 1 (ORx1) and Transmitter 2 (Tx2) to Observation Receiver 2 (ORx2) |        | 100     |      | dB   | 75 MHz < f ≤ 600 MHz                                                                                                                                                            |

|                                                                                                               |        | 65      |      | dB   | 600 MHz < f ≤ 5300 MHz                                                                                                                                                          |

|                                                                                                               |        | 55      |      | dB   | 5300 MHz < f ≤ 6000 MHz                                                                                                                                                         |

| Tx1 to ORx2 and Tx2 to ORx1                                                                                   |        | 105     |      | dB   | 75 MHz < f ≤ 600 MHz                                                                                                                                                            |

|                                                                                                               |        | 65      |      | dB   | 600 MHz < f ≤ 5300 MHz                                                                                                                                                          |

|                                                                                                               |        | 55      |      | dB   | 5300 MHz < f ≤ 6000 MHz                                                                                                                                                         |

| RECEIVERS                                                                                                     |        |         |      |      |                                                                                                                                                                                 |

| Center Frequency                                                                                              |        | 75      | 6000 | MHz  |                                                                                                                                                                                 |

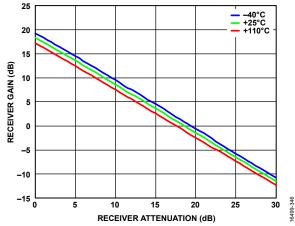

| Gain Range                                                                                                    |        | 30      |      | dB   |                                                                                                                                                                                 |

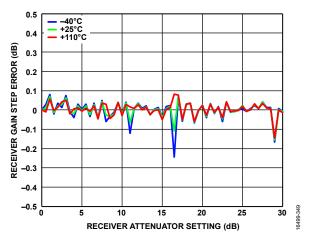

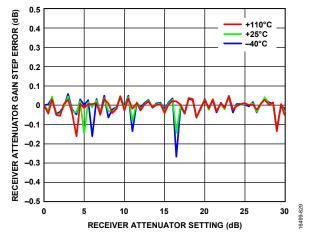

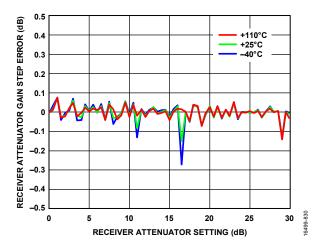

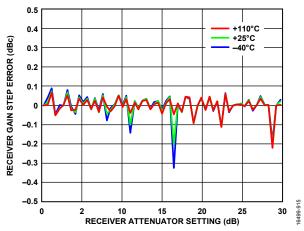

| Analog Gain Step                                                                                              |        | 0.5     |      | dB   | Attenuator steps from 0 dB to 6 dB                                                                                                                                              |

|                                                                                                               |        | 1       |      | dB   | Attenuator steps from 6 dB to 30 dB                                                                                                                                             |

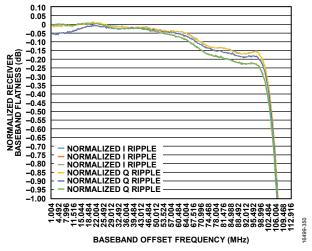

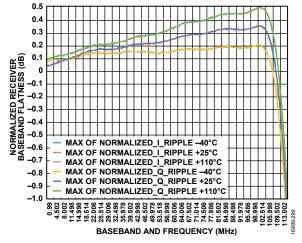

| Bandwidth Ripple                                                                                              |        | ±0.5    |      | dB   | 200 MHz bandwidth, compensated by programmable FIR filter                                                                                                                       |

|                                                                                                               |        | ±0.2    |      | dB   | Any 20 MHz bandwidth span, compensated by programmable FIR filter                                                                                                               |

| arameter                                                         | Symbol | Min 1 | Тур        | Max | Unit | Test Conditions/Comments                                                                                                                                                              |

|------------------------------------------------------------------|--------|-------|------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

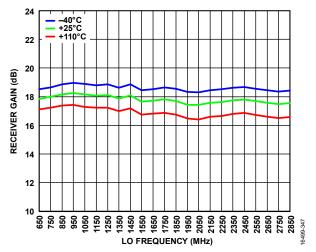

| Receiver Bandwidth                                               |        |       |            | 200 | MHz  |                                                                                                                                                                                       |

| Receiver Alias Band<br>Rejection                                 |        | 80    |            |     | dB   | Due to digital filters                                                                                                                                                                |

| Maximum Useable Input<br>Level                                   | Рнібн  |       |            |     |      | 0 dB attenuation, increases decibel for decibel with attenuation, CW = 1800 MHz, corresponds to -1 dBFS at ADC                                                                        |

|                                                                  |        | -     | -11        |     | dBm  | 75 MHz < f ≤ 3000 MHz                                                                                                                                                                 |

|                                                                  |        | -     | -10.2      |     | dBm  | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                               |

|                                                                  |        | -     | -9.5       |     | dBm  | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                               |

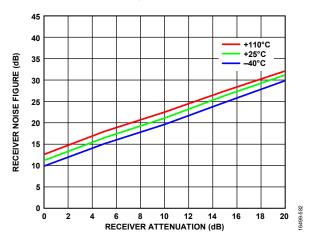

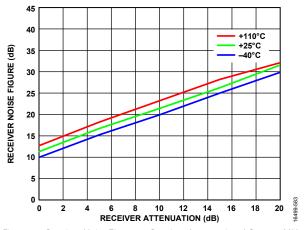

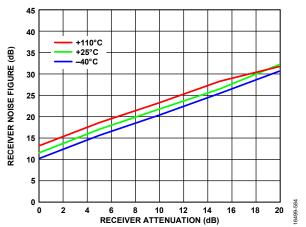

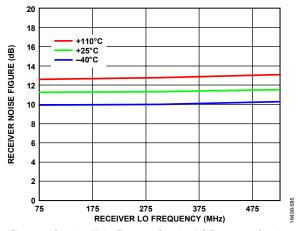

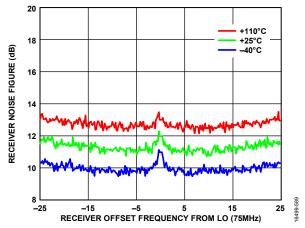

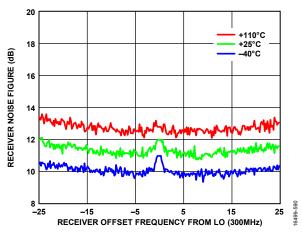

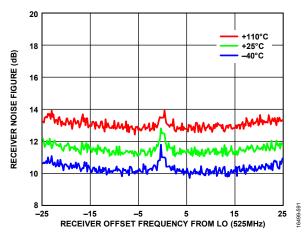

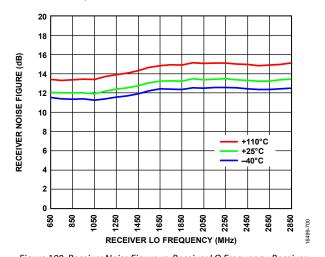

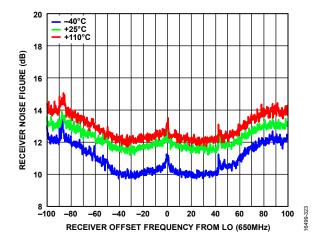

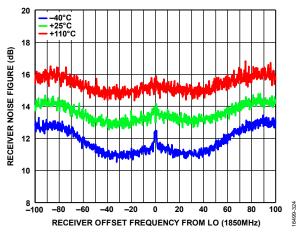

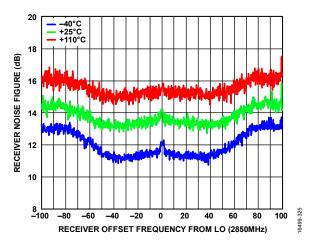

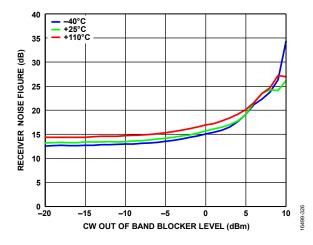

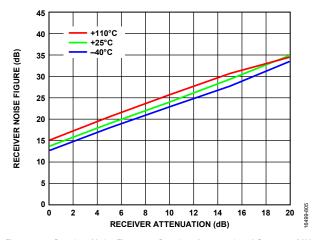

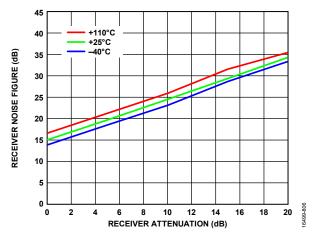

| Noise Figure                                                     | NF     |       |            |     |      | 0 dB attenuation, at receiver port                                                                                                                                                    |

|                                                                  |        | 1     | 11.5       |     | dB   | 75 MHz < f ≤ 600 MHz                                                                                                                                                                  |

|                                                                  |        | 1     | 12         |     | dB   | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                |

|                                                                  |        | 1     | 13         |     | dB   | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                               |

|                                                                  |        | 1     | 15.2       |     | dB   | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                               |

| Ripple                                                           |        | 1     | 1.8        |     | dB   | At band edge maximum bandwidth mode                                                                                                                                                   |

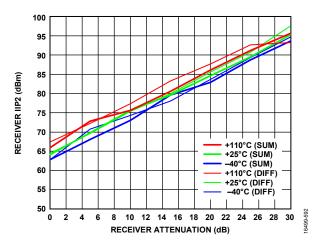

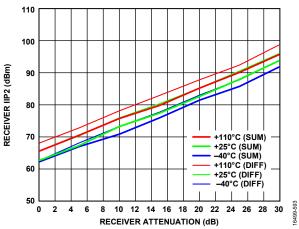

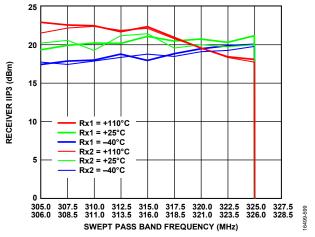

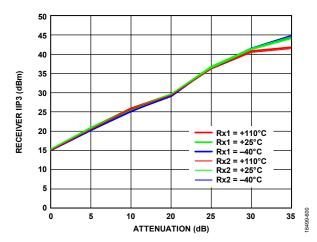

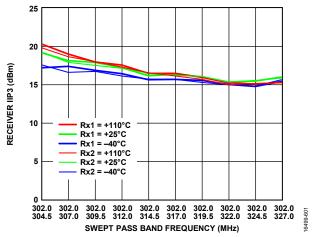

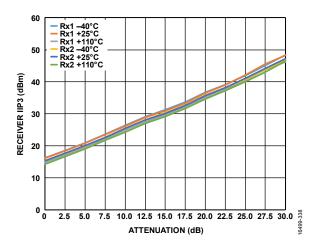

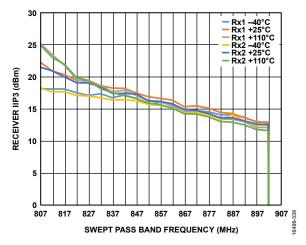

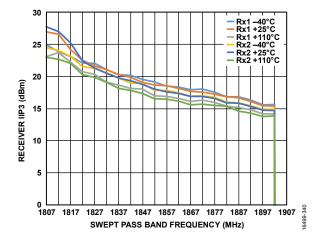

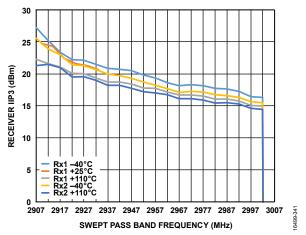

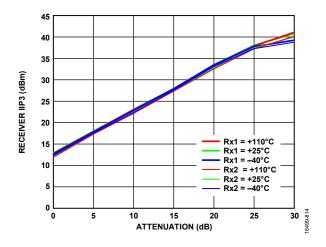

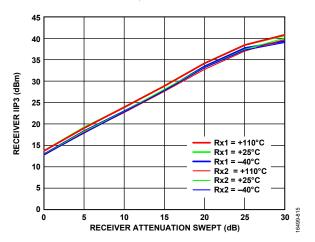

| Third-Order Input<br>Intermodulation<br>Intercept Point          | IIP3   |       |            |     |      |                                                                                                                                                                                       |

| Difference Product                                               | IIP3D  | 1     | 12         |     | dBm  | 75 MHz $<$ f $\le$ 600 MHz, (P <sub>HIGH</sub> $-$ 12) dB per tone, 600 MHz $<$ f $\le$ 6000 MHz, (P <sub>HIGH</sub> $-$ 10) dB per tone, two tones near band edge                    |

| Sum Product                                                      | IIP3S  | 1     | 12         |     | dBm  | 75 MHz $<$ f $\le$ 600 MHz, (P <sub>HIGH</sub> $-$ 12) dB per tone, 600 MHz $<$ f $\le$ 6000 MHz, (P <sub>HIGH</sub> $-$ 10) dB per tone, two tones at bandwidth/6 offset from the LO |

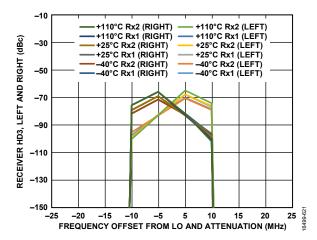

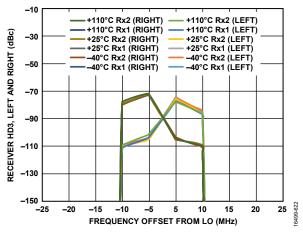

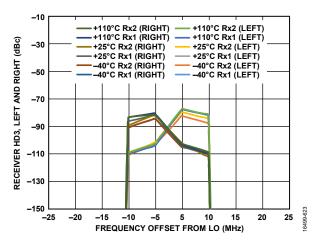

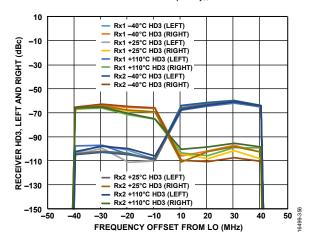

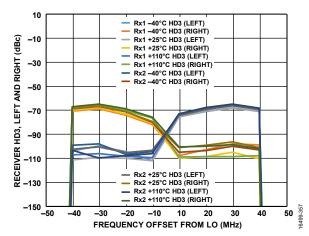

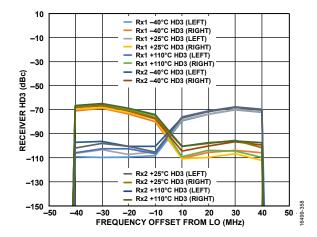

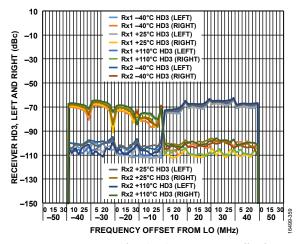

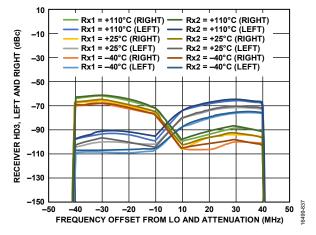

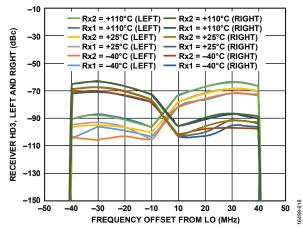

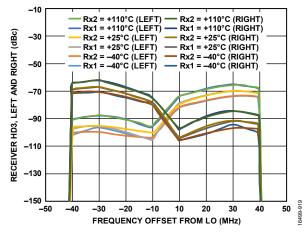

| Third-Order Harmonic<br>Distortion Product                       | HD3    |       |            |     |      | 75 MHz $<$ f $\le$ 600 MHz, (P <sub>HIGH</sub> $-$ 6) dB, 600 MHz $<$ f $\le$ 6000 MHz, (P <sub>HIGH</sub> $-$ 4) dI CW tone at bandwidth/6 offset from the LO                        |

|                                                                  |        | -     | -65        |     | dBc  | 75 MHz < f ≤ 600 MHz                                                                                                                                                                  |

|                                                                  |        | -     | -66        |     | dBc  | 600 MHz < f ≤ 4800 MHz                                                                                                                                                                |

|                                                                  |        | -     | -62        |     | dBc  | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                               |

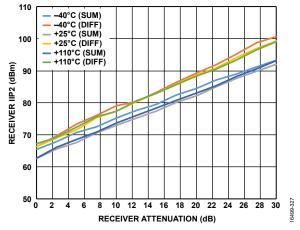

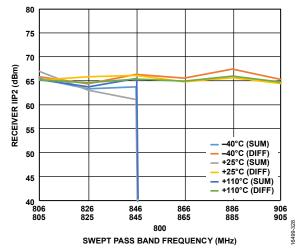

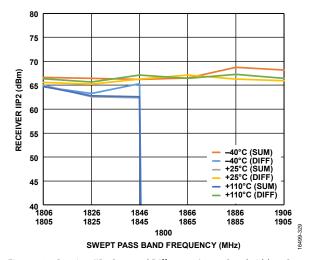

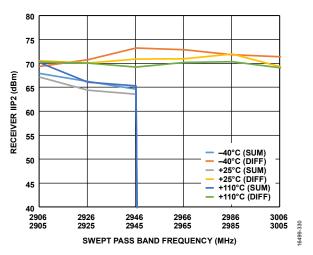

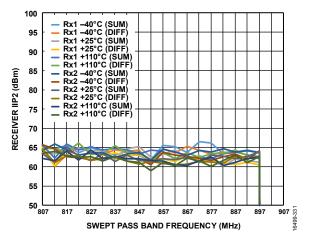

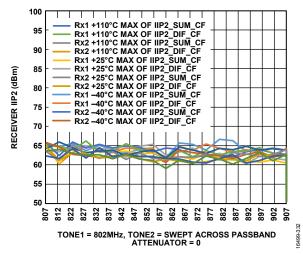

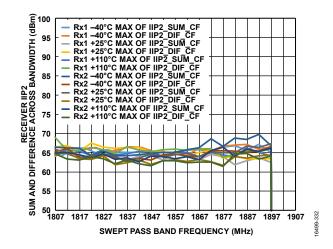

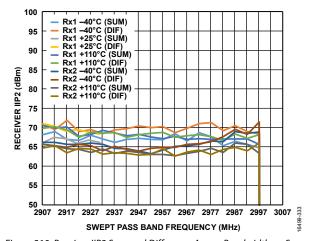

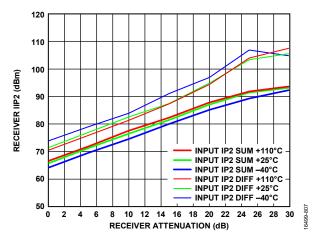

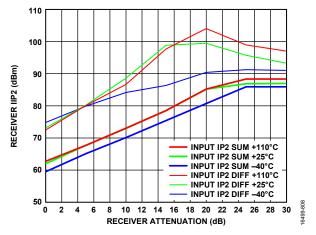

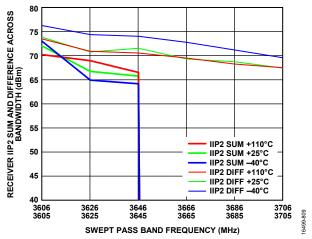

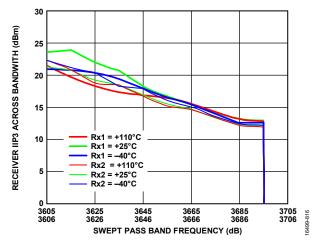

| Second-Order Input<br>Intermodulation<br>Intercept Point         | IIP2   | 6     | 62         |     | dBm  | 75 MHz $<$ f $\le$ 600 MHz, (P <sub>HIGH</sub> $-$ 12) dB per tone, 600 MHz $<$ f $\le$ 6000 MHz, (P <sub>HIGH</sub> $-$ 10) dB per tone, 0 dB attenuation, complex                   |

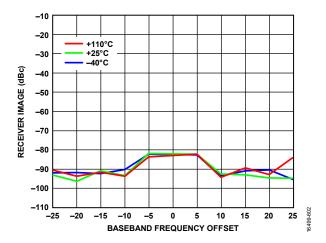

| Image Rejection                                                  |        | 7     | 75         |     | dB   | QEC active, within 200 MHz receiver bandwidth                                                                                                                                         |

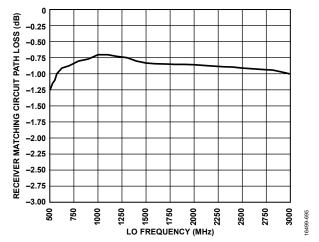

| Input Impedance                                                  |        | 1     | 100        |     | Ω    | Differential (see Figure 429)                                                                                                                                                         |

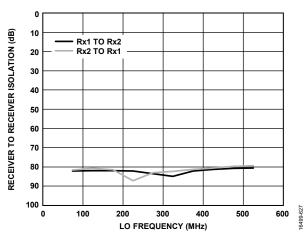

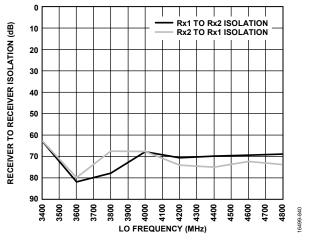

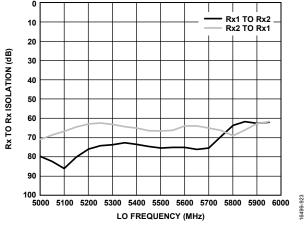

| Receiver to Receiver<br>Isolation                                |        | 7     | 77         |     | dB   | 75 MHz < f ≤ 600 MHz                                                                                                                                                                  |

|                                                                  |        | 6     | 65         |     | dB   | 600 MHz < f ≤ 4800 MHz                                                                                                                                                                |

|                                                                  |        | 6     | 61         |     | dB   | 4800 MHz < f ≤ 6000 MHz                                                                                                                                                               |

| Receiver Band Spurs<br>Referenced to RF Input<br>at Maximum Gain |        | -     | <b>-95</b> |     | dBm  | No more than one spur at this level por 10 MHz of receiver bandwidth                                                                                                                  |

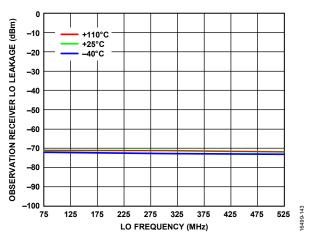

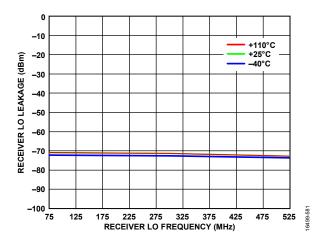

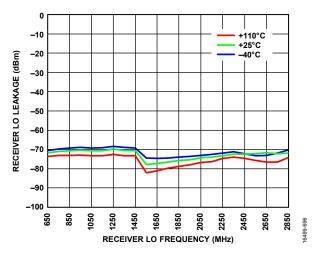

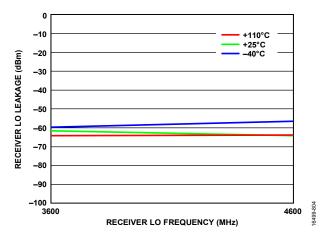

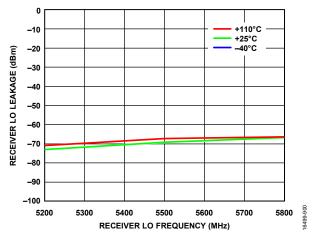

| Receiver LO Leakage at<br>Receiver Input at<br>Maximum Gain      |        |       |            |     |      | Leakage decreases decibel for decibe with attenuation for first 12 dB                                                                                                                 |

| ·                                                                |        | -     | <b>-70</b> |     | dBm  | 75 MHz < f ≤ 600 MHz                                                                                                                                                                  |

|                                                                  |        |       | <b>-70</b> |     | dBm  | 600 MHz < f ≤ 3000 MHz                                                                                                                                                                |

|                                                                  |        |       | -65        |     | dBm  | 3000 MHz < f ≤ 6000 MHz                                                                                                                                                               |

|                                          |                | Min | Тур        | Max                                   | Unit        | Test Conditions/Comments                                              |

|------------------------------------------|----------------|-----|------------|---------------------------------------|-------------|-----------------------------------------------------------------------|

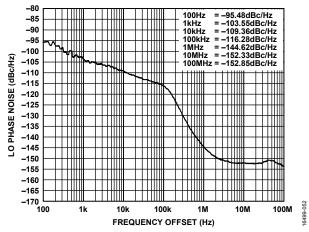

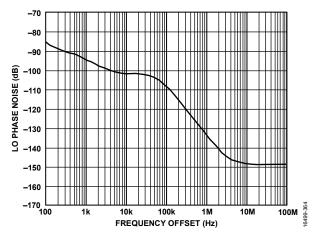

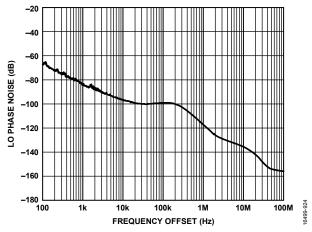

| LO SYNTHESIZER                           |                |     |            |                                       |             |                                                                       |

| LO Frequency Step                        |                |     | 2.3        |                                       | Hz          | 1.5 GHz to 2.8 GHz, 76.8 MHz phase frequency detector (PFD) frequency |

| LO Spur                                  |                |     | -85        |                                       | dBc         | Excludes integer boundary spurs                                       |

| Integrated Phase Noise                   |                |     |            |                                       |             | 2 kHz to 18 MHz                                                       |

| 75 MHz LO                                |                |     | 0.014      |                                       | °rms        | Narrow PLL loop bandwidth (50 kHz)                                    |

| 1900 MHz LO                              |                |     | 0.2        |                                       | °rms        | Narrow PLL loop bandwidth (50 kHz)                                    |

| 3800 MHz LO                              |                |     | 0.36       |                                       | °rms        | Wide PLL loop bandwidth (300 kHz)                                     |

| 5900 MHz LO                              |                |     | 0.54       |                                       | °rms        | Wide PLL loop bandwidth (300 kHz)                                     |

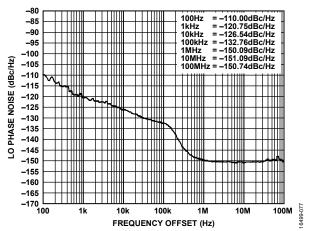

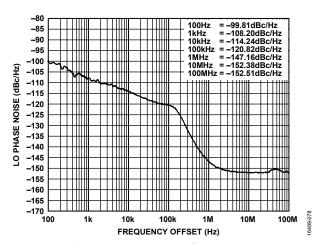

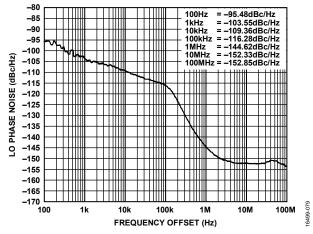

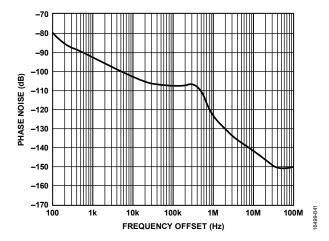

| Spot Phase Noise                         |                |     |            |                                       |             |                                                                       |

| 75 MHz LO                                |                |     |            |                                       |             | Narrow PLL loop bandwidth                                             |

| 10 kHz Offset                            |                |     | -126.5     |                                       | dBc/Hz      |                                                                       |

| 100 kHz Offset                           |                |     | -132.8     |                                       | dBc/Hz      |                                                                       |

| 1 MHz Offset                             |                |     | -150.1     |                                       | dBc/Hz      |                                                                       |

| 10 MHz Offset                            |                |     | -150.7     |                                       | dBc/Hz      |                                                                       |

| 1900 MHz LO                              |                |     |            |                                       |             | Narrow PLL loop bandwidth                                             |

| 100 kHz Offset                           |                |     | -100       |                                       | dBc/Hz      | •                                                                     |

| 200 kHz Offset                           |                |     | -115       |                                       | dBc/Hz      |                                                                       |

| 400 kHz Offset                           |                |     | -120       |                                       | dBc/Hz      |                                                                       |

| 600 kHz Offset                           |                |     | -129       |                                       | dBc/Hz      |                                                                       |

| 800 kHz Offset                           |                |     | -132       |                                       | dBc/Hz      |                                                                       |

| 1.2 MHz Offset                           |                |     | -135       |                                       | dBc/Hz      |                                                                       |

| 1.8 MHz Offset                           |                |     | -140       |                                       | dBc/Hz      |                                                                       |

| 6 MHz Offset                             |                |     | -150       |                                       | dBc/Hz      |                                                                       |

| 10 MHz Offset                            |                |     | -153       |                                       | dBc/Hz      |                                                                       |

| 3800 MHz LO                              |                |     |            |                                       |             | Wide PLL loop bandwidth                                               |

| 100 kHz Offset                           |                |     | -104       |                                       | dBc/Hz      |                                                                       |

| 1.2 MHz Offset                           |                |     | -125       |                                       | dBc/Hz      |                                                                       |

| 10 MHz Offset                            |                |     | -145       |                                       | dBc/Hz      |                                                                       |

| 5900 MHz LO                              |                |     | 5          |                                       | 0.5 0, 1.12 | Wide PLL loop bandwidth                                               |

| 100 kHz Offset                           |                |     | <b>-99</b> |                                       | dBc/Hz      |                                                                       |

| 1.2 MHz Offset                           |                |     | -119.7     |                                       | dBc/Hz      |                                                                       |

| 10 MHz Offset                            |                |     | -135.4     |                                       | dBc/Hz      |                                                                       |

| LO PHASE SYNCHRONIZATION                 |                |     | 133.1      |                                       | GDC/112     |                                                                       |

| Phase Deviation                          |                |     | 1.6        |                                       | ps/°C       | Change in LO delay per temperature                                    |

|                                          |                |     |            |                                       |             | change                                                                |

| EXTERNAL LO INPUT                        |                |     |            |                                       |             |                                                                       |

| Input Frequency                          | <b>f</b> extlo | 150 |            | 8000                                  | MHz         | Input frequency must be 2 × the desired LO frequency                  |

| Input Signal Power                       |                | 0   |            | 12                                    | dBm         | $50 \Omega$ matching at the source                                    |

|                                          |                |     | 3          |                                       | dBm         | $f_{EXTLO} \le 2 \text{ GHz}$ , add 0.5 dBm/GHz above 2 GHz           |

|                                          |                |     | 6          |                                       | dBm         | f <sub>EXTLO</sub> = 8 GHz                                            |

| External LO Input Signal<br>Differential |                |     |            |                                       |             | To ensure adequate QEC                                                |

| Phase Error                              |                |     |            | 3.6                                   | ps          |                                                                       |

| Amplitude Error                          |                |     |            | 1                                     | dB          |                                                                       |

| Duty Cycle Error                         |                |     |            | 2                                     | %           |                                                                       |

| Even Order Harmonics                     |                |     |            | _<br>_50                              | dBc         |                                                                       |

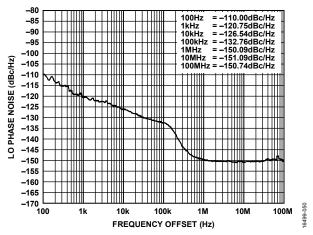

| CLOCK SYNTHESIZER                        |                |     |            | · · · · · · · · · · · · · · · · · · · |             |                                                                       |

| Integrated Phase Noise                   |                |     |            |                                       |             | 1 kHz to 100 MHz                                                      |

| 1966.08 MHz LO                           |                |     | 0.4        |                                       | °rms        | PLL optimized for close in phase noise                                |

| Parameter                                                                                                         | Symbol | Min                        | Тур                | Max                        | Unit   | Test Conditions/Comments                                                                                     |

|-------------------------------------------------------------------------------------------------------------------|--------|----------------------------|--------------------|----------------------------|--------|--------------------------------------------------------------------------------------------------------------|

| Spot Phase Noise                                                                                                  |        |                            |                    |                            |        |                                                                                                              |

| 1966.08 MHz                                                                                                       |        |                            |                    |                            |        |                                                                                                              |

| 100 kHz Offset                                                                                                    |        |                            | -109               |                            | dBc/Hz |                                                                                                              |

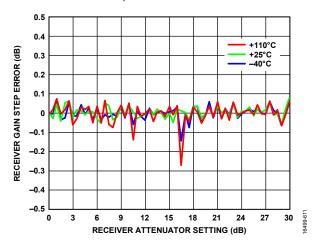

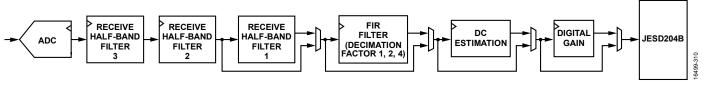

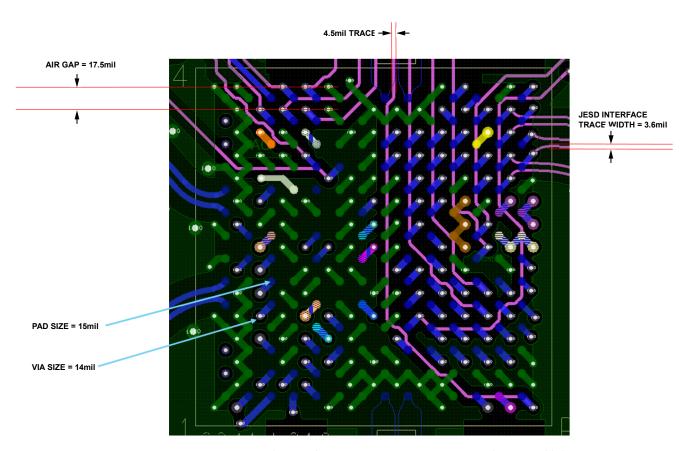

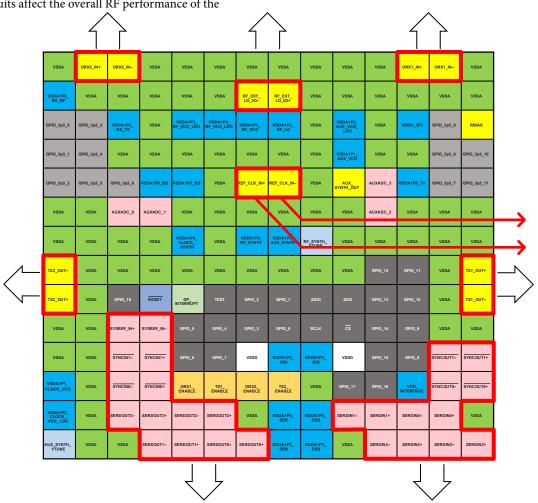

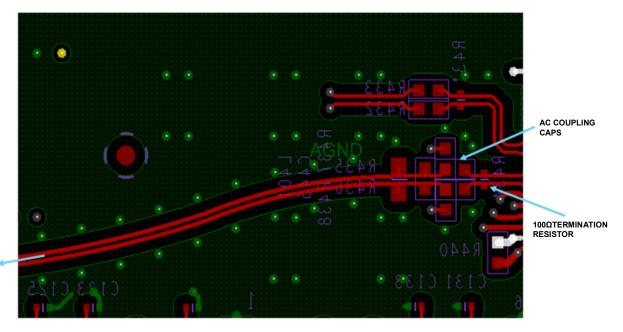

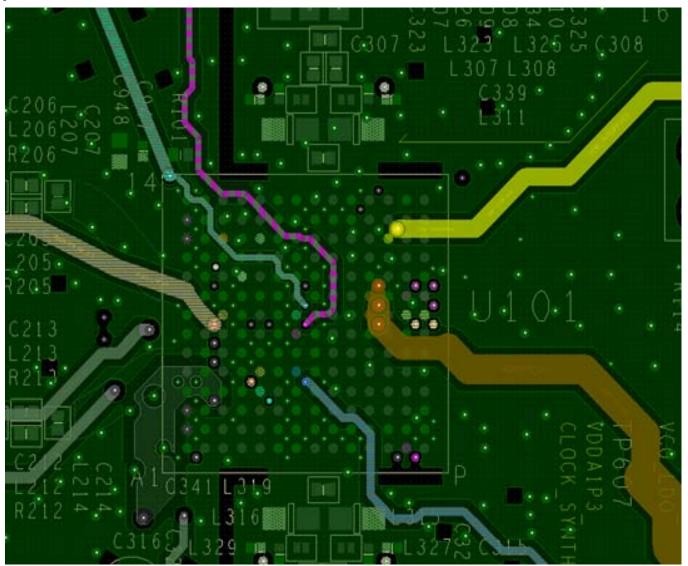

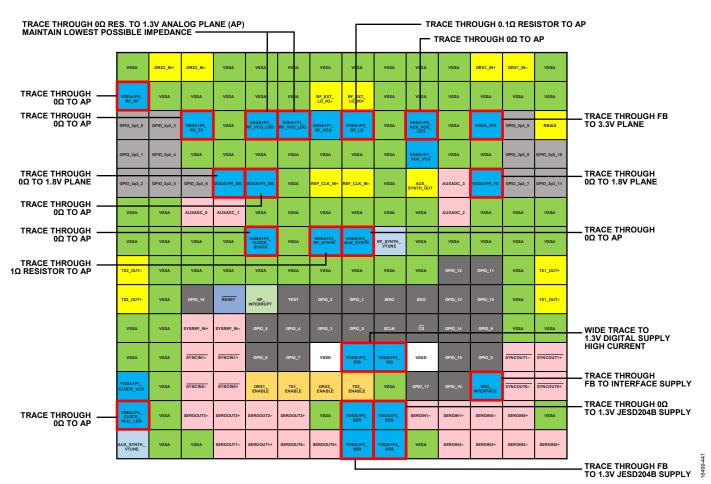

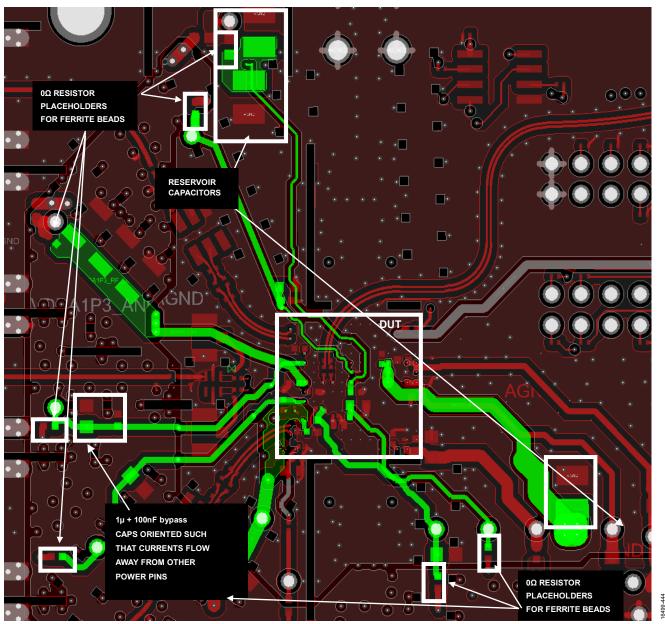

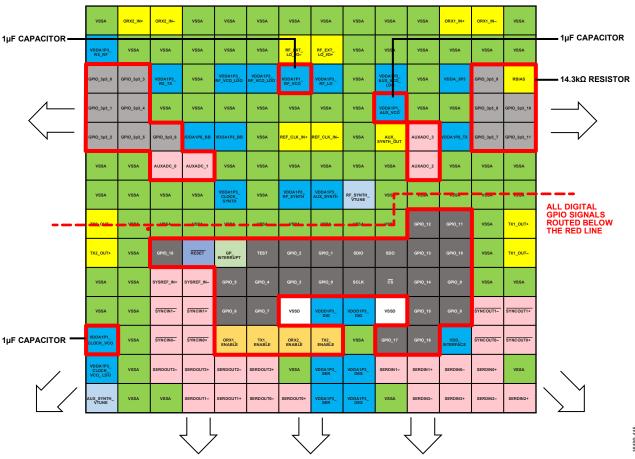

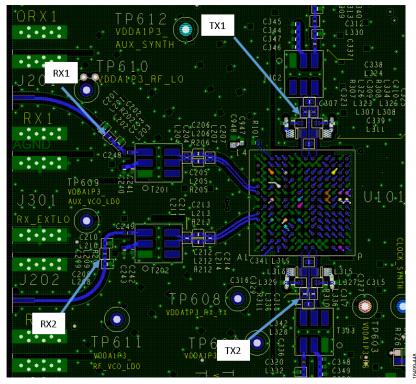

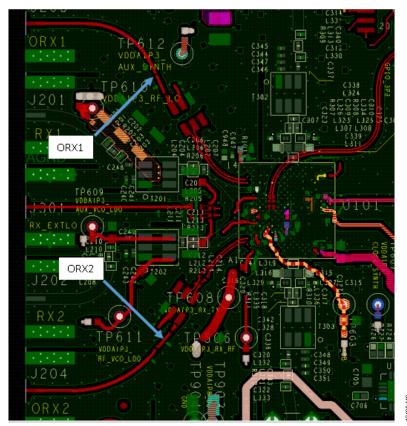

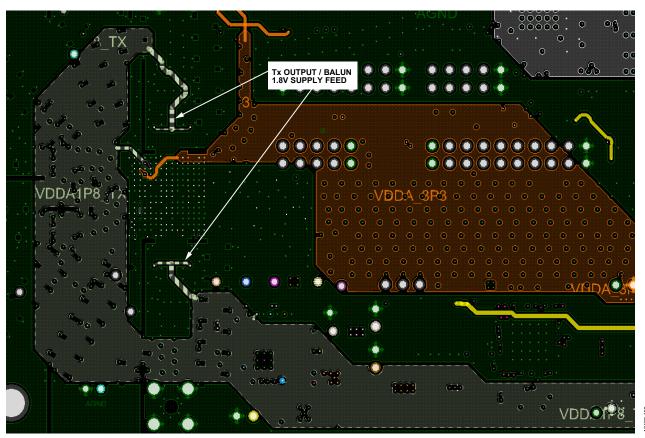

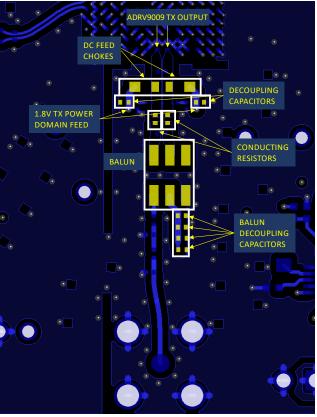

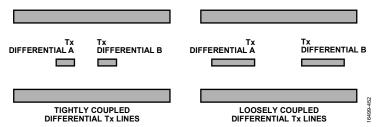

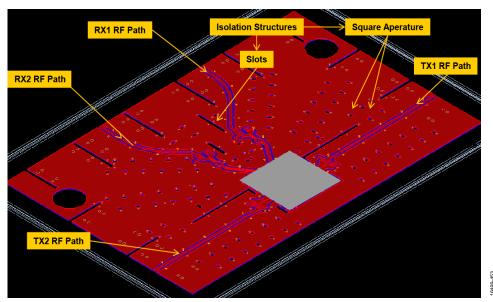

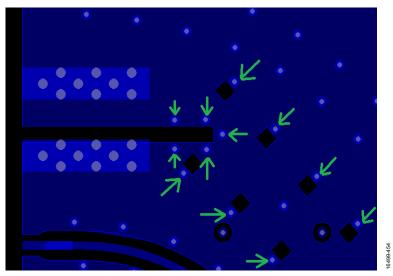

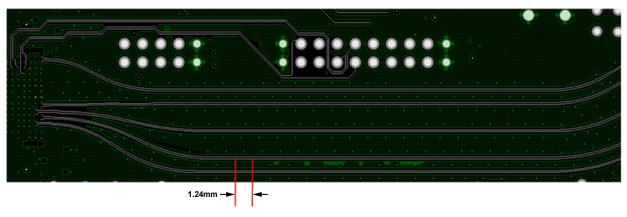

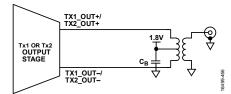

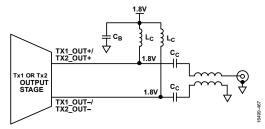

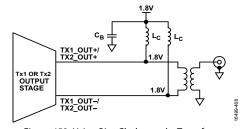

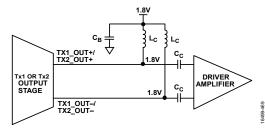

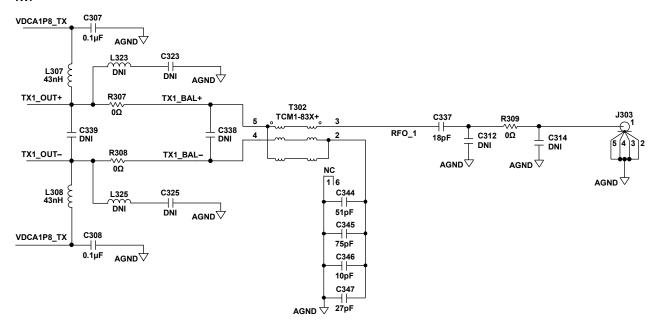

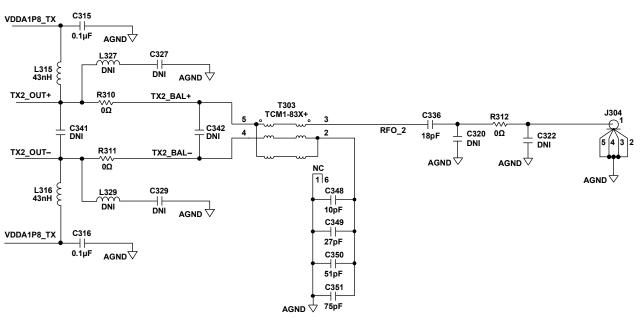

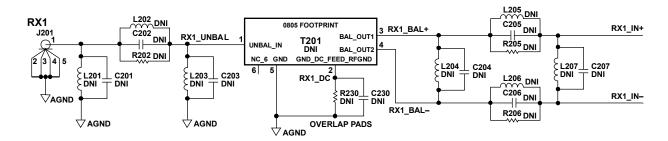

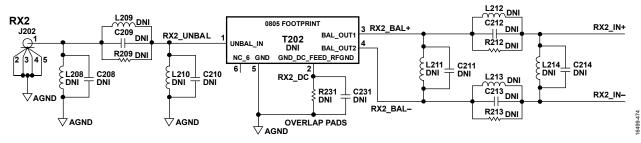

| 1 MHz Offset                                                                                                      |        |                            | -129               |                            | dBc/Hz |                                                                                                              |