# ispMACH®4000ZE Family

1.8V In-System Programmable

Ultra Low Power PLDs

February 2012 Data Sheet DS1022

### **Features**

#### High Performance

- f<sub>MAX</sub> = 260MHz maximum operating frequency

- t<sub>PD</sub> = 4.4ns propagation delay

- Up to four global clock pins with programmable clock polarity control

- Up to 80 PTs per output

#### Ease of Design

- Flexible CPLD macrocells with individual clock, reset, preset and clock enable controls

- Up to four global OE controls

- Individual local OE control per I/O pin

- Excellent First-Time-Fit<sup>™</sup> and refit

- Wide input gating (36 input logic blocks) for fast counters, state machines and address decoders

#### ■ Ultra Low Power

- Standby current as low as 10µA typical

- 1.8V core; low dynamic power

- Operational down to 1.6V V<sub>CC</sub>

- Superior solution for power sensitive consumer applications

- Per pin pull-up, pull-down or bus keeper control\*

- Power Guard with multiple enable signals\*

#### Broad Device Offering

- 32 to 256 macrocells

- Multiple temperature range support

- Commercial: 0 to 90°C junction (T<sub>i</sub>)

- Industrial: -40 to 105°C junction (T<sub>i</sub>)

- Space-saving ucBGA and csBGA packages\*

### ■ Easy System Integration

- Operation with 3.3V, 2.5V, 1.8V or 1.5V LVCMOS I/O

- 5V tolerant I/O for LVCMOS 3.3, LVTTL, and PCI interfaces

- Hot-socketing support

- · Open-drain output option

- Programmable output slew rate

- 3.3V PCI compatible

- · I/O pins with fast setup path

- Input hysteresis\*

- 1.8V core power supply

- IEEE 1149.1 boundary scan testable

- IEEE 1532 ISC compliant

- 1.8V In-System Programmable (ISP™) using Boundary Scan Test Access Port (TAP)

- Pb-free package options (only)

- On-chip user oscillator and timer\*

\*New enhanced features over original ispMACH 4000Z

Table 1. ispMACH 4000ZE Family Selection Guide

|                                           | ispMACH 4032ZE | ispMACH 4064ZE | ispMACH 4128ZE | ispMACH 4256ZE |

|-------------------------------------------|----------------|----------------|----------------|----------------|

| Macrocells                                | 32             | 64             | 128            | 256            |

| t <sub>PD</sub> (ns)                      | 4.4            | 4.7            | 5.8            | 5.8            |

| t <sub>S</sub> (ns)                       | 2.2            | 2.5            | 2.9            | 2.9            |

| t <sub>CO</sub> (ns)                      | 3.0            | 3.2            | 3.8            | 3.8            |

| f <sub>MAX</sub> (MHz)                    | 260            | 241            | 200            | 200            |

| Supply Voltages (V)                       | 1.8V           | 1.8V           | 1.8V           | 1.8V           |

| Packages <sup>1</sup> (I/O + Dedicated Ir | nputs)         |                |                |                |

| 48-Pin TQFP (7 x 7mm)                     | 32+4           | 32+4           |                |                |

| 64-Ball csBGA (5 x 5mm)                   | 32+4           | 48+4           |                |                |

| 64-Ball ucBGA (4 x 4mm)                   |                | 48+4           |                |                |

| 100-Pin TQFP (14 x 14mm)                  |                | 64+10          | 64+10          | 64+10          |

| 132-Ball ucBGA (6 x 6mm)                  |                |                | 96+4           |                |

| 144-Pin TQFP (20 x 20mm)                  |                |                | 96+4           | 96+14          |

| 144-Ball csBGA (7 x 7mm)                  |                | 64+10          | 96+4           | 108+4          |

<sup>1.</sup> Pb-free only.

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### Introduction

The high performance ispMACH 4000ZE family from Lattice offers an ultra low power CPLD solution. The new family is based on Lattice's industry-leading ispMACH 4000 architecture. Retaining the best of the previous generation, the ispMACH 4000ZE architecture focuses on significant innovations to combine high performance with low power in a flexible CPLD family. For example, the family's new Power Guard feature minimizes dynamic power consumption by preventing internal logic toggling due to unnecessary I/O pin activity.

The ispMACH 4000ZE combines high speed and low power with the flexibility needed for ease of design. With its robust Global Routing Pool and Output Routing Pool, this family delivers excellent First-Time-Fit, timing predictability, routing, pin-out retention and density migration.

The ispMACH 4000ZE family offers densities ranging from 32 to 256 macrocells. There are multiple density-I/O combinations in Thin Quad Flat Pack (TQFP), Chip Scale BGA (csBGA), and Ultra Chip Scale BGA (ucBGA) packages ranging from 32 to 144 pins/balls. Table 1 shows the macrocell, package and I/O options, along with other key parameters.

A user programmable internal oscillator and a timer are included in the device for tasks like LED control, keyboard scanner and similar housekeeping type state machines. This feature can be optionally disabled to save power.

The ispMACH 4000ZE family has enhanced system integration capabilities. It supports a 1.8V supply voltage and 3.3V, 2.5V, 1.8V and 1.5V interface voltages. Additionally, inputs can be safely driven up to 5.5V when an I/O bank is configured for 3.3V operation, making this family 5V tolerant. The ispMACH 4000ZE also offers enhanced I/O features such as slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis. The ispMACH 4000ZE family members are 1.8V in-system programmable through the IEEE Standard 1532 interface. IEEE Standard 1149.1 boundary scan testing capability also allows product testing on automated test equipment. The 1532 interface signals TCK, TMS, TDI and TDO are referenced to V<sub>CC</sub> (logic core).

### **Overview**

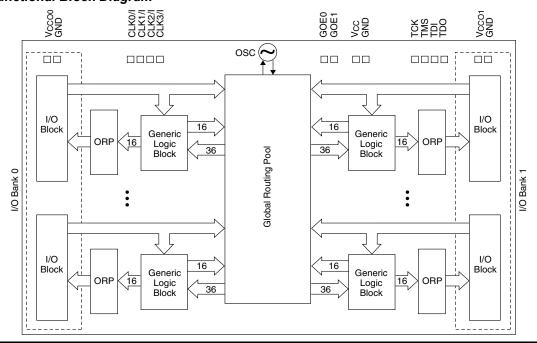

The ispMACH 4000ZE devices consist of multiple 36-input, 16-macrocell Generic Logic Blocks (GLBs) interconnected by a Global Routing Pool (GRP). Output Routing Pools (ORPs) connect the GLBs to the I/O Blocks (IOBs), which contain multiple I/O cells. This architecture is shown in Figure 1.

Figure 1. Functional Block Diagram

The I/Os in the ispMACH 4000ZE are split into two banks. Each bank has a separate I/O power supply. Inputs can support a variety of standards independent of the chip or bank power supply. Outputs support the standards compatible with the power supply provided to the bank. Support for a variety of standards helps designers implement designs in mixed voltage environments. In addition, 5V tolerant inputs are specified within an I/O bank that is connected to a  $V_{CCO}$  of 3.0V to 3.6V for LVCMOS 3.3, LVTTL and PCI interfaces.

### **Architecture**

There are a total of two GLBs in the ispMACH 4032ZE, increasing to 16 GLBs in the ispMACH 4256ZE. Each GLB has 36 inputs. All GLB inputs come from the GRP and all outputs from the GLB are brought back into the GRP to be connected to the inputs of any other GLB on the device. Even if feedback signals return to the same GLB, they still must go through the GRP. This mechanism ensures that GLBs communicate with each other with consistent and predictable delays. The outputs from the GLB are also sent to the ORP. The ORP then sends them to the associated I/O cells in the I/O block.

### **Generic Logic Block**

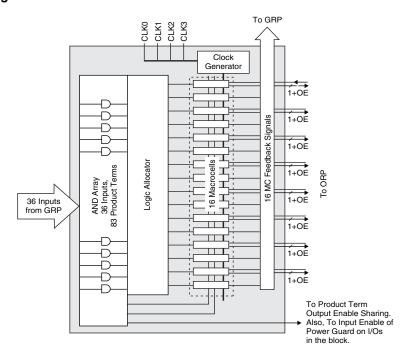

The ispMACH 4000ZE GLB consists of a programmable AND array, logic allocator, 16 macrocells and a GLB clock generator. Macrocells are decoupled from the product terms through the logic allocator and the I/O pins are decoupled from macrocells through the ORP. Figure 2 illustrates the GLB.

Figure 2. Generic Logic Block

### **AND Array**

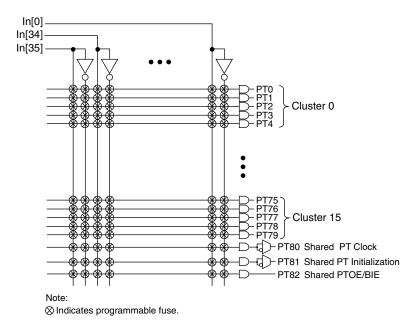

The programmable AND Array consists of 36 inputs and 83 output product terms. The 36 inputs from the GRP are used to form 72 lines in the AND Array (true and complement of the inputs). Each line in the array can be connected to any of the 83 output product terms via a wired-AND. Each of the 80 logic product terms feed the logic allocator with the remaining three control product terms feeding the Shared PT Clock, Shared PT Initialization and Shared PT OE. The Shared PT Clock and Shared PT Initialization signals can optionally be inverted before being fed to the macrocells.

Every set of five product terms from the 80 logic product terms forms a product term cluster starting with PT0. There is one product term cluster for every macrocell in the GLB. Figure 3 is a graphical representation of the AND Array.

Figure 3. AND Array

### **Enhanced Logic Allocator**

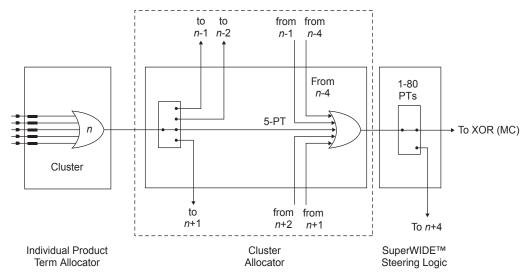

Within the logic allocator, product terms are allocated to macrocells in product term clusters. Each product term cluster is associated with a macrocell. The cluster size for the ispMACH 4000ZE family is 4+1 (total 5) product terms. The software automatically considers the availability and distribution of product term clusters as it fits the functions within a GLB. The logic allocator is designed to provide two speed paths: 20-PT Speed Locking path and an up to 80-PT path. The availability of these two paths lets designers trade timing variability for increased performance.

The enhanced Logic Allocator of the ispMACH 4000ZE family consists of the following blocks:

- Product Term Allocator

- Cluster Allocator

- Wide Steering Logic

Figure 4 shows a macrocell slice of the Logic Allocator. There are 16 such slices in the GLB.

Figure 4. Macrocell Slice

#### **Product Term Allocator**

The product term allocator assigns product terms from a cluster to either logic or control applications as required by the design being implemented. Product terms that are used as logic are steered into a 5-input OR gate associated with the cluster. Product terms that used for control are steered either to the macrocell or I/O cell associated with the cluster. Table 2 shows the available functions for each of the five product terms in the cluster.

Table 2. Individual PT Steering

| Product Term   | Logic    | Control                                                                     |

|----------------|----------|-----------------------------------------------------------------------------|

| PT <i>n</i>    | Logic PT | Single PT for XOR/OR                                                        |

| PT <i>n</i> +1 | Logic PT | Individual Clock (PT Clock)                                                 |

| PTn+2          | Logic PT | Individual Initialization or Individual Clock Enable (PT Initialization/CE) |

| PTn+3          | Logic PT | Individual Initialization (PT Initialization)                               |

| PT <i>n</i> +4 | Logic PT | Individual OE (PTOE)                                                        |

#### Cluster Allocator

The cluster allocator allows clusters to be steered to neighboring macrocells, thus allowing the creation of functions with more product terms. Table 3 shows which clusters can be steered to which macrocells. Used in this manner, the cluster allocator can be used to form functions of up to 20 product terms. Additionally, the cluster allocator accepts inputs from the wide steering logic. Using these inputs, functions up to 80 product terms can be created.

Table 3. Available Clusters for Each Macrocell

| Macrocell | Available Clusters |     |     |     |

|-----------|--------------------|-----|-----|-----|

| MO        | _                  | C0  | C1  | C2  |

| M1        | C0                 | C1  | C2  | C3  |

| M2        | C1                 | C2  | C3  | C4  |

| M3        | C2                 | C3  | C4  | C5  |

| M4        | C3                 | C4  | C5  | C6  |

| M5        | C4                 | C5  | C6  | C7  |

| M6        | C5                 | C6  | C7  | C8  |

| M7        | C6                 | C7  | C8  | C9  |

| M8        | C7                 | C8  | C9  | C10 |

| M9        | C8                 | C9  | C10 | C11 |

| M10       | C9                 | C10 | C11 | C12 |

| M11       | C10                | C11 | C12 | C13 |

| M12       | C11                | C12 | C13 | C14 |

| M13       | C12                | C13 | C14 | C15 |

| M14       | C13                | C14 | C15 | _   |

| M15       | C14                | C15 | _   | _   |

### Wide Steering Logic

The wide steering logic allows the output of the cluster allocator n to be connected to the input of the cluster allocator n+4. Thus, cluster chains can be formed with up to 80 product terms, supporting wide product term functions and allowing performance to be increased through a single GLB implementation. Table 4 shows the product term chains.

Table 4. Product Term Expansion Capability

| Expansion<br>Chains | Macrocells Associated with Expansion Chain (with Wrap Around) | Max PT/<br>Macrocell |

|---------------------|---------------------------------------------------------------|----------------------|

| Chain-0             | M0 Õ M4 Õ M8 Õ M12 Õ M0                                       | 75                   |

| Chain-1             | M1 Õ M5 Õ M9 Õ M13 Õ M1                                       | 80                   |

| Chain-2             | M2 Õ M6 Õ M10 Õ M14 Õ M2                                      | 75                   |

| Chain-3             | M3 Õ M7 Õ M11 Õ M15 Õ M3                                      | 70                   |

Every time the super cluster allocator is used, there is an incremental delay of t<sub>EXP</sub>. When the super cluster allocator is used, all destinations other than the one being steered to, are given the value of ground (i.e., if the super cluster is steered to M (n+4), then M (n) is ground).

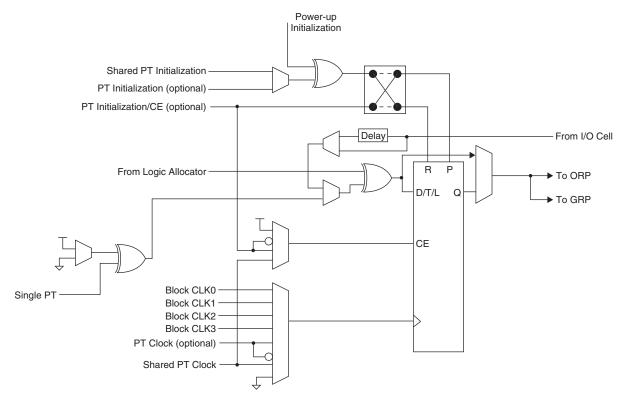

#### Macrocell

The 16 macrocells in the GLB are driven by the 16 outputs from the logic allocator. Each macrocell contains a programmable XOR gate, a programmable register/latch, along with routing for the logic and control functions. Figure 5 shows a graphical representation of the macrocell. The macrocells feed the ORP and GRP. A direct input from the I/O cell allows designers to use the macrocell to construct high-speed input registers. A programmable delay in this path allows designers to choose between the fastest possible set-up time and zero hold time.

Figure 5. Macrocell

### **Enhanced Clock Multiplexer**

The clock input to the flip-flop can select any of the four block clocks along with the shared PT clock, and true and complement forms of the optional individual term clock. An 8:1 multiplexer structure is used to select the clock. The eight sources for the clock multiplexer are as follows:

- Block CLK0

- Block CLK1

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

### **Clock Enable Multiplexer**

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

#### **Initialization Control**

The ispMACH 4000ZE family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

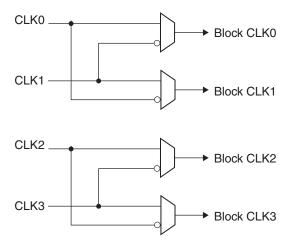

#### **GLB Clock Generator**

Each ispMACH 4000ZE device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

Figure 6. GLB Clock Generator

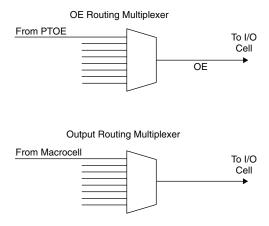

### **Output Routing Pool (ORP)**

The Output Routing Pool allows macrocell outputs to be connected to any of several I/O cells within an I/O block. This provides greater flexibility in determining the pinout and allows design changes to occur without affecting the pinout. The output routing pool also provides a parallel capability for routing macrocell-level OE product terms. This allows the OE product term to follow the macrocell output as it is switched between I/O cells. The enhanced ORP of the ispMACH 4000ZE family consists of the following elements:

- Output Routing Multiplexers

- OE Routing Multiplexers

Figure 7 shows the structure of the ORP from the I/O cell perspective. This is referred to as an ORP slice. Each ORP has as many ORP slices as there are I/O cells in the corresponding I/O block.

Figure 7. ORP Slice

### **Output Routing Multiplexers**

The details of connections between the macrocells and the I/O cells vary across devices and within a device dependent on the maximum number of I/Os available. Tables 5-7 provide the connection details.

Table 5. GLB/MC/ORP Combinations for ispMACH 4256ZE

| GLB/MC       | ORP Mux Input Macrocells             |

|--------------|--------------------------------------|

| [GLB] [MC 0] | M0, M1, M2, M3, M4, M5, M6, M7       |

| [GLB] [MC 1] | M2, M3, M4, M5, M6, M7, M8, M9       |

| [GLB] [MC 2] | M4, M5, M6, M7, M8, M9, M10, M11     |

| [GLB] [MC 3] | M6, M7, M8, M9, M10, M11, M12, M13   |

| [GLB] [MC 4] | M8, M9, M10, M11, M12, M13, M14, M15 |

| [GLB] [MC 5] | M10, M11, M12, M13, M14, M15, M0, M1 |

| [GLB] [MC 6] | M12, M13, M14, M15, M0, M1, M2, M3   |

| [GLB] [MC 7] | M14, M15, M0, M1, M2, M3, M4, M5     |

### Table 6. GLB/MC/ORP Combinations for ispMACH 4128ZE

| GLB/MC        | ORP Mux Input Macrocells             |

|---------------|--------------------------------------|

| [GLB] [MC 0]  | M0, M1, M2, M3, M4, M5, M6, M7       |

| [GLB] [MC 1]  | M1, M2, M3, M4, M5, M6, M7, M8       |

| [GLB] [MC 2]  | M2, M3, M4, M5, M6, M7, M8, M9       |

| [GLB] [MC 3]  | M4, M5, M6, M7, M8, M9, M10, M11     |

| [GLB] [MC 4]  | M5, M6, M7, M8, M9, M10, M11, M12    |

| [GLB] [MC 5]  | M6, M7, M8, M9, M10, M11, M12, M13   |

| [GLB] [MC 6]  | M8, M9, M10, M11, M12, M13, M14, M15 |

| [GLB] [MC 7]  | M9, M10, M11, M12, M13, M14, M15, M0 |

| [GLB] [MC 8]  | M10, M11, M12, M13, M14, M15, M0, M1 |

| [GLB] [MC 9]  | M12, M13, M14, M15, M0, M1, M2, M3   |

| [GLB] [MC 10] | M13, M14, M15, M0, M1, M2, M3, M4    |

| [GLB] [MC 11] | M14, M15, M0, M1, M2, M3, M4, M5     |

### Table 7. GLB/MC/ORP Combinations for ispMACH 4032ZE and 4064ZE

| GLB/MC        | ORP Mux Input Macrocells             |

|---------------|--------------------------------------|

| [GLB] [MC 0]  | M0, M1, M2, M3, M4, M5, M6, M7       |

| [GLB] [MC 1]  | M1, M2, M3, M4, M5, M6, M7, M8       |

| [GLB] [MC 2]  | M2, M3, M4, M5, M6, M7, M8, M9       |

| [GLB] [MC 3]  | M3, M4, M5, M6, M7, M8, M9, M10      |

| [GLB] [MC 4]  | M4, M5, M6, M7, M8, M9, M10, M11     |

| [GLB] [MC 5]  | M5, M6, M7, M8, M9, M10, M11, M12    |

| [GLB] [MC 6]  | M6, M7, M8, M9, M10, M11, M12, M13   |

| [GLB] [MC 7]  | M7, M8, M9, M10, M11, M12, M13, M14  |

| [GLB] [MC 8]  | M8, M9, M10, M11, M12, M13, M14, M15 |

| [GLB] [MC 9]  | M9, M10, M11, M12, M13, M14, M15, M0 |

| [GLB] [MC 10] | M10, M11, M12, M13, M14, M15, M0, M1 |

| [GLB] [MC 11] | M11, M12, M13, M14, M15, M0, M1, M2  |

| [GLB] [MC 12] | M12, M13, M14, M15, M0, M1, M2, M3   |

| [GLB] [MC 13] | M13, M14, M15, M0, M1, M2, M3, M4    |

| [GLB] [MC 14] | M14, M15, M0, M1, M2, M3, M4, M5     |

| [GLB] [MC 15] | M15, M0, M1, M2, M3, M4, M5, M6      |

### **Output Enable Routing Multiplexers**

The OE Routing Pool provides the corresponding local output enable (OE) product term to the I/O cell.

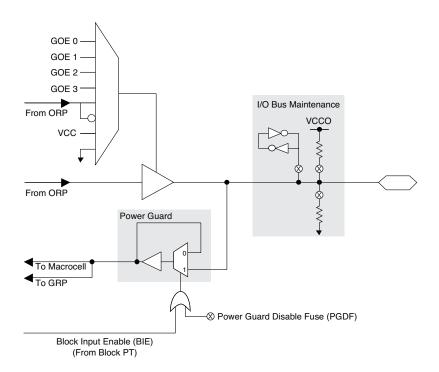

### I/O Cell

The I/O cell contains the following programmable elements: output buffer, input buffer, OE multiplexer, Power Guard and bus maintenance circuitry. Figure 8 details the I/O cell.

Figure 8. I/O Cell

Each output supports a variety of output standards dependent on the  $V_{CCO}$  supplied to its I/O bank. Outputs can also be configured for open drain operation. Each input can be programmed to support a variety of standards, independent of the  $V_{CCO}$  supplied to its I/O bank. The I/O standards supported are:

- LVTTL

LVCMOS 1.8

LVCMOS 1.5

- LVCMOS 2.5 3.3V PCI Compatible

All of the I/Os and dedicated inputs have the capability to provide a bus-keeper latch, pull-up resistor or pull-down resistor selectable on a "per-pin" basis. A fourth option is to provide none of these. The default in both hardware and software is such that when the device is erased or if the user does not specify, the input structure is configured to be a Pull-down Resistor.

Each ispMACH 4000ZE device I/O has an individually programmable output slew rate control bit. Each output can be individually configured for fast slew or slow slew. The typical edge rate difference between fast and slow slew setting is 20%. For high-speed designs with long, unterminated traces, the slow-slew rate will introduce fewer reflections, less noise and keep ground bounce to a minimum. For designs with short traces or well terminated lines, the fast slew rate can be used to achieve the highest speed.

The ispMACH 4000ZE family has an always on, 200mV typical hysteresis for each input operational at 3.3V and 2.5V. This provides improved noise immunity for slow transitioning signals.

### **Power Guard**

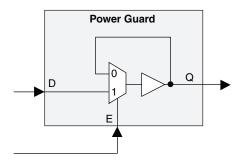

Power Guard allows easier achievement of standby current in the system. As shown in Figure 9, this feature consists of an enabling multiplexer between an I/O pin and input buffer, and its associated circuitry inside the device.

If the enable signal (E) is held low, all inputs (D) can be optionally isolated (guarded), such that, if any of these were toggled, it would not cause any toggle on internal pins (Q), thus, a toggling I/O pin will not cause any internal dynamic power consumption.

Figure 9. Power Guard

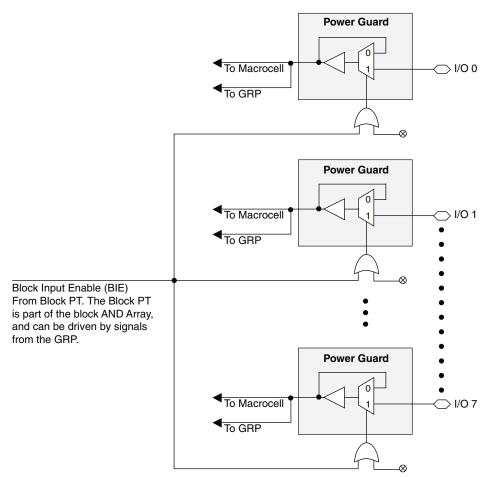

All the I/O pins in a block share a common Power Guard Enable signal. For a block of I/Os, this signal is called a Block Input Enable (BIE) signal. BIE can be internally generated using MC logic, or could come from external sources using one of the user I/O or input pins.

Any I/O pin in the block can be programmed to ignore the BIE signal. Thus, the feature can be enabled or disabled on a pin-by-pin basis.

Figure 10 shows Power Guard and BIE across multiple I/Os in a block that has eight I/Os.

Figure 10. Power Guard and BIE in a Block with 8 I/Os

The number of BIE inputs, thus the number of Power Guard "Blocks" that can exist in a device, depends on the device size. Table 8 shows the number of BIE signals available in the ispMACH 4000ZE family. The number of I/Os available in each block is shown in the Ordering Information section of this data sheet.

Table 8. Number of BIE Signals Available in ispMACH 4000ZE Devices

| Device         | Number of Logic Blocks, Power Guard Blocks and BIE Signals |  |

|----------------|------------------------------------------------------------|--|

| ispMACH 4032ZE | Two (Blocks: A and B)                                      |  |

| ispMACH 4064ZE | Four (Blocks: A, B, C and D)                               |  |

| ispMACH 4128ZE | Eight (Blocks: A, B, C,, H)                                |  |

| ispMACH 4256ZE | Sixteen (Blocks: A, B, C,, P)                              |  |

### **Power Guard for Dedicated Inputs**

Power Guard can optionally be applied to the dedicated inputs. The dedicated inputs and clocks are controlled by the BIE of the logic blocks shown in Tables 9 and 10.

Table 9. Dedicated Clock Inputs to BIE Association

| CLK/I    | 32 MC Block | 64MC Block | 128MC Block | 256MC Block |

|----------|-------------|------------|-------------|-------------|

| CLK0 / I | Α           | Α          | Α           | Α           |

| CLK1 / I | Α           | В          | D           | Н           |

| CLK2 / I | В           | С          | Е           | I           |

| CLK3 / I | В           | D          | Н           | Р           |

Table 10. Dedicated Inputs to BIE Association

| Dedicated Input | 4064ZE Block | 4128ZE Block | 4256ZE Block |

|-----------------|--------------|--------------|--------------|

| 0               | Α            | В            | D            |

| 1               | В            | С            | E            |

| 2               | В            | D            | G            |

| 3               | С            | F            | G            |

| 4               | D            | G            | J            |

| 5               | D            | Н            | L            |

| 6               | _            | _            | M            |

| 7               | _            | _            | 0            |

| 8               | _            | _            | 0            |

| 9               | _            | _            | В            |

For more information on the Power Guard function refer to TN1174, <u>Advanced Features of the ispMACH 4000ZE Family</u>.

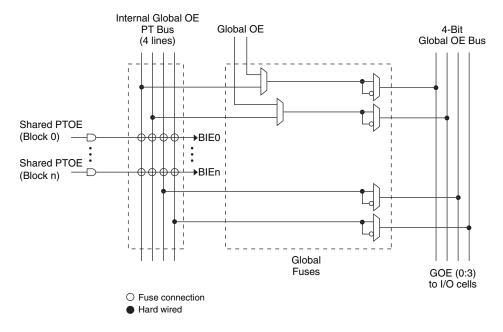

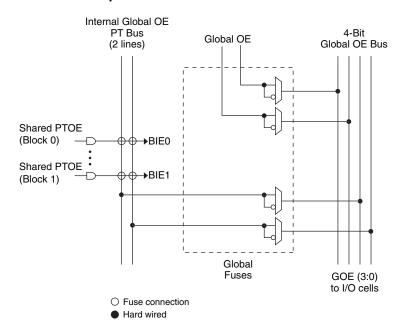

## Global OE (GOE) and Block Input Enable (BIE) Generation

Most ispMACH 4000ZE family devices have a 4-bit wide Global OE (GOE) Bus (Figure 11), except the ispMACH 4032 device that has a 2-bit wide Global OE Bus (Figure 12). This bus is derived from a 4-bit internal global OE (GOE) PT bus and two dual purpose I/O or GOE pins. Each signal that drives the bus can optionally be inverted.

Each GLB has a block-level OE PT that connects to all bits of the Global OE PT bus with four fuses. Hence, for a 256-macrocell device (with 16 blocks), each line of the bus is driven from 16 OE product terms. Figures 9 and 10 show a graphical representation of the global OE generation.

The block-level OE PT of each GLB is also tied to Block Input Enable (BIE) of that block. Hence, for a 256-macrocell device (with 16 blocks), each block's BIE signal is driven by block-level OE PT from each block.

Figure 11. Global OE Generation for All Devices Except ispMACH 4032ZE

Figure 12. Global OE Generation for ispMACH 4032ZE

## **On-Chip Oscillator and Timer**

An internal oscillator is provided for use in miscellaneous housekeeping functions such as watchdog heartbeats, digital de-glitch circuits and control state machines. The oscillator is disabled by default to save power. Figure 13 shows the block diagram of the oscillator and timer block.

Figure 13. On-Chip Oscillator and Timer

Table 11. On-Chip Oscillator and Timer Signal Names

| Signal Name | Input or Out-<br>put | Optional /<br>Required | Description                                                        |

|-------------|----------------------|------------------------|--------------------------------------------------------------------|

| OSCOUT      | Output               | Optional               | Oscillator Output (Nominal Frequency: 5MHz)                        |

| TIMEROUT    | Output               | Optional               | Oscillator Frequency Divided by an integer TIMER_DIV (Default 128) |

| TIMERRES    | Input                | Optional               | Reset the Timer                                                    |

| DYNOSCDIS   | Input                | Optional               | Disables the Oscillator, resets the Timer and saves the power.     |

OSCTIMER has two outputs, OSCOUT and TIMEROUT. The outputs feed into the Global Routing Pool (GRP). From GRP, these signals can drive any macrocell input, as well as any output pin (with macrocell bypass). The output OSCOUT is the direct oscillator output with a typical frequency of 5MHz, whereas, the output TIMEROUT is the oscillator output divided by an attribute TIMER\_DIV.

The attribute TIMER\_DIV can be: 128 (7 bits), 1024 (10 bits) or 1,048,576 (20 bits). The divided output is provided for those user situations, where a very slow clock is desired. If even a slower toggling clock is desired, then the programmable macrocell resources can be used to further divide down the TIMEROUT output.

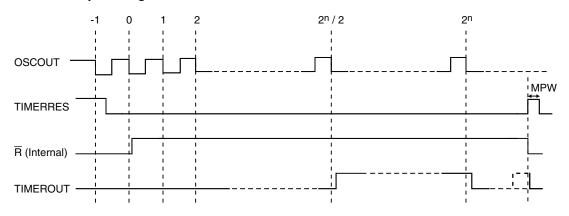

Figure 14 shows the simplified relationship among OSCOUT, TIMERRES and TIMEROUT. In the diagram, the signal " $\overline{R}$ " is an internal reset signal that is used to synchronize TIMERRES to OSCOUT. This adds one extra clock cycle delay for the first timer transition after TIMERRES.

Figure 14. Relationship Among OSCOUT, TIMERRES and TIMEROUT

Note: n = Number of bits in the divider (7, 10 or 20)

Metastability: If the signal TIMERRES is not synchronous to OSCOUT, it could make a difference of one or two clock cycles to the TIMEROUT going high the first time.

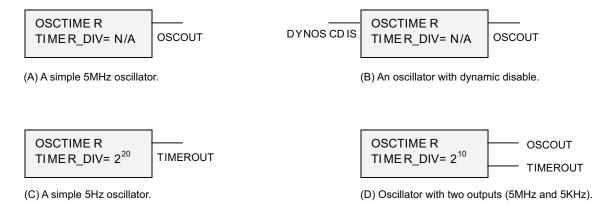

### **Some Simple Use Scenarios**

The following diagrams show a few simple examples that omit optional signals for the OSCTIMER block:

- A. An oscillator giving 5MHz nominal clock

- B. An oscillator that can be disabled with an external signal (5MHz nominal clock)

- C. An oscillator giving approximately 5 Hz nominal clock (TIMER\_DIV =  $2^{20}$  (1,048,576))

- D. An oscillator giving two output clocks: ~5MHz and ~5KHz (TIMER\_DIV= 2<sup>10</sup> (1,024))

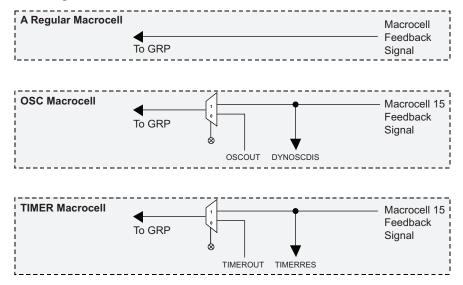

### **OSCTIMER Integration With CPLD Fabric**

The OSCTIMER is integrated into the CPLD fabric using the Global Routing Pool (GRP). The macrocell (MC) feedback path for two macrocells is augmented with a programmable multiplexer, as shown in Figure 15. The OSCTIMER outputs (OSCOUT and TIMEROUT) can optionally drive the GRP lines, whereas the macrocell outputs can drive the optional OSCTIMER inputs TIMERRES and DYNOSCDIS.

Figure 15. OSCTIMER Integration With CPLD Fabric

Table 12 shows how these two MCs are designated in each of the ispMACH4000ZE device.

Table 12. OSC and TIMER MC Designation

| Device         | Macrocell | Block Number | MC Number |

|----------------|-----------|--------------|-----------|

| ispMACH 4032ZE | OSC MC    | A            | 15        |

|                | TIMER MC  | B            | 15        |

| ispMACH 4064ZE | OSC MC    | A            | 15        |

|                | TIMER MC  | D            | 15        |

| ispMACH 4128ZE | OSC MC    | A            | 15        |

|                | TIMER MC  | G            | 15        |

| ispMACH 4256ZE | OSC MC    | C            | 15        |

|                | TIMER MC  | F            | 15        |

### Zero Power/Low Power and Power Management

The ispMACH 4000ZE family is designed with high speed low power design techniques to offer both high speed and low power. With an advanced E² low power cell and non sense-amplifier design approach (full CMOS logic approach), the ispMACH 4000ZE family offers fast pin-to-pin speeds, while simultaneously delivering low standby power without needing any "turbo bits" or other power management schemes associated with a traditional sense-amplifier approach.

The zero power ispMACH 4000ZE is based on the 1.8V ispMACH 4000Z family. With innovative circuit design changes, the ispMACH 4000ZE family is able to achieve the industry's lowest static power.

## **IEEE 1149.1-Compliant Boundary Scan Testability**

All ispMACH 4000ZE devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port operates with an LVCMOS interface that corresponds to the power supply voltage.

## I/O Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispMACH 4000ZE family of devices allows this by offering the user the ability to quickly configure the physical nature of the I/O cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM™ System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

## **IEEE 1532-Compliant In-System Programming**

Programming devices in-system provides a number of significant benefits including: rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispMACH 4000ZE devices provide In-System Programming (ISP™) capability through the Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains complaint to the IEEE 1149.1 standard. By using IEEE 1149.1 as the communication interface through which ISP is achieved, users get the benefit of a standard, well-defined interface. All ispMACH 4000ZE devices are also compliant with the IEEE 1532 standard.

The ispMACH 4000ZE devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispMACH 4000ZE devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common auto-

mated test equipment. This equipment can then be used to program ispMACH 4000ZE devices during the testing of a circuit board.

## **User Electronic Signature**

The User Electronic Signature (UES) allows the designer to include identification bits or serial numbers inside the device, stored in E<sup>2</sup>CMOS memory. The ispMACH 4000ZE device contains 32 UES bits that can be configured by the user to store unique data such as ID codes, revision numbers or inventory control codes.

## **Security Bit**

A programmable security bit is provided on the ispMACH 4000ZE devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

## **Hot Socketing**

The ispMACH 4000ZE devices are well-suited for applications that require hot socketing capability. Hot socketing a device requires that the device, during power-up and down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of I/O pin loading be minimal on active signals. The isp-MACH 4000ZE devices provide this capability for input voltages in the range 0V to 3.0V.

## **Density Migration**

The ispMACH 4000ZE family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# Absolute Maximum Ratings<sup>1, 2, 3, 4</sup>

- Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional

operation of the device at these or any other conditions above those indicated in the operational sections of this specification

is not implied.

- 2. Compliance with Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4. Please refer to the <u>Lattice ispMACH 4000V/B/C/ZC/ZE Product Family Qualification Summary</u> for complete data, including the ESD performance data.

- 5. Undershoot of -2V and overshoot of  $(V_{IH} (MAX) + 2V)$ , up to a total pin voltage of 6V is permitted for a duration of <20ns.

- 6. Maximum of 64 I/Os per device with VIN > 3.6V is allowed.

## **Recommended Operating Conditions**

| Symbol          |                                   | Parameter                  |                  |     | Units |

|-----------------|-----------------------------------|----------------------------|------------------|-----|-------|

| V               | Supply Voltage                    | Standard Voltage Operation | 1.7              | 1.9 | V     |

| V <sub>CC</sub> |                                   | Extended Voltage Operation | 1.6 <sup>1</sup> | 1.9 | V     |

| т               | Junction Temperature (Commercial) |                            | 0                | 90  | °C    |

| 1 j             | Junction Temperature (Industrial) |                            | -40              | 105 | °C    |

<sup>1.</sup> Devices operating at 1.6V can expect performance degradation up to 35%.

## **Erase Reprogram Specifications**

| Parameter             | Min.  | Max. | Units  |

|-----------------------|-------|------|--------|

| Erase/Reprogram Cycle | 1,000 | _    | Cycles |

Note: Valid over commercial temperature range.

## Hot Socketing Characteristics<sup>1,2,3</sup>

| Symbol | Parameter                    | Condition                               | Min. | Тур. | Max. | Units |

|--------|------------------------------|-----------------------------------------|------|------|------|-------|

| 1      | Input or I/O Leakage Current | $0 \le V_{IN} \le 3.0V$ , $Tj = 105$ °C | _    | ±30  | ±150 | μΑ    |

| IDK    | Input of 1/O Leakage Current | $0 \le V_{IN} \le 3.0V$ , $Tj = 130$ °C | _    | ±30  | ±200 | μΑ    |

<sup>1.</sup> Insensitive to sequence of  $V_{CCO}$  or  $V_{CCO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCO}$ , provided  $(V_{IN} - V_{CCO}) \le 3.6V$ .

<sup>2.</sup>  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCO} < V_{CCO}$  (MAX).

<sup>3.</sup>  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until fuse circuitry is active.

## I/O Recommended Operating Conditions

|                     | V <sub>CCC</sub> | <sub>O</sub> (V) <sup>1</sup> |

|---------------------|------------------|-------------------------------|

| Standard            | Min.             | Max.                          |

| LVTTL               | 3.0              | 3.6                           |

| LVCMOS 3.3          | 3.0              | 3.6                           |

| Extended LVCMOS 3.3 | 2.7              | 3.6                           |

| LVCMOS 2.5          | 2.3              | 2.7                           |

| LVCMOS 1.8          | 1.65             | 1.95                          |

| LVCMOS 1.5          | 1.4              | 1.6                           |

| PCI 3.3             | 3.0              | 3.6                           |

<sup>1.</sup> Typical values for  $\ensuremath{V_{\text{CCO}}}$  are the average of the min. and max. values.

### **DC Electrical Characteristics**

### **Over Recommended Operating Conditions**

| Symbol                                            | Parameter                             | Condition                                        | Min.                    | Тур. | Max.                    | Units |

|---------------------------------------------------|---------------------------------------|--------------------------------------------------|-------------------------|------|-------------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 2</sup> | Input Leakage Current                 | $0 \le V_{IN} < V_{CCO}$                         | _                       | 0.5  | 1                       | μΑ    |

| I <sub>IH</sub> <sup>1</sup>                      | Input High Leakage Current            | $V_{CCO} < V_{IN} \le 5.5V$                      | _                       | _    | 10                      | μΑ    |

| I <sub>PU</sub>                                   | I/O Weak Pull-up Resistor Current     | $0 \le V_{IN} \le 0.7V_{CCO}$                    | -20                     |      | -150                    | μΑ    |

| I <sub>PD</sub>                                   | I/O Weak Pull-down Resistor Current   | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)   | 30                      | _    | 150                     | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current       | V <sub>IN</sub> = V <sub>IL</sub> (MAX)          | 30                      |      | _                       | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current      | $V_{IN} = 0.7 V_{CCO}$                           | -20                     | _    | _                       | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current        | $0V \le V_{IN} \le V_{BHT}$                      | _                       | _    | 150                     | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current       | $V_{BHT} \le V_{IN} \le V_{CCO}$                 | _                       |      | -150                    | μΑ    |

| V <sub>BHT</sub>                                  | Bus Hold Trip Points                  | _                                                | V <sub>CCO</sub> * 0.35 | _    | V <sub>CCO</sub> * 0.65 | V     |

| C <sub>1</sub>                                    | I/O Capacitance <sup>3</sup>          | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 8    | _                       | pf    |

| O <sub>1</sub>                                    | 1/O Capacitance                       | $V_{CC}$ = 1.8V, $V_{IO}$ = 0 to $V_{IH}$ (MAX)  | _                       | 0    | _                       | ρι    |

| C                                                 | Clock Capacitance <sup>3</sup>        | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 6    | _                       | nf    |

| C <sub>2</sub>                                    | Опоск Сараспансе                      | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                       |      | _                       | pf    |

| C-                                                | Global Input Capacitance <sup>3</sup> | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 6    | _                       | nf    |

| C <sub>3</sub>                                    |                                       | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                       | O    | _                       | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup> I<sub>IH</sub> excursions of up to 1.5μA maximum per pin above the spec limit may be observed for certain voltage conditions on no more than 10% of the device's I/O pins.

<sup>3.</sup> Measured  $T_A = 25$ °C, f = 1.0MHz.

## **Supply Current**

To minimize transient current during power-on, configure CPLD I/Os to a pull-up or float state. If this logic scenario is not possible, then the recommended power sequence should assert VCC and VCCO at the same time or VCC before VCCO.

| Symbol                       | Parameter                      | Condition                                       | Min. | Тур. | Max. | Units |

|------------------------------|--------------------------------|-------------------------------------------------|------|------|------|-------|

| ispMACH 4                    | 032ZE                          |                                                 | •    | ,    | ,    |       |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 50   | _    | μΑ    |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 58   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 60   | _    | μΑ    |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 10   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 13   | 25   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 15   | 40   | μΑ    |

| ispMACH 4                    | 064ZE                          |                                                 | •    | ,    | ,    |       |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               |      | 80   | _    | μΑ    |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 89   | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 92   | _    | μΑ    |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 11   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 15   | 30   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 18   | 50   | μΑ    |

| ispMACH 4                    | 128ZE                          |                                                 | •    |      |      |       |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 168  | _    | μΑ    |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 190  | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 195  | _    | μΑ    |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 12   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 16   | 40   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 19   | 60   | μΑ    |

| ispMACH 4                    | 256ZE                          |                                                 |      |      |      |       |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 341  | _    | μΑ    |

| ICC <sup>1, 2, 3, 5, 6</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 361  | _    | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 372  | _    | μΑ    |

|                              |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C               | _    | 13   | _    | μΑ    |

| ICC <sup>4, 5, 6</sup>       | Standby Power Supply Current   | $Vcc = 1.9V, T_A = 0 \text{ to } 70^{\circ}C$   | _    | 32   | 65   | μΑ    |

|                              |                                | $Vcc = 1.9V, T_A = -40 \text{ to } 85^{\circ}C$ | _    | 43   | 100  | μΑ    |

<sup>1.</sup> Frequency = 1.0 MHz.

<sup>2.</sup> Device configured with 16-bit counters.

<sup>3.</sup>  $I_{CC}$  varies with specific device configuration and operating frequency.

<sup>4.</sup>  $V_{CCO}^{CCO} = 3.6V$ ,  $V_{IN} = 0V$  or  $V_{CCO}$ , bus maintenance turned off.  $V_{IN}$  above  $V_{CCO}$  will add transient current above the specified standby  $I_{CC}$ .

<sup>5.</sup> Includes  $V_{\mbox{\footnotesize CCO}}$  current without output loading.

<sup>6.</sup> This operating supply current is with the internal oscillator disabled. Enabling the internal oscillator adds approximately 15μA typical current plus additional current from any logic it drives.

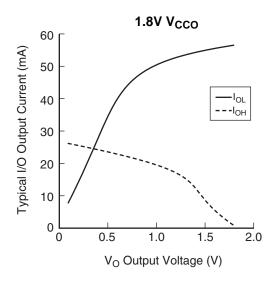

### I/O DC Electrical Characteristics

### **Over Recommended Operating Conditions**

|                         |         | V <sub>IL</sub>                     | V <sub>IH</sub>                     |         | V <sub>OL</sub>      | V <sub>OH</sub>         | l <sub>OL</sub> 1 | I <sub>OH</sub> <sup>1</sup> |

|-------------------------|---------|-------------------------------------|-------------------------------------|---------|----------------------|-------------------------|-------------------|------------------------------|

| Standard                | Min (V) | Max (V)                             | Min (V)                             | Max (V) | Max (V)              | Min (V)                 | (mA)              | (mA)                         |

| LVTTL                   | -0.3    | 0.80                                | 2.0                                 | 5.5     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0               | -4.0                         |

| LVIIL                   | -0.5    | 0.00                                | 2.0                                 | 5.5     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1               | -0.1                         |

| LVCMOS 3.3              | -0.3    | 0.80                                | 2.0                                 | 5.5     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0               | -4.0                         |

| EVOIVIOU 0.5            | -0.5    | 0.00                                | 2.0                                 | 3.5     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1               | -0.1                         |

| LVCMOS 2.5              | -0.3    | 0.70                                | 1.70                                | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0               | -4.0                         |

| LVOIVIOU 2.5            | -0.5    | 0.70                                | 1.70                                |         | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1               | -0.1                         |

| LVCMOS 1.8              | -0.3    | 0.35 * V <sub>CC</sub>              | 0.65 * V <sub>CC</sub>              | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0               | -2.0                         |

| LVOIVIOO 1.0            | -0.5    | 0.55 400                            | 0.03 400                            | 5.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1               | -0.1                         |

| LVCMOS 1.5 <sup>2</sup> | -0.3    | 0.35 * V <sub>CC</sub>              | 0.65 * V <sub>CC</sub>              | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0               | -2.0                         |

| LVCMOS 1.5              | -0.5    | 0.00 VCC                            | 0.00 \$00                           |         | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1               | -0.1                         |

| PCI 3.3                 | -0.3    | 0.3 * 3.3 * (V <sub>CC</sub> / 1.8) | 0.5 * 3.3 * (V <sub>CC</sub> / 1.8) | 5.5     | 0.1 V <sub>CCO</sub> | 0.9 V <sub>CCO</sub>    | 1.5               | -0.5                         |

<sup>1.</sup> The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the I/O bank, as shown in the logic signals connection table, shall not exceed *n*\*8mA. Where *n* is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

<sup>2.</sup> For 1.5V inputs, there may be an additional DC current drawn from  $V_{CC}$ , if the ispMACH 4000ZE  $V_{CC}$  and the  $V_{CC}$  of the driving device ( $V_{CC}$ d-d; that determines steady state  $V_{IH}$ ) are in the extreme range of their specifications. Typically, DC current drawn from  $V_{CC}$  will be  $2\mu$ A per input.

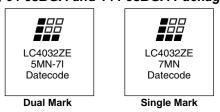

## ispMACH 4000ZE External Switching Characteristics

### **Over Recommended Operating Conditions**

|                                      |                                                                            | LC40 | 32ZE | LC4064ZE All De |      | evices |      |      |      |       |

|--------------------------------------|----------------------------------------------------------------------------|------|------|-----------------|------|--------|------|------|------|-------|

|                                      |                                                                            | -    | 4    | -               | 4    | •      | 5    | -    | 7    |       |

| Parameter                            | Description <sup>1, 2</sup>                                                | Min. | Max. | Min.            | Max. | Min.   | Max. | Min. | Max. | Units |

| t <sub>PD</sub>                      | 20-PT combinatorial propagation delay                                      | _    | 4.4  | _               | 4.7  |        | 5.8  | _    | 7.5  | ns    |

| t <sub>S</sub>                       | GLB register setup time before clock                                       | 2.2  | _    | 2.5             | _    | 2.9    | _    | 4.5  | _    | ns    |

| t <sub>ST</sub>                      | GLB register setup time before clock with T-type register                  | 2.4  | _    | 2.7             | _    | 3.1    | _    | 4.7  | _    | ns    |

| t <sub>SIR</sub>                     | GLB register setup time before clock, input register path                  | 1.0  | _    | 1.1             | _    | 1.3    | _    | 1.4  | _    | ns    |

| t <sub>SIRZ</sub>                    | GLB register setup time before clock with zero hold                        | 2.0  | _    | 2.1             | _    | 2.9    | _    | 4.0  | _    | ns    |

| t <sub>H</sub>                       | GLB register hold time after clock                                         | 0.0  | _    | 0.0             | _    | 0.0    | _    | 0.0  | _    | ns    |

| t <sub>HT</sub>                      | GLB register hold time after clock with T-type register                    | 0.0  | _    | 0.0             | _    | 0.0    | _    | 0.0  | _    | ns    |

| t <sub>HIR</sub>                     | GLB register hold time after clock, input register path                    | 1.0  | _    | 1.0             | _    | 1.3    | _    | 1.3  | _    | ns    |

| t <sub>HIRZ</sub>                    | GLB register hold time after clock, input register path with zero hold     | 0.0  | _    | 0.0             | _    | 0.0    | _    | 0.0  | _    | ns    |

| t <sub>CO</sub>                      | GLB register clock-to-output delay                                         | _    | 3.0  | _               | 3.2  | _      | 3.8  | _    | 4.5  | ns    |

| t <sub>R</sub>                       | External reset pin to output delay                                         |      | 5.0  | _               | 6.0  | _      | 7.5  | _    | 9.0  | ns    |

| t <sub>RW</sub>                      | External reset pulse duration                                              | 1.5  | _    | 1.7             | _    | 2.0    | _    | 4.0  | _    | ns    |

| t <sub>PTOE/DIS</sub>                | Input to output local product term output enable/disable                   | _    | 7.0  | _               | 8.0  | _      | 8.2  |      | 9.0  | ns    |

| t <sub>GPTOE/DIS</sub>               | Input to output global product term output enable/disable                  | _    | 6.5  | _               | 7.0  | _      | 10.0 | _    | 10.5 | ns    |

| t <sub>GOE/DIS</sub>                 | Global OE input to output enable/disable                                   | _    | 4.5  | _               | 4.5  | _      | 5.5  | _    | 7.0  | ns    |

| t <sub>CW</sub>                      | Global clock width, high or low                                            | 1.0  | _    | 1.5             | _    | 1.8    | _    | 2.8  | _    | ns    |

| t <sub>GW</sub>                      | Global gate width low (for low transparent) or high (for high transparent) | 1.0  | _    | 1.5             | _    | 1.8    | _    | 2.8  | _    | ns    |

| t <sub>WIR</sub>                     | Input register clock width, high or low                                    | 1.0  | _    | 1.5             | _    | 1.8    | _    | 2.8  | _    | ns    |

| f <sub>MAX</sub> (Int.) <sup>3</sup> | Clock frequency with internal feedback                                     | _    | 260  | _               | 241  |        | 200  | _    | 172  | MHz   |

| f <sub>MAX</sub> (Ext.)              | clock frequency with external feedback, $[1 / (t_S + t_{CO})]$             | _    | 192  |                 | 175  | _      | 149  | _    | 111  | MHz   |

<sup>1.</sup> Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

Timing v.0.8

<sup>2.</sup> Measured using standard switching GRP loading of 1 and 1 output switching.

<sup>3.</sup> Standard 16-bit counter using GRP feedback.

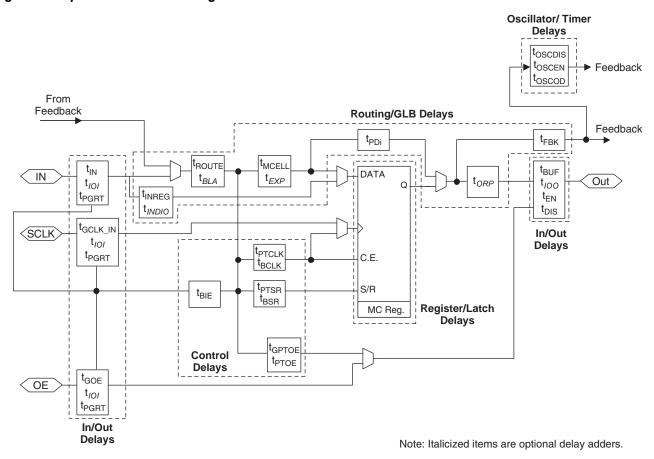

## **Timing Model**

The task of determining the timing through the ispMACH 4000ZE family, like any CPLD, is relatively simple. The timing model provided in Figure 16 shows the specific delay paths. Once the implementation of a given function is determined either conceptually or from the software report file, the delay path of the function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model for a particular design. Note that the internal timing parameters are given for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device. For more information on the timing model and usage, refer to TN1168, ispMACH 4000ZE Timing Model Design and Usage Guidelines.

Figure 16. ispMACH 4000ZE Timing Model

## **Over Recommended Operating Conditions**

|                      |                                                            | LC40 | 32ZE | LC40     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|----------------------|------------------------------------------------------------|------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                      |                                                            |      | 4    | -4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Parameter            | Description                                                | Min. | Max. | Min.     | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Units    |

| In/Out Delays        |                                                            |      | •    | 1        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •        |

| t <sub>IN</sub>      | Input Buffer Delay                                         | _    | 0.85 | _        | 0.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns       |

| t <sub>GCLK_IN</sub> | Global Clock Input Buffer Delay                            | _    | 1.60 | —        | 1.60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns       |

| t <sub>GOE</sub>     | Global OE Pin Delay                                        | _    | 2.25 | _        | 2.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns       |