# L9215A/G Short-Loop Sine Wave Ringing SLIC

# Introduction

The Agere Systems Inc. L9215 is a subscriber line interface circuit that is optimized for short-loop, power-sensitive applications. This device provides the complete set of line interface functionality (including power ringing) needed to interface to a subscriber loop. This device has the capability to operate with a Vcc supply of 3.3 V or 5 V and is designed to minimize external components required at all device interfaces.

#### Features

- Onboard ringing generation

- Three ringing input options:

- Sine wave

- -PWM

- Logic level square wave

- Flexible Vcc options:

5 V or 3.3 V Vcc

- No –5 V required

- Battery switch to minimize off-hook power

- 11 operating states:

- Scan mode for minimal power dissipation

- Forward and reverse battery active

- On-hook transmission states

- Meter pulse states

- Ring mode

- Disconnect mode

- Ultralow on-hook power:

- 27 mW scan mode

- 42 mW active mode

- Two SLIC gain options to minimal external components in codec interface

- Loop start, ring trip, and ground key detectors

- Software- or hardware-controllable current-limit and overhead voltage

- Meter pulse compatible

- 32-pin PLCC package

- 48-pin MLCC package

# Applications

- Voice over Internet Protocol (VoIP)

- Cable Modems

- Terminal Adapters (TA)

- Wireless Local Loop (WLL)

- *Telcordia Technologies*<sup>TM</sup> GR-909 Access

- Network Termination (NT)

- Key Systems

# Description

This device is optimized to provide battery feed, ringing, and supervision on short-loop plain old telephone service (POTS) loops.

This device provides power ring to the subscriber loop through amplification of a low-voltage input. It provides forward and reverse battery feed states, onhook transmission, a low-power scan state, meter pulse states, and a forward disconnect state.

The device requires a Vcc and battery to operate. Vcc may be either a 5 V or a 3.3 V supply. The ringing signal is derived from the high-voltage battery. A battery switch is included to allow for use of a lowervoltage battery in the off-hook mode, thus minimizing short-loop off-hook power.

Loop closure, ring trip, and ground key detectors are available. The loop closure detector has a fixed threshold with hysteresis. The ring trip detector requires a single-pole filter, thus minimizing external components required.

This device supports meter pulse applications. Meter pulse is injected into a dedicated meter pulse input. Injection of meter pulse onto tip and ring is controlled by the device's logic input pin.

Both the dc current limit and overhead voltage are programmable. Programming may be done by external resistors or an applied voltage source. If the voltage source is programmable, the current limit and overhead may be set via software control.

The device is offered with two gain options. This allows for an optimized codec interface, with minimal external components regardless of whether a firstgeneration or a programmable third-generation codec is used.

# **Table of Contents**

## Contents

# Page Contents

# Page

| Introduction                          | 1        |

|---------------------------------------|----------|

| Features                              | 1        |

| Applications                          | 1        |

| Description                           |          |

| Features                              |          |

| Description                           |          |

| Architecture Diagram                  |          |

| Pin Information                       |          |

| Operating States                      |          |

| State Definitions                     |          |

| Forward Active                        |          |

| Reverse Active                        |          |

| Forward Active with PPM               |          |

| Reverse Active with PPM               |          |

| Scan                                  |          |

| On-Hook Transmission—Forward Battery  | 12       |

| On-Hook Transmission with PPM—Forward |          |

| Battery                               |          |

| On-Hook Transmission—Reverse Battery  | 13       |

| On-Hook Transmission with PPM—Reverse |          |

| Battery                               |          |

| Disconnect                            |          |

| Ring                                  |          |

| Thermal Shutdown                      |          |

| Absolute Maximum Ratings              | 14       |

| Electrical Characteristics            |          |

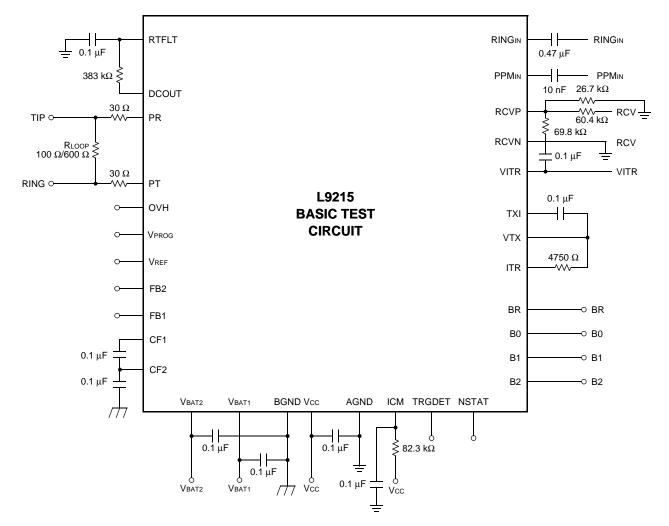

| Test Configurations                   |          |

| Applications                          |          |

| Power Control                         |          |

| dc Loop Current Limit                 | 24       |

| Overhead Voltage                      |          |

| Active Mode                           | ~ -      |

|                                       |          |

| On-Hook Transmission Mode             | 26       |

| Scan Mode                             | 26<br>26 |

|                                       | 26<br>26 |

| Loop Range                                 |    |

|--------------------------------------------|----|

| Battery Reversal Rate                      |    |

| Supervision                                |    |

| Loop Closure                               |    |

| Ring Trip                                  |    |

| Tip or Ring Ground Detector                |    |

| Power Ring                                 | 27 |

| Sine Wave Input Signal and Sine Wave Power |    |

| Ring Signal Output                         | 28 |

| PWM Input Signal and Sine Wave Power       |    |

| Ring Signal Output                         |    |

| 5 V Vcc Operation                          |    |

| 3.3 V Vcc Operation                        | 32 |

| Square Wave Input Signal and Trapezoidal   |    |

| Power Ring Signal Output                   |    |

| Periodic Pulse Metering (PPM)              |    |

| ac Applications                            |    |

| ac Parameters                              |    |

| Codec Types                                |    |

| First-Generation Codecs                    |    |

| Third-Generation Codecs                    |    |

| ac Interface Network                       |    |

| Design Examples                            | 35 |

| First-Generation Codec ac Interface        | ~- |

| Network—Resistive Termination              |    |

| Example 1, Real Termination                | 36 |

| First-Generation Codec ac Interface        | ~~ |

| Network—Complex Termination                | 39 |

| Complex Termination Impedance Design       | ~~ |

| Example                                    |    |

| ac Interface Using First-Generation Codec  |    |

| Set Zтg—Gain Shaping<br>Transmit Gain      |    |

| Receive Gain                               |    |

| Hybrid Balance                             |    |

| Blocking Capacitors                        |    |

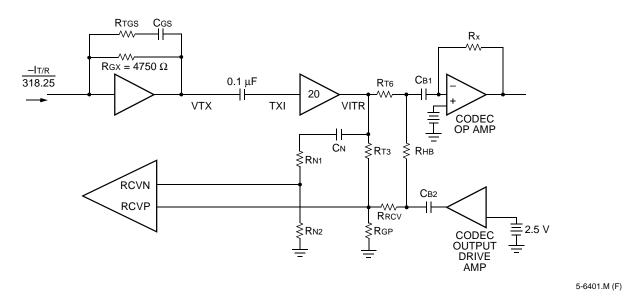

| Third-Generation Codec ac Interface        | 42 |

| Network—Complex Termination                | 15 |

| Outline Diagrams                           |    |

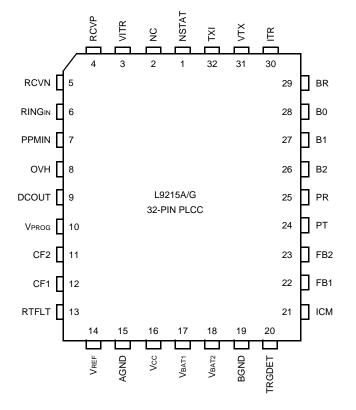

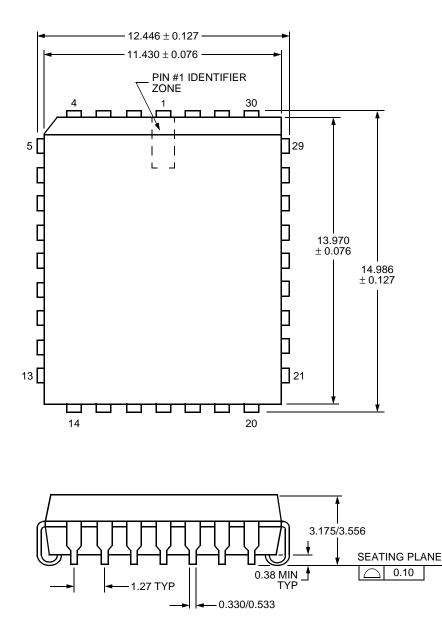

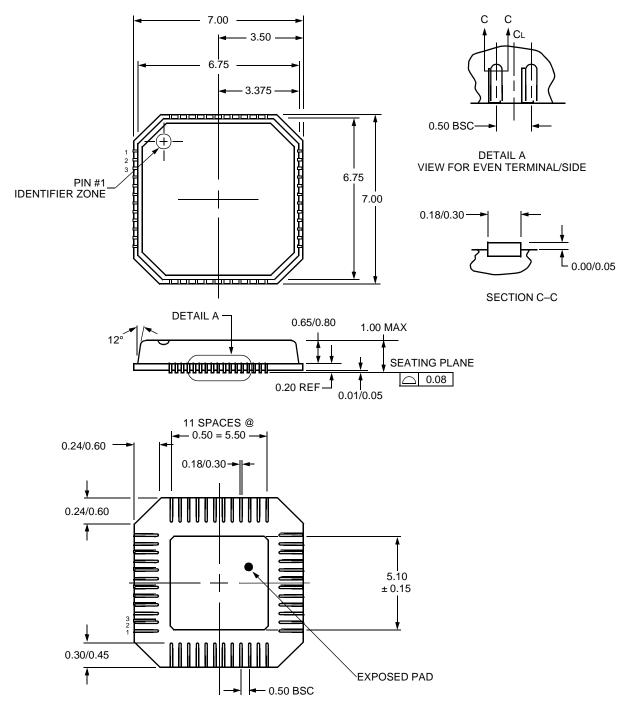

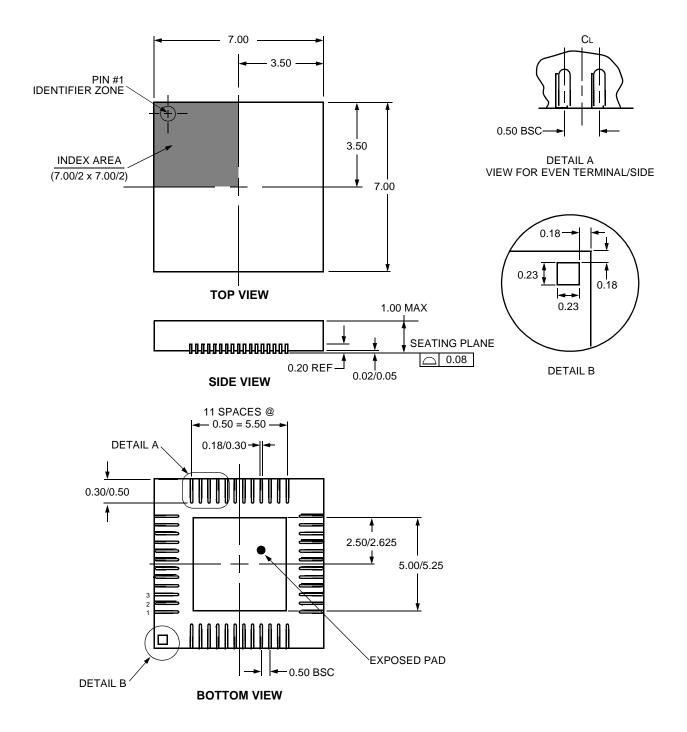

| 32-Pin PLCC                                | 47 |

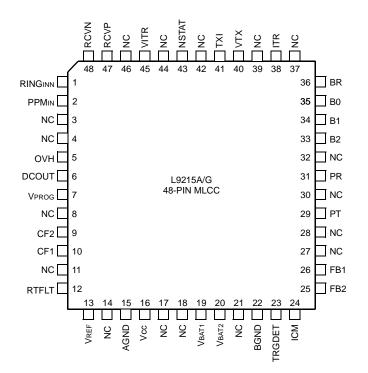

| 48-Pin MLCC                                |    |

| 48-Pin MLCC, JEDEC MO-220 VKKD-2           |    |

| Ordering Information                       |    |

| er den ny monnadorna                       | 00 |

# Table of Contents (continued)

# Figures

#### Page Tables

#### Page

| Figure 1. Architecture Diagram7                     |

|-----------------------------------------------------|

| Figure 2. 32-Pin PLCC Diagram8                      |

| Figure 3. 48-Pin MLCC Diagram8                      |

| Figure 4. Basic Test Circuit22                      |

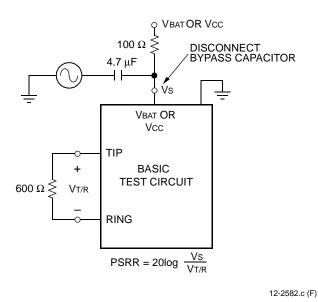

| Figure 5. Metallic PSRR23                           |

| Figure 6. Longitudinal PSRR23                       |

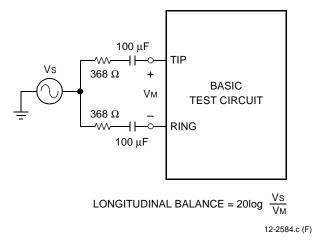

| Figure 7. Longitudinal Balance23                    |

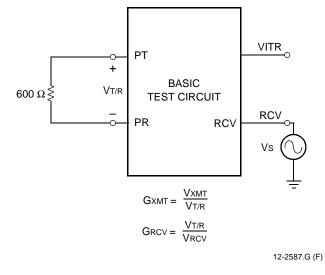

| Figure 8. ac Gains23                                |

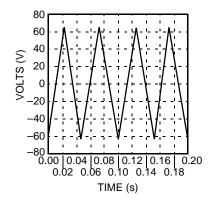

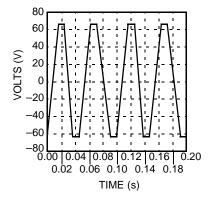

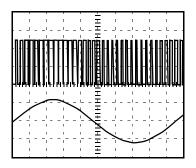

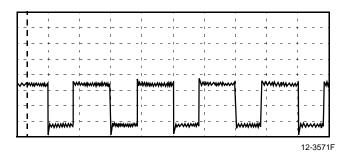

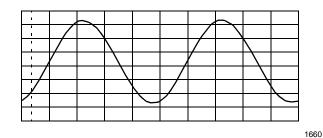

| Figure 9. Ringing Waveform Crest Factor = 1.627     |

| Figure 10. Ringing Waveform Crest Factor = 1.227    |

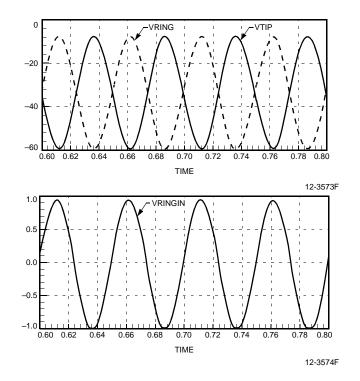

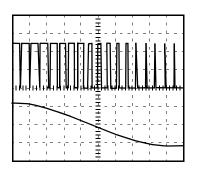

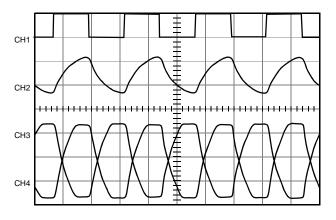

| Figure 11. Ring Mode Typical Operation28            |

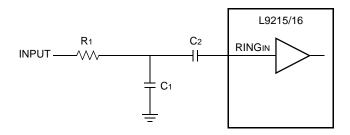

| Figure 12. RINGIN Operation                         |

| Figure 13. L9215/16 Ringing Input Circuit Selection |

| Table for Square Wave and PWM                       |

| Inputs                                              |

| Figure 14. Modulation Waveforms                     |

| Figure 15. 5 V PWM Signal Amplitude                 |

| Figure 16. Ringing Output on RING, with             |

| Vcc = 5 V                                           |

| Figure 17. 3.3 V PWM Signal Amplitude32             |

| Figure 18. Ringing Output on RING, with             |

| Vcc = 3.1 V                                         |

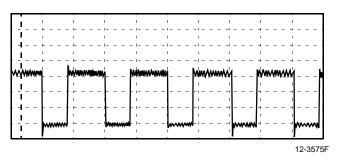

| Figure 19. Square Wave Input Signal and Trapezoidal |

| Power Ring Signal Output                            |

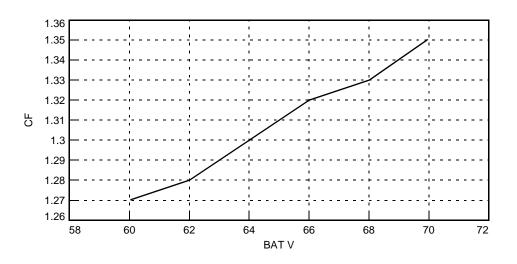

| Figure 20. Crest Factor vs. Battery Voltage         |

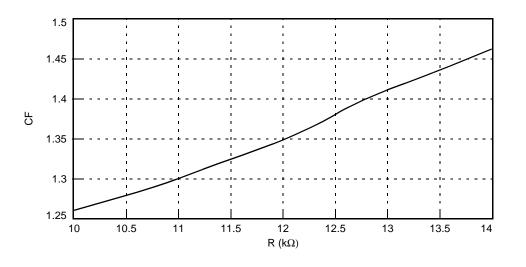

| Figure 21. Crest Factor vs. R (kΩ)33                |

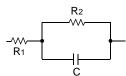

| Figure 22. ac Equivalent Circuit                    |

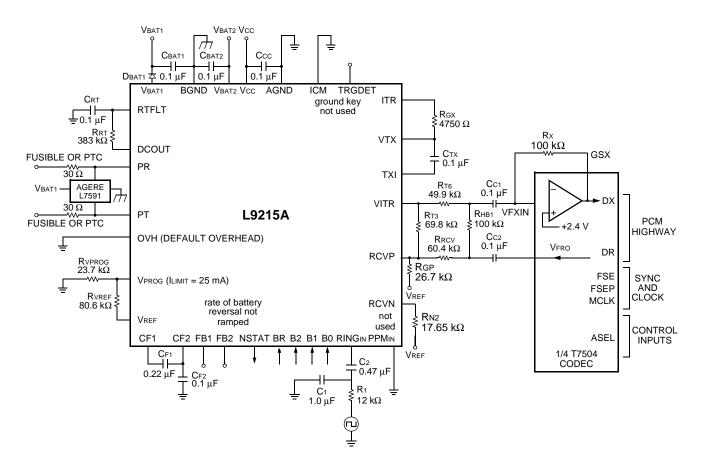

| Figure 23. Agere T7504 First-Generation Codec       |

| Resistive Termination; Nonmeter Pulse               |

| Application                                         |

| Figure 24. Interface Circuit Using First-Generation |

| Codec (Blocking Capacitors                          |

| Not Shown)40                                        |

| Figure 25. ac Interface Using First-Generation      |

| Codec (Including Blocking Capacitors)               |

| for Complex Termination Impedance42                 |

| Figure 26. Agere T7504 First-Generation Codec       |

| Complex Termination; Meter Pulse                    |

| Application                                         |

| Figure 27. Third-Generation Codec ac Interface      |

| Network; Complex Termination                        |

| Notwork, complex ronnination40                      |

| Table 1. Pin Descriptions                                                                                                        | 9        |

|----------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 2. Control States 1                                                                                                        |          |

| Table 3. Supervision Coding 1                                                                                                    | 1        |

| Table 4. Recommended Operating                                                                                                   |          |

| Characteristics 1                                                                                                                | 4        |

| Table 5. Thermal Characteristics 1                                                                                               |          |

| Table 6. Environmental Characteristics    1                                                                                      |          |

| Table 7. 5 V Supply Currents 1                                                                                                   |          |

| Table 8.5 V Powering                                                                                                             |          |

| Table 9. 3.3 V Supply Currents                                                                                                   |          |

| Table 10. 3.3 V Powering 1                                                                                                       |          |

| Table 11. 2-Wire Port       1         Table 12. Applag Dia Characteristica       1                                               |          |

| Table 12. Analog Pin Characteristics1Table 13. ac Feed Characteristics1                                                          |          |

| Table 13. ac reed Characteristics                                                                                                |          |

| Table 14. Logic inputs and Outputs ( $Vcc = 3.3 \text{ V}$ ) 2<br>Table 15. Logic inputs and Outputs ( $Vcc = 3.3 \text{ V}$ ) 2 | .0<br>20 |

| Table 16. Ringing Specifications                                                                                                 |          |

| Table 17. Ring Trip                                                                                                              |          |

| Table 18. PPM                                                                                                                    |          |

| Table 19. Typical Active Mode On- to Off-Hook                                                                                    | ••       |

| Tip/Ring Current-Limit Transient                                                                                                 |          |

| Response                                                                                                                         | 25       |

| Table 20. FB1 and FB2 Values vs. Typical                                                                                         |          |

| Ramp Time2                                                                                                                       | 6        |

| Table 21. Onset of Power Ringing Clipping                                                                                        |          |

| Vcc = 5 V, Cinput = 0.47 $\mu$ F2                                                                                                | 29       |

| Table 22. Onset of Power Ringing Clipping $Vcc = 3.1 \text{ V}$ , Cinput = 0.47 $\mu$ F                                          |          |

| Vcc = 3.1 V, Cinput = 0.47 $\mu$ F2                                                                                              | :9       |

| Table 23. Signal and Component Selection Chart 3                                                                                 | 0        |

| Table 24. Parts List L9215; Agere T7504                                                                                          |          |

| First-Generation Codec Resistive Termina-                                                                                        |          |

| tion; Nonmeter Pulse Application                                                                                                 | 8        |

| Table 25. Parts List L9215; Agere T7504                                                                                          |          |

| First-Generation Codec Complex Termina-                                                                                          |          |

| tion; Meter Pulse Application                                                                                                    | 4        |

| Table 26. Parts List L9215; Agere T8536<br>Third-Generation Codec Meter Pulse                                                    |          |

| Application ac and dc Parameters;                                                                                                |          |

| Fully Programmable                                                                                                               | G        |

|                                                                                                                                  | Ο        |

# Features

- Onboard balanced ringing generation:

- No ring relay

- No bulk ring generator required

- 15 Hz to 70 Hz ring frequency supported

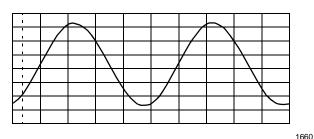

- Sine wave input-sine wave output

- PWM input-sine wave output

- Square wave input-trapezoidal output

- Power supplies requirements:

- Vcc talk battery and ringing battery required

- No -5 V supply required

- No high-voltage positive supply required

- Flexible Vcc options:

- 5 V or 3.3 V Vcc operation

- 5 V or 3.3 V Vcc interchangeable and transparent to users

- Logic-controlled battery switch:

Minimize off-hook power dissipation

- Minimal external components required

- 11 operating states:

- Forward active, VBAT2 applied

- Polarity reversal active, VBAT2 applied

- On-hook transmission, VBAT1 applied

- On-hook transmission polarity reversal, VBAT1 applied

- PPM active forward active, VBAT2 applied

- PPM active polarity reversal active, VBAT2 applied

- PPM active on-hook transmission, VBAT1 applied

- PPM active on-hook transmission polarity rever-

- sal, VBAT1 applied — Scan

- Forward disconnect

- Ring mode

- Unlatched parallel data control interface

- Ultralow SLIC power:

- Scan 38 mW (Vcc = 5 V)

- Forward/reverse active 57 mW (Vcc = 5 V)

- --- Scan 27 mW (Vcc = 3.3 V)

- Forward/reverse active 42 mW (Vcc = 3.3 V)

- Supervision:

- Loop start, fixed threshold with hysteresis

- Ring trip, single-pole ring trip filtering, fixed threshold as a function of battery voltage

- Common-mode current for ground key applications, user-adjustable threshold

- Adjustable current limit:

10 mA to 70 mA programming range

- Overhead voltage:

- Clamped typically <51 V differentially

- Clamped maximum <56.5 V single-ended

- Adjustable in active mode

- Thermal shutdown protection with hysteresis

- Longitudinal balance:

- ETSI/ITU-T balance

- Telcordia Technologies GR-909 balance

- Meter pulse compatible:

- Dedicated meter pulse signal input

- On-hook transmission of PPM

- ac interface:

- Two SLIC gain options to minimize external components required for interface to first- or third-generation codecs

- Sufficient dynamic range for direct coupling to codec output

- 32-pin PLCC package/48-pin MLCC package

- 90 V CBIC-S technology

# Description

The L9215 is designed to provide battery feed, ringing, and supervision functions on short plain old telephone service (POTS) loops. This device is designed for ultralow power in all operating states.

The L9215 offers 11 operating states. The device assumes use of a lower-voltage talk battery, a higher-voltage ringing battery, and a Vcc supply.

The L9215 requires only a positive Vcc supply. No –5 V supply is needed. The L9215 can operate with a Vcc of either 5 V or 3.3 V, allowing for greater user flexibility. The choice of Vcc voltage is transparent to the user; the device will function with either supply voltage connected.

Two batteries are used:

- 1. A high-voltage ring battery (VBAT1).

- VBAT1 is a maximum –75 V. VBAT1 is used for power ring signal amplification and for scan and on-hook transmission modes. This supply is current limited to approximately the maximum power ringing current, typically 50 mA.

- 2. A lower-voltage talk battery (VBAT2). VBAT2 is used for active mode powering.

# **Description** (continued)

Forward and reverse battery active modes are used for off-hook conditions. Since this device is designed for short-loop applications, the lower-voltage V<sub>BAT2</sub> is applied during the forward and reverse active states. Battery reversal is quiet, without breaking the ac path. Rate of battery reversal may be ramped to control switching time.

The magnitude of the overhead voltage in the forward and reverse active modes has a typical default value of 6.0 V, allowing for an undistorted signal of 3.14 dBm into 900  $\Omega$ . This overhead can be increased to accommodate higher signal levels and/or PPM. The ring trip detector is turned off during active modes to conserve power.

Because on-hook transmission is not allowed in the scan mode, an on-hook transmission mode is defined. This mode is functionally similar to the active mode, except the tip ring voltage is derived from the higher VBAT1 rather than VBAT2.

In the on-hook transmission modes with a primary battery whose magnitude is greater than a nominal 51 V, the magnitude of the tip-to-ground and ring-toground voltage is clamped at less than 56.5 V.

To minimize on-hook power, a low-power scan mode is available. In this mode, all functions except off-hook supervision are turned off to conserve power. On-hook transmission is not allowed in the scan mode.

In the scan mode with a primary battery whose magnitude is greater than a nominal 51 V, the magnitude of the tip-to-ground and ring-to-ground voltage is clamped at less than 56.5 V.

A forward disconnect mode is provided, where all circuits are turned off and power is denied to the loop.

The device offers a ring mode, in which a power ring signal is provided to the tip/ring pair. During the ring mode, a user-supplied, low-voltage ring signal (ac coupled) is input to the device's RINGIN input. This signal is amplified to produce the power ring signal. This signal may be a sine wave or filtered square wave to produce a sine wave on trapezoidal output. Ring trip detector and common-mode current detector are active during the ring mode.

This feature eliminates the need for a separate external ring relay, associated external circuitry, and a bulk ringing generator. See the Applications section of this data sheet for more information.

PPM is injected at the PPM<sub>IN</sub> pin (ac coupled). This is a high-impedance input that controls the PPM differential voltage on tip and ring. The PPM signal may be present at this pin at all times; however, PPM will only be transmitted to tip and ring during a PPM active mode. There are forward and reverse active, and forward and reverse on-hook transmission modes with PPM active.

No PPM shaping is done by the device. It is assumed that a shaped PPM input is presented to PPM<sub>IN</sub>.

The maximum allowed PPM current at the 200  $\Omega$  ac meter pulse load to avoid saturation of the device's internal AAC amplifier is 3 mArms. This signal level is sufficient to provide a minimum 200 mVrms to the 200  $\Omega$  PPM load under maximum specified dc loop conditions. Above 3 mArms PPM current, external meter pulse rejection may be required. See the Applications section of this data sheet for more information if on-hook transmission of PPM is required. Sufficient overhead to accommodate on-hook transmission must be programmed by the user at the OVH input.

Both the ring trip and loop closure supervision functions are included. The loop closure has a fixed typical 10.5 mA on- to off-hook threshold in the active mode and a fixed 11.5 mA on- to off-hook threshold from the scan mode. In either case, there is a 2 mA hysteresis. The ring trip detector requires only a single-pole filter at the input, minimizing external components. The ring trip threshold at a given battery voltage is fixed. Typical ring trip threshold is 42.5 mA for a -75 V V<sub>BAT1</sub>.

# Description (continued)

A common-mode current detector for tip or ring ground detection is included for ground key applications. The threshold is user programmable via external resistors. See the Applications section of this data sheet for more information on supervision functions.

Upon reaching the thermal shutdown temperature, the device will enter an all off mode. Upon cooling, the device will re-enter the state it was in prior to thermal shutdown. Hysteresis is built in to prevent oscillation.

Longitudinal balance is consistent with European ETSI and North American GR-909 requirements. Specifications are given in Table 6.

Data control is via a parallel unlatched control scheme.

The dc current limit is programmable in the active modes via an applied voltage source. The voltage source may be an external independent voltage source. Also, the programming voltage may be derived via a resistor divider network from the VREF SLIC output. A programmable external voltage source may be used to provide software control of the loop closure threshold. Design equations for this feature are given in the dc Loop Current Limit section of the Applications section of this data sheet.

Programming range is 10 mA to 70 mA with Vcc = 5 V and 10 mA to 45 mA with Vcc = 3.3 V. Programming accuracy is  $\pm 8\%$  at 22 mA to 28 mA current limit.

Circuitry is added to the L9215 to minimize the inrush of current from the Vcc supply and to the battery supply during an on- to off-hook transition, thus saving in power supply design cost. See the Applications section of this data sheet for more information.

Overhead is programmable in the active modes via an applied voltage source. The voltage source may be an external independent voltage source. Also the programming voltage may be derived via a resistor divider network from the VREF SLIC output.

If the overhead is not programmed, a default overhead of approximately 6.0 V is achieved. This is adequate for a 3.14 dBm overload into 900  $\Omega$ . For the default overhead, pin OVH is connected to ground. See the Applications section of this data sheet for more information.

Transmit and receive gains have been chosen to minimize the number of external components required in the SLIC-codec ac interface, regardless of the choice of codec. The L9215 uses a voltage feed-current sense architecture; thus, the transmit gain is a transconductance. The L9215 transconductance is set via a single external resistor, and this device is designed for optimal performance with a transconductance set at 300 V/A.

The L9215 offers an option for a single-ended to differential receive gain of either 8 or 2. These options are mask programmable at the factory and are selected by choice of code.

A receive gain of 8 is more appropriate when choosing a first-generation type codec where termination impedance, hybrid balance, and overall gains are set by external analog filters. The higher gain is typically required for synthesization of complex termination impedance.

A receive gain of 2 is more appropriate when choosing a third-generation type codec. Third-generation codecs will synthesize termination impedance and set hybrid balance and overall gains. To accomplish these functions, third-generation codecs typically have both analog and digital gain filters. For optimal signal-to-noise performance, it is best to operate the codec at a higher gain level. If the SLIC then provides a high gain, the SLIC output may be saturated causing clipping distortion of the signal at tip and ring. To avoid this situation, with a higher gain SLIC, external resistor dividers are used. These external components are not necessary with the lower gain offered by the L9215. See the Applications section of this data sheet for more information.

The L9215 is internally referenced to 1.5 V. This reference voltage is output at the VREF output of the device. The SLIC output VITR is also referenced to 1.5 V; therefore, it must be ac coupled to the codec input. However, the SLIC inputs RCVP/RCVN are floating inputs. If there is not feedback from RCVP/RCVN to VITR, RCVP/RCVN may be directly coupled to the codec output. If there is feedback from RCVP/RCVN to VITR, RCVP/RCVN must be ac coupled to the codec output.

The L9215 is packaged in a 32-pin PLCC surfacemount package and a 48-pin MLCC ultrasmall surfacemount package. Use L9215A for gain of 8 applications and L9215G for gain of 2 applications.

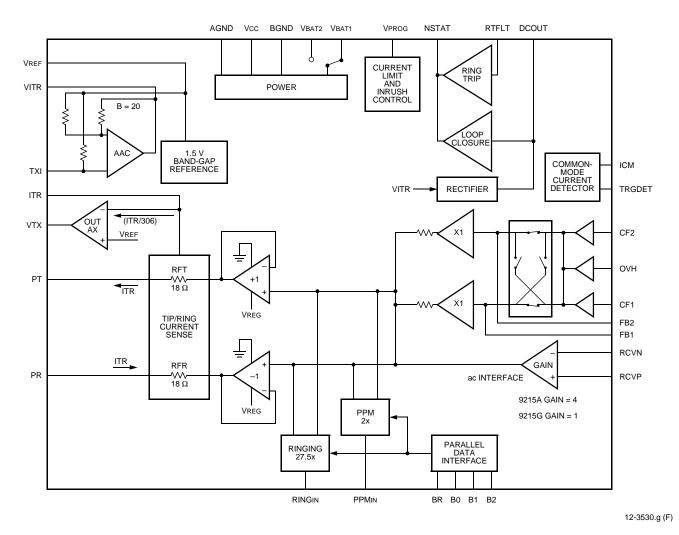

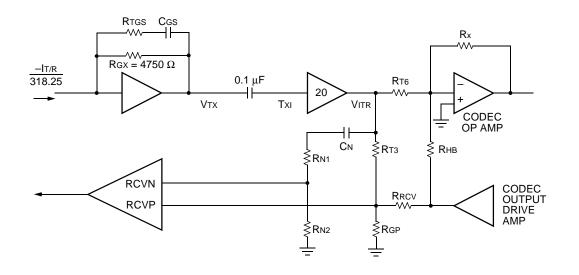

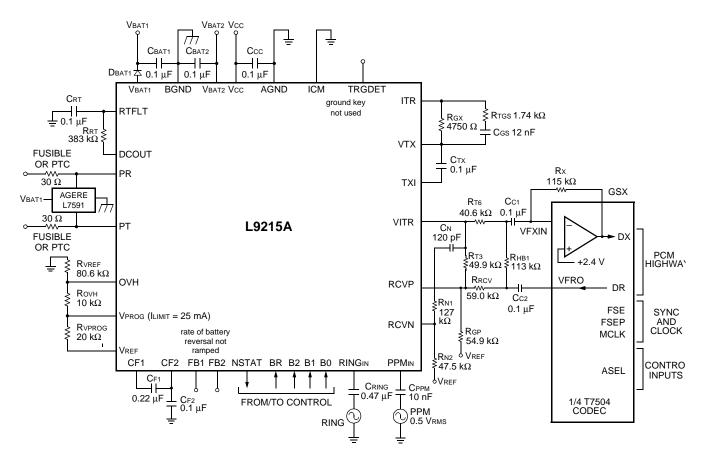

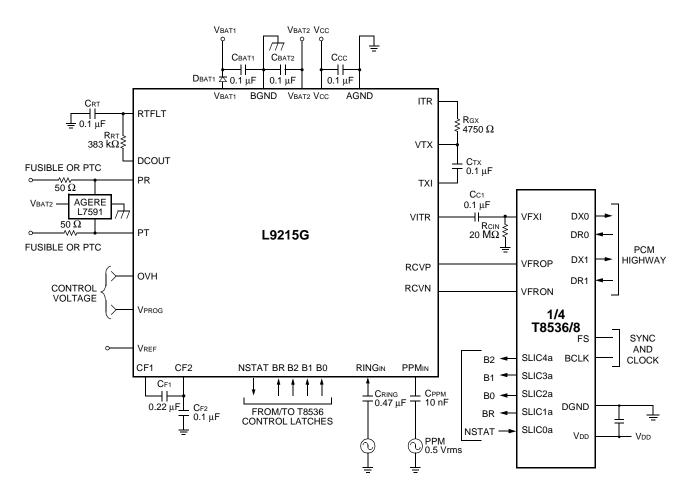

# **Architecture Diagram**

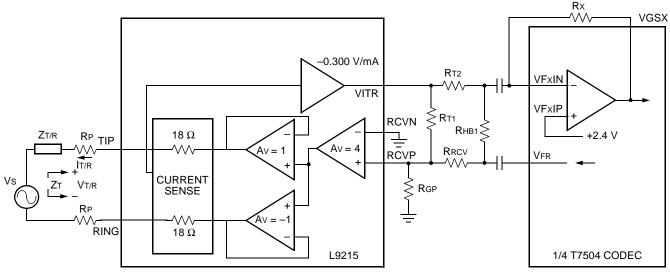

Figure 1. Architecture Diagram

# **Pin Information**

# Pin Information (continued)

## Table 1. Pin Descriptions

| 32-Pin<br>PLCC | 48-Pin<br>MLCC                                                              | Symbol | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-----------------------------------------------------------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 43                                                                          | NSTAT  | 0    | <b>Loop Closure Detector Output—Ring Trip Detector Output.</b> When low, this logic output indicates that an off-hook condition exists or ringing is tripped.                                                                                                                                                                                                                                                                                                              |

| 2              | 3, 4, 8, 11,<br>14, 17, 18,<br>21, 27, 28,<br>30, 32, 37,<br>39, 42, 44, 46 | NC     |      | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3              | 45                                                                          | VITR   | 0    | <b>Transmit ac Output Voltage.</b> Output of internal AAC amplifier. This output is a voltage that is directly proportional to the differential ac tip/ ring current.                                                                                                                                                                                                                                                                                                      |

| 4              | 47                                                                          | RCVP   | Ι    | <b>Receive ac Signal Input (Noninverting).</b> This high-impedance input controls to ac differential voltage on tip and ring. This node is a floating input.                                                                                                                                                                                                                                                                                                               |

| 5              | 48                                                                          | RCVN   | I    | <b>Receive ac Signal Input (Inverting).</b> This high-impedance input con-<br>trols to ac differential voltage on tip and ring. This node is a floating<br>input.                                                                                                                                                                                                                                                                                                          |

| 6              | 1                                                                           | RINGIN | I    | <b>Power Ring Signal Input.</b> ac-couple to a sine wave or lower crest factor low-voltage ring signal. The input here is amplified to provide the full-power ring signal at tip and ring. This signal may be applied continuously, even during nonringing states.                                                                                                                                                                                                         |

| 7              | 2                                                                           | PPMin  | Ι    | <b>Receive PPM Signal Input.</b> ac-couple to a 12 kHz or 16 kHz PPM signal. The input here is amplified to provide the differential PPM voltage on tip and ring. This signal may be applied continuously, even during non-PPM modes.                                                                                                                                                                                                                                      |

| 8              | 5                                                                           | OVH    | I    | <b>Overhead Voltage Program Input.</b> Connect a voltage source to this point to program the overhead voltage. Voltage source may be external or derived via a resistor divider from VREF. A programmable external voltage source may be used to provide software control of the overhead voltage. If a resistor or voltage source is not connected, the overhead voltage will default to a nominal 6.0 V. If the default overhead is desired, connect this pin to ground. |

| 9              | 6                                                                           | DCOUT  | 0    | <b>dc Output Voltage.</b> This output is a voltage that is directly proportional to the absolute value of the differential tip/ring current. This is used to set ring trip threshold.                                                                                                                                                                                                                                                                                      |

| 10             | 7                                                                           | Vprog  | Ι    | <b>Current-Limit Program Input.</b> Connect a voltage source to this point to program the dc current limit. Voltage source may be external or derived via a resistor divider from VREF. A programmable external voltage source may be used to provide software control of the current limit.                                                                                                                                                                               |

| 11             | 9                                                                           | CF2    | —    | Filter Capacitor. Connect a capacitor from this node to ground.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12             | 10                                                                          | CF1    |      | Filter Capacitor. Connect a capacitor from this node to CF2.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13             | 12                                                                          | RTFLT  | —    | <b>Ring Trip Filter.</b> Connect this lead to DCOUT via a resistor and to AGND with a capacitor to filter the ring trip circuit to prevent spurious responses. A single-pole filter is needed.                                                                                                                                                                                                                                                                             |

| 14             | 13                                                                          | Vref   | 0    | <b>SLIC Internal Reference Voltage.</b> Output of internal 1.5 V reference voltage.                                                                                                                                                                                                                                                                                                                                                                                        |

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| 32-Pin<br>PLCC | 48-Pin<br>MLCC | Symbol | Туре | Name/Function                                                                                                                                                                                                                  |

|----------------|----------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             | 15             | AGND   | GND  | Analog Signal Ground.                                                                                                                                                                                                          |

| 16             | 16             | Vcc    | PWR  | <b>Analog Power Supply.</b> User choice of 5 V or 3.3 V nominal power or supply.                                                                                                                                               |

| 17             | 19             | VBAT1  | PWR  | Battery Supply 1. High-voltage battery.                                                                                                                                                                                        |

| 18             | 20             | VBAT2  | PWR  | Battery Supply 2. Lower-voltage battery.                                                                                                                                                                                       |

| 19             | 22             | BGND   | GND  | Battery Ground. Ground return for the battery supplies.                                                                                                                                                                        |

| 20             | 23             | TRGDET | 0    | <b>Tip/Ring Ground Detect.</b> When high, this open collector output indicates the presence of a ring ground or a tip ground. This supervision output may be used in ground key or common-mode fault detection applications.   |

| 21             | 24             | ICM    | Ι    | <b>Common-Mode Current Sense.</b> To program tip or ring ground sense threshold, connect a resistor to Vcc and connect a capacitor to AGND to filter 50/60 Hz. If unused, the pin is connected to ground.                      |

| 22             | 25             | FB2    | _    | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node for controlling rate of battery reversal. If ramped battery reversal is not desired, this pin is left open.                                    |

| 23             | 26             | FB1    | _    | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node for controlling rate of battery reversal. If ramped battery reversal is not desired, this pin is left open.                                    |

| 24             | 29             | PT     | I/O  | <b>Protected Tip.</b> The output drive of the tip amplifier and input to the loop sensing circuit. Connect to loop through overvoltage and overcurrent protection.                                                             |

| 25             | 31             | PR     | I/O  | <b>Protected Ring.</b> The output drive of the ring amplifier and input to the loop sensing circuit. Connect to loop through overvoltage and overcurrent protection.                                                           |

| 26             | 33             | B2     | lu   | State Control Input. These pins have an internal 60 k $\Omega$ pull-up.                                                                                                                                                        |

| 27             | 34             | B1     |      |                                                                                                                                                                                                                                |

| 28             | 35             | B0     |      |                                                                                                                                                                                                                                |

| 29             | 36             | BR     |      |                                                                                                                                                                                                                                |

| 30             | 38             | ITR    | Ι    | <b>Transmit Gain.</b> Input to AX amplifier. Connect a resistor from this node to VTX to set transmit gain. Gain shaping for termination impedance with a COMBO I codec is also achieved with a network from this node to VTX. |

| 31             | 40             | VTX    | 0    | <b>ac Output Voltage.</b> Output of internal AX amplifier. The voltage at this pin is directly proportional to the differential tip/ring current.                                                                              |

| 32             | 41             | TXI    | Ι    | ac/dc Separation. Input to internal AAC amplifier. Connect a 0.1 $\mu F$ capacitor from this pin to VTX.                                                                                                                       |

# **Operating States**

#### Table 2. Control States

| B0 | B1 | B2 | BR | State                                                                          |

|----|----|----|----|--------------------------------------------------------------------------------|

| 1  | 1  | 0  | 1  | Forward active                                                                 |

| 1  | 1  | 0  | 0  | Forward active with PPM                                                        |

| 1  | 0  | 0  | 1  | Reverse active                                                                 |

| 1  | 0  | 0  | 0  | Reverse active with PPM                                                        |

| 1  | 1  | 1  | 1  | On-hook transmission forward battery (in this state, the device will power up) |

| 1  | 1  | 1  | 0  | On-hook transmission with PPM forward battery                                  |

| 1  | 0  | 1  | 1  | On-hook transmission reverse battery                                           |

| 1  | 0  | 1  | 0  | On-hook transmission with PPM reverse battery                                  |

| 0  | 1  | 1  | 1  | Scan                                                                           |

| 0  | 0  | 0  | 1  | Disconnect                                                                     |

| 0  | 1  | 1  | 0  | Ring                                                                           |

#### Table 3. Supervision Coding

| NSTAT                                                                                                | TRGDET                                              |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 0 = off-hook or ring trip or TSD.<br>1 = on-hook and no ring trip and no<br>TSD or DISCONNECT state. | 0 = no ring or tip ground<br>1 = ring or tip ground |

# **State Definitions**

# **Forward Active**

- Pin PT is positive with respect to PR.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- PPM input is off.

- Overhead is set to nominal 6.0 V for undistorted transmission of 3.14 dBm into 900 Ω and may be increased via OVH.

# **Reverse Active**

- Pin PR is positive with respect to PT.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- PPM input is off.

- Overhead is set to nominal 6.0 V for undistorted transmission of 3.14 dBm into 900 Ω and may be increased via OVH.

# Forward Active with PPM

- Pin PT is positive with respect to PR.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- PPM input is on.

- Overhead is set to nominal 6.0 V for undistorted transmission of 3.14 dBm into 900 Ω and may be increased via OVH to accommodate higher-voltage meter pulse signals.

## **Reverse Active with PPM**

- Pin PR is positive with respect to PT.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- PPM input is on.

- Overhead is set to nominal 6.0 V for undistorted transmission of 3.14 dBm into 900 Ω and may be increased via OVH to accommodate higher-voltage meter pulse signals.

## Scan

- Except for loop closure, all circuits (including ring trip and common-mode detector) are powered down.

- On-hook transmission is disabled.

- Pin PT is positive with respect to PR and VBAT1 is applied to tip/ring.

- The tip-to-ring on-hook differential voltage will be typically between -44 V and -51 V with a -70 V primary battery.

# **On-Hook Transmission—Forward Battery**

- Pin PT is positive with respect to PR.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and commonmode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip-to-ring on-hook differential voltage will be between –41 V and –49 V with a –70 V primary battery.

- PPM is off.

## State Definitions (continued)

# On-Hook Transmission with PPM—Forward Battery

- Pin PT is positive with respect to PR.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and commonmode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip-to-ring on-hook differential voltage will be between -41 V and -49 V with a -70 V primary battery.

- PPM is on.

#### **On-Hook Transmission—Reverse Battery**

- Pin PR is positive with respect to PT.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and commonmode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip-to-ring on-hook differential voltage will be between -41 V and -49 V with a -70 V primary battery.

- PPM is off.

# On-Hook Transmission with PPM—Reverse Battery

- Pin PR is positive with respect to PT.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and commonmode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip-to-ring on-hook differential voltage will be between -41 V and -49 V with a -70 V primary battery.

- PPM is on.

### Disconnect

- The tip/ring amplifiers and all supervision are turned off.

- The SLIC goes into a high-impedance state.

- NSTAT is forced high (on-hook).

#### Ring

- Power ring signal is applied to tip and ring.

- Input waveform at RINGIN is amplified.

- Ring trip supervision and common-mode current supervision are active; loop closure is inactive.

- Overhead voltage is reduced to typically 4 V, regardless of programming on OVH, and current limit set at VPROG is disabled.

- Current is limited by saturation current of the amplifiers themselves, typically 100 mA at 125 °C.

## Thermal Shutdown

- Not controlled via truth table inputs.

- NSTAT is forced low (off-hook) during this state

- This mode is caused by excessive heating of the device, such as may be encountered in an extended power cross situation.

# Absolute Maximum Ratings (@ TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                  | Symbol   | Min       | Тур | Max       | Unit |

|--------------------------------------------|----------|-----------|-----|-----------|------|

| dc Supply (Vcc)                            | —        | -0.5      | _   | 7.0       | V    |

| Battery Supply (VBAT1)                     | —        | —         |     | -80       | V    |

| Battery Supply (VBAT2)                     | —        | —         |     | VBAT1     | V    |

| Logic Input Voltage                        | —        | -0.5      | _   | Vcc + 0.5 | V    |

| Logic Output Voltage                       | —        | -0.5      | _   | Vcc + 0.5 | V    |

| Operating Temperature Range                | —        | -40       |     | 125       | °C   |

| Storage Temperature Range                  | —        | -40       | _   | 150       | °C   |

| Relative Humidity Range                    | —        | 5         | _   | 95        | %    |

| Ground Potential Difference (BGND to AGND) | —        | —         | _   | ±1        | V    |

| PT or PR Fault Voltage (dc)                | Vpt, Vpr | Vbat – 5  | —   | 3         | V    |

| PT or PR Fault Voltage (10 x 1000 μs)      | Vpt, Vpr | Vbat – 15 | _   | 15        | V    |

Note: The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. For example, inductance in a supply lead could resonate with the supply filter capacitor to cause a destructive overvoltage.

#### **Table 4. Recommended Operating Characteristics**

| Parameter                               | Min  | Тур | Max   | Unit |

|-----------------------------------------|------|-----|-------|------|

| 5 V dc Supplies (Vcc)                   |      | 5.0 | 5.25  | V    |

| 3 V dc Supplies (Vcc)                   | 3.13 | 3.3 | —     | V    |

| High Office Battery Supply (VBAT1)      | -60  | -70 | -75   | V    |

| Auxiliary Office Battery Supply (VBAT2) | -12  | —   | VBAT1 | V    |

| Operating Temperature Range             | -40  | 25  | 85    | °C   |

#### Table 5. Thermal Characteristics

| Parameter                                                                                                                                                                                                                                                            | Min  | Тур                          | Max | Unit                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|-----|------------------------------|

| Thermal Protection Shutdown (Tjc)                                                                                                                                                                                                                                    | 150  | 165                          |     | °C                           |

| 32-pin PLCC Thermal Resistance Junction to Ambient (θJA) <sup>1, 2</sup> :<br>Natural Convection 2S2P Board<br>Natural Convection 2S0P Board<br>Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S2P Board<br>Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S0P Board | <br> | 35.5<br>50.5<br>31.5<br>42.5 |     | °C/W<br>°C/W<br>°C/W<br>°C/W |

| 48-pin MLCC Thermal Resistance Junction to Ambient $(\theta_{JA})^{1, 2}$                                                                                                                                                                                            |      | 38                           |     | °C/W                         |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

2. Airflow, PCB board layers, and other factors can greatly affect this parameter.

# **Electrical Characteristics**

#### **Table 6. Environmental Characteristics**

| Parameter                   | Min | Тур | Max             | Unit |

|-----------------------------|-----|-----|-----------------|------|

| Temperature Range           | -40 | _   | 85              | °C   |

| Humidity Range <sup>1</sup> | 5   |     | 95 <sup>1</sup> | %RH  |

1. Not to exceed 26 grams of water per kilogram of dry air.

#### Table 7. 5 V Supply Currents

VBAT1 = -70 V, VBAT2 = -21 V, VCC = 5 V.

| Parameter                                                                      | Min | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------|-----|------|------|------|

| Supply Currents (scan state; no loop current):                                 |     |      |      |      |

| lvcc                                                                           |     | 4.30 | 4.80 | mA   |

| IVBAT1                                                                         |     | 0.24 | 0.35 | mA   |

| IVBAT2                                                                         |     | 3    | 6    | μΑ   |

| Supply Currents (forward/reverse active; no loop current, with or without PPM, |     |      |      |      |

| VBAT2 applied):                                                                |     |      |      |      |

| lvcc                                                                           |     | 5.95 | 7.0  | mA   |

| IVBAT1                                                                         |     | 25   | 85   | μΑ   |

| IVBAT2                                                                         |     | 1.2  | 1.40 | mA   |

| Supply Currents (on-hook transmission mode; no loop current, with or without   |     |      |      |      |

| PPM, VBAT1 applied):                                                           |     |      |      |      |

| lvcc                                                                           |     | 6.0  | 7.0  | mA   |

| IVBAT1                                                                         | —   | 1.5  | 1.9  | mA   |

| IVBAT2                                                                         |     | 1.5  | 6    | μΑ   |

| Supply Currents (disconnect mode):                                             |     |      |      |      |

| lvcc                                                                           |     | 2.7  | 3.75 | mA   |

| IVBAT1                                                                         |     | 15   | 110  | μΑ   |

| IVBAT2                                                                         |     | 3.5  | 25   | μΑ   |

| Supply Currents (ring mode; no load):                                          |     |      |      |      |

| lvcc                                                                           | —   | 5.9  | 6.5  | mA   |

| IVBAT1                                                                         | —   | 1.8  | 2.2  | mA   |

| IVBAT2                                                                         | —   | 2    | 6    | μA   |

#### Table 8. 5 V Powering

$V_{BAT1} = -70 \text{ V}, \text{ V}_{BAT2} = -21 \text{ V}, \text{ V}_{CC} = 5 \text{ V}.$

| Parameter                                                                        | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------|-----|-----|-----|------|

| Power Dissipation (scan state; no loop current)                                  | _   | 38  | 46  | mW   |

| Power Dissipation (forward/reverse active; no loop current, with or without PPM) | _   | 57  | 64  | mW   |

| Power Dissipation (on-hook transmission mode; no loop current, with or without   |     |     |     |      |

| PPM, VBAT1 applied)                                                              | —   | 135 | 165 | mW   |

| Power Dissipation (disconnect mode)                                              | _   | 14  | 23  | mW   |

| Power Dissipation (ring mode; no load)                                           |     | 156 | 184 | mW   |

## Table 9. 3.3 V Supply Currents

$V_{BAT1} = -70 \text{ V}, \text{ V}_{BAT2} = -21 \text{ V}, \text{ V}_{CC} = 3.3 \text{ V}.$

| Parameter                                                                   | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------|-----|------|------|------|

| Supply Currents (scan state; no loop current):                              |     |      |      |      |

| Ivcc                                                                        | —   | 3.2  | 3.6  | mA   |

| IVBAT1                                                                      | —   | 0.24 | 0.35 | mA   |

| IVBAT2                                                                      | —   | 3    | 6    | μA   |

| Supply Currents (forward/reverse active; no loop current, with/without PPM, |     |      |      |      |

| VBAT2 applied):                                                             |     |      |      |      |

| Ivcc                                                                        | —   | 4.8  | 5.7  | mA   |

| IVBAT1                                                                      | —   | 25   | 85   | μA   |

| IVBAT2                                                                      | —   | 1.2  | 1.4  | mA   |

| Supply Currents (on-hook transmission mode; no loop current, with/without   |     |      |      |      |

| PPM, VBAT1 applied):                                                        |     |      |      |      |

| Ivcc                                                                        | —   | 4.9  | 5.7  | mA   |

| IVBAT1                                                                      | —   | 1.5  | 1.9  | mA   |

| IVBAT2                                                                      | —   | 1.5  | 6    | μA   |

| Supply Currents (disconnect mode):                                          |     |      |      |      |

| lvcc                                                                        | —   | 1.8  | 2.5  | mA   |

| IVBAT1                                                                      | —   | 8    | 110  | μA   |

| IVBAT2                                                                      | —   | 2    | 25   | μA   |

| Supply Currents (ring mode; no loop current):                               |     |      |      |      |

| lvcc                                                                        | —   | 4.70 | 5.4  | mA   |

| VBAT1                                                                       | —   | 1.8  | 2.2  | mA   |

| IVBAT2                                                                      | —   | 2    | 6    | μA   |

#### Table 10. 3.3 V Powering

VBAT1 = -70 V, VBAT2 = -21 V, VCC = 3.3 V.

| Parameter                                                                                       | Min | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Power Dissipation (scan state; no loop current)                                                 |     | 27  | 36.5 | mW   |

| Power Dissipation (forward/reverse active; no loop current, with/without PPM, VBAT2 applied)    | _   | 42  | 53   | mW   |

| Power Dissipation (on-hook transmission mode; no loop current, with/without PPM, VBAT1 applied) | _   | 121 | 151  | mW   |

| Power Dissipation (disconnect mode)                                                             | _   | 6.5 | 15   | mW   |

| Power Dissipation (ring mode; no loop current)                                                  |     |     |      |      |

|                                                                                                 | —   | 141 | 172  | mW   |

#### Table 11. 2-Wire Port

| Parameter                                                                                                                                                | Min               | Тур            | Max                     | Unit          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------------------------|---------------|

| Tip or Ring Drive Current = dc + Longitudinal + Signal Currents + PPM                                                                                    | 105               |                |                         | mAp           |

| Tip or Ring Drive Current = Ringing + Longitudinal                                                                                                       | 65                |                |                         | mAp           |

| Signal Current                                                                                                                                           | 10                |                |                         | mArms         |

| Longitudinal Current Capability per Wire (Longitudinal current is indepen-<br>dent of dc loop current.)                                                  | 8.5               | 15             |                         | mArms         |

| PPM Signal Current = 1.25 VMAX into 200 $\Omega$ ac                                                                                                      | 6.25              |                | _                       | mArms         |

| Ringing Current (RLOAD = 1386 $\Omega$ + 40 $\mu$ F)                                                                                                     | 29                | _              | _                       | mArms         |

| Ringing Current Limit (RLOAD = $100 \Omega$ )                                                                                                            | —                 | _              | 50                      | mAp           |

| dc Loop Current—ILIM (RLOOP = 100 Ω):<br>Programming Range (Vcc = 5 V)<br>Programming Range (Vcc = 3.3 V)<br>Voltage at VPROG                            | 15<br>15<br>0.194 |                | 70<br>45<br>1.01        | mA<br>mA<br>V |

| dc Current Variation (current limit 22 mA to 28 mA)                                                                                                      | —                 |                | ±8                      | %             |

| dc Current Variation (current limit 70 mA)                                                                                                               | —                 |                | ±10                     | %             |

| dc Feed Resistance (does not include protection resistors)                                                                                               | —                 | 50             |                         | Ω             |

| Open Loop Voltages:<br>Scan Mode:<br> VBAT1  > 51 V  VTIP  –  VRING <br>PR to Battery Ground<br>PT to Battery Ground<br>OHT Mode:                        | 44<br>            | 51<br>—        | <br>56.5<br>56.5        | V<br>V        |

| $ V_{BAT1}  > 51 V (VOH = 0 V)  VTIP  -  VRING $<br>PR to Battery Ground<br>PT to Battery Ground<br>Active Mode (VOH = 0 V):<br>$ PT - PR  -  V_{BAT2} $ | 41<br>—<br>5.65   | 49<br>—<br>6.0 | <br>56.5<br>56.5<br>6.5 | V<br>V<br>V   |

| Ring Mode:<br> PT – PR  –  V <sub>BAT1</sub>                                                                                                             | _                 | 4.0            | _                       | V             |

## Table 11. 2-Wire Port (continued)

| Parameter                                                                                                                                                       | Min      | Тур          | Max | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----|----------|

| Loop Closure Threshold:<br>Active/On-hook Transmission Modes<br>Scan Mode                                                                                       |          | 10.5<br>11.5 |     | mA<br>mA |

| Loop Closure Threshold Hysteresis:<br>Vcc = 5 V<br>Vcc = 3.3 V                                                                                                  |          | 2<br>1       |     | mA<br>mA |

| Ground Key:<br>Differential Detector Threshold<br>Detection                                                                                                     | 5<br>50  | 8            | 10  | mA<br>ms |

| Longitudinal to Metallic Balance at PT/PR<br>Test Method: Q552 (11/96) Section 2.1.2 and <i>IEEE</i> <sup>®</sup> 455:<br>300 Hz to 600 Hz<br>600 Hz to 3.4 kHz | 52<br>52 | _            |     | dB<br>dB |

| Metallic to Longitudinal (harm) Balance:<br>200 Hz to 1000 Hz<br>100 Hz to 4000 Hz                                                                              | 40<br>40 | _            |     | dB<br>dB |

| PSRR 500 Hz—3000 Hz:<br>VBAT1, VBAT2<br>Vcc (5 V operation)                                                                                                     | 45<br>35 |              |     | dB<br>dB |

# Table 12. Analog Pin Characteristics

| Parameter                                 | Min         | Тур  | Max       | Unit |

|-------------------------------------------|-------------|------|-----------|------|

| TXI (input impedance)                     | —           | 100  | —         | kΩ   |

| Output Offset (VTX)                       | —           |      | ±10       | mV   |

| Output Offset (VITR)                      |             | —    | ±100      | mV   |

| Output Drive Current (VTX)                | ±300        | —    | —         | μA   |

| Output Drive Current (VITR)               | ±10         | —    | —         | μA   |

| Output Voltage Swing:                     |             |      |           |      |

| Maximum (VTX, VITR)                       | AGND        | —    | Vcc       | V    |

| Minimum (VTX)                             | AGND + 0.25 | —    | Vcc-0.5   | V    |

| Minimum (VITR)                            | AGND + 0.35 | —    | Vcc-0.4   | V    |

| Output Short-circuit Current              | —           | —    | ±50       | mA   |

| Output Load Resistance                    | 10          | —    | —         | kΩ   |

| Output Load Capacitance                   | _           | 20   | —         | pF   |

| RCVN and RCVP:                            |             |      |           |      |

| Input Voltage Range (Vcc = 5 V)           | 0           | —    | Vcc – 0.5 | V    |

| Input Voltage Range (Vcc = 3.3 V)         | 0           | —    | Vcc - 0.3 | V    |

| Input Bias Current                        | —           | 0.05 | —         | μA   |

| Differential PT/PR Current Sense (DCOUT): |             |      |           |      |

| Gain (PT/PR to DCOUT)                     |             | 67   | —         | V/A  |

| Offset Voltage at ILOOP = 0               | -20         |      | 20        | mV   |

#### Table 13. ac Feed Characteristics

| Parameter                                                                                                                                                                       | Min                       | Тур          | Max                         | Unit                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-----------------------------|-----------------------|

| ac Termination Impedance <sup>1</sup>                                                                                                                                           | 150                       | 600          | 1400                        | Ω                     |

| Total Harmonic Distortion (200 Hz—4 kHz) <sup>2</sup> :<br>Off-hook<br>On-hook                                                                                                  |                           | _            | 0.3<br>1.0                  | %<br>%                |

| Transmit Gain (f = 1004 Hz, 1020 Hz, current limit) <sup>3</sup> :<br>PT/PR Current to VITR                                                                                     | 300 - 3%                  | 300          | 300 + 3%                    | V/A                   |

| Receive Gain, f = 1004 Hz, 1020 Hz Open Loop:<br>RCVP or RCVN to PT—PR (gain of 8 option, L9215A)<br>RCVP or RCVN to PT—PR (gain of 2 option, L9215G)                           | 7.76<br>1.94              | 8<br>2       | 8.24<br>2.06                | _                     |

| Gain vs. Frequency (transmit and receive) <sup>2</sup> 600 Ω Termination,<br>1004 Hz, 1020 Hz Reference:<br>200 Hz—300 Hz<br>300 Hz—3.4 kHz<br>3.4 kHz—20 kHz<br>20 kHz—266 kHz | -0.3<br>-0.05<br>-3.0<br> | 0<br>0<br>0  | 0.05<br>0.05<br>0.05<br>2.0 | dB<br>dB<br>dB<br>dB  |

| Gain vs. Level (transmit and receive) <sup>2</sup> 0 dBV Reference:<br>-55 dB to +3.0 dB                                                                                        | -0.05                     | 0            | 0.05                        | dB                    |

| Idle-channel Noise (tip/ring) 600 Ω Termination:<br>Psophometric<br>C-Message<br>3 kHz Flat                                                                                     |                           | -82<br>8<br> | -77<br>13<br>20             | dBmp<br>dBrnC<br>dBrn |

| Idle-channel Noise (VTX) 600 Ω Termination:<br>Psophometric<br>C-Message<br>3 kHz Flat                                                                                          |                           | -82<br>8<br> | -77<br>13<br>20             | dBmp<br>dBrnC<br>dBrn |

1. Set externally either by discrete external components or a third- or fourth-generation codec. Any complex impedance R1 + R2  $\parallel$  C between 150  $\Omega$  and 1400  $\Omega$  can be synthesized.

2. This parameter is not tested in production. It is guaranteed by design and device characterization.

3. VITR transconductance depends on the resistor from ITR to VTX. This gain assumes an ideal 4750 Ω, the recommended value. Positive current is defined as the differential current flowing from PT to PR.

# Table 14. Logic Inputs and Outputs (Vcc = 5 V)

| Parameter                                                        | Symbol | Min  | Тур | Max | Unit |

|------------------------------------------------------------------|--------|------|-----|-----|------|

| Input Voltages:                                                  |        |      |     |     |      |

| Low Level                                                        | VIL    | -0.5 | 0.4 | 0.7 | V    |

| High Level                                                       | Vін    | 2.0  | 2.4 | Vcc | V    |

| Input Current:                                                   |        |      |     |     |      |

| Low Level (Vcc = 5.25 V, VI = 0.4 V)                             | lı∟    | —    |     | ±50 | μΑ   |

| High Level (Vcc = 5.25 V, Vi = 2.4 V)                            | Ін     | —    | —   | ±50 | μΑ   |

| Output Voltages (open collector with internal pull-up resistor): |        |      |     |     |      |

| Low Level (Vcc = 4.75 V, lo <sub>L</sub> = 200 μA)               | Vol    | 0    | 0.2 | 0.4 | V    |

| High Level (Vcc = 4.75 V, IoH = $-20 \mu\text{A}$ )              | Vон    | 2.4  | —   | Vcc | V    |

# Table 15. Logic Inputs and Outputs (Vcc = 3.3 V)

| Parameter                                                        | Symbol | Min  | Тур | Max | Unit |

|------------------------------------------------------------------|--------|------|-----|-----|------|

| Input Voltages:                                                  |        |      |     |     |      |

| Low Level                                                        | VIL    | -0.5 | 0.2 | 0.5 | V    |

| High Level                                                       | Vін    | 2.0  | 2.5 | Vcc | V    |

| Input Current:                                                   |        |      |     |     |      |

| Low Level (Vcc = 3.46 V, VI = 0.4 V)                             | lı∟    | —    | —   | ±50 | μΑ   |

| High Level (Vcc = 3.46 V, VI = 2.4 V)                            | Ін     | —    | —   | ±50 | μA   |

| Output Voltages (open collector with internal pull-up resistor): |        |      |     |     |      |

| Low Level (Vcc = 3.13 V, IoL = 200 μA)                           | Vol    | 0    | 0.2 | 0.5 | V    |

| High Level (Vcc = 3.13 V, IoH = $-5 \mu A$ )                     | Vон    | 2.2  | _   | Vcc | V    |

#### **Table 16. Ringing Specifications**

| Parameter                                                                                             | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| RINGIN (This input is ac coupled through 0.47 µF.):                                                   |     |     |     |      |

| Input Voltage Swing                                                                                   | 0   | —   | Vcc | V    |

| Input Impedance                                                                                       | —   | 100 | —   | kΩ   |

| Ring Signal Isolation:                                                                                | _   | 60  | _   | dB   |

| PT/PR to VITR                                                                                         |     |     |     |      |

| Ring Mode                                                                                             |     |     |     |      |

| Ring Signal Isolation:                                                                                |     | 80  |     | dB   |

| RINGIN to PT/PR                                                                                       |     |     |     |      |

| Nonring Mode                                                                                          |     |     |     |      |

| Ringing Voltage (5 REN 1380 $\Omega$ + 40 $\mu$ F load, 100 $\Omega$ loop, 2 x 50 $\Omega$ protection | 40  |     |     | Vrms |

| resistors, –70 V battery)                                                                             |     |     |     |      |

| Ringing Voltage (3 REN 2310 $\Omega$ + 24 $\mu$ F load, 250 $\Omega$ loop, 2 x 50 $\Omega$ protection | 40  | —   | _   | Vrms |

| resistors, –70 V battery)                                                                             |     |     |     |      |

| Ring Signal Distortion:                                                                               |     |     |     |      |

| 5 REN 1380 Ω, 40 μF Load, 100 Ω Loop                                                                  | —   | 3   | —   | %    |