## **Features**

- Lithium Chemistry CCCV Charger

- Adjustable Regulated Charging Up to 1.5A DC

- ♦ Adjustable Charge Voltage from 3.8V to 4.6V

- External and Internal Thermal Protection

- Safety Timer Secondary Termination

- LED Indicator Outputs

- Detects Power Outage and Switches Between Normal Power and Backup Battery

- Adjustable High-Efficiency Synchronous Buck Regulator with Skip Mode at Light Loads

- Low-Power Consumption in Discharge Mode

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE            | TOP<br>MARK |

|-------------|----------------|----------------------------|-------------|

| DS2731E+    | -20°C to +70°C | 28 TSSOP-EP*<br>(173 mils) | DS2731      |

| DS2731E+T&R | -20°C to +70°C | 28 TSSOP-EP*<br>(173 mils) | DS2731      |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T&R = Tape and reel.

\*EP = Exposed pad.

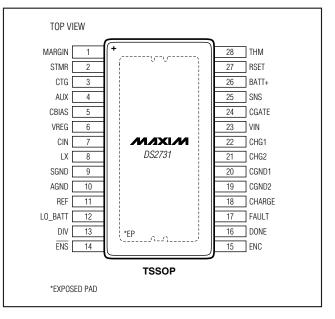

## **Pin Configuration**

Maxim Integrated Products 1

#### AUXILIARY POWER AUXILIARY POWER AUXILIARY POWER AUXILIARY POWER AUXILIARY POWER AUXILIARY

SWITCHING

REGULATOR

/VI/IXI/VI

##

drive LEDs.

**RAID** Controller Card

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

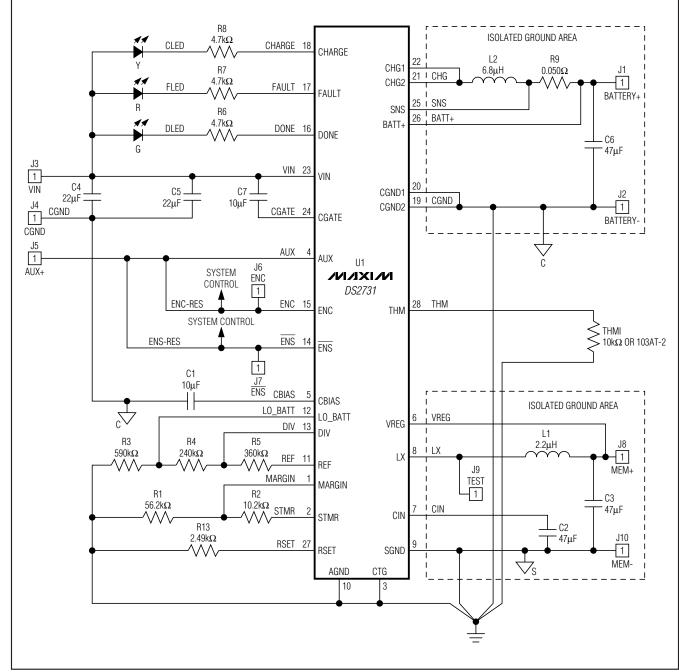

## **Typical Operating Circuit**

**Applications**

CACHE

MEMORY

**General Description**

The DS2731 is a complete power-management solution

for modular backup applications. It is well-suited for 2.5V

and below memory bus voltages, with an input voltage of 12V. The DS2731 includes an internal MOSFET switching

power stage for charging a one-cell lithium chemistry bat-

tery. It has a fully integrated synchronous buck regulator capable of supplying up to 450mA of cache backup sup-

ply current, and the necessary logic and power devices

for handling the switchover from system power to battery power. The battery charging method of the DS2731 is

constant current/constant voltage (CCCV). Output voltage

can be margined from 3.8V to 4.6V using a resistor-

divider. Charge is terminated when the charging current

falls below 5% of full charge current. Switchover to battery backup is initiated by an internal comparator and occurs

automatically when a sensed-input voltage drops below 2.93V. At light loads, the 2MHz internal synchronous buck

regulator operates in burst mode for maximum efficiency. All nonessential functions of the DS2731 are disabled while supplying holdup current to the cache memory, and the IC goes into very low-current dormant mode when the battery voltage drops below a user-settable threshold. The DS2731 keeps track of charge status and signals the user through open-drain I/O pins that can be used to

## ABSOLUTE MAXIMUM RATINGS

| Voltage Range on CGND1, CGND2, and      |                |

|-----------------------------------------|----------------|

| SGND Pins Relative to AGND              | 0.3V to +0.3V  |

| Voltage Range on VIN, CHG1, CHG2, and   |                |

| CGATE Pins Relative to AGND             | 0.3V to +16.0V |

| Voltage Range on CHARGE, FAULT, and     |                |

| DONE Pins Relative to AGND              | 0.3V to +16.0V |

| Voltage Range on Any Other Pin Relative |                |

| to AGND                                 | 0.3V to +6.0V  |

|                                         |                |

| Continuous Sink Current on VIN, CGNI<br>CGND2, SGND, AUX, BATT+ Pins |                          |

|----------------------------------------------------------------------|--------------------------|

| Continuous Source Current on CHG1,                                   |                          |

| CHG2, and LX Pins                                                    | 750mA each               |

| Continuous Sink Current on CHARGE,                                   |                          |

| FAULT, and DONE Pins                                                 | 20mA each                |

| Operating Temperature Range                                          | 40°C to +85°C            |

| Storage Temperature Range                                            | 55°C to +125°C           |

| Soldering Temperature                                                | Refer to the IPC/JEDEC   |

|                                                                      | J-STD-020 Specification. |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

(V<sub>IN</sub> = +10.8V to +13.2V,  $T_A$  = -20°C to +70°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                 | SYMBOL           | CONDITIONS                  | MIN  | ТҮР  | МАХ                         | UNITS |

|-------------------------------------------|------------------|-----------------------------|------|------|-----------------------------|-------|

| Charger Supply Voltage                    | VIN              | (Note 1)                    | 10.8 | 12.0 | 13.2                        | V     |

| Auxiliary Supply Voltage                  | V <sub>AUX</sub> | (Note 1)                    | 3.0  |      | 3.6                         | V     |

| Battery Voltage                           | VBATT+           | Operating as input (Note 1) | 2.7  |      | 5.0                         | V     |

| LED Voltage<br>(CHARGE, FAULT, DONE Pins) |                  | (Note 1)                    | 0    |      | V <sub>IN</sub><br>+ 0.3    | V     |

| Charger Enable (ENC)                      |                  | (Notes 1, 2)                | 0    |      | V <sub>CBIAS</sub><br>+ 0.3 | V     |

| Switcher Enable (ENS)                     |                  | (Notes 1, 2)                | 0    |      | V <sub>CIN</sub><br>+ 0.3   | V     |

## **CHARGER CIRCUIT ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +10.8V \text{ to } +13.2V, T_A = -20^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER                            | SYMBOL           | CONDITIONS                                                                                       | MIN  | ТҮР                   | МАХ | UNITS |

|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------|------|-----------------------|-----|-------|

| Charger Idle Supply Current          | l <sub>IN</sub>  | V <sub>IN</sub> > V <sub>UVLO-CHG</sub> (Note 3),<br>V <sub>AUX</sub> = 3.3V                     |      | 1                     |     | mA    |

|                                      | I <sub>AUX</sub> | VAUX > VTRIP                                                                                     |      | 100                   |     | μA    |

| Regulator Supply Current<br>(Note 3) | IBATT+           | V <sub>AUX</sub> < V <sub>TRIP</sub> ,<br>V <sub>BATT+</sub> > V <sub>SLEEP</sub> , ENS disabled |      | 100                   | 150 | μA    |

|                                      | ISLEEP           | $V_{IN} = V_{AUX} = 0.0V,$<br>$V_{BATT+} < V_{SLEEP}$                                            |      |                       | 10  | μA    |

| C <sub>BIAS</sub> Regulator Voltage  | VCBIAS           |                                                                                                  |      | 3.3                   |     | V     |

| CGATE Regulator Voltage              | VCGATE           |                                                                                                  |      | V <sub>IN</sub> - 4.0 |     | V     |

| C <sub>GATE</sub> Capacitance        | CCGATE           |                                                                                                  | 2.2  |                       |     | μF    |

| C <sub>BIAS</sub> Capacitance        | CCBIAS           |                                                                                                  | 0.22 |                       |     | μF    |

| Enable Logic-Low (ENS, ENC)          | VIL              | (Notes 4, 5)                                                                                     |      |                       | 0.4 | V     |

| Enable Logic-High (ENS, ENC)         | VIH              | (Notes 5, 6)                                                                                     | 1.6  |                       |     | V     |

## CHARGER CIRCUIT ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = +10.8V \text{ to } +13.2V, T_A = -20^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                     | SYMBOL               | CONDITIONS                                                  | MIN   | ТҮР  | MAX   | UNITS                    |

|-----------------------------------------------|----------------------|-------------------------------------------------------------|-------|------|-------|--------------------------|

| Enable Hysteresis (ENS, ENC)                  | VHYS-EN              |                                                             | 35    | 70   | 140   | mV                       |

| Pulldown Resistance (ENS, ENC)                | R <sub>PD</sub>      |                                                             | 100   | 200  | 300   | kΩ                       |

| LED Outputs Low<br>(CHARGE, DONE, FAULT)      | V <sub>OL</sub>      | I <sub>OL</sub> = 10mA                                      |       |      | 1.0   | V                        |

| Fault LED Flash Rate                          | <b>f</b> FAULT       |                                                             |       | 4    |       | Hz                       |

| Preconditioning Charge<br>Threshold           | V <sub>MIN</sub>     | (Note 1)                                                    | 2.55  | 2.60 | 2.70  | V                        |

| Preconditioning Hysteresis                    | VHYS                 |                                                             | 50    | 100  |       | mV                       |

| Preconditioning Charge Current                | IPRE                 | V <sub>BATT+</sub> < V <sub>MIN</sub>                       | 5.0   | 10.0 | 15.0  | % of<br>I <sub>CHG</sub> |

| Precondition Timeout                          | t <sub>PRE</sub>     |                                                             | 27    | 30   | 33    | min                      |

| Charge-Current Range                          | laura                | Charge current determined by RSET                           | 0.5   |      | 1.5   | А                        |

| (RSET Resistance)                             | ICHG                 | (Note 7)                                                    | 5.0   |      | 1.6   | kΩ                       |

| Charge-Current Accuracy IERR-CHC              |                      | RSET resistor tolerance 0.1%, $R_{SNS} = 0.050 \Omega$      | -5    |      | +5    | %                        |

| Overcurrent Clamp IOVERC                      |                      | $RSET = 0 \text{ or } R_{SNS} = 0$                          | 1.7   |      | 2.5   | А                        |

| Constant-Voltage Threshold<br>Range           | VCV                  | Charge voltage determined by MARGIN pin voltage             | 3.6   | 4.2  | 4.6   | V                        |

| MARGIN Pin Leakage                            | ILEAKAGE             |                                                             | -2    |      | +2    | μA                       |

| Constant-Voltage Charge<br>Accuracy           | VERR-CV              |                                                             | -25.0 |      | +25.0 | mV                       |

| Charge Termination (CV) Current               | ITERMINATE           | In constant-voltage mode                                    | 4.0   | 5.0  | 6.0   | % of<br>I <sub>CHG</sub> |

| Charge-Restart Threshold                      | Vdelta               | (Note 8)                                                    | 94    | 95   | 96    | % of<br>V <sub>CV</sub>  |

| Safety Timeout Range                          | towers               |                                                             | 1     |      | 10    | hr                       |

| (STMR Resistance)                             | tsafety.             |                                                             | 22    |      | 220   | kΩ                       |

| Safety Timeout Error                          | terr-safety          | $R_{\text{STMR}} = 22,000\Omega$                            | -5    |      | +5    | %                        |

| Battery Charger Switching Period              | tsw-CHG              | Full load (1.5A) (Note 9)                                   | 0.83  | 1.00 |       | μs                       |

| Charger Undervoltage Lockout                  | VUVLO-CHG            |                                                             | 8     |      | 10    | V                        |

| High-Side MOSFET<br>On-Resistance             | R <sub>DSON-CP</sub> | I <sub>CHG</sub> = 1A, V <sub>IN</sub> = 10.8V<br>(Note 10) |       |      | 0.4   | Ω                        |

| Low-Side MOSFET On-Resistance                 | R <sub>DSON-CN</sub> | I <sub>CHG</sub> = 1A, V <sub>IN</sub> = 10.8V (Note 10)    |       |      | 0.15  | Ω                        |

| Reverse Leakage of Charge FET<br>(CHG1, CHG2) | IREVERSE             | $V_{IN} = 0V, V_{CV} = 4.2V, ENC = 0V$                      |       |      | 10    | μA                       |

| Forward Leakage of Charge FET<br>(CHG1, CHG2) | IFORWARD             | $V_{IN} = 12V, V_{CV} = 4.2V, ENC = 0V$                     |       |      | 10    | μΑ                       |

| SNS Leakage Current                           | ILKG-CHG             | No charge current, $V_{IN} = 12V$                           | -2    |      | +2    | μA                       |

| Startup Time                                  | tstart -             | Using typical application components                        |       | 1    |       | ms                       |

## **BUCK REGULATOR AND POWER MUX CIRCUIT ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = +10.8V to +13.2V,  $T_A$  = -20°C to +70°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                                 | MIN   | ТҮР   | MAX    | UNITS |

|-------------------------------------------|----------------------|----------------------------------------------------------------------------|-------|-------|--------|-------|

| Auxiliary Input Trip Threshold            | VTRIP                | (Note 1)                                                                   | 2.85  | 2.93  | 3.00   | V     |

| Auxiliary Input Trip Hysteresis           | VHYS-TRIP            | Relative to actual VTRIP                                                   | 50    | 80    | 150    | mV    |

| Multiplexer Delay<br>Break-Before-Make    | <sup>t</sup> BREAK   | Switching to/from BATT+<br>(Note 11)                                       |       |       | 1      | μs    |

| Power Multiplexer On-Resistance           | R <sub>MUX</sub>     | I <sub>MUX</sub> = 10mA, BATT+ or AUX source                               |       | 0.6   | 1.0    | Ω     |

| Regulator Output Voltage Range            | VREG                 | Set by V <sub>DIV</sub> pin voltage                                        | 0.9   |       | 2.5    | V     |

| DIV Pin Voltage Range                     | V <sub>DIV</sub>     |                                                                            | 0.4   |       | VREF   | V     |

| Regulator Output Voltage Error            | Verr-reg             | (Note 9)                                                                   | -5.0  |       | +5.0   | %     |

| Low-Battery Threshold<br>Adjustment Range | VSLEEP               |                                                                            | 2.75  |       | 3.00   | V     |

| LO_BATT Pin Voltage Range                 | VLO-BATT             |                                                                            | 0.6   |       | VREF   | V     |

| V <sub>REF</sub> Voltage                  | V <sub>REF</sub>     |                                                                            | 1.220 | 1.238 | 1.260  | V     |

| V <sub>REF</sub> Load Range               | IREF                 |                                                                            | 1.22  |       | 126.00 | μA    |

| (Equivalent Resistance)                   | IKEF                 |                                                                            | 1000  |       | 10     | kΩ    |

| Buck Regulator Switching Period           | tsw-reg              | 50mA (Note 9)                                                              |       | 500   |        | ns    |

| Regulator Undervoltage Lockout            | Vuvlo-reg            |                                                                            | 2.45  |       | 2.70   | V     |

| Switching Power<br>pFET Resistance        | R <sub>DSON-SP</sub> | $I_{OUT} = 100mADC$<br>BATT+ = 3.0V, V <sub>AUX</sub> = 0 (Note 10)        |       |       | 0.6    | Ω     |

| Switching Power<br>nFET Resistance        | Rdson-sn             | I <sub>OUT</sub> = 100mADC<br>BATT+ = 3.0V, V <sub>AUX</sub> = 0 (Note 10) |       |       | 1.2    | Ω     |

| nFET Off Threshold                        | IOFFN                |                                                                            | 0     | 40    | 80     | mA    |

| Switching Power<br>pFET Overcurrent Limit | IOCLP                |                                                                            | 500   | 750   | 1000   | mA    |

| Switching Power<br>nFET Overcurrent Limit | IOCLN                |                                                                            | 400   | 650   | 900    | mA    |

| VREG Pin Leakage                          | ILKG-REG             |                                                                            | -2    |       | +2     | μA    |

## THERMAL PROTECTION CHARACTERISTICS

$(V_{IN} = +10.8V \text{ to } +13.2V, T_A = -20^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                                | SYMBOL                    | CONDITIONS                         | MIN   | ТҮР    | MAX   | UNITS                          |

|----------------------------------------------------------|---------------------------|------------------------------------|-------|--------|-------|--------------------------------|

| THM Pin Internal Pullup Voltage                          | VTHM                      | (Notes 1, 12)                      |       | VCBIAS |       | V                              |

| THM Pin Internal Resistance                              | R <sub>THM</sub>          | THM to C <sub>BIAS</sub> (Note 12) | 9.8   | 10.0   | 10.2  | kΩ                             |

| Thermistor Overtemperature<br>HALT Threshold             | V <sub>HOT</sub>          | (Notes 12, 13)                     | 0.271 | 0.283  | 0.292 | Ratio to<br>V <sub>CBIAS</sub> |

| Thermistor Overtemperature<br>Resume Threshold           | VHYS-HOT                  | (Notes 12, 13)                     |       | 0.3055 |       | Ratio to<br>V <sub>CBIAS</sub> |

| Thermistor Undertemperature<br>HALT Threshold            | VCOLD                     | (Notes 12, 13)                     | 0.727 | 0.739  | 0.748 | Ratio to<br>V <sub>CBIAS</sub> |

| Thermistor Undertemperature<br>Resume Threshold          | VHYS-COLD                 | (Notes 12, 13)                     |       | 0.714  |       | Ratio to<br>VCBIAS             |

| Thermistor Disable<br>Threshold                          | VDISABLE                  | (Notes 12, 13)                     | 0.02  | 0.03   | 0.04  | Ratio to<br>V <sub>CBIAS</sub> |

| Internal Overtemperature<br>Protection Threshold CCCV    | T <sub>PROTECT_CCCV</sub> | (Note 12)                          |       | 160    |       | °C                             |

| Internal Overtemperature<br>Hysteresis CCCV              | THYS-PROTECT_CCCV         | (Note 12)                          |       | -20    |       | °C                             |

| Internal Overtemperature<br>Protection Threshold MEM_REG | TPROTECT_MEMREG           | (Note 14)                          |       | 165    |       | °C                             |

| Internal Overtemperature<br>Hysteresis MEM_REG           | THYS-PROTECT_<br>MEMREG   | (Note 14)                          |       | -15    |       | °C                             |

| Charging Current Reduction<br>Threshold                  | Тсноке                    | (Note 12)                          |       | 100    |       | °C                             |

| Charging Current Reduction Rate                          | TCHOKE_RATE               | (Note 12)                          |       | 133    |       | mA/°C                          |

Note 1: All voltages referenced to AGND pin.

Note 2: V<sub>CIN</sub> is equivalent to V<sub>AUX</sub> when V<sub>AUX</sub> is greater than V<sub>TRIP</sub>, otherwise V<sub>CIN</sub> is equivalent to V<sub>BATT+</sub>.

**Note 3:** Supply-current specification is only for current drain of the IC and does not include cell-charge current, load-supply current, or any external resistor bias currents. The only exception is I<sub>SLEEP</sub>, which does account for complete current drain of the lithium cell during low-battery conditions.

**Note 4:** Below this voltage, the input is guaranteed to be logic-low.

**Note 5:** Operating from  $3.3V \pm 10\%$ .

Note 6: Above this voltage, the input is guaranteed to be logic-high.

**Note 7:** Assumes an R<sub>SNS</sub> value of  $0.05\Omega$ .

Note 8: Relative to V<sub>CV</sub>.

**Note 9:** With recommended application circuit.

Note 10: Includes complete package resistance.

Note 11: This specification is from the rising or falling edge of ENS to the closure of the switch and includes whatever delay is in the internal logic and FET drivers.

**Note 12:** Applies to charger.

**Note 13:** Multiply these values by  $C_{BIAS}$  voltage to get value in volts. Recommended value of resistor in divider network is 10k $\Omega \pm 1\%$ . Tolerance includes tolerances of internal resistance and  $C_{BIAS}$  voltage.

**Note 14:** Applies to memory buck regulator.

Figure 1. Typical Application Diagram

**Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                   |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MARGIN  | Voltage-Margining Input. Selects regulation voltage of charging circuit. Connect to the STMR pin through a resistor-divider.                                               |

| 2   | STMR    | Voltage Safety-Timer Input. Sets timeout period for a charge cycle based on external resistance to AGND.                                                                   |

| 3   | CTG     | Connect To Ground. Must be connected to AGND externally.                                                                                                                   |

| 4   | AUX     | Auxiliary. External supply input to switching supply. Connect to system 3.3V supply.                                                                                       |

| 5   | CBIAS   | Internal Regulator Output. Internal supply for the charging circuit generated from the V <sub>IN</sub> input. Bypass with a capacitor to AGND.                             |

| 6   | VREG    | Cache Voltage-Sense Input. Feedback for regulation of the switching circuit voltage. Connect to the positive side of the switching output load.                            |

| 7   | CIN     | Holdup/Bypass Capacitor. Internal supply for the switching regulator. Bypass with a 4.7µF capacitor to AGND.                                                               |

| 8   | LX      | Switching Node, Backup Supply. Output from the switching regulator. Connect to the switching regulator's external coil.                                                    |

| 9   | SGND    | Switcher Ground. Ground reference for the switching regulator. Connect to the negative side of the load.                                                                   |

| 10  | AGND    | Analog Ground. Ground reference for the charging circuit. Connect to the negative side of the battery.                                                                     |

| 11  | REF     | Voltage Reference for Backup. 1.238V voltage reference used to set regulation voltage and low-battery-<br>detection threshold. Connect to AGND through a resistor network. |

| 12  | LO_BATT | Low-Battery Detection. Selects the low-battery shutdown threshold of the switching regulator. Connect to the REF pin through a resistor-divider.                           |

| 13  | DIV     | Voltage Divider for Backup. Controls the voltage output level of the switching regulator. Connect to the REF pin through a resistor-divider.                               |

| 14  | ENS     | Enable Switcher. Active-low enable for the switching regulator.                                                                                                            |

| 15  | ENC     | Enable Charger. Active-high enable for the charging circuit.                                                                                                               |

| 16  | DONE    | Charge-Done Indicator. Open-drain active-low output indicating successful charge completion of the external cell.                                                          |

| 17  | FAULT   | Charger-Fault Indicator. Open-drain active-low output indicating failure during charge of the external cell.                                                               |

| 18  | CHARGE  | Charge Indicator. Open-drain active-low output indicating charge of the external cell in progress.                                                                         |

| 19  | CGND2   | Charger Ground 2. Ground reference for battery-charging circuit. Connect to negative side of external cell.                                                                |

| 20  | CGND1   | Charger Ground 1. Ground reference for battery-charging circuit. Connect to negative side of external cell.                                                                |

| 21  | CHG2    | High-Current Charger Output 2. Output from the charging circuit. Connect to charging circuit's external coil.                                                              |

| 22  | CHG1    | High-Current Charger Output 1. Output from the charging circuit. Connect to charging circuit's external coil.                                                              |

| 23  | VIN     | Charge-Supply Input. Connect to 10.8V to 13.2V system supply.                                                                                                              |

| 24  | CGATE   | Floating Gate Drive Bypass. Internal supply for the charger gate control. Bypass with a 2.2µF capacitor to VIN.                                                            |

| 25  | SNS     | Current-Sense Input. Feedback for regulator of charger current. Connect a 0.050 $\Omega$ sense resistor between SNS and BATT+.                                             |

| 26  | BATT+   | Battery Terminal Voltage. Feedback for regulation of charger voltage and supply to switching regulator during power loss.                                                  |

| 27  | RSET    | Charge-Setting Resistor Intput. Selects CC charge rate for external lithium cell. Connect to AGND through an external resistor.                                            |

| 28  | THM     | Thermistor Input. Connect to $10k\Omega$ NTC thermistor with good thermal contact to the external lithium cell.                                                            |

|     | EP      | Exposed Paddle. It is recommended the exposed pad be connected to system ground.                                                                                           |

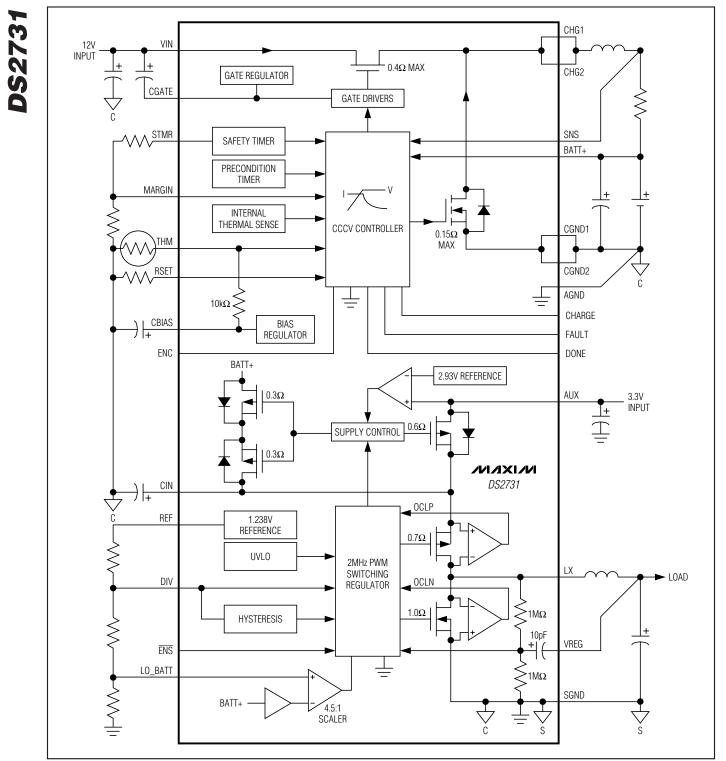

Figure 2. Block Diagram

# **DS2731**

# **Cache-Memory Battery-Backup Management IC**

## **Detailed Description**

The DS2731 is a complete power-management solution for modular backup applications. It is well suited for 2.5V and below memory bus voltages. It has a 12V supply input for battery charging and a 3.3V aux supply input for power failure circuitry and memory voltage regulation. The DS2731 includes an internal MOSFETswitching power stage for charging a lithium-ion (Li+) cell. It has a fully integrated synchronous-buck regulator capable of supplying up to 450mA of cache-backup supply current. It also handles switching from system power to battery power.

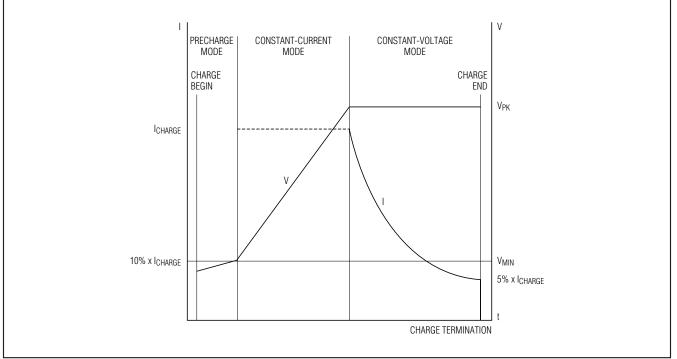

The battery-charging method is CCCV. Charging can be broken into three different modes: precondition, constant-current (CC) charge, and constant-voltage (CV) charge. Precondition mode charges at a reduced rate for a severely depleted cell. CC mode charge rate is user selectable from 0.5A to 1.5A. In CV mode, charge is terminated when the charging current falls below 5% of CC mode charge rate. The CV mode output is also user selectable from 3.8V to 4.6V. Charge status is signaled to the user through three open-drain pins that can be used to drive LEDs. A thermistor input is provided to prevent charging outside of temperature specifications and a safety timer prevents the continued charging of a damaged cell.

Switchover to battery backup is initiated by an internal comparator and occurs automatically when a sensed input voltage drops below 2.93V. The power failure switching circuitry can be disabled by the user. Memory voltage is user selectable from 0.9V to 2.5V. At light loads, the 2MHz internal synchronous buck regulator operates in burst mode for maximum efficiency. All nonessential functions of the DS2731 are disabled during a power failure while supplying holdup current to the cache memory. To prevent damaging the battery, the regulator shuts down and the IC goes into a very low-current dormant mode when the battery voltage drops below a user-settable threshold (LO\_BATT).

#### Li+ Charger s powered by the 12V

The CCCV charger circuitry is powered by the 12V input supply. When the charger circuitry is enabled, battery voltage is continuously monitored at the BATT+ pin. Charging begins when the battery voltage drops below the charge restart threshold. Accurate charge current measurements are achieved by the Kelvin remote-sense connections at the SNS and BATT+ pins. Measuring the voltage through a Kelvin remote-sense connection eliminates offset error caused by small trace resistances at high current.

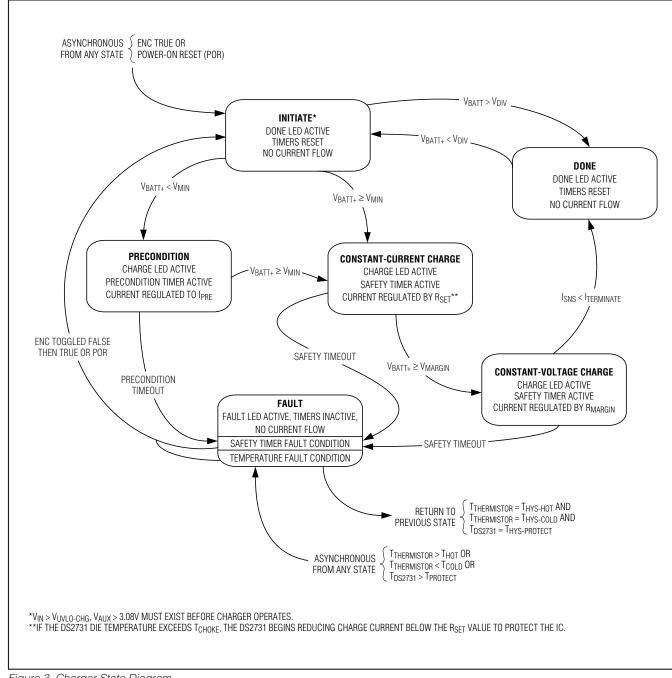

#### **Charging Algorithm**

From initiate, CC charging proceeds if ENC is high, the UVLO-CHG is false, the die temperature is below TPROTECT CCCV, and the battery is above the minimum voltage. If the battery is below the minimum voltage, the charger goes into preconditioning charge. Once the battery voltage exceeds V<sub>MIN</sub>, the charger proceeds to CC mode. Precondition charge has a default 30-minute timer. If the timer expires before the battery voltage exceeds VMIN, the charger goes to fault. For CC charging, the charge safety timer starts. CC charging proceeds until the output voltage reaches the CV set point. The charger then proceeds to CV mode. Charging terminates when the current drops below 5% of the CC charge rate. The charge-safety timer duration is the sum of the CC and CV charge times and should be set to about 15% above the expected maximum charge time. If the charge-safety timer expires, the charger goes to fault. After charge termination, the charger monitors the battery voltage for self-discharge. When it drops 200mV below the CV charge threshold, the charger enters Initiate and a new charge cycle begins.

Note:  $V_{\text{AUX}}$  must be above 3.08V for the charger to operate.

#### **Precharge Mode**

Precharge mode is intended to restore severely depleted cells. Batteries with a voltage <  $V_{MIN}$  charge at a reduced rate, 10% x I<sub>CHG</sub>, to prevent damaging the cell. Precharge mode has a fixed safety timer of 30 minutes. This timer is independent of the STMR pin. If the battery voltage has not exceeded  $V_{MIN}$  within 30 minutes, the charger goes to the fault state. The charge pin is active during precharge mode.

Figure 3. Charger State Diagram

M/XI/M

Figure 4. Li+ Battery Charging Characteristics

#### **Constant-Current (CC) Mode**

CC mode is entered either directly from initiate or after precharge. Current is regulated based on the voltage drop across an external 50m  $\!\Omega$  sense resistor and an internal feedback circuit. The CC charge rate is set by the RSET pin. It can be calculated by the following formula:

#### ICHARGE = 2500/R

Where R is the value of the resistor connected to RSET. The charge current can range from 0.5A to 1.5A.

The safety timer begins when CC mode is entered. If it expires during CC mode, the charger enters a fault state. If the current-sense feedback or RSET resistor is shorted, the charger clamps current at IOVERCURRENT.

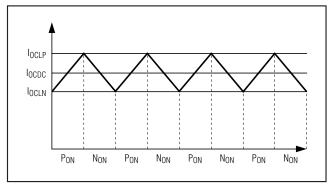

#### Li+ Charger CC Operation Detailed Description

In CC mode, the CCCV charger regulates current by monitoring the voltage drop across the SNS resistor. The differential voltage measurement provides feedback that controls the switching of the high-side and low-side FETs. Inside the DS2731 CHG1 and CHG2 pins are a high-side p-channel MOSFET (Q1) and a low-side n-channel MOSFET (Q2). Q1 and Q2 alternate on and off, either supplying current to the load and inductor or providing a current loop for the inductor to supply the load. The inductor charges during Q1 ON and discharges during Q2 ON. The Q1 and Q2 switching is controlled by the voltage across R<sub>SNS</sub>.

Figure 5. Li+ Battery Charger CC Operation Characteristics

The current in the inductor is a combination of the current in Q1 and Q2. The voltage on the inductor is higher during Q1 ON than Q2 ON. This allows the current in the inductor to remain continuous because the *power-in* approximately equals the *power-out*.

#### **Constant-Voltage (CV) Mode**

CV mode is entered after CC mode when the battery voltage reaches the CV output threshold. Battery voltage is measured at the BATT+ pin. When the voltage reaches the CV threshold set by the MARGIN pin, regulation goes from CC mode to CV mode. Charge termination occurs when the current drops below 5% of the CC charge rate.

The MARGIN pin sets the CV threshold according to the following formula:

#### $V_{PK}$ (CV Set Point) = 4.97V x R1/(R2 + R1)

Where R2 is the resistor between STMR and MARGIN, and R1 is the resistor between MARGIN and ground. Voltage regulation can be set from 3.8V to 4.6V. If the safety timer expires during CV mode the charger enters the fault state. A fault that occurs in CV mode, once cleared, causes the charger to transition to done. Charge resumes if/when the battery voltage collapses to 95% (VDELTA) of the CV threshold.

#### **Fault Conditions**

There are several types of fault conditions that can occur. The precondition timer or safety timer can expire and the charger enters the fault state. This fault condition must be cleared by power cycling the part or toggling ENC. If the temperate exceeds the hot or cold limits, the charger enters fault. In the case of a temperature fault, charging resumes once the temperature returns to the normal operation range unless the fault occurs in CV mode. If a fault occurs in CV mode, the charger sees a charge termination condition because the current has dropped below 5% x I<sub>CHG</sub>. Once the fault condition is removed the charger transitions to done. The charger remains in the done state unless the cell voltage collapses below 95% (V<sub>DELTA</sub>) of the CV threshold.

#### **Thermal Protection**

The charger circuitry has a shutdown feature that pauses charging if the internal die temperature exceeds 160°C. Charging resumes after the temperature has cooled 20°C below 160°C. The charger circuitry is also equipped with a temperature choke point. If the die temperature reaches 100°C, the CCCV charger begins to choke the current 133mA/°C above 100°C. The choke continues down to 0mA if the temperature continues to increase. These thermal-regulation features operate independent of the thermistor input.

#### **Enable Charger**

The ENC pin is an active-high input that enables the charger. When enabled, the DS2731 performs battery qualification and begins charging using the CCCV algorithm. Toggling ENC resets charge timers and clears fault conditions. Any time ENC is low, the DS2731 charging circuitry is disabled and the high-side switch is guaranteed to be off. No current can flow from the battery to the VIN pin when the charger is off.

#### **Safety Timer**

The charger has a safety timer that controls the maximum length of time for a charge cycle. It is user selectable from 1 to 10 hours. If this timer expires and the battery has failed to reach the termination current, the charger enters the fault state and is latched off. Charging does not continue until either power is cycled or the ENC pin is strobed low and then high again. The timer does not start until CC mode is entered and continues through CV mode. Precharge mode is not included in the STMR.

Timing Equation:

0.1647 x R<sub>STMR</sub> = t (in seconds); R<sub>STMR</sub> = R1 + R2

Where R1 is the resistor from MARGIN to ground and R2 is the resistor from STMR to MARGIN.

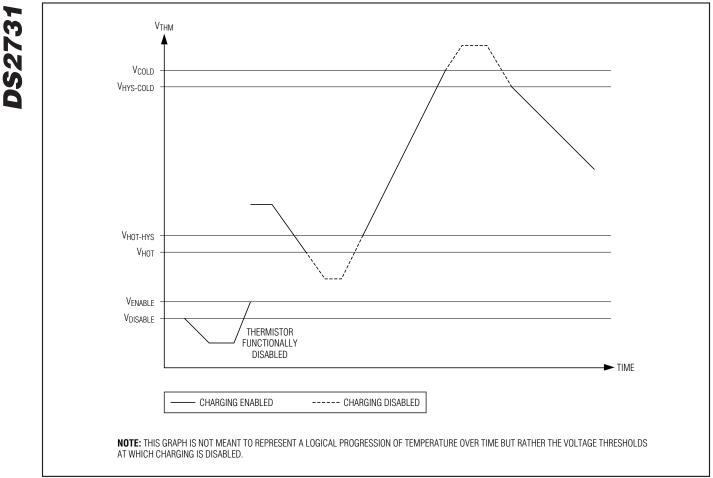

#### **Thermistor Input**

Battery temperature can be monitored using an external thermistor. The THM input goes to a comparator and is pulled up internally by a  $10 k\Omega$  resistor. The voltage on this pin must be above V<sub>HYS-HOT</sub> and below V<sub>HYS-COLD</sub> in order to start charging. Thermistor func-

Table 1. Thermistor Threshold

tionality can be disabled by grounding the THM pin and charging is independent of temperature. During charging, if the voltage on the THM pin goes below V<sub>HOT</sub> volts, the charger pauses until the voltage rises above V<sub>HYS-HOT</sub> volts. Also, if the voltage on the THM pin goes above V<sub>COLD</sub> volts, the charger pauses until the voltage falls below V<sub>HYS-COLD</sub> volts. All timers pause while charging is interrupted and resume when the temperature returns to the valid range. The charger enters the fault state when an overtemperature or undertemperature condition occurs. A 10k $\Omega$  NTC thermistor is recommended for this pin.

#### **Charge Status Indicators**

The CHARGE, FAULT, and DONE pins can be used as digital discretes or as LED drivers; they are open drain. When charging, the CHARGE pin is held low. When the charger detects a full battery/termination condition, ITERMINATE, the DONE pin goes low and the CHARGE pin goes high impedance. Any charging fault (overtemperature or expiration of the safety timer) causes the FAULT pin to flash at a 4Hz rate and the CHARGE and DONE pins go high impedance. The FAULT pin stays on solid, not flash, if the fault occurs in CV mode.

|               |                            |                                  | TEMPERA         | TURE (°C)                                  |

|---------------|----------------------------|----------------------------------|-----------------|--------------------------------------------|

| THM THRESHOLD | RATIO OF C <sub>BIAS</sub> | THERMISTOR<br>RESISTANCE<br>(kΩ) | SEMITEC 103AT-2 | FENWAL<br>197-103LAG-A01<br>173-103LAF-301 |

| COLD          | 0.739                      | 27.040                           | 0               | 4                                          |

| НОТ           | 0.283                      | 4.925                            | 45              | 42                                         |

| DISABLE       | 0.030                      | _                                | —               | —                                          |

#### Table 2. Charge Status Indicator Description

| CONDITION        | CHARGE PIN | DONE PIN | FAULT PIN | COMMENT                                               |

|------------------|------------|----------|-----------|-------------------------------------------------------|

| Precharge        | Low        | High-Z   | High-Z    | _                                                     |

| Battery Charged  | High-Z     | Low      | High-Z    | (Done)                                                |

| Fault            | High-Z     | High-Z   | Blinking  | 50% DF, 4Hz rate; low if fault occurs during CV mode. |

| Charger Disabled | High-Z     | High-Z   | High-Z    | _                                                     |

Figure 6. Temperature Operation

## Cache-Memory Battery-Backup Buck-Regulator Supply (2MHz PWM)

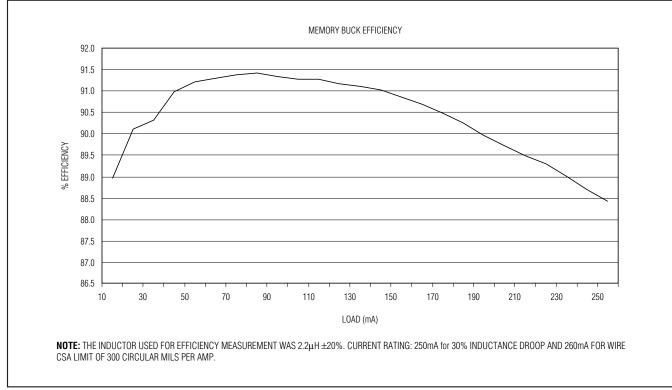

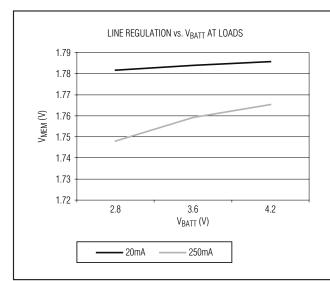

A 2MHz internal synchronous buck regulator is used to generate the appropriate cache-memory supply voltage. With careful inductor selection, high efficiencies can be achieved with this type of supply (see Figures 7a and 7b). The regulator has a user-selectable voltage range of 0.9V to 2.5V, and can supply up to 450mA. There is also a user-selectable LO\_BATT threshold with a range of 2.5V to 3V. If the battery voltage drops

below this threshold, the regulator shuts down and the IC goes into a low-power state until system power is restored. The regulator can be disabled by the ENS pin during normal power conditions. The buck regulator is designed to supply enough current to power the cache memory during data retention/refresh mode. The regulator can be enabled during normal system power, but it cannot supply power to the cache memory during normal operating conditions.

**Note:** The buck regulator and the charger should not run simultaneously.

### Buck-Regulator Operation Overview

VREG is the feedback pin for the 2MHz PWM switching regulator cache-memory supply. The switching node uses this voltage reference feedback to regulate the output voltage to the value specified by DIV. The switching power-supply high-side and low-side FETs drive LX. The output inductor is connected to this node. During normal operation, the switching frequency observed on the LX pin is approximately 2MHz. The exact switching frequency and duty factor varies based

on load and inductor selection. The SGND pin connects to the source of the internal low-side switch. This pin should be routed from the DS2731 to the negative terminal of the output capacitor. There are fast transient currents in this connection caused by the commutation of the body-drain diode of the low-side switch when the high-side switch turns on. Considerations should be taken during layout to minimize EMI. The buck regulator is equipped with an internal temperature-shutdown circuit that turns off the regulator if the circuit temperature reaches 165°C. Regulation resumes once the temperature has cooled 15°C below 165°C.

Figure 7a. Memory Buck Regulator Efficiency with 2.2µH Inductor

Figure 7b. Memory Buck Regulator Line Regulation vs. Battery Voltage at Loads

Figure 8. Buck Regulator Overcurrent Switching

## <u>Setting Memory Voltage</u> and Low-Battery Shutdown

The cache-memory and low-battery shutdown voltages are set using a 1.25V reference and resistor-divider. The 1.25V reference is supplied at the REF pin. This pin cannot supply power for any system loads. In order to ensure that the voltage reference is not overloaded, a 1M $\Omega$  total resistor-divider network is recommended.

#### **Memory Voltage**

The voltage on the DIV pin is the average DC voltage set point to which the cache-memory supply regulates. The cache-memory supply voltage can range from 0.9V to 2.5V and is set by the following formula:

$V_{DIV} \times 25/12 = V_{VREG}$

#### Low-Battery Shutdown

The voltage on the LO\_BATT pin is compared to the prescaled battery voltage. The scale factor is 4.5:1. When the scaled battery voltage drops below the voltage on LO\_BATT, the IC goes into quiescent-power mode. All circuitry is shut off and does not turn on again until the V<sub>BIAS</sub> voltage is stable and UVLO-REG is off. The low-battery voltage set point can be determined by the following formula:

VLO\_BATT x 4.5 = Low-Battery Voltage Set Point

# **DS2731**

# **Cache-Memory Battery-Backup Management IC**

Layout

Due to high-frequency switching, high-current loops, and large-voltage switching, special consideration should be taken for layout of the DS2731 board in order to reduce EMI.

## CCCV Charger

The CCCV charger generates a high-current loop from VIN to CHG1 and CHG2 to CGND1 and CGND2. Also, large dV/dT is generated at CHG1 and CHG2 from the switching on and off of the 12V supply. These combine to generate magnetic and electric fields. To reduce these fields, the high-current loop should be made as small as possible. Traces should be routed point-topoint, as straight as possible, and a ground plane/shield should be used to isolate the noise from nearby components. Also, the trace width of the charge path should be sufficiently large enough to accommodate the high current. SNS and BATT+ should be connected as close as possible to the SNS resistor and BATT+ terminal for accurate current regulation and battery voltage measurements.

The AGND pin is the analog reference connection. No charge current flows into AGND. It should be connected as close as possible to the negative terminal of the battery. This allows for a more accurate battery voltage measurement by avoiding any voltage drops caused by stray resistance in the high-current charge path.

#### **Cache-Memory Buck Regulator**

Even though the voltages and currents are not as high as the CCCV charger, care still needs to be taken during layout of the memory buck regulator. There are fasttransient voltages at LX. The fast-transient current loop is from CIN to LX to SGND. Again, the current loop should be routed as small as possible and ground shielding should be used to isolate the circuit.

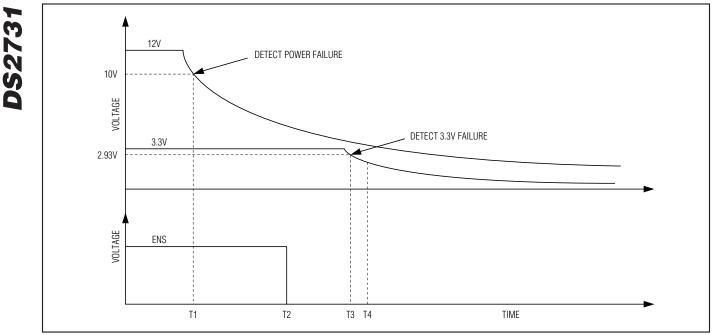

### **Power-Failure Switchover**

During a power-failure event, the DS2731 can assume responsibility for supplying power to the cache memory using the backup battery. As long as the 2MHz internal synchronous buck regulator is enabled and the battery voltage is above LO BATT, the buck regulator supplies power to the memory. During normal power the buck regulator runs off of the aux input voltage. The DS2731 monitors the aux input voltage for power failure. During a power-failure event, the DS2731 internally switches the buck-regulator supply to the battery backup. The battery is connected internally by a break-before-make switching mux. The break-before-make circuitry ensures that the battery is never connected to the 3.3V aux supply. The capacitor on the CIN pin provides power to the IC during switchover. If the buck regulator is disabled during normal power conditions, ENS must be driven low by the system when a loss of power is detected.

#### **Auxiliary Voltage**

The aux switch monitors the aux power supply. In the system, this supply fails before the cache-memory power supply. When it crosses 2.93V, a comparator in the DS2731 activates the power multiplexer and switches the power source for the buck regulator from the aux power to the battery. This occurs as a break-before-make operation to prevent current from flowing out of the battery into the aux supply.

#### **Bypass/Holdup Capacitor**

The bypass/holdup capacitor, connected to pin CIN, is sized to be able to support full input current to the switcher in the case where the ENS pin is low when the aux voltage falls below 2.93V. Since the power mux is break-before-make, the capacitor supplies power during the handover operation. Prior to the event, the capacitor is charged to 2.93V, and immediately afterwards it is connected to the battery voltage through the 1 $\Omega$  mux switch. If power is restored, the conduction path between the battery and holdup capacitor is opened before the capacitor is connected to the 3.3V aux supply.

#### **Enable Switcher**

The buck regulator is enabled by the ENS pin. If the pin is low, the regulator turns on supplying power to the cache memory. The ENS pin should be driven low by the system when the cache memory has halted active processing and is in its data-retention/refresh mode.

Figure 9. Expected Scenario for Multiplex Switchover from Aux to Battery

Actions Occurring During Time Intervals From T1 to T2: At T1, the power-failure signal occurs and the system must put the cache memory into its self-refresh mode. Then it must shut off the system cache supply. Between the time the system power supply is shut off and the ENS pin is driven low, the cache memory is powered from its local bypass capacitance.

From T2 to T3: When the ENS pin goes low, the DS2731 buck regulator turns on and takes over regulation of the cachememory voltage. The power source for the DS2731's switcher during this interval is the 3.3V aux voltage. From T3 to T4: At time T3, the DS2731 detects that the 3.3V aux supply is about to fail and activates the multiplexer. However, to prevent cross-connections between the 3.3V aux and the battery, the multiplexer is designed as break-beforemake. The interval T3-T4 is t<sub>BRK</sub>. During this interval the DS2731 switching supply uses the holdup capacitor on CIN as its power source. CIN must be sized so that it has enough capacity to hold up the regulator for t<sub>BRK</sub>.

After T4: At T4, the multiplexer connects CIN to the battery's positive terminal. The regulator operates from the battery.

## Reapplication of Power

This is essentially the reverse process from the powerloss sequence. Power is applied to the RAID card; the 12V and 3.3V buses turn on and become stable. The main cache-memory power supply turns on but the power MOSFET that connects the cache to the cachepower supply remains off. The cache-backup supply in the DS2731 automatically switches from the battery source to the 3.3V bus when the 3.3V bus goes above 2.93V. The system then disables ENS and enables the cache's power MOSFET, connecting the cache to the main cache power supply. Enough bulk storage capacitance must be available at the cache to hold up during this switchover time. The memory is now ready to exit from autorefresh mode (IDD6 for DDR2 memory) and resume full operation.

## Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 28 TSSOP     |              | <u>21-0108</u> |

**Revision History**

# DS2731

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                               | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------|------------------|

| 0                  | 11/07            | Initial release.                                          | —                |

| 1                  | 1/09             | Corrected part numbers in the Ordering Information table. | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

20

fucts **MAXIM** is a registered trademark of Maxim

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2009 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331