### STNRG011

# Digital combo multi-mode PFC and time-shift LLC resonant controller

Datasheet - production data

#### **Features**

- Digital combo multi-mode PFC + time-shift LLC resonant half-bridge controller

- Onboard 800 V startup circuit, line sense and X-cap discharge compliant with IEC 62368-1, for reduced standby power

- Enhanced fixed on time multi-mode TM PFC controller with input voltage feedforward, THD optimizer and frequency limitation

- Complete set of PFC protections

- · Time-shift control of resonant half-bridge

- Enhanced burst-mode at light load with fast transient response and line adaptive halfbridge brown-out protection

- Complete set of half-bridge protections

- Available in SO20 package

### **Applications**

- Open frame SMPS

- Flat screen TV SMPS

- ATX power supply

- · AC-DC adapter

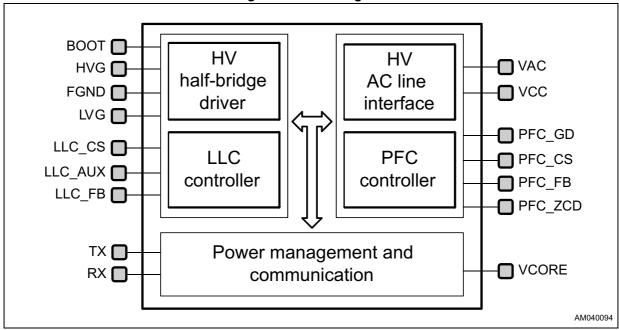

Figure 1. Block diagram

Contents STNRG011

## **Contents**

| 1 | Description |               |                                        |  |  |  |  |  |

|---|-------------|---------------|----------------------------------------|--|--|--|--|--|

| 2 | Pin co      | in connection |                                        |  |  |  |  |  |

| 3 | Abso        | lute max      | kimum ratings and thermal data7        |  |  |  |  |  |

| 4 | Detail      | ed bloc       | k diagram                              |  |  |  |  |  |

| 5 | Pin fu      | ınction       | 9                                      |  |  |  |  |  |

| 6 | Electr      | rical cha     | aracteristics11                        |  |  |  |  |  |

| 7 | Appli       | cation s      | chematics                              |  |  |  |  |  |

| 8 | Archi       | tecture       |                                        |  |  |  |  |  |

| 9 | Funct       | ional de      | escription                             |  |  |  |  |  |

|   | 9.1         | HV start      | up and VCC management                  |  |  |  |  |  |

|   | 9.2         | AC line       | monitor and protection                 |  |  |  |  |  |

|   |             | 9.2.1         | Brown-in/out                           |  |  |  |  |  |

|   |             | 9.2.2         | Line synchronization                   |  |  |  |  |  |

|   |             | 9.2.3         | Line disconnection and X-cap discharge |  |  |  |  |  |

|   |             | 9.2.4         | Vline surge stop                       |  |  |  |  |  |

|   |             | 9.2.5         | Line monitor for PFC control           |  |  |  |  |  |

|   |             | 9.2.6         | Early warning signal                   |  |  |  |  |  |

|   | 9.3         | Gate-dri      | vers                                   |  |  |  |  |  |

|   | 9.4         | PFC cor       | ntrol and fault management             |  |  |  |  |  |

|   |             | 9.4.1         | PFC resources                          |  |  |  |  |  |

|   |             | 9.4.2         | Vin reading                            |  |  |  |  |  |

|   |             | 9.4.3         | PFC output voltage feedback reading    |  |  |  |  |  |

|   |             | 9.4.4         | PFC OVP comparator                     |  |  |  |  |  |

|   |             | 9.4.5         | PFC RECOT comparator                   |  |  |  |  |  |

|   |             | 9.4.6         | PFC OC1 comparator                     |  |  |  |  |  |

|   |             | 9.4.7         | PFC OC2 comparator                     |  |  |  |  |  |

|   |             |               |                                        |  |  |  |  |  |

|      | 9.4.8   | PFC ZCD                                          | 22 |

|------|---------|--------------------------------------------------|----|

|      | 9.4.9   | PFC state machine event driven (SMED)            | 22 |

| 9.5  | PFC alg | orithm                                           | 22 |

|      | 9.5.1   | Ramp enhanced COT improved (patented)            | 22 |

|      | 9.5.2   | Operating modes                                  | 23 |

| 9.6  | PFC pro | otections                                        | 23 |

|      | 9.6.1   | PFC OVP                                          | 23 |

|      | 9.6.2   | PFC OCP2                                         | 23 |

|      | 9.6.3   | Surge                                            | 23 |

|      | 9.6.4   | PFC soft-start timeout                           | 23 |

|      | 9.6.5   | PFC UVP                                          | 23 |

|      | 9.6.6   | PFC_FB disconnection                             | 24 |

|      | 9.6.7   | PFC_CS disconnection                             | 24 |

|      | 9.6.8   | PFC_ZCD disconnection                            | 24 |

| 9.7  | LLC cor | itrol and fault management                       | 24 |

|      | 9.7.1   | LLC related resources                            | 24 |

|      | 9.7.2   | LLC OC1 comparator                               | 24 |

|      | 9.7.3   | LLC OC2 comparator                               | 25 |

|      | 9.7.4   | LLC ZCD comparator                               | 25 |

|      | 9.7.5   | LLC_FB voltage reading: OPTO feedback loop error | 25 |

|      | 9.7.6   | Shutdown feature                                 | 25 |

|      | 9.7.7   | SMEDs                                            | 25 |

|      | 9.7.8   | Algorithm                                        | 25 |

|      | 9.7.9   | Time-shift (patented)                            | 25 |

| 9.8  | LLC pro | tections                                         | 26 |

|      | 9.8.1   | Anti-capacitive protection                       | 26 |

|      | 9.8.2   | LLC OLP                                          | 26 |

|      | 9.8.3   | LLC OCP2                                         | 26 |

|      | 9.8.4   | LLC soft-start timeout                           | 26 |

|      | 9.8.5   | LLC OVP                                          | 26 |

|      | 9.8.6   | LLC_CS disconnection                             | 26 |

|      | 9.8.7   | LLC_AUX disconnection                            | 26 |

| 9.9  | ADC     |                                                  | 27 |

| 9.10 | Burst-m | ode                                              | 27 |

|      | 9.10.1  | Specific resources                               | 27 |

|      | 9.10.2  | Algorithm                                        | 27 |

|      |         |                                                  |    |

Contents STNRG011

| 12 | Revis | ion hist  | ory                 |          |      |      | 32       |

|----|-------|-----------|---------------------|----------|------|------|----------|

| 11 | Orde  | ring info | rmation             |          | <br> | <br> | <br>32   |

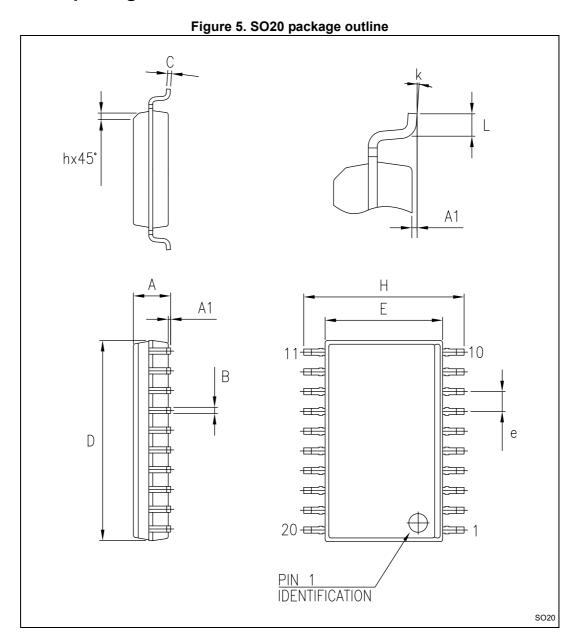

|    | 10.1  | SO20 p    | ackage information  | ١        | <br> | <br> | <br>30   |

| 10 | Packa | age info  | rmation             |          | <br> | <br> | <br>30   |

|    |       | 9.11.3    | Patches             |          | <br> | <br> | <br>. 29 |

|    |       | 9.11.2    | Black box           |          | <br> | <br> | <br>. 29 |

|    |       | 9.11.1    | Monitor             |          | <br> | <br> | <br>. 29 |

|    | 9.11  | Commu     | nication and config | guration | <br> | <br> | <br>28   |

STNRG011 Description

### 1 Description

The STNRG011 embodies a multi-mode (transition-mode and DCM) PFC controller, a high-voltage double-ended controller for the LLC resonant half-bridge, an 800 V-rated startup generator and a sophisticated digital engine, that manage optimal operation of three blocks.

The device comes in a 20-pin SO package and offers an advanced solution for power-factor-corrected high-efficiency converters supposed to comply with the most stringent energy saving regulations.

The power system and the control algorithms are managed by an 8-bit core with dedicated fast peripherals (SMED). Optimized digital algorithms together with HW analog IPs are implemented to guarantee a very high performance, BOM optimization and robustness.

The digital algorithms are stored into an internal ROM memory and all key application parameters can be stored into a device's NVM (non-volatile memory) memory during the production phase allowing wide configurability and calibration.

The device can also externally communicate through a 2-pin UART, allowing the monitoring function, the black box storing into an external E<sup>2</sup>PROM and the software patch upload from the external E<sup>2</sup>PROM.

Pin connection STNRG011

## 2 Pin connection

воот 20 VAC N.C. HVG 2 19 FGND VCC 3 18 PFC\_GD N.C. 17 PGND LVG 5 16 TX SGND 15 VCORE RX 7 14 LLC\_CS PFC\_FB 8 13 LLC\_AUX PFC\_CS 9 12

LLC\_FB

10

Figure 2. Pin connection (top view)

AM040095

PFC\_ZCD

11

## 3 Absolute maximum ratings and thermal data

Table 1. Absolute maximum ratings

| Symbol                                                                 | Pin                           | Parameter                                                  | Value                                                           | Unit |

|------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|------|

| V <sub>VAC</sub>                                                       | VAC                           | Voltage range                                              | -1 to 800                                                       | V    |

| V <sub>BOOT</sub>                                                      | BOOT                          | Floating supply voltage, referred to GND                   | -0.3 to 600 + VCC                                               | V    |

| V <sub>FGND</sub>                                                      | FGND                          | Floating ground voltage, connected to the half-bridge node | -3 up to a value included in the range BOOT - VCC and BOOT +0.3 | V    |

| dV <sub>FGND</sub> /dt                                                 | FGND                          | Floating ground max. slew rate                             | 50                                                              | V/ns |

| V <sub>HVG</sub>                                                       | HVG                           | HVG voltage                                                | FGND -0.3 to BOOT +0.3                                          | V    |

| V <sub>VCC</sub>                                                       | VCC                           | IC supply voltage                                          | -0.3 to 19                                                      | V    |

| V <sub>LVG</sub><br>V <sub>PFC_GD</sub>                                | LVG,<br>PFC_GD                | Voltage range                                              | -0.3 to VCC                                                     | V    |

| V <sub>VCORE</sub>                                                     | VCORE                         | Voltage range                                              | -0.3 to 5.5                                                     | V    |

| I <sub>PFC_CS</sub> , I <sub>LLC_CS</sub> , I <sub>PFC_ZCD</sub> ,     | PFC_CS,<br>LLC_CS,<br>PFC_ZCD | Clamped source current (pin voltage: < 0 V, self-limited)  | 2                                                               | mA   |

| V <sub>PFC_CS</sub> ,<br>V <sub>LLC_CS</sub> ,<br>V <sub>PFC_ZCD</sub> | PFC_CS,<br>LLC_CS,<br>PFC_ZCD | Positive voltage range                                     | VCORE +0.3                                                      | V    |

| V <sub>PFC_FB</sub> ,<br>V <sub>LLC_FB</sub>                           | PFC_FB.<br>LLC_FB             | Voltage range                                              | -0.3 to VCORE +0.3                                              | V    |

| V <sub>RX</sub>                                                        | RX                            | Voltage range                                              | -0.3 to VCORE +0.3                                              | V    |

| V <sub>TX</sub>                                                        | TX                            | Voltage range                                              | -0.3 to VCORE+ 0.3                                              | V    |

Table 2. Thermal data

| Symbol                | Parameter                                    | Value      | Unit |

|-----------------------|----------------------------------------------|------------|------|

| R <sub>th j-amb</sub> | Max. thermal resistance, junction to ambient | 120        | °C/W |

| T <sub>j</sub>        | Junction temperature operating range         | -40 to 150 | °C   |

| T <sub>stg</sub>      | Storage temperature                          | -55 to 150 | °C   |

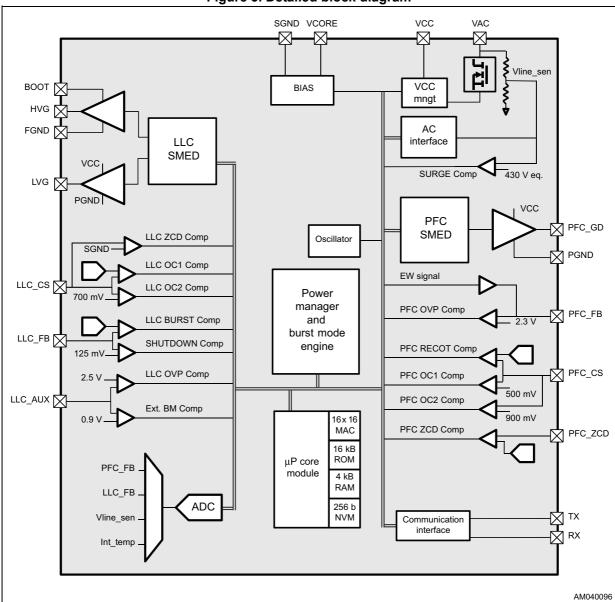

## 4 Detailed block diagram

Figure 3. Detailed block diagram

STNRG011 Pin function

## 5 Pin function

Table 3. Pin function detailed description

| No. | Name    | Function                                                                                                                                                                                                                                                                                                   |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | воот    | High-side gate-drive floating supply voltage.  The bootstrap capacitor is connected between this pin and FGND.  A fast diode has to be connected from this pin and VCC to guarantee recharge of the bootstrap capacitor.                                                                                   |

| 2   | HVG     | High-side gate-drive output.  The driver is capable of 0.5 A source and 0.75 A sink peak current (minimum values) to drive the upper MOSFET of the half-bridge leg.  A resistor internally connected to FGND ensures that the pin is never floating.                                                       |

| 3   | FGND    | High-side gate-drive floating ground.  It is the return path for the high-side gate-drive current.  Layout carefully the connection of this pin to avoid too large spikes below ground.                                                                                                                    |

| 4   | N.C.    | High-voltage spacer.  The pin is not internally connected to isolate the high-voltage section and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                  |

| 5   | LVG     | Low-side gate-drive output.  The driver is capable of 0.5 A source and 0.75 A sink peak current (minimum values) to drive the lower MOSFET of the half-bridge leg.  The pin is actively pulled to GND during UVLO.                                                                                         |

| 6   | TX      | TX pin for UART/SDA pin for I <sup>2</sup> C interface                                                                                                                                                                                                                                                     |

| 7   | RX      | RX pin for UART/SCL pin for I <sup>2</sup> C interface                                                                                                                                                                                                                                                     |

| 8   | LLC_CS  | LLC tank current sensing input. A voltage proportional to the tank current (usually obtained with a capacitive divider) has to be applied to this pin.  The information is used for zero-crossing detection (required by time-shift algorithm), the first and second level OCP.                            |

| 9   | LLC_AUX | LLC_AUX is connected to a divider sensing the auxiliary voltage from the LLC transformer.  The LLC OVP detection is active on this pin.                                                                                                                                                                    |

| 10  | LLC_FB  | The voltage from this pin is used as the LLC feedback voltage. It has to be connected to the feedback phototransistor collector and a pull-up resistor to VCORE.                                                                                                                                           |

| 11  | PFC_ZCD | PFC ZCD input, connected to the PFC AUX winding through a resistor divider detecting the PFC inductor demagnetization.                                                                                                                                                                                     |

| 12  | PFC_CS  | Current sense input for PFC.  The current flowing in the MOSFET is sensed through a resistor, and the resulting voltage is applied to this pin.  After GD turns on, a first voltage threshold cross allows enhanced COT control implementation. A second level can be detected for overcurrent protection. |

| 13  | PFC_FB  | Input for PFC output voltage. It is used for closing the PFC loop and OVP protection. It has to be connected with a voltage divider to the bulk capacitor. If the early warning feature is enabled this pin is brought to 5 V when the EW pulse is released.                                               |

| 14  | VCORE   | Internal VCORE bypass capacitor connection.                                                                                                                                                                                                                                                                |

|     |         |                                                                                                                                                                                                                                                                                                            |

Pin function STNRG011

Table 3. Pin function detailed description (continued)

| No. | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | SGND   | Signal ground. Reference ground for analog signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16  | PGND   | Power ground. Current return for the PFC gate-driver and the low-side gate-driver of the half-bridge. Keep the PCB trace that goes from this pin to the sources of the PFC and the low-side MOSFETs separate from the trace that collects the grounding of the bias components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17  | PFC_GD | PFC gate-driver output.  The output stage is able to drive power MOSFETs, it is capable of 0.7 A source current and 0.8 A sink current (minimum values).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18  | VCC    | Supply voltage of both the signal part of the IC and the gate-drivers. A bypass capacitor to GND is necessary to sustain the IC during startup and low power modes.  The voltage on the pin is internally clamped to protect the internal circuits from temporary excessive supply voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19  | N.C.   | The pin is not internally connected to isolate the high-voltage section and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20  | VAC    | High-voltage startup generator input. The pin has to be connected directly to the mains voltage through two dedicated diodes. If the voltage on the pin is higher than 50 V, an internal current source charges the capacitor connected between the pin VCC and GND until the voltage on the VCC pin reaches the startup threshold. Normally, the generator is re-enabled when the voltage on the VCC pin falls below the UVLO threshold. The pin is also used as the line voltage sensing input. This pin is internally connected to a 20 M $\Omega$ resistor divider. It is used for all line sense related functions: the AC brown-out, surge detection, line disconnection, input voltage feedforward, line synchronization. When a line disconnection is detected, the internal current source is activated to discharge the X-capacitor. |

### 6 Electrical characteristics

$T_j$  = 0 to +125 °C,  $V_{CC}$  =  $V_{BOOT}$  = 15  $V^{(a)}$ ,  $C_{HVG}$  =  $C_{LVG}$  =  $C_{PFC\_GD}$  = 1 nF; unless otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                 | Parameter                                                           | Test condition                                                                    | Min. | Тур. | Max. | Unit |

|------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| Supply voltage         |                                                                     |                                                                                   | •    | •    | •    |      |

| Vccz                   | Vcc clamp voltage                                                   | -                                                                                 | 19   | -    | -    | V    |

| Vcc                    | Operating range                                                     | After turn-on                                                                     | 9.5  | -    | 19   | V    |

| Vcc <sub>On</sub>      | Processing turn-on threshold                                        | (1)Voltage rising                                                                 | 16   | 17   | 18   | V    |

| Vcc <sub>Off</sub>     | Processing turn-off threshold                                       | (1)Voltage falling                                                                | 8    | 8.7  | 9.4  | V    |

| Hys                    | Hysteresis                                                          | -                                                                                 | -    | 8.3  | -    | V    |

| Vcc <sub>CoreOn</sub>  | VCC threshold for VCore turn-on                                     | (1)Voltage rising                                                                 | -    | 8    | -    | V    |

| Vcc <sub>CoreOff</sub> | VCC threshold for VCore turn-off                                    | (1)Voltage falling                                                                | -    | 7    | -    | V    |

| VCore                  | Operating range                                                     | I <sub>source</sub> 0 to 1 mA                                                     | 4.75 | -    | 5.25 | V    |

| Supply current         |                                                                     |                                                                                   |      |      |      |      |

| I <sub>Vccs</sub>      | Quiescent current during sleep (BM)                                 | T 25 °C                                                                           | -    | 0.5  | -    | mA   |

|                        |                                                                     | PFC and LLC off                                                                   | -    | - 18 | -    | mA   |

| I <sub>Vccop</sub>     | Operating supply current at $f_{SW}$ = 50 kHz, C = 1 nF, VCC = 12 V | PFC driver only (during PFC SS)                                                   | -    | 20   | -    |      |

|                        |                                                                     | All drivers                                                                       | -    | 22   | -    |      |

| High-voltage star      | tup generator                                                       |                                                                                   | •    |      |      |      |

| V <sub>VAC_BR</sub>    | Breakdown voltage                                                   | I <sub>HV</sub> < 50 μA<br>V <sub>CC</sub> > Vcc <sub>On</sub>                    | 800  | -    | -    | V    |

|                        |                                                                     | V <sub>VAC</sub> > 40 V<br>V <sub>CC</sub> < 0.8 V                                | -    | 1    | -    |      |

|                        |                                                                     | V <sub>VAC</sub> > 40 V<br>0.8 V < V <sub>CC</sub> < Vcc <sub>CoreOn</sub>        | -    | 6    | -    |      |

| ı                      | ON state VAC input surrent                                          | V <sub>VAC</sub> > 100 V<br>Vcc <sub>CoreOn</sub> < V <sub>CC</sub> < 14 V        | -    | 6    | -    | mΛ   |

| <sup>I</sup> VAC_on    | ON-state VAC input current                                          | V <sub>VAC</sub> > 100 V<br>14 V < V <sub>CC</sub> < Vcc <sub>On</sub>            | -    | 4    | -    | mA   |

|                        |                                                                     | 40 V < V <sub>VAC</sub> < 100 V<br>Vcc <sub>CoreOn</sub> < V <sub>CC</sub> < 14 V | -    | 20   | -    | 1    |

|                        |                                                                     | 40 V < V <sub>VAC</sub> < 100 V<br>14 V < V <sub>CC</sub> < Vcc <sub>On</sub>     | -    | 10   | -    |      |

a. Adjust  $V_{CC}$  above  $\mbox{Vcc}_{\mbox{On}}$  before setting at 15 V.

Electrical characteristics STNRG011

Table 4. Electrical characteristics (continued)

| Symbol                   | Parameter                       | Test condition                                                                    | Min.  | Тур.  | Max. | Unit |

|--------------------------|---------------------------------|-----------------------------------------------------------------------------------|-------|-------|------|------|

|                          |                                 | V <sub>VAC</sub> > 40 V                                                           | -0.5  | -0.75 | -1   |      |

|                          |                                 | V <sub>CC</sub> < 0.8 V                                                           | 0.0   | 0.70  |      |      |

|                          |                                 | V <sub>VAC</sub> > 40 V<br>0.8 V < V <sub>CC</sub> < Vcc <sub>CoreOn</sub>        | -3.5  | -5    | -7   |      |

|                          | ON state VOC shares surrent     | V <sub>VAC</sub> > 100 V<br>Vcc <sub>CoreOn</sub> < V <sub>CC</sub> < 14 V        | -     | -5    | -    | A    |

| I <sub>Vcc_charge</sub>  | ON-state VCC charge current     | V <sub>VAC</sub> > 100 V<br>14 V < V <sub>CC</sub> < Vcc <sub>On</sub>            | -     | -3.5  | -    | mA   |

|                          |                                 | 40 V < V <sub>VAC</sub> < 100 V<br>Vcc <sub>CoreOn</sub> < V <sub>CC</sub> < 14 V | -     | -18   | -    |      |

|                          |                                 | 40 V < V <sub>VAC</sub> < 100 V<br>14 V < V <sub>CC</sub> < Vcc <sub>On</sub>     | -     | -8    | -    |      |

| I <sub>VAC_off</sub>     | OFF-state VAC input current     | $V_{VAC}$ = 400 V, $V_{CC}$ > $Vcc_{On}$                                          | -     | 20    | 40   | μΑ   |

| I <sub>VAC_HV_SINK</sub> | VAC reading improvement current | V <sub>VAC</sub> = 100 V                                                          | -     | 100   | -    | μA   |

| PFC - gate-driver        |                                 |                                                                                   | I.    |       |      |      |

| V <sub>OL</sub>          | Output low voltage              | I <sub>sink</sub> = 100 mA                                                        | -     | -     | 0.7  | V    |

| V <sub>OH</sub>          | Output high voltage             | I <sub>source</sub> = -10 mA<br>V <sub>CC</sub> = 10 V,                           | 9.85  | 9.95  | -    | ٧    |

|                          |                                 | V <sub>CC</sub> = 18 V                                                            | 17.9  | 17.95 | -    |      |

| I <sub>srcpk</sub>       | Peak source current             | Cgate = 4.7 nF <sup>(2)</sup>                                                     | -0.7  | -1.1  | -    | Α    |

| I <sub>snkpk</sub>       | Peak sink current               | Cgate = 4.7 nF <sup>(2)</sup>                                                     | 0.8   | 1.3   | -    | Α    |

| t <sub>f</sub>           | Voltage fall time               | -                                                                                 | -     | 25    | -    | ns   |

| t <sub>r</sub>           | Voltage rise time               | -                                                                                 | -     | 30    | -    | ns   |

| PFC_GD_uvlo              | UVLO saturation                 | $V_{CC} = 0$ to $Vcc_{On}$ , $I_{sink} = 1$ mA                                    | -     | 0.9   | 1.15 | V    |

| Low-side gate-driv       | ver (voltages referred to GND)  | 1                                                                                 | l     |       |      |      |

| V <sub>OL</sub>          | Output low voltage              | I <sub>sink</sub> = 100 mA                                                        | -     | -     | 0.7  | V    |

| V <sub>OH</sub>          | Output high voltage             | I <sub>source</sub> = -10 mA<br>V <sub>CC</sub> = 10 V                            | 9.85  | 9.9   | -    | V    |

|                          |                                 | V <sub>CC</sub> = 18 V                                                            | 17.85 | 17.9  | -    |      |

| I <sub>srcpk</sub>       | Peak source current             | Cgate = 4.7 nF <sup>(2)</sup>                                                     | -0.5  | -0.8  | -    | Α    |

| I <sub>snkpk</sub>       | Peak sink current               | Cgate = 4.7 nF <sup>(2)</sup>                                                     | 0.75  | 1.2   | -    | Α    |

| t <sub>f</sub>           | Voltage fall time               | -                                                                                 | -     | 25    | -    | ns   |

| t <sub>r</sub>           | Voltage rise time               | -                                                                                 | -     | 40    | -    | ns   |

| LVG_uvlo                 | UVLO saturation                 | $V_{CC} = 0$ to $Vcc_{On}$ , $I_{sink} = 1$ mA                                    | -     | 0.9   | 1.1  | V    |

Table 4. Electrical characteristics (continued)

| Symbol             | Parameter                              | Test condition                                            | Min.     | Тур. | Max. | Unit                |

|--------------------|----------------------------------------|-----------------------------------------------------------|----------|------|------|---------------------|

| High-side gate-dri | ver (voltages referred to FGND)        |                                                           | <u>l</u> |      |      | <u>I</u>            |

| V <sub>OL</sub>    | Output low voltage                     | I <sub>sink</sub> = 100 mA                                | -        | -    | 0.7  | V                   |

| V <sub>OH</sub>    | Output high voltage                    | I <sub>source</sub> = -10 mA<br>V <sub>BOOT</sub> = 10 V, | 9.85     | 9.9  | -    | V                   |

|                    |                                        | V <sub>BOOT</sub> = 18 V                                  | 17.85    | 17.9 | -    |                     |

| I <sub>srcpk</sub> | Peak source current                    | Cgate = 4.7 nF <sup>(2)</sup>                             | -0.5     | -0.8 | -    | Α                   |

| I <sub>snkpk</sub> | Peak sink current                      | Cgate = 4.7 nF <sup>(2)</sup>                             | 0.75     | 1.2  | -    | Α                   |

| t <sub>f</sub>     | Voltage fall time                      | -                                                         | -        | 25   | -    | ns                  |

| t <sub>r</sub>     | Voltage rise time                      | -                                                         | -        | 40   | -    | ns                  |

| HVG_pdw            | HVG-FGND pull-down resistor            | -                                                         | -        | 25   | -    | kΩ                  |

| I <sub>FGND</sub>  | Current from V <sub>BOOT</sub> to FGND | V <sub>BOOT</sub> = 200 V                                 | -        | 1.5  | -    | μА                  |

| X-CAP discharge    | -                                      |                                                           | <b>'</b> | l    |      |                     |

| XCD_inact_time     | Inactivity detection time              | -                                                         | -        | 50   | -    | ms                  |

| I <sub>XCD</sub>   | Discharge current                      | -                                                         | 4        | -    | -    | mA                  |

| Brown-in/out       |                                        | -1                                                        | <u> </u> | I    |      | I                   |

| BI                 | TIL                                    | Vline rising                                              | 112      | 114  | 116  | V                   |

| ВО                 | - TH                                   | Vline falling                                             | -        | 108  | -    | V                   |

| BIBO_H             | HYST                                   | -                                                         | 5.25     | 6    | 6.75 | V                   |

| BO_mask            | Brown-out time                         | -                                                         | -        | 45   | -    | ms                  |

| Overtemperature (  | (by design)                            |                                                           |          |      | •    | •                   |

| OTD                | TH                                     | T rising                                                  | 130      | 140  | 150  | °C                  |

| ОТР                | HYST                                   | T falling                                                 | -        | -30  | -    | °C                  |

| ск                 | 1                                      |                                                           | <u>.</u> |      |      | ļ.                  |

| Fck                | System clock in run mode               | -                                                         | 57       | 60   | 63   | MHz                 |

| ADC                | 1                                      | 1                                                         |          | I    |      | I                   |

| ADC_res            | Resolution                             | Vin ADC > 50 mV                                           | -        | 10   | -    | bit                 |

| FSR_L              |                                        | CS                                                        | 0        | -    | 1.5  | V                   |

| FSR_H              | Conversion range                       | Other                                                     | 0        | -    | 2.5  | V                   |

| DNL                | Differential non linearity             | Vin ADC > 50 mV                                           | -        | ±1.5 | -    | Isb                 |

| Fck_ADC            | Clock frequency                        | Vin ADC > 50 mV                                           | -        | 15   | -    | MHz                 |

| Ts                 | Sampling time                          | Vin ADC > 50 mV                                           | -        | 7    | -    | ADC<br>Ck<br>cycles |

Electrical characteristics STNRG011

Table 4. Electrical characteristics (continued)

| Symbol                      | Parameter                                               | Test condition        | Min.        | Тур.                            | Max. | Unit                |

|-----------------------------|---------------------------------------------------------|-----------------------|-------------|---------------------------------|------|---------------------|

| Тс                          | Total conversion time (sampling included)               | Vin ADC > 50 mV       | -           | 18                              | -    | ADC<br>Ck<br>cycles |

| Comparators                 |                                                         |                       |             |                                 |      |                     |

| PFC_CS RECOT <sup>(3)</sup> | TH RISING (DAC 6 bits)                                  | Input pin PFC_CS      |             | SR = 12<br>EP = 1.              |      | mV                  |

|                             | HYST                                                    |                       |             | 5                               |      |                     |

| PFC_CS OC1                  | TH RISING                                               | Input pin PFC_CS      | -           | 500                             | -    | mV                  |

| 110_03001                   | TH FALLING                                              | Tiliput piil 1 1 0_00 | -           | 450                             | -    | 1111                |

| DEC                         | TH RISING                                               | Input pin DEC CS      | -           | 900                             | -    | mV                  |

| PFC_CS OC2                  | TH FALLING                                              | Input pin PFC_CS      | -           | 850                             | -    | IIIV                |

|                             | TH FALLING (TH_F)                                       |                       | 0/5         | 0/50/100/200                    |      |                     |

| PFC_ZCD ZCD <sup>(3)</sup>  | TH RISING (TH_R)                                        | Input pin PFC_ZCD     |             | 110 <sup>(4)</sup> /3<br>H_F +1 | mV   |                     |

|                             | TH RISING                                               | -Input pin PFC_FB     | -           | 2.33                            | -    | V                   |

| PFC_FB OVP                  | HYST                                                    |                       | -           | 75                              | -    | mV                  |

| LLC_FB <sup>(3)</sup>       | TH RISING                                               | landain II O FD       | 0.75/1/1.25 |                                 |      | V                   |

| BURST                       | HYST                                                    | Input pin LLC_FB      | 5/10        |                                 |      | mV                  |

| LLC FB                      | TH RISING                                               |                       | -           | 145                             | -    | mV                  |

| SHUTDOWN                    | TH FALLING                                              | Input pin LLC_FB      | -           | 125                             | -    |                     |

| LLO ALIX OVE                | TH RISING                                               | land sin LLO ALIV     | -           | 2.5                             | -    | V                   |

| LLC_AUX OVP                 | TH FALLING                                              | Input pin LLC_AUX     | -           | 2.4                             | -    |                     |

| LLO AUNT L DM               | TH RISING                                               | Les telephones Ally   | -           | 0.9                             | -    |                     |

| LLC_AUX Ext. BM             | TH FALLING                                              | Input pin LLC_AUX     | -           | 0.8                             | -    | V                   |

| LINE OLIDOF                 | TH RISING                                               | L ( . : . ) (A.C.     | -           | 430                             | -    | .,                  |

| LINE SURGE                  | TH FALLING                                              | Input pin VAC         | -           | 410                             | -    | V                   |

| LLC_CS OC1 <sup>(3)</sup>   | TH RISING   FSR = 500<br>  Input pin LLC_CS   STEP = 15 |                       |             | mV                              |      |                     |

|                             | HYST                                                    |                       | 20          |                                 | -    |                     |

| 110 00 000                  | TH RISING                                               | L                     | -           | 700                             | -    |                     |

| LLC_CS OC2                  | TH FALLING                                              | Input pin LLC_CS      | -           | 650                             | -    | mV                  |

<sup>1.</sup> Parameters tracking each other.

<sup>2.</sup> Guarantee by design, not production tested.

<sup>3.</sup> Thresholds and hysteresis are programmed by the software in use.

<sup>4.</sup> The selection for  $TH_R = 110 \text{ mV}$  is not allowed if  $TH_F = 200 \text{ mV}$ .

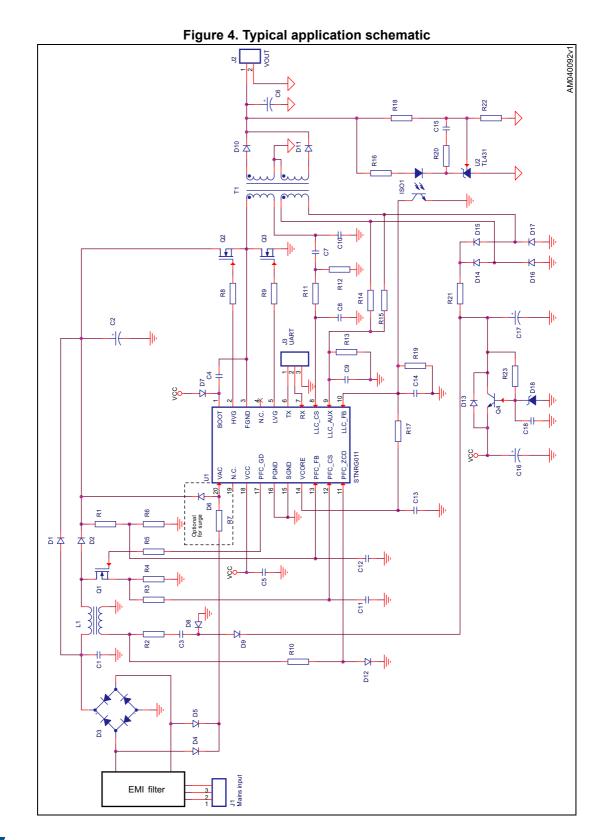

## 7 Application schematics

Architecture STNRG011

#### 8 Architecture

The PFC and LLC external MOSFETs gates are managed by the "State Machine Event Driven" (SMEDs): 2 for PFC (PFC SMEDs) and 2 for LLC (LLC SMEDs).

The SMEDs are programmable state machine driven by events:

- External events

- Analog comparators outputs

- Power manager generated events (protections)

- Internal events

- Timers events

#### **PFC SMEDs**

Inputs events: PFC RECOT, PFC OC1, PFC ZCD

Outputs: PFC\_GD

#### **LLC SMEDs**

Inputs events: LLC ZCDOutputs: LVG, HVG

The **µP subsystem** manages dynamically the control loop.

- Analog comparators thresholds setting

- SMED configuration

- SMED timers

- ADC scheduler

- Interrupt management

The multichannel **ADC** is controlled by a programmable event driven scheduler: sampling sequence can be configured and every sample can be triggered by a specific SMED state occurrence and an internal timer value. Different priorities can be programmed to allow fast sampling for real time control and slow sampling for state control (i.e. temperature).

The scheduler can be programmed to generate interrupts after completion of selectable conversions.

A dedicated AC line monitor easily follows the AC line providing system triggers.

The  $\mu P$  reads data from the ADC and performs the loop calculation with the support of a dedicated 16-b x 16-b multiplier and a 32-b accumulator unit.

A **Power management and burst-mode machine** manages the system power state in order to have very low idle consumption and fast activity restart during the burst-mode operation.

Hard protections are managed with a very low propagation delay; the protection enable and the latched/not latched response are programmable.

The power manager controls also the brown-in/out, VCC charge/discharge, AC monitor and X-cap discharge.

A **Watchdog** resets the system in case of missed μP signal for a long time.

STNRG011 Architecture

A **communication peripheral** allows serial communication at startup and during the normal operation for:

- External memory communication for

- Black box external recording

- Patch SW upload

- Monitoring

- Internal memory R/W and OTP management

- Test mode

### 9 Functional description

The main functions are:

- HV startup and VCC management

- Line monitor and protection

- Drivers

- PFC control and fault management

- Resonant LLC HB control and fault management

- Power management

- Communication and configuration

#### 9.1 HV startup and VCC management

The VAC pin voltage is a rectified sine wave at 100 Hz/120 Hz, connected to the mains AC line (Vline) through two dedicated diodes. The VAC pin is the device supply at the startup.

The VAC pin voltage is different from the PFC power path (Vin) where big caps are connected: the VAC pin partially follows the Vline also at no load condition while the Vin could be very close to a DC; this assumption allows to detect the AC line disconnection to implement the X-cap discharge function.

At the VAC pin a HV DMOS is internally connected to charge the capacitor connected to the VCC pin.

From the VCC pin an internal LDO provides the 5 V VCore for analog and digital circuitry; the digital section is supplied by the internal LDO from the VCORE pin.

At startup, from the HV DMOS the capacitor connected to the VCC pin is charged to provide the power supply to the whole device; then the HV DMOS is turned off.

The VCC pin starts sourcing current to the connected capacitor after a minimum 15 V VAC pin voltage.

The VCC capacitor charge current is limited to 0.75 mA during the first charge phase to limit the temperature increase in case the VCC pin is short-circuited at startup. After the VCC pin voltage is above 0.8 V, the charging current rises to 5 mA.

VCORE pin voltage rises when the VCC pin crosses 8 V ( $Vcc_{CoreOn}$ ). There is a VCORE overload protection that limits the VCC charging current below 1 mA in case the VCORE pin is short-circuited at startup. Then the VCC capacitor charge continues with an average current higher than 6 mA: the current is increased during the time the VAC pin voltage is below 100 V.

Once the VCC pin crosses the 17 V  $Vcc_{On}$  rising threshold the HV DMOS turns off and the whole device starts working: the  $\mu P$  boots.

If the VCC pin goes below the 9 V Vcc $_{Off}$  falling threshold (UVLO threshold) the  $\mu P$  stops working and the HV DMOS turns on again.

18/33 DocID030471 Rev 3

If the VCC pin falls below 7 V ( $Vcc_{CoreOff}$ ) the device stops working and the capacitor connected to the VCORE pin discharges. The VCC pin can rise again only after the voltage on the VCORE pin falls below 1 V.

The worst case average charging current from the 0.8~V to the  $Vcc_{on}$  threshold is estimated in 4.63~mA and 4.11~mA, in case the mains voltage is 115~Vac - 60~Hz and 230~Vac - 50~Hz respectively.

### 9.2 AC line monitor and protection

A HV voltage divider is internally connected to the VAC pin to generate Vline\_sense for the AC line monitoring and protection:

- Brown-in/out

- Line synchronization

- Line disconnection and X-cap discharge

- Surge detection and stop

- Line monitor for PFC control

#### 9.2.1 Brown-in/out

Brown-in and -out functions are implemented based on the Vline\_sense information.

The peak VAC voltage is monitored to enable and disable the PFC.

The PFC is enabled when the AC line crosses the brown-in threshold. The PFC is disabled after 45 ms the AC line is below the brown-out threshold.

In order to improve AC line reading and avoid false brown-in, the HV DMOS is turned on sinking  $I_{XCD}$  current for 100 ms in case of brown-out or line disconnection events. This function can be enabled / disabled through the dedicated NVM bit.

#### 9.2.2 Line synchronization

A dedicated digital peripheral manages the PFC synchronization with the AC line sine wave.

In order to improve AC line reading and synchronization, the HV DMOS is turned on sinking  $I_{VAC\_HV\_SINK}$  current at startup. This function can be enabled / disabled through the dedicated NVM bit.

#### 9.2.3 Line disconnection and X-cap discharge

The Vline\_sense is monitored to detect the AC line disconnection in order to discharge the X-cap through the internal HV DMOS.

The detection is based on AC activity absence on the VAC pin (the X-cap discharge function is triggered if there is no line activity for more than 50 ms). To discharge the X-cap, the HV DMOS turns on sinking a current of 4 mA minimum.

In order to improve AC line reading and avoid false brown-in, the HV DMOS is turned on sinking  $I_{XCD}$  current for 100 ms in case of brown-out or line disconnection events. This function can be enabled / disabled through the dedicated NVM bit.

The discharge current stays on until the VAC pin is discharged or the AC line activity is detected again.

#### 9.2.4 Vline surge stop

A surge can be detected on the VAC pin (430 V).

During the surge the PFC activity is stopped for one half-cycle.

If a line surge is detected during the PFC soft-start, the system shuts down with a not latched fault.

#### 9.2.5 Line monitor for PFC control

A 20  $\text{M}\Omega$  voltage divider for the AC line monitor is internally connected from the VAC pin to GND.

#### 9.2.6 Early warning signal

In case a brown-out or another stopping event (early warning managed faults) is detected then the STNRG011:

- Stops the PFC

- LLC continues switching for about 5 ms, trying to keep the LLC output voltage regulated

- PFC FB pin is pulled up to VCore voltage for about 5 msec (early warning signal)

The early warning managed faults are

- Brown-out

- X-cap

- PFC UVP

- LLC OLP

If any other faults/events will occur, the STNRG011 will stop both PFC and LLC and will generate an early warning signal for about 250  $\mu$ sec.

The early warning signal generation is active as soon as the device starts driving the PFC MOSFET.

This function can be enabled / disabled through the dedicated NVM bit.

#### 9.3 Gate-drivers

The HVG and LVG are matched drivers. Deadtimes are programmable by the user.

During the burst-mode sleep phase, the HS BOOT capacitor discharges. The burst packets always start with a LVG pulse to recharge the bootstrap capacitor. A fast external bootstrap diode is necessary.

### 9.4 PFC control and fault management

#### 9.4.1 PFC resources

Table 5. Related pins

| Pin name | Description                                | Level        | Function                              |

|----------|--------------------------------------------|--------------|---------------------------------------|

| PFC CS   | PFC MOSFET current sense                   | 0 - 125 mV   | 6-bit ramp<br>enhanced<br>COT feature |

|          |                                            | 500 mV       | OCP1                                  |

|          |                                            | 900 mV       | OCP2 fault                            |

| PFC_ZCD  | PFC auxiliary connection for ZCD detection | -            | -                                     |

| PFC_FB   | Reading for PFC Vout estimation            | ADC, 10 bits | -                                     |

| VAC      | Mains line voltage reading                 | ADC, 10 bits | -                                     |

| PFC_GD   | PFC MOSFET gate-driver                     | -            | -                                     |

#### 9.4.2 Vin reading

Input line voltage peak (Vin) reading on the VAC pin by the ADC at the AC line peak.

#### 9.4.3 PFC output voltage feedback reading

PFC output voltage reading on the PFC\_FB pin by the ADC.

#### 9.4.4 PFC OVP comparator

The PFC OVP comparator sets the limit for the PFC output voltage.

It monitors the PFC FB pin with respect to a fixed 2.3 V threshold.

#### 9.4.5 PFC RECOT comparator

The PFC RECOT comparator implements the  $T_{ON}$  adjustment for the ramp enhanced constant on-time (RECOT) control.

It monitors the PFC\_CS pin with respect to a programmable threshold.

Its output communicates to the PFC SMED.

#### 9.4.6 PFC OC1 comparator

The PFC OC1 comparator sets the limit for the operational maximum allowed peak current into the PFC MOSFET. If the OC1 threshold is hit the PFC\_GD is turned off. This protection works cycle by cycle.

It monitors the PFC\_CS pin with respect to a fixed 500 mV threshold.

Its output communicates to the PFC SMED.

#### 9.4.7 PFC OC2 comparator

The PFC OC2 comparator sets an HW limit for the current flowing into the PFC MOSFET: it triggers the OCP fault.

It monitors the PFC\_CS pin with respect to a fixed 900 mV threshold.

#### 9.4.8 PFC ZCD

The PFC ZCD comparator performs the zero cross detection to implement the soft switching of the PFC MOSFET.

It monitors the PFC\_ZCD pin with respect to two programmable rising and falling thresholds.

Its output communicates to the PFC SMED.

#### 9.4.9 PFC state machine event driven (SMED)

The PFC high frequency operations are managed by a programmable 8-state "State Machine Event Driven" (2 coupled 4-state SMEDs).

The SMED controls the PFC MOSFET based on the PFC comparators output and internally controlled counters.

It generates also the comparators' enable signals.

It works at 60 MHz.

### 9.5 PFC algorithm

The PFC operates based on a multi-mode scheme.

A constant on-time (COT) control is implemented;  $T_{ON}$  is calculated from the PFC feedback and the measured Vin peak.

T<sub>ON</sub> is calculated and updated at the line cycle valley.

Based on the working PFC's operating state variables the working mode is changed to optimize the overall efficiency.

#### 9.5.1 Ramp enhanced COT improved (patented)

The PFC control is based on the constant on-time scheme, with a proprietary improved algorithm: the calculated  $T_{ON}$  is applied only after the PFC RECOT comparator is triggered to balance the recovery diode energy and the EMI capacitor current.

The PFC RECOT comparator threshold is adjusted by the core with a 6-bit DAC and allows to apply the programmed base and ramp (defined by user into NVM).

This feature allows improving the total harmonic distortion (THD) and the power factor (PF) of the application.

#### 9.5.2 Operating modes

The PFC manager changes the operating modes by dynamically reconfiguring the SMEDs, obtaining optimal performances in term of both efficiency and THD/PF.

- Transition mode (TM mode)

- Valley skipping

- Discontinuous mode (DCM)

### 9.6 PFC protections

#### 9.6.1 PFC OVP

In case the bulk voltage triggers the PFC OVP comparator, the system enters the fault state; the overvoltage protection can be programmed as latched or not latched.

The device implements also software overvoltage protection (SW OVP) that allows turning off the PFC until the next line valley in case the SW OVP threshold is reached. The SW OVP threshold is a NVM parameter.

#### 9.6.2 PFC OCP2

If the PFC OC2 comparator is triggered, the PFC gate is truncated and remains off until the beginning of a new line half cycle. In case the PFC OC2 comparator is triggered for more than a programmable number of consecutives half line cycles the device enters the OCP2 fault and it is turned off.

The OCP2 fault can be programmed as latched or not latched.

#### 9.6.3 Surge

When the surge comparator signal is high the PFC MOSFET is turned off and an interrupt is generated. The device will turn on the PFC MOSFET at the new line half cycle if the surge comparator output is low.

#### 9.6.4 PFC soft-start timeout

If the PFC soft-start is not finished after 1 s the system enters the PFC soft-start timeout fault state and it is turned off. The fault is not latched.

#### 9.6.5 PFC UVP

If the PFC\_FB pin is below a threshold set by the user the device enters the PFC UVP fault and it is shut down. The system provides two different times of intervention configurable by NVM: adaptive and slow.

The slow intervention allows to shut off the system in case the UVP threshold is confirmed for at least 100 ms. The adaptive one allows to shut off the device immediately in case also the mains AC line is sensed below the brownout threshold for at least 1 half line cycle. On the contrary, the shut off will be delayed as if the intervention is set to slow, until the UVP and the mains conditions remain.

#### 9.6.6 PFC FB disconnection

If the PFC\_FB is stuck low the system enters the PFC\_FB disconnection fault state (latched) and it is turned off if the disconnection faults detection is enabled in NVM.

#### 9.6.7 PFC CS disconnection

If the PFC\_CS pin is stuck low (or high) during the the PFC soft-start the system enters the PFC\_CS disconnection fault state (latched) and it is shut down if the disconnection faults detection is enabled in NVM. In case the PFC\_CS is stuck high during the operative mode the system enters the PFC\_CS disconnection fault state and it is turned off if the disconnection faults detection is enabled in NVM.

#### 9.6.8 PFC ZCD disconnection

If the PFC\_ZCD pin is stuck low or high during the the PFC soft-start the system enters the PFC\_ZCD disconnection fault (latched) and it is turned off if the disconnection faults detection is enabled in NVM.

### 9.7 LLC control and fault management

#### 9.7.1 LLC related resources

| Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Level        | Function            |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|--|

| LLC_CS   | Low-side current sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 - 500 mV   | 5-bit OLP           |  |

|          | Low-side current sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 700 mV       | OCP2 fault          |  |

| LLC_AUX  | LLC auxiliary winding voltage sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.9 V        | External burst-mode |  |

|          | LLC auxiliary willuling voltage sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5 V        | LLC output OVP      |  |

| LLC_FB   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC, 10 bits | Feedback sense      |  |