# **TDC-GP1** General Purpose TDC 2 chan. 250ps / 1 chan. 125ps resolution

# **Functional description**

12.2.2001

# acam - solutions in time

Precision Time Interval Measurement

The information provided herein is believed to be reliable; however, acam assumes no responsibility for inaccuracies or omissions. Acam assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. acam does not authorize or warrant any acam product for use in life support devices and/or systems.

# Index

|   | The structure of the manual                                                         | 5      |  |

|---|-------------------------------------------------------------------------------------|--------|--|

| 1 | . Features of the TDC-GP1                                                           | 6      |  |

|   | 1.1 General Description                                                             |        |  |

|   | 1.2 Key features                                                                    |        |  |

|   | 1.3 Block diagram of the GP1                                                        |        |  |

|   | 1.4 Measurement range 11.5 Measurement range 2                                      | 8<br>0 |  |

|   | 1.5 Measurement range 2<br>1.6 R-L-C Unit                                           |        |  |

|   | 1.7 High Resolution Mode                                                            |        |  |

|   | 1.8 Resolution Adjust Mode                                                          |        |  |

|   | 1.9 Calibration                                                                     |        |  |

|   | 1.10 Main-ALU and Pre-ALU                                                           |        |  |

|   | 1.11 Result registers                                                               |        |  |

|   | 1.12 Control and value registers                                                    |        |  |

|   | 1.13 Microcontroller interface                                                      |        |  |

|   | 1.14 Miscellaneous functions of the GP1                                             |        |  |

| 2 |                                                                                     | 13     |  |

|   | <ul><li>2.1 Foreword</li><li>2.2 The Read- and Write Registers of GP1</li></ul>     |        |  |

|   | 2.2.4 Initialization                                                                |        |  |

|   | 2.3 Measuring in measurement range 1                                                |        |  |

|   | 2.4 Measuring in measurement range 2                                                | . 22   |  |

|   | 2.5 Measuring in the Resolution Adjust Mode                                         |        |  |

|   | 2.6 Add on the High Resolution Mode                                                 |        |  |

|   | 2.7 RLC-Measurements                                                                |        |  |

|   | 2.8 Calibration of the GP1                                                          |        |  |

|   | 2.9 Calculation Possibilities of the GP1                                            |        |  |

|   | 2.10 The micro-controller interface                                                 |        |  |

|   | <ul><li>2.11 Additional Functions of the GP1</li><li>2.12 Further Details</li></ul> |        |  |

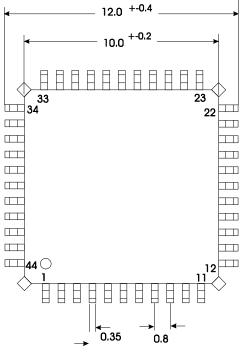

|   | 2.12.4 Package 44-TQFP                                                              |        |  |

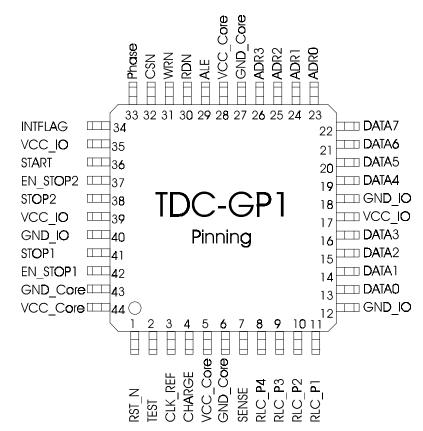

|   | 2.12.5 Pinout                                                                       |        |  |

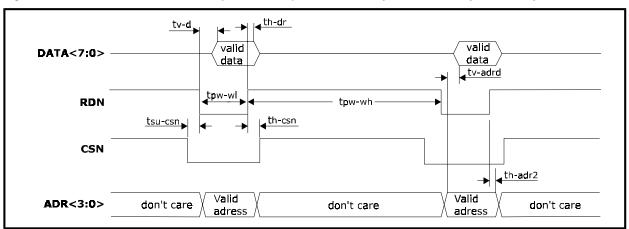

|   | 2.12.8 MIN/MAX Timings                                                              |        |  |

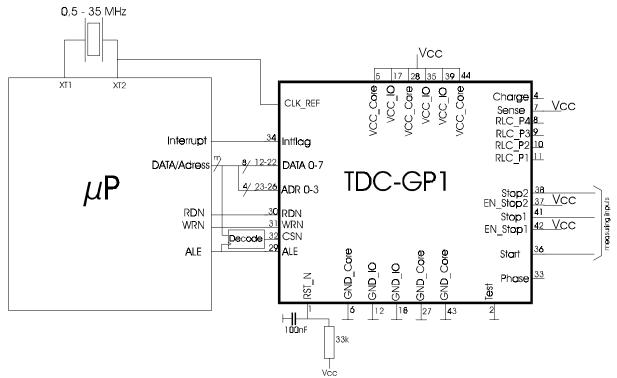

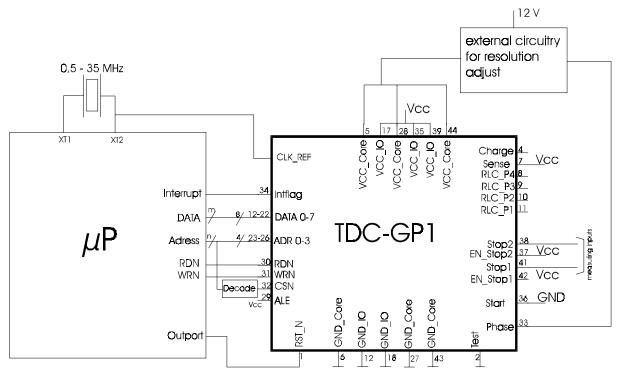

| З | . Applications                                                                      | 48     |  |

|   | 3.1 Application 1                                                                   | . 48   |  |

|   | 3.2 Application 2                                                                   | . 49   |  |

|   | 3.3 Single Measurement MB2                                                          |        |  |

|   | 3.4 Reading multihits                                                               | . 50   |  |

| 4 |                                                                                     | 51     |  |

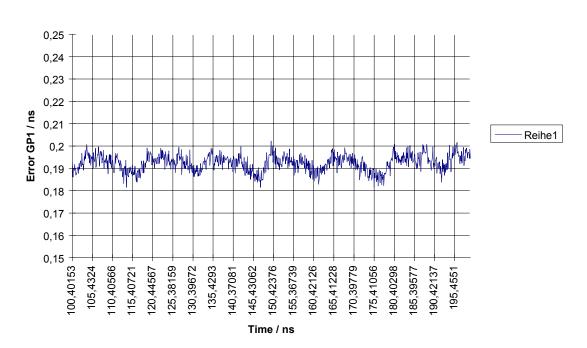

|   | 4.1 Meanings of the Terms 'Precision' and 'Resolution'                              |        |  |

|   | 4.2 Attainable Standard Deviations of the TDC-GP1                                   |        |  |

|   | 4.3 Offset Errors of the GP1                                                        |        |  |

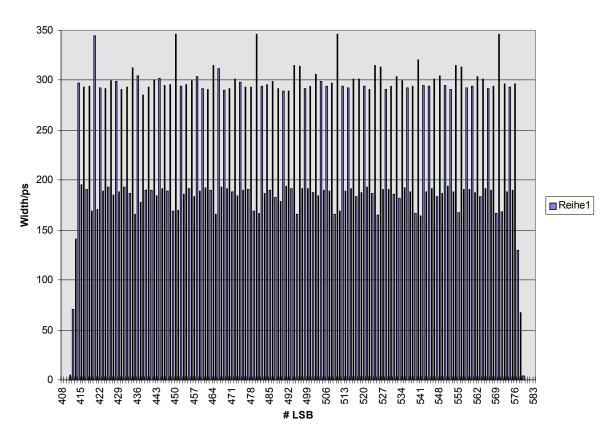

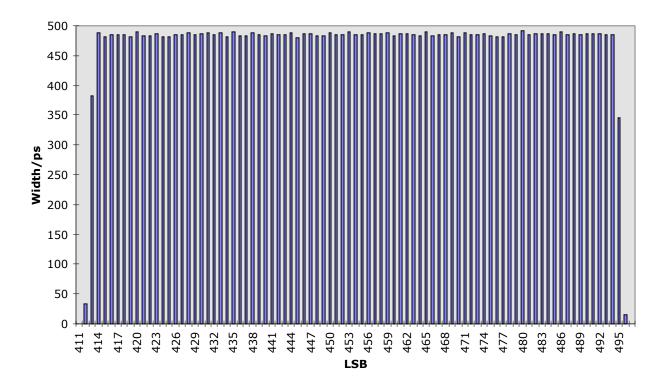

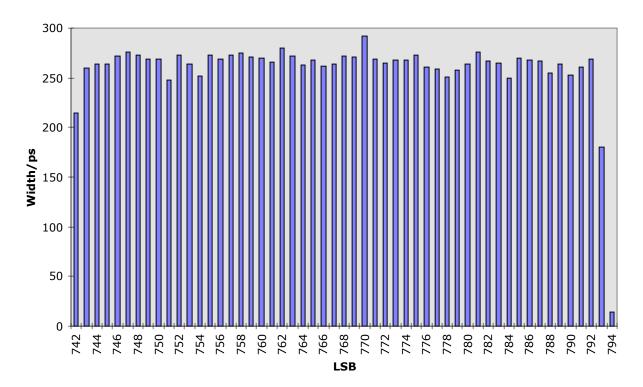

|   | <ul><li>4.4 Systematic Errors of the GP1</li><li>4.5 Histograms</li></ul>           |        |  |

| = | -                                                                                   |        |  |

| 9 | 5.1 Generation of the Calibration Values                                            | 55     |  |

|   | 5.2 Calculation Errors in Resolution Adjust Mode                                    |        |  |

|   | 5.3 Retrigger                                                                       |        |  |

| F |                                                                                     | 58     |  |

| - | Contact                                                                             |        |  |

# TDC-GP1

The structure of the manual

# 7 Guick Reference 59 7.1 Elec. Characteristics 59 7.2 Pin Description 59 7.3 Timings 59 6.4 Registers 60

# The structure of the manual

The manual of the TDC-GP1 is divided into 5 main sections. It is designed as an information and reference book. It's structure is clear so that it can answer almost any questions you have while working with the TDC-GP1 without drowning or overwhelming you in masses of unnecessarily detailed information. Certain information can therefore be found in various sections of this manual so that continuous searching and turning of pages becomes unnecessary.

The 5 main sections are:

# An introduction to the TDC-GP1

This section surveys the various functional possibilities the TDC-GP1 offers without describing any details regarding the specific functions. You will find everything noteworthy in this section concerning principle applications and measurement problems. This section should be interesting for anyone who is dealing with the chip for the first time or who is interested in getting a brief overview regarding new developments and applications.

# Details of the TDC-GP1

This section reveals in detail the functions of the chip. The various application possibilities are described with precision. A developer can find information here regarding circuit and software design.

# Application examples, application references

This section of the manual describes several specific examples regarding the circuit and controlling of the TDC-GP1.

### Measurement results and diagrams

All theory is grey. How good is the TDC-GP1 in fact? This is where the GP1 reveals it's skills as well as it's limits. This section of the manual is interesting for everyone, but especially for those customers who plan to - or have to - exhaust the chip's limits. It is also interesting for anyone looking to compare his own test results to ours. Are your measurement results clearly better or worse than ours, then call us or write us an email. We gladly give and receive tips.

# Known problems and solutions

Here you'll find descriptions and work around possibilities of problems of the TDC-GP1. 'Nobody is Perfect', the TDC-GP1 also has 'functionality', which weren't planned in this way or which are note very meaningful. This chapter should be read through in each case to be informed from the start.

# Last changes:

Okt-2000: Chapter 5.1 Secure calibration software routine Feb-2001: Chapter 2.4.4, 2.11.1 No Hit-Disable in MB2

# 1. Features of the TDC-GP1

# **1.1 General Description**

Even in today's high-tech world TDCs are still unfamiliar and unknown chips. Therefore, let's begin with a brief introduction.

The abbreviation TDC stands for  $\underline{\mathbf{T}}$  ime to  $\underline{\mathbf{D}}$  igital  $\underline{\mathbf{C}}$  onverter. These chips transform time intervals into digital values with highest precision. They can therefore be described as analogies to ADCs (<u>A</u>nalogue to  $\underline{\mathbf{D}}$  igital  $\underline{\mathbf{C}}$  onverter), which have the same function with analogous voltage. Although this definition would permit wrist watches or simple digital meters to be considered TDCs, the term TDC is used only to describe high precision time measuring devices. Generally the term 'TDC' is used for converters with a resolution of less than one nanosecond. This high resolution cannot be achieved using meters or similar devices without high expenditures so that new customized solutions become necessary.

The TDCs of the acam-messelectronic gmbh are based on the use of digital propagation times - mainly with CMOS processors. The resolution that can actually be achieved is in the range of 30 ps - 300 ps - depending on the semiconductor process used.

The GP1 seems to cover the lower resolution area with it's 250 ps in 2 channel mode or it's 125 ps in High Resolution Mode. This is however the area where most applications can be found. Just like any other chip, a TDC is not characterized by it's 'key features' alone such as for instance it's resolution but also by various other characteristics such as it's usability, it's flexibility regarding applications, it's smooth integration into available circuits, etc. We dedicated a lot of time and attention to these additional items and attempted to equip the GP1 with extensive functionality. We created a chip that enables a smooth application for many users.

# 1.2 Key features

- 2 channels with 250 ps resolution or 1 channel with 125ps resolution

- 4-fold multihit capabilities per channel Queuing for up to 8-fold multihit

- Resolution on both channels absolutely identical.

- Double pulse resolution approx. 15 ns

- Retriggerability

- 2 measurement ranges

- a. 3 ns 7,6 µs

b. 60 ns -200 ms (with predivider, only 1 channel)

The 8 events on both channels can be measured against one another arbitrarily, no minimum time difference, negative time differences possible

- Resolution Adjust Mode: quartz-accurate adjustment of resolution via software

- 4 ports for the measurement of resistors, inductors or capacitors

- Edge sensitivities of the measurement inputs are adjustable

- Enable pins are available to both stop inputs for powerful windowing possibilities

- Efficient internal 16-bit ALU, the measured result can be calibrated and multiplied with a 24 bit integer

- ALU's time for calculation is independent of the external clock. Approx. 4 µs for complete calibration and multiplication

- Up to 4 calibrated or 8 uncalibrated measurement values can be stored internally.

- Calibration and control clocks from 500 kHz up to 35 MHz (up to 100 MHz with use of internal predivider)

- Space saving and easy to handle 44-TQFP package (0.8 mm pitch, 1.27 mm max. building height)

- Industrial temperature range: -40 °C ... +85 °C

- Operating voltage : 2.7 V ... 5.5 V

- Extremely low power consumption, battery-driven operation possible

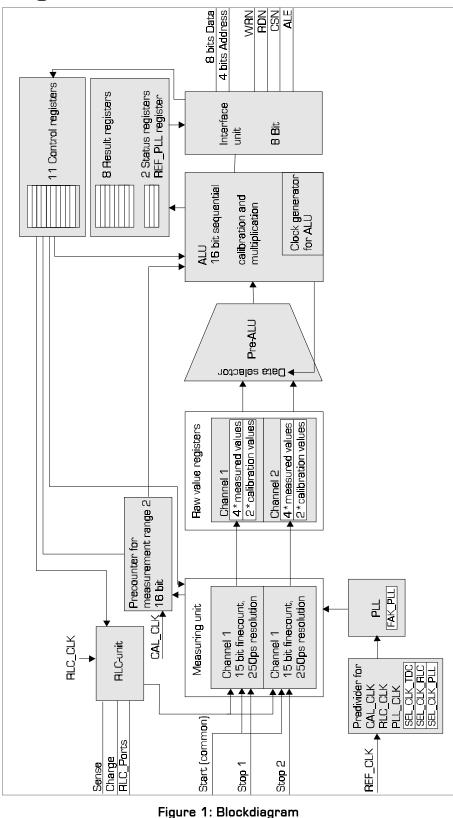

1.3 Block diagram of the GP1

# 1.3 Block diagram of the GP1

1.4 Measurement range 1

# 1.4 Measurement range 1

The GP1 offers 2 measuring channels with 250  $\ensuremath{\mathsf{ps}}$  resolution each and a basic measurement range of 15 bit.

- Both channels are absolutely identical with regard to resolution.

- Both channels have a common start input and measure up to four independent stops.

- The channels can optionally be queued behind one another, resulting in 1 channel with 8-fold multihit capability.

The various stops pulses can not only be calculated against the start pulse, but also each other. It makes no difference if the stops arrive on the same or different channels. All time difference combinations between the 8 possible results can be calculated. If you compare events which arrive on different channels it is possible to measure time differences down to zero. When comparing the events that arrive on one channel, the double pulse resolution of the specific channel limits the precision. Figure 1 illustrates the timings. The double pulse resolution is in the range of 15 ns typ. I.e. if two stops arrive on the same channel within less than 15 ns the second stop will be ignored since it arrived during the recovery time of the measurement unit.

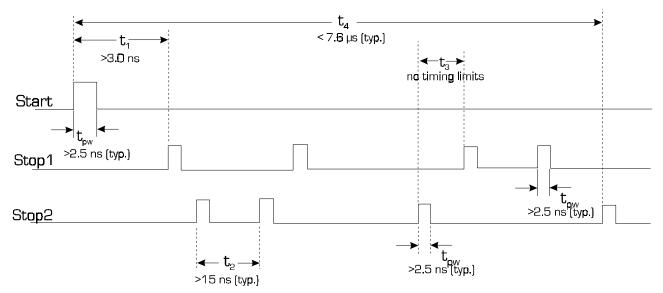

# Figure 2: Possible measuring sequences in 2-channel operation

It is not necessary to know which one of the two events was the first. If the time difference is negative the result will be negative as well.

Take as example the measurement of the phase difference of two signals which are phase modulated against each other. The first signal may be found on channel 1 and the second signal on channel 2. Not only the smallest possible phase differences can be measured but also negative phase situations can be identified and measured. The direct measurement of a phase modulation around 0 is possible.

The start on both channels must be activated at least 3 ns before the first stop. The last event that can be measured must arrive within 2<sup>16</sup> LSBs ( approx. 7.6  $\mu$ s) from the activation of the start. Otherwise the TDC will go into time-out. For measurements between stop 1 and stop 2, the position of the start pulse is not relevant to, but the time-out condition must be respected.

An additional feature in measurement range 1 is queuing. In this mode the two channels are connected internally one after the other. This results in the formation of a 1 channel TDC with 8-fold multihit capability. If the TDC is set to this option the value register of channel 1 will automatically move the stop from channel 1 to channel 2 after the register is full of hits. The stop input of channel 2 is ignored in this mode.

1.5 Measurement range 2

# 1.5 Measurement range 2

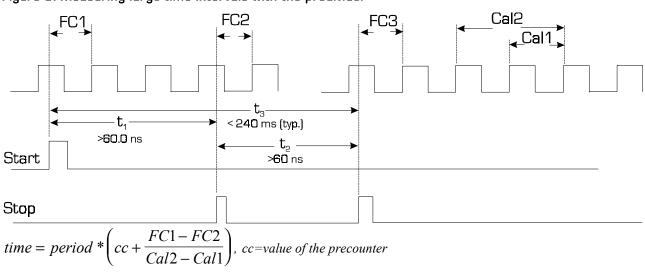

It is necessary to introduce a predivider in order to carry out measurements of large time intervals. When start is activated, the time difference from start to the next rising edge of the calibration clock is measured by the measurement unit (FC1). Afterwards a counter is activated that counts the periods of the predivider. The stop pulse of the measurement signal restarts the measurement unit. The following rising edge of the calibration clock stops the measurement unit (FC2). In the following one and two periods of the calibration clock will be measured for calibration. The GP1 is in possession of a 16 bit predivider. This allows the measurement of large time intervals (> 200 ms) with the <u>undiminished resolution of the TDCs</u>. The maximum measurement range is defined as  $T_{eff}$ \*SEL\_CLK\_TDC\*2<sup>16</sup>[2\*T<sub>ref</sub> < 7.6µs].

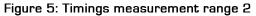

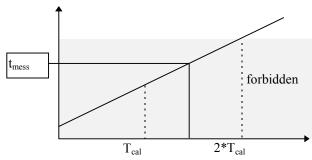

Figure 3: Measuring large time intervals with the predivider

For measurements in the measurement range 2 the GP1 is only in possession of 1 channel. The stop 1 input is active. This channel has 4-fold multihit capabilities in normal resolution mode. The stop events cannot be measured against each other, only against the start event. The double pulse resolution is 1.5  $T_{ref}$  SEL\_CLK\_TDC]+25 ns of the calibration clock.

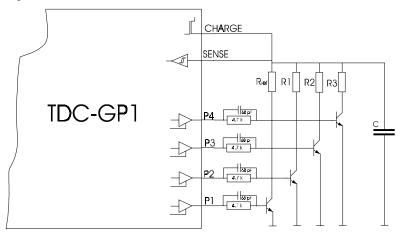

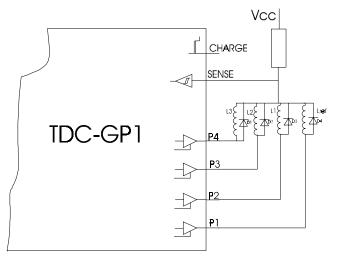

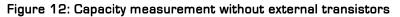

# 1.6 R-L-C Unit

Simple circuiting techniques make it possible to derive resistor, capacitor or inductor values from time interval measurements. The R-L-C unit makes this possible with only a few external components connected to the GP1. This unit enables the operation of the TDC with different sensor applications that fall back on the 3 basic dimensions of electronics. The GP1 has 4 measurement ports where resistors, inductors or capacitors can be connected. Generally, a ratio measurement happens, which means that e.g. a measuring resistor is set in proportion with a reference resistor. If the measured resistor is changing with temperature, a simple temperature measurement can be done. The same applies for other basic dimensions in electronics such as capacities and inductivities. One can also set them in relation to one another and measure other physical dimensions via time difference measurement.

# 1.7 High Resolution Mode

Due to it's circuit technique, the TDC-GP1 offers the possibility of combining both channels and therefore double the resolution of the device. This option can be activated via mode registers in the chips. This results in a 1 channel 4-fold multihit TDC with a resolution of approx. 125 ps. The stop 2 input of the TDC is turned off. The measuring possibilities of 1 channel remain according to Fig. 1. Events can still be measured against each other or against the start. If you use the High Resolution Mode in measurement range 2, only a 3-fold multihit capability remains.

# **1.8 Resolution Adjust Mode**

Another important feature of the GP1 is the Resolution Adjust Mode. In this mode the resolution of the TDC is quartz-accurately adjustable to a programmable value and <u>simultaneously for both channels</u>. As a reference for the regulation loop a clock is used which is derived from the external reference clock. The

1.9 Calibration

adjustment of the resolution happens via software by setting registers. The resulting resolution is defined by the programmer!

The resolution remains stable due to the changes in the measurement core voltage, which is regulated via PLL (Phase Locked Loop). The external circuit of the PLL regulation needs only a few small and cheap components.

<u>The Resolution Adjust Mode does not posses a start. It works with 2 channels with 4-fold multihit</u> <u>capabilities each</u>. The stop events can be measured against one another. The measurement range of this mode is only the half ( $2^{14}$  LSB, about 3.8 µs) which means that between the first and the last stop a time interval of more than  $2^{14}$  LSBs is not permitted.

# In this mode the resolution is not dependent on the single units anymore. It is independent of temperature and voltage and absolutely long-term stable. In this mode separate calibration is not necessary.

The range for resolution adjustment can reach values from -30% up to +8% of the normal resolution at 5 V and 25°C. During the entire process the unit can always be queried to check the lock of the regulation loop. If, e.g. the temperature differences are too large or an adjustment is too close to the physical limit of the resolution, the device will automatically switch to the floating resolution mode. It observes the process and switches back to regulation as soon as possible.

In this mode the unit needs more power. In contrast with normal mode the unit needs power also if no measurement is in progress. The necessary power reaches approx. 25 mA, regardless of the measuring rate. Battery operation of the GP1 is very limited in this mode.

The Resolution Adjust Mode also works in the High Resolution Mode. It does not however work in the measurement range 2.

# **1.9** Calibration

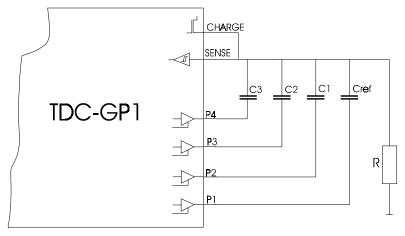

The GP1 can be calibrated via direct command or automatically via start/stop event. During the calibration process the length of one and two periods of the calibration clock are measured in a multihit process. The resulting calibration values are stored in a calibration value register. During a calculation process the main ALU refers to these registers.

A separate calibration process is activated in control register O setting bit 7 to '1'. This bit is automatically deleted after the process has ended.

When autocalibration is activated, a calibration run is started after reaching the number of selected hits on both channels. (please regard 'Known problems and solutions')

# 1.10 Main-ALU and Pre-ALU

The GP1 has 2 arithmetic logic units. In responsibility of the Pre-ALU is the conversion of raw values of the measuring unit, which are available in their own format, into unsigned integer values, so that further arithmetical calculations become possible. A data selection unit is connected in front of this ALU, which is responsible for the selection of the single raw values of the register. The pre-ALU does not need a clock. The main ALU has several purposes

- Offset correction and subtraction of non-calibrated values

- Calibration of the measured values with the Cal Values

- Multiplication of the calibrated values with a 24-bit integer. The MSB of the multiplication factor has the value 2°.

All values are channeled through the main ALU. According to the selected operation mode the values will be simply passed, will be calibrated inclusive offset correction, or they will be multiplied with a factor < 2.

<u>The main ALU has it's own clock generator that makes it independent of external clocks.</u> The calculation time for one calibration takes approx.  $2\mu$ s, for an adjoining multiplication also approx.  $2\mu$ s, so that approx.  $4 \mu$ s are needed for a complete cycle. The frequency of the clock generator can be adjusted. The main ALU is a 16 bit ALU.

# 1.11 Result registers

The main ALU stores the measurement results into the result registers (8 registers at 16 bit). Only result register values can be read out via microcontroller interface. An uncalibrated measured value (which is possible only in measurement range 1/resolution adjust) occupies 1 register. A calibrated and perhaps multiplied value occupies 2 registers. This means that 8 uncalibrated or 4 calibrated values can be stored in the GP1. Single registers or all registers can be read out at any time without destroying or promoting specific actions.

TDC-GP1

# 1.12 Control and value registers

The values are rotated and stored in register O through 7. If a further calculation process is started after the values were stored already into the top register, the new value will be stored in the lowest register. Since the micro-controller interface can activate numerous calculation processes, it is possible to perform many calculations of time differences between various hits without limitation by the number of output registers of the GP1.

# 1.12 Control and value registers

The following registers are available from GP1 Write:

- 7 control registers 8 bit each

- 4 value registers 8 bit each, 3 for the multiplication values and one for the adjust value of the PLL in the Resolution Adjust Mode

Read:

- 8 value registers for the measurement results

- 2 status registers (read only)

- 1 value register (read only) for the PLL adjust value proposal (Resolution Adjust Mode)

The registers are read out and stored via micro-controller interface

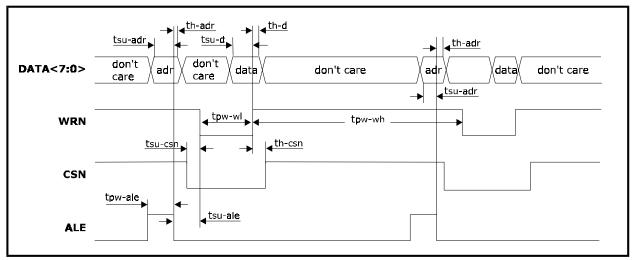

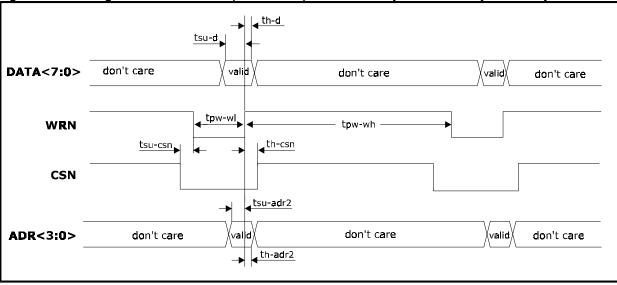

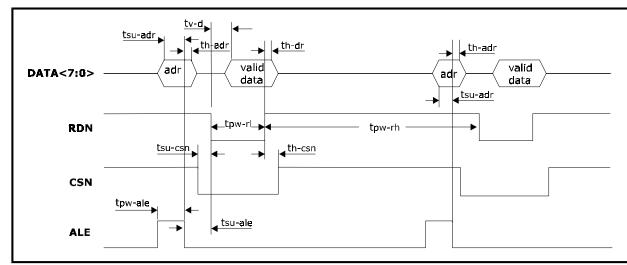

# 1.13 Microcontroller interface

The GP1 offers a standard 8-bit micro-controller interface. The values are stored and read out via the following signals

- WRN

- RDN

- CSN

- ALE

The addressing happens via a 4 bit address bus. The architecture of the interface is realized with target on familiar and common standards. The data bus and the address bus realized with separate pins. The pins can however be connected. Also, a '1' at the ALE input makes the internal address latch transparent so that the register can receive addresses directly. The data bus is bi-directional, the address bus unidirectional.

While reading the value registers an internal counter is responsible for the automatically address increment as long a the addresses remain unchanged. By simply setting the reading counter in the appropriate space and the appropriate number of reads, the measured values can be read out very simply. However, one can also jump to another measured value by setting the address pointer to a new value. A status register can be read out at any time if directly addressed. An automatic incrementation does not happen here.

# 1.14 Miscellaneous functions of the GP1

# a. Auto Noise Unit

The GP1 has a unit that adds a pseudo-random offset to the stop hits. The same offset is also added in the following calibration measurements. While measuring very stable time intervals this noise effect can achieve a suppression of the quantifying effects. A weighted average of several measured values becomes necessary. Single events are not effected in their precision. The Auto Noise Unit makes no sense in the Resolution Adjust Mode because the required effect is given automatically in this mode of measurement.

# b. Adjustable edge sensitivity

The edge sensitivity of the start input and the stop input can be adjusted via mode register.

# c. Channel enable

Every stop input can be disabled via external pins. This permits the control of a channel by adding external logic e g . Any number of hits can be faded out.

# d. Spike suppression for RDN and CSN

In case of a rough and disturbing environment it makes sense to limit the border frequency of the RDN and CSN signals so that spikes in the wires can be suppressed. This can be adjusted by the GP1 via mode register. If the **S**pike Suppression Interface is activated spikes can be suppressed for up to 6 ns. Without

# 1.14 Miscellaneous functions of the GP1

spike suppression such pulses - depending on their length - are either read by the GP1 or identified as a chip select signal. As a result false values may be stored in the register or the is retracted by mistake.

By activating the SUI interface the timing in the interface becomes slower. This should be taken into consideration.

# e. Half Resolution

Physically seen the GP1 has a relatively bad differential non-linear characteristic in normal or double resolution. This doesn't affect most applications. In some applications however (especially those involving physical experiments) a small differential non-linear characteristic is of great importance.

The characteristics of the digital TDC-principle used can be positively exploited. The differential non-linear characteristics are strictly periodical with period 2. This means that a narrow LSB is always followed by a wide LSB and vice versa. By combining 2 LSBs one can improve the non-linear characteristics by a lot. This is why the TDC-GP1 offers the option of dividing the resolution in half. The result is no more than a division by 2 of the uncalibrated measuring results.

# f. Retriggerability

If, during a measurement, more than one start pulse arrives (without retrigger) all starts after the first start will be ignored. This may not be convenient for all applications. It would sometimes be better if the last start could be measured against the stops. This option is however available in the Retrigger mode.

If more than one start arrives in retrigger mode without being intervened by a stop, every start initializes the measuring unit. As soon as the first stop arrived on one of the two channels, additional start pulses will be ignored. If the measurement unit overflows after a start and a second start arrives, the measurement unit will also be initialized again and a new measuring process will begin.

This mode is not applicable in the measurement range 2 or in the Resolution Adjust Mode.

# 2. Details of the GP1

# 2.1 Foreword

The goal of the main section is to describe to the user all possible settings of the GP1. Every possible function is explained in detail here. The appropriate adjustment of the register is explained as well as the functions of important registers including their complete content. The combination of the single features will be explained in detail as far as possible. This section of the manual is an absolute must for anyone who plans to design-in a GP1 or to write software for.

In order to understand the functions of a GP1 it is important to understand the register structure (please see the principle circuit diagram)

# a. Raw Value Registers

2\*6 raw value registers (15 bits) per channel. The resulting values of the measured unit are directly stored in this register. With the exception of the Resolution Adjust Mode all values are uncalibrated, meaning they are depending on production loss, voltage and temperature. Two of these 6 registers are reserved for calibration values.

# b. Result Registers (read only)

8 result registers with 16 bit. These registers are written on by the sequential ALU according to the set calculation mode. One register is necessary for uncalibrated values which are derived directly from the raw values or from the differences of raw values. Two registers are necessary for calibrated values. The result register is continuously written on in a circular manner, after writing to the 8th register the ALU will continue with writing to register one.

# c. Control Registers, Value Registers (write only)

7 control registers, where different process modes and other possibilities can be adjusted, and 4 value registers for the multiplication factor and the PLL adjustment factor.

# d. Status Registers (read only)

2 status registers where important status parameters of the GP1 can be read from.

# f. Value Register (read only)

The PLL in the Set Parameter Mode stores the evaluated division factor for the PLL in this register. This value is helpful for orientation, when resolution adjust is in use.

# 2.2 The Read- and Write Registers of GP1

The control registers in tabular form with short explanations

# 2.2.1 Write registers and addresses

Important remark: The write registers cannot be read.

| С | 01 | ntrol | register O |

|---|----|-------|------------|

|   |    |       |            |

| Address: | ddress: O   |                                                                                               |         |  |

|----------|-------------|-----------------------------------------------------------------------------------------------|---------|--|

| Bit No.  | Name        | Description                                                                                   | Default |  |

| 7        | CAL         | initializes a separate cal run $ ightarrow$ updates the cal values in the raw value registers | 0       |  |

| 6        | CALIBRATE   | Instructs the ALU to carry out a calibration calculation                                      | 0       |  |

| 5        | MULTIPLY    | Instructs the ALU to carry out a multiplication                                               | 0       |  |

| 4        | MESSB2      | switches to measurement with predivider, 1= with predivider                                   | 0       |  |

| З        | EN_CAL_AUTO | 1 = automatic calibration after measurement                                                   | 0       |  |

| 2        | EDGE_STP2   | selects edge sensitivity Stop2 - O=rise                                                       | 0       |  |

| 1        | EDGE_STP1   | selects edge sensitivity Stop1 - O=rise                                                       | 0       |  |

| 0        | EDGE_STA    | selects edge sensitivity Start - O=rise                                                       | 0       |  |

# Remark: optimum value for ADJ<5:0> = 0xOd

# Control register 1 Address: 1

| Bit No. | Name        | Description                        | Default |

|---------|-------------|------------------------------------|---------|

| 7       | RESO_ADJ    | switches to resolution adjust mode | 0       |

| 6       | HIGH_RES    | switches to high resolution mode   | 0       |

| 5       | ADJ<5>      | Adjustbit 5 of HIGH RES Mode       | 0       |

| 4       | ADJ<4>      | Adjustbit 4 of HIGH RES Mode       | 0       |

| 3       | ADJ<3>      | Adjustbit 3 of HIGH RES Mode       | 0       |

| 2       | ADJ<2>      | Adjustbit 2 of HIGH RES Mode       | 0       |

| 1       | ADJ<1>      | Adjustbit 1 of HIGH RES Mode       | 0       |

| 0       | ADJ <o></o> | Adjustbit O of HIGH RES Mode       | 0       |

# Control register 2

# Instruction register for ALU

| Address: 2 |                 | Calculation Instruction: HIT1_IN - HIT2_IN                  |         |

|------------|-----------------|-------------------------------------------------------------|---------|

| Bit No.    | Name            | Description                                                 | Default |

| 7          | HIT2_IN<3>      | Channel Select for upper Nibble: 0= channel1,<br>1=channel2 | 0       |

| 6          | HIT2_IN<2>      | #Hit for channel selected in bit 7                          | 1       |

| 5          | HIT2_IN<1>      | #Hit for channel selected in bit 7                          | 0       |

| 4          | HIT2_IN <o></o> | #Hit for channel selected in bit 7                          | 1       |

| 3          | HIT1_IN<3>      | Channel Select for lower Nibble: O= channel1,<br>1=channel2 | 0       |

| 2          | HIT1_IN<2>      | #Hit for channel selected in bit 7                          | 1       |

| 1          | HIT1_IN<1>      | #Hit for channel selected in bit 7                          | 0       |

| 0          | HIT1_IN <o></o> | #Hit for channel selected in bit 7                          | 1       |

| Control register 3<br>Address: 3 |                 | Control register for resolution in resolution adjust mode |         |

|----------------------------------|-----------------|-----------------------------------------------------------|---------|

| Bit No.                          | Name            | Description                                               | Default |

| 7                                | FAK_PLL<7>      | MSB division factor of PLL                                | 1       |

| 6                                |                 |                                                           | 0       |

| 5                                |                 |                                                           | 0       |

| 4                                |                 |                                                           | 0       |

| З                                |                 |                                                           | 0       |

| 2                                |                 |                                                           | 0       |

| 1                                |                 |                                                           | 0       |

| 0                                | FAK_PLL <o></o> | LSB division factor of PLL                                | 0       |

### Control register 4 Address: 4

| Auui 635 |                     |                                                                                      |         |  |

|----------|---------------------|--------------------------------------------------------------------------------------|---------|--|

| Bit No.  | Name                | Description                                                                          | Default |  |

| 7        | SEL_CLK_TDC<2>      | Factor for calibrating clock of TDC (Table in 2.11.3)                                | 0       |  |

| 6        | SEL_CLK_TDC<1>      |                                                                                      | 0       |  |

| 5        | SEL_CLK_TDC<0>      |                                                                                      | 0       |  |

| 4        | NEG_PH_PLL          | Negotiation of phase output of PLL (has to be '1'if the recommended circuit is used) | 0       |  |

| 3        | SET_PAR_PLL         | 1=Track mode of PLL (Set Par Mode)                                                   | 0       |  |

| 2        | SEL_CLK_PLL<2>      | Factor for reference clock of PLL (Table in 2.11.3)                                  | 0       |  |

| 1        | SEL_CLK_PLL<1>      |                                                                                      | 0       |  |

| 0        | SEL_CLK_PLL <o></o> |                                                                                      | 0       |  |

# TDC-GP1

# 2.2 The Read- and Write Registers of GP1

| Control | register 5 |

|---------|------------|

| Addreed | - 5<br>- 5 |

# RLC-Configuration register

| Bit No. | Name                | Description                                            | Default |

|---------|---------------------|--------------------------------------------------------|---------|

| 7       | RLC_NR<2>           | Attitude which one or how many RLC ports will be       | 1       |

|         |                     | measured                                               |         |

| 6       | RLC_NR<1>           | П                                                      | 0       |

| 5       | RLC_NR <o></o>      | 11                                                     | 0       |

| 4       | SINGLE_EN           | Measure selected ports = 1, 0= all Ports (1 to RLC_NR) | 0       |

| 3       | C_SEL               | Measure capacity ratios = 1                            | 0       |

| 2       | SEL_CLK_RLC<2>      | Factor for clock of RLC unit                           | 0       |

| 1       | SEL_CLK_RLC<1>      | П                                                      | 0       |

| 0       | SEL_CLK_RLC <o></o> | П                                                      | 0       |

# Control register 6

| Address: | 6 |

|----------|---|

|          |   |

| Bit No. | Name      | Description                                            | Default |

|---------|-----------|--------------------------------------------------------|---------|

| 7       | INT_SEL   | Interrupt Select (O= ALU ready, 1= Overflow)           | 0       |

| 6       | QUEUING   | Enable queuing in measurement range 1                  | 0       |

| 5       | RETRIG_EN | Enable retrigger mode                                  | 0       |

| 4       | NOISE_EN  | Noise enable                                           | 0       |

| 3       | RLC_EN    | Starts RLC measurement                                 | 0       |

| 2       | USE_TRANS | 1= Use of an external transistor at RLC Unit           | 0       |

| 1       | SPEED<1>  | Frequency setting BIGALU clock (default: lowest speed) | 1       |

| 0       | SPEED<0>  | (see also 2.9.8)                                       | 0       |

# Control register 7 Address: 7

| Address: / |                 |                                                   |         |

|------------|-----------------|---------------------------------------------------|---------|

| Bit No.    | Name            | Description                                       | Default |

| 7          | HALF_RES        | Half resolution of measuring circuit              | 0       |

| 6          | EN_SUI          | Enable spike suppression RDN                      | 0       |

| 5          | EN_HIT2<2>      | Number of the possible hits on channel 2 (max. 4) | 1       |

| 4          | EN_HIT2<1>      | п                                                 | 0       |

| 3          | EN_HIT2 <o></o> | "                                                 | 0       |

| 2          | EN_HIT1<2>      | Number of the possible hits on channel 1 (max. 4) | 1       |

| 1          | EN_HIT1<1>      | 11                                                | 0       |

| 0          | EN_HIT1 <o></o> | 11                                                | 0       |

# Registers 8-10 Address:8-10

|             |                              | Default |

|-------------|------------------------------|---------|

| Register 8  | Multiplication factor <70>   | 0       |

| Register 9  | Multiplication factor <158>  | 0       |

| Register 10 | Multiplication factor <2316> | 128     |

| Address | s 11:       | Special Address for Init                  |

|---------|-------------|-------------------------------------------|

| Bit No. | Name        | Description                               |

| 7       | POR.        | Power On Reset (1)                        |

| 6       | POR.        | Power On Reset (O)                        |

| 5       | POR.        | Power On Reset (1)                        |

| 4       | POR.        | Power On Reset (O)                        |

| З       | n.c.        |                                           |

| 2       | CLK_NOISE   | Clock for PRBS counter in auto noise unit |

| 1       | INIT_BIGALU | Init for Bigalu unit                      |

| 0       | INIT_TDC    | Init for TDC unit                         |

# 2.2.2 Read registers and addresses

The GP1 has the following read registers:

| Address | Name     | bits | Description                                         | with calibrated data |

|---------|----------|------|-----------------------------------------------------|----------------------|

| 0       | ERG_REGO | 16   | Result register 1                                   | Fractional portion O |

| 1       | ERG_REG1 | 16   | Result register 2                                   | Integer portion O    |

| 2       | ERG_REG2 | 16   | Result register 3                                   | Fractional portion 1 |

| 3       | ERG_REG3 | 16   | Result register 4                                   | Integer portion 1    |

| 4       | ERG_REG4 | 16   | Result register 5                                   | Fractional portion 2 |

| 5       | ERG_REG5 | 16   | Result register 6                                   | Integer portion 2    |

| 6       | ERG_REG6 | 16   | Result register 7                                   | Fractional portion 3 |

| 7       | ERG_REG7 | 16   | Result register 8                                   | Integer portion 3    |

| 8       | STAT1    | 8    | Status register 1                                   |                      |

| 9       | STAT2    | 8    | Status register 2                                   |                      |

| А       | REF_PLL  | 8    | Register for reference value of the PLL that is won |                      |

|         |          |      | on a SET_PAR run                                    |                      |

# Occupancy of status registers: Status register 1 Address: 8

| Bit No. | Name        | Description                                   |  |

|---------|-------------|-----------------------------------------------|--|

| 7       | PLL_LOCK    | Lock indication of the PLL                    |  |

| 6       | OFL         | Overflow indication of measurement unit       |  |

| 5       | HIT2_TDC<2> | Indicates number of present hits in channel 2 |  |

| 4       | HIT2_TDC<1> | Indicates number of present hits in channel 2 |  |

| 3       | HIT2_TDC<0> | Indicates number of present hits in channel 2 |  |

| 2       | HIT1_TDC<2> | Indicates number of present hits in channel 1 |  |

| 1       | HIT1_TDC<1> | Indicates number of present hits in channel 1 |  |

| 0       | HIT1_TDC<0> | Indicates number of present hits in channel 1 |  |

|         |             |                                               |  |

# Status register 2 Address: 9

| Address: 9 |            |                                                  |

|------------|------------|--------------------------------------------------|

| Bit No.    | Name       | Description                                      |

| 7          | N.C.       | not used                                         |

| 6          | N.C.       | not used                                         |

| 5          | RLC_END    | End of a RLC measurement                         |

| 4          | Multiply   | Indication of multiplication (=Bit5 ofRegister0) |

| 3          | Calibrate  | Indication of calibration (=Bit6 of Register 0)  |

| 2          | LD_REGS<2> | pointer position in result register              |

| 1          | LD_REGS<1> | pointer position in result register              |

| 0          | LD_REGS<0> | pointer position in result register              |

|            |            |                                                  |

2.2 The Read- and Write Registers of GP1

# 2.2.3 Explanations of read registers

# 2.2.3.1Data structure of the result registers

As one can see from the table above the GP1 has 8 result registers (ERG\_REGO ... ERG\_REG7) with 16 Bit each.

The data structure and the occupancy of the registers is dependent on whether calibrated or noncalibrated data are stored. For non-calibrated data one result register gets occupied. For calibrated data 2 result registers are needed. In this meaning non-calibrated data include also results that are measured in resolution adjust mode.

# Data structure of non-calibrated data

To get non-calibrated data one has to set bit 6 (Calibrate) of control register 0 to '0'. **Non-calibrated data are of the type 'Signed Integer'**. The numbers are available in complements of 2.

| Examples:        |                 |  |

|------------------|-----------------|--|

| Register content | resulting value |  |

| OxOABC           | 2748            |  |

| 0xC002           | -16382          |  |

| 0x7073           | 28787           |  |

| OxFF12           | -238            |  |

# Data structure of calibrated data

Calibrated data are fixed point numbers with 16 bits integer portion and 16 bits fractional portion.

Any calibrated result covers therefore 2 result registers. The fractional portion is in the lower registers and the integer portion digits in the upper ones.

| Examples:         |                 |                                        |

|-------------------|-----------------|----------------------------------------|

| Register contents | resulting value | Integer portion.Fractional portion     |

| OxOOO1.ABCD       | 1.671096        | (result of: 1+43981/65536)             |

| OxFFFE.1234       | -1.071105       | [only in measurement range 1]          |

| 0x0067.A001       | 103.62501       | (possible only in measurement range 2) |

| 0xD002.A001       | 53250.62501     | [possible only in measurement range 2] |

From the examples it's obvious that several cases must be distinguished:

- only in measurement range 1 negative results are possible.

- in measurement range 2 only positive results are possible, given as unsigned numbers

- without multiplication, the result in measurement range 1 cannot be bigger than ± 1.99 as it is not possible to calibrate time differences bigger than twice the period of the calibration clock.

# 2.2.3.2 Reading the result registers

While the status registers and the PLL register are read by standard memory mapping, a quite different procedure is used for the result registers.

# The following in principle applies to result registers:

Multiple results can be read by selecting the start address and sequentially reading data. An internal address pointer is increased by one after reading if the external address is held constant. To read a result always two 2 read strobes are necessary (without a change of the address). At the 8-Bit bus first the LSByte appears and afterwards the MSByte.

Examples:

1. Reading of all 8 result registers

Procedure: Put the address O and attaching 16 read strobes. Now all result registers will be read from LSByte to MSByte.

2. Reading of result register 1 and 3

Procedure: Put address 1 and two read strobes; then put address 3 and two read strobes.

# 2.2.3.3 Explanations of status registers

# Status register 1

Bit 0-5

2.2.4 Initialization

The signals HIT1\_TDC<2:0> and HIT2\_TDC<2:0> show the number hits present on each channel. It is possible for numbers of 0 to 4 respectively. These hit counters increment as soon as the hits are registered by the measuring unit. At the time of the registration these hits cannot be read, they have to be transferred with ALU operations to the result registers.

# Bit 6

Bit 6 indicates an overflow of the measuring unit. I. e. This bit is set to '1' if, during a measurement with a fixed number of allowed hits, the maximum time difference is broken.

# Bit 7

In resolution adjust mode this bit signals that the PLL has locked and the chosen resolution is set.

# Status register 2

# Bit 0-2

These bits indicate to which address of the result register the address pointer shows. I.e. if it points to '4' then the addresses 0 -- 3 already contain results, four 16-bit results or two 32-bit results are available.

The value 'O' has two meanings: that there is no result or that there are eight 16-bit results. If the interrupt flag (Pin 34) is set to 'O' this flag can be used to decide whether there is no result or 8 results. If INTFLAG is '1' there are 8 readable results present.

# Bit 3 and 4

These two bits show whether the ALU is prepared for calibration and/or multiplication. They directly reflect the content of bits 5 and 6 of the control register 0. Setting and Reading these bits can be used as a simple test for the microprocessor interface.

# Bit 5

Bit 5 indicates the end of an RLC-measurement.

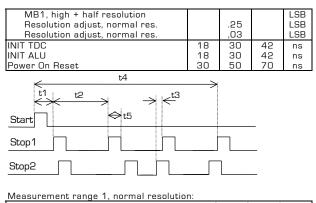

# 2.2.4 Initialization

Before starting a measurement, independently of the chosen measurement mode, an initialization of the chip is necessary. In the most elementary case this initialization is a Power On Reset. The GP1 has a comfortable Init command that offers several possibilities of the initialization. The Init command is explained by the table following:

| Address 11: |             | Special address for Init                  |

|-------------|-------------|-------------------------------------------|

| Bit<br>No.  | Name        | Description                               |

| 7           | POR.        | Power On Reset (1)                        |

| 6           | POR.        | Power On Reset (O)                        |

| 5           | POR.        | Power On Reset (1)                        |

| 4           | POR.        | Power On Reset (O)                        |

| З           | n.c.        |                                           |

| 2           | CLK_NOISE   | Clock for PRBS counter in auto noise unit |

| 1           | INIT_BIGALU | Init for Bigalu unit                      |

| 0           | INIT_TDC    | Init for TDC unit                         |

# Init of the GP1 internal measurement unit

The internal TDC unit is initialized with the INIT\_TDC. The hit counter is set to 'O', a possible timeout is deleted. The unit is ready for measurement again with the attitudes chosen before. The TDC unity is ready for measurement 30 ns after the positive edge of WRN.

# Init of the sequential ALU

The sequential ALU is initialized with INIT\_BIGALU. The write pointer is set to 'O' means to the first result register, The unity is ready again with the attitudes chosen before. 30 ns after the positive edge of WRN the BIGALU is ready again for calculation.

# Init of the Auto Noise Counter

When bit 2 is set to '1' the random counter of the auto noise unit is incremented, independently of whether this unit is enabled or not.

# Power On Reset

The Power On Reset is executed with a hex 'A' on the top nibble of the data bus. The entire chip is then set in it's basic state, all control and value registers will be initialized in their default values.

The raw value register of the TDC measuring unit and the result registers of the BIGALU can generally not be initialized. They also remain unchanged during a Power On Reset.

The Power On Reset can also be activated via the RST\_N pin with the same effect. This pin is 'low active' (min. duration 50 ns). In case that a Power On Reset is activated via software, additional commands can not processed within 50 ns after a positive edge of the WRN signal because the GP1 is in reset mode at this time.

# 2.3 Measuring in measurement range 1

# Adjustment of the measurement range:

| Relevant Register: | Control register O  | Address: O                    |

|--------------------|---------------------|-------------------------------|

| Relevant Bits:     | 4                   |                               |

| Effect:            | 0 = Measurement ran | ge 1; 1 = Measurement range 2 |

| Default:           | Measurement range 1 |                               |

# 2.3.1 Possible measuring sequences and timings

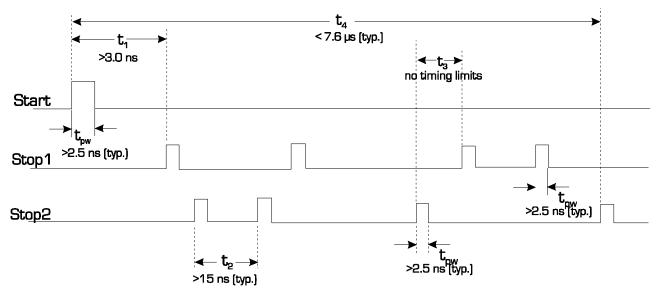

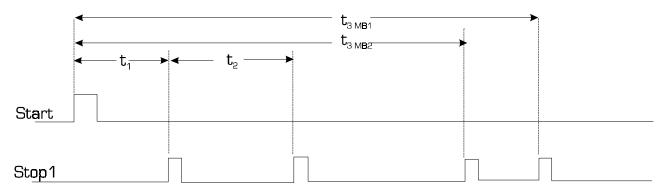

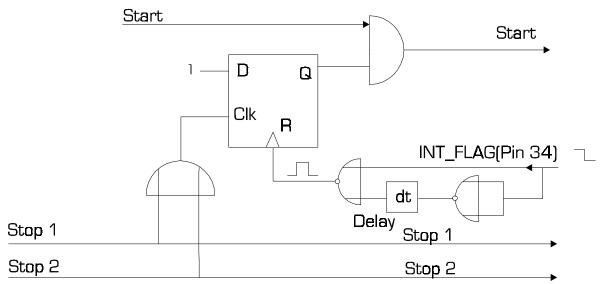

Figure 4: Timings measurement range 1

The measurement mode 1 offers a 2 channel TDC with common start and 4-fold multihit capabilities per channel. Figure 4 displays a typical measuring series.

The measuring unit for both channels is started by the sensitive edge of the start pulse. Every channel can receive four independent stops. The times of the events in relation to the common start are stored in 4 raw value registers on each channel. The following timings should be noted (typ.):

- a stop can be received at the earliest 3 ns after the start is activated. Stops that arrive earlier will be ignored

t1 min = 3 ns

- at least 15 ns must lie between 2 events on the same channel (double pulse resolution). If two events are closer, the second event will not be identified because it arrived during the channels recovery time.

→ t<sub>emm</sub> = 15 ns

- there are no restrictions or minimum time differences regarding 2 events on different channels

→ t₃ min = 0 ns

■ all measured events must arrive within 30.720 LSBs (2<sup>15</sup>-2<sup>11</sup>) after the start

2.3 Measuring in measurement range 1

■ the minimum pulse width for the start input and the stops inputs is

$\rightarrow$  t<sub>pw</sub>= 2,5 ns (typ.)

# The minimum pulse width is the same for all operation modes and for positive and negative pulses

# **2.3.2 ALU control in measurement range 1**

The detailed description of all the possibilities of the ALU is represented in section 2.9 further behind in this manual. Here a summary for measurement range 1.

In measurement range 1 it is possible to

- measure each stop on both channels against start

- measure the stops against each other

- calibrate and/or multiply the result optionally

The content of register 2 controls which events are measured against each other. It exists of two control values each 4 bit long (Nibbles). The calculation rule

Result = Lower nibble - Upper nibble

Whether it will be calibrated and multiplied is fixed in control register 0.

Some examples for clarification (for detailed explanations see section 2.9)

Example 1: Content register 0: 0x60 Content register 2: 0x01

is used.

Result: The first hit in channel 1 minus start is calculated, the result is calibrated and multiplied and written to result registers with 32bits. The complete calculation cycle lasts about 4.2  $\mu$ s. Make sure that the measurement result is not bigger than twice the cycle duration of the calibration clock. Otherwise the ALU will overflow.

Example 2: Content register 0: 0x00 Content register 2: 0xA3

Result: The 2nd hit of channel 2 is subtracted from the 3rd hit of channel 1. The result is written to the result register with 16 bit. The complete calculation cycle lasts about 180 ns.

# 2.3.2 Control of the measurements, adjustment possibilities

There are several possibilities of controlling and evaluating a measurement series.

Practically all adjustment possibilities can also be used for the other measuring modes. Please regard following advice:

# Enable the number of hits

Relevant register:Control register 7Address: 7Relevant Bits:5-0Effect:see tableDefault:4 hits per channelThe number of possible bits can be adjusted in the control

The number of possible hits can be adjusted in the control register 7 (address 7). The following adjustments should be made:

| EN_HITx<2> | EN_HITx<1> | EN_HITx <o></o> | Number of possible hits     |

|------------|------------|-----------------|-----------------------------|

| 0          | 0          | 0               | O Hits, Software Disable of |

|            |            |                 | channel                     |

| 0          | Ο          | 1               | 1 Hit                       |

| 0          | 1          | 0               | 2 Hits                      |

| 0          | 1          | 1               | 3 Hits                      |

| 1          | 0          | 0               | 4 Hits                      |

2.3 Measuring in measurement range 1

If both channels are set to O hits the entire measuring unit is disabled and a start will be ignored. This is valid for all measurement modes.

# Adjustment of edge sensitivity

| Relevant Register: | Control register O |          | Address: O |

|--------------------|--------------------|----------|------------|

| Relevant Bits:     | 2-0                |          |            |

| Effect:            | 0 = rise;          | 1 = fall |            |

| Default:           | rise               |          |            |

This adjustment can independently be used for all measuring modes.

# Retrigger Mode

| Relevant Register: | Control register 6 |        | Address: 6 |

|--------------------|--------------------|--------|------------|

| Relevant Bits:     | 5                  |        |            |

| Effect:            | 0 = off;           | 1 = on |            |

| Default:           | off                |        |            |

Every start initializes the measuring unit from the beginning until the first stop arrives. The new start is then considered the beginning of the measurement sequence (a different process happens without retrigger: further starts are ignored after the first start activated the measurement unit). After the first stop is activated on any of the two channels additional starts will be ignored. This enables numerous starts without intervening stops and to measure the last start against the stops.

<u>The retrigger mode makes sense only in measurement range 1. It must be deactivated in measurement range 2 and also has no effect in Resolution Adjust Mode.</u>

In retrigger mode the minimum time from start to a stop is redefined to

$\rightarrow$  t<sub>1 min</sub> = 6 ns

# See 5.3 Known problems and solutions: Retrigger

| Queuing            |             |          |            |

|--------------------|-------------|----------|------------|

| Relevant Register: | Control reg | jister 6 | Address: 6 |

| Relevant Bits:     | 6           |          |            |

| Effect:            | 0 = off;    | 1 = on   |            |

| Default:           | off         |          |            |

Queuing is considered the ability of using the available hits of both channels with only one stop. If queuing is enabled the second stop input is disabled. If the stop 1 input receives more than 4 stops, the stops will be switched to channel 2. The result is a 1 channel TDC with 8-fold multihit capability.

Queuing is also possible in the Resolution Adjust Mode, not in the measurement range 2.

# Auto Noise

| Relevant Register: | Control regi | ster 6 | Address: 6 |

|--------------------|--------------|--------|------------|

| Relevant Bits:     | 4            |        |            |

| Effect:            | O = off;     | 1 = on |            |

| Default:           | off          |        |            |

The Auto Noise Unit adds an offset delay to stop 1 and stop 2, which is controlled via a pseudo-random generator. The delays of the stop inputs are independent of each other so that the delay between the stops is varying.

# The meaning of this adjustment possibility:

If you wish to improve your measuring results by averaging as it is possible in numerous measuring series, it is necessary that the averaged values do not always display exactly the same time difference. Instead they should provide some 'noise' so that different steps of the characteristic curve of the GP1 are involved. This can not happen with very constant time differences. One would constantly hit the same LSB.

**Example:** While measuring a quartz-accurate clock an increase in accuracy via averaging is not possible without Auto Noise since the measured time difference is practically always the same. As a result the same LSB is constantly hit.

An auto noise unit which is part of the input circuit enables the use of weighted averaging, even for constant time differences. This auto noise unit adds an offset to the characteristic curve. The alteration is controlled via a 7 bit pseudo-random numerical generator. The length of the alteration is several LSBs.

TDC-GP1

# 2.4 Measuring in measurement range 2

The clocking of the random generator and - as a result - the generation of a new offset value is initialized setting bit 3 in register 11 to '1'. Otherwise the offset value is kept unchanged. This gives all the flexibility to the user he needs when using this option.

The offset must be kept constant during the calibration cycle that belongs to the measured value. This is automatically guarantied when autocalibration is in use. With a separate calibration it must be controlled directly.

Auto Noise is also applicable in measurement range 2. This option makes no sense in Resolution Adjust Mode and should therefore be turned off.

# 2.4 Measuring in measurement range 2

Adjustments in the measurement range:

| Relevant Register: | Control register O       | Address: O              |

|--------------------|--------------------------|-------------------------|

| Relevant Bits:     | 4                        |                         |

| Effect:            | 0 = Measurement range 1; | 1 = Measurement range 2 |

| Default:           | Measurement range 1      |                         |

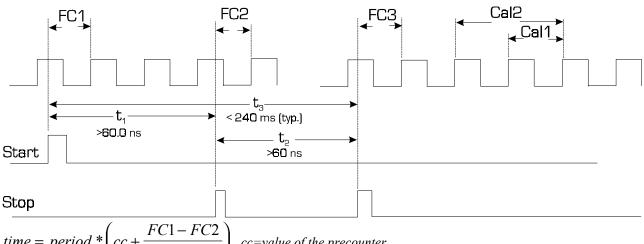

# 2.4.1Possible measuring sequences and timings

following stops will be handled like FC2. According to the formula in Figure 5 the measured time interval can be calculated, using existing calibration values or calibrated values generated after the measuring process. The GP1's predivider is 16 bits wide. This allows to measure large time intervals > 200 ms with the high resolution of the TDC and corresponds to <u>30 bit dynamic range</u>.

When using measurement range 2 only one channel is available. The stop 1 input is active. This channel has 4-fold multihit capability in normal resolution. No time differences between stops can be calculated, only against the start event.

The following timings should be noted:

- a stop can arrive 1.5 calibration clock periods +25 ns after the start at the earliest. Stops that arrive earlier will be ignored  $\rightarrow t_{1min} = 1.5 * CAL_CLK + 25ns$

- at least 1.5 calibration clock periods +25 ns must lie between two stops. If 2 stops are closer together, the second stop will not be recognized.

$\rightarrow$  t<sub>2min</sub> = 1.5 \* CAL\_CLK + 25ns

■ all measured stops arrive must within 2<sup>16</sup> calibration clock periods

$$\rightarrow$$

t<sub>3max</sub> = 2<sup>16</sup> \* CAL\_CLK

TDC-GP1

# 2.4 Measuring in measurement range 2

The calibration clock is derived from the external reference clock in combination with the calibration clock divider (register 4, bits 5-7).

# $CAL_CLK = T_{ref} * SEL_CLK_TDC.$

The higher the value for the clockdivider, the larger is the measurement range  $t_{\text{Smax}}$  and the worse is the double pulse resolution  $t_{\text{Pmin}}$ .

| Example 1:                                  |           | Example 2:                                 |           |

|---------------------------------------------|-----------|--------------------------------------------|-----------|

| Reference clock 20MHz: Tref                 | = 50ns.   | Reference clock 20MHz: Tref                | = 50ns.   |

| Calibration clock divider                   | = 64      | Calibration clock divider                  | = 1       |

| $\Delta t_{max} = 50 ns * 64 * 2^{16}$      | = 209.7ms | $\Delta t_{max} = 50 ns * 1 * 2^{16}$      | = 3.277ms |

| $\Delta t_{max} = 1.5 * 50 ns * 64 + 24 ns$ | = 4824ns  | $\Delta t_{max} = 1.5 * 50 ns * 1 + 24 ns$ | = 99ns    |

A time interval bigger than 200 ms can be measured with undiminished resolution of the GP1 using a lower frequency calibration clock. One should however acknowledge that the absolute precision of the measured time difference is dependent upon the calibration clock.

The upper limit of the measurement range is defined as

$2*T_{ref}*SEL_CLK_TDC < 30.720*Resolution (~7.6 \mu s).$

<u>Behavior of the GP1 at too small time intervals</u>: A time difference that is smaller than  $(1.5*CAL_CLK + 25 ns)$  cannot be measured with safety. The behavior of the GP1 can be described like this: time intervals between  $(0.5*CAL_CLK+25 ns)$  and  $(1.5*CAL_CLK+25ns)$  may be measured depending on the phase relationship between the start/stop pulses and the calibration clock. The probability that the value still can be measured decreases at sinking time intervals. Below  $(0.5*CAL_CLK + 25ns)$  no stop is recognized. It is important to know that no wrong results will occur. If it happens, that a time difference is measured, this will be correct. In case the time difference isn't measured the related stop is ignored an the measuring unit still continuos waiting for stops. If no further stop arrives an overflow of the measuring unit will be indicated.

# 2.4.2 Occupancy of raw value registers with measured values

In order to fully understand several adjustments in measurement range 2 and to successfully control this measurement mode it is absolutely necessary to be aware of how the raw value registers are occupied with measured values.

Each of the two measuring channels has 4 raw value registers where uncalibrated values of the measuring unit can be stored. These registers are occupied in measurement range 2 as follows:

| Channel | Raw Value<br>register | Stored values in measurement range 2 |                 |  |

|---------|-----------------------|--------------------------------------|-----------------|--|

|         |                       | Normal                               | High Resolution |  |

| 1       | 1                     | FC 1                                 | FC 1            |  |

| 1       | 2                     | FC 2                                 | FC 2            |  |

| 1       | 3                     | FC 3                                 | FC 3            |  |

| 1       | 4                     | FC 4                                 | FC 4            |  |

| 2       | 1                     | FC 5                                 | FC 1            |  |

| 2       | 2                     | n.c.                                 | FC 2            |  |

| 2       | 3                     | n.c.                                 | FC 3            |  |

| 2       | 4                     | n.c.                                 | FC 4            |  |

For completeness the 'High Resolution' Mode is displayed as well.

# 2.4.3 ALU control in measurement range 2

The detailed description of all the possibilities of the ALU is represented in section 2.9 further behind in this manual. Here a summary for the measurement range 2.

In measurement range 2 it's possible to

measure the stops against start.

2.4 Measuring in measurement range 2

### multiply the result.

It's not possible to measure the stops against each other.

Only calibrated results can be given out. Always the calibrate bit in register O must be set.

The control of which event is calculated against start is done in control register 2. It exists of 2 control values each of 4 bit (Nibbles). The calculation rule is

Result = Lower nibble - Upper nibble.

The ALU must be instructed in a way, that for the desired hit the correct finecounts are subtracted according to the formula

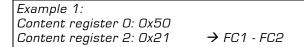

$$\Delta t = CAL\_CLK * \left(CC + \frac{FC1 - FC2}{Cal2 - Cal1}\right)$$

Some examples for clarification (For a detailed description see section 2.9)

Result: The time difference between the first hit and start is calculated, the result is calibrated and written to the result register with 32 bit. The complete calculation cycle lasts about 2.2  $\mu$ s.

Example 2: Content register 0: 0x50 Content register 2: 0x91 → FC1-FC5

Result: The time difference between the 4th hit and start is calculated, the result is calibrated and written to the result register with 32 bit. The complete calculation cycle lasts about 2.2 µs.

# 2.4.4 Control of the measuring

# Enable number of hits

| Relevant Register: | Control register 7      | Address: 7                      |

|--------------------|-------------------------|---------------------------------|

| Relevant Bits:     | 5-0                     |                                 |

| Effect:            | see table               |                                 |

| Default:           | 4 hits per channel (val | id only in measurement range 2) |

| EN_HIT1<20> | EN_HIT2<20> | No. of Hits |

|-------------|-------------|-------------|

| 2           | 0           | 1           |

| 3           | 0           | 2           |

| 4           | 0           | 3           |

| 4           | 1           | 4           |

The 2 finecount values (FC1 and FC2) are necessary for the generation of the measured values. For every further hit an additional FC value will be generated. The FC1 value is necessary for the start pulse and therefore for every measurement.

### Adjustments of edge sensitivity

Adjustments identical with measurement range 1, please see 2.3.4!!!

# Retrigger Mode

This mode can not be used in measurement range 2. It is absolutely necessary to turn it off!!!!

### Queuing

Queuing has no effect in measurement range 2.

# Auto Noise

The Auto Noise Unit functions like in measurement range 1. <u>The only difference is that while using the Auto Noise Unit no 4-fold multihit capability but only 3-fold multihit is given.</u>

**<u>ATTENTION</u>**: The fourth hit is permitted and will also be accepted. However, since the FC 5 value is found in the second channel, a different offset value is valid. The ALU doesn't take this into account. The results errors are even greater than measuring errors.

The Stop-Enables (pins 37, 42) must be activated for the duration of the measurement.

### <u>Please note:</u>

Auto Noise only makes sense in measurement range 2 when the start pulse is rigid in phase to the calibration clock. If the start pulse and calibration clock have no specific phase relation the Auto Noise becomes unnecessary. It practically occurs by itself.

# 2.5 Measuring in the Resolution Adjust Mode

# Adjustments of the measuring mode

| Relevant Register: | Control regis | ter 1  | Address: 1 |

|--------------------|---------------|--------|------------|

| Relevant Bits:     | 7             |        |            |

| Effect:            | O = off       | 1 = on |            |

| Default:           | off           |        |            |

In principle the high resolution of the GP1 is derived from the internal 'gate propagation times'. The gate propagation time is dependent upon voltage, temperature and the manufacturing process. Due to this dependency the resolution of the GP1 is not known and must first be calculated via calibration measurements. In addition, the resolution is not stable, it sways with voltage and temperature. <u>This does not apply in the Resolution Adjust Mode of the GP1</u>. In this mode the resolution of the GP1 can be adjusted quartz-accurately and absolutely temperature stable via Phase Locked Loop. The Phase Locked Loop regulates the core voltage of the GP1 so that the resolution is set exactly to the value programmed.

The Resolution Adjust Mode can be used in measurement range 1 during normal resolution as well as with High Resolution (Please see the limits given in the following section).

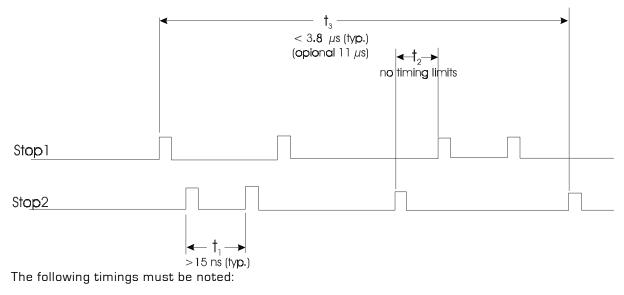

# 2.5.1 Possible measuring sequences and timings

The Resolution Adjust Mode works without the start input. The reason is that the measuring core can principally be found in a different operating mode. The measurement core is working all the time. The first stop pulse that arrives, whether on channel one or two, will be interpreted as start.

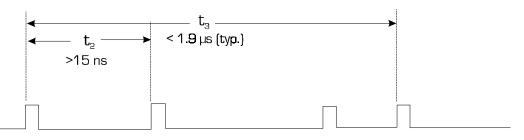

# Figure 6: Timings resolution adjust mode

there must be at least 15 ns time difference between 2 events on the <u>same</u> channel (double pulse resolution). If the events are closer, the second event won't be recognized because it arrives during the recovery time of the channel

Measurement range1: t1 min = 15 ns (typ.)

- no minimum time difference is required between 2 events on different channels

- Measurement range1: t<sub>2 min</sub> = 0 ns (typ.)

- all measured events must arrive within 15.360 LSBs (2<sup>14</sup>-2<sup>11</sup>) after the first event on one of the stop inputs

Measurement range1: t₃ max ≈ 3,8 µs (typ.)

# 2.5.2 ALU control in Resolution Adjust Mode

A detailed description of all the possibilities of the ALU is represented in section 2.9 further behind in this manual. Here a summary for the resolution adjust mode.

In resolution adjust mode it's possible to measure all stop events of both channels against each other. It's not possible to calibrate or multiply.

The control of which events are measured against each other is done in register 2. It exists of two adjustment values each 4 bit long (Nibbles). The calculation rule is:

Result = Lower nibble - Upper nibble. Some examples for clarification (For details see section 2.9)

Example 1: Content register 0: 0x00 Content register 2: 0x21

Result: The 2nd hit on channel 1 is subtracted from the first hit on channel 1, the result is written to the result register with 16 bit. The complete calculation cycle lasts about 180ns.

Example 2: Content register 0: 0x00 Content register 2: 0xA3

Result: The 2nd hit of channel 2 is subtracted from the 3rd hit on channel 1, the result is written to the result register with 16 bit. The complete calculation cycle lasts about 180 ns.

# 2.5.3 Limits in Resolution Adjust Mode

For Resolution Adjust Mode the following restrictions apply. Please note:

# Measurement range 2 is not allowed

The Resolution Adjust Mode can only be used in measurement range 1. No effective measurements are possible in measurement range 2. Since the construction of the measurements in measurement range 2 always demands a normalization (i.e. a calibration), a similar calculation also becomes necessary in the Resolution Adjust Mode, which would dissolve the positive effect of this mode.

# No calibration value generation possible

In the Resolution Adjust Mode a calibration value generation is not possible and also not necessary.

# No calibrate or multiply of the ALU

In this mode it is not possible for the ALU to perform a calibration. Multiplication can be done if the calculated value is positive.

# The measurement range is only half as large as without Resolution Adjust (15.360 LSBs)

Interpreting the results in a correct way it is possible to extend the measurement range to the triple (not possible in high resolution mode). See section 2.5.8.

No negative results at ' High Resolution '

In the High Resolution mode it isn't possible to calculate negative times. In fact this isn't necessary, because in this mode only multiple hits of one channel are measured and it is known before calculation which event is the first. The hit with the lower hit number can be subtracted from the hit with the higher hit number, not vice versa.

# 2.5.4 External circuit of the PLL

In case the Resolution Adjust mode should be used, an external circuit for the core supply voltage becomes necessary.

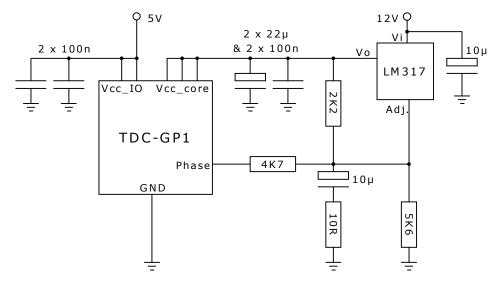

# Figure 7: PLL external circuit

Figure 7 displays an example of an inexpensive external circuit for the core supply voltage of the GP1 running in resolution adjust mode. It should be noted that the core voltage is regulated and not the I/O voltage of the module. The I/O voltage remains at 5 V. Otherwise the input protection diodes will be overdriven due to the too small voltage caused by the regulation.

Power consumption: The power consumption of the GP1 is higher in the Resolution Adjust mode. It is approx. 25 mA and is practically independent of the measuring rate.

# 2.5.5 Control of the measuring, Adjustment possibilities

# Adjustments of the measurement mode

| Relevant Register: | Control regist | er 1   | Address: 1    |

|--------------------|----------------|--------|---------------|

| Relevant Bits:     | 7              |        |               |

| Effect:            | O = off;       | 1 = on | ;Default: off |

|                    |                |        |               |

### Enable the number of hits

| Relevant Register:<br>Relevant Bits: | Control register 7<br>5-0       | Address: 7 |