# **Revision History**

# AS4C32M16D1 - 60-Ball, 8x13x1.2 mm (max) TFBGA PACKAGE

| Revision | Details               | Date        |

|----------|-----------------------|-------------|

| Rev 1.0  | Preliminary datasheet | August 2014 |

# 32M x 16 bit DDR Synchronous DRAM (SDRAM)

TFBGA option - Advanced (Rev. 1.0, Aug. /2014)

## Features

- Fast clock rate: 200MHz

- Differential Clock CK & CK

- Bi-directional DQS

- DLL enable/disable by EMRS

- Fully synchronous operation

- Internal pipeline architecture

- Four internal banks, 8M x 16-bit for each bank

- Programmable Mode and Extended Mode registers

- CAS Latency: 2, 2.5, 3

- Burst length: 2, 4, 8

- Burst Type: Sequential & Interleaved

- Individual bytes write mask control

- DM Write Latency = 0

- Auto Refresh and Self Refresh

- 8192 refresh cycles / 64ms

- Precharge & active power down

- Power supplies: VDD & VDDQ =  $2.5V \pm 0.2V$

- Operating temperature range

- Commercial (0° ~ 70°C)

- Industrial (-40° ~ 85°C)

- Interface: SSTL 2 I/O Interface

- Package: 60-Ball, 8x13x1.2 mm (max) TFBGA - Pb free and Halogen Free

All parts are ROHS compliant

## Overview

The AS4C32M16D1 is a high-speed CMOS double data rate synchronous DRAM containing 512 Mbits. It is internally configured as a guad 8M x 16 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CK). Data outputs occur at both rising edges of CK and  $\overline{CK}$ . Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a BankActivate command which is then followed by a Read or Write command. The device provides programmable Read or Write burst lengths of 2, 4, or 8. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst sequence. The refresh functions, either Auto or Self Refresh are easy to use. In addition, 512Mb DDR features programmable DLL option. By having a programmable mode register and extended mode register, the system can choose the most suitable modes to maximize its performance. These devices are well suited for applications requiring high memory band width; result in a device particularly well suited to high performance main memory and graphics applications.

# Table 1. Ordering Information

| Part Number      | Clock  | Data Rate   | Package       | Temperature | Temp Range |

|------------------|--------|-------------|---------------|-------------|------------|

| AS4C32M16D1-5BCN | 200MHz | 400Mbps/pin | 60 ball TFBGA | Commercial  | 0 ~ 70°C   |

| AS4C32M16D1-5BIN | 200MHz | 400Mbps/pin | 60 ball TFBGA | Industrial  | -40 ~ 85°C |

B: indicates TSOP II package

C: indicates Commercial temp.

I: indicates Industrial temp.

N: indicates lead free ROHS

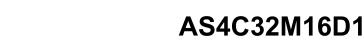

# Figure 1. Ball Assignment (Top View)

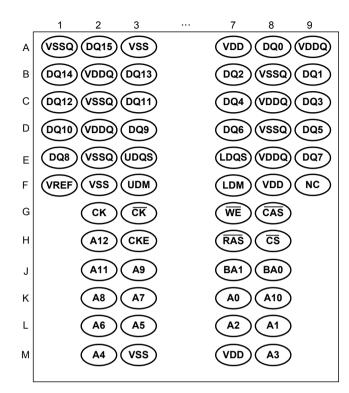

## Figure 2. Block Diagram

# Pin Descriptions

# Table 2. Pin Details

| Symbol      | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СК, СК      | Input             | <b>Differential Clock:</b> CK and $\overline{CK}$ are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of $\overline{CK}$ . Input and output data is referenced to the crossing of CK and $\overline{CK}$ (both directions of the crossing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CKE         | Input             | <b>Clock Enable:</b> CKE activates (HIGH) and deactivates (LOW) the CK signal. If CKE goes low synchronously with clock, the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. When all banks are in the idle state, deactivating the clock controls the entry to the Power Down and Self Refresh modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA0, BA1    | Input             | <b>Bank Activate:</b> BA0 and BA1 define to which bank the BankActivate, Read, Write, or BankPrecharge command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A0-A12      | Input             | <b>Address Inputs:</b> A0-A12 are sampled during the BankActivate command (row address A0-A12) and Read/Write command (column address A0-A9 with A10 defining Auto Precharge).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ĊS          | Input             | <b>Chip Select:</b> $\overline{CS}$ enables (sampled LOW) and disables (sampled HIGH) the command decoder. All commands are masked when $\overline{CS}$ is sampled HIGH. $\overline{CS}$ provides for external bank selection on systems with multiple banks. It is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RAS         | Input             | <b>Row Address Strobe:</b> The $\overline{RAS}$ signal defines the operation commands in conjunction with the $\overline{CAS}$ and $\overline{WE}$ signals and is latched at the positive edges of CK. When $\overline{RAS}$ and $\overline{CS}$ are asserted "LOW" and $\overline{CAS}$ is asserted "HIGH," either the BankActivate command or the Precharge command is selected by the $\overline{WE}$ signal. When the $\overline{WE}$ is asserted "HIGH," the BankActivate command is selected and the bank designated by BA is turned on to the active state. When the $\overline{WE}$ is asserted "LOW," the Precharge command is selected by BA is selected and the bank designated by BA is turned on to the active state. When the $\overline{WE}$ is asserted "LOW," the Precharge command is selected and the bank designated by BA is selected and the bank designated by BA is selected. |

| CAS         | Input             | <b>Column Address Strobe:</b> The $\overline{CAS}$ signal defines the operation commands in conjunction with the $\overline{RAS}$ and $\overline{WE}$ signals and is latched at the positive edges of CK. When $\overline{RAS}$ is held "HIGH" and $\overline{CS}$ is asserted "LOW," the column access is started by asserting $\overline{CAS}$ "LOW." Then, the Read or Write command is selected by asserting $\overline{WE}$ "HIGH" or "LOW".                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| WE          | Input             | Write Enable: The $\overline{WE}$ signal defines the operation commands in conjunction with the $\overline{RAS}$ and $\overline{CAS}$ signals and is latched at the positive edges of CK. The $\overline{WE}$ input is used to select the BankActivate or Precharge command and Read or Write command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LDQS,       | Input /           | Bidirectional Data Strobe: Specifies timing for Input and Output data. Read Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| UDQS        | Output            | Strobe is edge triggered. Write Data Strobe provides a setup and hold time for data and DQM. LDQS is for DQ0~7, UDQS is for DQ8~15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDM,<br>UDM | Input             | <b>Data Input Mask:</b> Input data is masked when DM is sampled HIGH during a write cycle. LDM masks DQ0-DQ7, UDM masks DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ0 - DQ15  | Input /<br>Output | <b>Data I/O:</b> The DQ0-DQ15 input and output data are synchronized with positive and negative edges of LDQS and UDQS. The I/Os are byte-maskable during Writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vdd         | Supply            | Power Supply: $2.5V \pm 0.2V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vss  | Supply | Ground                                                                                       |

|------|--------|----------------------------------------------------------------------------------------------|

| Vddq | Supply | <b>DQ Power:</b> 2.5V $\pm$ 0.2V. Provide isolated power to DQs for improved noise immunity. |

| Vssq | Supply | DQ Ground: Provide isolated ground to DQs for improved noise immunity.                       |

| VREF | Supply | Reference Voltage for Inputs: +0.5*VDDQ                                                      |

| NC   | -      | No Connect: These pins should be left unconnected.                                           |

# **Operation Mode**

Table 3 shows the truth table for the operation commands.

| Table 3. Truth Table (Note (1), (2)) |                       |        |      |    |       |      |                      |    |     |   |    |

|--------------------------------------|-----------------------|--------|------|----|-------|------|----------------------|----|-----|---|----|

| Command                              | State                 | CKEn-1 | CKEn | DM | BA0,1 | A10  | A0-9, 11-12          | CS | RAS |   | WE |

| BankActivate                         | Idle <sup>(3)</sup>   | Н      | Х    | Х  | V     | Ro   | w address            | L  | L   | Н | н  |

| BankPrecharge                        | Any                   | Н      | Х    | Х  | V     | L    | Х                    | L  | L   | Н | L  |

| Precharge All                        | Any                   | Н      | Х    | Х  | Х     | Н    | Х                    | L  | L   | Н | L  |

| Write                                | Active <sup>(3)</sup> | Н      | Х    | Х  | V     | L    | Column               | L  | Н   | L | L  |

| Write and AutoPrecharge              | Active <sup>(3)</sup> | Н      | Х    | Х  | V     | Н    | address<br>(A0 ~ A9) | L  | Н   | L | L  |

| Read                                 | Active <sup>(3)</sup> | Н      | Х    | Х  | V     | L    | Column               | L  | Н   | L | Н  |

| Read and Autoprecharge               | Active <sup>(3)</sup> | Н      | Х    | Х  | V     | Н    | address<br>(A0 ~ A9) | L  | Н   | L | Н  |

| Mode Register Set                    | Idle                  | Н      | Х    | Х  |       | OP   | code                 | L  | L   | L | L  |

| Extended MRS                         | Idle                  | Н      | Х    | Х  |       | OP ( | code                 | L  | L   | L | L  |

| No-Operation                         | Any                   | Н      | Х    | Х  | Х     | Х    | Х                    | L  | Н   | Н | Н  |

| Burst Stop                           | Active <sup>(4)</sup> | Н      | Х    | Х  | Х     | Х    | Х                    | L  | Н   | Н | L  |

| Device Deselect                      | Any                   | Н      | Х    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

| AutoRefresh                          | Idle                  | Н      | Н    | Х  | Х     | Х    | Х                    | L  | L   | L | Н  |

| SelfRefresh Entry                    | Idle                  | н      | L    | Х  | Х     | Х    | Х                    | L  | L   | L | Н  |

| SelfRefresh Exit                     | Idle                  | L      | Н    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

|                                      | (SelfRefresh)         |        |      |    |       |      |                      | L  | Н   | Н | Н  |

| Precharge Power Down Mode Entry      | Idle                  | Н      | L    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

|                                      |                       |        |      |    |       |      |                      | L  | Н   | Н | Н  |

| Precharge Power Down Mode Exit       | Any                   | L      | Н    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

|                                      | (PowerDown)           |        |      |    |       |      |                      | L  | Н   | Н | Н  |

| Active Power Down Mode Entry         | Active                | Н      | L    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

|                                      |                       |        |      |    |       |      |                      | L  | V   | V | V  |

| Active Power Down Mode Exit          | Any                   | L      | Н    | Х  | Х     | Х    | Х                    | Н  | Х   | Х | Х  |

|                                      | (PowerDown)           |        |      |    |       |      |                      | L  | Н   | Н | н  |

| Data Input Mask Disable              | Active                | Н      | Х    | L  | Х     | Х    | Х                    | Х  | Х   | Х | Х  |

| Data Input Mask Enable(5)            | Active                | Н      | Х    | Н  | Х     | Х    | Х                    | Х  | Х   | Х | Х  |

Note: 1. V=Valid data, X=Don't Care, L=Low level, H=High level

2. CKEn signal is input level when commands are provided.

CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are provided.

3. These are states of bank designated by BA signal.

Device state is 2, 4, and 8 burst operation.

LDM and UDM can be enabled respectively.

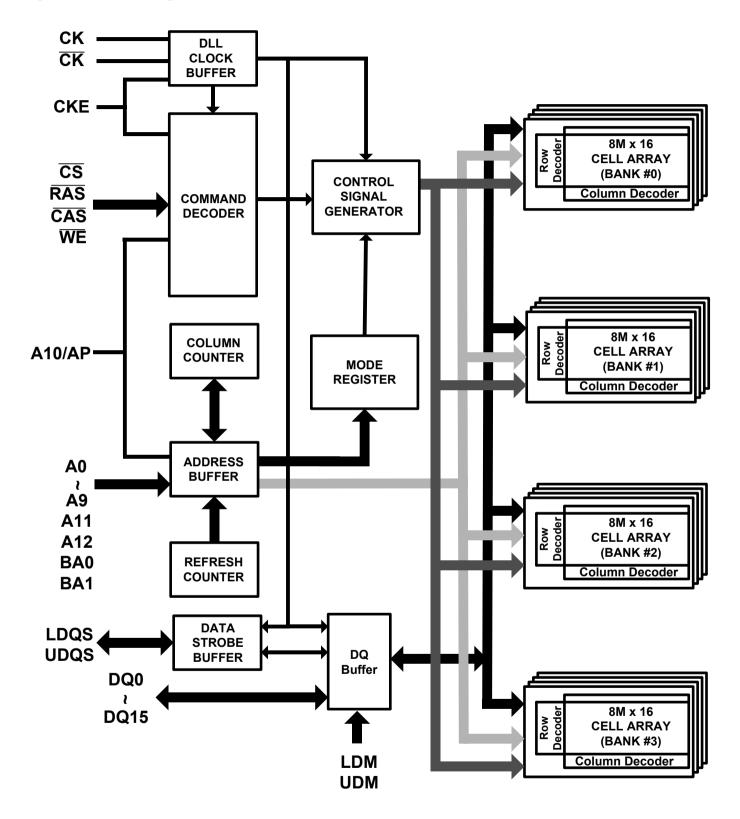

## Mode Register Set (MRS)

The Mode Register stores the data for controlling various operating modes of a DDR SDRAM. It programs CAS Latency, Burst Type, and Burst Length to make the DDR SDRAM useful for a variety of applications. The default value of the Mode Register is not defined; therefore the Mode Register must be written by the user. Values stored in the register will be retained until the register is reprogrammed. The Mode Register is written by asserting Low on  $\overline{CS}$ ,

$\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , BA1 and BA0 (the device should have all banks idle with no bursts in progress prior to writing into the mode register, and CKE should be High). The state of address pins A0~A12 and BA0, BA1 in the same cycle in which  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  are asserted Low is written into the Mode Register. A minimum of two clock cycles, tMRD, are required to complete the write operation in the Mode Register. The Mode Register is divided into various fields depending on functionality. The Burst Length uses A0~A2, Burst Type uses A3, and CAS Latency (read latency from column address) uses A4~A6. A logic 0 should be programmed to all the undefined addresses to ensure future compatibility. Reserved states should not be used to avoid unknown device operation or incompatibility with future versions. Refer to the table for specific codes for various burst lengths, burst types and CAS latencies.

## Table 4. Mode Register Bitmap

Burst Length Field (A2~A0) This field specifies the data length of column access using the A2~A0 pins and selects the Burst Length to be 2, 4, 8.

#### Table 5. Burst Length

| A2 | A1 | A0 | Burst Length |

|----|----|----|--------------|

| 0  | 0  | 0  | Reserved     |

| 0  | 0  | 1  | 2            |

| 0  | 1  | 0  | 4            |

| 0  | 1  | 1  | 8            |

| 1  | 0  | 0  | Reserved     |

| 1  | 0  | 1  | Reserved     |

| 1  | 1  | 0  | Reserved     |

| 1  | 1  | 1  | Reserved     |

#### • Addressing Mode Select Field (A3)

The Addressing Mode can be one of two modes, either Interleave Mode or Sequential Mode. Both Sequential Mode and Interleave Mode support burst length of 2, 4 and 8.

## Table 6. Addressing Mode

| A3 | Addressing Mode |  |  |  |  |

|----|-----------------|--|--|--|--|

| 0  | Sequential      |  |  |  |  |

| 1  | Interleave      |  |  |  |  |

Burst Definition, Addressing Sequence of Sequential and Interleave Mode

## Table 7. Burst Address ordering

| Burat Longth | Sta | rt Address | 6  | Sequential             | Interleave             |  |

|--------------|-----|------------|----|------------------------|------------------------|--|

| Burst Length | A2  | A1         | A0 | Sequential             | interleave             |  |

| 2            | Х   | Х          | 0  | 0, 1                   | 0, 1                   |  |

|              | Х   | Х          | 1  | 1, 0                   | 1, 0                   |  |

|              | Х   | 0          | 0  | 0, 1, 2, 3             | 0, 1, 2, 3             |  |

| 4            | Х   | 0          | 1  | 1, 2, 3, 0             | 1, 0, 3, 2             |  |

|              | Х   | 1          | 0  | 2, 3, 0, 1             | 2, 3, 0, 1             |  |

|              | Х   | 1          | 1  | 3, 0, 1, 2             | 3, 2, 1, 0             |  |

|              | 0   | 0          | 0  | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |  |

|              | 0   | 0          | 1  | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |  |

|              | 0   | 1          | 0  | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |  |

| 8            | 0   | 1          | 1  | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |  |

| 0            | 1   | 0          | 0  | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |  |

|              | 1   | 0          | 1  | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |  |

|              | 1   | 1          | 0  | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |  |

|              | 1   | 1          | 1  | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |  |

#### CAS Latency Field (A6~A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first read data. The minimum whole value of CAS Latency depends on the frequency of CK. The minimum whole value satisfying the following formula must be programmed into this field.  $t_{CAC}(min) \leq CAS$  Latency X  $t_{CK}$

#### Table 8. CAS Latency

| A6 | A5 | A4 | CAS Latency |

|----|----|----|-------------|

| 0  | 0  | 0  | Reserved    |

| 0  | 0  | 1  | Reserved    |

| 0  | 1  | 0  | 2 clocks    |

| 0  | 1  | 1  | 3 clocks    |

| 1  | 0  | 0  | Reserved    |

| 1  | 0  | 1  | Reserved    |

| 1  | 1  | 0  | 2.5 clocks  |

| 1  | 1  | 1  | Reserved    |

#### • Test Mode field (A8~A7)

These two bits are used to enter the test mode and must be programmed to "00" in normal operation.

#### Table 9. Test Mode

| A8 | A7 | Test Mode   |

|----|----|-------------|

| 0  | 0  | Normal mode |

| 1  | 0  | DLL Reset   |

• (BA0, BA1)

## Table 10. MRS/EMRS

| BA1 | BA0 | A12 ~ A0                  |

|-----|-----|---------------------------|

| RFU | 0   | MRS Cycle                 |

| RFU | 1   | Extended Functions (EMRS) |

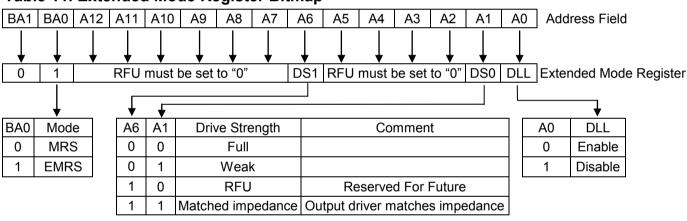

# **Extended Mode Register Set (EMRS)**

The Extended Mode Register Set stores the data for enabling or disabling DLL and selecting output driver strength. The default value of the extended mode register is not defined, therefore must be written after power up for proper operation. The Extended Mode Register is written by asserting Low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , BA1 and BA0 (the device should have all banks idle with no bursts in progress prior to writing into the mode register, and CKE should be High). The state of A0 ~ A12, BA0 and BA1 is written in the mode register in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{AS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  going low. The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register. A1 is used for setting driver strength to normal, or weak. Two clock cycles are required to complete the write operation in the extended mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. "High" on BA0 is used for EMRS. Refer to the table for specific codes.

## Table 11. Extended Mode Register Bitmap

| Table 12 | Absolute | Maximum | Rating |

|----------|----------|---------|--------|

|----------|----------|---------|--------|

|                                    |                              | -          |                               |      |

|------------------------------------|------------------------------|------------|-------------------------------|------|

| Symbol                             | Item                         |            | Values                        | Unit |

| VIN, VOUT                          | Input, Output Voltage        |            | - 0.5~ V <sub>DDQ</sub> + 0.5 | V    |

| Vdd, Vddq                          | Power Supply Voltage         |            | - 1~3.6                       | V    |

| F                                  |                              | Commercial | 0~70                          | °C   |

| T <sub>A</sub> Ambient Temperature |                              | Industrial | -40~85                        | °C   |

| Tstg                               | Storage Temperature          |            | - 55~150                      | °C   |

| TSOLDER                            | Soldering Temperature        |            | 260                           | °C   |

| PD                                 | Power Dissipation            |            | 1                             | W    |

| los                                | Short Circuit Output Current |            | 50                            | mA   |

Note1: Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

Note2: These voltages are relative to Vss

| Symbol   | Parameter                                              | Min.                    | Max.                   | Unit | Note        |

|----------|--------------------------------------------------------|-------------------------|------------------------|------|-------------|

| VDD      | Power Supply Voltage                                   | 2.3                     | 2.7                    | V    |             |

| Vddq     | Power Supply Voltage (for I/O Buffer)                  | 2.3                     | 2.7                    | V    |             |

| VREF     | Input Reference Voltage                                | 0.49*VDDQ               | 0.51* V <sub>DDQ</sub> | V    |             |

| VIH (DC) | Input High Voltage (DC)                                | V <sub>REF</sub> + 0.15 | V <sub>DDQ</sub> + 0.3 | V    |             |

| Vı∟(DC)  | Input Low Voltage (DC)                                 | -0.3                    | VREF – 0.15            | V    |             |

| Vtt      | Termination Voltage                                    | VREF - 0.04             | VREF + 0.04            | V    |             |

| VIN (DC) | Input Voltage Level, CK and $\overline{CK}$ inputs     | -0.3                    | VDDQ + 0.3             | V    |             |

| VID (DC) | Input Different Voltage, CK and $\overline{CK}$ inputs | 0.36                    | VDDQ + 0.6             | V    |             |

| lı –     | Input leakage current                                  | -2                      | 2                      | μA   |             |

| loz      | Output leakage current                                 | -5                      | 5                      | μA   |             |

| Іон      | Output High Current                                    | -16.2                   | -                      | mA   | Voн = 1.95V |

| lol      | Output Low Current                                     | 16.2                    | -                      | mA   | Vol = 0.35V |

## Table 13. Recommended D.C. Operating Conditions (T<sub>A</sub> = -40 ~ 85 °C)

**Note :** All voltages are referenced to V<sub>SS</sub>.

## Table 14. Capacitance (VDD = 2.5V, f = 1MHz, TA = 25 °C)

| Symbol | Parameter                                     | Min. | Max. | Unit |

|--------|-----------------------------------------------|------|------|------|

| CIN1   | Input Capacitance (CK, CK)                    | 2    | 3    | pF   |

| CIN2   | Input Capacitance (All other input-only pins) | 2    | 3    | pF   |

| CI/O   | DQ, DQS, DM Input/Output Capacitance          | 4    | 5    | pF   |

Note: These parameters are guaranteed by design, periodically sampled and are not 100% tested

# Table 15. D.C. Characteristics (V<sub>DD</sub> = $2.5V \pm 0.2V$ , T<sub>A</sub> = -40~85 °C)

|                                                                                                                                                                                                                                                                  |        | -5   |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|

| Parameter & Test Condition                                                                                                                                                                                                                                       | Symbol | Max. | Unit | Note |

| <b>OPERATING CURRENT:</b><br>One bank; Active-Precharge; tRC=tRC(min); tCK=tCK(min); DQ,DM<br>and DQS inputs changing once per clock cycle; Address and control<br>inputs changing once every two clock cycles.                                                  | IDD0   | 80   | mA   |      |

| <b>OPERATING CURRENT:</b><br>One bank; BL=4; reads - Refer to the following page for detailed test conditions                                                                                                                                                    | IDD1   | 90   | mA   |      |

| PRECHARGE POWER-DOWN STANDBY CURRENT:<br>All banks idle; power-down mode; tck=tck(min); CKE = LOW                                                                                                                                                                | IDD2P  | 5    | mA   |      |

| <b>PRECHARGE FLOATING STANDBY CURRENT:</b><br>CS = HIGH; all banks idle; CKE = HIGH; tcκ =tcκ(min); address and<br>other control inputs changing once per clock cycle; VIN = VREF for<br>DQ, DQS and DM                                                          | IDD2F  | 35   | mA   |      |

| PRECHARGE QUIET STANDBY CURRENT:<br>CS =HIGH; all banks idle; CKE =HIGH; tCK=tCK(min) address and<br>other control inputs stable at ≥ VIH(min) or ≤ VIL (max); VIN = VREF<br>for DQ, DQS and DM                                                                  | IDD2Q  | 35   | mA   |      |

| <b>ACTIVE POWER-DOWN STANDBY CURRENT</b> : one bank active; power-down mode; CKE=LOW; tck=tck(min)                                                                                                                                                               | IDD3P  | 20   | mA   |      |

| <b>ACTIVE STANDBY CURRENT</b> : $\overline{CS}$ =HIGH;CKE=HIGH; one bank active ; tRC=tRC(max);tCK=tCK(min);Address and control inputs changing once per clock cycle; DQ,DQS and DM inputs changing twice per clock cycle                                        | IDD3N  | 65   | mA   |      |

| <b>OPERATING CURRENT BURST READ</b> : BL=2; READS;<br>Continuous burst; one bank active; Address and control inputs<br>changing once per clock cycle; tcκ=tcκ(min); lout=0mA;50% of data<br>changing on every transfer                                           | IDD4R  | 130  | mA   |      |

| <b>OPERATING CURRENT BURST Write :</b> BL=2; WRITES;<br>Continuous Burst ;one bank active; address and control inputs<br>changing once per clock cycle; tck=tck(min); DQ,DQS and DM<br>changing twice per clock cycle; 50% of data changing on every<br>transfer | IDD4W  | 130  | mA   |      |

| AUTO REFRESH CURRENT : tRC=tRFC(min); tCK=tCK(min)                                                                                                                                                                                                               | IDD5   | 140  | mA   |      |

| SELF REFRESH CURRENT: Self Refresh Mode ; CKE≦<br>0.2V;tcк=tcк(min)                                                                                                                                                                                              | IDD6   | 6    | mA   | 1    |

| BURST OPERATING CURRENT 4 bank operation:<br>Four bank interleaving READs; BL=4;with Auto Precharge;<br>tRC=tRC(min); tCK=tCK(min); Address and control inputs change only<br>during Active, READ , or WRITE command                                             | IDD7   | 210  | mA   |      |

# Table 16. Electrical Characteristics and Recommended A.C. Operating Condition ( $V_{DD}$ = 2.5V ± 0.2V, T<sub>A</sub> = -40~85 °C)

| Symbol           | Parameter                                           |        | -5                         |      | Unit N | Not  |

|------------------|-----------------------------------------------------|--------|----------------------------|------|--------|------|

| Зушьог           | Parameter                                           |        | Min. Max.                  |      |        | NOTE |

|                  | CL                                                  | = 2    | 7.5                        | 12   | ns     |      |

| tск              | Clock cycle time CL                                 | = 2.5  | 6                          | 12   | ns     |      |

|                  | CL                                                  | = 3    | 5                          | 12   | ns     |      |

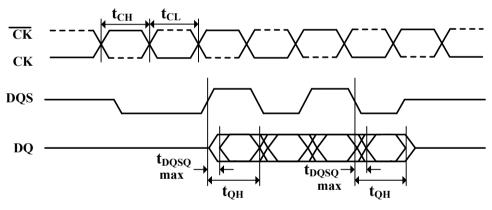

| tсн              | Clock high level width                              |        | 0.45                       | 0.55 | tск    |      |

| tc∟              | Clock low level width                               |        | 0.45                       | 0.55 | tск    |      |

| tнр              | Clock half period                                   |        | tclmin <b>or</b><br>tchmin | -    | ns     | 2    |

| tнz              | Data-out-high impedance time from CK,               | CK     | -                          | 0.7  | ns     | 3    |

| t∟z              | Data-out-low impedance time from CK, $\overline{C}$ | K      | -0.7                       | 0.7  | ns     | 3    |

| tdqscк           | DQS-out access time from CK, $\overline{CK}$        |        | -0.6                       | 0.6  | ns     |      |

| tac              | Output access time from CK, $\overline{CK}$         |        | -0.7                       | 0.7  | ns     |      |

| toasa            | DQS-DQ Skew                                         |        | -                          | 0.4  | ns     |      |

| tRPRE            | Read preamble                                       |        | 0.9                        | 1.1  | tск    |      |

| tRPST            | Read postamble                                      |        | 0.4                        | 0.6  | tск    |      |

| tooss            | CK to valid DQS-in                                  |        | 0.72                       | 1.25 | tск    |      |

| twpres           | DQS-in setup time                                   |        | 0                          | -    | ns     | 4    |

| twpre            | DQS Write preamble                                  |        | 0.25                       | -    | tск    |      |

| twpst            | DQS write postamble                                 |        | 0.4                        | 0.6  | tск    | 5    |

| tDQSH            | DQS in high level pulse width                       |        | 0.35                       | -    | tcĸ    | - U  |

| tDQSL            | DQS in low level pulse width                        |        | 0.35                       | _    | tcĸ    |      |

| tis              | Address and Control input setup time                |        | 0.7                        | -    | ns     | 6    |

| tiH              | Address and Control input setup time                |        | 0.7                        |      | ns     | 6    |

| tDS              | DQ & DM setup time to DQS                           |        | 0.4                        | -    | ns     | 0    |

| tDH              |                                                     |        | 0.4                        |      |        |      |

|                  | DQ & DM hold time to DQS                            |        |                            | -    | ns     |      |

| tqH              | DQ/DQS output hold time from DQS                    |        | thp - t <sub>QHS</sub>     | -    | ns     |      |

| tRC              | Row cycle time                                      |        | 55                         | -    | ns     |      |

| t <sub>RFC</sub> | Refresh row cycle time                              |        | 70                         | -    | ns     |      |

| tras             | Row active time                                     |        | 40                         | 70K  | ns     |      |

| tRCD             | Active to Read or Write delay                       |        | 15                         | -    | ns     |      |

| t <sub>RP</sub>  | Row precharge time                                  |        | 15                         | -    | ns     |      |

| trrd             | Row active to Row active delay                      |        | 10                         | -    | ns     |      |

| twr              | Write recovery time                                 |        | 15                         | -    | ns     |      |

| twrr             | Internal Write to Read Command Delay                |        | 2                          | -    | tск    |      |

| <b>t</b> MRD     | Mode register set cycle time                        |        | 10                         | -    | ns     |      |

| <b>t</b> REFI    | Average Periodic Refresh interval                   |        | -                          | 7.8  | μS     | 7    |

| txsrd            | Self refresh exit to read command delay             |        | 200                        | -    | tск    |      |

| <b>t</b> xsnr    | Self refresh exit to non-read command delay         |        | 75                         | -    | ns     |      |

| <b>t</b> dal     | Auto Precharge write recovery + precharge           | e time | twr+trp                    | -    | ns     |      |

| <b>t</b> DIPW    | DQ and DM input pulse width                         |        | 1.75                       | -    | ns     |      |

| tipw             | Control and Address input pulse width               |        | 2.2                        | -    | ns     |      |

| t <sub>QHS</sub> | Data Hold Skew Factor                               |        | -                          | 0.5  | ns     |      |

| t <sub>DSS</sub> | DQS falling edge to CK setup time                   |        | 0.2                        | -    | tск    |      |

| t <sub>DSH</sub> | DQS falling edge hold time from CK                  |        | 0.2                        | -    | tск    |      |

## Table 17. Recommended A.C. Operating Conditions (V<sub>DD</sub> = 2.5V ± 0.2V, T<sub>A</sub> = -40~85 °C)

| Symbol   | Parameter                                                   | Min.         | Max.         | Unit |

|----------|-------------------------------------------------------------|--------------|--------------|------|

| VIH (AC) | Input High Voltage (AC)                                     | Vref + 0.31  | -            | V    |

| VIL (AC) | Input Low Voltage (AC)                                      | -            | Vref – 0.31  | V    |

| VID (AC) | Input Different Voltage, CK and $\overline{CK}$ inputs      | 0.7          | Vddq + 0.6   | V    |

| VIX (AC) | Input Crossing Point Voltage, CK and $\overline{CK}$ inputs | 0.5*Vddq-0.2 | 0.5*VDDQ+0.2 | V    |

Note:

- 1) Enables on-chip refresh and address counters.

- 2) Min(tcL, tcH) refers to the smaller of the actual clock low time and actual clock high time as provided to the device.

- t<sub>HZ</sub> and t<sub>LZ</sub> transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving(HZ), or begins driving(LZ).

- 4) The specific requirement is that DQS be valid (High, Low, or at some point on a valid transition) on or before this CLK edge. A valid transition is defined as monotonic, and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from High-Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on t<sub>DQSS</sub>.

- 5) The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but system performance (bus turnaround) will degrade accordingly.

- 6) For command/address and CK &  $\overline{CK}$  slew rate  $\geq$  1.0V/ns.

- 7) A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.

- 8) Power-up sequence is described in Note 10

- 9) A.C. Test Conditions

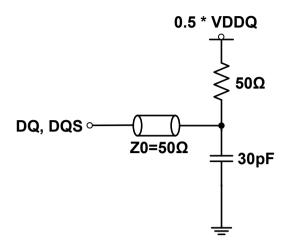

## Table 18. SSTL \_2 Interface

| Reference Level of Output Signals (VREF) | 0.5 * VDDQ                                          |

|------------------------------------------|-----------------------------------------------------|

| Output Load                              | Reference to the Test Load                          |

| Input Signal Levels                      | V <sub>REF</sub> +0.31 V / V <sub>REF</sub> -0.31 V |

| Input Signals Slew Rate                  | 1 V/ns                                              |

| Reference Level of Input Signals         | 0.5 * VDDQ                                          |

# Figure 3. SSTL\_2 A.C. Test Load

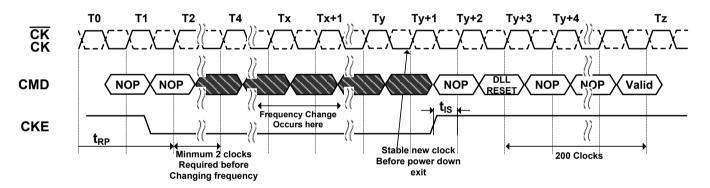

#### 10) Power up Sequence

Power up must be performed in the following sequence.

- 1) Apply power to V<sub>DD</sub> before or at the same time as V<sub>DDQ</sub>, V<sub>TT</sub> and V<sub>REF</sub> when all input signals are held "NOP" state and maintain CKE "LOW".

- 2) Start clock and maintain stable condition for minimum  $200\mu s$ .

- 3) Issue a "NOP" command and keep CKE "HIGH"

- 4) Issue a "Precharge All" command.

- 5) Issue EMRS enable DLL.

- 6) Issue MRS reset DLL. (An additional 200 clock cycles are required to lock the DLL).

- 7) Precharge all banks of the device.

- 8) Issue two or more Auto Refresh commands.

- 9) Issue MRS with A8 to low to initialize the mode register.

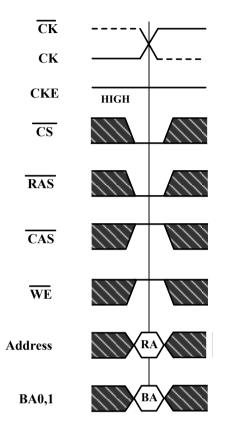

# **Timing Waveforms**

# Figure 4. Activating a Specific Row in a Specific Bank

RA=Row Address BA=Bank Address

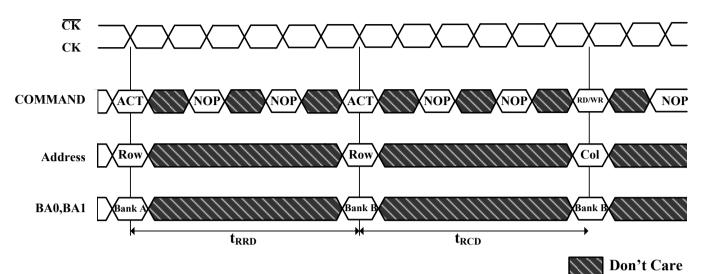

# Figure 5. tRCD and tRRD Definition

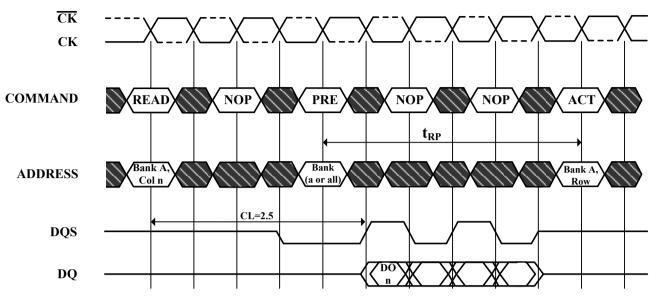

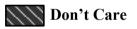

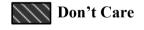

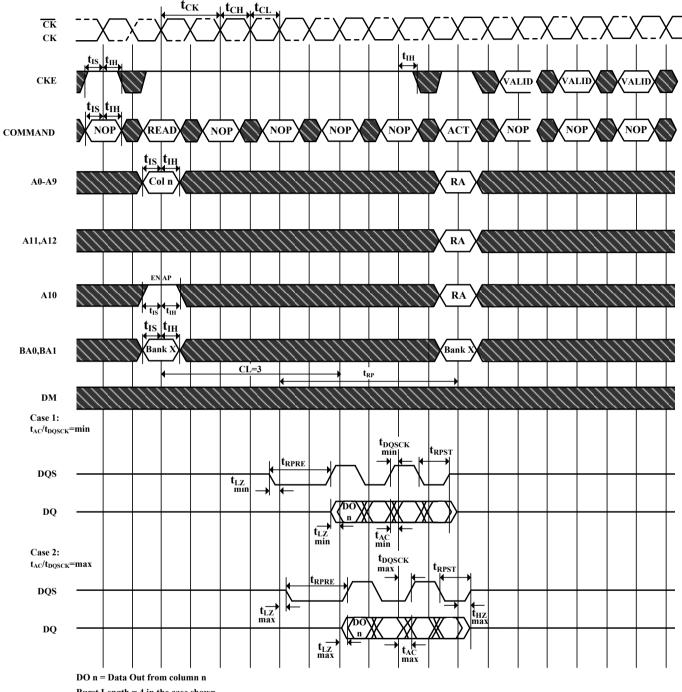

# Figure 6. READ Command

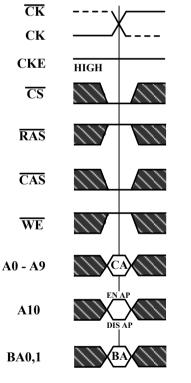

CA=Column Address BA=Bank Address EN AP=Enable Autoprecharge DIS AP=Disable Autoprecharge

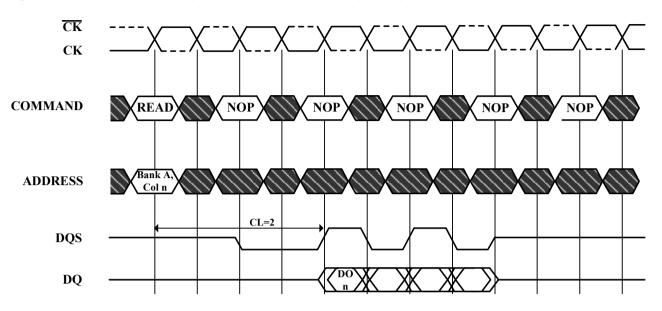

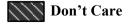

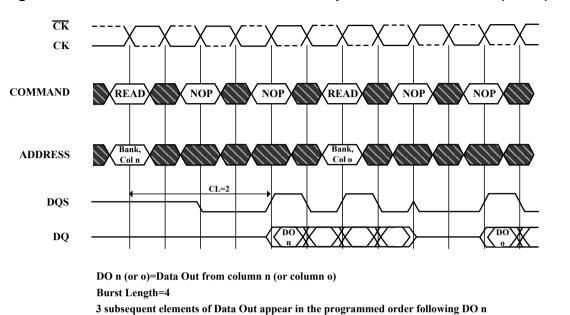

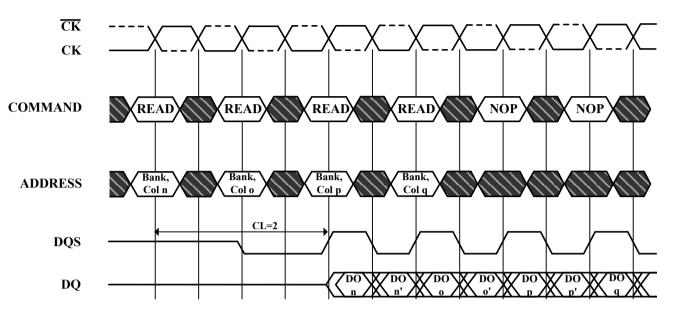

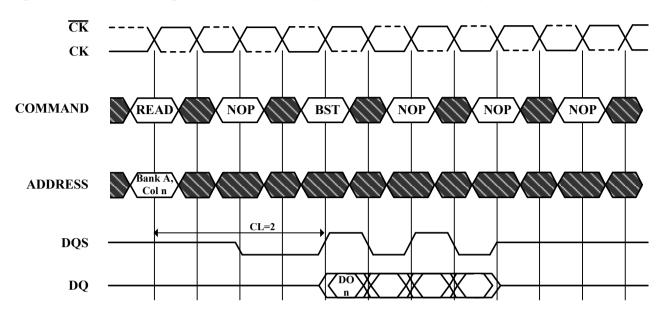

## Figure 7. Read Burst Required CAS Latencies (CL=2)

DO n=Data Out from column n Burst Length=4 3 subsequent elements of Data Out appear in the programmed order following DO n

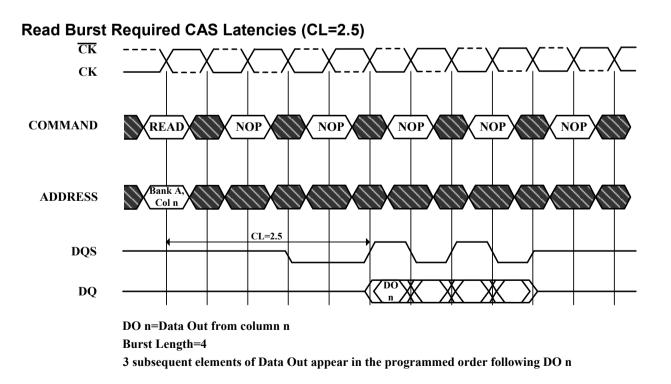

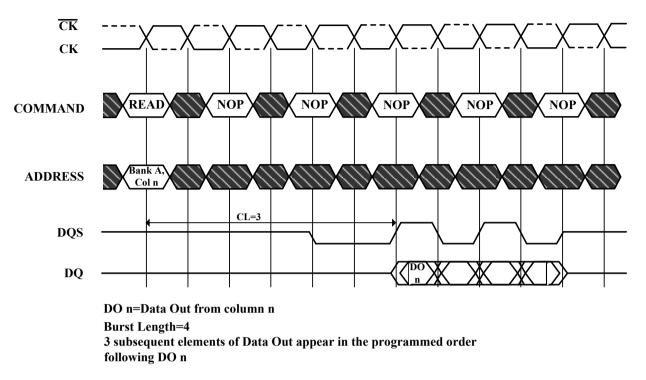

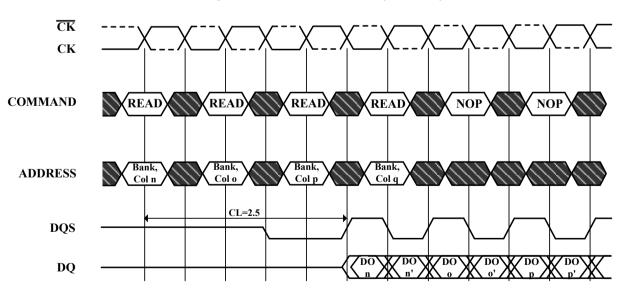

# Read Burst Required CAS Latencies (CL=3)

DO n (or o)=Data Out from column n (or column o) Burst Length=4 or 8 (if 4, the bursts are concatenated; if 8, the second burst interrupts the first) 3 subsequent elements of Data Out appear in the programmed order following DO n 3 (or 7) subsequent elements of Data Out appear in the programmed order following DO o

Read commands shown must be to the same device

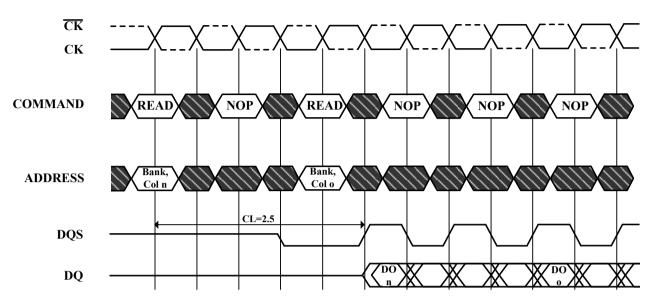

## Consecutive Read Bursts Required CAS Latencies (CL=2.5)

DO n (or o)=Data Out from column n (or column o) Burst Length=4 or 8 (if 4, the bursts are concatenated; if 8, the second burst interrupts the first) 3 subsequent elements of Data Out appear in the programmed order following DO n 3 (or 7) subsequent elements of Data Out appear in the programmed order following DO o Read commands shown must be to the same device

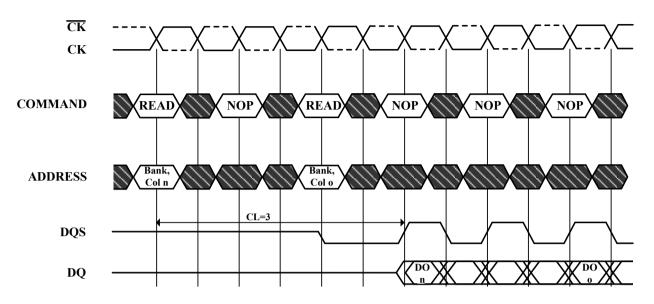

# Consecutive Read Bursts Required CAS Latencies (CL=3)

DO n (or o)=Data Out from column n (or column o)

Burst Length=4 or 8 (if 4, the bursts are concatenated; if 8, the second burst interrupts the first) 3 subsequent elements of Data Out appear in the programmed order following DO n 3 (or 7) subsequent elements of Data Out appear in the programmed order following DO o Read commands shown must be to the same device

#### Figure 9. Non-Consecutive Read Bursts Required CAS Latencies (CL=2)

Don't Care

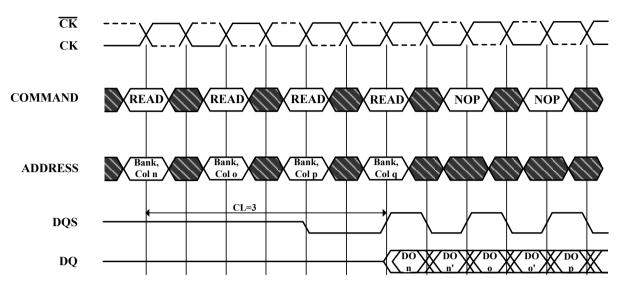

# Non-Consecutive Read Bursts Required CAS Latencies (CL=2.5)

(and following DO o)

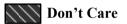

# Non-Consecutive Read Bursts Required CAS Latencies (CL=3)

(and following DO o)

Don't Care

DO n, etc. =Data Out from column n, etc. n', etc. =the next Data Out following DO n, etc. according to the programmed burst order Burst Length=2,4 or 8 in cases shown. If burst of 4 or 8, the burst is interrupted Reads are to active rows in any banks

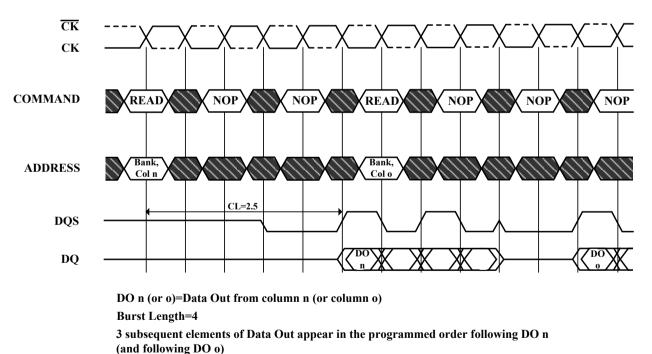

# Random Read Accesses Required CAS Latencies (CL=2.5)

DO n, etc. =Data Out from column n, etc. n', etc. =the next Data Out following DO n, etc. according to the programmed burst order Burst Length=2,4 or 8 in cases shown. If burst of 4 or 8, the burst is interrupted Reads are to active rows in any banks

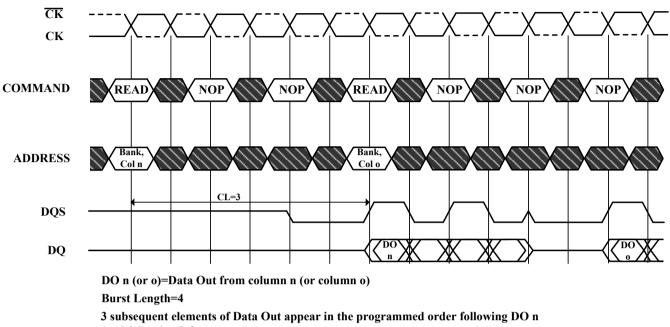

# Random Read Accesses Required CAS Latencies (CL=3)

DO n, etc. =Data Out from column n, etc.

n', etc. =the next Data Out following DO n, etc. according to the programmed burst order Burst Length=2,4 or 8 in cases shown. If burst of 4 or 8, the burst is interrupted Reads are to active rows in any banks

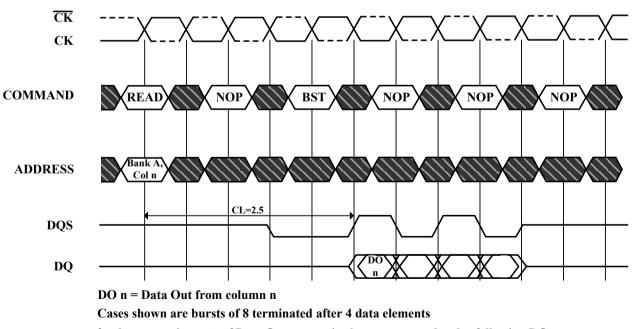

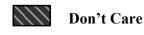

Figure 11. Terminating a Read Burst Required CAS Latencies (CL=2)

DO n = Data Out from column n Cases shown are bursts of 8 terminated after 4 data elements 3 subsequent elements of Data Out appear in the programmed order following DO n

Don't Care

# Terminating a Read Burst Required CAS Latencies (CL=2.5)

3 subsequent elements of Data Out appear in the programmed order following DO n

# Terminating a Read Burst Required CAS Latencies (CL=3)

DO n = Data Out from column n

Cases shown are bursts of 8 terminated after 4 data elements

3 subsequent elements of Data Out appear in the programmed order following DO n

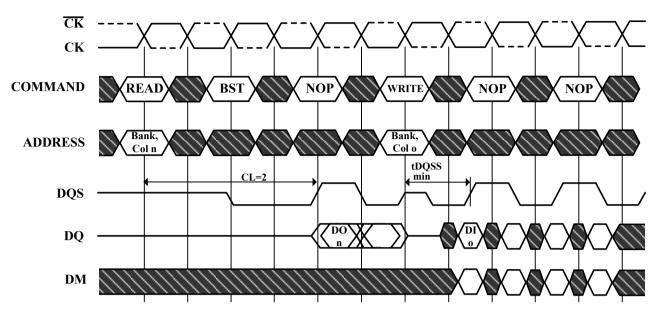

## Figure 12. Read to Write Required CAS Latencies (CL=2)

DO n (or o)= Data Out from column n (or column o)

Burst Length= 4 in the cases shown (applies for bursts of 8 as well; if burst length is 2, the BST command shown can be NOP)

1 subsequent element of Data Out appears in the programmed order following DO n Data in elements are applied following DI o in the programmed order

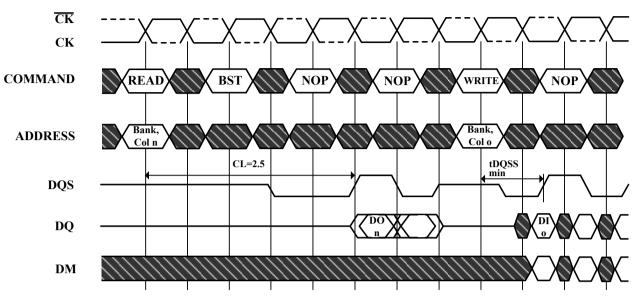

# Read to Write Required CAS Latencies (CL=2.5)

DO n (or o)= Data Out from column n (or column o)

Burst Length= 4 in the cases shown (applies for bursts of 8 as well; if burst length is 2, the BST command shown can be NOP)

1 subsequent element of Data Out appears in the programmed order following DO n Data in elements are applied following DI o in the programmed order

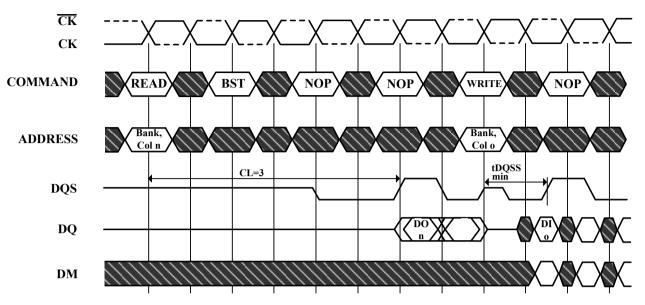

# Read to Write Required CAS Latencies (CL=3)

DO n (or o)= Data Out from column n (or column o)

Burst Length= 4 in the cases shown (applies for bursts of 8 as well; if burst length is 2, the BST command shown can be NOP)

1 subsequent element of Data Out appears in the programmed order following DO n Data in elements are applied following DI o in the programmed order

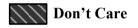

## Figure 13. Read to Precharge Required CAS Latencies (CL=2)

DO n = Data Out from column n

Cases shown are either uninterrupted bursts of 4, or interrupted bursts of 8 3 subsequent elements of Data Out appear in the programmed order following DO n

Precharge may be applied at (BL/2) tCK after the READ command Note that Precharge may not be issued before tRAS ns after the ACTIVE

command for applicable banks

The Active command may be applied if tRC has been met

## Read to Precharge Required CAS Latencies (CL=2.5)

DO n = Data Out from column n

Cases shown are either uninterrupted bursts of 4, or interrupted bursts of 8 3 subsequent elements of Data Out appear in the programmed order following DO n

Precharge may be applied at (BL/2) tCK after the READ command

Note that Precharge may not be issued before tRAS ns after the ACTIVE command for applicable banks

The Active command may be applied if tRC has been met

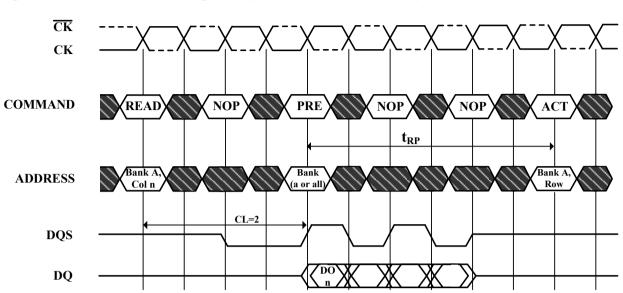

## Read to Precharge Required CAS Latencies (CL=3)

Precharge may be applied at (BL/2) tCK after the READ command Note that Precharge may not be issued before tRAS ns after the ACTIVE command for applicable banks

The Active command may be applied if tRC has been met

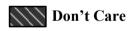

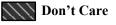

## Figure 14. Write Command

CA=Column Address BA=Bank Address EN AP=Enable Autoprecharge DIS AP=Disable Autoprecharge

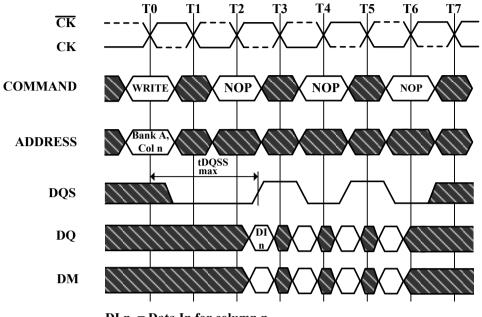

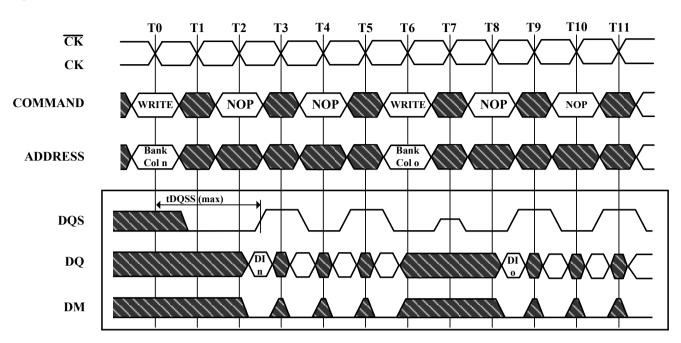

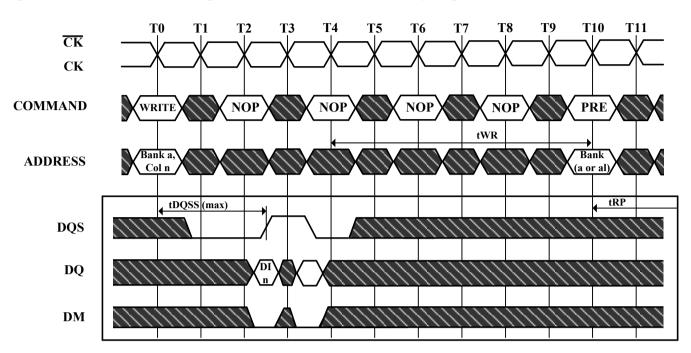

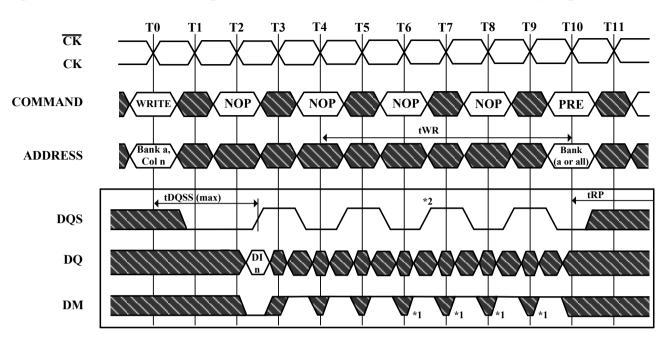

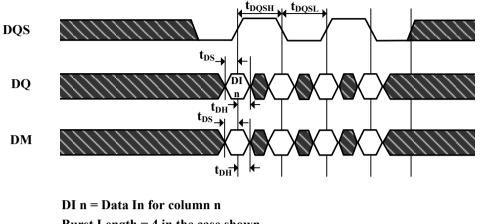

# Figure 15. Write Max DQSS

DI n = Data In for column n

**3** subsequent elements of Data In are applied in the programmed order following DI n

A non-interrupted burst of 4 is shown

A10 is LOW with the WRITE command (AUTO PRECHARGE disabled)

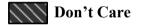

# Figure 16. Write Min DQSS

DI n = Data In for column n 3 subsequent elements of Data In are applied in the programmed order following DI n A non-interrupted burst of 4 is shown A10 is LOW with the WRITE command (AUTO PRECHARGE disabled)

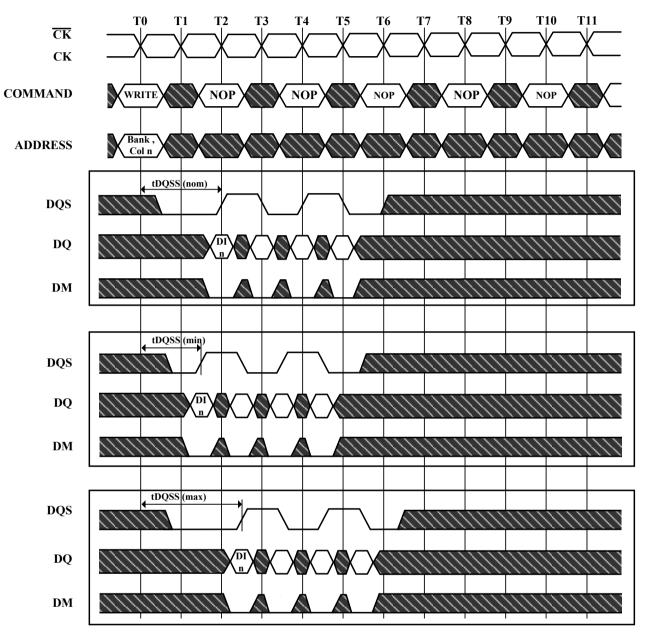

# Figure 17. Write Burst Nom, Min, and Max tDQSS

DI n = Data In for column n 3 subsequent elements of Data are applied in the programmed order following DI n A non-interrupted burst of 4 is shown A10 is LOW with the WRITE command (AUTO PRECHARGE disabled) DM=UDM & LDM

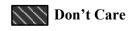

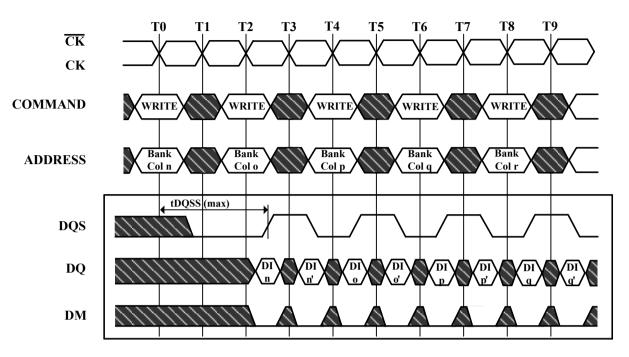

# Figure 18. Write to Write Max tDQSS

DI n, etc. = Data In for column n,etc.

3 subsequent elements of Data In are applied in the programmed order following DI n 3 subsequent elements of Data In are applied in the programmed order following DI o Non-interrupted bursts of 4 are shown DM= UDM & LDM

### Figure 19. Write to Write Max tDQSS, Non Consecutive

DI n, etc. = Data In for column n, etc.

3 subsequent elements of Data In are applied in the programmed order following DI n 3 subsequent elements of Data In are applied in the programmed order following DI o Non-interrupted bursts of 4 are shown DM= UDM & LDM

# Figure 20. Random Write Cycles Max tDQSS

DI n, etc. = Data In for column n, etc.

n', etc. = the next Data In following DI n, etc. according to the programmed burst order Programmed Burst Length 2, 4, or 8 in cases shown

If burst of 4 or 8, the burst would be truncated

Each WRITE command may be to any bank and may be to the same or different devices DM= UDM & LDM

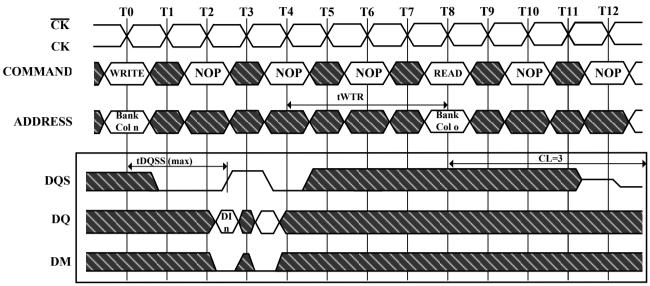

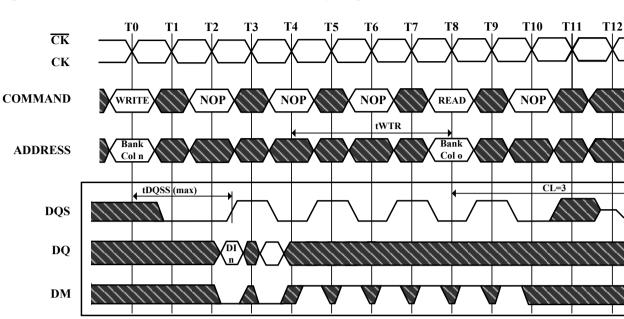

# Figure 21. Write to Read Max tDQSS Non Interrupting

DI n, etc. = Data In for column n, etc.

1 subsequent elements of Data In are applied in the programmed order following DI n A non-interrupted burst of 2 is shown

tWTR is referenced from the first positive CK edge after the last Data In Pair

A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled)

The READ and WRITE commands are to the same devices but not necessarily to the same bank DM= UDM & LDM

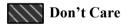

### Figure 22. Write to Read Max tDQSS Interrupting

DI n, etc. = Data In for column n, etc.

1 subsequent elements of Data In are applied in the programmed order following DI n An interrupted burst of 8 is shown, 2 data elements are written

tWTR is referenced from the first positive CK edge after the last Data In Pair

A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled)

The READ and WRITE commands are to the same devices but not necessarily to the same bank DM= UDM & LDM

### Figure 23. Write to Read Max tDQSS, ODD Number of Data, Interrupting

DI n = Data In for column n

An interrupted burst of 8 is shown, 1 data elements are written

tWTR is referenced from the first positive CK edge after the last Data In Pair (not the last desired Data In element)

A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled)

The READ and WRITE commands are to the same devices but not necessarily to the same bank DM= LDM & UDM

### Figure 24. Write to Precharge Max tDQSS, NON- Interrupting

DI n = Data In for column n

1 subsequent elements of Data In are applied in the programmed order following DI n A non-interrupted burst of 2 is shown

tWR is referenced from the first positive CK edge after the last Data In Pair A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled) DM= UDM & LDM

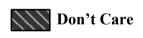

### Figure 25. Write to Precharge Max tDQSS, Interrupting

DI n = Data In for column n

An interrupted burst of 4 or 8 is shown, 2 data elements are written

tWR is referenced from the first positive CK edge after the last Data In Pair

A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled)

\*1 = can be don't care for programmed burst length of 4

\*2 = for programmed burst length of 4, DQS becomes don't care at this point

DM= UDM & LDM

### Figure 26. Write to Precharge Max tDQSS ODD Number of Data Interrupting

DI n = Data In for column n

An interrupted burst of 4 or 8 is shown, 1 data element is written

tWR is referenced from the first positive CK edge after the last Data In Pair

A10 is LOW with the WRITE command (AUTO PRECHARGE is disabled)

\*1 = can be don't care for programmed burst length of 4

\*2 = for programmed burst length of 4, DQS becomes don't care at this point

DM= UDM & LDM

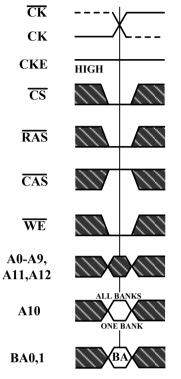

# Figure 27. Precharge Command

BA= Bank Address (if A10 is LOW, otherwise don't care)

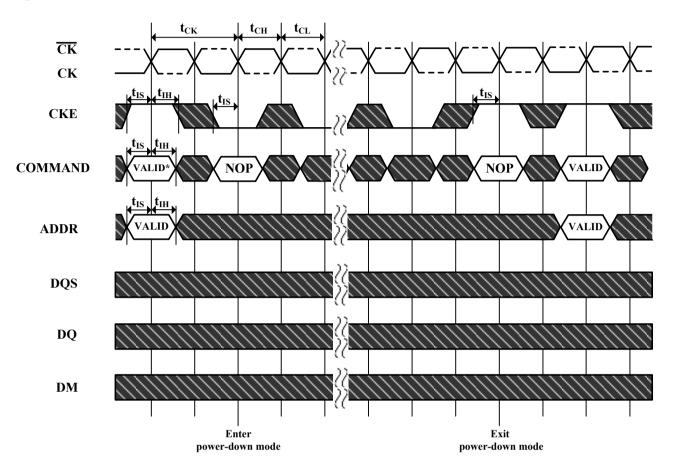

# Figure 28. Power-Down

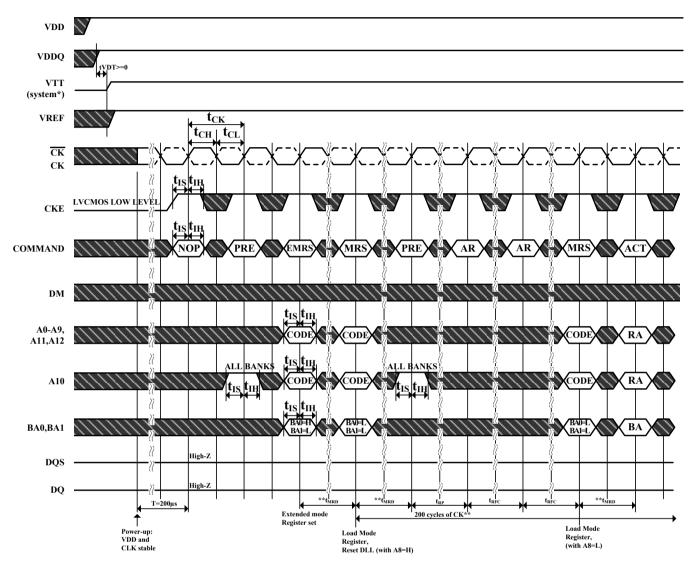

# Figure 29. Clock Frequency Change in Precharge

# Figure 30. Data input (Write) Timing

Burst Length = 4 in the case shown 3 subsequent elements of Data In are applied in the programmed order following DI n

Don't Care

Burst Length = 4 in the case shown

\*=VTT is not applied directly to the device, however tVTD must be greater than or equal to zero to avoid device latch-up. \*\* = tMRD is required before any command can be applied, and 200 cycles of CK are required before any executable command can be applied the two auto Refresh commands may be moved to follow the first MRS but precede the second PRECHARGE ALL command.

Don't Care

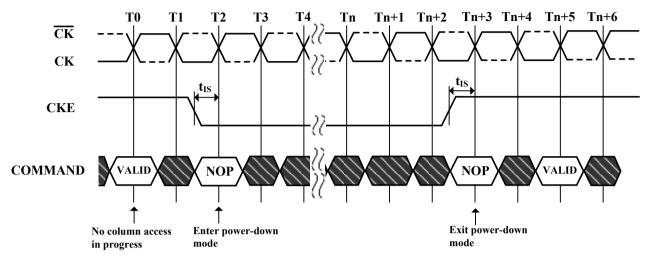

### Figure 33. Power Down Mode

No column accesses are allowed to be in progress at the time Power-Down is entered \*=If this command is a PRECHARGE ALL (or if the device is already in the idle state) then the Power-Down mode shown is Precharge Power Down. If this command is an ACTIVE (or if at least one row is already active) then the Power-Down mode shown is active Power Down.

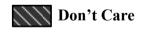

# Figure 34. Auto Refresh Mode

\*= "Don't Care", if A10 is HIGH at this point; A10 must be HIGH if more than one bank is active (i.e., must precharge all active banks) PRE = PRECHARGE, ACT = ACTIVE, RA = Row Address, BA = Bank Address, AR = AUTOREFRESH NOP commands are shown for ease of illustration; other valid commands may be possible after tRFC DM, DQ and DQS signals are all "Don't Care" /High-Z for operations shown

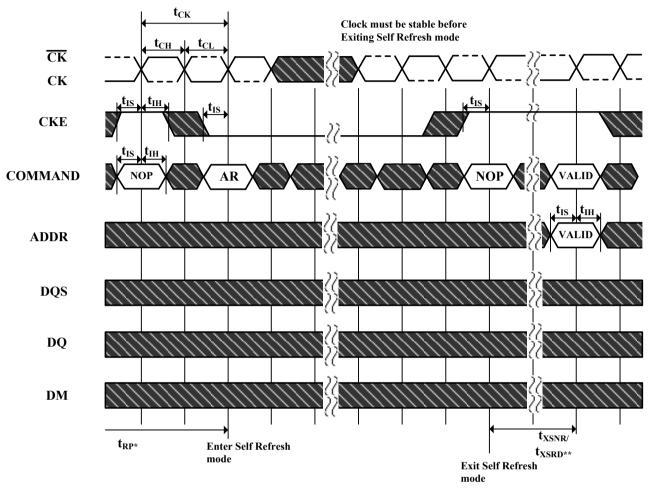

### Figure 35. Self Refresh Mode

\* = Device must be in the "All banks idle" state prior to entering Self Refresh mode \*\* = tXSNR is required before any non-READ command can be applied, and tXSRD (200 cycles of CK) is required before a READ command can be applied.

# Figure 36. Read without Auto Precharge

NOP commands are shown for ease of illustration; other commands may be valid at these times

Precharge may not be issued before tRAS ns after the ACTIVE command for applicable banks

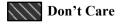

# Figure 37. Read with Auto Precharge

Burst Length = 4 in the case shown

3 subsequent elements of Data Out are provided in the programmed order following DO n

EN AP = Enable Autoprecharge

ACT = ACTIVE, RA = Row Address

NOP commands are shown for ease of illustration; other commands may be valid at these times

The READ command may not be issued until tRAP has been satisfied. If Fast Autoprecharge is supported, tRAP = tRCD, else the READ may not be issued prior to tRASmin - (BL\*tCK/2)

### Figure 38. Bank Read Access

would be limiting)

Rev. 1.0 Aug /2014

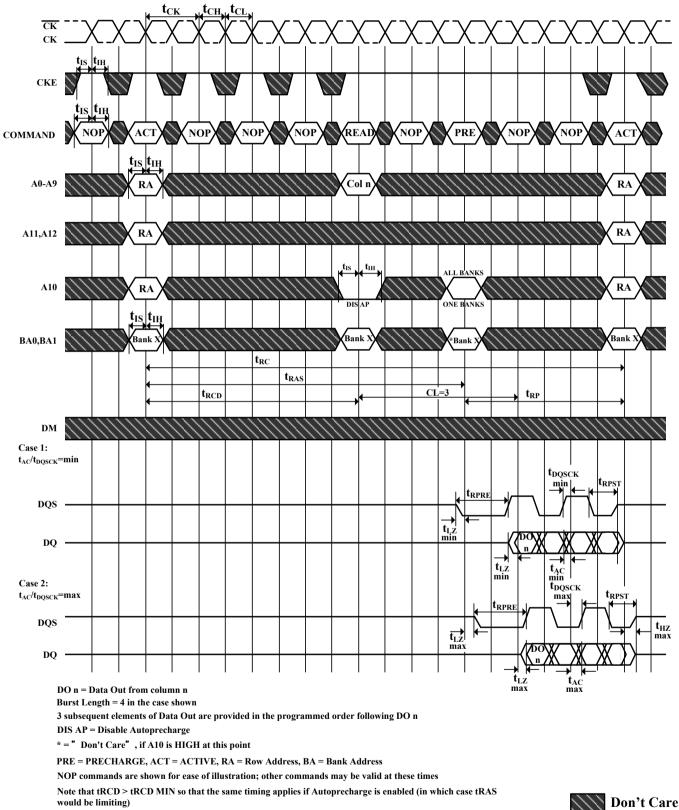

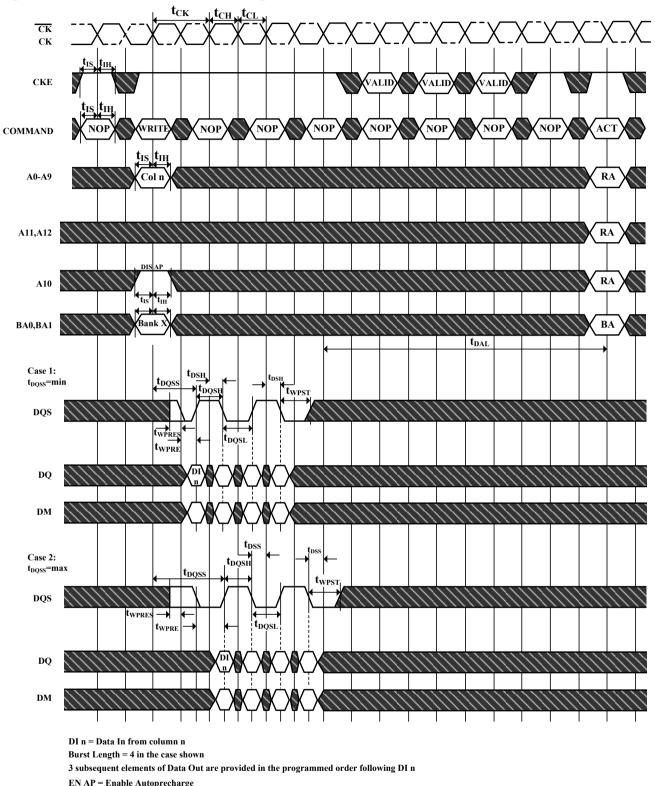

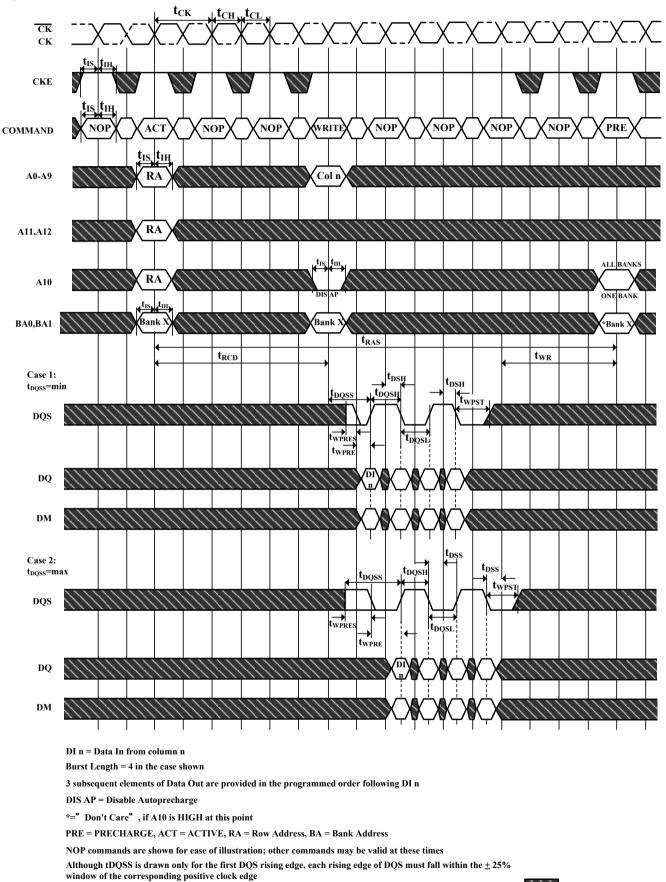

Figure 39. Write without Auto Precharge

Figure 40. Write with Auto Precharge

EN AP = Enable Autoprecharge

ACT = ACTIVE, RA = Row Address, BA = Bank Address

NOP commands are shown for ease of illustration; other commands may be valid at these times

Although tDQSS is drawn only for the first DQS rising edge, each rising edge of DQS must fall within the  $\pm\,25\%$ window of the corresponding positive clock edge

**Don't** Care

### Figure 41. Bank Write Access

Precharge may not be issued before tRAS ns after the ACTIVE command for applicable banks

### Figure 42. Write DM Operation

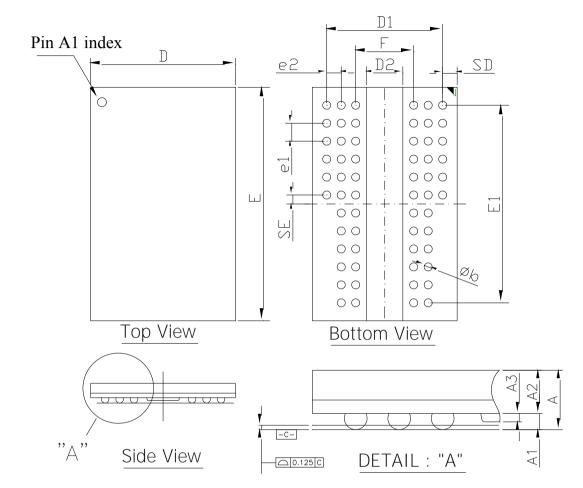

# Figure 43. BGA 60ball package Outline Drawing Information

| Symbol | Dimension (inch) |       |       | Dimension (mm) |       |       |

|--------|------------------|-------|-------|----------------|-------|-------|

|        | Min              | Nom   | Max   | Min            | Nom   | Max   |

| А      |                  |       | 0.047 |                |       | 1.20  |

| A1     | 0.012            | 0.014 | 0.016 | 0.30           | 0.35  | 0.40  |

| A2     |                  |       | 0.031 |                |       | 0.8   |

| A3     | 0.005            | 0.007 | 0.009 | 0.13           | 0.18  | 0.23  |

| D      | 0.311            | 0.315 | 0.319 | 7.90           | 8.00  | 8.10  |

| E      | 0.508            | 0.512 | 0.516 | 12.90          | 13.00 | 13.10 |

| D1     |                  | 0.252 |       |                | 6.40  |       |

| E1     |                  | 0.433 |       |                | 11.00 |       |

| e1     |                  | 0.039 |       |                | 1.00  |       |

| e2     |                  | 0.031 |       |                | 0.80  |       |

| b      | 0.016            | 0.018 | 0.020 | 0.40           | 0.45  | 0.50  |

| F      |                  | 0.126 |       |                | 3.20  |       |

| SD     |                  | 0.031 |       |                | 0.80  |       |

| SE     |                  | 0.02  |       |                | 0.50  |       |

| D2     |                  |       | 0.081 |                |       | 2.05  |

Alliance Memory Inc. reserves the rights to change the specifications and products without notice.

Alliance Memory, Inc., 551 Taylor Way, Suite #1, San Carlos, CA 94070, USA Tel: +1 650 610 6800 Fax: +1 650 620 9211

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331