# 16-Mbit (2048 K × 8/1024 K × 16/512 K × 32) nvSRAM

# Features

- 16-Mbit nonvolatile static random access memory (nvSRAM)

25-ns, 30-ns and 45-ns access times

- Internally organized as 2048 K × 8 (CY14X116L), 1024 K × 16 (CY14X116N), 512 K × 32 (CY14X116S)

- Hands-off automatic STORE on power-down with only a small capacitor

- STORE to QuantumTrap nonvolatile elements is initiated by software, device pin, or AutoStore on power-down

- RECALL to SRAM initiated by software or power-up

- High reliability

- □ Infinite read, write, and RECALL cycles

- □ 1 million STORE cycles to QuantumTrap

- Data retention: 20 years

- Sleep mode operation

- Low power consumption

- □ Active current of 75 mA at 45 ns

- $\Box$  Standby mode current of 650  $\mu$ A

- Sleep mode current of 10 μA

- Operating voltages:

CY14B116X: V<sub>CC</sub> = 2.7 V to 3.6 V

CY14E116X: V<sub>CC</sub> = 4.5 V to 5.5 V

- Industrial temperature: -40 °C to +85 °C

- Packages

- □ 44-pin thin small-outline package (TSOP II)

- □ 48-pin thin small-outline package (TSOP I)

- □ 54-pin thin small-outline package (TSOP II)

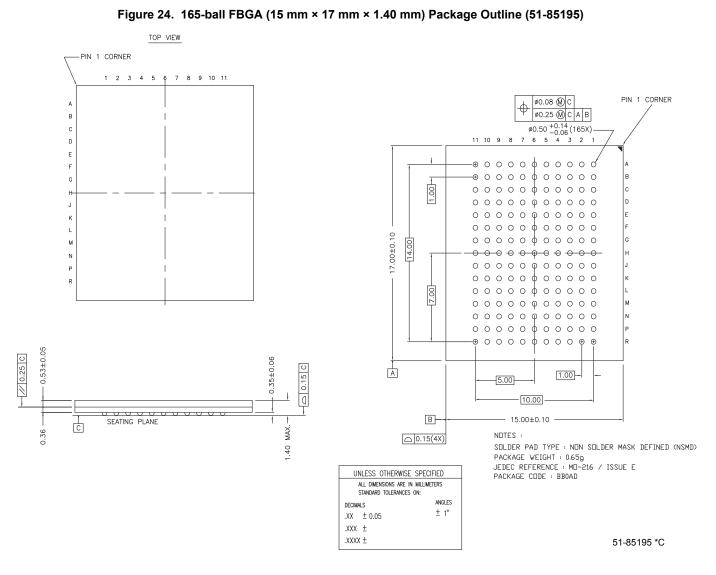

- 165-ball fine-pitch ball grid array (FBGA) package

- Restriction of hazardous substances (RoHS) compliant

- Offered speeds

- □ 44-pin TSOP II: 25 ns and 45 ns □ 48-pin TSOP I: 30 ns and 45 ns □ 54-pin TSOP II: 25 ns and 45 ns □ 165-ball FBGA: 25 ns and 45 ns

# **Functional Description**

The Cypress CY14X116L/CY14X116N/CY14X116S is a fast SRAM, with a nonvolatile element in each memory cell. The memory is organized as 2048 K bytes of 8 bits each or 1024 K words of 16 bits each or 512 K words of 32 bits each. The embedded nonvolatile elements incorporate QuantumTrap technology, producing the world's most reliable nonvolatile memory. The SRAM can be read and written an infinite number of times. The nonvolatile data residing in the nonvolatile elements do not change when data is written to the SRAM. Data transfers from the SRAM to the nonvolatile elements (the STORE operation) takes place automatically at power-down. On power-up, data is restored to the SRAM (the RECALL operation) from the nonvolatile memory. Both the STORE and RECALL operations are also available under software control.

For a complete list of related documentation, click here.

٠

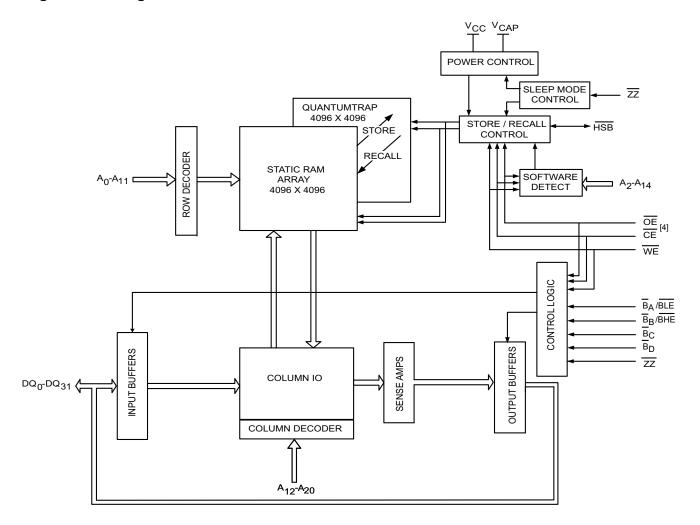

# Logic Block Diagram<sup>[1, 2, 3]</sup>

#### Notes

- 1. Address  $A_0 A_{20}$  for ×8 configuration, address  $A_0 A_{19}$  for ×16 configuration and address  $A_0 A_{18}$  for ×32 configuration.

- 2. Data DQ<sub>0</sub> DQ<sub>7</sub> for ×8 configuration, data DQ<sub>0</sub> DQ<sub>15</sub> for ×16 configuration and data DQ<sub>0</sub> DQ<sub>31</sub> for ×32 configuration.

- 3. BLE, BHE are applicable for ×16 configuration and  $\overline{B}_{A}$ ,  $\overline{B}_{B}$ ,  $\overline{B}_{C}$ ,  $\overline{B}_{D}$  are applicable for ×32 configuration only.

- 4. TSOP II package is offered in single CE. TSOP I and BGA packages are offered in dual CE options. In this datasheet, for a dual CE device, CE refers to the internal logical combination of CE<sub>1</sub> and CE<sub>2</sub> such that when CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW. For all other cases CE is HIGH.

# Contents

| Pinouts                                   | 4  |

|-------------------------------------------|----|

| Pin Definitions                           | 7  |

| Device Operation                          | 8  |

| SRAM Read                                 | 8  |

| SRAM Write                                | 8  |

| AutoStore Operation (Power-Down)          | 8  |

| Hardware STORE (HSB) Operation            | 9  |

| Hardware RECALL (Power-Up)                | 9  |

| Software STORE                            |    |

| Software RECALL                           | 9  |

| Sleep Mode                                |    |

| Preventing AutoStore                      | 12 |

| Data Protection                           | 12 |

| Maximum Ratings                           | 13 |

| Operating Range                           | 13 |

| DC Electrical Characteristics             | 13 |

| Data Retention and Endurance              |    |

| Capacitance                               | 14 |

| Thermal Resistance                        |    |

| AC Test Conditions                        |    |

| AC Switching Characteristics              |    |

| AutoStore/Power-Up RECALL Characteristics | 20 |

| Sleep Mode Characteristics                | 21 |

| Software Controlled STORE and RECALL    |    |

|-----------------------------------------|----|

| Characteristics                         | 22 |

| Hardware STORE Characteristics          | 23 |

| Truth Table For SRAM Operations         | 24 |

| For ×8 Configuration                    | 24 |

| For ×8 Configuration                    | 24 |

| For ×16 Configuration                   | 24 |

| For ×16 Configuration                   | 25 |

| For ×32 Configuration                   |    |

| Ordering Information                    | 26 |

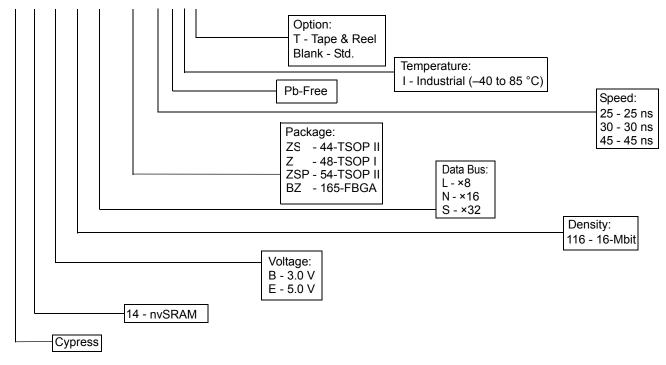

| Ordering Code Definitions               | 27 |

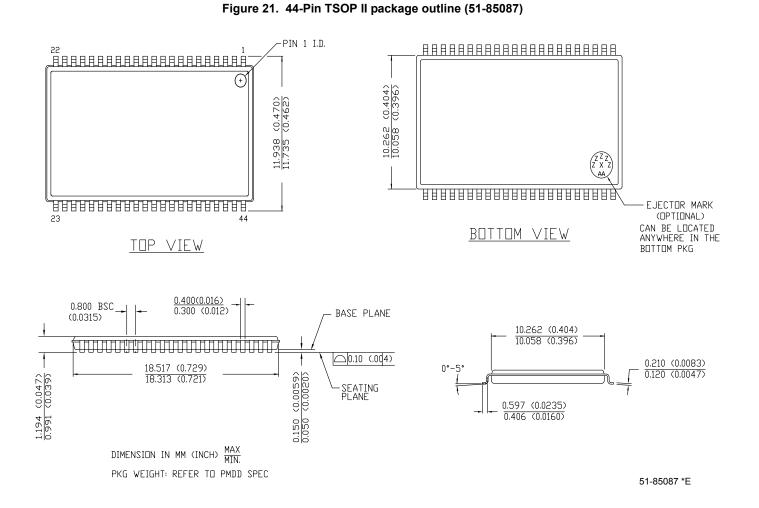

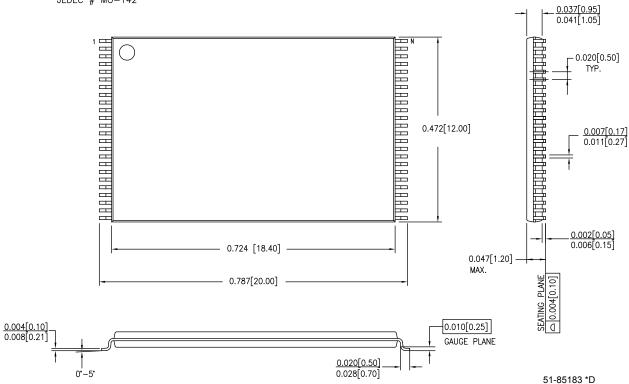

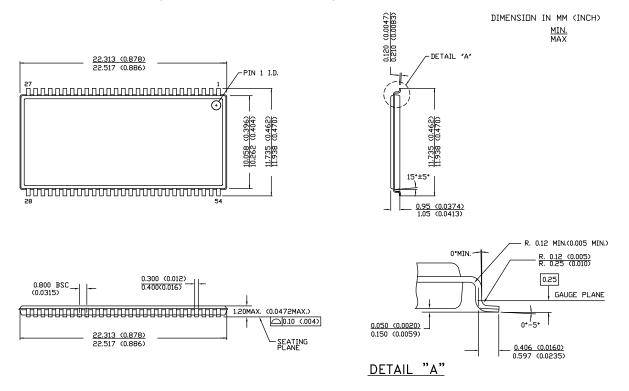

| Package Diagrams                        | 28 |

| Acronyms                                | 32 |

| Document Conventions                    | 32 |

| Units of Measure                        | 32 |

| Document History Page                   | 33 |

| Sales, Solutions, and Legal Information | 36 |

| Worldwide Sales and Design Support      | 36 |

| Products                                | 36 |

| PSoC® Solutions                         | 36 |

| Cypress Developer Community             | 36 |

| Technical Support                       | 36 |

### Pinouts

Figure 1. Pin Diagram: 44-Pin TSOP II (×8)

| NC              | 1  | 0              | 44 | HSB                       |

|-----------------|----|----------------|----|---------------------------|

| A <sub>20</sub> | 2  |                | 43 | □NC <sup>[6]</sup>        |

| A0 🗆            | 3  |                | 42 | □ A <sub>19</sub>         |

| A <sub>1</sub>  | 4  |                | 41 | A <sub>18</sub>           |

| A <sub>2</sub>  | 5  |                | 40 | A <sub>17</sub>           |

| A3 🗆            | 6  |                | 39 | A16                       |

| A <sub>4</sub>  | 7  |                | 38 | A <sub>15</sub>           |

| CE              | 8  |                | 37 |                           |

| DQ <sub>0</sub> | 9  | 44 - TSOP II   | 36 |                           |

| DQ <sub>1</sub> | 10 | (x8)           | 35 |                           |

| V <sub>CC</sub> | 11 |                | 34 | ⊒v <sub>ss</sub> °        |

| V <sub>SS</sub> | 12 | Top View       | 33 |                           |

| DQ <sub>2</sub> | 13 | (not to scale) | 32 | $\Box DQ_5$               |

| DQ <sub>3</sub> | 14 |                | 31 | □DQ₄                      |

| WE              | 15 |                | 30 |                           |

| A <sub>5</sub>  | 16 |                | 29 | $\Box A_{14}$             |

| A <sub>6</sub>  | 17 |                | 28 | A <sub>13</sub>           |

| A7              | 18 |                | 27 | $\square A_{12}$          |

| A <sub>8</sub>  | 19 |                | 26 | $\Box A_{11}$             |

| A9 🗌            | 20 |                | 25 |                           |

|                 | 21 |                | 24 | ∟ A <sub>10</sub><br>□ NC |

|                 | 22 |                | 23 |                           |

|                 |    |                | 20 |                           |

| Figure 2. | Pin Diagram: | 54-Pin | TSOP | II (×16) | ) |

|-----------|--------------|--------|------|----------|---|

|-----------|--------------|--------|------|----------|---|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | 54 - 7<br>2 (x<br>3<br>4 Top<br>5 (not t | TSOP II<br><16)<br>o View<br>o scale) | 54<br>53<br>52<br>51<br>50<br>49<br>48<br>47<br>46<br>45<br>44<br>43<br>42<br>41<br>39<br>38 | HSB           A18           A17           A16           BEE           DQ14           DQ14           VScc110           DQ9 |

|--------------------------------------------------------|------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| DQ0 🗖 9                                                |                                          |                                       | 46                                                                                           | DQ <sub>15</sub>                                                                                                          |

|                                                        |                                          |                                       | 45                                                                                           |                                                                                                                           |

| $DQ_2 \square 1$                                       | 1 <b>54 -</b>                            | isop II                               | 44                                                                                           |                                                                                                                           |

| $DQ_3 \square 12$                                      | 2 <b>()</b>                              | (16)                                  | 43                                                                                           | DQ <sub>12</sub>                                                                                                          |

| V <sub>CC</sub> 1                                      | 3                                        |                                       |                                                                                              | V <sub>SS</sub>                                                                                                           |

|                                                        | 4 Top                                    | o View                                | 41                                                                                           | V <sub>CC</sub>                                                                                                           |

|                                                        | <sup>5</sup> (not t                      | o scale)                              | 40                                                                                           | DQ <sub>11</sub>                                                                                                          |

| DQ <sub>5</sub> 1                                      | 6 `                                      | ,                                     | 39                                                                                           | DQ <sub>10</sub>                                                                                                          |

| DQ <sub>6</sub> 🗖 1                                    | 7                                        |                                       |                                                                                              | DQ <sub>9</sub>                                                                                                           |

| DQ <sub>7</sub> 🗌 1                                    | 8                                        |                                       | 37                                                                                           | DQ <sub>8</sub>                                                                                                           |

| WE 1                                                   | 9                                        |                                       | 36                                                                                           | V <sub>CAP</sub>                                                                                                          |

| A <sub>5</sub> 🗌 2                                     | 0                                        |                                       | 35                                                                                           | A <sub>14</sub>                                                                                                           |

| A <sub>6</sub> 🗖 2                                     | 1                                        |                                       | 34                                                                                           | A <sub>13</sub>                                                                                                           |

| A <sub>7</sub> 🗖 2                                     |                                          |                                       | 33                                                                                           | A <sub>12</sub>                                                                                                           |

| A <sub>8</sub> 🗌 2                                     |                                          |                                       | 32                                                                                           | A <sub>11</sub>                                                                                                           |

| A <sub>9</sub> 2                                       |                                          |                                       | 31                                                                                           | A <sub>10</sub>                                                                                                           |

|                                                        |                                          |                                       | 30                                                                                           |                                                                                                                           |

|                                                        |                                          |                                       | 29                                                                                           |                                                                                                                           |

| NC 2                                                   | 1                                        |                                       | 28                                                                                           | NC                                                                                                                        |

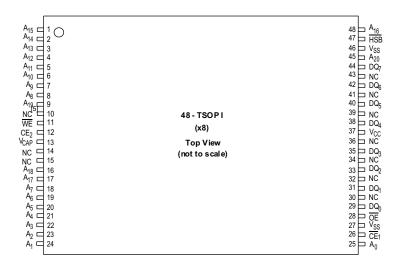

Figure 3. Pin Diagram: 48-Pin TSOP I (×8)

### Pinouts (continued)

### Figure 4. Pin Diagram: 48-Pin TSOP I (×16)

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 38 DQ4<br>37 Vcc<br>36 DQ11 |

|-------------------------------------------------------|-----------------------------|

|-------------------------------------------------------|-----------------------------|

### Figure 5. Pin Diagram: 165-Ball FBGA (×16)

|   | 1   | 2                | 3               | 4               | 5               | 6               | 7               | 8                 | 9               | 10               | 11               |

|---|-----|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|------------------|------------------|

| Α | NC  | A <sub>6</sub>   | A <sub>8</sub>  | WE              | BLE             | CE <sub>1</sub> | NC              | OE                | A <sub>5</sub>  | A <sub>3</sub>   | NC               |

| В | NC  | DQ <sub>0</sub>  | DQ <sub>1</sub> | A <sub>4</sub>  | BHE             | CE <sub>2</sub> | NC              | A <sub>2</sub>    | NC              | NC               | NC               |

| С | ZZ  | NC               | NC              | V <sub>SS</sub> | A <sub>0</sub>  | A <sub>7</sub>  | A <sub>1</sub>  | V <sub>SS</sub>   | NC              | DQ <sub>15</sub> | DQ <sub>14</sub> |

| D | NC  | DQ <sub>2</sub>  | NC              | V <sub>SS</sub>   | NC              | NC               | NC               |

| E | NC  | V <sub>CAP</sub> | NC              | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>CC</sub>   | NC              | DQ <sub>13</sub> | NC               |

| F | NC  | $DQ_3$           | NC              | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>12</sub> |

| G | HSB | NC               | NC              | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | NC               |

| н | NC  | NC               | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | V <sub>CC</sub> | NC               | NC               |

| J | NC  | NC               | NC              | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | DQ <sub>8</sub>  | NC               |

| К | NC  | NC               | $DQ_4$          | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | NC               |

| L | NC  | $DQ_5$           | NC              | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>9</sub>  |

| М | NC  | NC               | NC              | V <sub>SS</sub>   | NC              | DQ <sub>10</sub> | NC               |

| Ν | NC  | DQ <sub>6</sub>  | DQ <sub>7</sub> | V <sub>SS</sub> | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub>  | V <sub>SS</sub>   | NC              | NC               | NC               |

| Р | NC  | NC               | NC              | A <sub>13</sub> | A <sub>19</sub> | NC              | A <sub>18</sub> | A <sub>12</sub>   | NC              | DQ <sub>11</sub> | NC               |

| R | NC  | NC               | A <sub>15</sub> | NC              | A <sub>17</sub> | NC              | A <sub>16</sub> | NC <sup>[6]</sup> | A <sub>14</sub> | NC               | NC               |

6. Address expansion for 32-Mbit. NC pin not connected to die.

## Pinouts (continued)

|   |     |                  | F                | igure 6. Pi     | in Diagram      | n: 165-Ball     | FBGA (×3        | 2)                |                 |                  |                  |

|---|-----|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|------------------|------------------|

|   | 1   | 2                | 3                | 4               | 5               | 6               | 7               | 8                 | 9               | 10               | 11               |

| Α | NC  | A <sub>6</sub>   | A <sub>8</sub>   | WE              | B <sub>A</sub>  | CE <sub>1</sub> | B <sub>C</sub>  | OE                | A <sub>5</sub>  | A <sub>3</sub>   | NC               |

| В | NC  | DQ <sub>0</sub>  | DQ <sub>1</sub>  | A <sub>4</sub>  | B <sub>B</sub>  | CE <sub>2</sub> | B <sub>D</sub>  | A <sub>2</sub>    | NC              | NC               | DQ <sub>31</sub> |

| С | ZZ  | NC               | $DQ_4$           | V <sub>SS</sub> | A <sub>0</sub>  | A <sub>7</sub>  | A <sub>1</sub>  | V <sub>SS</sub>   | NC              | DQ <sub>27</sub> | DQ <sub>26</sub> |

| D | NC  | $DQ_2$           | $DQ_5$           | $V_{SS}$        | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>   | NC              | NC               | DQ <sub>30</sub> |

| Е | NC  | V <sub>CAP</sub> | $DQ_6$           | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>CC</sub>   | NC              | DQ <sub>25</sub> | DQ <sub>29</sub> |

| F | NC  | $DQ_3$           | DQ <sub>7</sub>  | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>24</sub> |

| G | HSB | NC               | DQ <sub>12</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>28</sub> |

| Н | NC  | NC               | V <sub>CC</sub>  | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | V <sub>CC</sub> | NC               | NC               |

| J | NC  | NC               | DQ <sub>13</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | DQ <sub>20</sub> | DQ <sub>19</sub> |

| К | NC  | NC               | DQ <sub>8</sub>  | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>18</sub> |

| L | NC  | DQ <sub>9</sub>  | DQ <sub>14</sub> | V <sub>CC</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>CC</sub>   | NC              | NC               | DQ <sub>21</sub> |

| М | NC  | NC               | DQ <sub>15</sub> | V <sub>SS</sub>   | NC              | DQ <sub>22</sub> | DQ <sub>17</sub> |

| Ν | NC  | DQ <sub>10</sub> | DQ <sub>11</sub> | $V_{SS}$        | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub>  | V <sub>SS</sub>   | NC              | NC               | DQ <sub>16</sub> |

| Р | NC  | NC               | NC               | A <sub>13</sub> | NC              | NC              | A <sub>18</sub> | A <sub>12</sub>   | NC              | DQ <sub>23</sub> | NC               |

| R | NC  | NC               | A <sub>15</sub>  | NC              | A <sub>17</sub> | NC              | A <sub>16</sub> | NC <sup>[7]</sup> | A <sub>14</sub> | NC               | NC               |

<sup>7.</sup> Address expansion for 32-Mbit. NC pin not connected to die.

# **Pin Definitions**

| Pin Name                                | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A_0 - A_{20}$                          |              | Address inputs. Used to select one of the 2,097,152 bytes of the nvSRAM for the ×8 configuration.                                                                                                                                                                                                                                                                                                                                                            |

| $A_0 - A_{19}$                          | Input        | Address inputs. Used to select one of the 1,048,576 words of the nvSRAM for the ×16 configuration.                                                                                                                                                                                                                                                                                                                                                           |

| $A_0 - A_{18}$                          |              | Address inputs. Used to select one of the 524,288 words of the nvSRAM for the ×32 configuration.                                                                                                                                                                                                                                                                                                                                                             |

| $DQ_0 - DQ_7$                           |              | Bidirectional data I/O lines for the ×8 configuration. Used as input or output lines depending on operation.                                                                                                                                                                                                                                                                                                                                                 |

| $DQ_0 - DQ_{15}$                        | Input/Output | Bidirectional data I/O lines for the ×16 configuration. Used as input or output lines depending on operation.                                                                                                                                                                                                                                                                                                                                                |

| $DQ_0 - DQ_{31}$                        |              | Bidirectional data I/O lines for ×32 configuration. Used as input or output lines depending on operation.                                                                                                                                                                                                                                                                                                                                                    |

| WE                                      | Input        | Write Enable input, Active LOW. When selected LOW, data on the I/O pins is written to the specific address location.                                                                                                                                                                                                                                                                                                                                         |

| CE                                      | land         | Chip Enable input in TSOP II package, Active LOW. When LOW, selects the chip. When HIGH, deselects the chip.                                                                                                                                                                                                                                                                                                                                                 |

| $\overline{CE}_{1,}CE_{2}$              | Input        | <b>Chip Enable input in FBGA package.</b> The device is selected and a memory access begins on the falling edge of $\overline{CE}_1$ (while $\overline{CE}_2$ is HIGH) or the rising edge of $\overline{CE}_2$ (while $\overline{CE}_1$ is LOW).                                                                                                                                                                                                             |

| ŌĒ                                      | Input        | <b>Output Enable, Active LOW.</b> The Active LOW $\overline{OE}$ input enables the data output buffers during read cycles. Deasserting $\overline{OE}$ HIGH causes the I/O pins to tristate.                                                                                                                                                                                                                                                                 |

| $\overline{BLE}/\overline{B}_{A}^{[8]}$ | Input        | Byte Enable, Active LOW. When selected LOW, enables DQ7–DQ0.                                                                                                                                                                                                                                                                                                                                                                                                 |

| BHE/B <sub>B</sub> <sup>[8]</sup>       | Input        | Byte Enable, Active LOW. When selected LOW, enables DQ <sub>15</sub> –DQ <sub>8</sub> .                                                                                                                                                                                                                                                                                                                                                                      |

| B <sub>C</sub> <sup>[8]</sup>           | Input        | Byte Enable, Active LOW. When selected LOW, enables DQ <sub>23</sub> –DQ <sub>16</sub> .                                                                                                                                                                                                                                                                                                                                                                     |

| B <sub>D</sub> <sup>[8]</sup>           | Input        | Byte Enable, Active LOW. When selected LOW, enables DQ <sub>31</sub> –DQ <sub>24</sub> .                                                                                                                                                                                                                                                                                                                                                                     |

| ZZ <sup>[9]</sup>                       | Input        | <b>Sleep Mode Enable.</b> When the $\overline{ZZ}$ pin is pulled LOW, the device enters a low-power Sleep mode and consumes the lowest power. Since this input is logically AND'ed with $\overline{CE}$ , $\overline{ZZ}$ must be HIGH for normal operation.                                                                                                                                                                                                 |

| V <sub>CC</sub>                         | Power Supply | Power supply inputs to the device.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub>                         | Power Supply | Ground for the device. Must be connected to ground of the system.                                                                                                                                                                                                                                                                                                                                                                                            |

| HSB                                     | Input/Output | <b>Hardware STORE Busy (HSB)</b> . When LOW, this output indicates that a Hardware STORE is in progress. When pulled LOW external to the <u>chip</u> it initiates a nonvolatile STORE operation. After each Hardware and Software STORE operation, HSB is driven HIGH for a short time (t <sub>HHHD</sub> ) with standard output high current and then a weak internal pull-up resistor keeps this pin HIGH (external pull-up resistor connection optional). |

| V <sub>CAP</sub>                        | Power Supply | AutoStore capacitor. Supplies power to the nvSRAM during power loss to store data from SRAM to nonvolatile elements.                                                                                                                                                                                                                                                                                                                                         |

| NC                                      | NC           | No Connect. Die pads are not connected to the package pin.                                                                                                                                                                                                                                                                                                                                                                                                   |

Notes

8. BLE, BHE are applicable for ×16 configuration and B<sub>A</sub>, B<sub>B</sub>, B<sub>C</sub>, B<sub>D</sub> are applicable for ×32 configuration only.

9. Sleep mode feature is offered in 165-ball FBGA package only.

# **Device Operation**

The CY14X116L/CY14X116N/CY14X116S nvSRAM is made up of two functional components paired in the same physical cell. These are an SRAM memory cell and a nonvolatile QuantumTrap cell. The SRAM memory cell operates as a standard fast static RAM. Data in the SRAM is transferred to the nonvolatile cell (the STORE operation) automatically at power-down, or from the nonvolatile cell to the SRAM (the RECALL operation) on power-up. Both the STORE and RECALL operations are also available under software control. Using this unique architecture, all cells are stored and recalled in parallel. During the STORE and RECALL operations, SRAM read and write operations are inhibited. The CY14X116L/CY14X116N/ CY14X116S supports infinite reads and writes to the SRAM. In addition, it provides infinite RECALL operations from the nonvolatile cells and up to 1 million STORE operations. See the Truth Table For SRAM Operations on page 24 for a complete description of read and write modes.

### SRAM Read

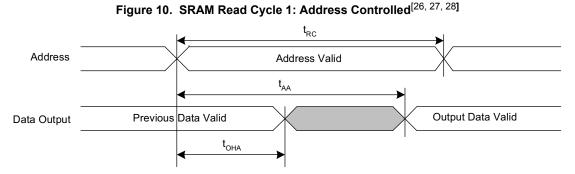

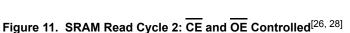

The CY14X116L/CY14X116N/CY14X116S performs a read cycle whenever  $\overline{CE}$  and  $\overline{OE}$  are LOW, and  $\overline{WE}$ ,  $\overline{ZZ}$ , and  $\overline{HSB}$  are HIGH. The address specified on pins  $A_0\text{--}A_{20}$  or  $A_0\text{--}A_{19}$  or A0-A18 determines which of the 2,097,152 data bytes or 1,048,576 words of 16 bits or 524,288 words of 32 bits each are accessed. Byte enables (BLE, BHE) determine which bytes are enabled to the output, in the case of 16-bit words and byte enables  $(\overline{B}_A, \overline{B}_B, \overline{B}_C, \overline{B}_D)$  determine which bytes are enabled to the output, in the case of 32-bit words. When the read is initiated by an address transition, the outputs are valid after a delay of tAA (read cycle 1). If the read is initiated by  $\overline{CE}$  or  $\overline{OE}$ , the outputs are valid at  $t_{ACE}$  or at  $t_{DOE}$ , whichever is later (read cycle 2). The data output repeatedly responds to address changes within the tAA access time without the need for transitions on any control input pins. This remains valid until another address change or until CE or OE is brought HIGH, or WE or HSB is brought LOW.

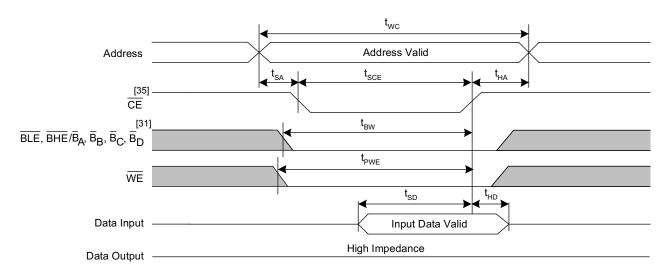

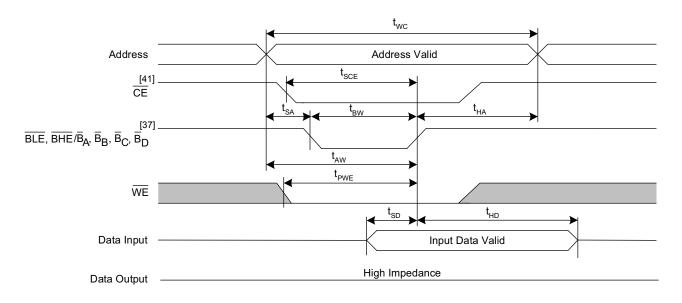

### **SRAM Write**

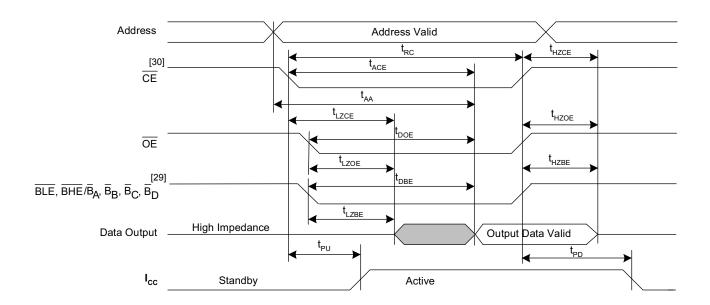

A write cycle is performed when  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{HSB}$  is HIGH. The address inputs must be stable before entering the write cycle and must remain stable until  $\overline{CE}$  or  $\overline{WE}$  goes HIGH at the end of the cycle. The data on the common I/O pins  $DQ_0-DQ_{31}$  is written into the memory if it is valid  $t_{SD}$  before the end of a  $\overline{WE}$ -controlled write or before the end of a  $\overline{CE}$ -controlled write or before the end of a  $\overline{CE}$ -controlled write. The Byte Enable inputs ( $\overline{BLE}$ ,  $\overline{BHE}$  determine which bytes are written, in the case of 16-bit words and Byte Enable inputs ( $\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$ ) determine which bytes are written, in the case of 32-bit words. Keep  $\overline{OE}$  HIGH during the entire write cycle to avoid data bus contention on the common I/O lines. If  $\overline{OE}$  is left LOW, the internal circuitry turns off the output buffers  $t_{HZWE}$  after  $\overline{WE}$  goes LOW.

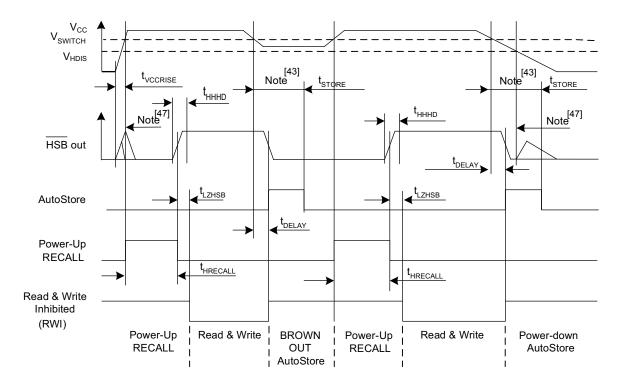

### AutoStore Operation (Power-Down)

The CY14X116L/CY14X116N/CY14X116S stores data to the nonvolatile QuantumTrap cells using one of the three storage operations. These three operations are: Hardware STORE, activated by the HSB; Software STORE, activated by an address sequence; AutoStore, on device power-down. The AutoStore operation is a unique feature of nvSRAM and is enabled by default on the CY14X116L/CY14X116N/CY14X116S.

During normal operation, the device draws current from V<sub>CC</sub> to charge a capacitor connected to the V<sub>CAP</sub> pin. This stored charge is used by the chip to perform a STORE operation during power-down. If the voltage on the V<sub>CC</sub> pin drops below V<sub>SWITCH</sub>, the part automatically disconnects the V<sub>CAP</sub> pin from V<sub>CC</sub> and a STORE operation is initiated with power provided by the V<sub>CAP</sub> capacitor.

**Note** If the capacitor is not connected to the  $V_{CAP}$  pin, AutoStore must be disabled using the soft sequence specified in the section Preventing AutoStore on page 12. If AutoStore is enabled without a capacitor on the  $V_{CAP}$  pin, the device attempts an AutoStore operation without sufficient charge to complete the STORE. This corrupts the data stored in the nvSRAM.

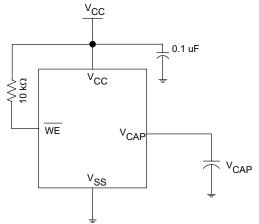

#### Figure 7. AutoStore Mode

Figure 7 shows the proper connection of the storage capacitor (V<sub>CAP</sub>) for the automatic STORE operation. Refer to DC Electrical Characteristics on page 13 for the size of the V<sub>CAP</sub>. The voltage on the V<sub>CAP</sub> pin is driven to V<sub>VCAP</sub> by a regulator on the chip. A pull-up resistor should be placed on WE to hold it inactive during power-up. This pull-up resistor is only effective if the WE signal is in tristate during power-up. When the nvSRAM comes out of power-up-RECALL, the host microcontroller must be active or the WE held inactive until the host microcontroller comes out of reset.

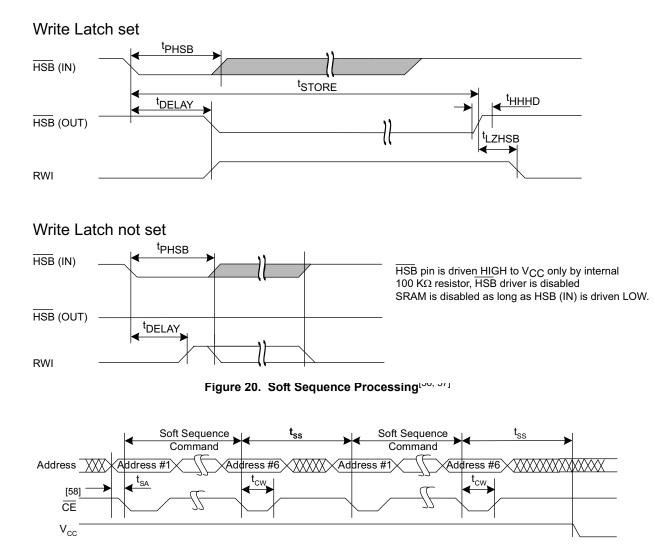

To reduce unnecessary nonvolatile STOREs, AutoStore and Hardware STORE operations are ignored unless at least one write operation has taken place (which sets a write latch) since the most recent STORE or RECALL cycle. Software initiated STORE cycles are performed regardless of whether a write operation has taken place.

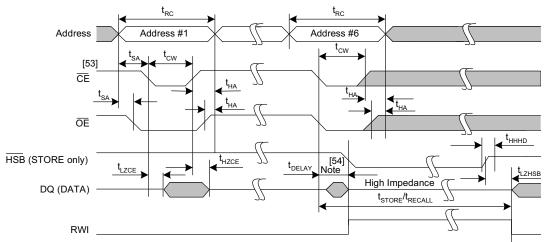

### Hardware STORE (HSB) Operation

The CY14X116L/CY14X116N/CY14X116S provides the  $\overline{\text{HSB}}$  pin to control and acknowledge the STORE operations. The  $\overline{\text{HSB}}$  pin is used to request a Hardware STORE cycle. When the HSB pin is driven LOW, the device conditionally initiates a STORE operation after t<sub>DELAY</sub>. A STORE cycle begins only if a write to the SRAM has taken place since the last STORE or RECALL cycle. The HSB pin also acts as an open drain driver (an internal 100-k $\Omega$  weak pull-up resistor) that is internally driven LOW to indicate a busy condition when the STORE (initiated by any means) is in progress.

**Note** After each Hardware and Software STORE operation, HSB is driven HIGH for a short time ( $t_{HHHD}$ ) with standard output high current and then remains HIGH by an internal 100-k $\Omega$  pull-up resistor.

SRAM write operations that are in progress when  $\overline{\text{HSB}}$  is driven LOW by any means are given time ( $t_{\text{DELAY}}$ ) to complete before the STORE operation is initiated. However, any SRAM write cycles requested after  $\overline{\text{HSB}}$  goes LOW are inhibited until  $\overline{\text{HSB}}$  returns HIGH. If the write latch is not set,  $\overline{\text{HSB}}$  is not driven LOW by the device. However, any of the SRAM read and write cycles are inhibited until  $\overline{\text{HSB}}$  is returned HIGH by the host microcontroller or another external source.

During any STORE operation, regardless of how it is initiated, the device continues to drive the HSB pin LOW, releasing it only when the STORE is complete. Upon completion of the STORE operation, the nvSRAM memory access is inhibited for  $t_{LZHSB}$  time after the HSB pin returns HIGH. Leave the HSB unconnected if it is not used.

### Hardware RECALL (Power-Up)

During power-up or after any low-power condition ( $V_{CC} < V_{SWITCH}$ ), an internal RECALL request is latched. When  $V_{CC}$  again exceeds the  $V_{SWITCH}$  on power-up, a RECALL cycle is automatically initiated and takes  $t_{HRECALL}$  to complete. During this time, the HSB pin is driven LOW by the HSB driver and all reads and writes to nvSRAM are inhibited.

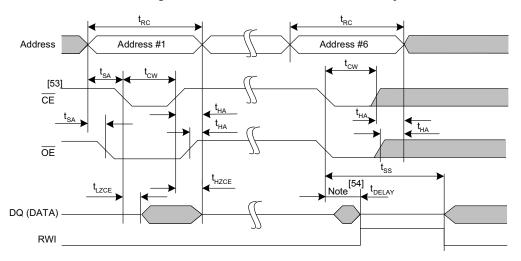

### Software STORE

Data is transferred from the SRAM to the nonvolatile memory by a software address sequence. A Software STORE cycle is initiated by executing sequential CE or OE controlled read cycles from six specific address locations in exact order. During the

STORE cycle, the previous nonvolatile data is first erased, followed by a store into the nonvolatile elements. After a STORE cycle is initiated, further reads and writes are disabled until the cycle is completed.

Because a sequence of reads from specific addresses is used for STORE initiation, it is important that no other read or write accesses intervene in the sequence. Otherwise, the sequence is aborted and no STORE or RECALL takes place.

To initiate the Software STORE cycle, the following read sequence must be performed:

- 1. Read address 0x4E38 Valid Read

- 2. Read address 0xB1C7 Valid Read

- 3. Read address 0x83E0 Valid Read

- 4. Read address 0x7C1F Valid Read

- 5. Read address 0x703F Valid Read

- 6. Read address 0x8FC0 Initiate STORE cycle

The software sequence may be clocked with  $\overline{\text{CE}}$ -controlled reads or  $\overline{\text{OE}}$ -controlled reads, with  $\overline{\text{WE}}$  kept HIGH for all the six read sequences. After the sixth address in the sequence is entered, the STORE cycle commences and the chip is disabled. HSB is driven LOW. After the t<sub>STORE</sub> cycle time is fulfilled, the SRAM is activated again for the read and write operation.

### Software RECALL

Data is transferred from the nonvolatile memory to the SRAM by a software address sequence. A software RECALL cycle is initiated with a sequence of read operations in a manner similar to the Software STORE initiation. To initiate the RECALL cycle, perform the following sequence of CE or OE controlled read operations:

- 1. Read address 0x4E38 Valid Read

- 2. Read address 0xB1C7 Valid Read

- 3. Read address 0x83E0 Valid Read

- 4. Read address 0x7C1F Valid Read

- 5. Read address 0x703F Valid Read

- 6. Read address 0x4C63 Initiate RECALL cycle

Internally, RECALL is a two-step procedure. First, the SRAM data is cleared; then, the nonvolatile information is transferred into the SRAM cells. After the t<sub>RECALL</sub> cycle time, the SRAM is again ready for read and write operations. The RECALL operation does not alter the data in the nonvolatile elements.

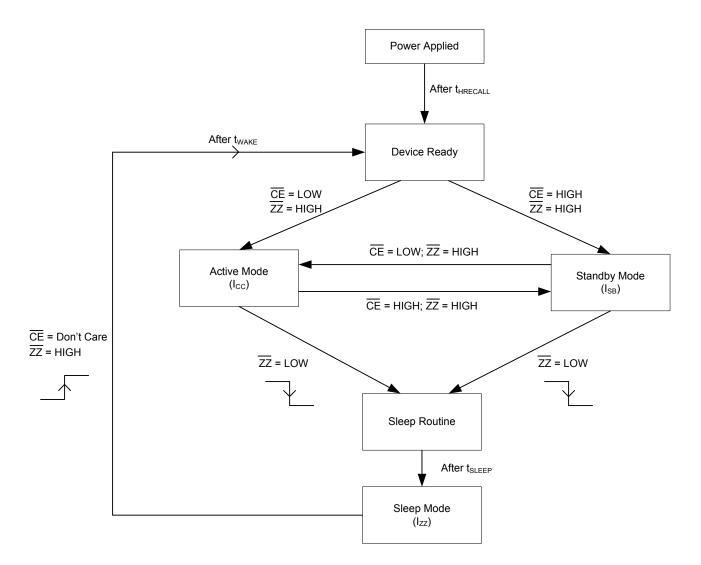

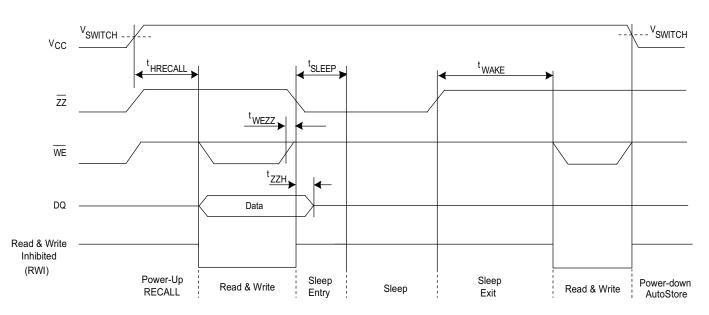

### Sleep Mode

In Sleep mode, the device consumes the lowest power supply current (I<sub>ZZ</sub>). The device enters a low-power Sleep mode after asserting the  $\overline{ZZ}$  pin LOW. After the Sleep mode is registered, the nvSRAM does a STORE operation to secure the data to the nonvolatile memory and then enters the low-power mode. The device starts consuming I<sub>ZZ</sub> current after t<sub>SLEEP</sub> time from the instance when the sleep mode is initiated. When the  $\overline{ZZ}$  pin is LOW, all input pins are ignored except the  $\overline{ZZ}$  pin. The nvSRAM is not accessible for normal operations while it is in sleep mode.

When the  $\overline{ZZ}$  pin is de-asserted (HIGH), there is a delay t<sub>WAKE</sub> before the user can access the device. If sleep mode is not used, the  $\overline{ZZ}$  pin should be tied to V<sub>CC</sub>.

**Note** When nvSRAM enters sleep mode, it initiates a nonvolatile STORE cycle, which results in losing one endurance cycle for every Sleep mode entry unless data has not been written to the nvSRAM since the last nonvolatile STORE/RECALL operation.

**Note** If the  $\overline{ZZ}$  pin is LOW during power-up, the device will not be in Sleep mode. However, the I/Os are in tristate until the  $\overline{ZZ}$  pin is de-asserted (HIGH).

### Figure 8. Sleep Mode (ZZ) Flow Diagram

#### Table 1. Mode Selection

| <b>CE</b> <sup>[10]</sup> | WE | OE | <b>BLE</b> , <b>BHE</b> / $\overline{\mathbf{B}}_{A}$ , $\overline{\mathbf{B}}_{B}$ , $\overline{\mathbf{B}}_{C}$ , $\overline{\mathbf{B}}_{D}$ <sup>[11]</sup> | <b>A<sub>15</sub> - A<sub>0</sub></b> <sup>[12]</sup>    | Mode                                                                                   | I/O                                                                                                   | Power                                   |

|---------------------------|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Н                         | Х  | Х  | X                                                                                                                                                               | X                                                        | Not selected                                                                           | Output High Z                                                                                         | Standby                                 |

| L                         | Н  | L  | L                                                                                                                                                               | Х                                                        | Read SRAM                                                                              | Output Data                                                                                           | Active                                  |

| L                         | L  | Х  | L                                                                                                                                                               | Х                                                        | Write SRAM                                                                             | Input Data                                                                                            | Active                                  |

| L                         | Н  | L  | X                                                                                                                                                               | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x8B45 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>AutoStore<br>Disable  | Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data                | Active <sup>[13]</sup>                  |

| L                         | Н  | L  | X                                                                                                                                                               | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x4B46 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>AutoStore<br>Enable   | Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data | Active <sup>[13]</sup>                  |

| L                         | Η  | L  | X                                                                                                                                                               | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x8FC0 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Nonvolatile<br>STORE  | Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output High Z              | Active I <sub>CC2</sub> <sup>[13]</sup> |

| L                         | Н  | L  | Х                                                                                                                                                               | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x4C63 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Nonvolatile<br>RECALL | Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output Data<br>Output High Z              | Active <sup>[13]</sup>                  |

Notes

- 10. The TSOP II package is offered in single CE. TSOP I, and BGA packages are offered in dual CE options. In this datasheet, for a dual CE device, CE refers to the internal logical combination of CE<sub>1</sub> and CE<sub>2</sub> such that when CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW. For all other cases CE is HIGH. Intermediate voltage levels are not permitted on any of the chip enable pins (CE for the single chip enable device; CE<sub>1</sub> and CE<sub>2</sub> for the dual chip enable device).

- 11.  $\overline{\text{BLE}}$ ,  $\overline{\text{BHE}}$  are applicable for the ×16 configuration and  $\overline{\text{B}}_{\text{A}}$ ,  $\overline{\text{B}}_{\text{B}}$ ,  $\overline{\text{B}}_{\text{C}}$ ,  $\overline{\text{B}}_{\text{D}}$  are applicable for the ×32 configuration only.

12. While there are 21 address lines on the CY14X116L (20 address lines on the CY14X116N and 19 address lines on the CY14X116S), only 13 address lines (A<sub>14</sub>-A<sub>2</sub>) are used to control software modes. The remaining address lines are don't care.

13. The six consecutive address locations must be in the order listed. WE must be HIGH during all six cycles to enable a nonvolatile operation.

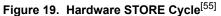

### Preventing AutoStore

The AutoStore function is disabled by initiating an AutoStore disable sequence. A sequence of read operations is performed in a manner similar to the Software STORE initiation. To initiate the AutoStore disable sequence, the following sequence of  $\overrightarrow{CE}$  or  $\overrightarrow{OE}$  controlled read operations must be performed:

- 1. Read address 0x4E38 Valid Read

- 2. Read address 0xB1C7 Valid Read

- 3. Read address 0x83E0 Valid Read

- 4. Read address 0x7C1F Valid Read

- 5. Read address 0x703F Valid Read

- 6. Read address 0x8B45 AutoStore Disable

AutoStore is re-enabled by initiating an AutoStore enable sequence. A sequence of read operations is performed in a manner similar to the software RECALL initiation. To initiate the AutoStore enable sequence, the following sequence of CE or OE controlled read operations must be performed:

- 1. Read address 0x4E38 Valid Read

- 2. Read address 0xB1C7 Valid Read

- 3. Read address 0x83E0 Valid Read

- 4. Read address 0x7C1F Valid Read

- 5. Read address 0x703F Valid Read

- 6. Read address 0x4B46 AutoStore Enable

If the AutoStore function is disabled or re-enabled, a manual software STORE operation must be performed to save the AutoStore state through subsequent power-down cycles. The part comes from the factory with AutoStore enabled and 0x00 written in all cells.

#### **Data Protection**

The CY14X116L/CY14X116N/CY14X116S protects data from corruption during low-voltage conditions by inhibiting all externally initiated STORE and write operations. The low-voltage condition is detected when  $V_{CC}$  is less than  $V_{SWITCH}$ . If the CY14X116L/CY14X116N/CY14X116S is in a write mode at power-up (both  $\overline{CE}$  and  $\overline{WE}$  are LOW), after a RECALL or STORE, the write is inhibited until the SRAM is enabled after t<sub>LZHSB</sub> (HSB to output active). This protects against inadvertent writes during power-up or brownout conditions.

# **Maximum Ratings**

Exceeding maximum ratings may impair the useful life of the device. These user guidelines are not tested.

| Storage temperature65 °C to +150 °C                                                 |

|-------------------------------------------------------------------------------------|

| Maximum accumulated storage time                                                    |

| At 150 °C ambient temperature 1000 h                                                |

| At 85 °C ambient temperature 20 Years                                               |

| Maximum junction temperature 150 °C                                                 |

| Supply voltage on $V_{CC}$ relative to $V_{SS}$                                     |

| CY14B116X:0.5 V to +4.1 V                                                           |

| CY14E116X:0.5 V to +7.0 V                                                           |

| Voltage applied to outputs                                                          |

| in high-Z state                                                                     |

| Input voltage0.5 V to Vcc + 0.5 V                                                   |

| Transient voltage (<20 ns) on any pin to ground potential–2.0 V to $V_{CC}$ + 2.0 V |

|                                                                                     |

# **DC Electrical Characteristics**

### Over the Operating Range

| Package power dissipation<br>capability (T <sub>A</sub> = 25 °C)1.0 W |

|-----------------------------------------------------------------------|

| Surface mount lead soldering<br>temperature (3 Seconds)+260 °C        |

| DC output current (1 output at a time, 1s duration) 20 mA             |

| Static discharge voltage                                              |

| Latch-up current > 140 mA                                             |

# **Operating Range**

| Product   | Range                           | Ambient<br>Temperature<br>(T <sub>A</sub> ) | v <sub>cc</sub> |

|-----------|---------------------------------|---------------------------------------------|-----------------|

| CY14B116X | Industrial                      | –40 °C to +85 °C                            | 2.7 V to 3.6 V  |

| CY14E116X | 116X Industrial 40 °C to +85 °C |                                             | 4.5 V to 5.5 V  |

| Parameter                        | Description                                                          | Test Conditions                                                                                                               |                             | Min  | <b>Typ</b> <sup>[14]</sup> | Мах | Unit |

|----------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|----------------------------|-----|------|

| V <sub>CC</sub>                  | Power supply                                                         |                                                                                                                               | CY14B116X                   | 2.7  | 3.0                        | 3.6 | V    |

|                                  |                                                                      |                                                                                                                               | CY14E116X                   | 4.5  | 5.0                        | 5.5 | V    |

| I <sub>CC1</sub>                 | Average V <sub>CC</sub> current                                      | Values obtained without output loads                                                                                          | t <sub>RC</sub> = 25/30 ns  | -    | -                          | 95  | mA   |

|                                  |                                                                      | (I <sub>OUT</sub> = 0 mA)                                                                                                     | t <sub>RC</sub> = 45 ns     | -    | -                          | 75  | mA   |

| I <sub>CC2</sub>                 | Average V <sub>CC</sub> current during STORE                         | All inputs don't care, $V_{CC} = V_{CC}$ (max).<br>Average current for duration $t_{STORE}$                                   |                             | -    | -                          | 10  | mA   |

| I <sub>CC3</sub>                 | Average $V_{CC}$ current at $t_{RC}$ = 200 ns, $V_{CC}$ (Typ), 25 °C | All inputs cycling at CMOS Levels.<br>Values obtained without output loads (I <sub>OI</sub>                                   | <sub>דע</sub> = 0 mA).      | -    | 50                         | _   | mA   |

| I <sub>CC4</sub> <sup>[15]</sup> | Average V <sub>CAP</sub> current during AutoStore cycle              | All inputs don't care. Average current for                                                                                    | duration t <sub>STORE</sub> | _    | -                          | 6   | mA   |

| I <sub>SB</sub>                  | V <sub>CC</sub> standby current                                      | $\overline{CE} \ge (V_{CC} - 0.2 \text{ V}). V_{IN} \le 0.2 \text{ V or} \ge (V_{CC})$                                        |                             | -    | -                          | 650 | μA   |

|                                  |                                                                      | <ul> <li>0.2 V). 'Standby current level after<br/>nonvolatile cycle is complete. Inputs are<br/>static. f = 0 MHz.</li> </ul> | t <sub>RC</sub> = 45 ns     | -    | -                          | 500 | μA   |

| I <sub>ZZ</sub>                  | Sleep mode current                                                   | All inputs are static at CMOS Level                                                                                           |                             | -    | -                          | 10  | μA   |

| I <sub>IX</sub> <sup>[16]</sup>  | Input lea <u>kag</u> e current<br>(except HSB)                       | $V_{CC} = V_{CC} \text{ (max)}, V_{SS} \le V_{IN} \le V_{CC}$                                                                 |                             | –1   | -                          | +1  | μA   |

|                                  | Inpu <u>t lea</u> kage current<br>(for HSB)                          | $V_{CC} = V_{CC} \text{ (max)}, V_{SS} \le V_{IN} \le V_{CC}$                                                                 |                             | -100 | -                          | +1  | μA   |

#### Notes

15. This parameter is only guaranteed by design and is not tested.

16. The HSB pin has I<sub>OUT</sub> = -2 uA for V<sub>OH</sub> of 2.4 V when both active HIGH and LOW drivers are disabled. When they are enabled standard V<sub>OH</sub> and V<sub>OL</sub> are valid. This parameter is characterized but not tested.

<sup>14.</sup> Typical values are at 25 °C, V\_{CC} = V\_{CC}(Typ). Not 100% tested.

# DC Electrical Characteristics (continued)

### Over the Operating Range

| Parameter                             | Description                                                        | Test Conditions                                                                                                                      | Min            | <b>Typ</b> <sup>[14]</sup> | Max                   | Unit |

|---------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------|-----------------------|------|

| I <sub>OZ</sub>                       | Off state output<br>leakage current                                | $\frac{V_{CC}}{BLE, BHE/B_A, B_B, B_{C,}} \leq V_{OUT} \leq V_{CC}, \overline{CE} \text{ or } \overline{OE} \geq V_{IH} \text{ or }$ | -1             | -                          | +1                    | μA   |

| V <sub>IH</sub>                       | Input HIGH voltage                                                 |                                                                                                                                      | 2.0            | -                          | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub>                       | Input LOW voltage                                                  |                                                                                                                                      | $V_{SS} - 0.5$ | _                          | 0.8                   | V    |

| V <sub>OH</sub>                       | Output HIGH voltage                                                | I <sub>OUT</sub> = –2 mA                                                                                                             | 2.4            | -                          | -                     | V    |

| V <sub>OL</sub>                       | Output LOW voltage                                                 | I <sub>OUT</sub> = 4 mA                                                                                                              | -              | -                          | 0.4                   | V    |

| V <sub>CAP</sub> <sup>[17]</sup>      | Storage capacitor                                                  | Between $V_{CAP}$ pin and $V_{SS}$                                                                                                   | 19.8           | 22.0                       | 82.0                  | μF   |

| V <sub>VCAP</sub> <sup>[18, 19]</sup> | Maximum voltage<br>driven on V <sub>CAP</sub> pin by<br>the device | V <sub>CC</sub> = V <sub>CC</sub> (max)                                                                                              | -              | -                          | 5.0                   | V    |

### **Data Retention and Endurance**

Over the Operating Range

| Parameter         | Description                  | Min       | Unit   |

|-------------------|------------------------------|-----------|--------|

| DATA <sub>R</sub> | Data retention               | 20        | Years  |

| NV <sub>C</sub>   | Nonvolatile STORE operations | 1,000,000 | Cycles |

### Capacitance

In the following table, the capacitance parameters are listed. <sup>[19]</sup>

| Parameter        | Description              | Test Conditions                         | Max<br>(All packages<br>except 165-FBGA) | Max<br>(165-FBGA package) | Unit |

|------------------|--------------------------|-----------------------------------------|------------------------------------------|---------------------------|------|

| C <sub>IN</sub>  | Input capacitance        | $T_A = 25 ^{\circ}C, f = 1 \text{MHz},$ | 8                                        | 10                        | pF   |

| C <sub>IO</sub>  | Input/Output capacitance | $V_{CC} = V_{CC} (Typ)$                 | 8                                        | 10                        | pF   |

| C <sub>OUT</sub> | Output capacitance       |                                         | 8                                        | 10                        | pF   |

### **Thermal Resistance**

In the following table, the thermal resistance parameters are listed.<sup>[19]</sup>

| Parameter     | Description                                 | Test Conditions                                                       | 44-TSOP II | 48-TSOP I | 54-TSOP II | 165-FBGA | Unit |

|---------------|---------------------------------------------|-----------------------------------------------------------------------|------------|-----------|------------|----------|------|

| $\Theta_{JA}$ | Thermal resistance<br>(Junction to ambient) | Test conditions follow standard test methods and procedures           | 44.6       | 35.6      | 41.1       | 15.6     | °C/W |

| $\Theta_{JC}$ | Thermal resistance<br>(Junction to case)    | for measuring thermal<br>impedance, in accordance with<br>EIA/JESD51. | 2.4        | 2.33      | 4.6        | 2.9      | °C/W |

#### Notes

19. These parameters are only guaranteed by design and are not tested.

<sup>17.</sup> Min V<sub>CAP</sub> value guarantees that there is a sufficient charge available to complete a successful AutoStore operation. Max V<sub>CAP</sub> value guarantees that the capacitor on V<sub>CAP</sub> is charged to a minimum voltage during a Power-Up RECALL cycle so that an immediate power-down cycle can complete a successful AutoStore. Therefore it is always recommended to use a capacitor within the specified min and max limits.

<sup>18.</sup> Maximum voltage on V<sub>CAP</sub> pin (V<sub>VCAP</sub>) is provided for guidance when choosing the V<sub>CAP</sub> capacitor. The voltage rating of the V<sub>CAP</sub> capacitor across the operating temperature range should be higher than the V<sub>VCAP</sub> voltage

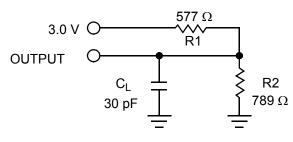

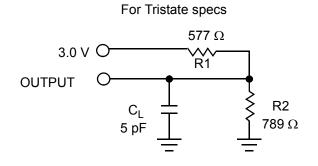

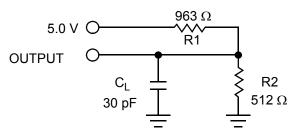

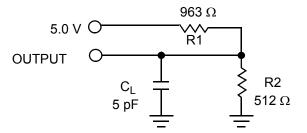

### Figure 9. AC Test Loads and Waveforms

For 3 V (CY14B116X):

For 5 V (CY14E116X):

For Tristate specs

# **AC Test Conditions**

|                                          | CY14B116X        | CY14E116X        |

|------------------------------------------|------------------|------------------|

| Input pulse levels                       | 0 V to 3 V       | 0 V to 3 V       |

| Input rise and fall times (10%–90%)      | <u>&lt;</u> 3 ns | <u>&lt;</u> 3 ns |

| Input and output timing reference levels | 1.5 V            | 1.5 V            |

# **AC Switching Characteristics**

# Over the Operating Range<sup>[20]</sup>

| Parame                                    | ters             | Description                       | 25  | ns  | 30  | ns  | 45  | ns  | Unit |

|-------------------------------------------|------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|------|

| Cypress Parameter                         | Alt Parameter    | Description                       | Min | Max | Min | Max | Min | Max | Unit |

| SRAM Read Cycle                           | _                | -                                 |     |     |     |     | -   |     |      |

| t <sub>ACE</sub>                          | t <sub>ACS</sub> | Chip enable access time           | -   | 25  | -   | 30  | -   | 45  | ns   |

| t <sub>RC</sub> <sup>[22]</sup>           | t <sub>RC</sub>  | Read cycle time                   | 25  | -   | 30  | -   | 45  | -   | ns   |

| t <sub>AA</sub> <sup>[23]</sup>           | t <sub>AA</sub>  | Address access time               | -   | 25  | -   | 30  | -   | 45  | ns   |

| t <sub>DOE</sub>                          | t <sub>OE</sub>  | Output enable to data valid       | -   | 12  | -   | 14  | -   | 20  | ns   |

| t <sub>OHA</sub> <sup>[23]</sup>          | t <sub>OH</sub>  | Output hold after address change  | 3   | -   | 3   | -   | 3   | -   | ns   |

| t <sub>LZCE</sub> <sup>[24]</sup>         | t <sub>LZ</sub>  | Chip enable to output active      | 3   | -   | 3   | -   | 3   | -   | ns   |

| t <sub>HZCE</sub> <sup>[21, 24]</sup>     | t <sub>HZ</sub>  | Chip disable to output inactive   | -   | 10  | -   | 12  | -   | 15  | ns   |

| t <sub>LZOE</sub> <sup>[24]</sup>         | t <sub>OLZ</sub> | Output enable to output active    | 0   | -   | 0   | -   | 0   | -   | ns   |

| t <sub>HZOE</sub> <sup>[21, 24]</sup>     | t <sub>онz</sub> | Output disable to output inactive | -   | 10  | -   | 12  | -   | 15  | ns   |

| t <sub>PU</sub> <sup>[24]</sup>           | t <sub>PA</sub>  | Chip enable to power active       | 0   | -   | 0   | -   | 0   | -   | ns   |

| t <sub>PD</sub> <sup>[24]</sup>           | t <sub>PS</sub>  | Chip disable to power standby     | -   | 25  | -   | 30  | -   | 45  | ns   |

| t <sub>DBE</sub>                          |                  | Byte enable to data valid         | _   | 12  | -   | 14  | -   | 20  | ns   |

| t <sub>LZBE</sub> <sup>[24]</sup>         |                  | Byte enable to output active      | 0   | -   | 0   | -   | 0   | -   | ns   |

| t <sub>HZBE</sub> [21, 24]                |                  | Byte disable to output inactive   | -   | 10  | -   | 12  | -   | 15  | ns   |

| SRAM Write Cycle                          | •                |                                   |     |     |     |     |     |     |      |

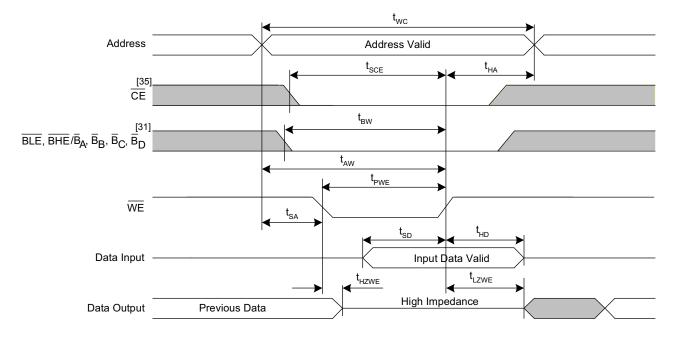

| t <sub>WC</sub>                           | t <sub>WC</sub>  | Write cycle time                  | 25  | -   | 30  | -   | 45  | -   | ns   |

| t <sub>PWE</sub>                          | t <sub>WP</sub>  | Write pulse width                 | 20  | -   | 24  | -   | 30  | -   | ns   |

| t <sub>SCE</sub>                          | t <sub>CW</sub>  | Chip enable to end of write       | 20  | -   | 24  | -   | 30  | -   | ns   |

| t <sub>SD</sub>                           | t <sub>DW</sub>  | Data setup to end of write        | 10  | -   | 14  | -   | 15  | -   | ns   |

| t <sub>HD</sub>                           | t <sub>DH</sub>  | Data hold after end of write      | 0   | _   | 0   | -   | 0   | _   | ns   |

| t <sub>AW</sub>                           | t <sub>AW</sub>  | Address setup to end of write     | 20  | -   | 24  | -   | 30  | -   | ns   |

| t <sub>SA</sub>                           | t <sub>AS</sub>  | Address setup to start of write   | 0   | -   | 0   | -   | 0   | -   | ns   |

| t <sub>HA</sub>                           | t <sub>WR</sub>  | Address hold after end of write   | 0   | -   | 0   | -   | 0   | -   | ns   |

| t <sub>HZWE</sub> <sup>[21, 24, 25]</sup> | t <sub>WZ</sub>  | Write enable to output disable    | -   | 10  | -   | 12  | -   | 15  | ns   |

| t <sub>LZWE</sub> <sup>[24]</sup>         | t <sub>ow</sub>  | Output active after end of write  | 3   | -   | 3   | -   | 3   | -   | ns   |

| t <sub>BW</sub>                           |                  | Byte enable to end of write       | 20  | -   | 24  | -   | 30  | -   | ns   |

Notes

20. Test conditions assume a signal transition time of 3 ns or less, timing reference levels of  $V_{CC}/2$ , input pulse levels of 0 to  $V_{CC}$ (Typ), and output loading of the specified  $I_{OL}/I_{OH}$  and 30 pF load capacitance as shown in Figure 9.

$21.\,t_{HZCE},\,t_{HZOE},\,t_{HZBE}\,\text{and}\,t_{HZWE}\,\text{are specified with a load capacitance of 5 pF}.\,Transition \,\text{is measured } \pm 200\,\text{mV}\,\text{from the steady state output voltage}.$

22. WE must be HIGH during SRAM read cycles.

23. Device is continuously selected with  $\overline{CE}$ ,  $\overline{OE}$  and  $\overline{BLE}$ ,  $\overline{BHE}/\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$  LOW.

24. These parameters are only guaranteed by design and are not tested.

25. If WE is LOW when CE goes LOW, the outputs remain in the high impedance state.

Notes

- 26. WE must be HIGH during SRAM read cycles.

- 27. Device is continuously selected with  $\overline{CE}$ ,  $\overline{OE}$  and  $\overline{BLE}$ ,  $\overline{BHE}/\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$  LOW.

- 28. HSB must remain HIGH during Read and Write cycles.

- 29. BLE, BHE are applicable for the ×16 configuration and B<sub>A</sub>, B<sub>B</sub>, B<sub>C</sub>, B<sub>D</sub> are applicable for the ×32 configuration only.

30. TSOP II package is offered in single CE and BGA package is offered in dual CE options. In this datasheet, for a dual CE device, CE refers to the internal logical combination of CE<sub>1</sub> and CE<sub>2</sub> such that when CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW. For all other cases CE is HIGH. Intermediate voltage levels are not permitted on any of the chip enable pins (CE for the single chip enable device; CE<sub>1</sub> and CE<sub>2</sub> for the dual chip enable device).

### Figure 12. SRAM Write Cycle 1: WE Controlled<sup>[32, 34, 36]</sup>

#### Note<u>s</u>

- 31. BLE, BHE are applicable for the ×16 configuration and  $\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$  are applicable for the ×32 configuration only.

- 32. If WE is LOW when CE goes LOW, the outputs remain in the high impedance state.

- 33. WE must be HIGH during SRAM read cycles.

- 34. HSB must remain HIGH during Read and Write cycles.

- 35. TSOP II package is offered in single CE. TSOP I and BGA packages are offered in dual CE options. In this datasheet, for a dual CE device, CE refers to the internal logical combination of CE<sub>1</sub> and CE<sub>2</sub> such that when CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW. For all other cases CE is HIGH. Intermediate voltage levels are not permitted on any of the chip enable pins (CE for the single chip enable device; CE<sub>1</sub> and CE<sub>2</sub> for the dual chip enable device).

- 36.  $\overline{CE}$  or  $\overline{WE}$  must be  $\geq V_{IH}$  during address transitions.

Figure 14. SRAM Write Cycle 3:  $\overline{BHE}$ ,  $\overline{BLE}$ /  $\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$ Controlled<sup>[38, 39, 40]</sup>

Notes

- 37. BLE, BHE are applicable for the ×16 configuration and  $\overline{B}_A$ ,  $\overline{B}_B$ ,  $\overline{B}_C$ ,  $\overline{B}_D$  are applicable for the ×32 configuration only.

- 38. If  $\overline{\text{WE}}$  is LOW when  $\overline{\text{CE}}$  goes LOW, the outputs remain in the high impedance state.

- 39. HSB must remain HIGH during Read and Write cycles.

- 40.  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  must be  $\geq V_{\text{IH}}$  during address transitions.

<sup>41.</sup> TSOP II package is offered in single CE. TSOP I and BGA packages are offered in dual CE options. In this datasheet, for a dual CE device, CE refers to the internal logical combination of CE<sub>1</sub> and CE<sub>2</sub> such that when CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW. For all other cases CE is HIGH. Intermediate voltage levels are not permitted on any of the chip enable pins (CE for the single chip enable device; CE<sub>1</sub> and CE<sub>2</sub> for the dual chip enable device).

# AutoStore/Power-Up RECALL Characteristics

#### Over the Operating Range

| Parameter                              | Description                               |           | Min | Max  | Unit |

|----------------------------------------|-------------------------------------------|-----------|-----|------|------|

| t <sub>HRECALL</sub> <sup>[42]</sup>   | Power-Up RECALL duration                  |           | -   | 30   | ms   |

| t <sub>STORE</sub> <sup>[43]</sup>     | STORE cycle duration                      |           | -   | 8    | ms   |

| t <sub>DELAY</sub> <sup>[44, 45]</sup> | Time allowed to complete SRAM write cycle |           | -   | 25   | ns   |

| V <sub>SWITCH</sub>                    | Low-voltage trigger level                 | CY14B116X | -   | 2.65 | V    |

|                                        |                                           | CY14E116X | -   | 4.40 | V    |

| t <sub>VCCRISE</sub> <sup>[45]</sup>   | V <sub>CC</sub> rise time                 |           | 150 | -    | μS   |

| V <sub>HDIS</sub> <sup>[45]</sup>      | HSB output disable voltage                |           | -   | 1.9  | V    |

| t <sub>LZHSB</sub> <sup>[45]</sup>     | HSB to output active time                 |           | _   | 5    | μS   |

| t <sub>HHHD</sub> <sup>[45]</sup>      | HSB HIGH active time                      |           | _   | 500  | ns   |

### Figure 15. AutoStore or Power-Up RECALL<sup>[46]</sup>

#### Notes

42.  $t_{\mbox{HRECALL}}$  starts from the time  $V_{\mbox{CC}}$  rises above  $V_{\mbox{SWITCH}}$

43. If an SRAM write has not taken place since the last nonvolatile cycle, no AutoStore or Hardware STORE takes place.

44. On a Hardware STORE and AutoStore initiation, SRAM write operation continues to be enabled for time t<sub>DELAY</sub>.

45. These parameters are only guaranteed by design and are not tested.

46. Read and Write cycles are ignored during STORE, RECALL, and while  $V_{CC}$  is below  $V_{SWITCH}$ .

47. During power-up and power-down, HSB glitches when HSB pin is pulled up through an external resistor.

# **Sleep Mode Characteristics**

### Over the Operating Range