# Digital Power Monitor with Clear Pin and ALERT Output

Data Sheet ADM1192

#### **FEATURES**

Powered from 3.15 V to 26 V

Precision current sense amplifier

Precision voltage input

12-bit ADC for current and voltage readback

ALERT output allows basic P-channel FET hot swap up to 26 V

SETV input for setting overcurrent alert threshold

Programmable overcurrent filtering via TIMER pin

CLRB input pin

I<sup>2</sup>C fast mode-compliant interface (400 kHz maximum)

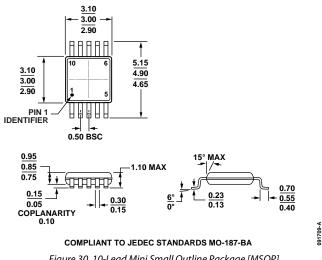

10-lead MSOP

#### **APPLICATIONS**

Power monitoring/power budgeting

Central office equipment

Telecommunications and data communications equipment

PCs/servers

#### **GENERAL DESCRIPTION**

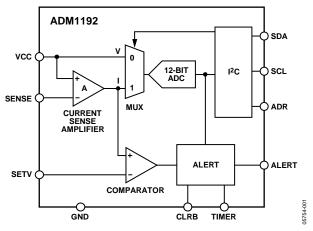

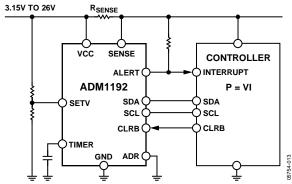

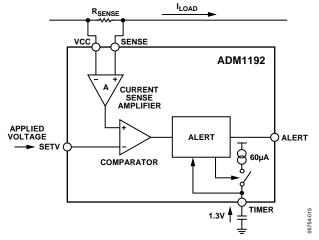

The ADM1192 is an integrated current sense amplifier that offers digital current and voltage monitoring via an on-chip 12-bit analog-to-digital converter (ADC), communicated through an  $I^2C^*$  interface.

An internal current sense amplifier measures voltage across the sense resistor in the power path via the VCC pin and the SENSE pin.

A 12-bit ADC can measure the current seen in the sense resistor and in the supply voltage on the VCC pin. An industry-standard I<sup>2</sup>C interface allows a controller to read current and voltage data from the ADC. Measurements can be initiated by an I<sup>2</sup>C command. Alternatively, the ADC can run continuously, and the user can read the latest conversion data whenever it is required. Up to four unique I<sup>2</sup>C addresses can be created, depending on the way the ADR pin is connected.

A SETV pin is also included. A voltage applied to this pin is internally compared with the output voltage on the current sense amplifier. The output of the SETV comparator asserts when the current sense amplifier output exceeds the SETV voltage. This event is detected at the ALERT block. The ALERT block then charges up the external TIMER capacitor with a fixed current. When this timing cycle is complete, the ALERT output asserts.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

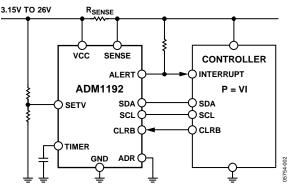

Figure 2. Applications Diagram

The ALERT output can be used as a flag to warn a micro-controller or field programmable gate array (FPGA) of an overcurrent condition. ALERT outputs of multiple ADM1192 devices can be tied together and used as a combined alert.

A basic P-channel FET hot swap circuit can be implemented with the ALERT output. The value of the TIMER capacitor should be set so that the charging time of this capacitor is much longer than the period during which a higher than nominal inrush current may be flowing.

The ADM1192 is packaged in a 10-lead MSOP.

Trademarks and registered trademarks are the property of their respective owners.

| TABLE OF CONTENTS                                                                            |                                                                      |    |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----|

| Features                                                                                     | Identifying the ADM1192 on the I <sup>2</sup> C Bus                  | 10 |

| Applications1                                                                                | General I <sup>2</sup> C Timing                                      | 10 |

| General Description                                                                          | Write and Read Operations                                            | 12 |

| Functional Block Diagram 1                                                                   | Quick Command                                                        |    |

| Revision History                                                                             | Write Command Byte                                                   |    |

| Specifications                                                                               | Write Extended Command Byte                                          |    |

| •                                                                                            | ·                                                                    |    |

| Absolute Maximum Ratings                                                                     | Read Voltage and/or Current Data Bytes                               |    |

| Thermal Characteristics                                                                      | Applications Information                                             |    |

| ESD Caution                                                                                  | ALERT Output                                                         | 16 |

| Pin Configuration and Function Descriptions6                                                 | SETV Pin                                                             | 16 |

| Typical Performance Characteristics                                                          | Kelvin Sense Resistor Connection                                     | 16 |

| Voltage and Current Readback10                                                               | Outline Dimensions                                                   | 17 |

| Serial Bus Interface                                                                         | Ordering Guide                                                       | 17 |

| REVISION HISTORY                                                                             |                                                                      |    |

| 7/13—Rev. C to Rev. D                                                                        | Added ADC Conversion Time Parameter                                  | 3  |

|                                                                                              | Changes to Input Current for 00 Decode, I <sub>ADRLOW</sub> , Param  |    |

| Changed SETV Pin Rating, Table 2 5 Changes to CLRB Pin and ALERT Pin Descriptions, Table 4 6 | Changes to Input Current for 11 Decode, I <sub>ADRHIGH</sub> , Paran |    |

| Changes to Table 15                                                                          | Added Endnote 2                                                      |    |

| Changes to the Implementing a Basic Hot Swap Circuit and the                                 | Changes to Figure 6                                                  |    |

| SETV Pin Sections                                                                            | Changes to Figure 17                                                 | 9  |

| Changes to Figure 2816                                                                       | Changes to General I <sup>2</sup> C Timing Section, Step 3           |    |

| Moved the Kelvin Sense Resistor Connection Section                                           | Changes to Table 5                                                   |    |

|                                                                                              | Changes to Quick Command Section                                     |    |

|                                                                                              | Changes to Figure 21                                                 |    |

| 6/12—Rev. B to Rev. C                                                                        | Changes to Table 7                                                   |    |

| Changes to Low Level Input Voltage, $V_{\rm IL}$ Parameter, Test                             | Changes to Write Extended Command Byte Section                       |    |

| Conditions/Comments Column, Table 1 and High Level Input                                     | Changes to Figure 23                                                 |    |

| Voltage, V <sub>IH</sub> Parameter, Test Conditions/Comments Column,                         | Changes to Table 9 and Table 11                                      | 13 |

| Table 1                                                                                      | Changes to Converting ADC Codes to Voltage and                       | 1. |

| Changes to SETV Pin Parameter, Rating Column, Table 2 5                                      | Current Readings Section                                             |    |

| Changes to Pin 3, Description Column, Table 4 and Pin 10                                     | Changes to Figure 27                                                 | 10 |

| Description Column, Table 4                                                                  |                                                                      |    |

| Changes to Bit 2, Function Column, Table 9                                                   | 4/07—Rev. 0 to Rev. A                                                |    |

| Changes to Overcurrent Flag Section                                                          | Changes to Table 5                                                   | 10 |

| Changes to Kelvin Sense Resistor Connection Section                                          | Changes to Figure 18 and Figure 19                                   |    |

| Deleted Figure 30; Renumbered Sequentially                                                   | Changes to Figure 23                                                 |    |

| Updated Outline Dimensions                                                                   | Changes to Figure 25 and Figure 26                                   | 14 |

|                                                                                              | Added Applications Information Heading                               | 16 |

| 2/08—Rev. A to Rev. B                                                                        |                                                                      |    |

| Changes to Figure 2 1                                                                        | 9/06—Revision 0: Initial Version                                     |    |

| Changed V <sub>VCC</sub> to V <sub>CC</sub> Throughout                                       |                                                                      |    |

# **SPECIFICATIONS**

$V_{CC}$  = 3.15 V to 26 V,  $T_A$  = -40°C to +85°C, typical values at  $T_A$  = 25°C, unless otherwise noted.

Table 1.

| Parameter                                                                         | Min       | Тур                   | Max   | Unit           | Test Conditions/Comments                                  |

|-----------------------------------------------------------------------------------|-----------|-----------------------|-------|----------------|-----------------------------------------------------------|

| VCC PIN                                                                           |           |                       |       |                |                                                           |

| Operating Voltage Range, Vcc                                                      | 3.15      |                       | 26    | V              |                                                           |

| Supply Current, Icc                                                               |           | 1.7                   | 2     | mA             |                                                           |

| Undervoltage Lockout, Vuvlo                                                       |           | 2.8                   |       | V              | VCC rising                                                |

| Undervoltage Lockout Hysteresis, Vuvlohyst                                        |           | 80                    |       | mV             |                                                           |

| MONITORING ACCURACY <sup>1</sup>                                                  |           |                       |       |                |                                                           |

| Current Sense Absolute Accuracy                                                   |           |                       |       |                |                                                           |

| 0°C to +70°C                                                                      | -1.45     |                       | +1.45 | %              | V <sub>SENSE</sub> = 75 mV                                |

|                                                                                   | -1.8      |                       | +1.8  | %              | $V_{SENSE} = 50 \text{ mV}$                               |

|                                                                                   | -2.8      |                       | +2.8  | %              | V <sub>SENSE</sub> = 25 mV                                |

|                                                                                   | -5.7      |                       | +5.7  | %              | V <sub>SENSE</sub> = 12.5 mV                              |

| 0°C to +85°C                                                                      | -1.5      |                       | +1.5  | %              | V <sub>SENSE</sub> = 75 mV                                |

|                                                                                   | -1.8      |                       | +1.8  | %              | V <sub>SENSE</sub> = 50 mV                                |

|                                                                                   | -2.95     |                       | +2.95 | %              | V <sub>SENSE</sub> = 25 mV                                |

|                                                                                   | -6.1      |                       | +6.1  | %              | V <sub>SENSE</sub> = 12.5 mV                              |

| -40°C to +85°C                                                                    | -1.95     |                       | +1.95 | %              | V <sub>SENSE</sub> = 75 mV                                |

|                                                                                   | -2.45     |                       | +2.45 | %              | V <sub>SENSE</sub> = 50 mV                                |

|                                                                                   | -3.85     |                       | +3.85 | %              | V <sub>SENSE</sub> = 25 mV                                |

|                                                                                   | -6.7      |                       | +6.7  | / <sub>%</sub> | V <sub>SENSE</sub> = 23 V<br>V <sub>SENSE</sub> = 12.5 mV |

| V <sub>SENSE</sub> for ADC Full Scale <sup>2</sup>                                | -0.7      | 105.04                | +0.7  |                | V 25H25 — 12.3 111V                                       |

| Voltage Sense Accuracy                                                            |           | 105.84                |       | mV             |                                                           |

| 0°C to +70°C                                                                      | -0.85     |                       | +0.85 | %              | V <sub>cc</sub> = 3.0 V to 5.5 V (low range)              |

|                                                                                   | -0.9      |                       | +0.9  | %              | $V_{cc} = 10.8 \text{ V to } 16.5 \text{ V (high range)}$ |

| 0°C to +85°C                                                                      | -0.85     |                       | +0.85 | %              | $V_{CC} = 3.0 \text{ V to } 5.5 \text{ V (low range)}$    |

|                                                                                   | -0.9      |                       | +0.9  | %              | V <sub>CC</sub> = 10.8 V to 16.5 V (high range)           |

| −40°C to +85°C                                                                    | -0.9      |                       | +0.9  | %              | $V_{CC} = 3.0 \text{ V to } 5.5 \text{ V (low range)}$    |

|                                                                                   | -1.15     |                       | +1.15 | %              | V <sub>CC</sub> = 10.8 V to 16.5 V (high range)           |

| V <sub>CC</sub> for ADC Full Scale <sup>3</sup>                                   |           |                       |       |                |                                                           |

| Low Range (VRANGE = 1)                                                            |           | 6.65                  |       | V              |                                                           |

| High Range (VRANGE = 0)                                                           |           | 26.52                 |       | V              |                                                           |

| CLRB PIN                                                                          |           |                       |       |                |                                                           |

| Logic Low Threshold, V <sub>CLRBL</sub>                                           |           |                       | 8.0   | V              |                                                           |

| Input Current for Logic Low Input, IclrBL                                         | -40       | -22                   |       | μΑ             | $V_{CLRB} = 0 V \text{ to } 0.8 V$                        |

| Logic High Threshold, V <sub>CLRBH</sub>                                          | 1.6       |                       |       | mV             |                                                           |

| Input Current for Logic High Input, Iclrbh                                        |           | 3                     | 6     | μΑ             | V <sub>CLRB</sub> = 1.6 V to 5.5 V                        |

| ADC CONVERSION TIME⁴                                                              |           | 150                   |       | μs             |                                                           |

| SENSE PIN                                                                         |           |                       |       |                |                                                           |

| Input Current, I <sub>SENSE</sub>                                                 | <u>-1</u> |                       | +1    | μΑ             | $V_{SENSE} = V_{CC}$                                      |

| SETV PIN                                                                          |           |                       | 4     |                | L                                                         |

| Overcurrent Trip Threshold                                                        | 98        | 100                   | 102   | mV             | $V_{SETV} = 1.8 \text{ V}$                                |

| Occupant Tria Calin V (V)                                                         | 49.5      | 50                    | 50.5  | mV             | $V_{SETV} = 0.9 \text{ V}$                                |

| Overcurrent Trip Gain, V <sub>SETV</sub> /(V <sub>CC</sub> – V <sub>SENSE</sub> ) | 4         | 18                    | . 1   |                | $V_{SETV} = 0.9 \text{ V to } 1.9 \text{ V}$              |

| Input Current, I <sub>SETVLEAK</sub>                                              | –1        | 2                     | +1    | μΑ             | $V_{SETV} = 0.9 \text{ V to } 1.9 \text{ V}$              |

| Glitch Filter, t <sub>SETVGLITCH</sub>                                            |           | 3<br>ov D   Page 3 of |       | μs             |                                                           |

Rev. D | Page 3 of 20

| Parameter                                                                       | Min                       | Тур  | Max                  | Unit | Test Conditions/Comments                                                   |

|---------------------------------------------------------------------------------|---------------------------|------|----------------------|------|----------------------------------------------------------------------------|

| TIMER PIN                                                                       |                           |      |                      |      |                                                                            |

| Pull-Up Current (Overcurrent Fault), ITIMERUPOC                                 | -46                       | -62  | -78                  | μΑ   | $(18.125 \times V_{SENSE}) > V_{SETV}, V_{TIMER} = 1 V$                    |

| Pull-Down Current, ItiMERDN                                                     |                           | 100  |                      | μA   | Normal operation, V <sub>TIMER</sub> = 1 V                                 |

| Pin Threshold High, VTIMERH                                                     | 1.275                     | 1.3  | 1.325                | V    | TIMER rising                                                               |

| ALERT PIN                                                                       |                           |      |                      |      |                                                                            |

| Output Low Voltage, VALERTOL                                                    |                           | 0.05 | 0.1                  | V    | $I_{ALERT} = -100 \mu A$                                                   |

|                                                                                 |                           | 1    | 1.5                  | mA   | $I_{ALERT} = -2 \text{ mA}$                                                |

| Input Current, I <sub>ALERT</sub>                                               | -1                        |      | +1                   | μΑ   | $V_{ALERT} = V_{CC}$ ; ALERT asserted                                      |

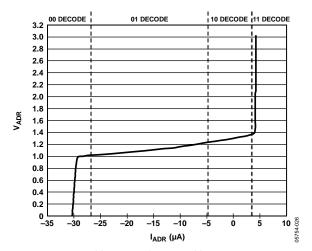

| ADR PIN                                                                         |                           |      |                      |      |                                                                            |

| Set Address to 00, V <sub>ADRLOWV</sub>                                         | 0                         |      | 0.8                  | V    | Low state                                                                  |

| Set Address to 01, R <sub>ADRLOWZ</sub>                                         | 80                        | 120  | 160                  | kΩ   | Resistor to ground state, load pin with specified resistance for 01 decode |

| Set Address to 10, I <sub>ADRHIGHZ</sub>                                        | -0.3                      |      | +0.3                 | μΑ   | Open state, maximum load allowed on ADR pin for 10 decode                  |

| Set Address to 11, V <sub>ADRHIGHV</sub>                                        | 2                         |      | 5.5                  | V    | High state                                                                 |

| Input Current for 00 Decode, IADRLOW                                            | -40                       | -25  |                      | μΑ   | $V_{ADR} = 0 V \text{ to } 0.8 V$                                          |

| Input Current for 11 Decode, IADRHIGH                                           |                           | 3    | 6                    | μΑ   | V <sub>ADR</sub> = 2.0 V to 5.5 V                                          |

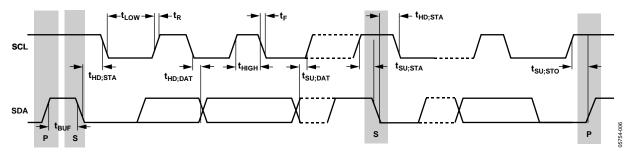

| I <sup>2</sup> C TIMING                                                         |                           |      |                      |      |                                                                            |

| Low Level Input Voltage, V <sub>IL</sub>                                        |                           |      | 0.3 V <sub>BUS</sub> | V    | $V_{BUS} = 3.0 \text{ V to } 5.5 \text{ V}$                                |

| High Level Input Voltage, V <sub>IH</sub>                                       | 0.7 V <sub>BUS</sub>      |      |                      | V    | $V_{BUS} = 3.0 \text{ V to } 5.5 \text{ V}$                                |

| Low Level Output Voltage on SDA, Vol                                            |                           |      | 0.4                  | V    | $I_{OL} = 3 \text{ mA}$                                                    |

| Output Fall Time on SDA from V <sub>IHMIN</sub> to V <sub>ILMAX</sub>           | 20 + 0.1 C <sub>BUS</sub> |      | 250                  | ns   | C <sub>BUS</sub> = bus capacitance from SDA to GND                         |

| Maximum Width of Spikes Suppressed by<br>Input Filtering on SDA Pin and SCL Pin | 50                        |      | 250                  | ns   |                                                                            |

| Input Current, I., on SDA/SCL When Not<br>Driving a Logic Low Output            | -10                       |      | +10                  | μΑ   |                                                                            |

| Input Capacitance on SDA/SCL                                                    |                           | 5    |                      | рF   |                                                                            |

| SCL Clock Frequency, f <sub>SCL</sub>                                           |                           |      | 400                  | kHz  |                                                                            |

| Low Period of the SCL Clock                                                     | 600                       |      |                      | ns   |                                                                            |

| High Period of the SCL Clock                                                    | 1300                      |      |                      | ns   |                                                                            |

| Setup Time for Repeated Start Condition, tsu;STA                                | 600                       |      |                      | ns   |                                                                            |

| SDA Output Data Hold Time, t <sub>HD;DAT</sub>                                  | 100                       |      | 900                  | ns   |                                                                            |

| Setup Time for a Stop Condition, t <sub>SU;STO</sub>                            | 600                       |      |                      | ns   |                                                                            |

| Bus Free Time Between a Stop and a Start Condition, t <sub>BUF</sub>            | 1300                      |      |                      | ns   |                                                                            |

| Capacitive Load for Each Bus Line                                               |                           |      | 400                  | рF   |                                                                            |

<sup>1</sup> Monitoring accuracy is a measure of the error in a code that is read back for a particular voltage/current. This is a combination of amplifier error, reference error, ADC

error, and error in ADC full-scale code conversion factor.

This is an absolute value to be used when converting ADC codes to current readings; any inaccuracy in this value is factored into absolute current accuracy values (see the Specifications for the Current Sense Absolute Accuracy parameter).

<sup>&</sup>lt;sup>3</sup> These are absolute values to be used when converting ADC codes to voltage readings; any inaccuracy in these values is factored into voltage accuracy values (see the Specifications for the Voltage Sense Accuracy parameter).

Time between the receipt of the command byte and the actual ADC result being placed in the register.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                           | Rating          |

|-------------------------------------|-----------------|

| VCC Pin                             | 30 V            |

| SENSE Pin                           | 30 V            |

| TIMER Pin                           | -0.3 V to +6 V  |

| CLRB Pin                            | −0.3 V to +6 V  |

| SETV Pin                            | 30 V            |

| ALERT Pin                           | 30 V            |

| SDA Pin, SCL Pin                    | −0.3 V to +6 V  |

| ADR Pin                             | -0.3 V to +6 V  |

| Storage Temperature Range           | −65°C to +125°C |

| Operating Temperature Range         | -40°C to +85°C  |

| Lead Temperature (Soldering 10 sec) | 300°C           |

| Junction Temperature                | 150°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type | θја   | Unit |

|--------------|-------|------|

| 10-Lead MSOP | 137.5 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

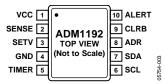

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC      | Positive Supply Input Pin. The operating supply voltage range is 3.15 V to 26 V. An undervoltage lockout (UVLO) circuit resets the ADM1192 when a low supply voltage is detected.                                                                                                                                                                                                                                                                         |

| 2       | SENSE    | Current Sense Input Pin. A sense resistor between the VCC pin and the SENSE pin generates a voltage across a sense resistor. This voltage is proportional to the load current. A current sense amplifier amplifies this voltage before it is digitized by the ADC.                                                                                                                                                                                        |

| 3       | SETV     | Input Pin. The voltage driven onto this pin is compared with the output of the internal current sense amplifier. The lower the voltage on the SETV, the lower the current level that causes the ALERT output to assert. Typical response time is 1 $\mu$ s to 2 $\mu$ s.                                                                                                                                                                                  |

| 4       | GND      | Chip Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5       | TIMER    | Timer Input Pin. An external capacitor, C <sub>TIMER</sub> , sets the timing period for masking overcurrent conditions. This timing period should be sufficient to allow the inrush current to completely charge up the load without tripping an overcurrent fault. This makes the device robust against false triggering due to current transients.                                                                                                      |

| 6       | SCL      | I <sup>2</sup> C Clock Pin. Open-drain input; requires an external resistive pull-up.                                                                                                                                                                                                                                                                                                                                                                     |

| 7       | SDA      | I <sup>2</sup> C Data I/O Pin. Open-drain input/output; requires an external resistive pull-up.                                                                                                                                                                                                                                                                                                                                                           |

| 8       | ADR      | I <sup>2</sup> C Address Pin. This pin can be tied low, tied high, left floating, or tied low through a resistor to set four I <sup>2</sup> C addresses.                                                                                                                                                                                                                                                                                                  |

| 9       | CLRB     | Clear Pin. A latched overcurrent condition can be cleared by toggling this pin low. Holding this pin low disables the ALERT output.                                                                                                                                                                                                                                                                                                                       |

| 10      | ALERT    | Alert Output Pin. Active high, open-drain configuration. This pin asserts high when an overcurrent condition is present. The level at which an overcurrent condition is detected depends on either the voltage on the SETV pin or the value in the ALERT_TH register. The ALERT_EN register determines which is used in the comparison. This pin has a latching function and must be cleared manually using either the ALERT_EN register or the CLRB pin. |

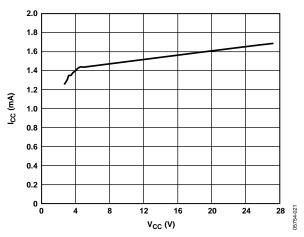

# TYPICAL PERFORMANCE CHARACTERISTICS

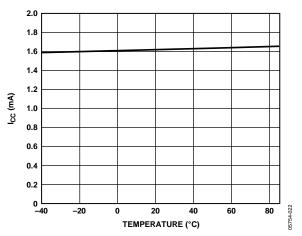

Figure 4. Supply Current vs. Supply Voltage

Figure 5. Supply Current vs. Temperature

Figure 6. Address Pin Voltage vs. Address Pin Current for Four Addressing Options on Each Address Pin

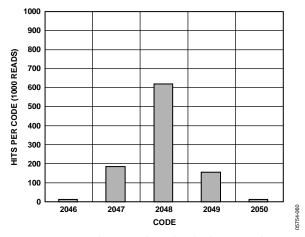

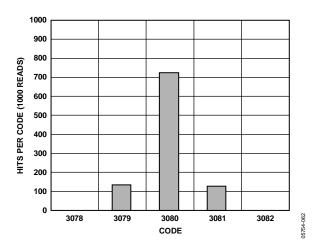

Figure 7. ADC Noise with Current Channel, Midcode Input, and 1000 Reads

Figure 8. ADC Noise with 14:1 Voltage Channel, 5 V Input, and 1000 Reads

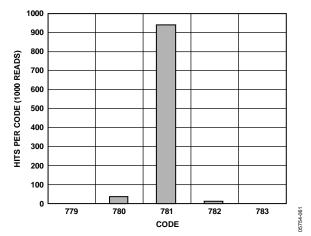

Figure 9. ADC Noise with 7:1 Voltage Channel, 5 V Input, and 1000 Reads

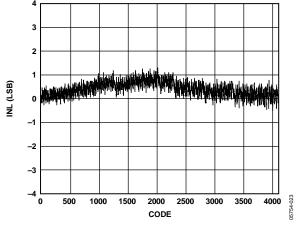

Figure 10. INL for ADC

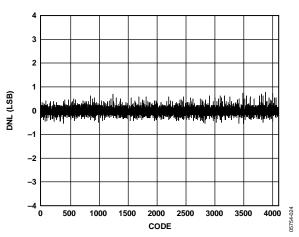

Figure 11. DNL for ADC

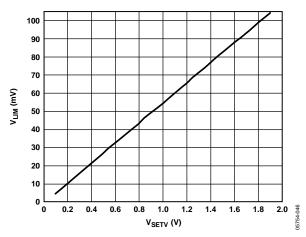

Figure 12. Overcurrent Limit Threshold vs. SETV Pin Voltage

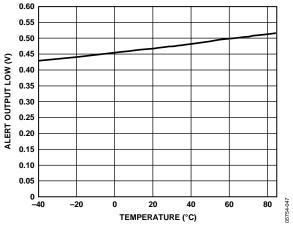

Figure 13. ALERT Output Low Voltage vs. Temperature at 1 mA

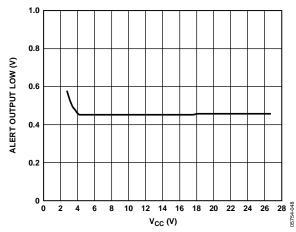

Figure 14. ALERT Output Low Voltage vs. Supply Voltage at 1 mA

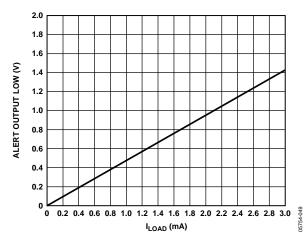

Figure 15. ALERT Output Low Voltage vs. Load Current

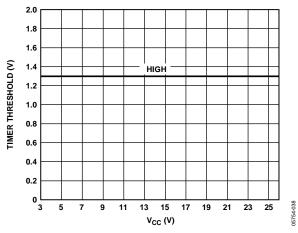

Figure 16. Timer Threshold vs. Supply Voltage

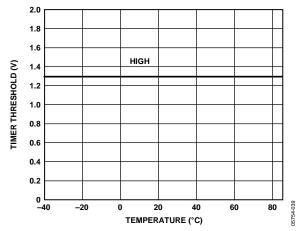

Figure 17. Timer Threshold vs. Temperature

#### **VOLTAGE AND CURRENT READBACK**

The ADM1192 contains the components to allow voltage and current readback over an I²C bus. The voltage output of the current sense amplifier and the voltage on the VCC pin are fed into a 12-bit ADC via a multiplexer. The device can be instructed to convert voltage and/or current at any time during operation via an I²C command. When all conversions are complete, the voltage and/or current values can be read back with 12-bit accuracy in two or three bytes.

#### **SERIAL BUS INTERFACE**

Control of the ADM1192 is carried out via the serial system management bus (I<sup>2</sup>C). This interface is compatible with the I<sup>2</sup>C fast mode (400 kHz maximum). The ADM1192 is connected to this bus as a slave device, under the control of a master device.

#### **IDENTIFYING THE ADM1192 ON THE I<sup>2</sup>C BUS**

The ADM1192 has a 7-bit serial bus slave address. When the device powers up, it does so with a default serial bus address. The five MSBs of the address are set to 01011; the two LSBs are determined by the state of the ADR pin. There are four configurations available on the ADR pin that correspond to four I<sup>2</sup>C addresses for the two LSBs (see Table 5). This scheme allows four ADM1192 devices to operate on a single I<sup>2</sup>C bus.

#### **GENERAL I<sup>2</sup>C TIMING**

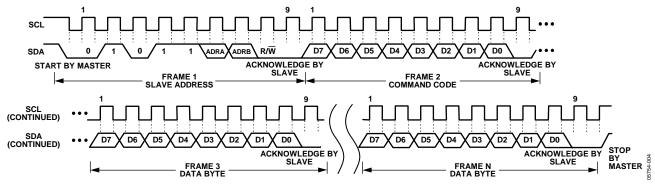

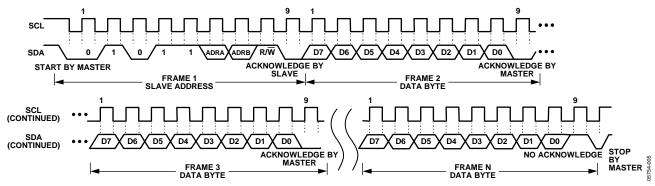

Figure 18 and Figure 19 show timing diagrams for general write and read operations using the I<sup>2</sup>C. The I<sup>2</sup>C specification defines conditions for different types of read and write operations, which are discussed in the Write and Read Operations section. The general I<sup>2</sup>C protocol operates as follows:

1. The master initiates a data transfer by establishing a start condition, defined as a high-to-low transition on the serial data line, SDA, while the serial clock line, SCL, remains high. This indicates that a data stream is to follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next eight bits, consisting of a 7-bit slave address (MSB first) plus an  $R/\overline{W}$  bit that determines the direction of the data transfer, that is, whether data is written to or read from the slave device (0 = write, 1 = read).

The peripheral whose address corresponds to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the acknowledge bit, and holding it low during the high period of this clock pulse. All other devices on the bus now remain idle while the selected device waits for data to be read from it or written to it. If the  $R/\overline{W}$  bit is 0, the master writes to the slave device. If the  $R/\overline{W}$  bit is 1, the master reads from the slave device.

2. Data is sent over the serial bus in sequences of nine clock pulses: eight bits of data followed by an acknowledge bit from the slave device. Data transitions on the data line must occur during the low period of the clock signal and remain stable during the high period because a low-to-high transition when the clock is high can be interpreted as a stop signal.

If the operation is a write operation, the first data byte after the slave address is a command byte. This tells the slave device what to expect next. It can be an instruction, such as telling the slave device to expect a block write, or it can be a register address that tells the slave where subsequent data is to be written.

Because data can flow in only one direction, as defined by the  $R/\overline{W}$  bit, it is not possible to send a command to a slave device during a read operation. Before performing a read operation, it may be necessary to first execute a write operation to tell the slave what sort of read operation to expect and/or the address from which data is to be read.

3. When all data bytes are read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10<sup>th</sup> clock pulse to assert a stop condition. In read mode, the master device releases the SDA line during the SCL low period before the ninth clock pulse, but the slave device does not pull it low. This is known as a no acknowledge. The master then takes the data line low during the SCL low period before the 10<sup>th</sup> clock pulse, and then high during the 10<sup>th</sup> clock pulse to assert a stop condition.

Table 5. Setting I<sup>2</sup>C Addresses via the ADR Pin

| Base Address | ADR Pin State      | ADR Pin Logic State | Address in Binary <sup>1</sup> | Address in Hex |

|--------------|--------------------|---------------------|--------------------------------|----------------|

| 01011        | Ground             | 00                  | 0101100X                       | 0x58           |

|              | Resistor to ground | 01                  | 0101101X                       | 0x5A           |

|              | Floating           | 10                  | 0101110X                       | 0x5C           |

|              | High               | 11                  | 0101111X                       | 0x5E           |

$<sup>^{1}</sup>$  X = don't care.

Figure 18. General I<sup>2</sup>C Write Timing Diagram

Figure 19. General I<sup>2</sup>C Read Timing Diagram

Figure 20. Serial Bus Timing Diagram

# WRITE AND READ OPERATIONS

The  $\rm I^2C$  specification defines several protocols for different types of read and write operations. The operations used in the ADM1192 are discussed in this section. Table 6 shows the abbreviations used in the command diagrams (see Figure 21 to Figure 26).

Table 6. I<sup>2</sup>C Abbreviations

| Abbreviation | Condition      |

|--------------|----------------|

| S            | Start          |

| Р            | Stop<br>Read   |

| R            | Read           |

| W            | Write          |

| A            | Acknowledge    |

| N            | No acknowledge |

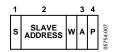

#### **QUICK COMMAND**

The quick command operation allows the master to check if the slave is present on the bus, as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address, followed by the write bit (low).

- 3. The addressed slave device asserts an acknowledge on SDA.

- The master asserts a stop condition on SDA to end the transaction.

Figure 21. Quick Command

#### **WRITE COMMAND BYTE**

In the write command byte operation, the master device sends a command byte to the slave device, as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address, followed by the write bit (low).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master sends the command byte. The command byte is identified by an MSB = 0. An MSB = 1 indicates an extended register write (see the Write Extended Command Byte section).

- 5. The slave asserts an acknowledge on SDA.

- 6. The master asserts a stop condition on SDA to end the transaction.

Figure 22. Write Command Byte

The seven LSBs of the command byte are used to configure and control the ADM1192. Table 7 provides details of the function of each bit.

**Table 7. Command Byte Operations**

| Bit | Default | Name           | Function                                                                                                                                                                                                                                                                                                          |

|-----|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C0  | 0       | V_CONT         | LSB, set to convert voltage continuously. If readback is attempted before the first conversion is complete, the ADM1192 asserts an acknowledge and returns all 0s in the returned data.                                                                                                                           |

| C1  | 0       | V_ONCE         | Set to convert voltage once. Self-clears. I <sup>2</sup> C asserts a no acknowledge on attempted reads until the ADC conversion is complete.                                                                                                                                                                      |

| C2  | 0       | I_CONT         | Set to convert current continuously. If readback is attempted before the first conversion is complete, the ADM1192 asserts an acknowledge and returns all 0s in the returned data.                                                                                                                                |

| C3  | 0       | I_ONCE         | Set to convert current once. Self-clears. I <sup>2</sup> C asserts a no acknowledge on attempted reads until the ADC conversion is complete.                                                                                                                                                                      |

| C4  | 0       | VRANGE         | Selects different internal attenuation resistor networks for voltage readback. A 0 in C4 selects a 14:1 voltage divider. A 1 in C4 selects a 7:2 voltage divider. With an ADC full scale of 1.902 V, the voltage at the VCC pin for an ADC full-scale result is 26.52 V for VRANGE = 0 and 6.65 V for VRANGE = 1. |

| C5  | 0       | Not applicable | Unused.                                                                                                                                                                                                                                                                                                           |

| C6  | 0       | STATUS_RD      | Status Read. When this bit is set, the data byte read back from the ADM1192 is the status byte. This contains the status of the device alerts. See Table 15 for full details of the status byte.                                                                                                                  |

#### WRITE EXTENDED COMMAND BYTE

In the write extended command byte operation, the master device writes to one of the three extended registers of the slave device, as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address, followed by the write bit (low).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master sends the register address byte. The MSB of this byte is set to 1 to indicate an extended register write. The two LSBs indicate which of the three extended registers are to be written to (see Table 8). All other bits should be set to 0.

- 5. The slave asserts an acknowledge on SDA.

- 6. The master sends the extended command byte (refer to Table 9, Table 10, and Table 11).

- 7. The slave asserts an acknowledge on SDA.

- 8. The master asserts a stop condition on SDA to end the transaction.

Figure 23. Write Extended Byte

Table 9, Table 10, and Table 11 provide the details of each extended register.

**Table 8. Extended Register Addresses**

|    |    |    | _  |    |    |    |                   |

|----|----|----|----|----|----|----|-------------------|

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | Extended Register |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | ALERT_EN          |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | ALERT_TH          |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | CONTROL           |

Table 9. ALERT\_EN Register Operations

| Bit | Default | Name         | Function                                                                                                                                                                                                                                                                          |

|-----|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0       | EN_ADC_OC1   | LSB, enabled if a single ADC conversion on the I channel exceeds the threshold set in the ALERT_TH register.                                                                                                                                                                      |

| 1   | 0       | EN_ADC_OC4   | Enabled if four consecutive ADC conversions on the I channel exceed the threshold set in the ALERT_TH register.                                                                                                                                                                   |

| 2   | 1       | EN_OC_ALERT  | Enables the OC_ALERT register. If an overcurrent condition is present compared to the SETV threshold, and the TIMER pin charges to 1.3 V, the OC_ALERT register captures and latches this condition.                                                                              |

| 3   | 0       | EN_OFF_ALERT | Enables an alert if the hot swap operation is turned off by an operation that writes the SWOFF bit high. This allows a software override of the ALERT output and turns on a P-channel FET controlled by ALERT.                                                                    |

| 4   | 0       | CLEAR        | Clears the OC_ALERT and ADC_ALERT status bits in the status register. The value of these bits can immediately change if the source of the alert is not cleared and the alert function is not disabled. The CLEAR bit self-clears to 0 after the STATUS register bits are cleared. |

#### Table 10. ALERT TH Register Operations

| Bit   | Default | Function                                                                                                              |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------|

| [7:0] | FF      | The ALERT_TH register sets the current level at which an alert occurs. Defaults to ADC full scale. The ALERT_TH 8-bit |

|       |         | value corresponds to the top eight bits of the current channel data.                                                  |

#### **Table 11. CONTROL Register Operations**

| Bit | Default | Name  | Function                                                                                                 |

|-----|---------|-------|----------------------------------------------------------------------------------------------------------|

| 0   | 0       | SWOFF | LSB, forces the ALERT pin to deassert. Can be active only if the EN_OFF_ALERT bit is high (see Table 9). |

#### **READ VOLTAGE AND/OR CURRENT DATA BYTES**

Depending on how the device is configured, the ADM1192 can be set up to provide information in three ways after a conversion (or conversions): voltage and current readback, voltage only readback, and current only read back. See the Write Command Byte section for more details.

#### **Voltage and Current Readback**

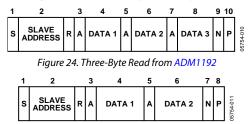

The ADM1192 digitizes both voltage and current. Three bytes are read back in the format shown in Table 12.

Table 12. Voltage and Current Readback Format

| Byte | Contents        | B7  | B6  | B5 | B4 | В3 | B2 | B1 | BO |

|------|-----------------|-----|-----|----|----|----|----|----|----|

| 1    | Voltage<br>MSBs | V11 | V10 | V9 | V8 | V7 | V6 | V5 | V4 |

| 2    | Current<br>MSBs | I11 | I10 | 19 | 18 | 17 | 16 | 15 | 14 |

| 3    | LSBs            | V3  | V2  | V1 | V0 | 13 | 12 | l1 | 10 |

#### Voltage Readback

The ADM1192 digitizes voltage only. Two bytes are read back in the format shown in Table 13.

Table 13. Voltage Only Readback Format

| Byte Contents |              | В7  | B6  | B5 | В4 | В3 | B2 | B1 | B0 |

|---------------|--------------|-----|-----|----|----|----|----|----|----|

| 1             | Voltage MSBs | V11 | V10 | V9 | V8 | V7 | V6 | V5 | V4 |

| 2             | Voltage LSBs | V3  | V2  | V1 | V0 | 0  | 0  | 0  | 0  |

#### **Current Readback**

The ADM1192 digitizes current only. Two bytes are read back in the format shown in Table 14.

Table 14. Current Only Readback Format

| Byte | Contents     | B7  | B6  | B5 | B4 | В3 | B2 | В1 | ВО |

|------|--------------|-----|-----|----|----|----|----|----|----|

| 1    | Current MSBs | l11 | l10 | 19 | 18 | 17 | 16 | 15 | 14 |

| 2    | Current LSBs | 13  | 12  | l1 | 10 | 0  | 0  | 0  | 0  |

The following series of events occurs when the master receives three bytes (voltage and current data) from the slave device:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address, followed by the read bit (high).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master receives the first data byte.

- 5. The master asserts an acknowledge on SDA.

- 6. The master receives the second data byte.

- 7. The master asserts an acknowledge on SDA.

- 8. The master receives the third data byte.

- 9. The master asserts a no acknowledge on SDA.

- The master asserts a stop condition on SDA, and the transaction ends.

For cases where the master is reading voltage only or current only, two data bytes are read and Step 7 and Step 8 are not required.

Figure 25. Two-Byte Read from ADM1192

#### **Converting ADC Codes to Voltage and Current Readings**

Equation 1 and Equation 2 can be used to convert ADC codes representing voltage and current from the ADM1175 12-bit ADC into actual voltage and current values.

$$Voltage = (V_{FULLSCALE}/4096) \times Code \tag{1}$$

where

$V_{FULLSCALE}$  = 6.65 V (7:2 range) or 26.52 V (14:1 range). *Code* is the ADC voltage code read from the device (Bit V11 to Bit V0).

$$Current = ((I_{FULLSCALE}/4096) \times Code)/Sense Resistor$$

(2)

where.

$I_{FULLSCALE} = 105.84 \text{ mV}.$

*Code* is the ADC current code read from the device (Bit I11 to Bit I0).

#### **Read Status Register**

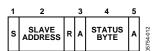

A single register of status data can also be read from the ADM1192 as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address, followed by the read bit (high).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master receives the status byte.

- 5. The master asserts an acknowledge on SDA.

Figure 26. Status Read from ADM1192

Table 15 shows the ADM1192 STATUS registers in detail. Note that Bit 1, Bit 3, and Bit 5 are cleared by writing to Bit 4 (the CLEAR bit) of the ALERT\_EN register.

### **Table 15. Status Byte Operations**

| Bit | Name       | Function                                                                                                                                                                                       |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | ADC_OC     | An ADC-based overcurrent comparison has been detected on the last three conversions.                                                                                                           |

| 1   | ADC_ALERT  | An ADC-based overcurrent trip has occurred, causing the alert. Cleared by writing to Bit 4 of the ALERT_EN register.                                                                           |

| 2   | OC         | An overcurrent condition is present (that is, the output of the current sense amplifier is greater than the voltage on the SETV input).                                                        |

| 3   | OC_ALERT   | An overcurrent condition has caused the ALERT block to latch a fault, and the ALERT output has asserted. Cleared by writing to Bit 4 of the ALERT_EN register or by toggling the CLRB pin low. |

| 4   | OFF_STATUS | Set to 1 by writing to the SWOFF bit of the CONTROL register.                                                                                                                                  |

| 5   | OFF_ALERT  | An alert has been caused by the SWOFF bit. Cleared by writing to Bit 4 of the ALERT_EN register.                                                                                               |

# APPLICATIONS INFORMATION ALERT OUTPUT

The ALERT output is an open-drain pin with 30 V tolerance. There are two uses for this output.

#### **Overcurrent Flag**

The ALERT pin can be connected to the general-purpose logic input of a controller. During normal operation, the ADM1192 drives this output low. When an overcurrent condition occurs, the output asserts high. An external pull-up resistor should be used. This pin is configured by default to trigger the SETV threshold at power-up.

Figure 27. Using the ALERT Output as an Interrupt

#### Implementing a Basic Hot Swap Circuit

A basic P-channel FET hot swap circuit can be created. The ALERT output should be connected to the GATE pin of a P-channel FET connected in series with the power path. A pull-up from GATE to source ensures that the P-channel FET GATE is pulled up and the device held off as soon as power is applied. When the ADM1192 powers up, the GATE is pulled low by the ALERT output. A capacitor on the ALERT pin determines the slew rate of the GATE pin at startup. Note that, if a current fault occurs during the operation, the ALERT output asserts high, turning off the P-channel FET.

Figure 28. P-Channel FET Hot Swap Implementation

#### **SETV PIN**

The SETV pin allows the user to adjust the current level that trips the ALERT output. The output of the current sense amplifier is compared with the voltage driven onto the SETV pin. If the current sense amplifier output is higher than the SETV voltage, the output of the comparator asserts. By driving a different voltage onto the SETV pin, the ADM1192 detects an overcurrent condition at a different current level, with a gain of 18. The 100 mV ADC full-scale sense voltage corresponds to 1.8 V on the SETV pin. See Figure 12 for an illustration of this relationship.

Figure 29. SETV Operation

When the output of the SETV comparator asserts, this tells the ALERT block to begin charging the external TIMER capacitor with a 62  $\mu A$  charging current. When the voltage on the TIMER capacitor reaches 1.3 V, the charging cycle is complete. The ALERT output then asserts (goes high). Different values of TIMER capacitor generate different time delays between current faults occurring and the ALERT output asserting. When using the ALERT output to implement a hot swap circuit, the TIMER capacitor should be chosen to generate a large enough startup delay to allow the maximum inrush current to completely charge up the load without tripping an ALERT fault.

#### **KELVIN SENSE RESISTOR CONNECTION**

When using a low value sense resistor for high current measurement, the problem of parasitic series resistance can arise. The pad and solder resistance can be a substantial fraction of the rated resistance, making the total resistance larger than expected.

This error problem can be largely avoided by using a Kelvin sense connection. This type of connection separates the high current path through the resistor and the voltage drop across the resistor. A four pad resistor may be used or a split pad layout can be used with a two pad sense resistor to achieve Kelvin sensing.

# **OUTLINE DIMENSIONS**

Figure 30. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option | Branding |  |

|--------------------|-------------------|---------------------|----------------|----------|--|

| ADM1192-1ARMZ-R7   | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | M5M      |  |

| EVAL-ADM1192EBZ    |                   | Evaluation Board    |                |          |  |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

# **NOTES**

# NOTES

**NOTES**

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331