# 128, 256, 512 and 1024 Channel CESoP Processors

**Data Sheet**

April 2008

Features

#### General

- Circuit Emulation Services over Packet (CESoP) transport for MPLS, IP and Ethernet networks

- On chip timing & synchronization recovery across a packet network

- Grooming capability for Nx64 Kbps trunking

#### **Circuit Emulation Services**

- Supports ITU-T Recommendation Y.1413 and Y.1453

- Supports IETF RFC4553 and RFC5086

- Supports MEF8 and MFA 8.0.0

- Structured, synchronous CESoP with clock recovery

- Unstructured, asynchronous CESoP, with integral per stream clock recovery

#### **TDM Interfaces**

- Up to 32 T1/E1, 8 J2, or 2 T3/E3 ports

- H.110, H-MVIP, ST-BUS backplanes

- Up to 1024 bi-directional 64 Kbps channels

### **Ordering Information**

#### -40°C to +85°C

- Direct connection to LIUs, framers, backplanes

- Dual reference Stratum 4 and 4E DPLL for synchronous operation

#### **Network Interfaces**

Up to 3 x 100 Mbps MII Fast Ethernet or Dual Redundant 1000 Mbps GMII/TBI Ethernet Interfaces

#### **System Interfaces**

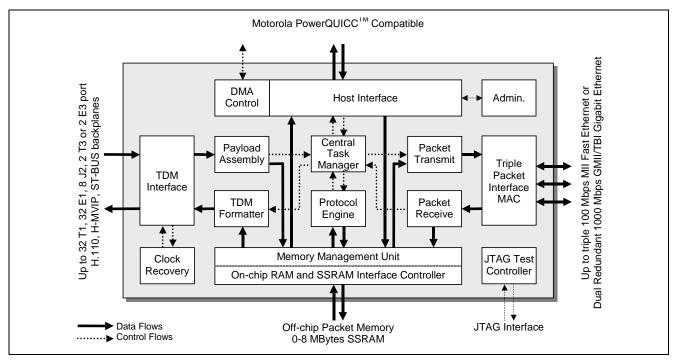

- Flexible 32 bit host CPU interface (Motorola PowerQUICC<sup>™</sup> compatible)

- On-chip packet memory for self-contained operation, with buffer depths of over 16 ms

- Up to 8 Mbytes of off-chip packet memory, supporting buffer depths of over 128 ms

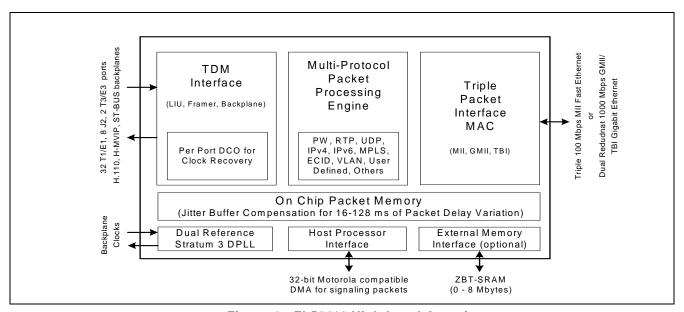

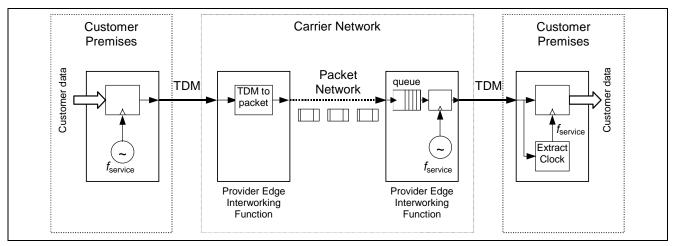

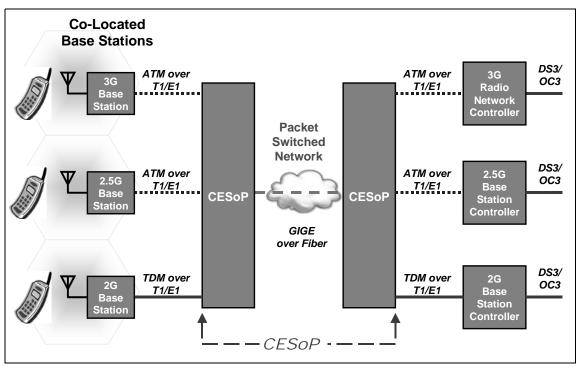

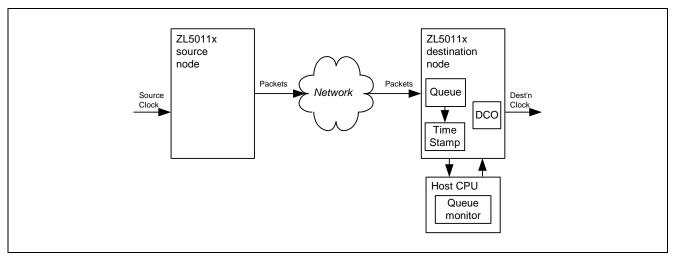

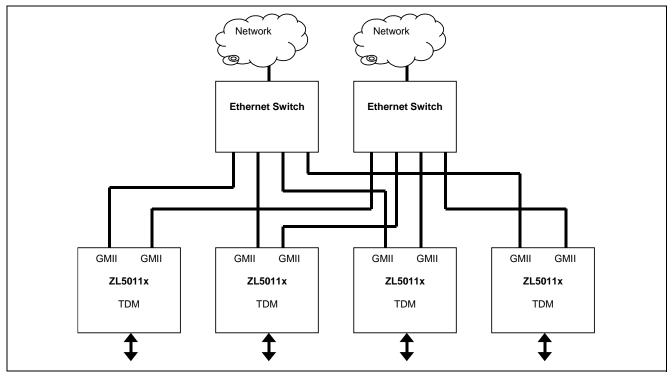

Figure 1 - ZL50111 High Level Overview

### **Packet Processing Functions**

- Flexible, multi-protocol packet encapsulation including support for IPv4, IPv6, RTP, MPLS, L2TPv3, ITU-T Y.1413, RFC4553, RFC5086 and user programmable

- · Packet re-sequencing to allow lost packet detection

- Four classes of service with programmable priority mechanisms (WFQ and SP) using egress queues

- Flexible classification of incoming packets at layers 2, 3, 4 and 5

- Supports up to 128 separate CESoP connections across the Packet Switched Network

### **Applications**

- Circuit Emulation Services over Packet Networks

- · Leased Line support over packet networks

- Multi-Tenant Unit access concentration

- TDM over Cable

- Fibre To The Premises G/E-PON

- · Layer 2 VPN services

- · Customer-premise and Provider Edge Routers and Switches

- Packet switched backplane applications

### **Description**

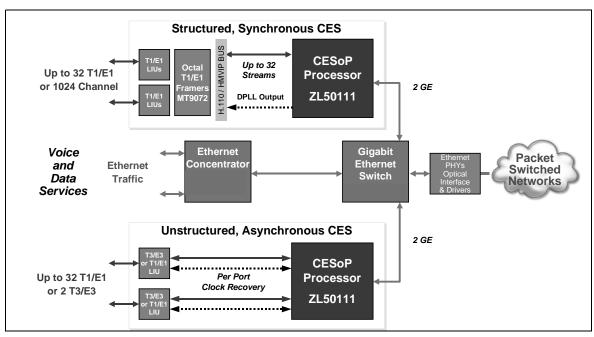

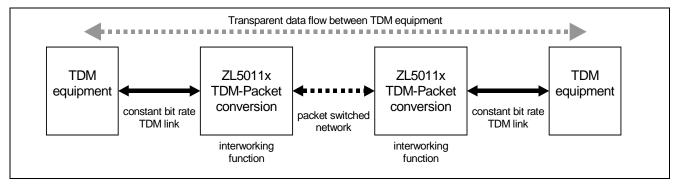

The ZL50110/11/12/14 family of CESoP processors are highly functional TDM to Packet bridging devices. The ZL50110/11/12/14 provides both structured and unstructured circuit emulation services over packet (CESoP) for up to 32 T1, 32 E1 and 8 J2 streams across a packet network based on MPLS, IP or Ethernet. The ZL50111 also supports unstructured T3 and E3 streams.

The circuit emulation features in the ZL50110/11/12/14 family supports the ITU Recommendations Y.1413 and Y.1453, as well as the CESoP standards from the Metro Ethernet Forum (MEF)-and MPLS and Frame Relay Alliance. The ZL50110/11/14 also supports IETF RFC4553 and RFC5086.

The ZL50110/11/12/14 provides up to triple 100 Mbps MII ports or dual redundant 1000 Mbps GMII/TBI ports.

The ZL50110/11/12/14 incorporates a range of powerful clock recovery mechanisms for each TDM stream, allowing the frequency of the source clock to be faithfully generated at the destination, enabling greater system performance and quality. Timing is carried using RTP or similar protocols, and both adaptive and differential clock recovery schemes are included, allowing the customer to choose the correct scheme for the application. An externally supplied clock may also be used to drive the TDM interface of the ZL50110/11/12/14.

The ZL50110/11/12/14 incur very low latency for the data flow, thereby increasing QoS when carrying voice services across the Packet Switched Network. Voice, when carried using CESoP, which typically has latencies of less than 10 ms, does not require expensive processing such as compression and echo cancellation.

The ZL50110/11/12/14 is capable of assembling user-defined packets of TDM traffic from the TDM interface and transmitting them out the packet interfaces using a variety of protocols. The ZL50110/11/12/14 supports a range of different packet switched networks, including Ethernet VLANs, IP and MPLS.

The ZL50110/11/12/14 can support up to 4 protocol stacks at the same time, provided that each protocol stack can be uniquely identified by a mask & match approach.

Packets received from the packet interfaces are parsed to determine the egress destination, and are appropriately queued to the TDM interface, they can also be forwarded to the host interface, or back toward the packet interface. Packets queued to the TDM interface can be re-ordered based on sequence number, and lost packets filled in to maintain timing integrity.

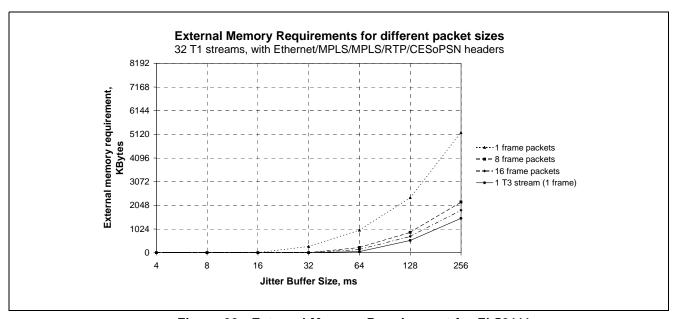

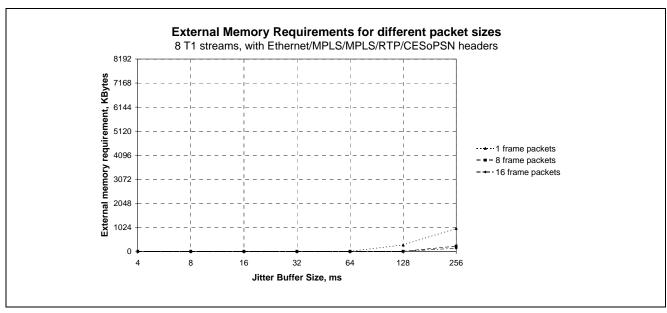

The ZL50110/11/12/14 family includes sufficient on-chip memory that external memory is not required in most applications. This reduces system costs and simplifies the design. For applications that do require more memory (e.g., high stream count or high latency), the device supports up to 8 Mbytes of SSRAM.

A comprehensive evaluation system is available upon request from your local Zarlink representative or distributor. This system includes the CESoP processor, various TDM interfaces and a fully featured evaluation software GUI that runs on a Windows PC.

### **Device Line Up**

There are four products within the ZL50110/11/12/14 family, with capacity as shown in the following table:

| Device  | TDM Interfaces                                                                                                                         | Ethernet Packet I/F                                                                                                    | Notes  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------|

| ZL50114 | 4 T1, 4 E1, or 1 J2 streams or<br>4 MVIP/ST-BUS streams at 2.048 Mbps or<br>1 H.110/H-MVIP/ST-BUS streams at<br>8.192 Mbps             | Dual 100 Mbps MII or<br>Dual Redundant 1000 Mbps GMII/TBI                                                              | Note 1 |

| ZL50110 | 8 T1, 8 E1 or 2 J2 streams or<br>8 MVIP/ST-BUS streams at 2.048 Mbps or<br>2 H.110/H-MVIP/ST-BUS streams at<br>8.192 Mbps              | Dual 100 Mbps MII or<br>Dual Redundant 1000 Mbps GMII/TBI                                                              | Note 1 |

| ZL50112 | 16 T1, 16 E1, 4 J2 streams or<br>16 MVIP/ST-BUS streams at 2.048 Mbps or<br>4 H.110/H-MVIP/ST-BUS streams at<br>8.192 Mbps             | Triple 100 Mbps MII or<br>Dual Redundant 1000 Mbps GMII/TBI<br>or Single 100 Mbps MII and Single<br>1000 Mbps GMII/TBI | Note 1 |

| ZL50111 | 32 T1, 32 E1, 8 J2, 2 T3, 2 E3 streams or<br>32 MVIP/ST-BUS streams at 2.048 Mbps or<br>8 H.110/H-MVIP/ST-BUS streams at<br>8.192 Mbps | Triple 100 Mbps MII or<br>Dual Redundant 1000 Mbps GMII/TBI<br>or Single 100 Mbps MII and Single<br>1000 Mbps GMII/TBI | Note 1 |

Table 1 - Capacity of Devices in the ZL50110/11/14 Family

Note 1: T1/E1/J2 is for unstructured mode, and the H-MVIP/H.110/ST-BUS is for structured mode.

### **Table of Contents**

| 1 0        | Changes Summary                                                   | 11   |

|------------|-------------------------------------------------------------------|------|

|            | Physical Specification                                            |      |

|            | ·                                                                 |      |

| 3.0        | External Interface Description                                    |      |

|            | 3.1 TDM Interface                                                 |      |

|            |                                                                   |      |

|            | 3.1.2 ZL50112 Variant TDM Stream Connection                       |      |

|            | 3.1.4 ZL50110 Variant TDM Stream Connection                       |      |

|            | 3.1.5 TDM Signals Common to ZL50110, ZL50111, ZL50112 and ZL50114 |      |

|            | 3.2 PAC Interface                                                 |      |

|            | 3.3 Packet Interfaces                                             |      |

|            | 3.4 External Memory Interface                                     |      |

|            | 3.5 CPU Interface                                                 |      |

|            | 3.6 System Function Interface                                     |      |

|            | 3.7 Test Facilities                                               |      |

|            | 3.7.1 Administration, Control and Test Interface                  |      |

|            | 3.7.2 JTAG Interface                                              |      |

|            | 3.8 Miscellaneous Inputs.                                         |      |

|            | 3.9 Power and Ground Connections                                  |      |

|            | 3.10 ZL50111, ZL50112, ZL50110 and ZA50114 Internal Connections   |      |

|            | 3.11 ZL50112 Internal Connections                                 |      |

|            | 3.12 ZL50112 Auxiliary Clocks                                     |      |

| <b>4</b> 0 | Typical Applications                                              |      |

|            | 4.1 Leased Line Provision                                         |      |

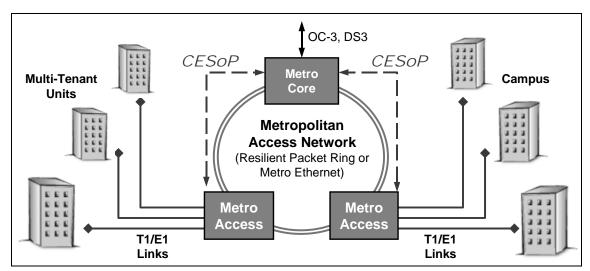

|            | 4.2 Metropolitan Area Network Aggregation                         |      |

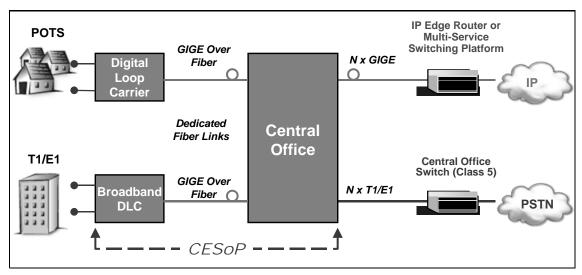

|            | 4.3 Digital Loop Carrier                                          |      |

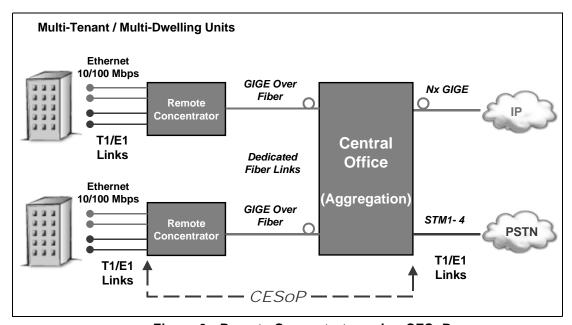

|            | 4.4 Remote Concentrator                                           |      |

|            | 4.5 Cell Site Backhaul                                            |      |

|            | 4.6 Equipment Architecture Example                                |      |

| 5.0        | Functional Description                                            |      |

|            | 5.1 Block Diagram                                                 |      |

|            | 5.2 Data and Control Flows.                                       |      |

|            | 5.3 TDM Interface                                                 |      |

|            | 5.3.1 TDM Interface Block.                                        |      |

|            | 5.3.2 Structured TDM Port Data Formats                            |      |

|            | 5.3.3 TDM Clock Structure                                         |      |

|            | 5.3.3.1 Synchronous TDM Clock Generation                          | . 60 |

|            | 5.3.3.2 Asynchronous TDM Clock Generation                         | . 60 |

|            | 5.4 Payload Assembly                                              |      |

|            | 5.4.1 Structured Payload Operation                                |      |

|            | 5.4.1.1 Structured Payload Order                                  |      |

|            | 5.4.2 Unstructured Payload Operation                              | . 62 |

|            | 5.5 Protocol Engine                                               | . 63 |

|            | 5.6 Packet Transmission                                           |      |

|            | 5.7 Packet Reception                                              |      |

|            | 5.8 TDM Formatter                                                 | . 63 |

| 6.0        | Clock Recovery                                                    | . 64 |

|            | 6.1 Differential Clock Recovery                                   |      |

|            | 6.2 Adaptive Clock Recovery                                       |      |

|            | 6.3 SYSTEM_CLK Considerations                                     |      |

| 7.0        | System Features                                                   | . 67 |

|            | -                                                                 |      |

## **Table of Contents**

| 7.1 Latency                                       | 67 |

|---------------------------------------------------|----|

| 7.2 Loopback Modes                                | 67 |

| 7.3 Host Packet Generation                        | 67 |

| 7.4 Loss of Service (LOS)                         |    |

| 7.5 External Memory Requirement                   | 68 |

| 7.6 GIGABIT Ethernet - Recommended Configurations |    |

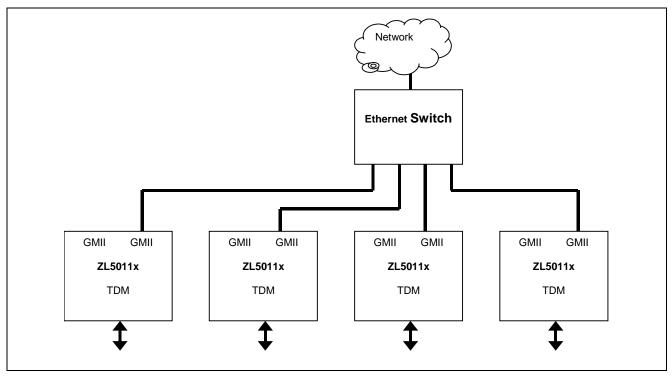

| 7.6.1 Central Ethernet Switch                     |    |

| 7.6.2 Redundant Ethernet Switch                   |    |

| 7.7 Power Up sequence                             | 71 |

| 7.8 JTAG Interface and Board Level Test Features  |    |

| 7.9 External Component Requirements               |    |

| 7.9.1 Host Processor                              |    |

| 7.9.2 Other components                            |    |

| 7.10 Miscellaneous Features                       |    |

| 7.11 Test Modes Operation                         |    |

| 7.11.1 Overview                                   |    |

| 7.11.1.1 System Normal Mode                       |    |

| 7.11.1.2 System Tri-State Mode                    |    |

| 7.11.2 Test Mode Control                          |    |

| 7.11.3 System Normal Mode                         |    |

| 7.11.4 System Tri-state Mode                      |    |

| 8.0 DPLL Specification                            |    |

| 8.1 Modes of Operation                            |    |

| 8.1.1 Locking Mode (normal operation)             | 74 |

| 8.1.2 Holdover Mode                               |    |

| 8.1.3 Freerun Mode                                |    |

| 8.1.4 Powerdown Mode                              |    |

| 8.2 Reference Monitor Circuit                     |    |

| 8.3 Locking Mode Reference Switching              |    |

| 8.4 Locking Range                                 |    |

| 8.5 Locking Time                                  |    |

| 8.6 Lock Status                                   |    |

| 8.7 Jitter                                        |    |

| 8.7.1 Acceptance of Input Wander                  |    |

| 8.7.2 Intrinsic Jitter                            |    |

| 8.7.3 Jitter Tolerance                            |    |

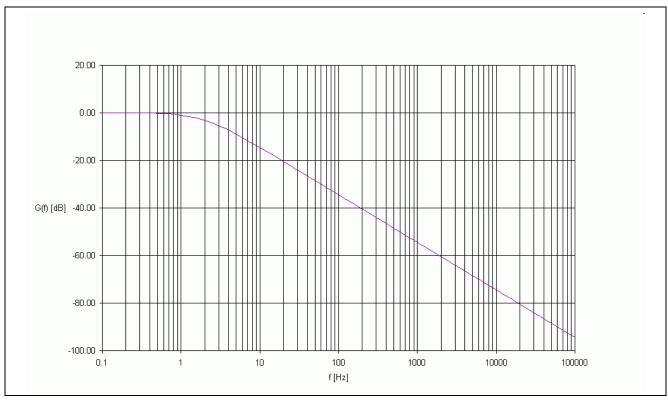

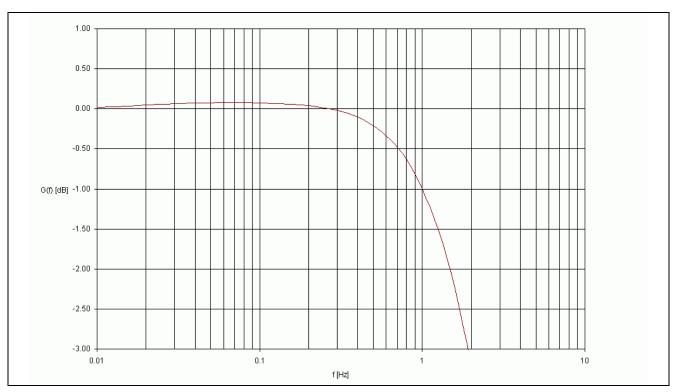

| 8.7.4 Jitter Transfer                             |    |

| 8.8 Maximum Time Interval Error (MTIE)            |    |

| 9.0 Memory Map and Register Definitions           | 79 |

| 10.0 DC Characteristics                           | 80 |

| 11.0 AC Characteristics                           | 82 |

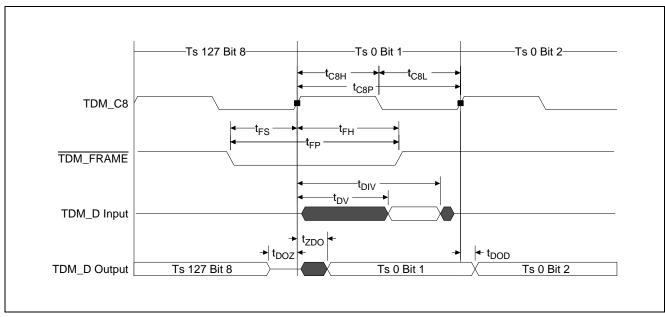

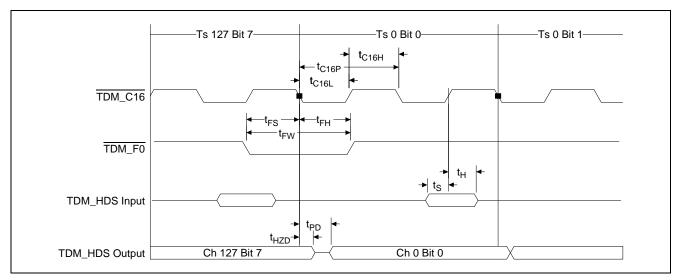

| 11.1 TDM Interface Timing - ST-BUS                | 82 |

| 11.1.1 ST-BUS Slave Clock Mode                    |    |

| 11.1.2 ST-BUS Master Clock Mode                   | 84 |

| 11.2 TDM Interface Timing - H.110 Mode            | 85 |

| 11.3 TDM Interface Timing - H-MVIP                | 86 |

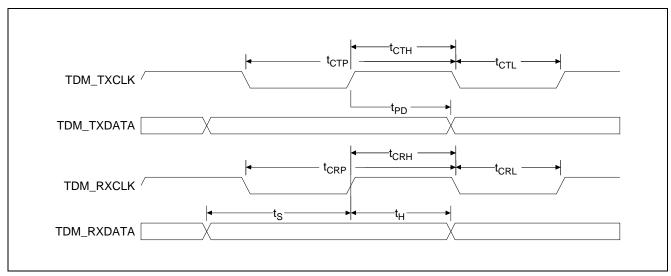

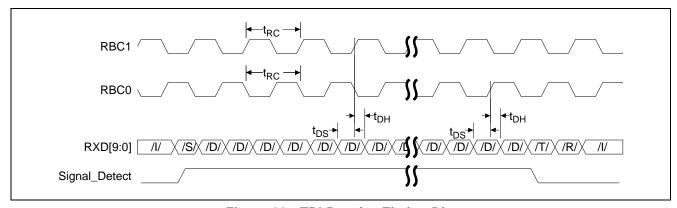

| 11.4 TDM LIU Interface Timing                     | 87 |

| 11.5 PAC Interface Timing                         | 88 |

| 11.6 Packet Interface Timing                      | 88 |

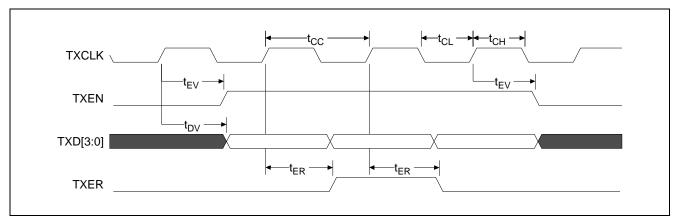

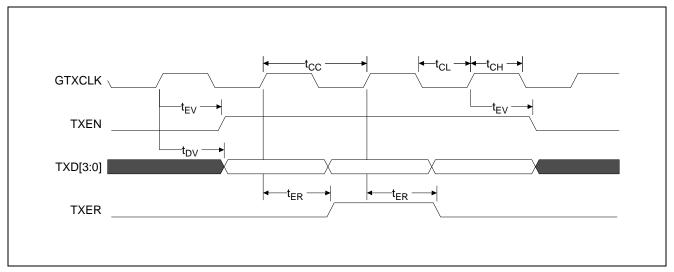

| 11.6.1 MII Transmit Timing                        | 88 |

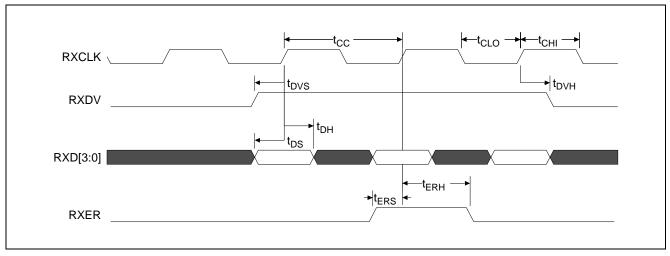

| 11.6.2 MII Receive Timing                         |    |

| 11.6.3 GMII Transmit Timing                       | 91 |

|                                                   |    |

## **Table of Contents**

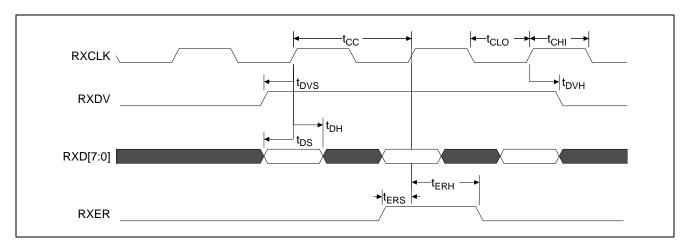

| 11.6.4 GMII Receive Timing                                              | 92  |

|-------------------------------------------------------------------------|-----|

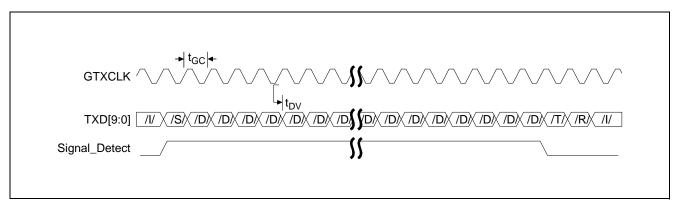

| 11.6.5 TBI Interface Timing                                             |     |

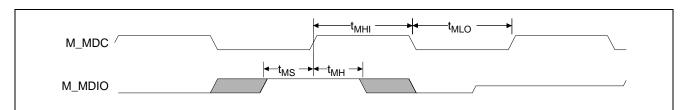

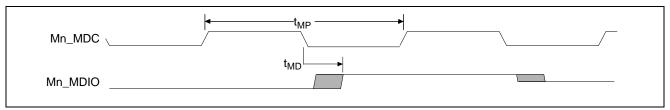

| 11.6.6 Management Interface Timing                                      |     |

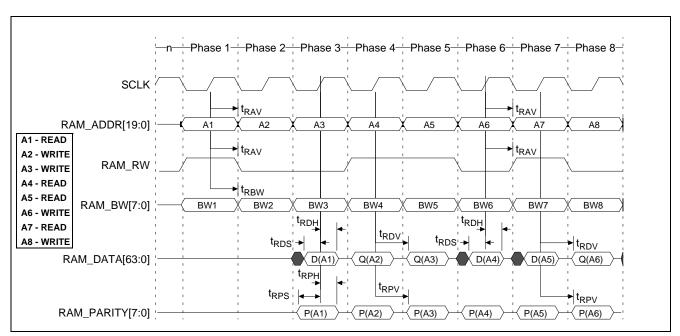

| 11.7 External Memory Interface Timing                                   | 95  |

| 11.8 CPU Interface Timing                                               | 96  |

| 11.9 System Function Port                                               |     |

| 11.10 JTAG Interface Timing                                             | 100 |

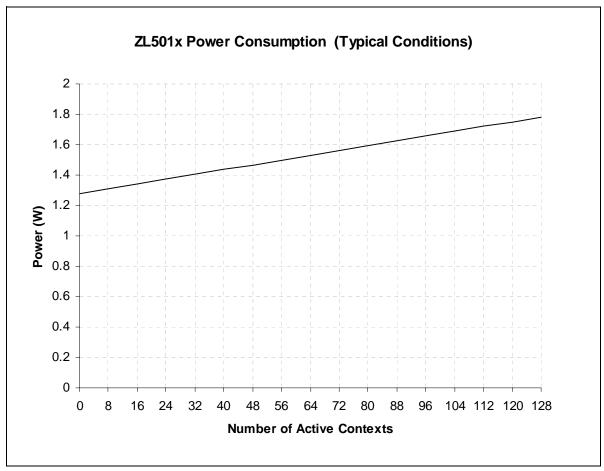

| 12.0 Power Characteristics                                              | 102 |

| 13.0 Design and Layout Guidelines                                       | 103 |

| 13.1 High Speed Clock & Data Interfaces                                 |     |

| 13.1.1 External Memory Interface - special considerations during layout | 104 |

| 13.1.2 GMAC Interface - special considerations during layout            | 104 |

| 13.1.3 TDM Interface - special considerations during layout             | 104 |

| 13.1.4 Summary                                                          | 104 |

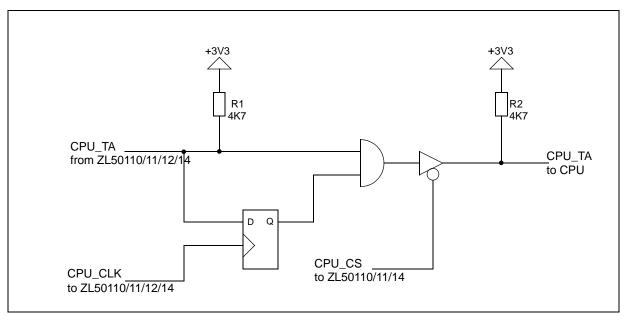

| 13.2 CPU TA Output                                                      | 104 |

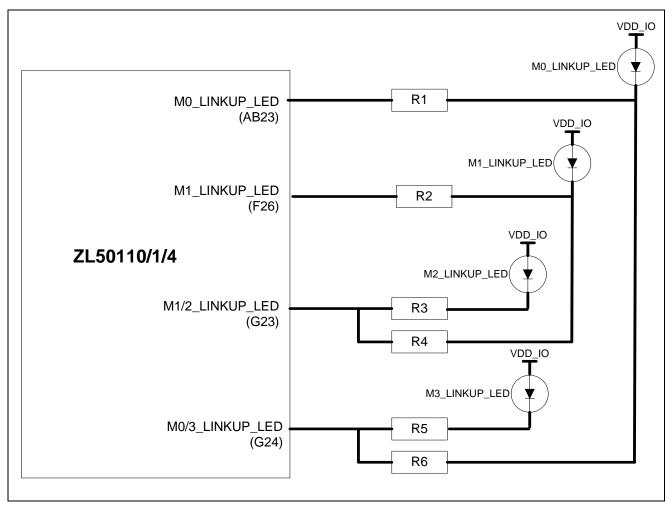

| 13.3 Mx_LINKUP_LED Outputs                                              | 105 |

| 14.0 Reference Documents                                                | 108 |

| 14.1 External Standards/Specifications                                  | 108 |

| 14.2 Zarlink Standards                                                  |     |

| 15 0 Glossary                                                           | 100 |

## **List of Figures**

| Figure 1 - ZL50111 High Level Overview                                | 1   |

|-----------------------------------------------------------------------|-----|

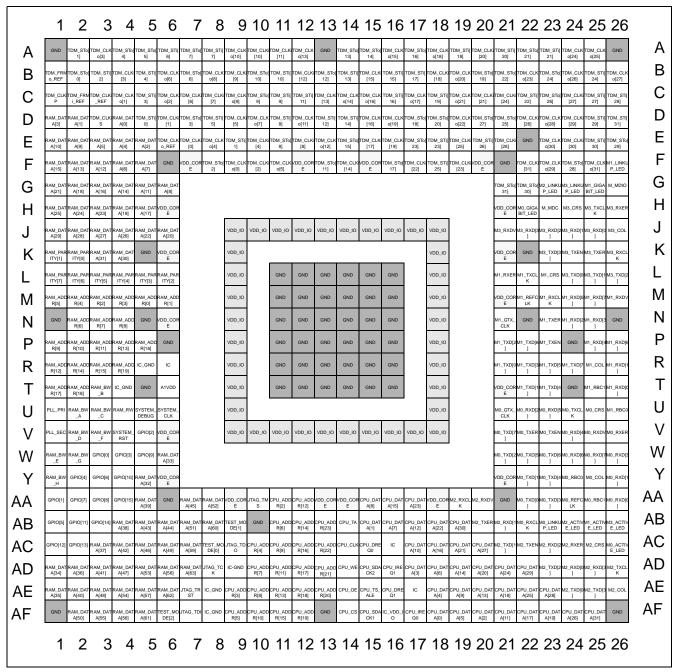

| Figure 2 - ZL50111 Package View and Ball Positions                    | 14  |

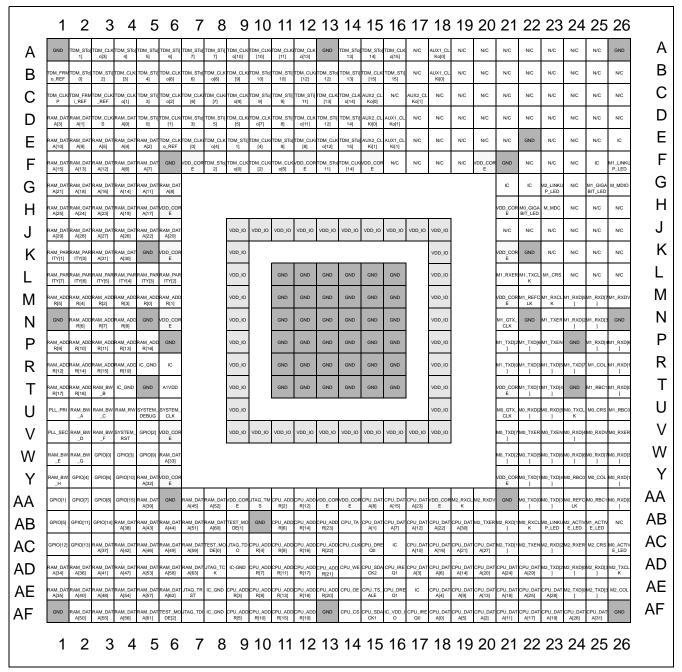

| Figure 3 - ZL50112 Package View and Ball Positions                    | 15  |

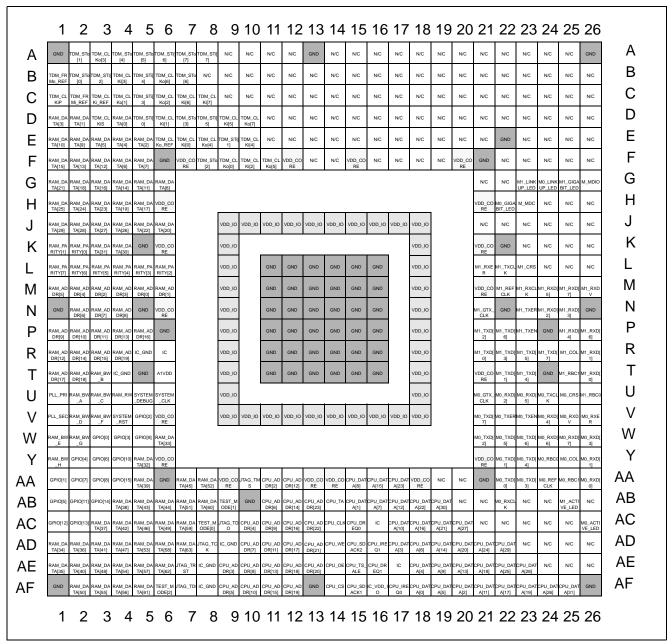

| Figure 4 - ZL50110 Package View and Ball Positions                    | 16  |

| Figure 5 - ZL50114 Package View and Ball Positions                    | 17  |

| Figure 6 - Leased Line Services Over a Circuit Emulation Link         | 51  |

| Figure 7 - Metropolitan Area Network Aggregation using CESoP          | 51  |

| Figure 8 - Digital Loop Carrier using CESoP                           | 52  |

| Figure 9 - Remote Concentrator using CESoP                            | 53  |

| Figure 10 - Cell Site Backhaul using CESoP                            | 54  |

| Figure 11 - Equipment example using CESoP                             | 55  |

| Figure 12 - ZL50110/11/12/14 Family Operation                         |     |

| Figure 13 - ZL50110/11/12/14 Data and Control Flows                   | 56  |

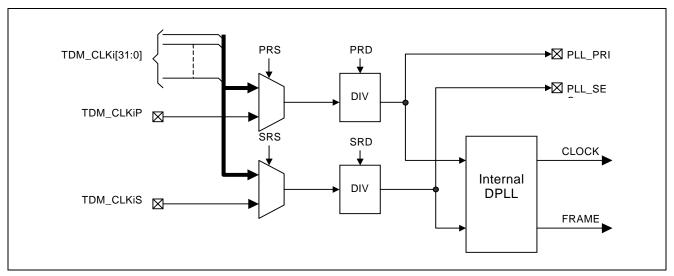

| Figure 14 - Synchronous TDM Clock Generation                          |     |

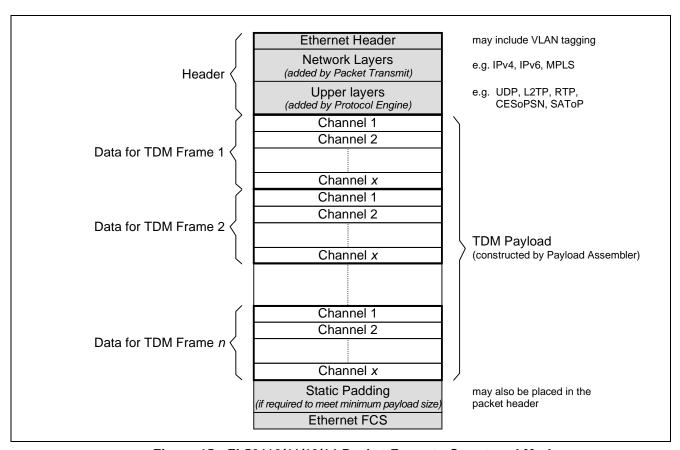

| Figure 15 - ZL50110/11/12/14 Packet Format - Structured Mode          |     |

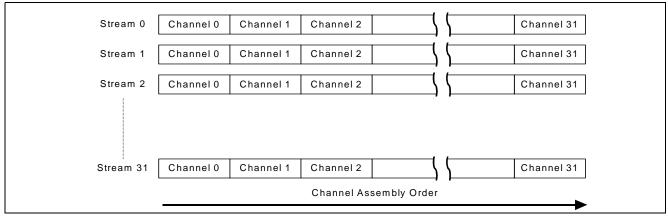

| Figure 16 - Channel Order for Packet Formation                        | 62  |

| Figure 17 - ZL50110/11/12/14 Packet Format - Unstructured Mode        | 62  |

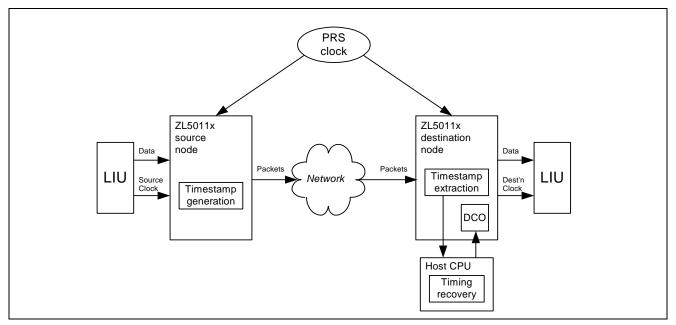

| Figure 18 - Differential Clock Recovery                               | 65  |

| Figure 19 - Adaptive Clock Recovery                                   |     |

| Figure 20 - External Memory Requirement for ZL50111                   |     |

| Figure 21 - External Memory Requirement for ZL50110                   |     |

| Figure 22 - Gigabit Ethernet Connection - Central Ethernet Switch     |     |

| Figure 23 - Gigabit Ethernet Connection - Redundant Ethernet Switch   |     |

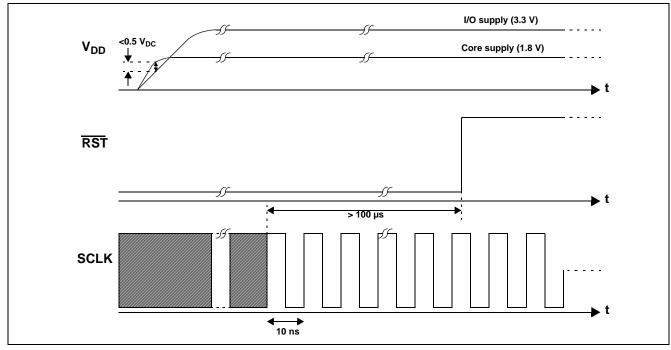

| Figure 24 - Powering Up the ZL50110/11/12/14                          |     |

| Figure 25 - Jitter Transfer Function                                  |     |

| Figure 26 - Jitter Transfer Function - Detail                         |     |

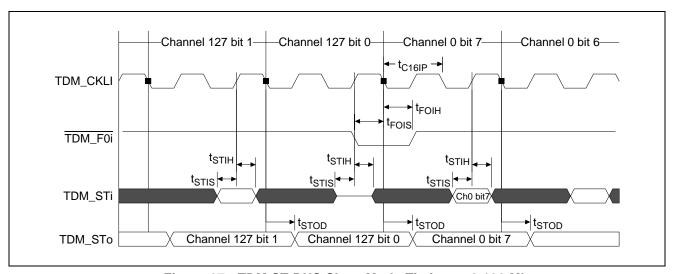

| Figure 27 - TDM ST-BUS Slave Mode Timing at 8.192 Mbps                |     |

| Figure 28 - TDM ST-BUS Slave Mode Timing at 2.048 Mbps                |     |

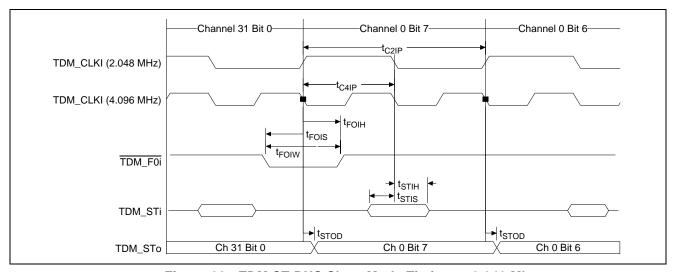

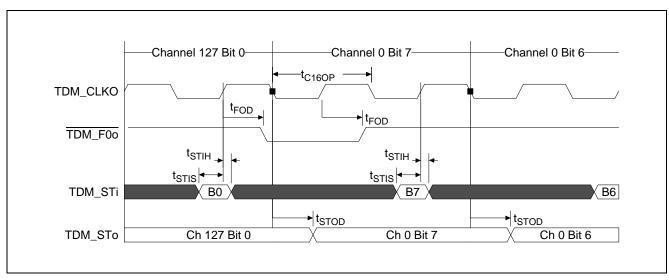

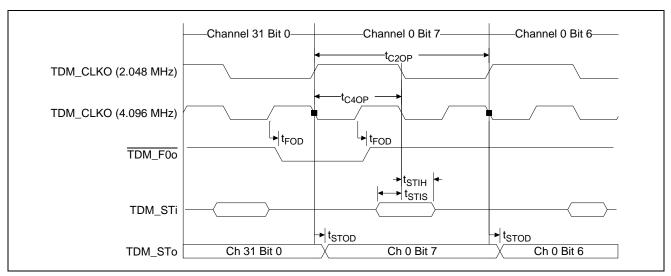

| Figure 29 - TDM Bus Master Mode Timing at 8.192 Mbps                  |     |

| Figure 30 - TDM Bus Master Mode Timing at 2.048 Mbps                  |     |

| Figure 31 - H.110 Timing Diagram                                      |     |

| Figure 32 - TDM - H-MVIP Timing Diagram for 16 MHz Clock (8.192 Mbps) |     |

| Figure 33 - TDM-LIU Structured Transmission/Reception                 |     |

| Figure 34 - MII Transmit Timing Diagram                               |     |

| Figure 35 - MII Receive Timing Diagram                                |     |

| Figure 36 - GMII Transmit Timing Diagram                              |     |

| Figure 37 - GMII Receive Timing Diagram                               |     |

| Figure 38 - TBI Transmit Timing Diagram                               |     |

| Figure 39 - TBI Receive Timing Diagram                                |     |

| Figure 40 - Management Interface Timing for Ethernet Port - Read      |     |

| Figure 41 - Management Interface Timing for Ethernet Port - Write     |     |

| Figure 42 - External RAM Read and Write Timing                        |     |

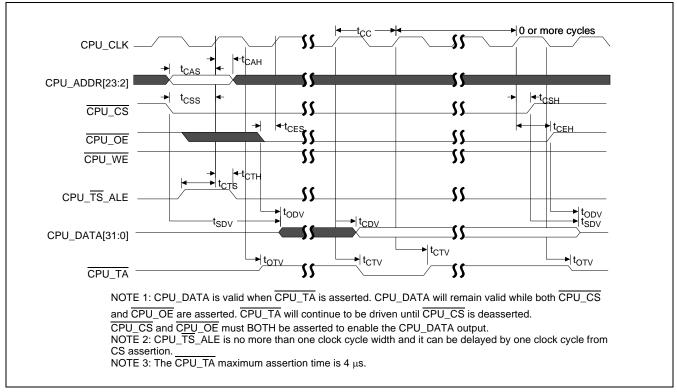

| Figure 43 - CPU Read - MPC8260                                        |     |

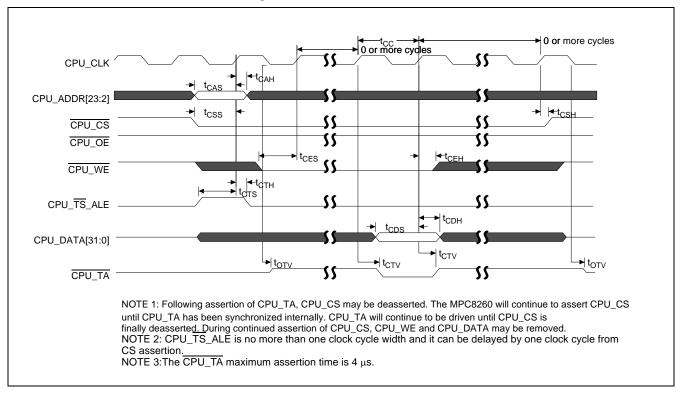

| Figure 44 - CPU Write - MPC8260                                       |     |

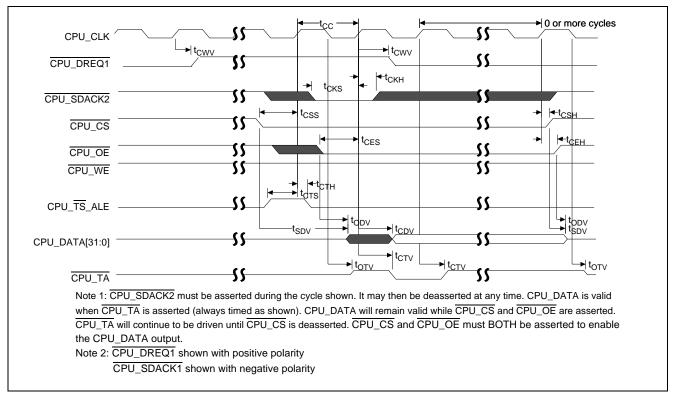

| Figure 45 - CPU DMA Read - MPC8260                                    |     |

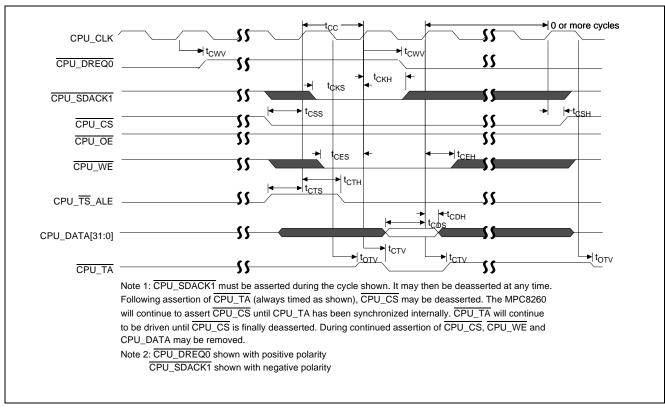

| Figure 46 - CPU DMA Write - MPC8260                                   |     |

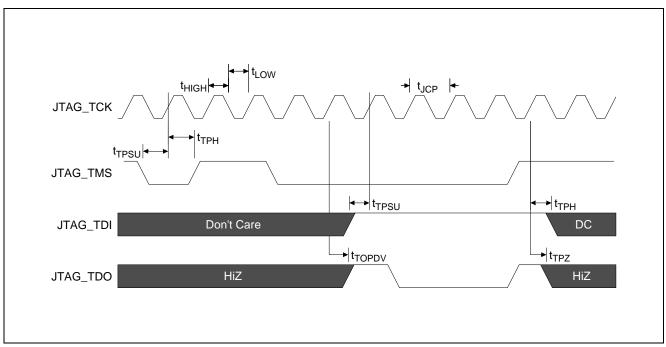

| Figure 47 - JTAG Signal Timing                                        |     |

| Figure 48 - JTAG Clock and Reset Timing                               |     |

| rigare to 917.0 Clock and Robet Hilling                               | 101 |

## **List of Figures**

| Figure 49 - ZL50110/11/12/14 Power Consumption Plot | 102 |

|-----------------------------------------------------|-----|

| Figure 50 - CPU_TA Board Circuit                    | 105 |

| Figure 51 - Mx LINKUP LED Stuffing Option           | 106 |

### **List of Tables**

| Table 1 - Capacity of Devices in the ZL50110/11/14 Family                       | 4   |

|---------------------------------------------------------------------------------|-----|

| Table 2 - TDM Interface ZL50111 Stream Pin Definition                           | 23  |

| Table 3 - TDM Interface ZL50112 Stream Pin Definition                           | 25  |

| Table 4 - TDM Interface ZL50110 Stream Pin Definition                           | 28  |

| Table 5 - TDM Interface ZL50114 Stream Pin Definition                           | 29  |

| Table 6 - TDM Interface Common Pin Definition                                   | 30  |

| Table 7 - PAC Interface Package Ball Definition                                 | 31  |

| Table 8 - Packet Interface Signal Mapping - MII to GMII/TBI                     | 32  |

| Table 9 - MII Management Interface Package Ball Definition                      | 33  |

| Table 10 - MII Port 0 Interface Package Ball Definition                         | 34  |

| Table 11 - MII Port 1 Interface Package Ball Definition                         | 37  |

| Table 12 - MII Port 2 Interface Package Ball Definition                         | 39  |

| Table 13 - MII Port 3 Interface Package Ball Definition                         | 40  |

| Table 14 - External Memory Interface Package Ball Definition                    | 42  |

| Table 15 - CPU Interface Package Ball Definition                                | 44  |

| Table 16 - System Function Interface Package Ball Definition                    | 47  |

| Table 17 - Administration/Control Interface Package Ball Definition             | 48  |

| Table 18 - JTAG Interface Package Ball Definition                               | 48  |

| Table 19 - Miscellaneous Inputs Package Ball Definitions                        | 49  |

| Table 20 - Power and Ground Package Ball Definition                             |     |

| Table 21 - No Connection Ball Definition                                        | 50  |

| Table 22 - No Connection Ball Definition                                        | 50  |

| Table 23 - Auxiliary clock Ball Definition                                      | 50  |

| Table 24 - Standard Device Flows                                                | 57  |

| Table 25 - TDM Services Offered by the ZL50110/11/12/14 Family                  | 58  |

| Table 26 - Some of the TDM Port Formats Accepted by the ZL50110/11/12/14 Family | 59  |

| Table 27 - DMA Maximum Bandwidths                                               | 67  |

| Table 28 - Test Mode Control                                                    | 73  |

| Table 29 - DPLL Input Reference Frequencies                                     | 74  |

| Table 30 - TDM ST-BUS Master Timing Specification                               | 84  |

| Table 31 - TDM H.110 Timing Specification                                       | 85  |

| Table 32 - TDM H-MVIP Timing Specification                                      | 86  |

| Table 33 - TDM - LIU Structured Transmission/Reception                          | 87  |

| Table 34 - PAC Timing Specification                                             | 88  |

| Table 35 - MII Transmit Timing - 100 Mbps                                       | 88  |

| Table 36 - MII Receive Timing - 100 Mbps                                        | 90  |

| Table 37 - GMII Transmit Timing - 1000 Mbps                                     | 91  |

| Table 38 - GMII Receive Timing - 1000 Mbps                                      | 92  |

| Table 39 - TBI Timing - 1000 Mbps                                               | 93  |

| Table 40 - MAC Management Timing Specification                                  | 94  |

| Table 41 - External Memory Timing                                               | 95  |

| Table 42 - CPU Timing Specification                                             |     |

| Table 43 - System Clock Timing                                                  |     |

| Table 44 - JTAG Interface Timing                                                |     |

| Table 45 - Mx_LINKUP_LED Pin Assignments                                        |     |

| Table 46 - Mx LINKUP LED Stuffing Option                                        | 107 |

### 1.0 Changes Summary

The following table captures the changes from the April 2007 issue.

| Page                    | Item                    | Change                                                                                                |

|-------------------------|-------------------------|-------------------------------------------------------------------------------------------------------|

| Several                 | Include ZL50112 device  | Add description for ZL50112                                                                           |

| 1, 2 and 3              | Standard                | Updated IETF RFC number and standards in general                                                      |

| 1, 58, 74,<br>75 and 77 | Stratum 3 DPLL          | Updated the description for Stratum 3 DPLL                                                            |

| 1, 4, 23, 51<br>and 58  | STS-1 stream            | Remove STS-1 stream                                                                                   |

| 13                      | Section 2.0             | Combine the packaged descriptions for all devices                                                     |

| 32                      | Section 3.3             | Include more detailed description for the packet interface                                            |

| 48                      | Section 3.7.2           | ZL50112 and ZL50111 share the same JTAG ID                                                            |

| 55                      | Section 4.6             | Change the title of the section                                                                       |

| 56                      | Section 5.0             | Add a note about jumbo packets                                                                        |

| 58                      | Section 5.3             | Include a paragraph to clarify the support for structure and unstructure modes at the same time       |

| 60                      | Section 5.4             | Include more detailed description for the Payload Assembly                                            |

| 62                      | Section 5.4.2           | Add a note at the end of the section                                                                  |

| 63                      | Section 5.8             | Include more detailed description for the TDM formatter                                               |

| 64                      | Section 6.0             | Include more detailed description for Clock Recovery                                                  |

| 64                      | Section 6.1             | Include more detailed description for Differential Clock Recovery                                     |

| 65                      | Section 6.2             | Updated the description of Adaptive Clock Recovery                                                    |

| 72                      | Section 7.9             | Added sub sections                                                                                    |

| 86                      | Table 32                | TDM_HDS Input Setup and TDM_HDS Input Hold, Max. time corrected.                                      |

| 93                      | Section 11.6.5          | Updated TXD[9:0] output delay                                                                         |

| 94                      | Section 11.6.6          | UpdatedSection 11.6.6 Management Interface Timing (M_MDIO hold time and Figure 40)                    |

| 97                      | Figure 43 and Figure 44 | CPU_TS_ALE and CPU_TA. Added mode details in Figure 43 and Figure 44 Added the CPU_TA assertion time. |

The following table captures the changes from the February 2006 issue.

| Page | Item                                        | Change               |

|------|---------------------------------------------|----------------------|

| 95   | Table 41, Table 41 - External Memory Timing | Added Minimum Values |

The following table captures the changes from the April 2005 issue.

| Page   | Item                          | Change                                                                                                       |

|--------|-------------------------------|--------------------------------------------------------------------------------------------------------------|

|        |                               | Clarified ZL50111 supports 3 MII ports, ZL50110/4 support 2 MII ports.                                       |

| 47, 48 | Section 3.6 and Section 3.7.2 | Added external pull-up/pull-down resistor recommendations for SYSTEM_RST, SYSTEM_DEBUG, JTAG_TRST, JTAG_TCK. |

| 66     | Section 6.3                   | Added Section 6.3 SYSTEM_CLK Considerations.                                                                 |

The following table captures the changes from the January 2005 issue.

| Page | Item      | Change                                                                                                                                             |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|      |           | Clarified data sheet to indicate ZL50110/11/12/14 supports clock recovery in both synchronous and asynchronous modes of operation.                 |

| 98   | Figure 45 | Inverted polarity of CPU_DREQ0 and CPU_DREQ1 to conform with default MPC8260. Polarity of CPU_DREQ and CPU_SDACK remains programmable through API. |

| 98   | Figure 46 | Inverted polarity of CPU_DREQ0 and CPU_DREQ1 to conform with default MPC8260. Polarity of CPU_DREQ and CPU_SDACK remains programmable through API. |

The following table captures the changes from the October 2004 issue.

| Page | Item          | Change                                                |

|------|---------------|-------------------------------------------------------|

| 48   | Section 3.7.1 | Added 5 kohm pulldown recommendation to GPIO signals. |

The following table captures the changes from the September 2004 issue.

| Page       | ltem                                                        | Change                                                                                      |

|------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 12, 16, 19 | Fig. 2 and Ball Signal<br>Assignment Table                  | Corrected Mx_LINKUP_LED pin assignment.                                                     |

| 73         | DC Electrical Characteristics Table and Output Levels Table | Changed Electrical Characteristics to differentiate between 3.3 V and 5 V tolerant signals. |

| 98         | Section 13.3                                                | New section added; Mx_LINKUP_LED Outputs.                                                   |

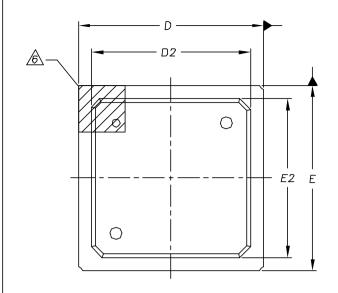

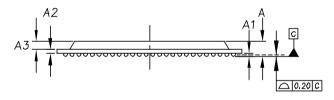

### 2.0 Physical Specification

The ZL50110/11/12/14 is packaged in a PBGA device.

#### Features:

• Body Size: 35 mm x 35 mm (typ)

• Ball Count: 552

• Ball Pitch: 1.27 mm (typ)

• Ball Matrix: 26 x 26

Ball Diameter: 0.75 mm (typ)

Total Package Thickness: 2.33 mm (typ)

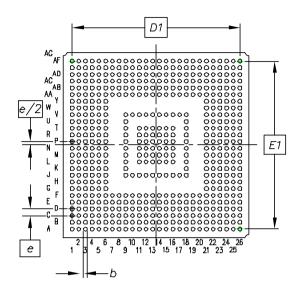

ZL50111 Package view from TOP side. Note that ball A1 is non-chamfered corner.

Figure 2 - ZL50111 Package View and Ball Positions

ZL50112 Package view from TOP side. Note that ball A1 is non-chamfered corner.

Figure 3 - ZL50112 Package View and Ball Positions

ZL50110 Package view from TOP side. Note that ball A1 is non-chamfered corner.

Figure 4 - ZL50110 Package View and Ball Positions

ZL50114 Package view from TOP side. Note that ball A1 is non-chamfered corner.

|    | 1                 | 2                 | 3                 | , 4             | 1      | 5             | 6                 | 7                | 8                | 9                | 10               | 11               | 12               | 13               | 14           | 15              | 16               | 17               | 18               | 19               | 20               | 21               | 22                 | 23                | 24                | 25                 | 26            |     |

|----|-------------------|-------------------|-------------------|-----------------|--------|---------------|-------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|--------------------|-------------------|-------------------|--------------------|---------------|-----|

| Α  | GND               | TDM_STo           | TDM_CL<br>Ko[3]   | N/C             | 1      | N/C           | N/C               | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | GND              | N/C          | N/C             | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C                | N/C               | N/C               | N/C                | GND           | F   |

| В  | TDM_FR<br>Mo_REF  | TDM_STo           | TDM_STi           | TDM_C           | LN     | N/C           | N/C               | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C          | N/C             | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C                | N/C               | N/C               | N/C                | N/C           | Е   |

| С  |                   | TDM_FR<br>Mi_REF  | TDM_CL            | TDM_C<br>Ko[1]  |        | M_STI[<br>3]  | TDM_CL<br>Ko[2]   | N/C              | N/C          | N/C             | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C                | N/C               | N/C               | N/C                | N/C           | C   |

| D  | RAM_DA<br>TA[3]   | RAM_DA<br>TA[1]   | TDM_CL<br>KiS     | RAM_D<br>TA[0]  |        | M_STI[<br>0]  | TDM_CL<br>Ki[1]   | TDM_STo          | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C          | N/C             | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | N/C                | N/C               | N/C               | N/C                | N/C           |     |

| Ε  | RAM_DA<br>TA[10]  | RAM_DA<br>TA[9]   | RAM_DA<br>TA[5]   | RAM_D<br>TA[4]  | A RAI  |               | TDM_CL<br>Ko_REF  | TDM_CL<br>Ki[0]  | N/C              | TDM_STI          | N/C              | N/C              | N/C              | N/C              | N/C          | N/C             | N/C              | N/C              | N/C              | N/C              | N/C              | N/C              | GND                | N/C               | N/C               | N/C                | N/C           | E   |

| F  | RAM_DA<br>TA[15]  | RAM_DA<br>TA[13]  | RAM_DA<br>TA[12]  | RAM_D<br>TA[6]  | A RAI  | M_DA<br>[A[7] | GND               | VDD_CO<br>RE     | TDM_STo          | TDM_CL<br>Ko[0]  | TDM_CL<br>Ki[2]  | N/C              | VDD_CO<br>RE     | N/C              | N/C          | VDD_CO<br>RE    | N/C              | N/C              | N/C              | N/C              | VDD_CO<br>RE     | GND              | N/C                | N/C               | N/C               | N/C                | N/C           | F   |

| G  | RAM_DA<br>TA[21]  | RAM_DA<br>TA[18]  | RAM_DA<br>TA[16]  | RAM_D<br>TA[14] | A RAI  | M_DA<br>A[11] | RAM_DA<br>TA[8]   |                  |                  |                  |                  |                  |                  |                  |              |                 |                  |                  |                  |                  |                  | N/C              | N/C                | M1_LINK<br>UP_LED | M0_LINK<br>UP_LED | M1_GIGA<br>BIT_LED | M_MDIO        | (   |

| Н  |                   |                   | RAM_DA<br>TA[23]  |                 |        | M_DA<br>A[17] | VDD_CO<br>RE      |                  |                  |                  |                  |                  |                  |                  |              |                 |                  |                  |                  | Ī                |                  | VDD_CO<br>RE     | M0_GIGA<br>BIT_LED | M_MDC             | N/C               | N/C                | N/C           | H   |

| J  |                   |                   | RAM_DA<br>TA[27]  |                 |        |               | RAM_DA<br>TA[20]  |                  |                  | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO       | VDD_IO          | VDD_IO           | VDD_IO           | VDD_IO           |                  |                  | N/C              | N/C                | N/C               | N/C               | N/C                | N/C           | J   |

| K  | RAM_PA<br>RITY[1] | RAM_PA<br>RITY[0] | RAM_DA<br>TA[31]  | RAM_D<br>TA[30] | A G    | SND           | VDD_CO<br>RE      |                  |                  | VDD_IO           |                  |                  |                  |                  |              |                 |                  | 1                | VDD_IO           |                  |                  | VDD_CO<br>RE     | GND                | N/C               | N/C               | N/C                | N/C           | ŀ   |

| L  | RAM_PA<br>RITY[7] | RAM_PA<br>RITY[6] | RAM_PA<br>RITY[5] | RAM_P           | A RAI  | M_PA<br>TY[3] | RAM_PA<br>RITY[2] |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | M1_RXE<br>R      | M1_TXCL<br>K       | M1_CRS            | N/C               | N/C                | N/C           | L   |

| M  | RAM_AD<br>DR[5]   | RAM_AD<br>DR[4]   | RAM_AD<br>DR[2]   | RAM_A<br>DR[3]  | D RAI  | M_AD<br>R[0]  | RAM_AD<br>DR[1]   |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | VDD_CO<br>RE     | M1_REF<br>CLK      | M1_RXCL<br>K      | M1_RXD[<br>5]     | M1_RXD[<br>7]      | M1_RXD<br>V   | N   |

| Ν  | GND               | RAM_AD<br>DR[6]   |                   | RAM_A<br>DR[8]  | D G    | SND           | VDD_CO<br>RE      |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | M1_GTX_<br>CLK   | GND                | M1_TXER           | M1_RXD[<br>2]     | M1_RXD[<br>3]      | GND           | 1   |

| Р  |                   |                   | RAM_AD<br>DR[11]  |                 |        | M_AD<br>R[16] | GND               |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | M1_TXD[<br>2]    | M1_TXD[<br>6]      | M1_TXEN           | GND               | M1_RXD[<br>4]      | M1_RXD[<br>6] | F   |

| R  | RAM_AD<br>DR[12]  | RAM_AD<br>DR[14]  | RAM_AD<br>DR[15]  | RAM_A<br>DR[19] | D IC_  | _GND          | IC                |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | M1_TXD[<br>0]    | M1_TXD[<br>3]      | M1_TXD[<br>5]     | M1_TXD[<br>7]     | M1_COL             | M1_RXD[<br>1] | F   |

| Τ  | RAM_AD<br>DR[17]  | RAM_AD<br>DR[18]  | RAM_BW<br>_B      | IC_GNI          | G      | SND           | A1VDD             |                  |                  | VDD_IO           |                  | GND              | GND              | GND              | GND          | GND             | GND              |                  | VDD_IO           |                  |                  | VDD_CO<br>RE     | M1_TXD[<br>1]      | M1_TXD[<br>4]     | GND               | M1_RBC1            | M1_RXD[<br>0] |     |

| U  | PLL_PRI           | RAM_BW<br>_A      | RAM_BW<br>_C      | RAM_R           | W SYS  | STEM<br>EBUG  | SYSTEM<br>_CLK    |                  |                  | VDD_IO           |                  |                  |                  |                  |              |                 |                  |                  | VDD_IO           |                  |                  | M0_GTX_<br>CLK   | M0_RXD[<br>2]      | M0_RXD[<br>5]     | M0_TXCL<br>K      | M0_CRS             | M1_RBC0       | ι.  |

| V  | PLL_SEC           | RAM_BW<br>_D      | RAM_BW<br>_F      | SYSTEM<br>_RST  | И GP   | PIO[2]        | VDD_CO<br>RE      |                  |                  | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO           | VDD_IO       | VDD_IO          | VDD_IO           | VDD_IO           | VDD_IO           |                  |                  | M0_TXD[<br>7]    | M0_TXER            | M0_TXEN           | M0_RXD[<br>4]     | M0_RXD<br>V        | M0_RXE<br>R   | ١   |

| W  | RAM_BW<br>_E      | RAM_BW<br>_G      | GPIO[0]           | GPIO[3          | ] GP   | PIO[9]        | RAM_DA<br>TA[33]  |                  |                  |                  |                  |                  |                  |                  |              |                 |                  |                  |                  |                  |                  | M0_TXD[<br>2]    | M0_TXD[<br>5]      | M0_TXD[<br>6]     | M0_RXD[<br>6]     | M0_RXD[<br>7]      | M0_RXD[<br>3] | V   |

| Υ  | RAM_BW<br>_H      | GPIO[4]           | GPIO[6]           | GPIO[10         | ) RAI  | M_DA<br>A[32] | VDD_CO<br>RE      |                  | ı                |                  |                  | ı                |                  |                  |              |                 |                  |                  |                  |                  |                  | VDD_CO<br>RE     | M0_TXD[<br>1]      | M0_TXD[<br>4]     | M0_RBC0           | M0_COL             | M0_RXD[<br>1] | . ` |

| AΑ | GPIO[1]           | GPI0[7]           | GPIO[8]           | GPIO[18         | S] RAI | M_DA<br>A[39] | GND               | RAM_DA<br>TA[45] | RAM_DA<br>TA[52] | VDD_CO<br>RE     | JTAG_TM<br>S     | CPU_AD<br>DR[2]  | CPU_AD<br>DR[12] | VDD_CO<br>RE     | VDD_CO<br>RE | CPU_DAT<br>A[8] | CPU_DAT<br>A[15] | CPU_DAT<br>A[23] | VDD_CO<br>RE     | N/C              | N/C              | GND              | M0_TXD[<br>0]      | M0_TXD[<br>3]     | M0_REF<br>CLK     | M0_RBC1            | M0_RXD[<br>0] | AA  |

| AB | GPIO[5]           | GPI0[11]          | GPIO[14]          | RAM_D<br>TA[38] | A RAI  | M_DA<br>A[43] | RAM_DA<br>TA[44]  | RAM_DA<br>TA[51] | RAM_DA<br>TA[60] | TEST_M<br>ODE[1] | GND              | CPU_AD<br>DR[6]  | CPU_AD<br>DR[14] | CPU_AD<br>DR[23] | CPU_TA       | CPU_DAT<br>A[1] | CPU_DAT<br>A[7]  | CPU_DAT<br>A[12] | CPU_DAT<br>A[22] | CPU_DAT<br>A[30] | N/C              | N/C              | M0_RXCL<br>K       | N/C               | N/C               | M1_ACTI<br>VE_LED  | N/C           | AE  |

| AC | GPIO[12]          | GPIO[13]          | RAM_DA<br>TA[37]  | RAM_D<br>TA[42] | A RAI  | M_DA<br>A[46] | RAM_DA<br>TA[49]  | RAM_DA<br>TA[59] | TEST_M<br>ODE[0] | JTAG_TD<br>O     | CPU_AD<br>DR[4]  | CPU_AD<br>DR[9]  | CPU_AD<br>DR[16] | CPU_AD<br>DR[22] | CPU_CLK      | CPU_DR<br>EQ0   | IC               | CPU_DAT<br>A[10] | CPU_DAT<br>A[16] | CPU_DAT<br>A[21] | CPU_DAT<br>A[27] | N/C              | N/C                | N/C               | N/C               | N/C                | VE_LED        | Α(  |

| AD | RAM_DA<br>TA[34]  | RAM_DA<br>TA[36]  | RAM_DA<br>TA[41]  |                 |        |               | RAM_DA<br>TA[58]  | RAM_DA<br>TA[63] | JTAG_TC          | IC_GND           | CPU_AD<br>DR[7]  | CPU_AD<br>DR[11] | CPU_AD<br>DR[17] | CPU_AD<br>DR[21] | CPU_WE       | CPU_SD<br>ACK2  | CPU_IRE<br>Q1    | CPU_DAT<br>A[3]  | CPU_DAT<br>A[6]  | CPU_DAT<br>A[14] | CPU_DAT<br>A[20] | CPU_DAT<br>A[24] | CPU_DAT<br>A[29]   | N/C               | N/C               | N/C                | N/C           | Αľ  |

| ΑE | RAM_DA<br>TA[35]  | RAM_DA<br>TA[40]  | RAM_DA<br>TA[48]  | RAM_D<br>TA[54] | A RAI  | M_DA<br>A[57] | RAM_DA<br>TA[62]  | JTAG_TR<br>ST    | IC_GND           | CPU_AD<br>DR[3]  | CPU_AD<br>DR[8]  | CPU_AD<br>DR[13] | CPU_AD<br>DR[18] | CPU_AD<br>DR[20] | CPU_OE       | CPU_TS_<br>ALE  | CPU_DR<br>EQ1    | IC               | CPU_DAT<br>A[4]  | CPU_DAT<br>A[9]  | CPU_DAT<br>A[13] | CPU_DAT<br>A[18] | CPU_DAT<br>A[25]   | CPU_DAT<br>A[28]  | N/C               | N/C                | N/C           | ΑE  |

| ΑF | GND               | RAM_DA<br>TA[50]  | RAM_DA<br>TA[55]  | RAM_D<br>TA[56] | A RAI  | M_DA<br>A[61] | TEST_M<br>ODE[2]  | JTAG_TD          | IC_GND           | CPU_AD<br>DR[5]  | CPU_AD<br>DR[10] | CPU_AD<br>DR[15] | CPU_AD<br>DR[19] | GND              | CPU_CS       | CPU_SD<br>ACK1  | IC_VDD_I<br>O    | CPU_IRE<br>Q0    | CPU_DAT<br>A[0]  | CPU_DAT<br>A[5]  | CPU_DAT<br>A[2]  | CPU_DAT<br>A[11] | CPU_DAT<br>A[17]   | CPU_DAT<br>A[19]  | CPU_DAT<br>A[26]  | CPU_DAT<br>A[31]   | GND           | ΑF  |

|    | 1                 | 2                 | 3                 | , 4             | 1      | 5             | 6                 | 7                | 8                | 9                | 10               | 11               | 12               | 13               | 14           | 15              | 16               | 17               | 18               | 19               | 20               | 21               | 22                 | 23                | 24                | 25                 | 26            |     |

Figure 5 - ZL50114 Package View and Ball Positions

### **Ball Signal Assignment**

| Ball              | Signal Name  |

|-------------------|--------------|

| Number            |              |

| A1                | GND          |

| A2                | TDM_STo[1]   |

| А3                | TDM_CLKo[3]  |

| A4 <sup>‡</sup>   | TDM_STo[4]   |

| A5 <sup>‡</sup>   | TDM_STo[5]   |

| A6 <sup>‡</sup>   | TDM_STi[6]   |

| A7 <sup>‡</sup>   | TDM_STo[7]   |

| A8 <sup>‡</sup>   | TDM_STi[7]   |

| A9 <sup>†</sup>   | TDM_CLKo[10] |

| A10 <sup>†</sup>  | TDM_CLKi[10] |

| A11 <sup>†</sup>  | TDM_CLKi[11] |

| A12 <sup>†</sup>  | TDM_CLKo[13] |

| A13               | GND          |

| A14 <sup>†</sup>  | TDM_STo[13]  |

| A15 <sup>†</sup>  | TDM_STo[14]  |

| A16 <sup>†</sup>  | TDM_CLKo[15] |

| A17 <sup>*</sup>  | TDM_STo[16]  |

| A18 <sup>†*</sup> | TDM_CLKo[18] |

| A19 <sup>*</sup>  | TDM_STi[18]  |

| A20 <sup>*</sup>  | TDM_CLKi[20] |

| A21 <sup>*</sup>  | TDM_STi[20]  |

| A22*              | TDM_STo[21]  |

| A23 <sup>*</sup>  | TDM_STi[21]  |

| A24 <sup>*</sup>  | TDM_CLKo[24] |

| A25 <sup>*</sup>  | TDM_CLKo[25] |

| A26               | GND          |

| B1                | TDM_FRMo_REF |

| B2                | TDM_STo[0]   |

| В3                | TDM_STi[2]   |

| B4                | TDM_CLKi[3]  |

| B5 <sup>‡</sup>   | TDM_STi[4]   |

| B6 <sup>‡</sup>   | TDM_CLKo[6]  |

| B7 <sup>‡</sup>   | TDM_STo[6]   |

| B8 <sup>†</sup>   | TDM_CLKo[8]  |

| B9 <sup>†</sup>   | TDM_CLKi[9]  |

| B10 <sup>†</sup>  | TDM_STo[10]  |

| B11 <sup>†</sup>  | TDM_STi[10]  |

| Ball<br>Number    | Signal Name  |

|-------------------|--------------|

| B12 <sup>†</sup>  | TDM_CLKi[12] |

| B13 <sup>†</sup>  | TDM_STo[12]  |

| B14 <sup>†</sup>  | TDM_STi[13]  |

| B15 <sup>†</sup>  | TDM_CLKi[15] |

| B16 <sup>†</sup>  | TDM_STi[15]  |

| B17 <sup>*</sup>  | TDM_STi[17]  |

| B18 <sup>†*</sup> | TDM_CLKi[18] |

| B19 <sup>*</sup>  | TDM_CLKo[20] |

| B20 <sup>*</sup>  | TDM_STo[19]  |

| B21 <sup>*</sup>  | TDM_STo[22]  |

| B22 <sup>*</sup>  | TDM_CLKo[23] |

| B23 <sup>*</sup>  | TDM_STo[24]  |

| B24 <sup>*</sup>  | TDM_CLKo[26] |

| B25 <sup>*</sup>  | TDM_STi[24]  |

| B26 <sup>*</sup>  | TDM_CLKo[27] |

| C1                | TDM_CLKiP    |

| C2                | TDM_FRMi_REF |

| C3                | TDM_CLKi_REF |

| C4                | TDM_CLKo[1]  |

| C5                | TDM_STi[3]   |

| C6                | TDM_CLKo[2]  |

| C7 <sup>‡</sup>   | TDM_CLKi[6]  |

| C8 <sup>‡</sup>   | TDM_CLKi[7]  |

| C9 <sup>†</sup>   | TDM_CLKo[9]  |

| C10 <sup>†</sup>  | TDM_STo[9]   |

| C11 <sup>†</sup>  | TDM_STi[9]   |

| C12 <sup>†</sup>  | TDM_STi[11]  |

| C13 <sup>†</sup>  | TDM_CLKi[13] |

| C14 <sup>†</sup>  | TDM_CLKo[14] |

| C15 <sup>*</sup>  | TDM_CLKo[16] |

| C16 <sup>*</sup>  | TDM_STi[16]  |

| C17 <sup>*</sup>  | TDM_CLKo[17] |

| C18 <sup>*</sup>  | TDM_STi[19]  |

| C19 <sup>*</sup>  | TDM_CLKo[21] |

| C20 <sup>*</sup>  | TDM_CLKi[21] |

| C21 <sup>*</sup>  | TDM_CLKi[24] |

| C22 <sup>*</sup>  | TDM_STi[22]  |

| C23 <sup>*</sup>  | TDM_STo[26]  |

| Ball<br>Number    | Signal Name  |

|-------------------|--------------|

| C24 <sup>*</sup>  | TDM_CLKi[27] |

| C25 <sup>*</sup>  | TDM_STi[27]  |

| C26*              | TDM_STi[28]  |

| D1                | RAM_DATA[3]  |

| D2                | RAM_DATA[1]  |

| D3                | TDM_CLKiS    |

| D4                | RAM_DATA[0]  |

| D5                | TDM_STi[0]   |

| D6                | TDM_CLKi[1]  |

| D7                | TDM_STo[3]   |

| D8 <sup>‡</sup>   | TDM_STi[5]   |

| D9 <sup>‡</sup>   | TDM_CLKi[5]  |

| D10 <sup>‡</sup>  | TDM_CLKo[7]  |

| D11 <sup>†</sup>  | TDM_STi[8]   |

| D12 <sup>†</sup>  | TDM_CLKo[11] |

| D13 <sup>†</sup>  | TDM_STi[12]  |

| D14 <sup>†</sup>  | TDM_STi[14]  |

| D15 <sup>†*</sup> | TDM_CLKi[16] |

| D16 <sup>†</sup>  | TDM_CLKo[19] |

| D17 <sup>*</sup>  | TDM_STo[18]  |

| D18 <sup>*</sup>  | TDM_STo[20]  |

| D19 <sup>*</sup>  | TDM_CLKo[22] |

| D20 <sup>*</sup>  | TDM_STo[27]  |

| D21 <sup>*</sup>  | TDM_STo[25]  |

| D22 <sup>*</sup>  | TDM_CLKi[26] |

| D23 <sup>*</sup>  | TDM_CLKo[28] |

| D24 <sup>*</sup>  | TDM_CLKi[29] |

| D25 <sup>*</sup>  | TDM_STi[29]  |

| D26 <sup>*</sup>  | TDM_STi[31]  |

| E1                | RAM_DATA[10] |

| E2                | RAM_DATA[9]  |

| E3                | RAM_DATA[5]  |

| E4                | RAM_DATA[4]  |

| E5                | RAM_DATA[2]  |

| E6                | TDM_CLKo_REF |

| E7                | TDM_CLKi[0]  |

| E8 <sup>‡</sup>   | TDM_CLKo[4]  |

| E9                | TDM_STi[1]   |

| Ball              | Signal Name  |

|-------------------|--------------|

| Number            | Signal Name  |

| E10 <sup>‡</sup>  | TDM_CLKi[4]  |

| E11 <sup>†</sup>  | TDM_STo[8]   |

| E12 <sup>†</sup>  | TDM_CLKi[8]  |

| E13 <sup>†</sup>  | TDM_CLKo[12] |

| E14 <sup>†</sup>  | TDM_STo[15]  |

| E15 <sup>*</sup>  | TDM_CLKi[17] |

| E16 <sup>*</sup>  | TDM_CLKi[19] |

| E17 <sup>*</sup>  | TDM_STo[23]  |

| E18 <sup>*</sup>  | TDM_STi[23]  |

| E19 <sup>*</sup>  | TDM_CLKi[25] |

| E20 <sup>*</sup>  | TDM_STi[26]  |

| E21 <sup>*</sup>  | TDM_CLKi[28] |

| E22               | GND          |

| E23 <sup>*</sup>  | TDM_CLKo[30] |

| E24 <sup>*</sup>  | TDM_CLKi[30] |

| E25 <sup>*</sup>  | TDM_STi[30]  |

| E26 <sup>†*</sup> | TDM_STo[29]  |

| F1                | RAM_DATA[15] |

| F2                | RAM_DATA[13] |

| F3                | RAM_DATA[12] |

| F4                | RAM_DATA[6]  |

| F5                | RAM_DATA[7]  |

| F6                | GND          |

| F7                | VDD_CORE     |

| F8                | TDM_STo[2]   |

| F9                | TDM_CLKo[0]  |

| F10               | TDM_CLKi[2]  |

| F11 <sup>‡</sup>  | TDM_CLKo[5]  |

| F12               | VDD_CORE     |

| F13 <sup>†</sup>  | TDM_STo[11]  |

| F14 <sup>†</sup>  | TDM_CLKi[14] |

| F15               | VDD_CORE     |

| F16 <sup>*</sup>  | TDM_STo[17]  |

| F17 <sup>*</sup>  | TDM_CLKi[22] |

| F18 <sup>*</sup>  | TDM_STi[25]  |

| F19 <sup>*</sup>  | TDM_CLKi[23] |

| F20               | VDD_CORE     |

| F21               | GND          |

| Ball<br>Number   | Signal Name     |

|------------------|-----------------|

| F22 <sup>*</sup> | TDM_CLKi[31]    |

| F23 <sup>*</sup> | TDM_CLKo[29]    |

| F24 <sup>*</sup> | TDM_STo[28]     |

| F25 <sup>*</sup> | TDM_CLKo[31]    |

| F26 <sup>†</sup> | M1_LINKUP_LED   |

| G1               | RAM_DATA[21]    |

| G2               | RAM_DATA[18]    |

| G3               | RAM_DATA[16]    |

| G4               | RAM_DATA[14]    |

| G5               | RAM_DATA[11]    |

| G6               | RAM_DATA[8]     |

| G21 <sup>*</sup> | TDM_STo[31]     |

| G22 <sup>*</sup> | TDM_STo[30]     |

| G23              | M1/2_LINKUP_LED |

| G24              | M0/3_LINKUP_LED |

| G25              | M1_GIGABIT_LED  |

| G26              | M_MDIO          |

| H1               | RAM_DATA[25]    |

| H2               | RAM_DATA[24]    |

| НЗ               | RAM_DATA[23]    |

| H4               | RAM_DATA[19]    |

| H5               | RAM_DATA[17]    |

| H6               | VDD_CORE        |

| H21              | VDD_CORE        |

| H22              | M0_GIGABIT_LED  |

| H23              | M_MDC           |

| H24 <sup>*</sup> | M3_CRS          |

| H25 <sup>*</sup> | M3_TXCLK        |

| H26 <sup>*</sup> | M3_RXER         |

| J1               | RAM_DATA[29]    |

| J2               | RAM_DATA[28]    |

| J3               | RAM_DATA[27]    |

| J4               | RAM_DATA[26]    |

| J5               | RAM_DATA[22]    |

| J6               | RAM_DATA[20]    |

| J9               | VDD_IO          |

| J10              | VDD_IO          |

| J11              | VDD_IO          |

| Ball<br>Number   | Signal Name   |

|------------------|---------------|

| J12              | VDD_IO        |

| J13              | VDD_IO        |

| J14              | VDD_IO        |

| J15              | VDD_IO        |

| J16              | VDD_IO        |

| J17              | VDD_IO        |

| J18              | VDD_IO        |

| J21 <sup>*</sup> | M3_RXDV       |

| J22*             | M3_RXD[3]     |

| J23 <sup>*</sup> | M3_RXD[2]     |

| J24 <sup>*</sup> | M3_RXD[1]     |

| J25 <sup>*</sup> | M3_RXD[0]     |

| J26 <sup>*</sup> | M3_COL        |

| K1               | RAM_PARITY[1] |

| K2               | RAM_PARITY[0] |

| K3               | RAM_DATA[31]  |

| K4               | RAM_DATA[30]  |

| K5               | GND           |

| K6               | VDD_CORE      |

| K9               | VDD_IO        |

| K18              | VDD_IO        |

| K21              | VDD_CORE      |

| K22              | GND           |

| K23 <sup>*</sup> | M3_TXD[3]     |

| K24 <sup>*</sup> | M3_TXEN       |

| K25 <sup>*</sup> | M3_TXER       |

| K26 <sup>*</sup> | M3_RXCLK      |

| L1               | RAM_PARITY[7] |

| L2               | RAM_PARITY[6] |

| L3               | RAM_PARITY[5] |

| L4               | RAM_PARITY[4] |

| L5               | RAM_PARITY[3] |

| L6               | RAM_PARITY[2] |

| L9               | VDD_IO        |

| L11              | GND           |

| L12              | GND           |

| L13              | GND           |

| L14              | GND           |

| Ball<br>Number   | Signal Name |

|------------------|-------------|

| L15              | GND         |

| L16              | GND         |

| L18              | VDD_IO      |

| L21              | M1_RXER     |

| L22              | M1_TXCLK    |

| L23              | M1_CRS      |

| L24 <sup>*</sup> | M3_TXD[0]   |

| L25 <sup>*</sup> | M3_TXD[1]   |

| L26*             | M3_TXD[2]   |

| M1               | RAM_ADDR[5] |

| M2               | RAM_ADDR[4] |

| М3               | RAM_ADDR[2] |

| M4               | RAM_ADDR[3] |

| M5               | RAM_ADDR[0] |

| M6               | RAM_ADDR[1] |

| M9               | VDD_IO      |

| M11              | GND         |

| M12              | GND         |

| M13              | GND         |

| M14              | GND         |

| M15              | GND         |

| M16              | GND         |

| M18              | VDD_IO      |

| M21              | VDD_CORE    |

| M22              | M1_REFCLK   |

| M23              | M1_RXCLK    |

| M24              | M1_RXD[5]   |

| M25              | M1_RXD[7]   |

| M26              | M1_RXDV     |

| N1               | GND         |

| N2               | RAM_ADDR[6] |

| N3               | RAM_ADDR[7] |

| N4               | RAM_ADDR[8] |

| N5               | GND         |

| N6               | VDD_CORE    |

| N9               | VDD_IO      |

| N11              | GND         |

| N12              | GND         |

| Ball<br>Number | Signal Name  |

|----------------|--------------|

| N13            | GND          |

| N14            | GND          |

| N15            | GND          |

| N16            | GND          |

| N18            | VDD_IO       |

| N21            | M1_GTX_CLK   |

| N22            | GND          |

| N23            | M1_TXER      |

| N24            | M1_RXD[2]    |

| N25            | M1_RXD[3]    |

| N26            | GND          |

| P1             | RAM_ADDR[9]  |

| P2             | RAM_ADDR[10] |

| P3             | RAM_ADDR[11] |

| P4             | RAM_ADDR[13] |

| P5             | RAM_ADDR[16] |

| P6             | GND          |

| P9             | VDD_IO       |

| P11            | GND          |

| P12            | GND          |

| P13            | GND          |

| P14            | GND          |

| P15            | GND          |

| P16            | GND          |

| P18            | VDD_IO       |

| P21            | M1_TXD[2]    |

| P22            | M1_TXD[6]    |

| P23            | M1_TXEN      |

| P24            | GND          |

| P25            | M1_RXD[4]    |

| P26            | M1_RXD[6]    |

| R1             | RAM_ADDR[12] |

| R2             | RAM_ADDR[14] |

| R3             | RAM_ADDR[15] |

| R4             | RAM_ADDR[19] |

| R5             | IC_GND       |

| R6             | IC           |

| R9             | VDD_IO       |

| Ball<br>Number | Signal Name  |

|----------------|--------------|

| R11            | GND          |

| R12            | GND          |

| R13            | GND          |

| R14            | GND          |

| R15            | GND          |

| R16            | GND          |

| R18            | VDD_IO       |

| R21            | M1_TXD[0]    |

| R22            | M1_TXD[3]    |

| R23            | M1_TXD[5]    |

| R24            | M1_TXD[7]    |

| R25            | M1_COL       |

| R26            | M1_RXD[1]    |

| T1             | RAM_ADDR[17] |

| T2             | RAM_ADDR[18] |

| T3             | RAM_BW_B     |

| T4             | IC_GND       |

| T5             | GND          |

| T6             | A1VDD        |

| Т9             | VDD_IO       |

| T11            | GND          |

| T12            | GND          |

| T13            | GND          |

| T14            | GND          |

| T15            | GND          |

| T16            | GND          |

| T18            | VDD_IO       |

| T21            | VDD_CORE     |

| T22            | M1_TXD[1]    |

| T23            | M1_TXD[4]    |

| T24            | GND          |

| T25            | M1_RBC1      |

| T26            | M1_RXD[0]    |

| U1             | PLL_PRI      |

| U2             | RAM_BW_A     |

| U3             | RAM_BW_C     |

| U4             | RAM_RW       |

| U5             | SYSTEM_DEBUG |

| Ball<br>Number | Signal Name  |  |  |  |

|----------------|--------------|--|--|--|

| U6             | SYSTEM_CLK   |  |  |  |

| U9             | VDD_IO       |  |  |  |

| U18            | VDD_IO       |  |  |  |

| U21            | M0_GTX_CLK   |  |  |  |

| U22            | M0_RXD[2]    |  |  |  |

| U23            | M0_RXD[5]    |  |  |  |

| U24            | M0_TXCLK     |  |  |  |

| U25            | M0_CRS       |  |  |  |

| U26            | M1_RBC0      |  |  |  |

| V1             | PLL_SEC      |  |  |  |

| V2             | RAM_BW_D     |  |  |  |

| V3             | RAM_BW_F     |  |  |  |

| V4             | SYSTEM_RST   |  |  |  |

| V5             | GPIO[2]      |  |  |  |

| V6             | VDD_CORE     |  |  |  |

| V9             | VDD_IO       |  |  |  |

| V10            | VDD_IO       |  |  |  |

| V11            | VDD_IO       |  |  |  |

| V12            | VDD_IO       |  |  |  |

| V13            | VDD_IO       |  |  |  |

| V14            | VDD_IO       |  |  |  |

| V15            | VDD_IO       |  |  |  |

| V16            | VDD_IO       |  |  |  |

| V17            | VDD_IO       |  |  |  |

| V18            | VDD_IO       |  |  |  |

| V21            | M0_TXD[7]    |  |  |  |

| V22            | M0_TXER      |  |  |  |

| V23            | M0_TXEN      |  |  |  |

| V24            | M0_RXD[4]    |  |  |  |

| V25            | M0_RXDV      |  |  |  |

| V26            | M0_RXER      |  |  |  |

| W1             | RAM_BW_E     |  |  |  |

| W2             | RAM_BW_G     |  |  |  |

| W3             | GPIO[0]      |  |  |  |

| W4             | GPIO[3]      |  |  |  |

| W5             | GPIO[9]      |  |  |  |

| W6             | RAM_DATA[33] |  |  |  |

| W21            | M0_TXD[2]    |  |  |  |

| Ball<br>Number    | Signal Name  |  |  |  |

|-------------------|--------------|--|--|--|

| W22               | M0_TXD[5]    |  |  |  |

| W23               | M0_TXD[6]    |  |  |  |

| W24               | M0_RXD[6]    |  |  |  |

| W25               | M0_RXD[7]    |  |  |  |

| W26               | M0_RXD[3]    |  |  |  |

| Y1                | RAM_BW_H     |  |  |  |

| Y2                | GPIO[4]      |  |  |  |

| Y3                | GPIO[6]      |  |  |  |

| Y4                | GPIO[10]     |  |  |  |

| Y5                | RAM_DATA[32] |  |  |  |

| Y6                | VDD_CORE     |  |  |  |

| Y21               | VDD_CORE     |  |  |  |

| Y22               | M0_TXD[1]    |  |  |  |

| Y23               | M0_TXD[4]    |  |  |  |

| Y24               | M0_RBC0      |  |  |  |

| Y25               | M0_COL       |  |  |  |

| Y26               | M0_RXD[1]    |  |  |  |

| AA1               | GPIO[1]      |  |  |  |

| AA2               | GPIO[7]      |  |  |  |

| AA3               | GPIO[8]      |  |  |  |

| AA4               | GPIO[15]     |  |  |  |

| AA5               | RAM_DATA[39] |  |  |  |

| AA6               | GND          |  |  |  |

| AA7               | RAM_DATA[45] |  |  |  |

| AA8               | RAM_DATA[52] |  |  |  |

| AA9               | VDD_CORE     |  |  |  |

| AA10              | JTAG_TMS     |  |  |  |

| AA11              | CPU_ADDR[2]  |  |  |  |

| AA12              | CPU_ADDR[12] |  |  |  |

| AA13              | VDD_CORE     |  |  |  |

| AA14              | VDD_CORE     |  |  |  |

| AA15              | CPU_DATA[8]  |  |  |  |

| AA16              | CPU_DATA[15] |  |  |  |

| AA17              | CPU_DATA[23] |  |  |  |

| AA18              | VDD_CORE     |  |  |  |

| AA19 <sup>†</sup> | M2_RXCLK     |  |  |  |

| AA20 <sup>†</sup> | M2_RXDV      |  |  |  |

| AA21              | GND          |  |  |  |

| Ball<br>Number    | Signal Name   |  |  |  |

|-------------------|---------------|--|--|--|

| AA22              | M0_TXD[0]     |  |  |  |

| AA23              | M0_TXD[3]     |  |  |  |

| AA24              | M0_REFCLK     |  |  |  |

| AA25              | M0_RBC1       |  |  |  |

| AA26              | M0_RXD[0]     |  |  |  |

| AB1               | GPIO[5]       |  |  |  |

| AB2               | GPIO[11]      |  |  |  |

| AB3               | GPIO[14]      |  |  |  |

| AB4               | RAM_DATA[38]  |  |  |  |

| AB5               | RAM_DATA[43]  |  |  |  |

| AB6               | RAM_DATA[44]  |  |  |  |

| AB7               | RAM_DATA[51]  |  |  |  |

| AB8               | RAM_DATA[60]  |  |  |  |

| AB9               | TEST_MODE[1]  |  |  |  |

| AB10              | GND           |  |  |  |

| AB11              | CPU_ADDR[6]   |  |  |  |

| AB12              | CPU_ADDR[14]  |  |  |  |

| AB13              | CPU_ADDR[23]  |  |  |  |

| AB14              | CPU_TA        |  |  |  |

| AB15              | CPU_DATA[1]   |  |  |  |

| AB16              | CPU_DATA[7]   |  |  |  |

| AB17              | CPU_DATA[12]  |  |  |  |

| AB18              | CPU_DATA[22]  |  |  |  |

| AB19              | CPU_DATA[30]  |  |  |  |

| AB20 <sup>†</sup> | M2_TXER       |  |  |  |

| AB21 <sup>†</sup> | M2_RXD[1]     |  |  |  |

| AB22              | M0_RXCLK      |  |  |  |

| AB23 <sup>†</sup> | M0_LINKUP_LED |  |  |  |

| AB24 <sup>†</sup> | M2_ACTIVE_LED |  |  |  |

| AB25              | M1_ACTIVE_LED |  |  |  |

| AB26 <sup>*</sup> | M3_ACTIVE_LED |  |  |  |

| AC1               | GPIO[12]      |  |  |  |

| AC2               | GPIO[13]      |  |  |  |

| AC3               | RAM_DATA[37]  |  |  |  |

| AC4               | RAM_DATA[42]  |  |  |  |

| AC5               | RAM_DATA[46]  |  |  |  |

| AC6               | RAM_DATA[49]  |  |  |  |

| AC7               | RAM_DATA[59]  |  |  |  |

|                   |               |  |  |  |

| Ball              | Signal Name   |  |  |  |

|-------------------|---------------|--|--|--|

| Number            | Signal Hame   |  |  |  |

| AC8               | TEST_MODE[0]  |  |  |  |

| AC9               | JTAG_TDO      |  |  |  |

| AC10              | CPU_ADDR[4]   |  |  |  |

| AC11              | CPU_ADDR[9]   |  |  |  |

| AC12              | CPU_ADDR[16]  |  |  |  |

| AC13              | CPU_ADDR[22]  |  |  |  |

| AC14              | CPU_CLK       |  |  |  |

| AC15              | CPU_DREQ0     |  |  |  |

| AC16              | IC            |  |  |  |

| AC17              | CPU_DATA[10]  |  |  |  |

| AC18              | CPU_DATA[16]  |  |  |  |

| AC19              | CPU_DATA[21]  |  |  |  |

| AC20              | CPU_DATA[27]  |  |  |  |

| AC21 <sup>†</sup> | M2_TXD[1]     |  |  |  |

| AC22 <sup>†</sup> | M2_TXEN       |  |  |  |

| AC23 <sup>†</sup> | M2_RXD[2]     |  |  |  |

| AC24 <sup>†</sup> | M2_RXER       |  |  |  |

| AC25 <sup>†</sup> | M2_CRS        |  |  |  |

| AC26              | M0_ACTIVE_LED |  |  |  |

| AD1               | RAM_DATA[34]  |  |  |  |

| AD2               | RAM_DATA[36]  |  |  |  |

| AD3               | RAM_DATA[41]  |  |  |  |

| AD4               | RAM_DATA[47]  |  |  |  |

| AD5               | RAM_DATA[53]  |  |  |  |

| AD6               | RAM_DATA[58]  |  |  |  |

| AD7               | RAM_DATA[63]  |  |  |  |

| AD8               | JTAG_TCK      |  |  |  |

| AD9               | IC_GND        |  |  |  |

| AD10              | CPU_ADDR[7]   |  |  |  |

| AD11              | CPU_ADDR[11]  |  |  |  |

| AD12              | CPU_ADDR[17]  |  |  |  |

| AD13              | CPU_ADDR[21]  |  |  |  |

| AD14              | CPU_WE        |  |  |  |

| AD15              | CPU_SDACK2    |  |  |  |

| AD16              | CPU_IREQ1     |  |  |  |

| AD17              | CPU_DATA[3]   |  |  |  |

| AD18              | CPU_DATA[6]   |  |  |  |

| AD19              | CPU_DATA[14]  |  |  |  |

| Ball              |              |  |  |  |

|-------------------|--------------|--|--|--|

| Number            | Signal Name  |  |  |  |

| AD20              | CPU_DATA[20] |  |  |  |

| AD21              | CPU_DATA[24] |  |  |  |

| AD22              | CPU_DATA[29] |  |  |  |

| AD23 <sup>†</sup> | M2_TXD[2]    |  |  |  |

| AD24 <sup>†</sup> | M2_RXD[0]    |  |  |  |

| AD25 <sup>†</sup> | M2_RXD[3]    |  |  |  |

| AD26 <sup>†</sup> | M2 TXCLK     |  |  |  |

| AE1               | RAM_DATA[35] |  |  |  |

| AE2               | RAM_DATA[40] |  |  |  |

| AE3               | RAM_DATA[48] |  |  |  |

| AE4               | RAM_DATA[54] |  |  |  |

| AE5               | RAM_DATA[57] |  |  |  |

| AE6               | RAM_DATA[62] |  |  |  |

| AE7               | JTAG_TRST    |  |  |  |

| AE8               | IC_GND       |  |  |  |

| AE9               | CPU_ADDR[3]  |  |  |  |

| AE10              | CPU_ADDR[8]  |  |  |  |

| AE11              | CPU_ADDR[13] |  |  |  |

| AE12              | CPU_ADDR[18] |  |  |  |

| AE13              | CPU_ADDR[20] |  |  |  |

| AE14              | CPU_OE       |  |  |  |

| AE15              | CPU_TS_ALE   |  |  |  |

| AE16              | CPU_DREQ1    |  |  |  |

| AE17              | IC           |  |  |  |

| AE18              | CPU_DATA[4]  |  |  |  |

| AE19              | CPU_DATA[9]  |  |  |  |

| AE20              | CPU_DATA[13] |  |  |  |

| AE21              | CPU_DATA[18] |  |  |  |

| AE22              | CPU_DATA[25] |  |  |  |

| AE23              | CPU_DATA[28] |  |  |  |

| AE24 <sup>†</sup> | M2_TXD[0]    |  |  |  |

| AE25 <sup>†</sup> | M2_TXD[3]    |  |  |  |

| AE26 <sup>†</sup> | M2_COL       |  |  |  |

| AF1               | GND          |  |  |  |

| AF2               | RAM_DATA[50] |  |  |  |

| AF3               | RAM_DATA[55] |  |  |  |

| AF4               | RAM_DATA[56] |  |  |  |

| AF5               | RAM_DATA[61] |  |  |  |

|                   | =            |  |  |  |

| Ball<br>Number                          | Signal Name  |  |  |  |  |

|-----------------------------------------|--------------|--|--|--|--|

| AF6                                     | TEST_MODE[2] |  |  |  |  |

| AF7                                     | JTAG_TDI     |  |  |  |  |

| AF8                                     | IC_GND       |  |  |  |  |

| AF9                                     | CPU_ADDR[5]  |  |  |  |  |

| AF10                                    | CPU_ADDR[10] |  |  |  |  |

| AF11                                    | CPU_ADDR[15] |  |  |  |  |

| AF12                                    | CPU_ADDR[19] |  |  |  |  |

| AF13                                    | GND          |  |  |  |  |

| AF14                                    | CPU_CS       |  |  |  |  |

| AF15                                    | CPU_SDACK1   |  |  |  |  |

| AF16                                    | IC_VDD_IO    |  |  |  |  |

| AF17                                    | CPU_IREQ0    |  |  |  |  |

| AF18                                    | CPU_DATA[0]  |  |  |  |  |

| AF19                                    | CPU_DATA[5]  |  |  |  |  |

| AF20                                    | CPU_DATA[2]  |  |  |  |  |

| AF21                                    | CPU_DATA[11] |  |  |  |  |

| AF22                                    | CPU_DATA[17] |  |  |  |  |

| AF23                                    | CPU_DATA[19] |  |  |  |  |

| AF24                                    | CPU_DATA[26] |  |  |  |  |

| AF25                                    | CPU_DATA[31] |  |  |  |  |

| AF26                                    | GND          |  |  |  |  |

| Not connected on ZI 50112, ZI 50110 and |              |  |  |  |  |

<sup>\*</sup> Not connected on ZL50112, ZL50110 and ZL50114 - leave open circuit.

<sup>†</sup> Not Connected on ZL50110 and ZL50114 - leave open circuit.

<sup>‡</sup> Not Connected on ZL50114 - leave open circuit.

N/C - Not Connected - leave open circuit.

<sup>\*</sup> Internally Connected on ZL50112 - leave open circuit.

IC - Internally Connected - leave open circuit.

IC\_GND - tie to ground

IC\_VDD\_IO - tie to VDD\_IO

### 3.0 External Interface Description

The following key applies to all tables:

- I Input

- O Output

- D Internal 100 k $\Omega$  pull-down resistor present

- U Internal 100 kΩ pull-up resistor present

- T Tri-state Output

### 3.1 TDM Interface

All TDM Interface signals are 5 V tolerant.

All TDM Interface inputs (including data, clock and frame pulse) have internal pull-down resistors so they can be safely left unconnected if not used.

### 3.1.1 ZL50111 Variant TDM Stream Connection

| Signal        | I/O |      | Packa | ge Ball | ls  | Description                                |

|---------------|-----|------|-------|---------|-----|--------------------------------------------|

| TDM_STi[31:0] | ΙD  | [31] | D26   | [15]    | B16 | TDM port serial data input streams. For    |

|               |     | [30] | E25   | [14]    | D14 | different standards these pins are given   |

|               |     | [29] | D25   | [13]    | B14 | different identities:                      |

|               |     | [28] | C26   | [12]    | D13 | ST-BUS: TDM_STi[31:0]                      |

|               |     | [27] | C25   | [11]    | C12 | H.110: TDM_D[31:0]                         |

|               |     | [26] | E20   | [10]    | B11 | H-MVIP: TDM_HDS[31:0]                      |