### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

July 2010

# FAN6982 CCM Power Factor Correction Controller

#### **Features**

- Continuous Conduction Mode

- Innovative Switching-Charge Multiplier-Divider

- Average-Current-Mode for Input-Current Shaping

- TriFault Detect™ Prevent Abnormal Operation for Feedback Loop

- Power-On Sequence Control

- Soft-Start Capability

- Brownout Protection

- Cycle-by-Cycle Peak Current Limiting.

- Improves Light-Load Efficiency

- Fulfills Class-D Requirements of IEC 1000-3-2

- Wide Range Universal AC Input Voltage

- Maximum Duty Cycle 97%

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

### **Applications**

- Desktop PC Power Supply

- Internet Server Power Supply

- LCD TV/Monitor Power Supply

- DC Motor Power Supply

### **Description**

The FAN6982 is a 14-pin, Continuous Conduction Mode (CCM) PFC controller IC intended for Power Factor Correction (PFC) pre-regulators. The FAN6982 includes circuits for the implementation of leading edge, average current, "boost"-type power factor correction, and results in a power supply that fully complies with the IEC1000-3-2 specification.

A TriFault Detect™ function helps reduce external components and provides full protection for feedback loops such as open, short, and over voltage. An overvoltage comparator shuts down the PFC stage in the event of a sudden load decrease. The RDY signal can be used for power-on sequence control. The EN function can choose to enable or disable the range function. FAN6982 also includes PFC soft-start, peak current limiting, and input voltage brownout protection.

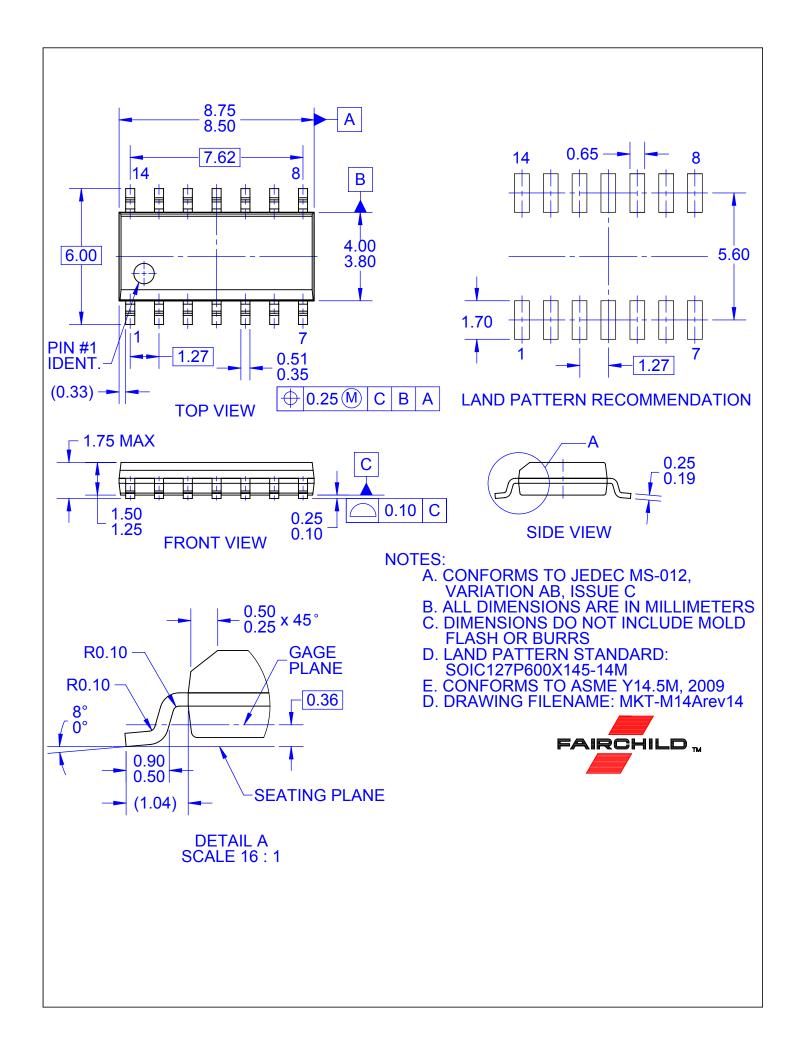

### **Ordering Information**

| Part Number   Operating Temperature Range |                 | Package                            | Packing Method |  |

|-------------------------------------------|-----------------|------------------------------------|----------------|--|

| FAN6982MY                                 | -40°C to +105°C | 14-Pin Small Outline Package (SOP) | Tape & Reel    |  |

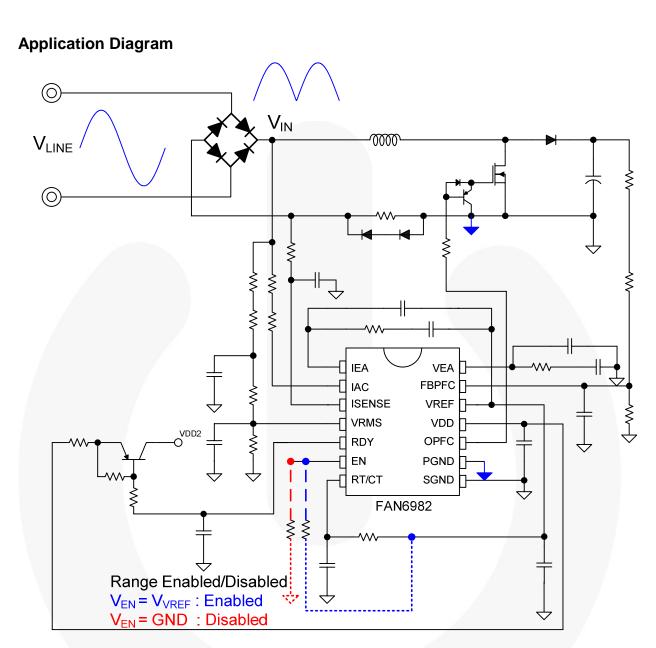

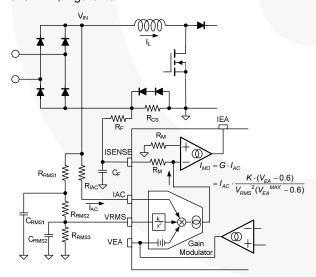

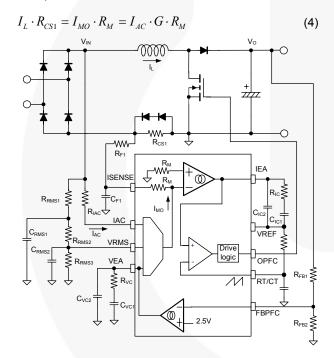

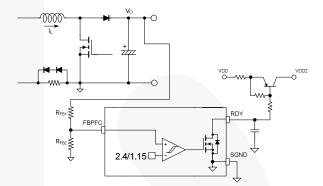

Figure 1. Typical Application

### **Block Diagram**

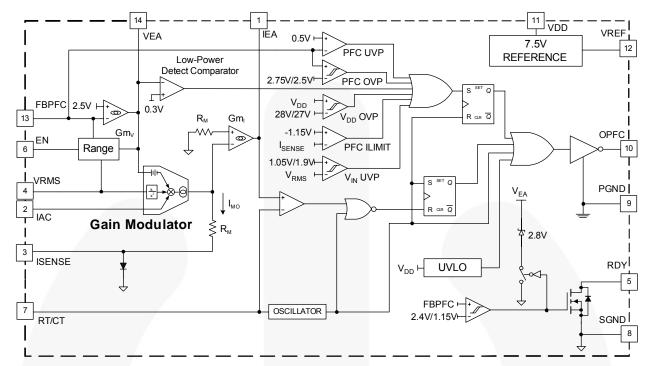

Figure 2. Functional Block Diagram

### **Marking Information**

- F Fairchild Logo

- Z Plant Code

- X 1-Digit Year Code

- Y 1-Digit Week Code

- TT 2-Digit Die-Run Code

- T Package Type (M: SOP)

- P Y: Green Package

- M Manufacture Flow Code

Figure 3. Top Mark

## **Pin Configuration**

Figure 4. Pin Configuration

### **Pin Definitions**

| Pin # | Name   | Description                                                                                                                                                                                                                                      |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IEA    | <b>Output of Current Amplifier</b> . This is the output of the PFC current amplifier. The signal from this pin is compared with sawtooth and determines the pulsewidth for PFC gate drive.                                                       |

| 2     | IAC    | Input AC Current. For normal operation, this input is used to provide current reference for the multiplier. The suggested maximum $I_{AC}$ is $100\mu A$ .                                                                                       |

| 3     | ISENSE | Current Sense. The non-inverting input of the PFC current amplifier and the output of multiplier and PFC I <sub>LIMIT</sub> comparator.                                                                                                          |

| 4     | VRMS   | Line-Voltage Detection. The pin is used for PFC multiplier.                                                                                                                                                                                      |

| 5     | RDY    | <b>Ready Signal</b> . This pin controls the power-on sequence. Once the FAN6982 is turned on and the FBPFC voltage exceeds in 2.4V, the RDY pin pulls LOW impedance. If the FBPFC voltage is lower than 1.15V, the RDY pin pulls HIGH impedance. |

| 6     | EN     | <b>Enable Range Function</b> . The range function is enabled when EN is connected to $V_{\text{REF}}$ . The range function is disabled when EN is connected to GND.                                                                              |

| 7     | RT/CT  | Oscillator RC Timing Connection. Oscillator timing node; timing set by RT and CT.                                                                                                                                                                |

| 8     | SGND   | Signal Ground.                                                                                                                                                                                                                                   |

| 9     | PGND   | Power Ground.                                                                                                                                                                                                                                    |

| 10    | OPFC   | Gate Drive. The totem-pole output drive for PFC MOSFET. This pin is internally clamped under 15V to protect the MOSFET.                                                                                                                          |

| 11    | VDD    | <b>Power Supply</b> . The threshold voltages for startup and turn-off are 11V and 9.3V, respectively. The operating current is lower than 10mA.                                                                                                  |

| 12    | VREF   | Reference Voltage. Buffered output for the internal 7.5V reference.                                                                                                                                                                              |

| 13    | FBPFC  | Voltage Feedback Input. The feedback input for PFC voltage loop. The inverting input of PFC error amplifier. This pin is connected to the PFC output through a divider network.                                                                  |

| 14    | VEA    | Output of Voltage Amplifier. The error-amplifier output for PFC voltage feedback loop. A compensation network is connected between this pin and ground.                                                                                          |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               | Paramete                                 | Min.                                 | Max.   | Unit                   |      |

|----------------------|------------------------------------------|--------------------------------------|--------|------------------------|------|

| $V_{DD}$             | DC Supply Voltage                        |                                      |        | 30                     | V    |

| V <sub>H</sub>       | OPFC, RDY, EN, VREF                      |                                      | -0.3   | 30.0                   | V    |

| V <sub>L</sub>       | IAC, VRMS, RT/CT, FBPFC, VEA             |                                      | -0.3   | 7.0                    | V    |

| V <sub>IEA</sub>     | IEA                                      |                                      | 0      | V <sub>VREF</sub> +0.3 | V    |

| V <sub>N</sub>       | ISENSE                                   |                                      | -5.0   | 0.7                    | V    |

| I <sub>AC</sub>      | Input AC Current                         |                                      |        | 1                      | mA   |

| I <sub>REF</sub>     | VREF Output Current                      |                                      | 5      | mA                     |      |

| I <sub>PFC-OUT</sub> | Peak PFC OUT Current, Source or S        |                                      | 0.5    | Α                      |      |

| P <sub>D</sub>       | Power Dissipation, T <sub>A</sub> < 50°C |                                      | 800    | mW                     |      |

| R <sub>⊙ j-a</sub>   | Thermal Resistance (Junction-to-Air)     |                                      | 104.10 | °C/W                   |      |

| R <sub>⊝ j-c</sub>   | Thermal Resistance (Junction-to-Case)    |                                      |        | 40.61                  | °C/W |

| $T_J$                | Operating Junction Temperature           |                                      | -40    | +125                   | °C   |

| T <sub>STG</sub>     | Storage Temperature Range                |                                      | -55    | +150                   | °C   |

| TL                   | Lead Temperature (Soldering)             |                                      | \      | +260                   | °C   |

| ECD                  |                                          | Human Body Model,<br>JESD22-A114     |        | 4.5                    | 12/  |

| ESD                  | Electrostatic Discharge Capability       | Charged Device Model,<br>JESD22-C101 |        | 1.0                    | kV   |

#### Notes:

- 1. All voltage values, except differential voltage, are given with respect to the GND pin.

- 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                           |  | Max. | Unit |  |

|----------------|-------------------------------------|--|------|------|--|

| T <sub>A</sub> | I. I ()nerating Ambient Lemperature |  | +105 | °C   |  |

### **Electrical Characteristics**

Unless otherwise noted; V<sub>DD</sub>=15V, T<sub>A</sub>= 25°C, T<sub>A</sub>=T<sub>J</sub>, R<sub>T</sub>=27k $\Omega$ , and C<sub>T</sub>=1000pF.

| Symbol                          | Parameter                                              | Conditions                                                                                              | Min. | Тур. | Max. | Units |

|---------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub> Section         |                                                        |                                                                                                         |      | •    |      |       |

| $V_{\text{DD-OP}}$              | Continuously Operating Voltage                         |                                                                                                         |      |      | 22   | V     |

| I <sub>DD ST</sub>              | Startup Current                                        | V <sub>DD</sub> =V <sub>TH-ON</sub> -0.1V; OPFC Open                                                    |      | 30   | 80   | μA    |

| I <sub>DD-OP</sub>              | Operating Current                                      | V <sub>DD</sub> =13V; OPFC Open                                                                         | 2.0  | 2.3  | 3.0  | mA    |

| $V_{\text{TH-ON}}$              | Turn-on Threshold Voltage                              |                                                                                                         | 10   | 11   | 12   | V     |

| $	riangle V_{TH}$               | Hysteresis                                             |                                                                                                         | 1.35 |      | 1.90 | V     |

| $V_{\text{DD-OVP}}$             | V <sub>DD</sub> OVP                                    |                                                                                                         | 27   | 28   | 29   | V     |

| $\triangle V_{\text{DD-OVP}}$   | V <sub>DD</sub> OVP Hysteresis                         |                                                                                                         |      | 1    |      | V     |

| Oscillator                      |                                                        |                                                                                                         |      |      |      |       |

| f <sub>OSC</sub>                | PFC Frequency                                          | $R_T$ =27k $\Omega$ , $C_T$ =1000pF                                                                     | 60   | 64   | 67   | kHz   |

| $f_{DV}^{(3)}$                  | Voltage Stability                                      | $11V \le V_{DD} \le 22V$                                                                                |      |      | 2    | %     |

| f <sub>DT</sub> <sup>(3)</sup>  | Temperature Stability                                  | -40°C ~ +105°C                                                                                          | V    |      | 2    | %     |

| $f_{TV}$                        | Total Variation                                        | Line, Temperature                                                                                       | 58   |      | 70   | kHz   |

| $f_{RV}$                        | Ramp Voltage                                           | Valley-to-Peak                                                                                          |      | 2.8  |      | V     |

| I <sub>OSC-DIS</sub>            | Discharge Current                                      | V <sub>RAMP</sub> =0V, V <sub>RT/CT</sub> =2.5V                                                         | 6.5  |      | 15.0 | mA    |

| f <sub>RANGE</sub>              | Frequency Range                                        |                                                                                                         | 50   |      | 75   | kHz   |

| t <sub>PFC-DEAD</sub>           | PFC Dead Time                                          | $R_T$ =27k $\Omega$ , $C_T$ =1000pF                                                                     | 400  | 600  | 800  | ns    |

| V <sub>REF</sub>                |                                                        |                                                                                                         |      |      |      |       |

| $V_{VREF}$                      | Reference Voltage                                      | I <sub>REF</sub> =0mA, C <sub>REF</sub> =0.1µF                                                          | 7.4  | 7.5  | 7.6  | V     |

| $\triangle V_{VREF1}$           | Load Regulation of Reference Voltage                   | $C_{REF}$ =0.1 $\mu$ F, $I_{REF}$ =0 $m$ A to 3.5 $m$ A $V_{VDD}$ =14 $V$ , Rise/Fall Time > 20 $\mu$ s |      | 30   | 50   | mV    |

| $\triangle V_{VREF2}$           | Line Regulation of Reference Voltage                   | C <sub>REF</sub> =0.1µF, V <sub>VDD</sub> =11V to 22V                                                   |      |      | 25   | mV    |

| $\triangle V_{VREF-DT}$         | Temperature Stability <sup>(3)</sup>                   | -40°C ~ +105°C                                                                                          |      | 0.4  | 0.5  | %     |

| $\triangle V_{VREF-TV}$         | Total Variation <sup>(3)</sup>                         | Line, Load, Temperature                                                                                 | 7.35 |      | 7.65 | V     |

| $\triangle V_{VREF-LS}$         | Long-Term Stability <sup>(3)</sup>                     | T <sub>J</sub> =125°C, 0 ~ 1000HRs                                                                      | 5    |      | 25   | mV    |

| I <sub>REF-MAX</sub>            | Maximum Current                                        | V <sub>VREF</sub> > 7.35V                                                                               | 5    |      | /-   | mA    |

| Brownout                        |                                                        |                                                                                                         |      | ı    |      |       |

| V <sub>RMS-UVL</sub>            | V <sub>RMS</sub> Threshold Low                         | When V <sub>RMS</sub> =1.05V at 75 V <sub>RMS</sub>                                                     | 1.00 | 1.05 | 1.10 | V     |

| V <sub>RMS-UVH</sub>            | V <sub>RMS</sub> Threshold High                        | When V <sub>RMS</sub> =1.9V at 85 • 1.414                                                               | 1.85 | 1.90 | 1.95 | V     |

| $\triangle V_{\text{RMS-UVP}}$  | Hysteresis                                             |                                                                                                         | 750  | 850  | 950  | mV    |

| t <sub>UVP</sub>                | Under-Voltage Protection<br>Debounce Time              |                                                                                                         | 340  | 410  | 480  | ms    |

| RDY Section                     | 1                                                      |                                                                                                         |      |      |      |       |

| V <sub>FBPFC-RD</sub>           | FBPFC Voltage Level to Pull Low Impedance with RDY Pin |                                                                                                         | 2.3  | 2.4  | 2.5  | V     |

| $\triangle V_{\text{FBPFC-RD}}$ | Hysteresis                                             |                                                                                                         | 1.15 | 1.25 | 1.35 | V     |

| I <sub>RDY-LEK</sub>            | Leakage Current of RDY<br>High Impedance               | V <sub>FBPFC</sub> <2.4V                                                                                |      |      | 500  | nA    |

| $V_{RDY-L}$                     | RDY Low Voltage                                        | I <sub>SINK</sub> =2mA                                                                                  |      |      | 0.5  | V     |

Continued on the following page...

### **Electrical Characteristics** (Continued)

Unless otherwise noted;  $V_{DD}$ =15V,  $T_A$ = 25°C,  $T_A$ = $T_J$ ,  $R_T$ =27k $\Omega$ , and  $C_T$ =1000pF.

| Symbol                    | Parameter                               | Conditions                                                                              | Min. | Тур. | Max.  | Units |

|---------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------|------|------|-------|-------|

| Voltage Erro              | r Amplifier                             |                                                                                         | 1    | u e  | ı     | l     |

| $V_{REF}$                 | Reference Voltage                       |                                                                                         | 2.45 | 2.50 | 2.55  | V     |

| A <sub>V</sub>            | Open-Loop Gain <sup>(3)</sup>           | At T <sub>A</sub> =25°C                                                                 | 35   | 42   |       | dB    |

| $Gm_V$                    | Transconductance                        | V <sub>NONINV</sub> =V <sub>INV</sub> , V <sub>VEA</sub> =3.75V at T <sub>A</sub> =25°C | 50   | 70   | 90    | µmho  |

| I <sub>FBPFC-L</sub>      | Maximum Source Current                  | V <sub>FBPFC</sub> =2V, V <sub>VEA</sub> =1.5V                                          | 40   | 50   |       | μA    |

| I <sub>FBPFC-H</sub>      | Maximum Sink Current                    | V <sub>FBPFC</sub> =3V, V <sub>VEA</sub> =6V                                            |      | -50  | -40   | μA    |

| I <sub>BS</sub>           | Input Bias Current                      |                                                                                         | -1   |      | 1     | μA    |

| $V_{VEA-H}$               | Output High Voltage on V <sub>VEA</sub> |                                                                                         | 5.8  | 6.0  |       | V     |

| $V_{VEA-L}$               | Output Low Voltage on V <sub>VEA</sub>  |                                                                                         |      | 0.1  | 0.4   | V     |

| Current Erro              | r Amplifier                             |                                                                                         |      |      |       |       |

| V <sub>ISENSE</sub>       | Input Voltage Range                     |                                                                                         | -1.5 |      | 0.7   | V     |

| Aı                        | Open-Loop Gain <sup>(3)</sup>           | At T <sub>A</sub> =25°C                                                                 | 40   | 50   |       | dB    |

| Gm <sub>I</sub>           | Transconductance                        | V <sub>NONINV</sub> =V <sub>INV</sub> , V <sub>IEA</sub> =3.75V                         | 75   | 88   | 100   | μmho  |

| V <sub>OFFSET</sub>       | Input Offset Voltage                    | V <sub>VEA</sub> =0V, I <sub>AC</sub> Open                                              | -10  |      | 10    | mV    |

| V <sub>IEA-H</sub>        | Output High Voltage                     |                                                                                         | 6.8  | 7.4  | 8.0   | V     |

| $V_{IEA-L}$               | Output Low Voltage                      |                                                                                         |      | 0.1  | 0.4   | V     |

| IL                        | Source Current                          | V <sub>ISENSE</sub> = -0.6V, V <sub>IEA</sub> =1.5V                                     | 35   | 50   |       | μΑ    |

| lμ                        | Sink Current                            | V <sub>ISENSE</sub> = +0.6V, V <sub>IEA</sub> =4.0V                                     |      | -50  | -35   | μΑ    |

| PFC OVP Co                | mparator                                |                                                                                         |      |      |       |       |

| $V_{FBPFC-OVP}$           | Over Voltage Protection                 |                                                                                         | 2.70 | 2.75 | 2.80  | V     |

| $\triangle V_{FBPFC-OVP}$ | PFC OVP Hysteresis                      |                                                                                         | 200  | 250  | 300   | mV    |

| Low-Power I               | Detect Comparator                       |                                                                                         |      |      | •     |       |

| V <sub>VEA-OFF</sub>      | VEA Voltage Off OPFC                    |                                                                                         | 0.2  | 0.3  | 0.4   | V     |

| PFC Soft-Sta              | nrt                                     | 1                                                                                       |      | l.   | ı     |       |

| V <sub>VEA_CLAMP</sub>    | PFC Soft-Start                          | V <sub>FBPFC</sub> < 2.4V                                                               | 2.2  | 2.8  | 3.3   | V     |

| EN Section                |                                         |                                                                                         | /    |      |       |       |

| V <sub>EN-H</sub>         | High Voltage Level of V <sub>EN</sub>   | V <sub>EN</sub> =V <sub>VREF</sub>                                                      | 7.4  | 7.5  | 7.6   | V     |

| V <sub>EN-L</sub>         | Low Voltage Level of V <sub>EN</sub>    | V <sub>EN</sub> =GND                                                                    |      | 0    |       | V     |

| Range                     |                                         |                                                                                         |      | l.   |       | I     |

| V <sub>VRMS-L</sub>       | RMS AC Voltage Low                      | When V <sub>VRMS</sub> =1.95V at 132V <sub>RMS</sub>                                    | 1.90 | 1.95 | 20.00 | V     |

| V <sub>VRMS-H</sub>       | RMS AC Voltage High                     | When V <sub>VRMS</sub> =2.45V at 150 V <sub>RMS</sub>                                   | 2.40 | 2.45 | 2.50  | V     |

| V <sub>VEA-L</sub>        | VEA Low                                 | When V <sub>VEA</sub> =1.95V at 30% Loading                                             | 1.90 | 1.95 | 2.00  | V     |

| V <sub>VEA-H</sub>        | VEA High                                | When V <sub>VEA</sub> =2.45V at 40% Loading                                             | 2.40 | 2.45 | 2.50  | V     |

| I <sub>TC</sub>           | Source Current from FBPFC               |                                                                                         | 18   | 20   | 22    | μA    |

Continued on the following page...

### **Electrical Characteristics** (Continued)

Unless otherwise noted;  $V_{DD}$ =15V,  $T_A$ = 25°C,  $T_A$ = $T_J$ ,  $R_T$ =27k $\Omega$ , and  $C_T$ =1000pF.

| Symbol                    | Parameter                                                         | Conditions                                                                                                | Min.  | Тур.  | Max.   | Units |

|---------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|

| Gain Modula               | ator                                                              |                                                                                                           |       |       |        | I.    |

| I <sub>AC</sub>           | Input for AC Current                                              | Multiplier Linear Range                                                                                   | 0     |       | 100    | μA    |

|                           |                                                                   | $I_{IAC}$ =17.67 $\mu$ A, $V_{VRMS}$ =1.080 $V_{FBPFC}$ =2.25 $V$ , at $T_A$ =25 $^{\circ}$ C             | 7.500 | 9.000 | 10.500 |       |

|                           |                                                                   | $I_{IAC}$ =20 $\mu$ A, $V_{VRMS}$ =1.224 $V_{VFBPFC}$ =2.25 $V$ , at $T_A$ =25 $^{\circ}$ C               | 6.367 | 7.004 | 7.704  |       |

| GAIN                      | Gain Modulator <sup>(3)(4)</sup>                                  | $I_{IAC}$ =25.69 $\mu$ A, $V_{VRMS}$ =1.585 $V$<br>$V_{FBPFC}$ =2.25 $V$ , at $T_A$ =25 $^{\circ}$ C      | 3.801 | 4.182 | 4.600  |       |

|                           |                                                                   | $I_{IAC}$ =51.62 $\mu$ A, $V_{VRM}$ S=3.169 $V_{VBPFC}$ =2.25 $V$ , at $T_A$ =25 $^{\circ}$ C             | 0.950 | 1.045 | 1.149  |       |

|                           |                                                                   | $I_{IAC}$ =62.23 $\mu$ A, $V_{VRMS}$ =3.803 $V_{VBPFC}$ =2.25 $V$ , at $T_A$ =25 $^{\circ}$ C             | 0.660 | 0.726 | 0.798  |       |

| BW                        | Bandwidth                                                         | I <sub>IAC</sub> =40μA                                                                                    |       | 2     |        | kHz   |

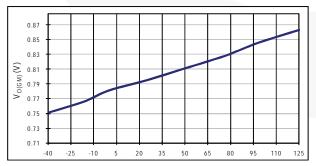

| $V_{O(GM)}$               | Output Voltage=5.7kΩ × (I <sub>SENSE</sub> -I <sub>OFFSET</sub> ) | $I_{AC}$ =20 $\mu$ A, $V_{RMS}$ =1.224 $V$<br>$V_{FBPFC}$ =2.25 $V$ , at $T_{A}$ =25 $^{\circ}$ C         | 0.710 | 0.798 | 0.885  | V     |

| PFC I <sub>LIMIT</sub> Co | mparator                                                          |                                                                                                           |       |       |        |       |

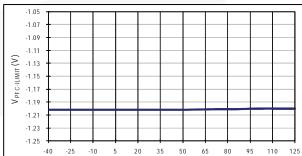

| V <sub>PFC-ILIMIT</sub>   | Peak Current Limit<br>Threshold Voltage<br>Cycle-by-Cycle Limit   |                                                                                                           | -1.25 | -1.15 | -1.05  | V     |

| $\triangle V_{pk}$        | PFC I <sub>LIMIT</sub> -Gain Modulator<br>Output                  | I <sub>IAC</sub> =17.67μA, V <sub>VRMS</sub> =1.08V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C | 200   |       |        | mV    |

| PFC Output                | Driver                                                            |                                                                                                           |       |       | •      |       |

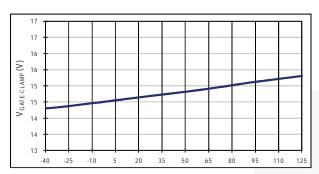

| $V_{\text{GATE-CLAMP}}$   | Gate Output Clamping<br>Voltage                                   | V <sub>DD</sub> =22V                                                                                      | 13    | 15    | 17     | V     |

| $V_{GATE-L}$              | Gate Low Voltage                                                  | V <sub>DD</sub> =15V; I <sub>O</sub> =100mA                                                               |       |       | 1.5    | V     |

| V <sub>GATE-H</sub>       | Gate High Voltage                                                 | V <sub>DD</sub> =13V; I <sub>O</sub> =100mA                                                               | 8     |       |        | V     |

| t <sub>R</sub>            | Gate Rising Time                                                  | V <sub>DD</sub> =15V; C <sub>L</sub> =4.7nF;<br>O/P= 2V to 9V                                             | 40    | 70    | 120    | ns    |

| t <sub>F</sub>            | Gate Falling Time                                                 | V <sub>DD</sub> =15V; C <sub>L</sub> =4.7nF;<br>O/P= 9V to 2V                                             | 40    | 60    | 110    | ns    |

| D <sub>PFC-MAX</sub>      | Maximum Duty Cycle                                                | V <sub>IEA</sub> <1.2V                                                                                    | 94    | 97    |        | %     |

| D <sub>PFC-MIN</sub>      | Minimum Duty Cycle                                                | V <sub>IEA</sub> >4.5V                                                                                    |       |       | 0      | %     |

| Tri-Fault Det             | tect                                                              |                                                                                                           |       |       |        |       |

| t <sub>FBPFC_OPEN</sub>   | Time to FBPFC Open                                                | V <sub>FBPFC</sub> =V <sub>FBPFC-OVP</sub> to FBPFC<br>OPEN, 470pF from FBPFC to GND                      |       | 2     | 4      | ms    |

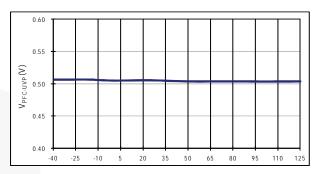

| $V_{PFC-UVP}$             | PFC Feedback Under-<br>Voltage Protection                         |                                                                                                           | 0.4   | 0.5   | 0.6    | V     |

#### Notes:

- This parameter, although guaranteed by design, is not 100% production tested.

This gain is the maximum gain of modulation with a given V<sub>RMS</sub> voltage when V<sub>EA</sub> is saturated to high.

### **Typical Performance Characteristics**

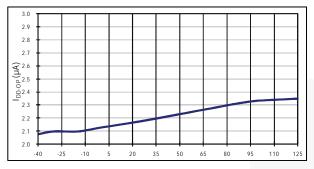

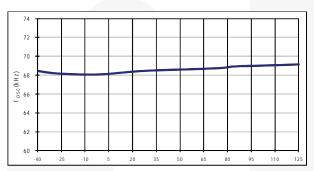

Figure 5. I<sub>DD-OP</sub> vs. Temperature

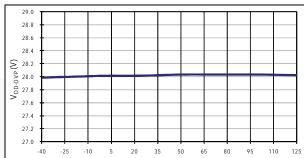

Figure 6. V<sub>DD-OVP</sub> vs. Temperature

Figure 7. fosc vs. Temperature

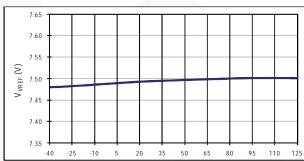

Figure 8. V<sub>VREF</sub> vs. Temperature

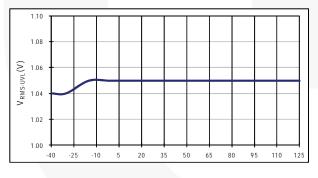

Figure 9. V<sub>RMS-UVL</sub> vs. Temperature

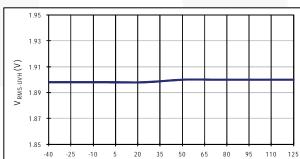

Figure 10. V<sub>RMS-UVH</sub> vs. Temperature

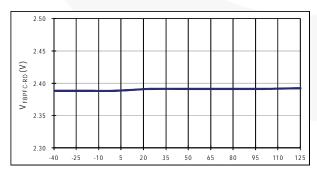

Figure 11. V<sub>FBPFC-RD</sub> vs. Temperature

Figure 12. I<sub>RDY-LEK</sub> vs. Temperature

### **Typical Performance Characteristics** (Continued)

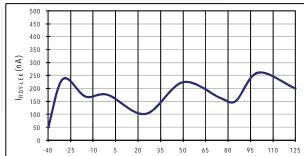

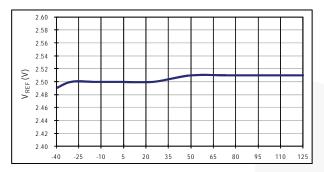

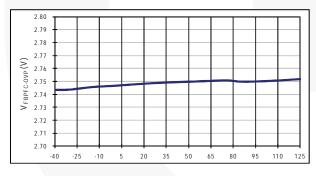

Figure 13. V<sub>REF</sub> vs. Temperature

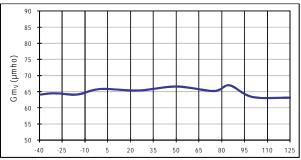

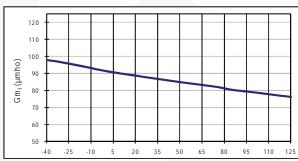

Figure 14. Gm<sub>V</sub> vs. Temperature

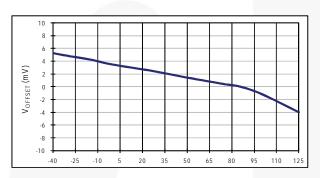

Figure 15. V<sub>OFFSET</sub> vs. Temperature

Figure 16. Gm<sub>I</sub> vs. Temperature

Figure 17. V<sub>FBPFC-OVP</sub> vs. Temperature

Figure 18. I<sub>TC</sub> vs. Temperature

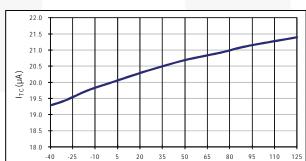

Figure 19. V<sub>O(GM)</sub> vs. Temperature

Figure 20. V<sub>PFC-ILIMIT</sub> vs. Temperature

### **Typical Performance Characteristics** (Continued)

Figure 21.  $V_{GATE-CLAMP}$  vs. Temperature

Figure 22.  $V_{\text{PFC-UVP}}$  vs. Temperature

### **Functional Description**

#### **Oscillator**

The internal oscillator frequency of FAN6982 is determined by the timing resistor and capacitor on the RT/CT pin, but note that the optimum operation for FAN6982 is between 50 and 75kHz. The frequency of the internal oscillator is given by:

$$f_{OSC} = \frac{1}{0.56 \cdot R_T \cdot C_T + 360C_T} \tag{1}$$

The dead time for the PFC gate drive signal is determined by

$$t_{DEAD} = 360C_T \tag{2}$$

The dead time should be smaller than 2% of switching period to minimize line current distortion around line zero crossing.

#### **Gain Modulator**

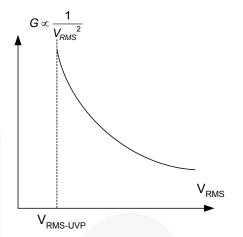

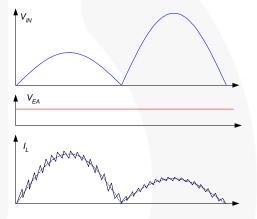

Gain modulator is the key block for PFC stage because it provides the reference to the current control error amplifier for the input current shaping, as shown in Figure 23. The output current of gain modulator is a function of  $V_{\text{EA}}$ ,  $I_{\text{AC}}$  and  $V_{\text{RMS}}$ . The gain of the gain modulator is given as a ratio between  $I_{\text{MO}}$  and  $I_{\text{AC}}$  with a given  $V_{\text{RMS}}$  when  $V_{\text{EA}}$  is saturated to high. The gain is inversely proportional to  $V_{\text{RMS}}^2$ , as shown in Figure 24, to implement line feed-forward. This automatically adjusts the reference of current control error amplifier according to the line voltage such that the input power of PFC converter is not changed with line voltage, as shown in, Figure 25.

Figure 23. Gain Modulator Block

Figure 24. Modulation Gain Characteristics

Figure 25. Line Feed-Forward Operation

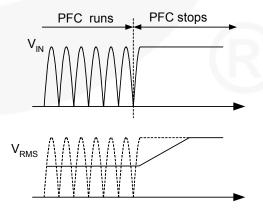

To sense the RMS value of the line voltage, an averaging circuit with two poles is typically employed as shown in Figure 23. Notice that the input voltage of PFC is clamped at the peak of the line voltage once PFC stops switching since the junction capacitance of bridge diode is not discharged, as shown in Figure 26.

Therefore, the voltage divider for  $V_{\text{RMS}}$  should be designed considering the brownout protection trip point and minimum operation line voltage.

Figure 26. V<sub>RMS</sub> According to the PFC Operation

The rectified sinusoidal signal is obtained by the current flowing into the IAC pin. The resistor  $R_{\text{IAC}}$  should be large enough to prevent saturation of the gain modulator as:

$$\frac{\sqrt{2}V_{LINE.BO}}{R_{IAC}} \cdot G^{MAX} < 159 \mu A \tag{3}$$

where  $V_{\text{LINE,BO}}$  is the line voltage that trips brownout protection,  $G^{MAX}$  is the maximum modulator gain when  $V_{\text{RMS}}$  is 1.08V, and 159 $\mu$ A is the maximum output current of the gain modulator.

#### **Current-Control of Boost Stage**

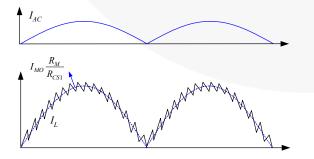

As shown in Figure 27 the FAN6982 employs two control loops for power factor correction, a current-control loop and a voltage-control loop. The current-control loop shapes inductor current, as shown in Figure 28, based on the reference signal obtained at IAC pin as:

Figure 27. Gain Modulation Block

Figure 28. Inductor Current Shaping

The current-control feedback loop also has a pulse-bypulse current limit comparator that forces the PFC switch to turn off if the ISENSE pin voltage drops below -1.15V until the next switching cycle.

#### **Voltage-Control of Boost Stage**

The voltage-control loop regulates PFC output voltage using internal error amplifier such that the FBPFC voltage is same as internal reference of 2.5V.

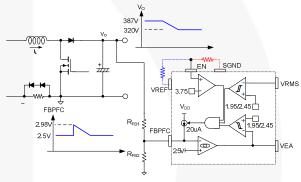

To improve system efficiency at low AC line voltage and light-load condition, FAN6982 provides adjustable PFC output voltage. As shown in Figure 29, FAN6982 monitors  $V_{EA}$  and  $V_{RMS}$  to adjust the PFC output voltage. When  $V_{EA}$  and  $V_{RMS}$  are lower than thresholds, internal current source of  $20\mu A$  is enabled that flows through  $R_{FB2}$ , increasing the voltage of the FBPFC pin. This causes the PFC output voltage to reduce when  $20\mu A$  is enabled as:

$$V_{OPFC2} = \frac{R_{FB1} + R_{FB2}}{R_{FB2}} \times (2.5 - 20 \mu A \times R_{FB2})$$

(5)

Figure 29. Block of Adjustable PFC Output

#### **Brownout Protection**

FAN6982 has a built-in internal brownout protection comparator monitoring the voltage of the VRMS pin. Once the VRMS pin voltage is lower than 1.05V, the PFC stage is shutdown to protect the system from over current. FAN6982 starts up the boost stage once the VRMS voltage increases above 1.9V.

#### TriFault Detect™

To improve power supply reliability, reduce system component count, and simplify compliance to UL 1950 safety standards; the FAN6982 includes TriFault Detect technology. This feature monitors FBPFC for certain PFC fault conditions.

In the case of a feedback path failure, the output of the PFC could exceed operating limits. Should FBPFC go too low, or too high, or open; TriFault Detect senses the error and terminates the PFC output drive.

TriFault detect is an entirely internal circuit. It requires no external components to serve its protective function.

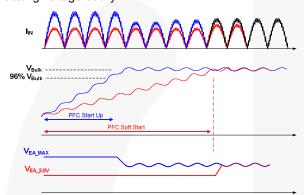

#### **PFC Soft-Start Function**

The FAN6982 PFC soft-start function is shown in Figure 30. When bulk voltage is under the 96% of setting voltage;  $V_{EA}$  clamps to 2.8V, the output current of multiplier cuts half, the rectifier line current is limited by current loop, and PFC output rise time increases.

When bulk voltage is over 96%, the clamping function is disabled, and the bulk voltage can be regulated by voltage error amplifier.

There have two advantages with PFC soft-start: one is the MOSFET experience of current is reduced, which can obtain more de-rating with MOSFET current level. The other one is to reduce the overshoot of PFC bulk voltage at the rising time because the charge current becomes small, the bulk voltage can not exceed to setting voltage easily.

Figure 30. PFC Soft-Start

#### **RDY Function**

The FAN6982 RDY function, is shown in Figure 31, is controlled by voltage of FBPFC. If the voltage of FBPFC is over than 96% of 2.5V, the RDY pin is connected to SGND. If the FBPFC is under the 46% of 2.5V, the RDY appears open-drain situation. Usually the capacitor is parallel with the RDY pin to prevent the layout noise.

The PNP transistor can control the AHB LLC or dualforward controller on the same side or the "op-to" to control the LLC controller on the other side.

Figure 31. RDY Application Circuit

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

FAN6982MY

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию .

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331