# Low Quiescent Current, Programmable Delay Time, Supervisory Circuit

The NCP308 series is one of the ON Semiconductor Supervisory circuit IC families. It is optimized to monitor system voltages from 0.405 V to 5.5 V, asserting an active low open–drain  $\overline{RESET}$  output, together with Manual Reset ( $\overline{MR}$ ) Input. The part comes with both fixed and externally adjustable versions.

#### **Features**

- Wide Supply Voltage Range 1.6 to 5.5 V

- Very Low Quiescent Current 1.6 μA

- Fixed Threshold Voltage Versions for Standard Voltage Rails Including 0.9 V, 1.2 V, 1.25 V, 1.5 V, 1.8 V, 1.9 V, 2.5 V, 2.8 V, 3.0 V, 3.3 V, 5.0 V

- Adjustable Version with Low Threshold Voltage 0.405 V (min)

- High Threshold Voltage Accuracy: 0.31% typ

- Support Manual Reset Input (MR)

- Open–Drain RESET Output (Push–pull Output upon Request)

- Flexible Delay Time Programmability: 1.25 ms to 10 s

- Temperature Range: -40°C to +125°C

- Small TSOP-6 and WDFN6 2 x 2 mm, Pb-Free packages

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb–Free Devices

# **Typical Applications**

- DSP or Microcontroller Applications

- Notebook/Desktop Computers

- PDAs/Hand-Held Products

- Portable/Battery-Powered Products

- FPGA/ASIC Applications

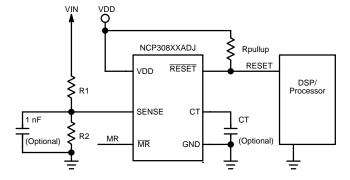

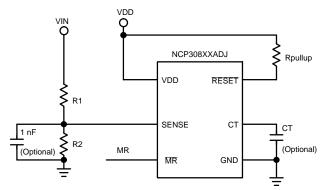

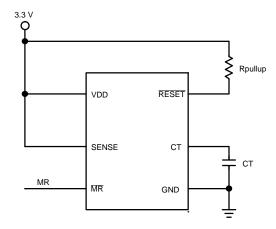

Figure 1. Typical Application Circuit for Adjustable Versions

# ON Semiconductor®

www.onsemi.com

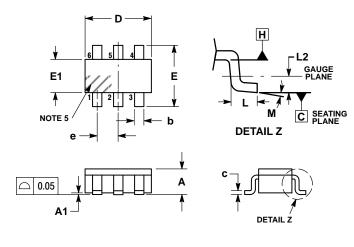

#### MARKING DIAGRAMS

TSOP-6 CASE 318G

WDFN6 CASE 511BR

XXX, XX= Specific Device Code

A =Assembly Location

Y = Year

W = Work Week

M = Date Code

■ Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the ordering information section on page 9 of this data sheet.

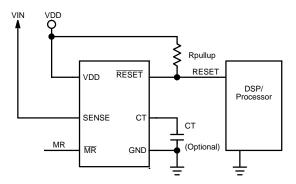

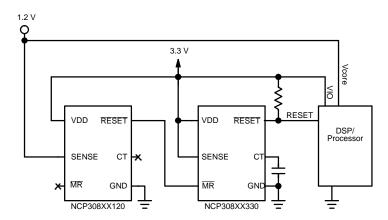

Figure 2. Typical Application Circuit for Fixed Versions

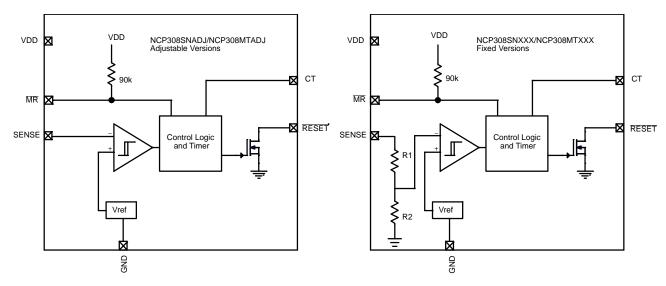

Figure 3. Functional Block Diagrams of Adjustable and Fixed Versions

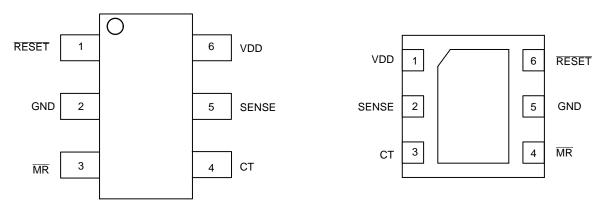

Figure 4. Pin Connections Diagram (Top View)

**Table 1. PIN OUT DESCRIPTION**

|            | Pin Number TSOP-6 WDFN6 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       |                         |                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD        | 6                       | 1              | <b>Supply Voltage</b> . A 0.1uF ceramic capacitor placed close to this pin is helpful for transient and parasitic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SENSE      | 5                       | 2              | <b>Sense Input</b> , this is the voltage to be monitored. If the voltage at this terminal drops below the threshold voltage V <sub>IT</sub> , then RESET is asserted. SENSE does not necessary monitor VDD, it can monitor any voltage lower than VDD.                                                                                                                                                                                                                                                                                                                                                                                                |

| СТ         | 4                       | 3              | Reset Delay Time Setting Pin. Connecting this pin to VDD through a 40 k $\Omega$ to 200 k $\Omega$ resistor or leaving it open results in fixed reset delay times. Connecting this pin to a ground referenced capacitor ( $\geq$ 100 pF) gives a user–programmable reset delay time. See the Setting Reset Delay Time section for more information.                                                                                                                                                                                                                                                                                                   |

| MR         | 3                       | 4              | <b>Manual Reset input</b> , MR low asserts RESET. MR is internally tied to VDD by a 90 kΩ pull–up Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

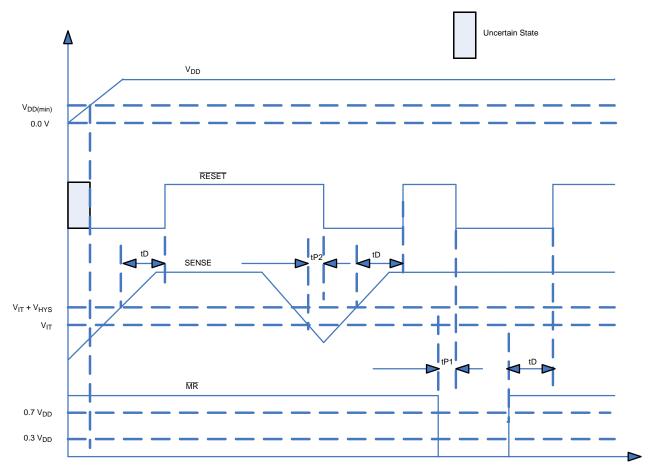

| RESET      | 1                       | 6              | <b>RESET Output</b> , is an Active low open drain N–Channel MOSFET output, it is driven to a low impedance state when $\overline{\text{RESET}}$ is asserted (either the SENSE input is lower than the threshold voltage (V <sub>IT</sub> ) or the $\overline{\text{MR}}$ pin is set to a logic low). RESET will keep low (asserted) for the reset delay time after both SENSE is above V <sub>IT</sub> and $\overline{\text{MR}}$ is set to a logic high. A pull–up resistor from $10\text{k}\Omega$ to $1\text{M}\Omega$ should be used on this pin. See Figure 5 for behavior of RESET depends on VDD, SENSE and $\overline{\text{MR}}$ conditions. |

| GND        | 2                       | 5              | Ground terminal. Should be connected to PCB ground reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EXP<br>PAD | _                       | Exposed<br>Pad | Exposed pad, under WDFN6 package, connect it to ground plane for better thermal dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Figure 5. Timing Diagram Showing MR and SENSE Reset Timing

Table 2. TRUTH TABLE

| MR | SENSE > V <sub>IT</sub> | RESET |

|----|-------------------------|-------|

| L  | N                       | L     |

| L  | Y                       | L     |

| Н  | N                       | L     |

| Н  | Y                       | Н     |

**Table 3. MAXIMUM RATINGS**

| Rating                                                                     | Symbol           | Value                            | Unit    |

|----------------------------------------------------------------------------|------------------|----------------------------------|---------|

| Input voltage range, V <sub>DD</sub>                                       | $V_{DD}$         | -0.3 to + 6.0                    | V       |

| CT voltage range V <sub>CT</sub> , RESET, MR<br>Current through CT pin     | Іст              | $-0.3$ to $V_{DD} + 0.3 \le 6.0$ | V<br>mA |

| SENSE pin voltage                                                          |                  | -0.3 to + 8.0                    | V       |

| RESET pin current                                                          |                  | 5                                | mA      |

| Thermal Resistance Junction-to-Air<br>TSOP-6<br>WDFN6                      | $R_{	hetaJA}$    | 305<br>220                       | °C/W    |

| Human Body Model (HBM) ESD Rating (Note 1)                                 | ESD HBM          | 2000                             | V       |

| Machine Model (MM) ESD Rating (Note 1)                                     | ESD MM           | 100                              | V       |

| Charged Device Model (CDM) ESD Rating (Note 1)                             | ESD CDM          | 500                              | V       |

| Latch up Current: (Note 2) All pins, except digital pins Digital pins (MR) | I <sub>LU</sub>  | ±100<br>±10                      | mA      |

| Storage Temperature Range                                                  | T <sub>STG</sub> | -65 to + 150                     | °C      |

| Maximum Junction Temperature                                               | TJ               | -40 to +150                      | °C      |

| Moisture Sensitivity (Note 3)                                              | MSL              | Level 1                          |         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 3. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

This device series contains ESD protection and passes the following tests:

Human Body Model (HBM) +/-2.0 kV per JEDEC standard: JESD22-A114

Machine Model (MM) +/-100 V per JEDEC standard: JESD22-A115

Charged Device Model (CDM) 500 V per JEDEC standard: JESD22-C101.

Latch up Current per JEDEC standard: JESD78 class II.

**Table 4. ELECTRICAL CHARACTERISTICS** 1.6 V ≤  $V_{DD}$  ≤ 5.5 V,  $R_{pullup}$  = 100 kΩ,  $C_{LRESET}$  = 50 pF, over operating temperature range ( $T_{J}$  = -40°C to +125°C), unless otherwise specified. Typical values are at  $T_{J}$  = +25°C.

| Symbol                | Parameter                                         |                                                           | Conditions                                                                      | Min                 | Тур                       | Max                 | Unit             |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------------|---------------------|------------------|

| V <sub>DD</sub>       | Supply Voltage Ra                                 | nge                                                       | −40°C < T <sub>J</sub> < +125°C                                                 | 1.6                 |                           | 5.5                 | V                |

| V <sub>DD</sub> (min) | Minimum V <sub>DD</sub> Gua<br>Output Valid (Note | ranteed RESET<br>4)                                       |                                                                                 |                     | 0.5                       | 0.8                 | V                |

| I <sub>DD</sub>       | Supply Current (Current into VDD pin)             |                                                           | V <sub>DD</sub> = 3.3V, RESET not asserted MR, RESET, CT open                   |                     | 1.6                       | 5.0                 | μΑ               |

|                       |                                                   |                                                           | V <sub>DD</sub> = 5.5V, RESET not asserted MR, RESET, CT open                   |                     | 1.6                       | 6.0                 |                  |

| V <sub>OL</sub>       | Low-level output v                                | oltage of RESET                                           | $1.3V \le V_{DD} < 1.6V$ , $I_{OL} = 0.4 \text{ mA}$                            |                     |                           | 0.3                 | V                |

|                       |                                                   |                                                           | $1.6V \le V_{DD} \le 5.5V$ , $I_{OL} = 1.0 \text{ mA}$                          |                     |                           | 0.4                 |                  |

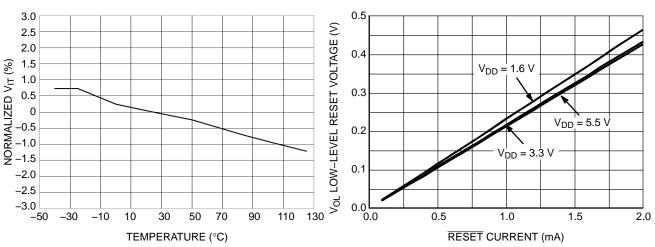

| V <sub>IT</sub> %     | Negative going SE                                 | NSE threshold                                             |                                                                                 | -1.75               | ±0.75                     | +1.75               | %                |

|                       | voltage accuracy                                  |                                                           | T <sub>J</sub> = +25°C                                                          | -0.31               | -                         | 0.31                |                  |

|                       |                                                   |                                                           | −20°C < T <sub>J</sub> < +85°C                                                  | -1.0                | ±0.5                      | +1.0                |                  |

| V <sub>HYS</sub>      | Hysteresis on                                     | 1.6V≤V <sub>DD</sub> ≤4.2V                                |                                                                                 |                     | 1.0                       | 3.0                 | %V <sub>IT</sub> |

|                       | V <sub>IT</sub>                                   | 4.2V≤V <sub>DD</sub> ≤5.5V                                |                                                                                 |                     | 1.75                      | 3.75                |                  |

| R <sub>MR</sub>       | MR Internal pull-up                               | resistance                                                |                                                                                 |                     | 90                        |                     | kΩ               |

| I <sub>SENSE</sub>    | Input current at<br>SENSE pin                     | NCP308XXADJ                                               | V <sub>SENSE</sub> = V <sub>IT</sub>                                            |                     | 10                        |                     | nA               |

|                       |                                                   | Fixed versions                                            | V <sub>SENSE</sub> = 5.5 V                                                      |                     | 110                       |                     |                  |

| I <sub>OH</sub>       | RESET leakage C                                   | urrent                                                    | V <sub>RESET</sub> = 5.5 V, RESET not asserted                                  |                     |                           | 300                 | nA               |

| C <sub>IN</sub>       | Input                                             | CT pin                                                    | $V_{IN} = 0 V \text{ to } V_{DD}$                                               |                     | 5                         |                     | pF               |

|                       | capacitance, any pin                              | Other pins                                                | V <sub>IN</sub> = 0 V to 5.5 V                                                  |                     | 5                         |                     |                  |

| V <sub>IL</sub>       | MR logic low input                                |                                                           |                                                                                 | 0                   |                           | 0.3 V <sub>DD</sub> | V                |

| V <sub>IH</sub>       | MR logic high inpu                                | t                                                         |                                                                                 | 0.7 V <sub>DD</sub> |                           | V <sub>DD</sub>     | V                |

| tw                    | Input pulse width to assert RESET MR              | SENSE                                                     | V <sub>IH</sub> = 1.05 V <sub>IT</sub> , V <sub>IL</sub> = 0.95 V <sub>IT</sub> |                     | 20                        |                     | μS               |

|                       |                                                   | MR                                                        | $V_{IH} = 0.7 \ V_{DD}, \ V_{IL} = 0.3 \ V_{DD}$                                |                     | 150                       |                     |                  |

| t <sub>D</sub>        | Reset delay time                                  | $C_T = Open$ $C_T = V_{DD}$ $C_T = 100 pF$ $C_T = 180 nF$ | (Guaranteed by design and characterization)                                     |                     | 20<br>300<br>1.25<br>1200 |                     | ms               |

| t <sub>P1</sub>       | Propagation delay from MR                         | MR to RESET                                               | $V_{IH} = 0.7 V_{DD}, V_{IL} = 0.3 V_{DD}$                                      |                     | 150                       |                     | ns               |

| t <sub>P2</sub>       | Propagation<br>delay from<br>SENSE                | SENSE to<br>RESET                                         | $V_{IH} = 1.05 \ V_{IT}, \ V_{IL} = 0.95 \ V_{IT}$                              |                     | 20                        |                     | μS               |

<sup>4.</sup> The lowest supply voltage (VDD) at which RESET becomes active.

5. NCP308XX: XX = MT (WDFN6 package) or SN (TSOP-6 package).

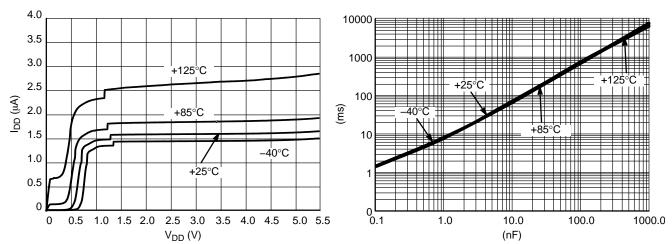

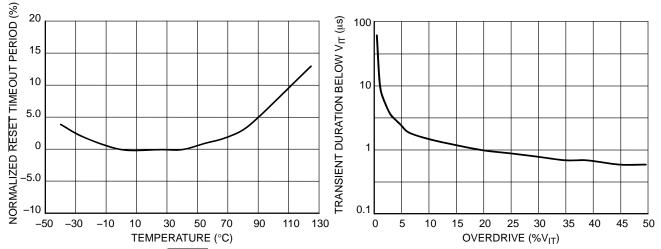

## TYPICAL OPERATING CHARACTERISTICS

Figure 6. Supply Current vs. Input Voltage

Figure 7. RESET Timeout Period vs. CT

Figure 8. Normalized RESET Timeout Period vs.

Temperature

Figure 9. Maximum Transient Duration at Sense vs. Sense Threshold Overdrive Voltage

Figure 10. Normalized Sense Threshold Voltage (V<sub>IT</sub>) vs. Temperature

Figure 11. Low-Level RESET Voltage vs. RESET Current

#### DETAILED DESCRIPTION

The NCP308 microprocessor supervisory product family is designed to assert a  $\overline{RESET}$  signal when either the SENSE pin voltage drops below  $V_{IT}$  or the Manual Reset input  $(\overline{MR})$  is driven low. The  $\overline{RESET}$  output remains asserted for a programmable delay time after both  $\overline{MR}$  and SENSE voltages return above the respective thresholds. A broad range of voltage threshold and reset delay time options are available, allowing NCP308 series to be used in a wide range of applications.

Reset threshold voltages can be factory–set from 0.82 V to 3.3 V or from 4.4 V to 5.0 V, while the NCP308XXADJ can be used for any voltage above 0.405 V using an external resistor divider.

Flexible delay time can be easily got with CT pin according to Table 5:

**Table 5. DELAY TIME SETTING TABLE**

| CT pin Configuration                                                                   | Delay Time (tD)                                                                            |  |  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| CT = VDD                                                                               | 300 ms (fixed)                                                                             |  |  |

| CT = Open                                                                              | 20 ms (fixed)                                                                              |  |  |

| Connecting a capacitor be-<br>tween pin CT and GND<br>(Capacitor CT value ><br>100 pF) | 1.25 ms ~ 10 s, depends on capacitor value (Refer to the Setting Reset Delay Time Section) |  |  |

#### Output

The  $\overline{RESET}$  output is typically connected to the  $\overline{RESET}$  control pin of a microprocessor. For Open–Drain output versions, a pull–up resistor must be used to hold this line high when  $\overline{RESET}$  is not asserted. The  $\overline{RESET}$  output is active once  $V_{DD}$  is over  $V_{DD}$ (min), this voltage is much lower than most microprocessors' functional voltage range.  $\overline{RESET}$  remains high as long as SENSE is above its threshold ( $V_{IT}$ ) and the Manual Reset input ( $\overline{MR}$ ) is logic high. If either SENSE falls below  $V_{IT}$  or  $\overline{MR}$  is driven low,  $\overline{RESET}$  is asserted.

Once  $\overline{MR}$  is again logic high and SENSE is above (V<sub>IT</sub> + V<sub>HYS</sub>), the  $\overline{RESET}$  pin goes to a high impedance state after delay time (tD). The open–drain structure of  $\overline{RESET}$  is capable to allow the reset signal for the microprocessor to have a voltage higher than V<sub>DD</sub> (up to 5.5 V). The pull–up resistor should be no smaller than 10 k $\Omega$  as a result of the finite impedance of the  $\overline{RESET}$  line.

## **SENSE Input**

The SENSE input should be connected to the monitored voltage directly. If the voltage on this pin drops below  $V_{IT}$ , then  $\overline{RESET}$  is asserted. The comparator has a built—in hysteresis to prevent erratic reset operation. It is good practice to put a 1 nF to 10 nF bypass capacitor on the SENSE input to reduce its sensitivity to transients and layout parasitic.

The NCP308XXADJ can be used to monitor any voltage rail down to 0.405 V by the circuit shown in Figure 12. The new  $V_{\text{IT}}$ ' can be derived from resistor divider network of R1 and R2 by:

$$V_{IT}' = \left(\frac{R1}{R2} + 1\right) \times V_{IT}$$

(eq. 1)

Figure 12. Using NCP308XXADJ to Monitor a User-Defined Threshold Voltage

#### Manual Reset Input (MR)

The Manual Reset input  $(\overline{MR})$  allows a processor or other logic circuits to initiate a reset. A logic low on  $\overline{MR}$  causes  $\overline{RESET}$  to assert. After  $\overline{MR}$  returns to a logic high and SENSE is above its reset threshold,  $\overline{RESET}$  is de–asserted after the delay time set by CT pin.  $\overline{MR}$  is internally tied to  $V_{DD}$  by a 90 k $\Omega$  resistor so this pin can be left unconnected if  $\overline{MR}$  will not be used.

Figure 13 shows how  $\overline{MR}$  can be used to monitor multiple system voltages (e.g. I/O supply voltage of some DSP/processors should be setup before core voltage, and DSP/processor can only start after both I/O and core voltages setup).

Figure 13. Using MR to Monitor Multiple System Voltages

# **Setting Reset Delay Time**

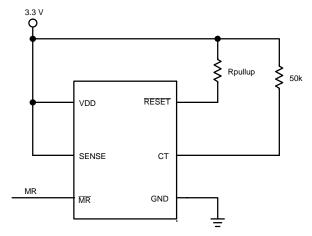

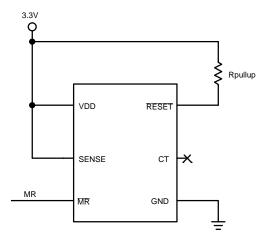

The NCP308 has three options for setting the reset delay time as shown in Table 5. Figure 14 shows the configuration for a fixed 300 ms typical delay time by tying CT to  $V_{DD}$ ; a resistor from 40 k $\Omega$  to 200 k $\Omega$  must be used. Figure 15 shows a fixed 20 ms delay time by leaving the CT pin unconnected.

Figure 16 shows a user-defined program time between 1.25 ms and 10 s by connecting a capacitor between CT pin and ground.

Figure 14. Delay Time Fixed to 300 ms when CT Connected to VDD by Resistor

Figure 15. Delay Time Fixed to 20 ms when CT is Open

Figure 16. Delay Time Set by Capacitor

The capacitor CT should be  $\geq 100$  pF for NCP308 to recognize that the capacitor is present. The capacitor value for a given delay time can be calculated using the following equation:

$CT(nF) = (tD(s) - 0.5 \times 10^{-3}(s)) \times 175$  (eq. 2)

Parasitic capacitances of CT pin should be considered to avoid reset delay time deviation or error.

threshold overdrive, as shown in the Maximum Transient Duration at Sense vs. Sense Threshold Overdrive Voltage graph (Figure 9) in Typical Operating Characteristics section.

# **Immunity to Sense Pin Voltage Transients**

NCP308 is relatively immune to short negative transients on SENSE pin. Sensitivity to transients is dependent on

# **ORDERING INFORMATION**

| Device          | Status (Note 6) | Threshold<br>Voltage<br>(V <sub>IT</sub> ) | Nominal<br>Monitored<br>Voltage | Marking | Package            | Shipping <sup>†</sup> |

|-----------------|-----------------|--------------------------------------------|---------------------------------|---------|--------------------|-----------------------|

| NCP308SNADJT1G  | Active          | 0.405 V                                    | Adjustable                      | ADJ     |                    |                       |

| NCV308SNADJT1G* | Active          | 0.405 V                                    | Version                         | VDJ     |                    |                       |

| NCP308SN090T1G  | Active          | 0.84 V                                     | 0.9 V                           | 090     |                    |                       |

| NCP308SN120T1G  | Active          | 1.12 V                                     | 1.2 V                           | 120     |                    |                       |

| NCP308SN125T1G  | Active          | 1.16 V                                     | 1.25 V                          | 125     |                    |                       |

| NCP308SN150T1G  | Active          | 1.40 V                                     | 1.5 V                           | 150     |                    |                       |

| NCP308SN180T1G  | Active          | 1.67 V                                     | 1.8 V                           | 180     | TSOP-6             |                       |

| NCP308SN190T1G  | Active          | 1.77 V                                     | 1.9 V                           | 190     | (Pb-Free)          |                       |

| NCP308SN250T1G  | Active          | 2.33 V                                     | 2.5 V                           | 250     |                    |                       |

| NCP308SN280T1G  | Active          | 2.61 V                                     | 2.8 V                           | 280     |                    | 3000 / Tape & Reel    |

| NCP308SN300T1G  | Active          | 2.79 V                                     | 3.0 V                           | 300     |                    |                       |

| NCP308SN330T1G  | Active          | 3.07 V                                     | 3.3 V                           | 330     |                    |                       |

| NCV308SN330T1G* | Active          | 3.07 V                                     | 3.3 V                           | 33A     |                    |                       |

| NCP308SN500T1G  | Active          | 4.65 V                                     | 5.0 V                           | 500     |                    |                       |

| NCP308MTADJTBG  | Active          | 0.405 V                                    | Adjustable<br>Version           | AA      |                    |                       |

| NCP308MT090TBG  | Active          | 0.84 V                                     | 0.9 V                           | AC      | 1                  |                       |

| NCP308MT120TBG  | Active          | 1.12 V                                     | 1.2 V                           | AD      |                    |                       |

| NCP308MT125TBG  | Active          | 1.16 V                                     | 1.25 V                          | AE      |                    |                       |

| NCP308MT150TBG  | Active          | 1.40 V                                     | 1.5 V                           | AF      |                    |                       |

| NCP308MT180TBG  | Active          | 1.67 V                                     | 1.8 V                           | AG      | WDFN6<br>(Pb-Free) |                       |

| NCP308MT190TBG  | Active          | 1.77 V                                     | 1.9 V                           | AH      |                    |                       |

| NCP308MT250TBG  | Active          | 2.33 V                                     | 2.5 V                           | AJ      |                    |                       |

| NCP308MT280TBG  | Active          | 2.61 V                                     | 2.8 V                           | AK      |                    |                       |

| NCP308MT300TBG  | Active          | 2.79 V                                     | 3.0 V                           | AL      |                    |                       |

| NCP308MT330TBG  | Active          | 3.07 V                                     | 3.3 V                           | AM      |                    |                       |

| NCP308MT500TBG  | Active          | 4.65 V                                     | 5.0 V                           | AN      |                    |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Canable

<sup>6.</sup> The marketing status are defined as below:

Active: Products in production and recommended for new designs;

Under Request: Device has been announced but is not in production. Samples may or may not be available.

# **PACKAGE DIMENSIONS**

## TSOP-6 CASE 318G-02 ISSUE U

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

4. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D AND E1 ARE DETERMINED AT DATUM H.

5. PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   | 0.90        | 1.00 | 1.10 |  |

| A1  | 0.01        | 0.06 | 0.10 |  |

| b   | 0.25        | 0.38 | 0.50 |  |

| С   | 0.10        | 0.18 | 0.26 |  |

| D   | 2.90        | 3.00 | 3.10 |  |

| Е   | 2.50        | 2.75 | 3.00 |  |

| E1  | 1.30        | 1.50 | 1.70 |  |

| е   | 0.85        | 0.95 | 1.05 |  |

| L   | 0.20        | 0.40 | 0.60 |  |

| L2  | 0.25 BSC    |      |      |  |

| м   | 0° 10°      |      |      |  |

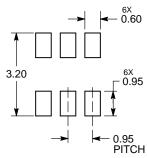

# **RECOMMENDED SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

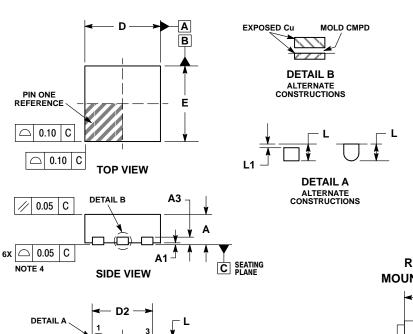

#### PACKAGE DIMENSIONS

## WDFN6 2x2, 0.65P CASE 511BR **ISSUE O**

F2

Φ

0.10 (M)

0.05 (M)

С Α В

С

NOTE 3

| | |

**BOTTOM VIEW**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25 mm FROM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| TAD AO WELE AO THE TETIN |             |      |  |  |

|--------------------------|-------------|------|--|--|

|                          | MILLIMETERS |      |  |  |

| DIM                      | MIN         | MAX  |  |  |

| Α                        | 0.70        | 0.80 |  |  |

| A1                       | 0.00        | 0.05 |  |  |

| A3                       | 0.20 REF    |      |  |  |

| b                        | 0.25        | 0.35 |  |  |

| D                        | 2.00 BSC    |      |  |  |

| D2                       | 1.50        | 1.70 |  |  |

| E                        | 2.00        | BSC  |  |  |

| E2                       | 0.90        | 1.10 |  |  |

| е                        | 0.65 BSC    |      |  |  |

| L                        | 0.20        | 0.40 |  |  |

| L1                       |             | 0.15 |  |  |

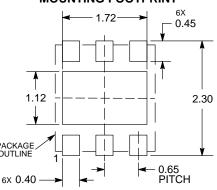

## RECOMMENDED MOUNTING FOOTPRINT\*

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and in are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all Claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научно-исследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

**Телефон:** +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331