# 1Mx18, 512Kx36 18Mb QUADP (Burst 2) Synchronous SRAM (2.5 CYCLE READ LATENCY)

OCTOBER 2014

#### **FEATURES**

- 512Kx36 and 1Mx18 configuration available.

- On-chip Delay-Locked Loop (DLL) for wide data valid window.

- Separate independent read and write ports with concurrent read and write operations.

- Synchronous pipeline read with EARLY write operation.

- Double Data Rate (DDR) interface for read and write input ports.

- 2.5 Cycle read latency.

- Fixed 2-bit burst for read and write operations.

- Clock stop support.

- Two input clocks (K and K#) for address and control registering at rising edges only.

- Two echo clocks (CQ and CQ#) that are delivered simultaneously with data.

- Data valid pin (QVLD).

- +1.8V core power supply and 1.5, 1.8V VDDQ, used with 0.75, 0.9V VREF.

- HSTL input and output interface.

- Registered addresses, write and read controls, byte writes, data in, and data outputs.

- Full data coherency.

- Boundary scan using limited set of JTAG 1149.1 functions.

- Byte Write capability.

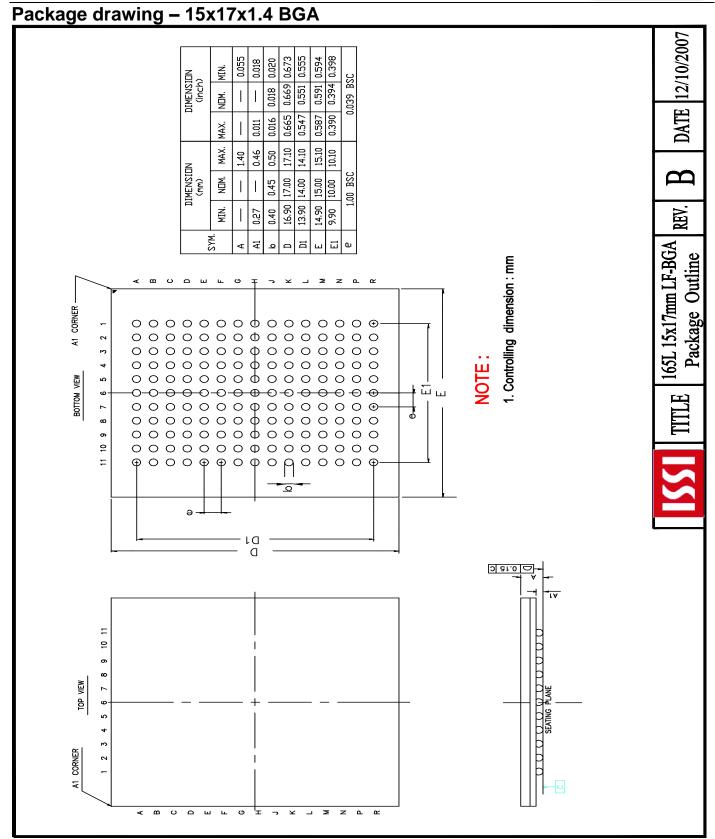

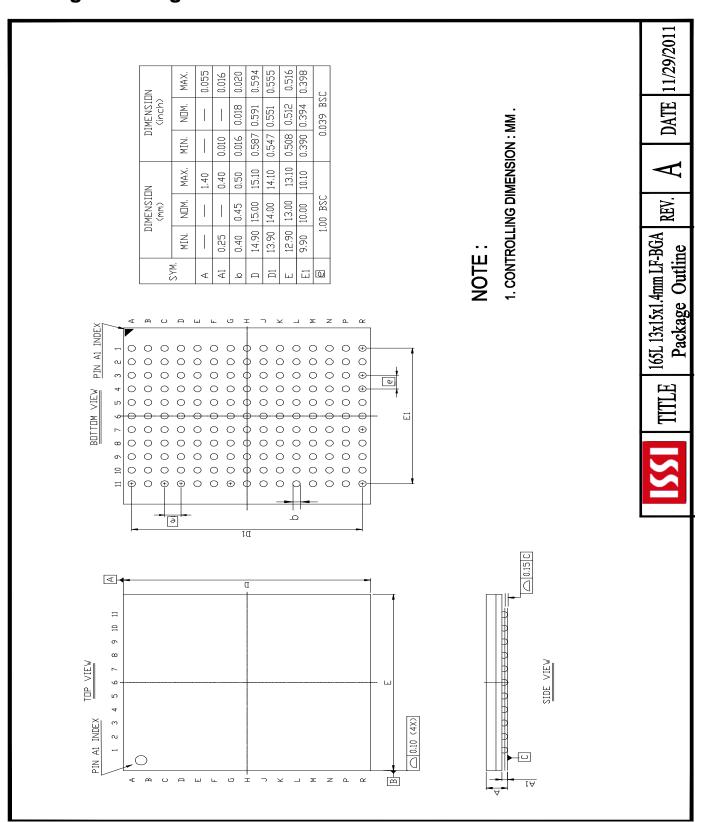

- Fine ball grid array (FBGA) package option:

13mmx15mm and 15mmx17mm body size 165-ball (11 x 15) array

- Programmable impedance output drivers via 5x user-supplied precision resistor.

- ODT (On Die Termination) feature is supported optionally on data input, K/K#, and BW<sub>x</sub>#.

- The end of top mark (A/A1/A2) is to define options.

IS61QDPB251236A : Don't care ODT function and pin connection

IS61QDPB251236A1 : Option1

IS61QDPB251236A2 : Option2

Refer to more detail description at page 6 for each ODT option.

#### **DESCRIPTION**

The 18Mb IS61QDPB251236A/A1/A2 and IS61QDPB21M18A/A1/A2 are synchronous, high-performance CMOS static random access memory (SRAM) devices. These SRAMs have separate I/Os, eliminating the need for high-speed bus turnaround. The rising edge of K clock initiates the read/write operation, and all internal operations are self-timed. Refer to the *Timing Reference Diagram for Truth Table* for a description of the basic operations of these QUADP (Burst of 2) SRAMs. Read and write addresses are registered on alternating rising edges of the K clock. Read and write performed in double data rate.

The following are registered internally on the rising edge of the K clock:

- Read address

- Read enable

- Write enable

- Data-in for early writes

The following are registered on the rising edge of the K# clock:

- Write address

- Byte writes

- Data-in for second burst addresses

Byte writes can change with the corresponding data-in to enable or disable writes on a per-byte basis. An internal write buffer enables the data-ins to be registered half a cycle earlier than the write address. The first data-in burst is clocked at the same time as the write command signal, and the second burst is timed to the following rising edge of the K# clock.

During the burst read operation, the data-outs from the first bursts are updated from output registers of the second rising edge of the K# clock (starting two and half cycles later after read command). The data-outs from the second bursts are updated with the third rising edge of the K clock. The K and K# clocks are used to time the data-outs.

The device is operated with a single +1.8V power supply and is compatible with HSTL I/O interface.

Copyright © 2014 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

# Package ballout and description

## x36 FBGA Ball Configuration (Top View)

|   | 1     | 2                  | 3                  | 4                | 5                 | 6               | 7                 | 8                | 9                  | 10                 | 11  |

|---|-------|--------------------|--------------------|------------------|-------------------|-----------------|-------------------|------------------|--------------------|--------------------|-----|

| Α | CQ#   | NC/SA <sup>1</sup> | NC/SA <sup>1</sup> | W#               | BW <sub>2</sub> # | K#              | BW <sub>1</sub> # | R#               | NC/SA <sup>1</sup> | NC/SA <sup>1</sup> | CQ  |

| В | Q27   | Q18                | D18                | SA               | BW <sub>3</sub> # | K               | BW <sub>0</sub> # | SA               | D17                | Q17                | Q8  |

| С | D27   | Q28                | D19                | $V_{SS}$         | SA                | SA              | SA                | $V_{SS}$         | D16                | Q7                 | D8  |

| D | D28   | D20                | Q19                | $V_{SS}$         | $V_{SS}$          | $V_{SS}$        | $V_{SS}$          | $V_{SS}$         | Q16                | D15                | D7  |

| Е | Q29   | D29                | Q20                | $V_{\text{DDQ}}$ | Vss               | Vss             | $V_{SS}$          | $V_{\text{DDQ}}$ | Q15                | D6                 | Q6  |

| F | Q30   | Q21                | D21                | $V_{\text{DDQ}}$ | $V_{DD}$          | V <sub>SS</sub> | $V_{DD}$          | $V_{DDQ}$        | D14                | Q14                | Q5  |

| G | D30   | D22                | Q22                | $V_{\text{DDQ}}$ | $V_{DD}$          | V <sub>SS</sub> | $V_{DD}$          | $V_{DDQ}$        | Q13                | D13                | D5  |

| Н | Doff# | $V_{REF}$          | $V_{DDQ}$          | $V_{\text{DDQ}}$ | $V_{DD}$          | Vss             | $V_{DD}$          | $V_{\text{DDQ}}$ | $V_{DDQ}$          | $V_{REF}$          | ZQ  |

| J | D31   | Q31                | D23                | $V_{DDQ}$        | $V_{DD}$          | V <sub>SS</sub> | $V_{DD}$          | $V_{DDQ}$        | D12                | Q4                 | D4  |

| K | Q32   | D32                | Q23                | $V_{\text{DDQ}}$ | $V_{DD}$          | V <sub>SS</sub> | $V_{DD}$          | $V_{DDQ}$        | Q12                | D3                 | Q3  |

| L | Q33   | Q24                | D24                | $V_{\text{DDQ}}$ | Vss               | Vss             | Vss               | $V_{\text{DDQ}}$ | D11                | Q11                | Q2  |

| M | D33   | Q34                | D25                | $V_{SS}$         | V <sub>SS</sub>   | V <sub>SS</sub> | V <sub>SS</sub>   | $V_{SS}$         | D10                | Q1                 | D2  |

| N | D34   | D26                | Q25                | $V_{SS}$         | SA                | SA              | SA                | $V_{SS}$         | Q10                | D9                 | D1  |

| Р | Q35   | D35                | Q26                | SA               | SA                | QVLD            | SA                | SA               | Q9                 | D0                 | Q0  |

| R | TDO   | TCK                | SA                 | SA               | SA                | ODT             | SA                | SA               | SA                 | TMS                | TDI |

Notes:

# x18 FBGA Ball Configuration (Top View)

| _ | 1     | 2                  | 3                  | 4                | 5                 | 6               | 7                  | 8                | 9         | 10                 | 11  |

|---|-------|--------------------|--------------------|------------------|-------------------|-----------------|--------------------|------------------|-----------|--------------------|-----|

| Α | CQ#   | NC/SA <sup>1</sup> | NC/SA <sup>1</sup> | W#               | BW <sub>1</sub> # | K#              | NC/SA <sup>1</sup> | R#               | SA        | NC/SA <sup>1</sup> | CQ  |

| В | NC    | Q9                 | D9                 | SA               | NC                | K               | BW <sub>0</sub> #  | SA               | NC        | NC                 | Q8  |

| С | NC    | NC                 | D10                | $V_{SS}$         | SA                | SA              | SA                 | $V_{SS}$         | NC        | Q7                 | D8  |

| D | NC    | D11                | Q10                | $V_{SS}$         | $V_{SS}$          | Vss             | Vss                | $V_{SS}$         | NC        | NC                 | D7  |

| E | NC    | NC                 | Q11                | $V_{DDQ}$        | $V_{SS}$          | V <sub>SS</sub> | $V_{SS}$           | $V_{DDQ}$        | NC        | D6                 | Q6  |

| F | NC    | Q12                | D12                | $V_{DDQ}$        | $V_{DD}$          | $V_{SS}$        | $V_{DD}$           | $V_{DDQ}$        | NC        | NC                 | Q5  |

| G | NC    | D13                | Q13                | $V_{\text{DDQ}}$ | $V_{DD}$          | Vss             | $V_{DD}$           | $V_{\text{DDQ}}$ | NC        | NC                 | D5  |

| Н | Doff# | $V_{REF}$          | $V_{DDQ}$          | $V_{DDQ}$        | $V_{DD}$          | V <sub>SS</sub> | $V_{DD}$           | $V_{DDQ}$        | $V_{DDQ}$ | $V_{REF}$          | ZQ  |

| J | NC    | NC                 | D14                | $V_{DDQ}$        | $V_{DD}$          | $V_{SS}$        | $V_{DD}$           | $V_{DDQ}$        | NC        | Q4                 | D4  |

| K | NC    | NC                 | Q14                | $V_{\text{DDQ}}$ | $V_{DD}$          | Vss             | $V_{DD}$           | $V_{\text{DDQ}}$ | NC        | D3                 | Q3  |

| L | NC    | Q15                | D15                | $V_{DDQ}$        | $V_{SS}$          | V <sub>SS</sub> | $V_{SS}$           | $V_{DDQ}$        | NC        | NC                 | Q2  |

| М | NC    | NC                 | D16                | V <sub>SS</sub>  | Vss               | V <sub>SS</sub> | V <sub>SS</sub>    | V <sub>SS</sub>  | NC        | Q1                 | D2  |

| N | NC    | D17                | Q16                | $V_{SS}$         | SA                | SA              | SA                 | $V_{SS}$         | NC        | NC                 | D1  |

| Р | NC    | NC                 | Q17                | SA               | SA                | QVLD            | SA                 | SA               | NC        | D0                 | Q0  |

| R | TDO   | TCK                | SA                 | SA               | SA                | ODT             | SA                 | SA               | SA        | TMS                | TDI |

<sup>1.</sup> The following balls are reserved for higher densities: 9A for 36M, 3A for 72M, 10A for 144Mb, and 2A for 288Mb.

<sup>1.</sup> The following balls are reserved for higher densities: 3A for 36M, 10A for 72M, 2A for 144Mb, and 7A for 288Mb.

# **Ball Description**

| Symbol            | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K, K#             | Input              | Input clock: This input clock pair registers address and control inputs on the rising edge of K, and registers data on the rising edge of K and the rising edge of K#. K# is ideally 180 degrees out of phase with K. All synchronous inputs must meet setup and hold times around the clock rising edges. These balls cannot remain VREF level.                                                                                                                                                                        |

| CQ, CQ#           | Output             | Synchronous echo clock outputs: The edges of these outputs are tightly matched to the synchronous data outputs and can be used as a data valid indication. These signals are free running clocks and do not stop when Q tri-states.                                                                                                                                                                                                                                                                                     |

| Doff#             | Input              | DLL disable and reset input: when low, this input causes the DLL to be bypassed and reset the previous DLL information. When high, DLL will start operating and lock the frequency after tCK lock time. The device behaves in one clock read latency mode when the DLL is turned off. In this mode, the device can be operated at a frequency of up to 167 MHz.                                                                                                                                                         |

| QVLD              | Output             | Valid output indicator: The Q Valid indicates valid output data. QVLD is edge aligned with CQ and CQ#.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SA                | Input              | Synchronous address inputs: These inputs are registered and must meet the setup and hold times around the rising edge of K. These inputs are ignored when device is deselected.                                                                                                                                                                                                                                                                                                                                         |

| D0 - Dn           | Input              | Synchronous data inputs: Input data must meet setup and hold times around the rising edges of K and K# during WRITE operations. See BALL CONFIGURATION figures for ball site location of individual signals.  The x18 device uses D0~D17. D18~D35 should be treated as NC pin.  The x36 device uses D0~D35.                                                                                                                                                                                                             |

| Q0 - Qn           | Output             | Synchronous data outputs: Output data is synchronized to the respective CQ and CQ#, or to the respective K and K# if C and /C are tied to high. This bus operates in response to R# commands. See BALL CONFIGURATION figures for ball site location of individual signals. The x18 device uses Q0~Q17. Q18~Q35 should be treated as NC pin. The x36 device uses Q0~Q35.                                                                                                                                                 |

| W#                | Input              | Synchronous write: When low, this input causes the address inputs to be registered and a WRITE cycle to be initiated. This input must meet setup and hold times around the rising edge of K.                                                                                                                                                                                                                                                                                                                            |

| R#                | Input              | Synchronous read: When low, this input causes the address inputs to be registered and a READ cycle to be initiated. This input must meet setup and hold times around the rising edge of K.                                                                                                                                                                                                                                                                                                                              |

| BW <sub>x</sub> # | Input              | Synchronous byte writes: When low, these inputs cause their respective byte to be registered and written during WRITE cycles. These signals are sampled on the same edge as the corresponding data and must meet setup and hold times around the rising edges of K and #K for each of the two rising edges comprising the WRITE cycle. See Write Truth Table for signal to data relationship.                                                                                                                           |

| $V_{REF}$         | Input<br>reference | HSTL input reference voltage: Nominally VDDQ/2, but may be adjusted to improve system noise margin. Provides a reference voltage for the HSTL input buffers.                                                                                                                                                                                                                                                                                                                                                            |

| $V_{DD}$          | Power              | Power supply: 1.8 V nominal. See DC Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $V_{DDQ}$         | Power              | Power supply: Isolated output buffer supply. Nominally 1.5 V. See DC Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{SS}$          | Ground             | Ground of the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ZQ                | Input              | Output impedance matching input: This input is used to tune the device outputs to the system data bus impedance. Q and CQ output impedance are set to 0.2xRQ, where RQ is a resistor from this ball to ground. This ball can be connected directly to VDDQ, which enables the minimum impedance mode. This ball cannot be connected directly to VSS or left unconnected. In ODT (On Die Termination) enable devices, the ODT termination values tracks the value of RQ. The ODT range is selected by ODT control input. |

| TMS, TDI, TCK     | Input              | IEEE1149.1 input pins for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TDO               | Output             | IEEE1149.1 output pins for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NC                | N/A                | No connect: These signals should be left floating or connected to ground to improve package heat dissipation.                                                                                                                                                                                                                                                                                                                                                                                                           |

| ODT               | Input              | ODT control; Refer to SRAM features for the details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **SRAM Features description**

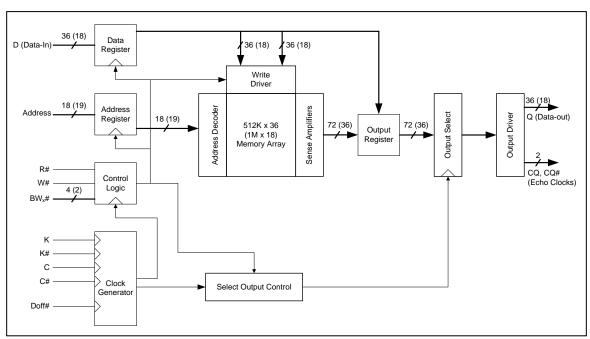

### **Block Diagram**

Note: Numerical values in parentheses refer to the x18 device configuration.

### **Read Operations**

The SRAM operates continuously in a burst-of-two mode. Read cycles are started by registering R# in active low state at the rising edge of the K clock. R# can be activated every other cycle because two full cycles are required to complete the burst of two in DDR mode. A set of free-running echo clocks, CQ and CQ#, are produced internally with timings identical to the data-outs. The echo clocks can be used as data capture clocks by the receiver device.

The data corresponding to the first address is clocked two and half cycles later by the rising edge of the K# clock. The data corresponding to the second burst is clocked three cycles later by the following rising edge of the K clock.

A NOP operation (R# is high) does not terminate the previous read.

### Write Operations

Write operations can also be initiated at every rising edge of the K clock with first data whenever W# is low. The write address is provided half cycle with second data later, registered by the rising edge of K#, so the write always occurs in bursts of two.

The write data is provided in an 'early write' mode; that is, the data-in corresponding to the first address of the burst, is presented half cycle before the rising edge of the following K clock. The data-in corresponding to the second write burst address follows next, registered by the rising edge of K#.

The data-in provided for writing is initially kept in write buffers. The information in these buffers is written into the array on the third write cycle. A read cycle to the last write address produces data from the write buffers. Similarly, a read address followed by the same write address produces the latest write data. The SRAM maintains data coherency.

During a write, the byte writes independently control which byte of any of the four burst addresses is written (see X18/X36 Write Truth Tables and Timing Reference Diagram for Truth Table).

Whenever a write is disabled (W# is high at the rising edge of K), data is not written into the memory.

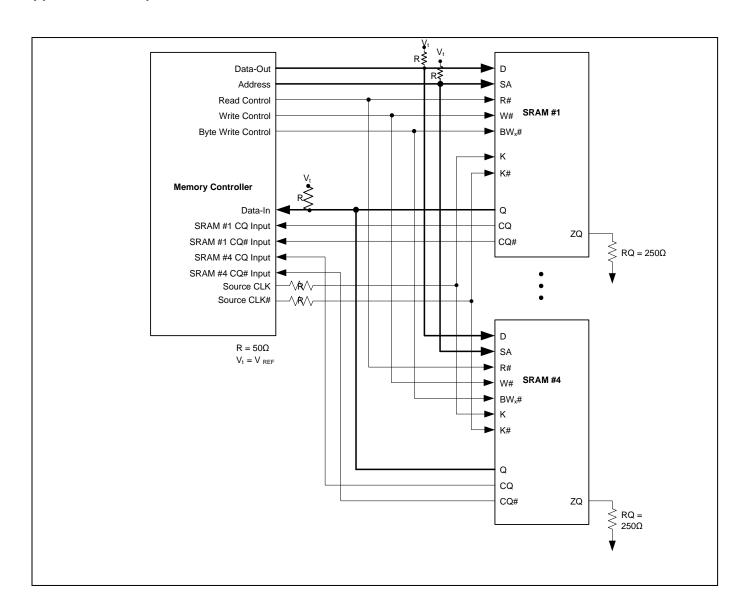

## **RQ Programmable Impedance**

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and Vss to enable the SRAM to adjust its output driver impedance. The value of RQ must be 5x the value of the intended line impedance driven by the SRAM. For example, an RQ of  $250\Omega$  results in a driver impedance of  $50\Omega$ . The allowable range of RQ to guarantee impedance matching is between  $175\Omega$  and  $350\Omega$  at  $V_{DDQ}$ =1.5V. The RQ resistor should be placed less than two inches away from the ZQ ball on the SRAM module. The capacitance of the loaded ZQ trace must be less than 7.5pF.

The ZQ pin can also be directly connected to  $V_{\tiny DDQ}$  to obtain a minimum impedance setting. ZQ must never be connected to  $V_{\tiny SS}$ .

### **Programmable Impedance and Power-Up Requirements**

Periodic readjustment of the output driver impedance is necessary as the impedance is greatly affected by drifts in supply voltage and temperature. During power-up, the driver impedance is in the middle of allowable impedances value. The final impedance value is achieved within 1024 clock cycles.

### **Depth Expansion**

Separate input and output ports enable easy depth expansion, as each port can be selected and deselected independently. Read and write operations can occur simultaneously without affecting each other. Also, all pending read and write transactions are always completed prior to deselecting the corresponding port.

### Valid Data Indicator (QVLD)

A data valid pin (QVLD) is available to assist in high-speed data output capture. This output signal is edge-aligned with the echo clock and is asserted HIGH half a cycle before valid read data is available and asserted LOW half a cycle before the final valid read data arrives.

### **Delay Locked Loop (DLL)**

Delay Locked Loop (DLL) is a new system to align the output data coincident with clock rising or falling edge to enhance the output valid timing characteristics. It is locked to the clock frequency and is constantly adjusted to match the clock frequency. Therefore device can have stable output over the temperature and voltage variation.

DLL has a limitation of locking range and jitter adjustment which are specified as tKHKH and tKCvar respectively in the AC timing characteristics. In order to turn this feature off, applying logic low to the Doff# pin will bypass this. In the DLL off mode, the device behaves with one clock cycle latency and a longer access time which is known in DDR-I or legacy QUAD mode.

The DLL can also be reset without power down by toggling Doff# pin low to high or stopping the input clocks K and K# for a minimum of 30ns.(K and K# must be stayed either at higher than VIH or lower than VIL level. Remaining Vref is not permitted.) DLL reset must be issued when power up or when clock frequency changes abruptly. After DLL being reset, it gets locked after 2048 cycles of stable clock.

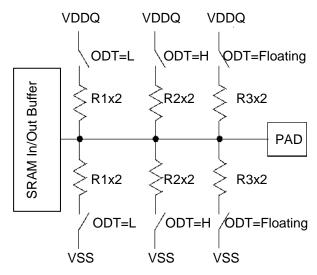

### **ODT (On Die Termination)**

On Die Termination (ODT) is a feature that allows a SRAM to change input resistive termination condition by ODT pin which function can have three status, High, Low, and Floating. Each status can have different ODT termination value that tracks the value of RQ (Refer to the table of Fig1) and ODT of QUADP is always turned on during the read and write function after ODT level to connect with ODT resistor is forced.

Fig1. Functional representation of ODT

|                      | R1              | R2     | R3              |

|----------------------|-----------------|--------|-----------------|

| Option1 <sup>3</sup> | 0.3x            | 0.6x   | 0.6x            |

| Ориопт               | RQ <sup>1</sup> | $RQ^2$ | RQ <sup>2</sup> |

| Option2 <sup>4</sup> | ODT             | 0.6x   | ODT             |

| Optionz              | disable         | $RQ^2$ | disable         |

#### Notes

- 1. Allowable range of RQ to guarantee impedance matching a tolerance of ±20% is 175Ω<RQ<350Ω.

- 2. Allowable range of RQ to guarantee impedance matching a tolerance of  $\pm 20\%$  is  $175\Omega < RQ < 250\Omega$ .

- 3. ODT control pin is connected to VDDQ through  $3.5k\Omega$ . Therefore it is recommended to connect it to VSS through less than  $100\Omega$  to make it low.

- 4. ODT control pin is connected to VSS through  $3.5k\Omega$ . Therefore it is recommended to connect it to VDDQ through less than  $100\Omega$  to make it high.

### **ODT PIN**

For option1 case, low input level of ODT pin can select strong (RQ $^{1}$ ) input termination range (175 $\Omega$ <RQ<350 $\Omega$ ) and high input level of ODT pin can select weak (RQ $^{2}$ ) input termination range (175 $\Omega$ <RQ<250 $\Omega$ ) with K, K#, D0 to Dn, BWx# and if ODT pin is on floating condition, it set weak (RQ $^{2}$ ) input termination range which ODT pin is connected by pull-up resistor internally. For option2 case, high input level of ODT pin can select weak (RQ $^{2}$ ) input termination range (175 $\Omega$ <RQ<250 $\Omega$ ) with D0 to Dn, BWx# and low input level or floating of ODT pin can select disable of the ODT function.

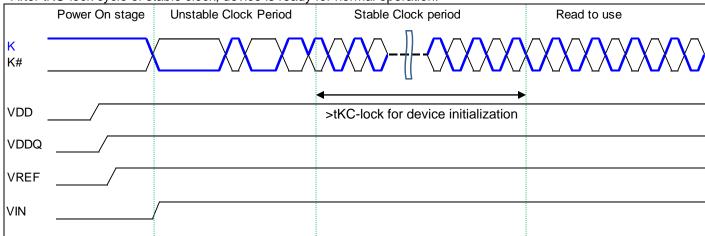

## **Power-Up and Power-Down Sequences**

The recommendation of voltage apply sequence is :  $V_{DD} \rightarrow V_{DDQ} \stackrel{1)}{\longrightarrow} V_{REF} \stackrel{2)}{\longrightarrow} V_{IN}$

- 1)  $V_{DDQ}$  can be applied concurrently with  $V_{DD}$ .

- 2) V<sub>REF</sub> can be applied concurrently with V<sub>DDQ</sub>.

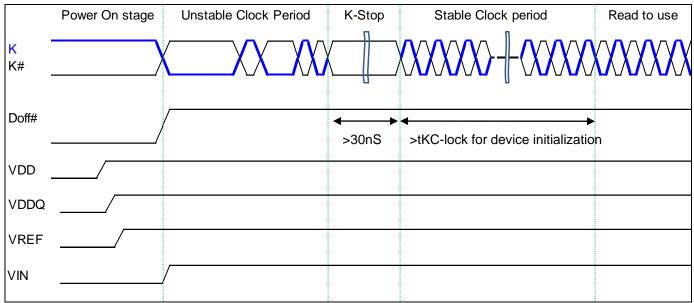

After power and clock signals are stabilized, device can be ready for normal operation after tKC-Lock cycles. In tKC-lock cycle period, device initializes internal logics and locks DLL. Depending on /Doff status, locking DLL will be skipped. The following timing pictures are possible examples of power up sequence.

### Sequence1. /Doff is fixed low

After tKC-lock cycle of stable clock, device is ready for normal operation.

Note) All inputs including clocks must be either logically High or Low during Power On stage. Timing above shows only one of cases.

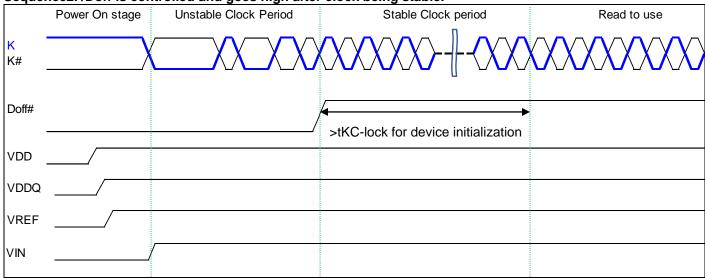

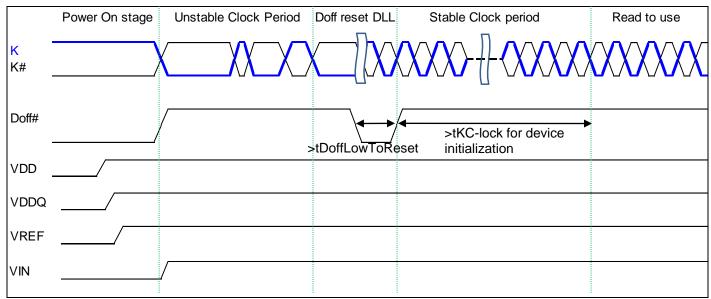

Sequence2. /Doff is controlled and goes high after clock being stable.

Note) All inputs including clocks must be either logically High or Low during Power On stage. Timing above shows only one of cases.

Sequence3. /Doff is controlled but goes high before clock being stable.

Because DLL has a risk to be locked with the unstable clock, DLL needs to be reset and locked with the stable input.

a) K-stop to reset. If K or K# stays at VIH or VIL for more than 30nS, DLL will be reset and ready to re-lock. In tKC-Lock period, DLL will be locked with a new stable value. Device can be ready for normal operation after that.

Note) All inputs including clocks must be either logically High or Low during Power On stage. Timing above shows only one of cases.

a) /Doff Low to reset. If /Doff toggled low to high, DLL will be reset and ready to re-lock. In tKC-Lock period, DLL will be locked with a new stable value. Device can be ready for normal operation after that.

Note) Applying DLL reset sequences (sequence 3a, 3b) are also required when operating frequency is changed without power off. Note) All inputs including clocks must be either logically High or Low during Power On stage. Timing above shows only one of cases.

# **Application Example**

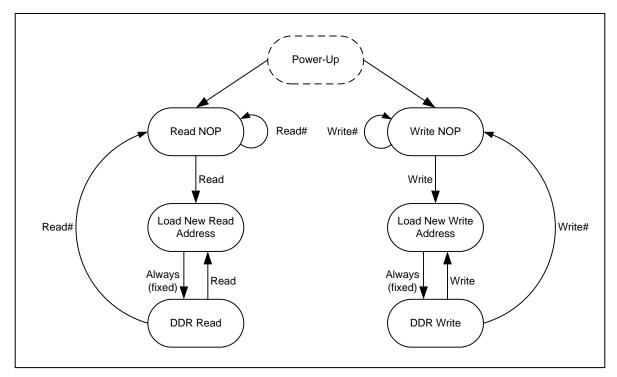

## **State Diagram**

- 1. Internal burst counter is fixed as two-bit linear; that is when first address is A0+0, next internal burst addresses are A0+1.

- 2. Read refers to read active status with R# = LOW. Read# refers to read inactive status with R# = HIGH.

- 3. Write refers to write active status with W# = LOW. Write# refers to write inactive status with W# = HIGH.

- 4. The read and write state machines can be active simultaneously.

- 5. State machine control timing sequence is controlled by K.

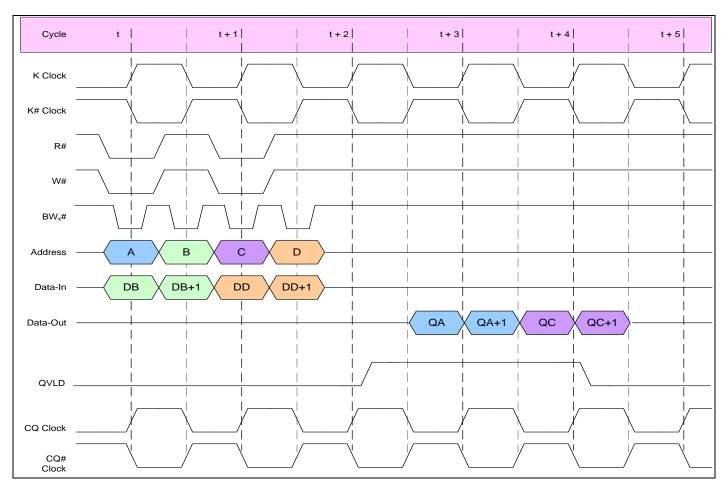

### **Timing Reference Diagram for Truth Table**

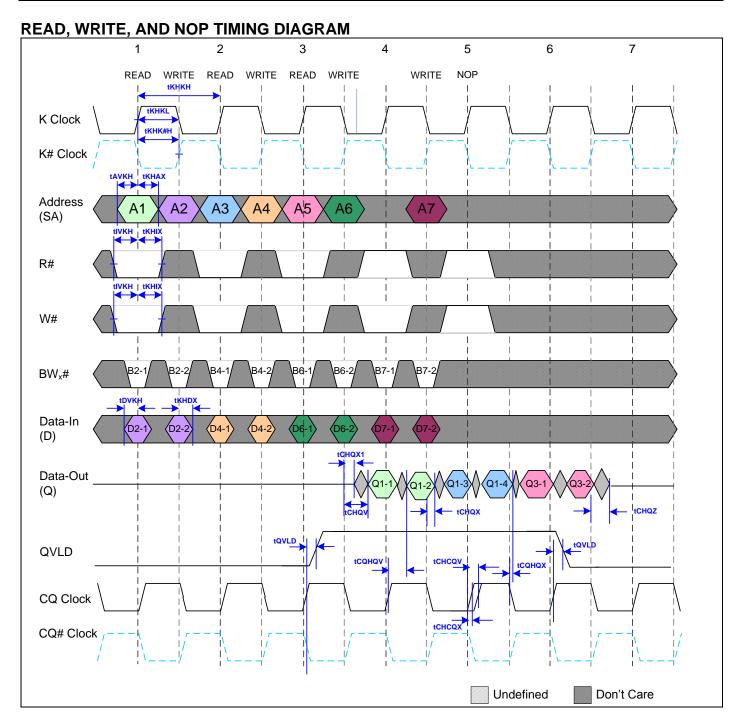

The *Timing Reference Diagram for Truth Table* is helpful in understanding the *Clock and Write Truth Tables*, as it shows the cycle relationship between clocks, address, data in, data out, and control signals. Read command is issued at the beginning of cycle "t". Write command is issued at the beginning of cycle "t+1".

### **Clock Truth Table**

(Use the following table with the Timing Reference Diagram for Truth Table.)

| Mode               | Clock             | Con | trols | Data                     | a In                          | Data Out                       |                               |  |

|--------------------|-------------------|-----|-------|--------------------------|-------------------------------|--------------------------------|-------------------------------|--|

| Wode               | К                 | R#  | W#    | D <sub>B</sub>           | D <sub>B+1</sub>              | Q <sub>A</sub>                 | Q <sub>A+1</sub>              |  |

| Stop Clock         | Stop              | Х   | Х     | Previous State           | Previous State                | Previous State                 | Previous State                |  |

| No Operation (NOP) | $L \rightarrow H$ | Н   | Н     | Х                        | X                             | High-Z                         | High-Z                        |  |

| Read A             | L → H             | L   | Х     | Х                        | Х                             | D <sub>OUT</sub> at K# (t+2.5) | D <sub>OUT</sub> at K (t+3.0) |  |

| Write B            | L → H             | Х   | L     | D <sub>IN</sub> at K (t) | D <sub>IN</sub> at K# (t+0.5) | Х                              | Х                             |  |

#### Notes:

- 1. Internal burst counter is always fixed as two-bit.

- 2. X = "don't care"; H = logic "1"; L = logic "0".

- 3. A read operation is started when control signal R is active low

- 4. A write operation is started when control signal W is active low.

- 5. Before entering into stop clock, all pending read and write must be completed.

- 6. Consecutive read or write operations can be started only at every other K clock rising edge. If two read or write operations are issued in consecutive K clock rising edges, the second one will be ignored.

- 7. If both R# and W# are active low after a NOP operation, the write operation will be ignored.

- 8. For timing definitions, refer to the AC Timing Characteristics table. Signals must meet AC specifications at timings indicated in parenthesis with respect to switching clocks K, K#.

### x18 Write Truth Table

(Use the following table with the Timing Reference Diagram for Truth Table.)

| Operation       | K (t)             | K# (t+0.5)        | BW <sub>0</sub> # | BW₁# | D <sub>B</sub> | D <sub>B+1</sub> |

|-----------------|-------------------|-------------------|-------------------|------|----------------|------------------|

| Write Byte 0    | $L \rightarrow H$ |                   | L                 | Н    | D0-8 (t)       |                  |

| Write Byte 1    | $L \rightarrow H$ |                   | Н                 | L    | D9-17 (t)      |                  |

| Write All Bytes | $L \rightarrow H$ |                   | L                 | L    | D0-17 (t)      |                  |

| Abort Write     | $L \rightarrow H$ |                   | Н                 | Н    | Don't Care     |                  |

| Write Byte 0    |                   | $L\toH$           | L                 | Н    |                | D0-8 (t+0.5)     |

| Write Byte 1    |                   | $L \rightarrow H$ | Н                 | L    |                | D9-17 (t+0.5)    |

| Write All Bytes |                   | $L \rightarrow H$ | L                 | L    |                | D0-17 (t+0.5)    |

| Abort Write     |                   | $L \rightarrow H$ | Н                 | Н    |                | Don't Care       |

- 1. Refer to the *Timing Reference Diagram for Truth Table*. Cycle time starts at n and is referenced to the K clock.

- 2. For all cases, W# needs to be active low during the rising edge of K occurring at time t.

- 3. For timing definitions refer to the AC Timing Characteristics table. Signals must meet AC specifications with respect to switching clocks K and K#.

### x36 Write Truth Table

(Use the following table with the *Timing Reference Diagram for Truth Table*.)

| Operation       | K (t)             | K# (t+0.5)        | BW <sub>0</sub> # | BW <sub>1</sub> # | BW <sub>2</sub> # | BW <sub>3</sub> # | D <sub>B</sub> | D <sub>B+1</sub>  |

|-----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------|-------------------|

| Write Byte 0    | $L \rightarrow H$ |                   | L                 | Н                 | Н                 | Н                 | D0-8 (t)       |                   |

| Write Byte 1    | L → H             |                   | Н                 | L                 | Н                 | Н                 | D9-17 (t)      |                   |

| Write Byte 2    | L → H             |                   | Н                 | Н                 | L                 | Н                 | D18-26 (t)     |                   |

| Write Byte 3    | L → H             |                   | Н                 | Н                 | Н                 | L                 | D27-35 (t)     |                   |

| Write All Bytes | L → H             |                   | L                 | L                 | L                 | L                 | D0-35 (t)      |                   |

| Abort Write     | $L \rightarrow H$ |                   | Н                 | Н                 | Н                 | Н                 | Don't Care     |                   |

| Write Byte 0    |                   | $L \rightarrow H$ | L                 | Н                 | Н                 | Н                 |                | D0-8 (t+0.5)      |

| Write Byte 1    |                   | $L \rightarrow H$ | Н                 | L                 | Н                 | Н                 |                | D9-17 (t+0.5)     |

| Write Byte 2    |                   | $L \rightarrow H$ | Н                 | Н                 | L                 | Н                 |                | D18-26<br>(t+0.5) |

| Write Byte 3    |                   | $L \rightarrow H$ | Н                 | Н                 | Н                 | L                 |                | D27-35<br>(t+0.5) |

| Write All Bytes |                   | L → H             | L                 | L                 | L                 | L                 |                | D0-35 (t+0.5)     |

| Abort Write     |                   | $L \rightarrow H$ | Н                 | Н                 | Н                 | Н                 |                | Don't Care        |

- 1. For all cases, W# needs to be active low during the rising edge of K occurring at time t.

- 2. For timing definitions refer to the AC Timing Characteristics table. Signals must meet AC specifications with respect to switching clocks K and K#.

# **Electrical Specifications**

### **Absolute Maximum Ratings**

| Parameter                | Symbol            | Min  | Max                  | Units |

|--------------------------|-------------------|------|----------------------|-------|

| Power Supply Voltage     | V <sub>DD</sub>   | -0.5 | 2.9                  | V     |

| I/O Power Supply Voltage | $V_{DDQ}$         | -0.5 | 2.9                  | V     |

| DC Input Voltage         | V <sub>IN</sub>   | -0.5 | V <sub>DD</sub> +0.3 | V     |

| Data Out Voltage         | V <sub>DOUT</sub> | -0.5 | 2.6                  | V     |

| Junction Temperature     | TJ                | -    | 110                  | °C    |

| Storage Temperature      | T <sub>STG</sub>  | -55  | +125                 | °C    |

#### Note:

Stresses greater than those listed in this table can cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this datasheet is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Operating Temperature Range**

| Temperature Range | Symbol         | Min | Max | Units |

|-------------------|----------------|-----|-----|-------|

| Commercial        | T <sub>A</sub> | 0   | +70 | °C    |

| Industrial        | T <sub>A</sub> | -40 | +85 | °C    |

#### **DC Electrical Characteristics**

(Over the Operating Temperature Range, V<sub>DD</sub>=1.8V±5%)

| Parameter                                                                                                            | Symbol            | Min                   | Max                  | Units | Notes |

|----------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|----------------------|-------|-------|

| x36 Average Power Supply Operating Current                                                                           | I <sub>DD30</sub> |                       | 740                  |       |       |

| (I <sub>OUT</sub> =0, V <sub>IN</sub> =V <sub>IH</sub> or V <sub>IL</sub> )                                          | $I_{DD33}$        | _                     | 690                  | mA    | 1, 2  |

| (1001-0, VIN-VIH OI VIL)                                                                                             | $I_{DD40}$        |                       | 600                  |       |       |

| x18 Average Power Supply Operating Current                                                                           | I <sub>DD30</sub> |                       | 690                  |       |       |

| (I <sub>OUT</sub> =0, V <sub>IN</sub> =V <sub>IH</sub> or V <sub>IL</sub> )                                          | $I_{DD33}$        | _                     | 640                  | mΑ    | 1, 2  |

| (IOUT=0, VIN=VIH OT VIL)                                                                                             | $I_{DD40}$        |                       | 550                  |       |       |

| Power Supply Standby Current                                                                                         | I <sub>SB30</sub> |                       | 310                  |       |       |

| (R#=V <sub>IH</sub> , W#=V <sub>IH</sub> . All other inputs=V <sub>IH</sub> or V <sub>IL</sub> , I <sub>IH</sub> =0) | I <sub>SB33</sub> | _                     | 285                  | mA    | 1,2   |

|                                                                                                                      | I <sub>SB40</sub> |                       | 270                  |       |       |

| Input leakage current                                                                                                |                   |                       |                      |       |       |

| ( 0 ≤V <sub>IN</sub> ≤V <sub>DDQ</sub> for all input balls except V <sub>REF</sub> , ZQ, TCK,                        | I <sub>LI</sub>   | -2                    | +2                   | μΑ    | 3,4   |

| TMS, TDI ball)                                                                                                       |                   |                       |                      |       |       |

| Output leakage current                                                                                               |                   |                       |                      |       |       |

| (0 ≤V <sub>OUT</sub> ≤V <sub>DDQ</sub> for all output balls except TDO ball; Output                                  | $I_{LO}$          | -2                    | +2                   | μA    |       |

| must be disabled.)                                                                                                   |                   |                       |                      |       |       |

| Output "high" level voltage (IoH=-100uA, Nominal ZQ)                                                                 | V <sub>OH</sub>   | V <sub>DDQ</sub> -0.2 | $V_{DDQ}$            | V     |       |

| Output "low" level voltage (IoH= 100uA, Nominal ZQ)                                                                  | V <sub>OL</sub>   | V <sub>SS</sub>       | V <sub>SS</sub> +0.2 | V     |       |

- 1. IOUT = chip output current.

- 2. The numeric suffix indicates the part operating at speed, as indicated in *AC Timing Characteristics* table (that is, I<sub>DD25</sub> indicates 2.5ns cycle time).

- 3. ODT must be disabled.

- 4. Balls with ODT and DOFF# do not follow this spec, ILI = ±5uA.

## **Recommended DC Operating Conditions**

(Over the Operating Temperature Range)

| Parameter                    | Symbol              | Min                   | Typical | Max                   | Units | Notes |

|------------------------------|---------------------|-----------------------|---------|-----------------------|-------|-------|

| Supply Voltage               | $V_{DD}$            | 1.8–5%                | 1.8     | 1.8+5%                | V     | 1     |

| Output Driver Supply Voltage | $V_{DDQ}$           | 1.4                   | 1.5     | $V_{DD}$              | V     | 1     |

| Input High Voltage           | V <sub>IH</sub>     | V <sub>REF</sub> +0.1 | -       | V <sub>DDQ</sub> +0.2 | V     | 1, 2  |

| Input Low Voltage            | V <sub>IL</sub>     | -0.2                  | -       | V <sub>REF</sub> -0.1 | V     | 1, 3  |

| Input Reference Voltage      | V <sub>REF</sub>    | 0.68                  | 0.75    | 0.95                  | V     | 1, 5  |

| Clock Signal Voltage         | V <sub>IN-CLK</sub> | -0.2                  | -       | V <sub>DDQ</sub> +0.2 | V     | 1, 4  |

#### Notes:

- 1. All voltages are referenced to  $V_{SS}$ . All  $V_{DD}$ ,  $V_{DDQ}$ , and  $V_{SS}$  pins must be connected.

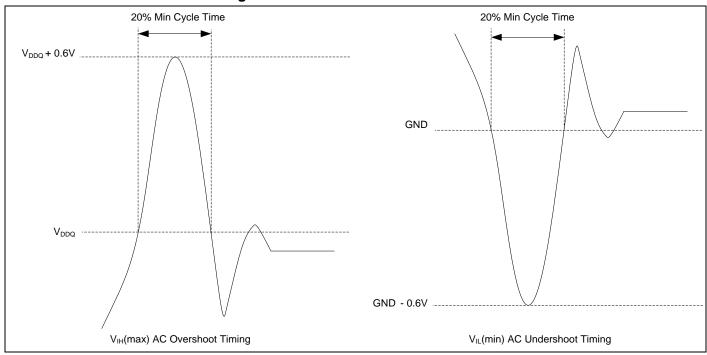

- 2.  $V_{IH}(max)$  AC = See Overshoot and Undershoot Timings.

- 3.  $V_{IL}(min)$  AC = See Overshoot and Undershoot Timings.

- 4. V<sub>IN-CLK</sub> specifies the maximum allowable DC excursions of each clock (K and K#).

- 5. Peak-to-peak AC component superimposed on  $V_{REF}$  may not exceed 5% of  $V_{REF}$ .

### **Overshoot and Undershoot Timings**

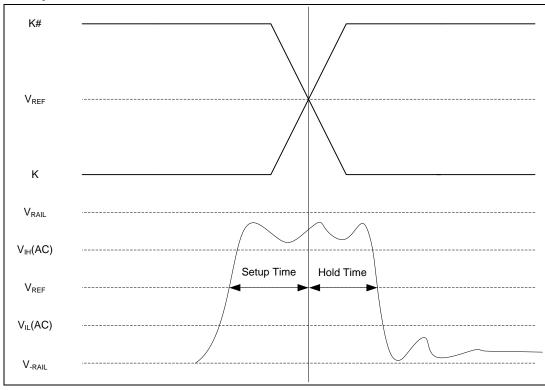

## **Typical AC Input Characteristics**

| Parameter              | Symbol                   | Min                   | Max                   | Units | Notes      |

|------------------------|--------------------------|-----------------------|-----------------------|-------|------------|

| AC Input Logic HIGH    | V <sub>IH</sub> (AC)     | V <sub>REF</sub> +0.2 |                       | V     | 1, 2, 3, 4 |

| AC Input Logic LOW     | V <sub>IL</sub> (AC)     |                       | V <sub>REF</sub> -0.2 | V     | 1, 2, 3, 4 |

| Clock Input Logic HIGH | V <sub>IH-CLK</sub> (AC) | V <sub>REF</sub> +0.2 |                       | V     | 1, 2, 3    |

| Clock Input Logic LOW  | V <sub>IL-CLK</sub> (AC) |                       | V <sub>REF</sub> -0.2 | V     | 1, 2, 3    |

#### Notes:

- 1. The peak-to-peak AC component superimposed on  $V_{REF}$  may not exceed 5% of the DC component of  $V_{REF}$ .

- 2. Performance is a function of  $V_{IH}$  and  $V_{IL}$  levels to clock inputs.

- 3. See the AC Input Definition diagram.

- 4. See the *AC Input Definition* diagram. The signals should swing monotonically with no steps rail-to-rail with input signals never ringing back past V<sub>IH</sub> (AC) and V<sub>IL</sub> (AC) during the input setup and input hold window. V<sub>IH</sub> (AC) and V<sub>IL</sub> (AC) are used for timing purposes only.

### **AC Input Definition**

### **PBGA Thermal Characteristics**

| Parameter                                                  | Symbol          | 13x15 BGA | 15x17 BGA | Units |

|------------------------------------------------------------|-----------------|-----------|-----------|-------|

| Thermal resistance (junction to ambient at airflow = 1m/s) | $R_{	heta JA}$  | 19.6      | 18.0      | °C/W  |

| Thermal resistance (junction to pins)                      | $R_{\theta JB}$ | 4.02      | 3.30      | °C/W  |

| Thermal resistance (junction to case)                      | $R_{	heta JC}$  | 4.53      | 4.20      | °C/W  |

Note: these parameters are guaranteed by design and tested by a sample basis only.

## Pin Capacitance

| Parameter                                       | Symbol                          | Test Condition                           | Max | Units |

|-------------------------------------------------|---------------------------------|------------------------------------------|-----|-------|

| Input or output capacitance except D and Q pins | C <sub>IN</sub> ,C <sub>O</sub> |                                          | 5   | рF    |

| D and Q capacitance (D0–Dx, Q0-Qx)              | $C_{DQ}$                        | TA = 25°C, f = 1 MHz, VDD = 1.8V, VDDQ = | 6   | pF    |

| Clocks Capacitance (K, K, C, C)                 | C <sub>CLK</sub>                | 1.5V                                     | 4   | pF    |

<sup>1.</sup> Note: these parameters are guaranteed by design and tested by a sample basis only.

### **Programmable Impedance Output Driver DC Electrical Characteristics**

(Over the Operating Temperature Range, V<sub>DD</sub>=1.8V±5%, V<sub>DDQ</sub>=1.5V/1.8V)

| Parameter                 | Symbol          | Min                       | Max                | Units | Notes |

|---------------------------|-----------------|---------------------------|--------------------|-------|-------|

| Output Logic HIGH Voltage | $V_{OH}$        | V <sub>DDQ</sub> /2 -0.12 | $V_{DDQ}/2 + 0.12$ | V     | 1, 3  |

| Output Logic LOW Voltage  | V <sub>OL</sub> | V <sub>DDQ</sub> /2 -0.12 | $V_{DDQ}/2 + 0.12$ | V     | 2, 3  |

Notes

1. For 175Ω□□≤ RQ ≤□350Ω:

$$| \text{ Ioh } | = \frac{\left(\frac{V_{\text{DDQ}}}{2}\right)}{\left(\frac{RQ}{5}\right)}$$

2. For 175Ω□□≤□RQ ≤□350Ω:

$$| lol | = \frac{\left(\frac{V_{DDQ}}{2}\right)}{\left(\frac{RQ}{5}\right)}$$

3. Parameter Tested with RQ=250Ω and V<sub>DDQ</sub>=1.5V

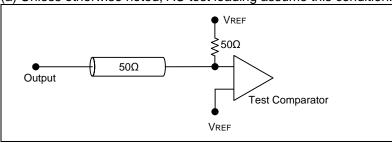

### **AC Test Conditions**

(Over the Operating Temperature Range, V<sub>DD</sub>=1.8V±5%, V<sub>DDQ</sub>=1.5V/1.8V)

| Symbol          | Conditions                                                                       | Units                                                                                                                                                                                                    | Notes                                                                                                                                                                                                                                                       |

|-----------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DDQ}$       | 1.5/1.8                                                                          | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

| V <sub>IH</sub> | V <sub>REF</sub> +0.5                                                            | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

| V <sub>IL</sub> | V <sub>REF</sub> -0.5                                                            | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

| $V_{REF}$       | 0.75/0.9                                                                         | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

| T <sub>R</sub>  | 2                                                                                | V/ns                                                                                                                                                                                                     |                                                                                                                                                                                                                                                             |

| T <sub>F</sub>  | 2                                                                                | V/ns                                                                                                                                                                                                     |                                                                                                                                                                                                                                                             |

|                 | $V_{REF}$                                                                        | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

|                 | $V_{REF}$                                                                        | V                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |

|                 |                                                                                  |                                                                                                                                                                                                          | 1, 2                                                                                                                                                                                                                                                        |

|                 | V <sub>DDQ</sub> V <sub>IH</sub> V <sub>IL</sub> V <sub>REF</sub> T <sub>R</sub> | V <sub>DDQ</sub> 1.5/1.8  V <sub>IH</sub> V <sub>REF</sub> +0.5  V <sub>IL</sub> V <sub>REF</sub> -0.5  V <sub>REF</sub> 0.75/0.9  T <sub>R</sub> 2  T <sub>F</sub> 2  V <sub>REF</sub> V <sub>REF</sub> | VDDQ         1.5/1.8         V           VIH         VREF+0.5         V           VIL         VREF-0.5         V           VREF         0.75/0.9         V           TR         2         V/ns           TF         2         V/ns           VREF         V |

Notes

See AC Test Loading.

2. Parameter Tested with RQ=250 $\Omega$  and V<sub>DDQ</sub>=1.5V

## **AC Test Loading**

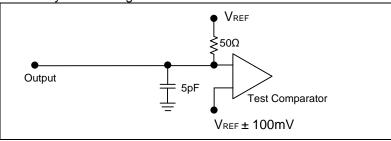

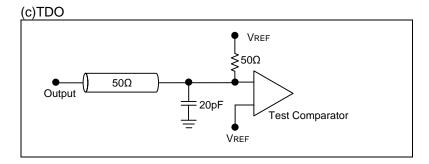

(a) Unless otherwise noted, AC test loading assume this condition.

(b) tCHQZ and tCHQX1 are specified with 5pF load capacitance and measured when transition occurs ±100mV from the steady state voltage.

## **AC Timing Characteristics**

(Over the Operating Temperature Range,  $V_{DD}$ =1.8V±5%,  $V_{DDQ}$ =1.5V/1.8V)

| Parameter                                                       | Symbol          | 30 (33    | 33MHz) | 33 (30    | 0MHz) | 40 (25 | 0MHz) | unit   | notos |

|-----------------------------------------------------------------|-----------------|-----------|--------|-----------|-------|--------|-------|--------|-------|

| Parameter                                                       | Symbol          | Min       | Max    | Min       | Max   | Min    | Max   | unit   | notes |

| Clock                                                           |                 |           |        |           |       |        |       |        |       |

| Clock Cycle Time (K, K#,C,C#)                                   | tKHKH           | 3.00      | 8.4    | 3.33      | 8.4   | 4.00   | 8.4   | ns     |       |

| Clock Phase Jitter (K, K#,C,C#)                                 | tKC var         |           | 0.3    |           | 0.3   |        | 0.3   | ns     | 4     |

| Clock High Time (K, K#,C,C#)                                    | tKHKL           | 0.4       |        | 0.4       |       | 0.4    |       | cycle  |       |

| Clock Low Time (K, K#,C,C#)                                     | tKLKH           | 0.4       |        | 0.4       |       | 0.4    |       | cycle  |       |

| Clock to Clock $(K_H \rightarrow K\#_H, C_H \rightarrow C\#_H)$ | tKHK#H          | 1.35      |        | 1.50      |       | 1.80   |       | ns     |       |

| Clock to Data Clock (K > C, K# > C#)                            | tKHCH           | 0         | 1.35   | 0         | 1.48  | 0      | 1.8   | ns     |       |

| DLL Lock Time (K,C)                                             | tKC lock        | 1024      |        | 1024      |       | 1024   |       | cycles | 5     |

| Doff Low period to DLL reset                                    | tDoffLowToReset | 5         |        | 5         |       | 5      |       | ns     |       |

| K static to DLL reset                                           | tKCreset        | 30        |        | 30        |       | 30     |       | ns     |       |

| Output Times                                                    |                 |           |        |           |       |        |       |        |       |

| C,C# High to Output Valid                                       | tCHQV           |           | 0.45   |           | 0.45  |        | 0.45  | ns     | 1,3   |

| C,C# High to Output Hold                                        | tCHQX           | -<br>0.45 |        | -<br>0.45 |       | -0.45  |       | ns     | 1,3   |

| C,C# High to Echo Clock Valid                                   | tCHCQV          |           | 0.45   |           | 0.45  |        | 0.45  | ns     | 1     |

| C,C# High to Echo Clock Hold                                    | tCHCQX          | -<br>0.45 |        | -<br>0.45 |       | -0.45  |       | ns     | 1     |

| CQ, CQ# High to Output Valid                                    | tCQHQV          |           | 0.30   |           | 0.30  |        | 0.30  | ns     | 1,3   |

| CQ, CQ# High to Output Hold                                     | tCQHQX          | 0.30      |        | 0.30      |       | -0.30  |       | ns     | 1,3   |

| C,C# High to Output High-Z                                      | tCHQZ           |           | 0.45   |           | 0.45  |        | 0.45  | ns     | 1,3   |

| C,C# High to Output Low-Z                                       | tCHQX1          | -<br>0.45 |        | -<br>0.45 |       | -0.45  |       | ns     | 1,3   |

| Setup Times                                                     |                 |           |        |           |       |        |       |        |       |

| Address valid to K rising edge                                  | tAVKH           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| R#,W# control inputs valid to K rising edge                     | tIVKH           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| BW <sub>x</sub> # control inputs valid to K rising edge         | tIVKH2          | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| Data-in valid to K, K# rising edge                              | tDVKH           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| Hold Times                                                      |                 |           |        |           |       |        |       |        |       |

| K rising edge to address hold                                   | tKHAX           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| K rising edge to R#,W# control inputs hold                      | tKHIX           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| K rising edge to BW <sub>x</sub> # control inputs hold          | tKHIX2          | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

| K, K# rising edge to data-in hold                               | tKHDX           | 0.30      |        | 0.30      |       | 0.30   |       | ns     | 2     |

- 1. All address inputs must meet the specified setup and hold times for all latching clock edges.

- 2. Control signals are R#, W#, BW<sub>0</sub>#, BW<sub>1</sub># and (BW<sub>2</sub>#, BW<sub>3</sub># for x36)

- To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ. The specs as shown do not imply bus contention because tCHQX1 is a MIN parameter that is worst case at totally different test conditions (0 C, 1.9V) than tCHQZ, which is a MAX parameter (worst case at 70 C, 1.7V) It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

- 4. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 5. V<sub>DD</sub> slew rate must be less than 0.1V DC per 50ns for DLL lock retention. DLL lock time begins once V<sub>DD</sub> and input clock are stable.

- 6. The data sheet parameters reflect tester guard bands and test setup variations.

- If address A1 = A2, data Q1-1 = D2-1 and data Q1-2 = D2-2. Write data is forwarded immediately as read results.

- B2-1 and B2-2 refer to all BWx# byte controls for D2-1 and D2-2 respectively.

- B4-1 and B4-2 refer to all BWx# byte controls for D4-1 and D4-2 respectively. 3.

- 4. B6-1 and B6-2 refer to all BWx# byte controls for D6-1 and D6-2 respectively.

- B7-1 and B7-2 refer to all BWx# byte controls for D7-1 and D7-2 respectively. 5.

- Outputs are disabled one cycle after a NOP.

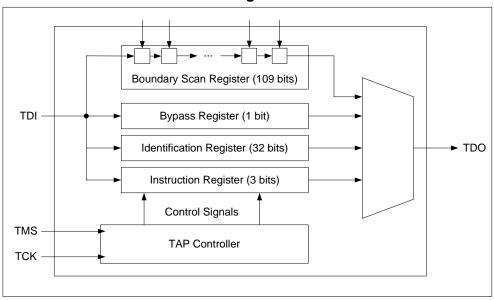

# IEEE 1149.1 Serial Boundary Scan of JTAG

These SRAMs incorporate a serial boundary scan Test Access Port (TAP) controller in 165 FBGA package. That is fully compliant with IEEE Standard 1149.1-2001. The TAP controller operates using standard 1.8 V interface logic levels.

### Disabling the JTAG feature

These SRAMs operate without using the JTAG feature. To disable the TAP controller, TCK must be tied Low (VSS) to prevent clocking of the device. TDI and TMS are internally pulled up and may be unconnected. They may alternatively be connected to VDD through a pull up resistor. TDO must be left unconnected. Upon power up, the device comes up in a reset state, which does not interfere with the operation of the device.

## **Test Access Port Signal List:**

### **Test Clock (TCK)**

The test clock is to operate only TAP controller. All inputs are captured on the rising edge of TCK. All outputs are driven from the falling edge of TCK.

### Test Mode Select (TMS)

The TMS input is to set commands of the TAP controller and is sampled on the rising edge of TCK. This pin can be left unconnected at SRAM operation. The pin is pulled up internally to keep logic high level.

### Test Data-In (TDI)

The TDI pin is to receive serially input information into the instruction and data registers. It can be connected to the input of any of the registers. The register between TDI and TDO is chosen by the instruction that is loaded into the TAP instruction register. For information on loading the instruction register (Refer to the TAP Controller State Diagram). TDI is internally pulled up and can be unconnected at SRAM. TDI is connected to the most significant bit (MSB) on any register.

### Test Data-Out (TDO)

The TDO pin is to drive serially clock data out from the JTAG registers. The output is active, depending upon the current state of the TAP state machine (Refer to instruction codes). The output changes on the falling edge of TCK. TDO is connected to the least significant bit (LSB) of any register.

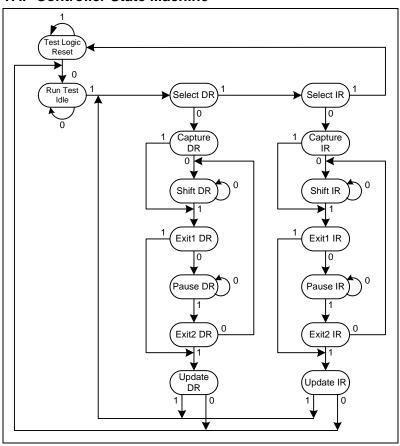

# **TAP Controller State and Block Diagram**

### **TAP Controller State Machine**

### **Performing a TAP Reset**

A Reset is performed by forcing TMS HIGH (VDD) for five rising edges of TCK. This Reset does not affect the operation of the SRAM and can be performed while the SRAM is operating. At power up, the TAP is reset internally to ensure that TDO comes up in a High Z state.

## **TAP Registers**

Registers are connected between the TDI and TDO pins and allow data to be scanned into and out of the SRAM test circuitry. Only one register can be selected at a time through the instruction registers. Data is serially loaded into the TDI pin on the rising edge of TCK and output on the TDO pin on the falling edge of TCK.

## **Instruction Register**

This register is loaded during the update-IR state of the TAP controller. Three-bit instructions can be serially loaded into the instruction register. At power-up, the instruction register is loaded with the IDCODE instruction. It is also loaded with the IDCODE instruction if the controller is placed in a reset state as described in the previous section. When the TAP controller is in the capture-IR state, the two LSBs are loaded with a binary "01" pattern to allow for fault isolation of the board-level serial test data path.

### **Bypass Register**

The bypass register is a single-bit register that can be placed between the TDI and TDO balls. It is to skip certain chips without serial boundary scan. This allows data to be shifted through the SRAM with minimal delay. The bypass register is set LOW  $(V_{SS})$  when the BYPASS instruction is executed.

#### **Boundary Scan Register**

The boundary scan register is connected to all the input and output balls on the SRAM. Several No Connected(NC) balls are also included in the scan register to reserve other product options. The boundary scan register is loaded with the contents of the SRAM input and output ring when the TAP controller is in the capture-DR state and is then placed between the TDI and TDO balls when the controller is moved to the shift-DR state. The EXTEST, SAMPLE/PRELOAD, and SAMPLE Z instructions can be used to capture the contents of the input and output ring. Each bit corresponds to one of the balls on the SRAM package. The MSB of the register is connected to TDI, and the LSB is connected to TDO.

### Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code during the Capture-DR state when the IDCODE command is loaded in the instruction register. The IDCODE is hardwired into the SRAM and can be shifted out when the TAP controller is in the shift-DR state. The ID register has a vendor ID code and other information

#### **TAP Instruction Set**

TAP Instruction Set is available to set eight instructions with the three bit instruction register and all combinations are listed in the TAP Instruction Code Table. Three of listed instructions on this table are reserved and must not be used. Instructions are loaded serially into the TAP controller during the Shift-IR state when the instruction register is placed between TDI and TDO. To execute an instruction once it is shifted in, the TAP controller must be moved into the Update-IR state.

#### **IDCODE**

The IDCODE instruction causes a vendor-specific, 32-bit code to be loaded into the instruction register. It also places the instruction register between the TDI and TDO balls and allows the IDCODE to be shifted out of the device when the TAP controller enters the shift-DR state. The IDCODE instruction is loaded into the instruction register upon power-up or whenever the TAP controller is given a test logic reset state.

### **SAMPLE Z**

The SAMPLE Z instruction connects the boundary scan register between the TDI and TDO pins when the TAP controller is in a Shift-DR state. The SAMPLE Z command puts the output bus into a High Z state until the next command is supplied during the Update IR state.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a IEEE 1149.1 basic instruction which connects the boundary scan register between the TDI and TDO pins when the TAP controller is in a Shift-DR state.. A snapshot of data on the inputs and output balls is captured in the boundary scan register when the TAP controller is in a Shift-DR state. The user must be aware that the TAP controller clock can only operate at a frequency up to 20 MHz, while the SRAM clock operates significantly faster. Because there is a large difference between the clock frequencies, it is possible that during the capture-DR state, an input or output will undergo a transition. The TAP may then try to capture a signal while in transition. This will not harm the device, but there is no guarantee as to the value that will be captured. Repeatable results may not be possible. To ensure that the boundary scan register will capture the correct value of a signal, the SRAM signal must be stabilized long enough to meet the TAP controller's capture setup plus hold time. The SRAM clock input might not be captured correctly if there is no way in a design to stop (or slow) the clock during a SAMPLE/ PRELOAD instruction. If this is an issue, it is still possible to capture all other signals and simply ignore the value of the CK and CK# captured in the boundary scan register. Once the data is captured, it is possible to shift out the data by putting the TAP into the shift-DR state. This places the boundary scan register between the TDI and TDO balls.

PRELOAD places an initial data pattern at the latched parallel outputs of the boundary scan register cells before the selection of another boundary scan test operation. The shifting of data for the SAMPLE and PRELOAD phases can occur concurrently when required, that is, while the data captured is shifted out, the preloaded data can be shifted in.

#### **BYPASS**

When the BYPASS instruction is loaded in the instruction register and the TAP is placed in a shift-DR state, the bypass register is placed between TDI and TDO. The advantage of the BYPASS instruction is that it shortens the boundary scan path when multiple devices are connected together on a board.

### **PRIVATE**

Do not use these instructions. They are reserved for future use and engineering mode.

#### **EXTEST**

The EXTEST instruction drives the preloaded data out through the system output pins. This instruction also connects the boundary scan register for serial access between the TDI and TDO in the Shift-DR controller state. IEEE Standard 1149.1 mandates that the TAP controller be able to put the output bus into a tri-state mode. The boundary scan register has a special bit located at bit #109. When this scan cell, called the "EXTEST output bus tri-state," is latched into the preload register during the Update-DR state in the TAP controller, it directly controls the state of the output (Q-bus) pins, when the EXTEST is entered as the current instruction. When HIGH, it enables the output buffers to drive the output bus. When LOW, this bit places the output bus into a High Z condition. This bit can be set by entering the SAMPLE/PRELOAD or EXTEST command, and then shifting the desired bit into that cell during the Shift-DR state. During Update-DR, the value loaded into that shift-register cell latches into the preload register. When the EXTEST instruction is entered, this bit directly controls the output Q-bus pins. Note that this bit is pre-set LOW to enable the output when the device is powered up, and also when the TAP controller is in the Test-Logic-Reset state.

### **JTAG DC Operating Characteristics**

(Over the Operating Temperature Range, Vpp=1.8V±5%)

| Parameter                   | Symbol              | Min  | Max                  | Units | Notes                    |

|-----------------------------|---------------------|------|----------------------|-------|--------------------------|

| JTAG Input High Voltage     | V <sub>IH1</sub>    | 1.3  | V <sub>DD</sub> +0.3 | V     |                          |

| JTAG Input Low Voltage      | V <sub>IL1</sub>    | -0.3 | 0.5                  | V     |                          |

| JTAG Output High Voltage    | V <sub>OH1</sub>    | 1.4  | -                    | V     | I <sub>OH1</sub>  =2mA   |

| JTAG Output Low Voltage     | V <sub>OL1</sub>    | -    | 0.4                  | V     | I <sub>OL1</sub> =2mA    |

| JTAG Output High Voltage    | $V_{OH2}$           | 1.6  | -                    | V     | I <sub>OH2</sub>  =100uA |

| JTAG Output Low Voltage     | V <sub>OL2</sub>    | -    | 0.2                  | V     | I <sub>OL2</sub> =100uA  |

| JTAG Input Leakage Current  | I <sub>LIJTAG</sub> | -100 | +100                 | uA    | 0 ≤ Vin ≤ VDD            |

| JTAG Output Leakage Current | I <sub>LOJTAG</sub> | -5   | +5                   | uA    | 0 ≤ Vout ≤ VDD           |

<sup>1.</sup> All voltages referenced to VSS (GND); All JTAG inputs and outputs are LVTTL-compatible.

### **JTAG AC Test Conditions**

(Over the Operating Temperature Range, V<sub>DD</sub>=1.8V±5%, V<sub>DDQ</sub>=1.5V/1.8V)

| Parameter                               | Symbol           | Conditions | Units |

|-----------------------------------------|------------------|------------|-------|

| Input Pulse High Level                  | V <sub>IH1</sub> | 1.3        | V     |

| Input Pulse Low Level                   | V <sub>IL1</sub> | 0.5        | V     |

| Input Rise Time                         | T <sub>R1</sub>  | 1.0        | ns    |

| Input Fall Time                         | T <sub>F1</sub>  | 1.0        | ns    |

| Input and Output Timing Reference Level |                  | 0.9        | V     |

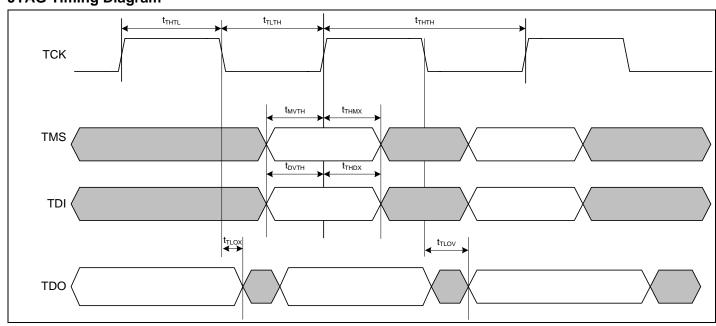

### **JTAG AC Characteristics**

(Over the Operating Temperature Range, V<sub>DD</sub>=1.8V±5%, V<sub>DDQ</sub>=1.5V/1.8V)

| Parameter                | Symbol            | Min | Max | Units |

|--------------------------|-------------------|-----|-----|-------|

| TCK cycle time           | t <sub>THTH</sub> | 50  | _   | ns    |

| TCK high pulse width     | t <sub>THTL</sub> | 20  | _   | ns    |

| TCK low pulse width      | t <sub>TLTH</sub> | 20  | _   | ns    |

| TMS Setup                | t <sub>MVTH</sub> | 5   | _   | ns    |

| TMS Hold                 | t <sub>THMX</sub> | 5   | _   | ns    |

| TDI Setup                | t <sub>DVTH</sub> | 5   | _   | ns    |

| TDI Hold                 | t <sub>THDX</sub> | 5   | _   | ns    |