## <u>TOSHIBA</u>

TOSHIBA Bi-CMOS Integrated Circuit Silicon Monolithic

# TB6860WBG

Qi compliant wireless power receiver and charger IC

## 1. Outline

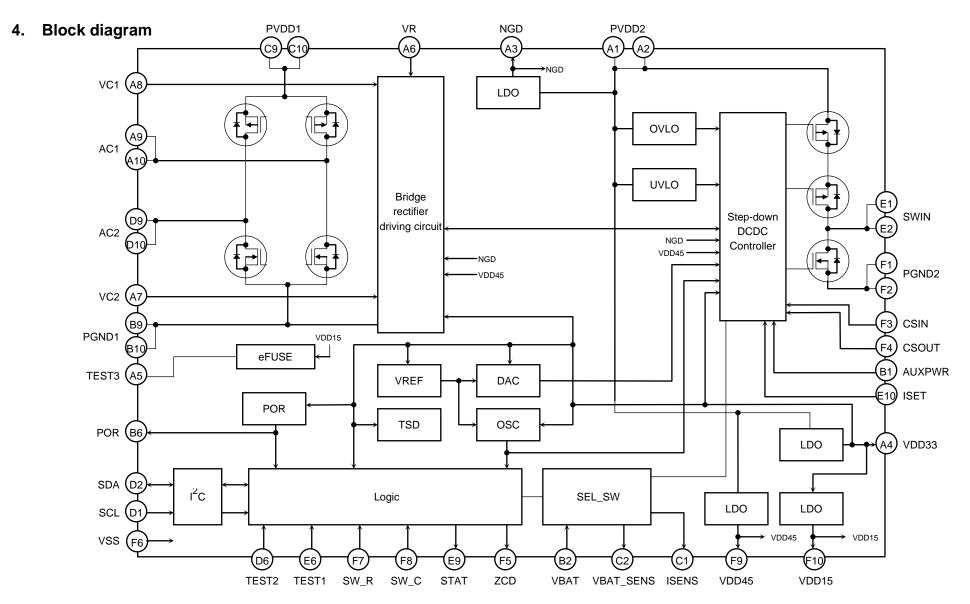

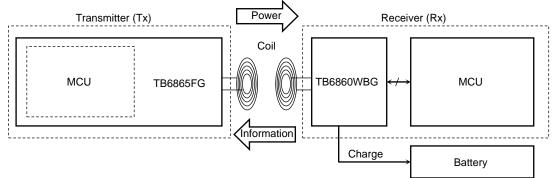

The TB6860WBG is Qi compliant wireless power receiver (Rx) IC. The TB6860WBG includes a bridge rectifier circuit, a modulation circuit, and a step-down DCDC converter. The wireless power system is constructed easily by combining with the TB6865FG which is a wireless power transmitter (Tx) IC. Charge mode and feed mode can be selected because the step-down DCDC converter has two operating modes. It expands usage flexibility.

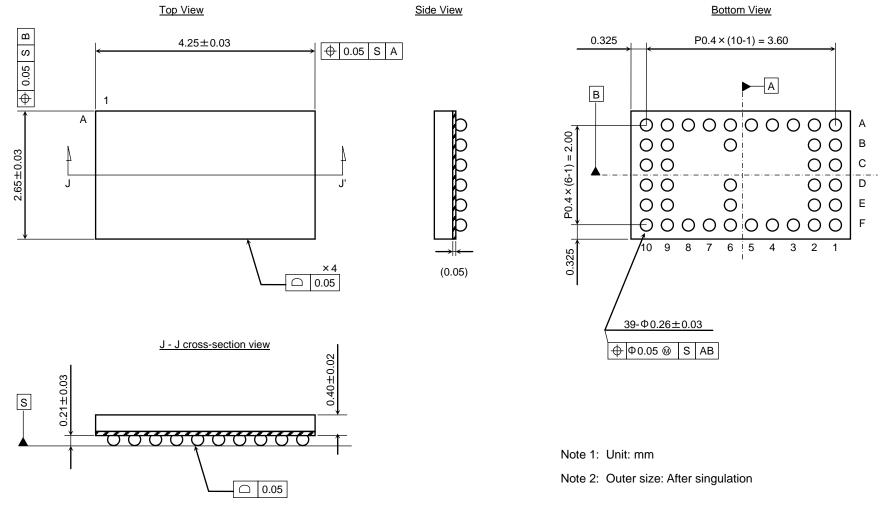

#### S-WFBGA39-0305-0.40A01

## 2. Applications

Mobile devices (Smartphone, tablet), Battery pack, Mobile accessory etc.

## 3. Features

- Input voltage

- Maximum output current

- : PVDD2 = 3.4V to 12V

- : Step-down DCDC converter ... 1.2A

- 3.3V-LDO output (VDD33) ..... 60mA

- : Selectable modes (feed mode or charge mode) Switching frequency 3MHz

- I<sup>2</sup>C communication (Slave/Fast mode)

Synchronous rectification step-down DCDC converter

- WPC v1.0.3 compliant modulation

- Under voltage lockout (UVLO)

- Over voltage lockout(OVLO)

- Over current limit protection (OCL)

- Thermal shutdown protection (TSD)

- Package

: WCSP (4.25mm×2.65mm)

This product has a MOS structure and is sensitive to electrostatic discharge. When handling this product, ensure that the environment is protected against electrostatic discharge by using an earth strap, a conductive mat and an ionizer. Ensure also that the ambient temperature and relative humidity are maintained at reasonable levels.

Figure 4.1 Block diagram

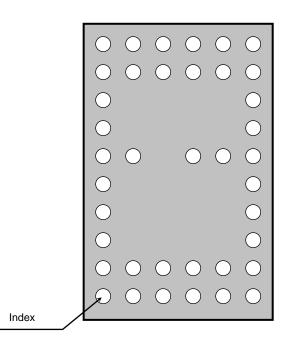

## 5. Pin Assignment

| 10 | AC1   | PGND1  | PVDD1     | AC2   | ISET  | VDD15 |

|----|-------|--------|-----------|-------|-------|-------|

| 9  | AC1   | PGND1  | PVDD1     | AC2   | STAT  | VDD45 |

| 8  | VC1   |        |           |       |       | SW_C  |

| 7  | VC2   |        |           |       |       | SW_R  |

| 6  | VR    | POR    |           | TEST2 | TEST1 | VSS   |

| 5  | TEST3 |        |           |       |       | ZCD   |

| 4  | VDD33 |        |           |       |       | CSOUT |

| 3  | NGD   |        |           |       |       | CSIN  |

| 2  | PVDD2 | VBAT   | VBAT_SENS | SDA   | SWIN  | PGND2 |

| 1  | PVDD2 | AUXPWR | ISENS     | SCL   | SWIN  | PGND2 |

|    | А     | В      | С         | D     | E     | F     |

|    |       |        |           |       |       |       |

(Top View)

Figure 5.1 Pin Assignment

Note: The pin configuration figure is indicated that package ball side is located on the back and indicating pins from the surface view

## 6. Pin function

#### Table 6.1 Pin function

| Pin<br>Number | Pin symbol | I/O | Description                                                                                                                                                                                                                                   |

|---------------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C9, C10       | PVDD1      | 0   | Bridge rectifier voltage output<br>Connect smoothing ceramic capacitor between PVDD1 and GND. And connect PVDD1<br>with PVDD2.                                                                                                                |

| A9, A10       | AC1        | I/O | Antonno terminale for receiver                                                                                                                                                                                                                |

| D9, D10       | AC2        | I/O | Antenna terminals for receiver                                                                                                                                                                                                                |

| B9, B10       | PGND1      | -   | Power ground 1<br>Connect to common ground (GND).                                                                                                                                                                                             |

| F5            | ZCD        | ο   | Test terminal 4<br>Keep open condition.                                                                                                                                                                                                       |

| B6            | POR        | 0   | Power On Reset                                                                                                                                                                                                                                |

| D2            | SDA        | I/O | DATA terminal for I <sup>2</sup> C (Note)<br>Connect to pull-up resistor because it is an open drain terminal.                                                                                                                                |

| D1            | SCL        | I   | CLK input terminal for I <sup>2</sup> C (Note)                                                                                                                                                                                                |

| F6            | VSS        | -   | Analog ground terminal<br>Connect to common ground (GND)                                                                                                                                                                                      |

| E6            | TEST1      | I   | Test terminal 1<br>Connect to GND                                                                                                                                                                                                             |

| D6            | TEST2      | I   | Test terminal 2<br>Connect to GND                                                                                                                                                                                                             |

| A5            | TEST3      | I   | Test terminal 3<br>Connect to VDD33                                                                                                                                                                                                           |

| F7            | SW_R       | I   | Input terminal for resistance load ASK modulation control<br>This terminal is available by setting internal resister. When it's not in use, connect to GND.                                                                                   |

| F8            | SW_C       | I   | Input terminal for capacitive load ASK modulation control<br>This terminal is available by setting internal resister. When it's not in use, connect to GND.                                                                                   |

| E9            | STAT       | 0   | Status signal output terminal<br>STAT="L" : Step-down DCDC converter is on.<br>STAT="H" : Step-down DCDC converter is off.                                                                                                                    |

| C2            | VBAT_SENS  | 0   | Monitor terminal for battery voltage<br>One third of VBAT input voltage is output.                                                                                                                                                            |

| C1            | ISENS      | 0   | Monitor terminal for output current<br>It's possible to monitor following three kinds of voltages by setting internal resister.<br>1) Output current voltage<br>2) The voltage of VBAT×1/3 (VBAT_SENS output)<br>3) The voltage of PVDD2×1/8. |

| A8            | VC1        | 0   | Capacitor connection terminal 1 for capacitive load ASK modulation<br>This terminal is open drain. When using this function, connect capacitor between VC1 and<br>AC1. When it's not in use, connect to GNO or keep open condition.           |

| A7            | VC2        | 0   | Capacitor connection terminal 2 for capacitive load ASK modulation<br>This terminal is open drain. When using this function, connect capacitor between VC2 and<br>AC2. When it's not in use, connect to GNO or keep open condition.           |

Note: The SDA and SCL pins have ESD protection diodes to VDD33. TB6862WBG cannot share the  $I^2C$  bus with other peripheral IC.

### Table 6.2 Pin function

| Pin<br>Number | Pin symbol | I/O | Description                                                                                                                                                                                                                                    |

|---------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2        | PVDD2      | -   | Power supply terminal<br>This terminal supplies power to internal LDOs and step-down DCDC converter. Connect<br>capacitor between PVDD2 and GND.                                                                                               |

| E1, E2        | SWIN       | 0   | Step-down DCDC converter output terminal<br>Connect inductor between SWIN and CSIN.                                                                                                                                                            |

| F1, F2        | PGND2      | -   | Power ground 2<br>Connect to common ground (GND).                                                                                                                                                                                              |

| F3            | CSIN       | I   | Current sense input terminal (+)<br>Connect resistor for current detection of $68m\Omega$ between CSIN and CSOUT.                                                                                                                              |

| F4            | CSOUT      | I   | Current sense input terminal (-) Connect resistor for current detection of $68m\Omega$ between CSIN and CSOUT.                                                                                                                                 |

| B1            | AUXPWR     | I   | Voltage feedback input                                                                                                                                                                                                                         |

| F9            | VDD45      | 0   | 4.5V-LDO output terminal for internal circuit<br>It is impossible to supply power to external parts. Connect capacitor between VDD45 and<br>GND.                                                                                               |

| A4            | VDD33      | 0   | 3.3V-LDO output terminal<br>Connect capacitor between VDD33 and GND.                                                                                                                                                                           |

| F10           | VDD15      | 0   | 1.5V-LDO output terminal for internal circuit.<br>It is impossible to supply power to external parts. Connect capacitor between VDD15 and GND.                                                                                                 |

| A3            | NGD        | 0   | PVDD2-4.5V output terminal for internal circuit.<br>It is impossible to supply power to external parts. Connect capacitor between NGD and<br>PVDD2.                                                                                            |

| B2            | VBAT       | I   | Battery voltage input terminal<br>In charge mode, input output voltage of external battery.                                                                                                                                                    |

| E10           | ISET       | I   | Test terminal 5<br>Connect to GND                                                                                                                                                                                                              |

| A6            | VR         | 0   | Resistor connect terminal for resistance load ASK modulation control<br>This terminal is open drain terminal. When using this function, connect resistor between VR<br>and PVDD1. When it's not in use, connect to GNO or keep open condition. |

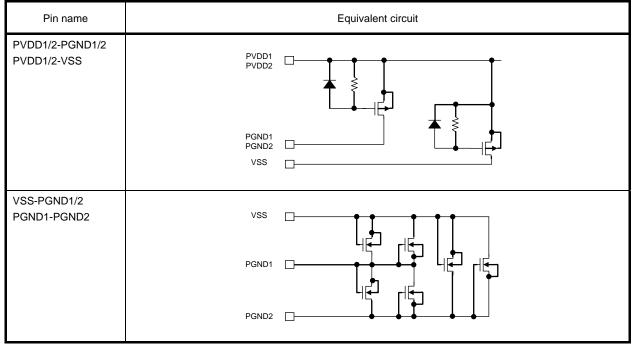

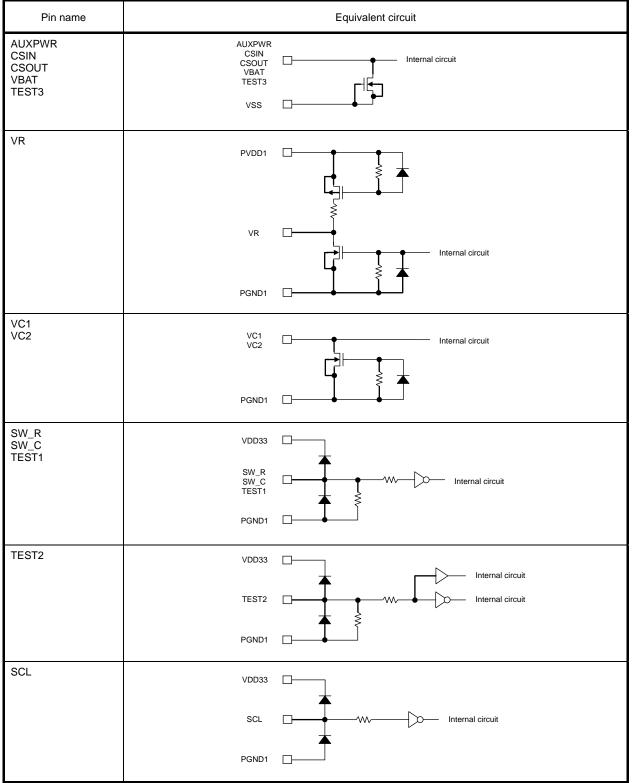

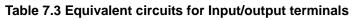

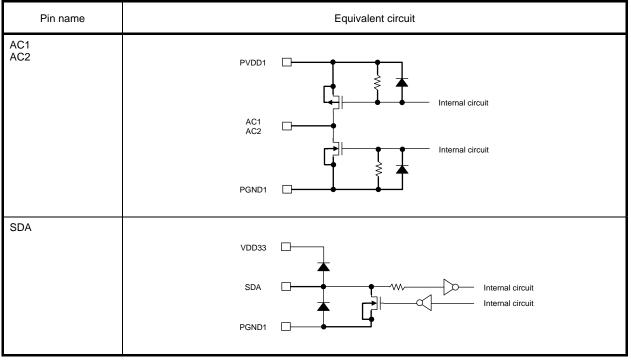

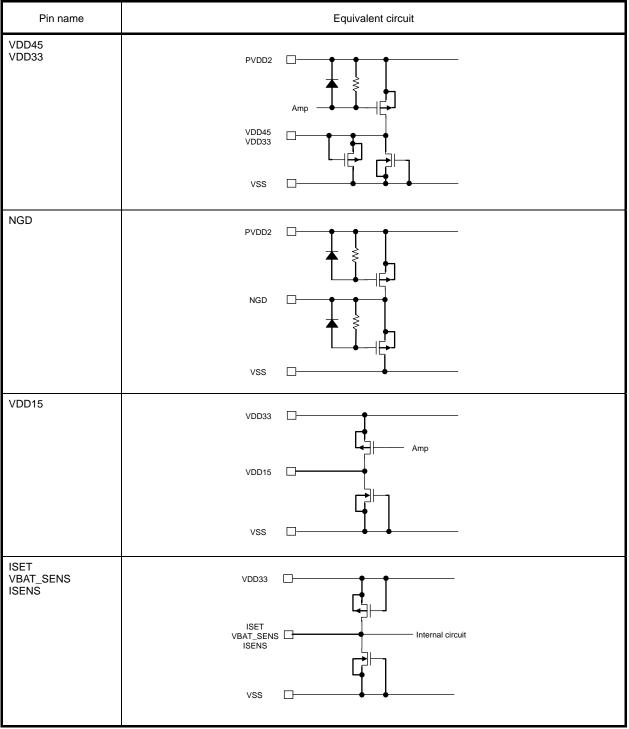

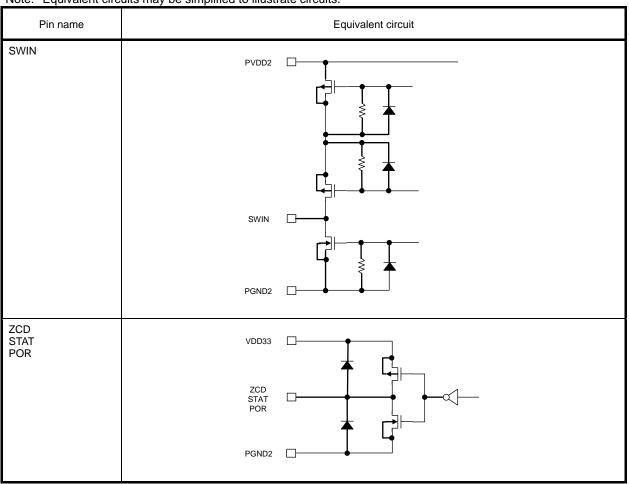

## 7. Equivalent circuits for input/output/power supply terminals

## 7.1 Power supply terminal

### Table 7.1 Equivalent circuits for power supply terminals

## 7.2 Input terminal

#### Table 7.2 Equivalent circuits for input terminals

## 7.3 Input/output terminal

## 7.4 Output terminal

## Table 7.4 Equivalent circuits for output terminals

### Table 7.5 Equivalent circuits for output terminals

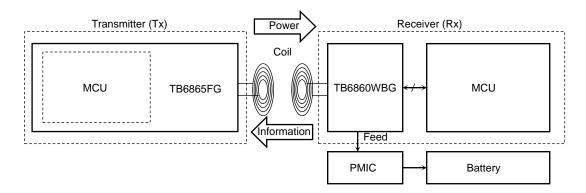

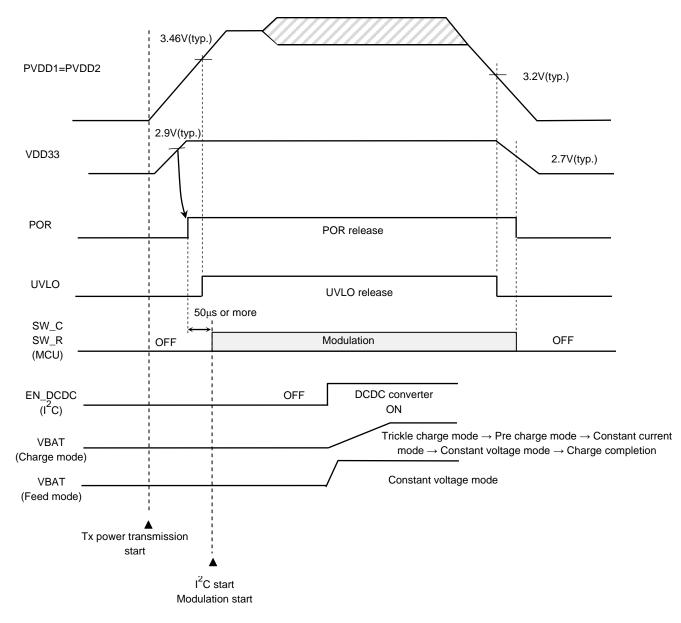

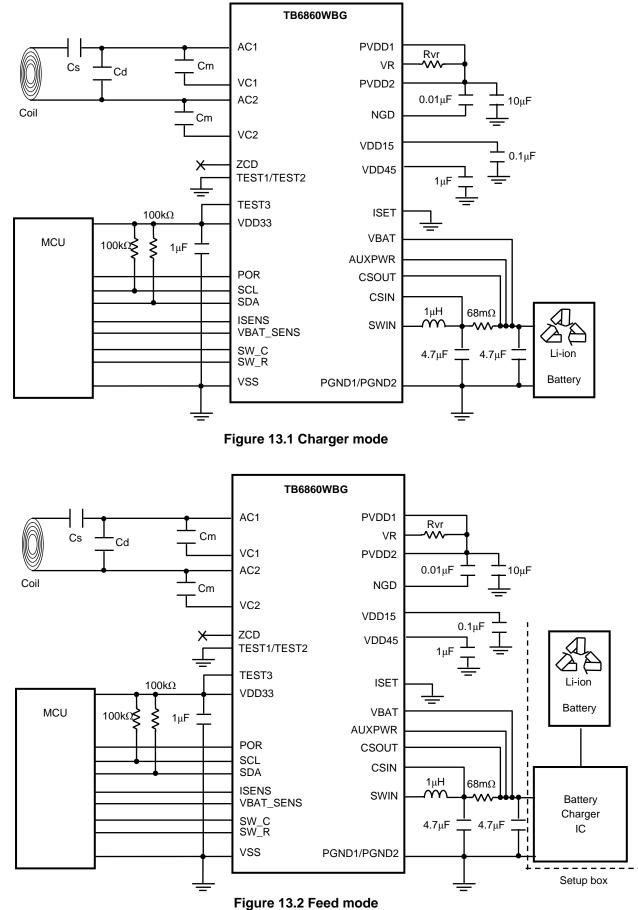

## 8. Function

The TB6860WBG is Qi compliant wireless power receiver (Rx) IC. Qi compliant wireless power system transfers power by adjoining coils of transmitter (Tx) and receiver (Rx). The TB6860WBG includes a bridge rectifier circuit which rectifies AC power received by a coil (Rx), a modulation circuit for communicating from Rx to Tx side, and a step-down DCDC converter for supplying power to the load. The step-down DCDC converter makes possible to operate the driver in two modes of charge mode and feed mode. Select the operating mode depending on the method of power feed to the system. Construction of the circuit when the TB6860WBG charges battery directly (charge mode) is shown in Figure 8.1. And the Figure 8.2 indicates the construction of the circuit when the TB6860WBG feeds power to the battery charging circuit (feed mode). It is possible to feed power to the load with high efficiency by adopting step-down DCDC converter.

(1) Charging the battery directly

Figure 8.1 Charge mode

(2) Charging the battery through feeding power to the external PMIC

Figure 8.2 Feed mode

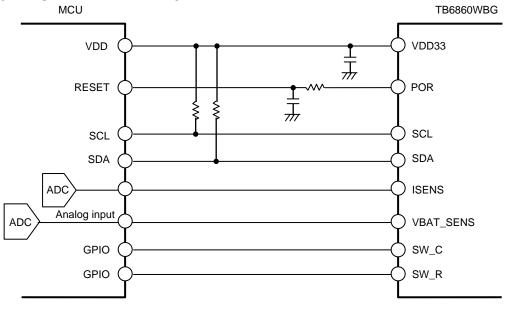

Communication from Rx to Tx is necessary to construct wireless feed system. Rx should monitor receiving power and return communication signal according to Qi standard. The TB6860WBG includes a modulation circuit and a power circuit (VDD33) which drives MCU. The communication signal between Rx and Tx should be input from MCU to the TB6860WBG. And it should be controlled by  $I^2C$  interface to enable each function which is fed power from the TB6860WBG. Construct the system by combining the MCU which includes AD converter,  $I^2C$  interface, and GPIO. Connecting description is shown in the Figure 8.3.

Figure 8.3 Example of connection with MCU

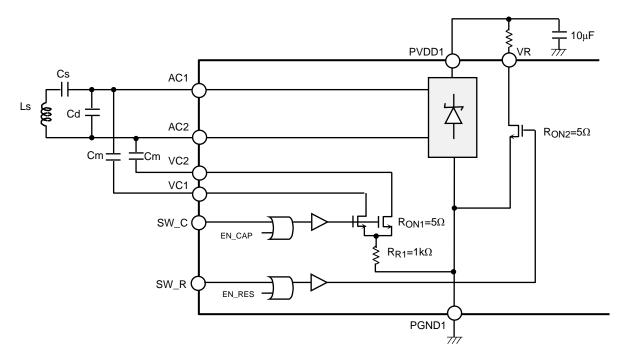

The TB6860WBG drives modulated operation, which is necessary to communicate between Rx and Tx by inputting data to SW\_C terminal or SW\_R terminal from MCU. The TB6860WBG supports two ASK modulations of capacitive load and resistance load. In case of ASK modulation by capacitive load, connect the capacitor to VC1 and VC2 terminals and input data to SW\_C terminal. In case of ASK modulation by resistance load, connect the resistor between VR terminal and PVDD1 terminal and input data to SW\_R terminal. It is possible to drive modulated operation without inputting data to SW\_C terminal and SW\_R terminal by using I<sup>2</sup>C interface. In this case, EN\_CAP register and EN\_RES register are re-written by I<sup>2</sup>C interface.

#### 8.1 Step-down DCDC converter charge/feed mode

Step-down DCDC converter operates with switching frequency of 3MHz (typ.). Step-down DCDC converter has two operation modes of charge mode and feed mode. Operation mode is configured by CH\_DC register. Step-down DCDC converter is turned on and off by EN\_DCDC register. When step-down DCDC converter turns on, STAT outputs "L", and when it turns off, STAT outputs "H".

#### 8.1.1 Waiting mode

When EN\_DCDC is set "0", the step-down DCDC converter is turned off and the operation moves to waiting mode. When EN\_DCDC is set "1", the step-down DCDC converter starts operation with charge mode or feed mode according to the CH\_DC register set. Make sure to configure the related registers before turning on the step-down DCDC converter. EN\_DCDC register is rewritten to "0" automatically and the operation moves to the waiting mode in following two cases; operation of the step-down DCDC converter stops by protection circuits and charging is completed in the charge mode.

#### 8.1.2 Charge mode

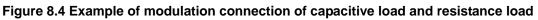

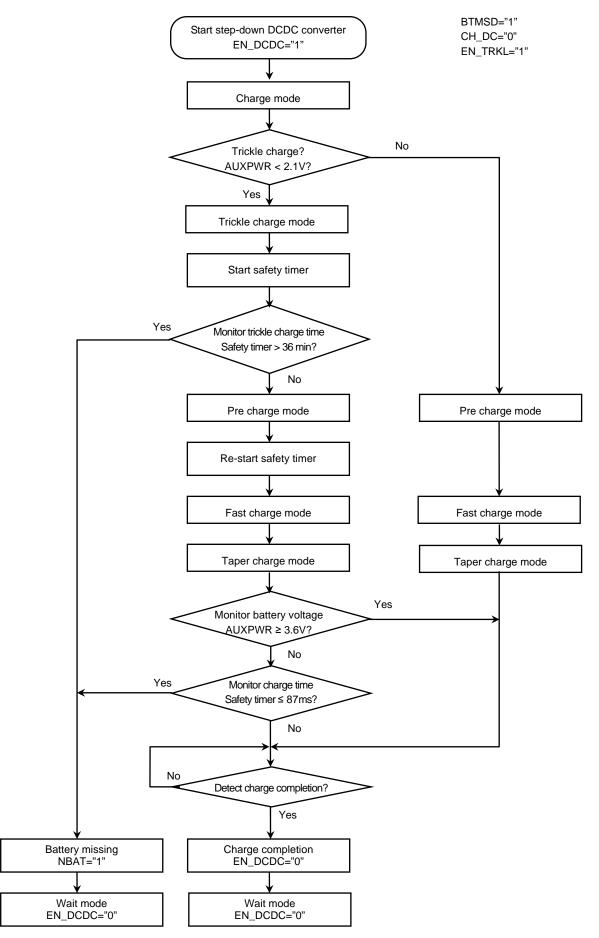

It is possible to charge the battery directly by setting CH\_DC "0" and operates the step-down DCDC converter in charge mode. Charge mode has the constant current (CC) charge modes (trickle charge, pre-charge, and fast charge) and the constant voltage (CV) charge mode (taper charge). Control, switch, and charge completion of these modes are detected by monitoring battery voltage by AUXPWR terminal and monitoring charging current by the voltage between CSIN terminal and CSOUT terminal.

#### (1) Trickle charge mode

It detects charge of the over discharged battery and abnormal operation. The trickle charge can be turned on and off by the EN\_TRKL register. When the step-down DCDC converter is set on (EN\_DCDC="1") while the trickle charge is on (EN\_TRKL="1"), the voltage of the battery is detected. When the voltage of the battery is detected 2.1 V or less, the trickle charge starts. The charge current of the trickle charge mode is 40mA (typ.). When the step-down DCDC converter is set on (EN\_DCDC="1") while the trickle charge is off (EN\_TRKL="0"), the operation moves to the pre charge mode regardless of the voltage of the battery. When the voltage of the battery reaches 2.1 V during the trickle charge mode, it moves to the pre charge mode.

#### (2) Pre charge mode

It charges the over discharged battery. When the voltage of the battery reaches 2.1 V while the trickle charge is on (EN\_TRKL="1"), the pre charge starts. When the step-down DCDC converter is set on (EN\_DCDC="1") while the trickle charge is off (EN\_TRKL="0"), the pre charge also starts. The charge current in the pre charge mode can be set in the range of 0mA to 400mA by the PRCC2-0 register. When the voltage of the battery reaches the voltage configured by FSTV3-0 register during the pre charge mode, the operation moves to the fast charge mode.

#### (3) Fast charge mode

It is a rapid charge mode. When the voltage of the battery reaches the voltage configured by FSTV3-0 register during the pre charge mode, the operation moves to the fast charge mode. The charge current of the fast charge mode can be set in the range of 0mA to 1,200mA by CCLT4-0 register. When the voltage of the battery reaches the voltage set by CVF7-0 register during the fast charge mode, the operation moves to the taper charge mode.

#### (4) Taper charge mode

It is the charge mode of the constant voltage. When the voltage of the battery reaches the voltage set by CVF7-0 register during the fast charge mode, the taper charge starts. The charge voltage of the taper charge mode can be set by CVF7-0 register in the range of 3.0V to 5.55V. In the taper charge mode, the detection of charge completion can be set on or off by the EN\_TERM register. When the charge completion detection is on (EN\_TERM="1"), the charge is judged completed in the case the charge current decreases to the current value set by TERMC1-0 register. When charge completion is detected, the step-down DCDC converter is turned off (EN\_DCDC="0") and the operation moves to the waiting mode. The current of termination can be set by TERMC1-0 register in the range of 50mA to 200mA. When the charge completion detection is turned off (EN\_DCDC="0"), this detection is invalid and setting of EN\_DCDC register should be set "0" to stop charging.

| Charge mode       | Control | Charge current | Starting condition                            | Finishing condition                             | Remarks                                                                                          |

|-------------------|---------|----------------|-----------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Trickle<br>charge | СС      | 40mA           | EN_TRKL="1"<br>&<br>Battery voltage<2.1V      | EN_TRKL="1"<br>&<br>Battery voltage≥2.1V        | ON or OFF setting of<br>the trickle charge is<br>possible by<br>EN_TRKL register                 |

| Pre charge        | СС      | 50mA to 400mA  | EN_TRKL="0"<br>or<br>Battery voltage≥2.1V     | Battery voltage≥FSVT3-0<br>(2.1V to 3.6V)       |                                                                                                  |

| Fast charge       | СС      | 1,200mA (max)  | Battery voltage≥<br>FSVT3-0<br>(2.1V to 3.6V) | Battery voltage≥CVF7-0<br>(3.0V to 5.55V)       |                                                                                                  |

| Taper charge      | CV      | 50mA to 200mA  | Battery voltage≥CVF7-0<br>(3.0V to 5.55V)     | Charge current ≤<br>TERMC1-0<br>(50mA to 200mA) | ON or OFF setting of<br>the charge<br>completion detection<br>is possible by<br>EN_TERM register |

Table 8.1 Charge mode

Note: Make sure to set CVF7-0 voltage > FSVT3-0 voltage.

Figure 8.5 Output of charge mode

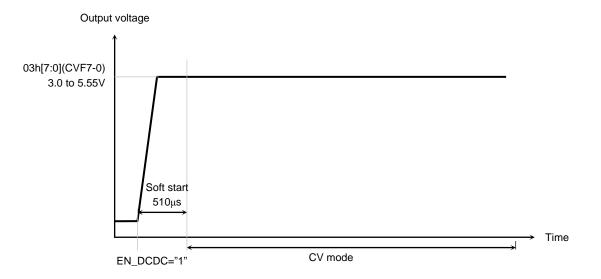

#### 8.1.3 Feed mode

The step-down DCDC converter operates in feed mode by setting CH\_DC="1". The constant voltage is supplied in this mode. Feed mode has soft start and CV mode. These modes are switched by internal counter automatically. The output voltage can be set in the range of 3.0V to 5.55V by CVF7-0 register. The over current limit value is different between the soft start mode and CV mode.

#### (1) Soft start

It avoids rush current which is generated just after startup. Soft start starts by setting the step-down DCDC converter on (EN\_DCDC="1"). The over current limit value changes three steps as follows;

For 170µs just after soft start starting: 300mA

170µs to 340µs: 600mA

340 $\mu s$  to 510  $\mu s$  : 900 mA

The operation moves to the feed mode after  $510 \mu s$  of starting soft start.

#### (2) CV mode

It supplies constant voltage. The over current limit value is 2.4A in this mode

| Feed mode | Allowable current (typ.) | Over current limit (typ.) | Setting voltage (typ.)    | Remarks                       |

|-----------|--------------------------|---------------------------|---------------------------|-------------------------------|

| CV        | 1.2A                     | 2.4A                      | 3.0V to 5.55V<br>(CVF7-0) | CCLT4-0 setting is not valid. |

## 8.2 Circuit state in each operation mode

| Mode      |                | Rectifier circuit,<br>Modulation circuit,<br>LDO | Step-down<br>DCDC<br>converter | UVLO,<br>OVLO(Note1),<br>TSD | Safety<br>timer<br>(Note2) | OCL     | I <sup>2</sup> C | Writable<br>register |

|-----------|----------------|--------------------------------------------------|--------------------------------|------------------------------|----------------------------|---------|------------------|----------------------|

| Waiting n | node           | Enable                                           | Disable                        | Enable                       | Disable                    | Disable | Access enable    | All address          |

|           | Trickle charge | Enable                                           | Enable                         | Enable                       | Enable                     | Enable  | Access enable    | 00h (Note3)          |

| Charge    | Pre charge     | Enable                                           | Enable                         | Enable                       | Enable                     | Enable  | Access enable    | 00h (Note3)          |

| mode      | Fast charge    | Enable                                           | Enable                         | Enable                       | Enable                     | Enable  | Access enable    | 00h (Note3)          |

|           | Taper charge   | Enable                                           | Enable                         | Enable                       | Enable                     | Enable  | Access enable    | 00h (Note3)          |

| Feed      | Soft start     | Enable                                           | Enable                         | Enable                       | Disable                    | Enable  | Access enable    | 00h (Note3)          |

| mode      | CV             | Enable                                           | Enable                         | Enable                       | Disable                    | Enable  | Access enable    | 00h (Note3)          |

#### Table 8.3 Circuit in each mode

Note 1: It is possible to turn OVLO function on or off by setting of 00h[7] resister, (EN\_OVLO).

Note 2: It is possible to turn safety timer on or off by setting of 01h[3] resister, (BTMSD).

Note 3: No writing any resisters except 00h resister at Charge mode and Feed mode.

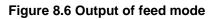

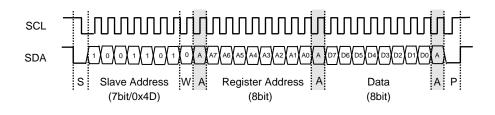

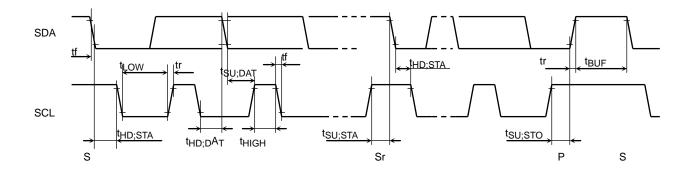

### 8.3 Interface

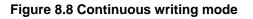

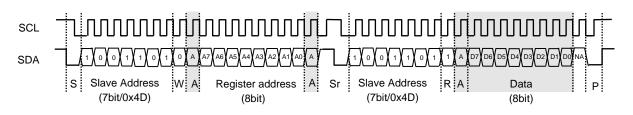

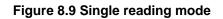

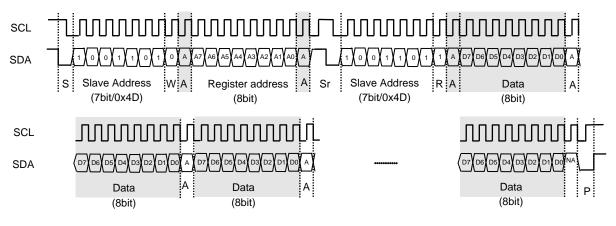

Each function of the TB6860WBG is configured by  $I^2C$  interface. It supports the sleeve function ( $I^2C$  standard) and the fast mode (400 kHz). Single writing, continuous writing, single reading, and continuous reading are possible. The sleeve address of the TB6860WBG is fixed 0b1001101.As for description of writing and reading; refer to below Figure 8.7 to Figure 8.10.

| Symbol        | Description                         |  |  |  |  |

|---------------|-------------------------------------|--|--|--|--|

| S             | Start condition                     |  |  |  |  |

| Sr            | Repeat start condition              |  |  |  |  |

| Slave Address | Sleeve address (7bit)               |  |  |  |  |

| R             | Read mode (R/W=1)                   |  |  |  |  |

| W             | Write mode (R/W=0)                  |  |  |  |  |

| A             | Acknowledge signal (output L level) |  |  |  |  |

| NA            | Non acknowledge signal (output HiZ) |  |  |  |  |

| Р             | Stop condition                      |  |  |  |  |

## Table 8.4 Description of I<sup>2</sup>C interface

Figure 8.7 Single writing mode

Note 1: In continuous writing, return ACK without writing data to register 06h.

Figure 8.10 Continuous reading mode

- Note 1: When ACK="1", the command of stop condition should be input to MCU.

- Note 2: When stop condition is recognized, the TB6860WBG opens SDA to wait for the start condition. In case the data is under accessed, transferred data is not executed. Clock count is initialized.

- Note 3: When the command is interrupted on the way, the command before interrupted is reflected. And the interrupted command is not executed. Please set the command again to reflect the command.

## 9. Detail description of functions

## 9.1 Register

The TB6860WBG can change the operation mode arbitrarily by changing the register by  $I^2C$  interface. The content of register is described in below table.

| Address | Command                                                    | Write/Read | Functions                                                                         |

|---------|------------------------------------------------------------|------------|-----------------------------------------------------------------------------------|

| 00h     | Operation set                                              | W/R        | Operation mode set                                                                |

| 01h     | Charge function set                                        | W/R        | Charge function set                                                               |

| 02h     | Charge voltage/current set                                 | W/R        | Threshold set between pre charge and fast charge voltage. Pre charge current set. |

| 03h     | Output voltage level set                                   | W/R        | Output voltage set                                                                |

| 04h     | Termination current set<br>/Charge current set             | W/R        | Termination current set, Fast charge current set                                  |

| 05h     | Input over current limit/<br>Current sense output mode set | W/R        | Input over current limit set, output mode of ISENS terminal set                   |

| 06h     | Charge information read                                    | R          | Charge mode information read, status of error read                                |

| 07h     | Test mode 1                                                | W/R        | Toshiba test mode. Do not access.                                                 |

| 10h     | Test mode 2                                                | R          | Toshiba test mode. Do not access.                                                 |

Table 9.1 Description of register

Connected host side (MCU) controls the register. Under managed by the host side, the TB6860WBG changes the operation mode.

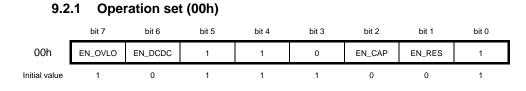

#### Table 9.2 Operation set: 00h

| Address |            | 7                     | 6                     | 5   | 4   | 3   | 2                                    | 1                                    | 0   |

|---------|------------|-----------------------|-----------------------|-----|-----|-----|--------------------------------------|--------------------------------------|-----|

|         | Bit Symbol | EN_OVLO               | EN_DCDC               | -   | -   | -   | EN_CAP                               | EN_RES                               | -   |

|         | Write/Read | W/R                   | W/R                   | W/R | W/R | W/R | W/R                                  | W/R                                  | W/R |

|         | Default    | 1                     | 0                     | 1   | 1   | 1   | 0                                    | 0                                    | 1   |

| 00h     |            | OVLO<br>Enable        | DCDC<br>Enable        | -   | -   | -   | Capacitive<br>Load Enable            | Resistance<br>Load Enable            | -   |

|         | Function   | 0:Disable<br>1:Enable | 0:Disable<br>1:Enable | 1   | 1   | 0   | 0:Terminal<br>(SW_C)<br>1:FET enable | 0:Terminal<br>(SW_R)<br>1:FET enable | 1   |

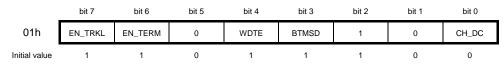

#### Table 9.3 Charge function set: 01h

| Address |            | 7                           | 6                          | 5   | 4                             | 3                              | 2   | 1   | 0                            |

|---------|------------|-----------------------------|----------------------------|-----|-------------------------------|--------------------------------|-----|-----|------------------------------|

|         | Bit Symbol | EN_TRKL                     | EN_TERM                    | -   | WDTE                          | BTMSD                          | -   | -   | CH_DC                        |

| 01h     | Write/Read | W/R                         | W/R                        | W/R | W/R                           | W/R                            | W/R | W/R | W/R                          |

|         | Default    | 1                           | 1                          | 0   | 1                             | 1                              | 1   | 0   | 0                            |

|         | Function   | Trickle<br>Charge<br>Enable | End Charge<br>Cycle Enable | -   | Watch-<br>Dog Timer<br>Enable | Battery<br>Missing<br>Detector | -   | -   | Charge/<br>Feed Mode Set     |

|         |            | 0:Disable<br>1:Enable       | 0:Disable<br>1:Enable      | 0   |                               | 0:Disbale<br>1:Enable          | 1   | 0   | 0:Charge Mode<br>1:Feed Mode |

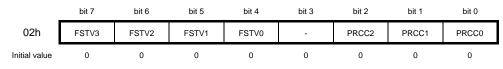

| Address |            | 7           | 6                        | 5                        | 4           | 3   | 2          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0           |  |  |

|---------|------------|-------------|--------------------------|--------------------------|-------------|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

|         | Bit Symbol | FSTV3       | FSTV2                    | FSTV1                    | FSTV0       | -   | PRCC2      | PRCC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PRCC0       |  |  |

|         | Write/Read | W/R         | W/R                      | W/R                      | W/R         | W/R | W/R        | W/R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W/R         |  |  |

|         | Default    | 0           | 0                        | 0                        | 0           | 0   | 0          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0           |  |  |

| 02h     |            | Threshold S | Set between Pi<br>change | re-charge and<br>voltage | Fast-charge | -   | Pre        | -charge Curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Current Set |  |  |

| 02      | Function   | 0h: 2.1V    | 4h: 2.5V                 | 8h: 2.9V                 | Ch: 3.3V    |     | 000: 50m/  | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100: 250mA  |  |  |

|         | Function   | 1h: 2.2V    | 5h: 2.6V                 | 9h: 3.0V                 | Dh: 3.4V    | 0   | 001: 100mA | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101: 300mA  |  |  |

|         |            | 2h: 2.3V    | 6h: 2.7V                 | Ah: 3.1V                 | Eh: 3.5V    | 0   | 010: 150mA | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110: 350mA  |  |  |

|         |            | 3h: 2.4V    | 7h: 2.8V                 | Bh: 3.2V                 | Fh: 3.6V    |     | 011: 200mA | N Contraction of the second se | 111: 400mA  |  |  |

### Table 9.4 Charge voltage/current set: 02h

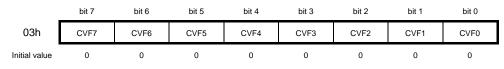

#### Table 9.5 Output voltage level set: 03h

| Address |            | 7                                      | 6                          | 5     | 4              | 3      | 2                                   | 1    | 0    |  |  |

|---------|------------|----------------------------------------|----------------------------|-------|----------------|--------|-------------------------------------|------|------|--|--|

| Address | Bit Symbol | CVF7                                   | CVF6                       | CVF5  | CVF4           | CVF3   | CVF2                                | CVF1 | CVF0 |  |  |

|         | Write/Read | W/R                                    | W/R                        | W/R   | W/R            | W/R    | W/R                                 | W/R  | W/R  |  |  |

|         | Default    | 0                                      | 0                          | 0     | 0              | 0      | 0                                   | 0    | 0    |  |  |

| 03h     |            |                                        | CV Mode Output Voltage Set |       |                |        |                                     |      |      |  |  |

|         | Function   | 00h:3.000V<br>01h:3.010V<br>02h:3.020V |                            | Volta | ige Step = 10m | iV/bit | FDh:5.530<br>FEh:5.540<br>FFh:5.550 | V    |      |  |  |

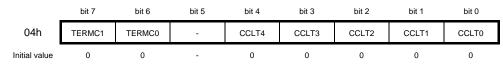

#### Table 9.6 Termination/charge current set: 04h

| Address |            | 7                       | 6                    | 5          | 4                                             | 3      | 2                                                                                         | 1     | 0                    |

|---------|------------|-------------------------|----------------------|------------|-----------------------------------------------|--------|-------------------------------------------------------------------------------------------|-------|----------------------|

| Address | Bit Symbol | TERMC1                  | TERMC0               | -          | CCLT4                                         | CCLT3  | CCLT2                                                                                     | CCLT1 | CCLT0                |

|         | Write/Read | W/R                     | W/R                  | -          | W/R                                           | W/R    | W/R                                                                                       | W/R   | W/R                  |

|         | Default    | 0                       | 0                    | -          | 0                                             | 0      | 0                                                                                         | 0     | 0                    |

|         |            | Termination Current Set |                      |            | Charge Current Limit Set                      |        |                                                                                           |       |                      |

| 04h     | Function   | 00: 50mA<br>01:100mA    | 10:150mA<br>11:200mA | Don't care | 00h:0mA<br>01h:50mA<br>02h:100mA<br>03h:150mA | Curren | 15h:1050mA<br>16h:1100mA<br>t step=50mA/bit 17h:1150mA<br>18h:1200mA<br>19h to 1Fh: Prohi |       | 00mA<br>50mA<br>00mA |

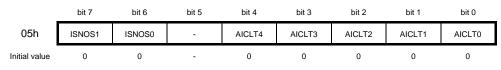

#### Table 9.7 Input over current limit/current sense output mode set: 05h

| Address |            | 7                                                                       | 6      | 5          | 4                                              | 3       | 2                                                                                            | 1      | 0                    |

|---------|------------|-------------------------------------------------------------------------|--------|------------|------------------------------------------------|---------|----------------------------------------------------------------------------------------------|--------|----------------------|

| Address | Bit Symbol | ISNOS1                                                                  | ISNOS0 | -          | AICLT4                                         | AICLT3  | AICLT2                                                                                       | AICLT1 | AICLT0               |

|         | Write/Read | W/R                                                                     | W/R    | -          | W/R                                            | W/R     | W/R                                                                                          | W/R    | W/R                  |

|         | Default    | 0                                                                       | 0      | -          | 0                                              | 0       | 0                                                                                            | 0      | 0                    |

|         |            | ISENS Output Select                                                     |        |            | Input Current Limit Set                        |         |                                                                                              |        |                      |

| 05h     | Function   | 00: DCDC con<br>current<br>01: VBAT×1/3<br>10: PVDD2×1/<br>11: Prohibit | ·      | Don't care | 00h:0mA<br>01h:100mA<br>02h:200mA<br>03h:300mA | Current | 15h:2100mA<br>16h:2200mA<br>urrent step=100mA/bit 17h:2300mA<br>18h:2400mA<br>19h to 1Fh: Pi |        | 00mA<br>00mA<br>00mA |

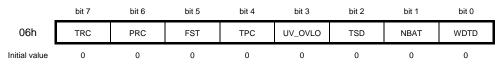

### Table 9.8 Charge information read: 06h

| Address |            | 7                             | 6                         | 5        | 4                           | 3                                | 2                      | 1                                                  | 0                                     |

|---------|------------|-------------------------------|---------------------------|----------|-----------------------------|----------------------------------|------------------------|----------------------------------------------------|---------------------------------------|

|         | Bit Symbol | TRC                           | PRC                       | FST      | TPC                         | UV_OVLO                          | TSD                    | NBAT                                               | WDTD                                  |

|         | Write/Read | R                             | R                         | R        | R                           | R                                | R                      | R                                                  | R                                     |

|         | Default    | 0                             | 0                         | 0        | 0                           | 0                                | 0                      | 0                                                  | 0                                     |

| 06h     |            |                               | Charge                    | e Status |                             | Voltage<br>Detect                | TSD Detect             | Battery<br>Connection<br>Error Detect              | Watch-dog<br>Timer Detect             |

|         |            | 0:Nop*<br>1:Trickle<br>Charge | 0:Nop*<br>1:Pre<br>Charge | 1:Fast   | 0:Nop*<br>1:Taper<br>Charge | 0:Nop*<br>1:UVLO/OVL<br>O Detect | 0:Nop*<br>1:TSD Detect | 0:Nop*<br>1: Battery<br>Connection<br>Error Detect | 0:Nop*<br>1:Watch-dog<br>Timer Detect |

\* Nop: Non-operation

#### Table 9.9 Test mode 1/2: 07h/10h

| Address  |            | 7 | 6                                 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|------------|---|-----------------------------------|---|---|---|---|---|---|

| Audless  | Bit Symbol |   | TEST Mode                         |   |   |   |   |   |   |

| 07h, 10h | Function   |   | Toshiba test mode (Do not access) |   |   |   |   |   |   |

### 9.2 Detail description of register

This register sets operation mode. It sets the on and off modes of each circuit.

$EN_OVLO (bit7) : ON/OFF$  setting of the over voltage lockout (OVLO) mode.

#### Table 9.10 EN\_OVLO set

| EN_OVLO | Function |                 |

|---------|----------|-----------------|

| 0       | Disable  |                 |

| 1       | Enable   | (Initial value) |

$EN_DCDC$  (bit6) : ON/OFF setting of the step-down DCDC converter.

Table 9.11 EN\_DCDC set

| EN_DCDC | Function |                 |

|---------|----------|-----------------|

| 0       | Disable  | (Initial value) |

| 1       | Enable   |                 |

EN\_CAP (bit2) : Selecting input of capacitive load modulation operation.

#### Table 9.12 EN\_CAP set

| EN_CAP | Function        |                 |

|--------|-----------------|-----------------|

| 0      | SW_C terminal   | (Initial value) |

| 1      | Internal FET ON |                 |

EN\_RES (bit1) : Selecting input of resistance load modulation operation.

#### Table 9.13 EN\_RES set

| EN_RES | Function        |                 |

|--------|-----------------|-----------------|

| 0      | SW_R terminal   | (Initial value) |

| 1      | Internal FET ON |                 |

Note 1: Bit5, bit4, and bit0 must be fixed "1".

#### 9.2.2 Charge function set (01h)

This register sets conditions and on/off of charge function.

EN\_TRKL (bit7) : Setting ON/OFF of the trickle charge mode.

#### Table 9.14 EN\_TRKL set

| EN_TRKL | Function |                 |

|---------|----------|-----------------|

| 0       | Disable  |                 |

| 1       | Enable   | (Initial value) |

EN\_TREM (bit6) : Setting ON/OFF of the charge completion of the taper charge mode.

| Table | 9.15 | EN | TREM | set |

|-------|------|----|------|-----|

|       |      |    |      |     |

| EN_TREM | Function |

|---------|----------|

| 0       | Disable  |

| 1       | Enable   |

(Initial value)

WDTE (bit4) : Setting ON/OFF of the watch dog timer.

#### Table 9.16 WDTE set

| WDTE | Function |

|------|----------|

| 0    | Disable  |

| 1    | Enable   |

(Initial value)

BTMSD (bit3) : Setting ON/OFF of the battery connection error detection

#### Table 9.17 BTMSD set

| BTMSD | Function |

|-------|----------|

| 0     | Disable  |

| 1     | Enable   |

CH\_DC (bit0) : Switching the charge and feed modes.

#### Table 9.18 CH\_DC set

| CH_DC | Function    |  |

|-------|-------------|--|

| 0     | Charge mode |  |

| 1     | Feed mode   |  |

(Initial value)

(Initial value)

Note 1: Bit5 and bit1 must be fixed "0".

Note 2: Bit2 must be fixed "1".

(Initial value)

#### 9.2.3 Charge voltage/current set (02h)

This register sets the threshold voltage between the pre charge and the fast charge modes in charging and sets the current of the pre charge.

FSTV3-0(bit7-4) : Selecting the threshold voltage between the pre charge and the fast charge modes.

| FSTV3 | FSTV2 | FSTV1 | FSTV0 | Threshold voltage |

|-------|-------|-------|-------|-------------------|

| 0     | 0     | 0     | 0     | 2.1V              |

| 0     | 0     | 0     | 1     | 2.2V              |

| 0     | 0     | 1     | 0     | 2.3V              |

| 0     | 0     | 1     | 1     | 2.4V              |

| 0     | 1     | 0     | 0     | 2.5V              |

| 0     | 1     | 0     | 1     | 2.6V              |

| 0     | 1     | 1     | 0     | 2.7V              |

| 0     | 1     | 1     | 1     | 2.8V              |

| 1     | 0     | 0     | 0     | 2.9V              |

| 1     | 0     | 0     | 1     | 3.0V              |

| 1     | 0     | 1     | 0     | 3.1V              |

| 1     | 0     | 1     | 1     | 3.2V              |

| 1     | 1     | 0     | 0     | 3.3V              |

| 1     | 1     | 0     | 1     | 3.4V              |

| 1     | 1     | 1     | 0     | 3.5V              |

| 1     | 1     | 1     | 1     | 3.6V              |

#### Table 9.19 FSTV3-0 set

PRCC2-0(bit2-0) : Selecting the current of the pre charge.

#### Table 9.20 PRCC2-0 set

| PRCC2 | PRCC1 | PRCC0 | Pre charge current |                 |

|-------|-------|-------|--------------------|-----------------|

| 0     | 0     | 0     | 50mA               | (Initial value) |

| 0     | 0     | 1     | 100mA              |                 |

| 0     | 1     | 0     | 150mA              |                 |

| 0     | 1     | 1     | 200mA              |                 |

| 1     | 0     | 0     | 250mA              |                 |

| 1     | 0     | 1     | 300mA              |                 |

| 1     | 1     | 0     | 350mA              |                 |

| 1     | 1     | 1     | 400mA              |                 |

Note 1: Bit3 must be fixed "0".

### 9.2.4 Output voltage level set (03h)

This register sets output voltage of constant voltage (CV) mode. Output voltage can be changed with a step of 10mV.

CVF7-0(bit7-0) : Selecting output voltage in the CV mode.

| CVF7-0(bin) | Output voltage of CV mode |                 |

|-------------|---------------------------|-----------------|

| 0000000     | 3.000V                    | (Initial value) |

| 0000001     | 3.010V                    |                 |

| 00000010    | 3.020V                    |                 |

| 00000011    | 3.030V                    |                 |

| :           | :                         | -               |

| 01111110    | 4.260V                    |                 |

| 01111111    | 4.270V                    |                 |

| 1000000     | 4.280V                    |                 |

| 1000001     | 4.290V                    |                 |

| :           | :                         | -               |

| 11111100    | 5.520V                    |                 |

| 11111101    | 5.530V                    |                 |

| 11111110    | 5.540V                    |                 |

| 11111111    | 5.550V                    |                 |

| Table | 9.21 | <b>CVF7-0</b> | set |

|-------|------|---------------|-----|

| Iabio |      |               |     |

#### 9.2.5 Termination current/charge current set (04h)

This register sets the current of the termination and the fast charge.

TERMC1-0(bit7-6): Selecting the current of the termination.

#### Table 9.22 TERMC1-0 set

| TERMC1 | TERMC0 | Current of termination |                 |

|--------|--------|------------------------|-----------------|

| 0      | 0      | 50mA                   | (Initial value) |

| 0      | 1      | 100mA                  |                 |

| 1      | 0      | 150mA                  |                 |

| 1      | 1      | 200mA                  |                 |

CCLT4-0(bit4-0) : Selecting the current of the fast charge. The current can be changed with a step of 50mA.

| CCLT4 | CCLT3 | CCLT2 | CCLT1 | CCLT0 | Current of fast charge |                 |

|-------|-------|-------|-------|-------|------------------------|-----------------|

| 0     | 0     | 0     | 0     | 0     | 0mA                    | (Initial value) |

| 0     | 0     | 0     | 0     | 1     | 50mA                   |                 |

| 0     | 0     | 0     | 1     | 0     | 100mA                  |                 |

| 0     | 0     | 0     | 1     | 1     | 150mA                  |                 |

| :     | :     | :     | :     | :     | :                      |                 |

| 1     | 0     | 1     | 1     | 0     | 1,100mA                |                 |

| 1     | 0     | 1     | 1     | 1     | 1,150mA                |                 |

| 1     | 1     | 0     | 0     | 0     | 1,200mA                |                 |

| 1     | 1     | 0     | 0     | 1     | Forbidden to set       |                 |

| 1     | 1     | 0     | 1     | 0     | Forbidden to set       |                 |

| :     | :     | :     | :     | :     | :                      | -               |

| 1     | 1     | 1     | 1     | 0     | Forbidden to set       |                 |

| 1     | 1     | 1     | 1     | 1     | Forbidden to set       |                 |

#### Table 9.23 CCLT4-0 set

Note 1: Do not set CCLT4-0 from 0b11001 to 0b11111.

#### 9.2.6 Input over current limit set/ISENS output mode set (05h)

This register sets output mode of ISEN terminal and input over current limit.

ISNOS1-0(bit7-6): Selecting output mode of ISENS terminal.

#### Table 9.24 ISNOS1-0 set

| ISNOS1 | ISNOS0 | Output mode            |                 |

|--------|--------|------------------------|-----------------|

| 0      | 0      | Output Current voltage | (Initial value) |

| 0      | 1      | VBAT×1/3               |                 |

| 1      | 0      | PVDD2×1/8              |                 |

| 1      | 1      | Forbidden to set       |                 |

AICLT4-0(bit4-0) : Selecting the input over current limit.

Limit value can be changed with a step of 100mA.

This configured value is valid in the CC mode. Set it including an operation margin for the charge current.

| AICLT4 | AICLT3 | AICLT2 | AICLT1 | AICLT0 | Over current limit |                 |

|--------|--------|--------|--------|--------|--------------------|-----------------|

| 0      | 0      | 0      | 0      | 0      | 0mA                | (Initial value) |

| 0      | 0      | 0      | 0      | 1      | 100mA              |                 |

| 0      | 0      | 0      | 1      | 0      | 200mA              |                 |

| 0      | 0      | 0      | 1      | 1      | 300mA              |                 |

| :      | :      | :      | :      | :      | :                  |                 |

| 1      | 0      | 1      | 1      | 0      | 2,200mA            |                 |

| 1      | 0      | 1      | 1      | 1      | 2,300mA            |                 |

| 1      | 1      | 0      | 0      | 0      | 2,400mA            |                 |

| 1      | 1      | 0      | 0      | 1      | Forbidden to set   |                 |

| 1      | 1      | 0      | 1      | 0      | Forbidden to set   |                 |

| :      | :      | :      | :      | :      | :                  | _               |

| 1      | 1      | 1      | 1      | 0      | Forbidden to set   |                 |

| 1      | 1      | 1      | 1      | 1      | Forbidden to set   |                 |

#### Table 9.25 AICLT4-0 set

Note 1: Do not set AICLT4-0 from 0b11001 to 0b11111.

This register confirms the state in the chip. When the register data which is read is "1", it indicates active. This register is only for reading. Make sure that when data is written to this register, transferred command is invalid. State information of each bit is shown below. The Bit3-0 automatically are initialized when DCDC converter start to works (EN\_DCDC="1").

| Command<br>name | bit  | Description                                                   | Data=0        | Data=1    |

|-----------------|------|---------------------------------------------------------------|---------------|-----------|

| TRC             | bit7 | Read whether the state is in the trickle charge or not.       | Non active    | Active    |

| PRC             | bit6 | Read whether the state is in the pre charge or not.           | Non active    | Active    |

| FST             | Bit5 | Read whether the state is in the fast charge or not.          | Non active    | Active    |

| TPC             | bit4 | Read whether the state is in the taper charge or not.         | Non active    | Active    |

| UV_OVLO         | bit3 | Read detection result of over voltage/under voltage circuits. | Non detection | Detection |

| TSD             | bit2 | Read detection result of thermal shutdown circuit.            | Non detection | Detection |

| NBAT            | bit1 | Read detection result of battery connecting error.            | Non detection | Detection |

| WDTD            | bit0 | Read detection of watch-dog timer error.                      | Non detection | Detection |

#### Table 9.26 Charge information read

#### 9.2.8 Test mode (07h/10h) bit 6 bit 7 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 Initial value 07h Test mode 1(8bit) 00h 10h Test mode 2(8bit) 00h

This register is for Toshiba test mode. Do not access to 07h and 10h registers.

### 9.3 Detection and protection function

The TB6860WBG has two voltage detections and two protection functions.

#### 9.3.1 Under voltage lockout (UVLO) function

UVLO function avoids malfunction when the voltage of PVDD2 terminal is low. The detection condition is that the voltage of PVDD2 terminal drops below 3.2V (typ.). UVLO is deactivated when the voltage of PVDD2 terminal rises over 3.46V (typ.). UVLO turns off the step-down DCDC converter (EN\_DCDC="0") and outputs high signal for STAT which corresponds to wait mode. The error flag which indicates abnormal input voltage is configured UV\_OVLO="1". To re-start the step-down DCDC converter, the step-down DCDC converter should be set on (EN\_DCDC="1") again. The error flag keeps the flag until the step-down DCDC converter is set on (EN\_DCDC="1") or POR starts operation.

#### 9.3.2 Over voltage lockout (OVLO) function

OVLO function avoids malfunction when the voltage of PVDD2 terminal is high. OVLO is activated when EN\_OVLO="1". The detection condition is that the voltage of PVDD2 terminal rises over 17V (typ.).OVLO is deactivated when the voltage of PVDD2 terminal drops below 16V. OVLO turns off the step-down DCDC converter (EN\_DCDC="0") and outputs high signal for STAT which corresponds to wait mode. The error flag which indicates abnormal input voltage is configured UV\_OVLO="1". To re-start the step-down DCDC converter, the step-down DCDC converter should be set on (EN\_DCDC="1") again. The error flag keeps the flag until the step-down DCDC converter is set on (EN\_DCDC="1") or POR starts operation.

#### 9.3.3 Thermal shutdown protection (TSD) function

TSD function protects the IC from internal temperature rise. The detection condition is that the internal temperature rises over 150°C (typ.). TSD is deactivated when the internal temperature drops below 130°C (typ.). TSD turns off the step-down DCDC converter (EN\_DCDC="0") and outputs high signal for STAT which corresponds to wait mode. The error flag which indicates abnormal internal temperature is configured TSD="1". To re-start the step-down DCDC converter, the step-down DCDC converter should be set on (EN\_DCDC="1") again. The error flag keeps the flag until the step-down DCDC converter is set on (EN\_DCDC="1") or POR starts operation.

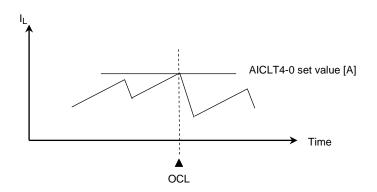

#### 9.3.4 Over current limit protection (OCL) function

OCL function protects the IC from overcurrent of the step-down DCDC converter. The detection condition is that the value of current which flows in MOSFET (high side) of the step-down DCDC converter reaches the specified value. Setting method of the detection current depends on the operation mode of the step-down DCDC converter. When the step-down DCDC converter drives in charge mode, OCL detection current can be set in the range from 0 mA to 2.4 A by the register of AICLT4-0. When it drives in feed mode, OCL detection current is fixed depending on each mode. When OCL detects over current, MOSFET (high side) of the step-down DCDC converter is turned off and MOSFET (low side) is turned on. OCL function operates every switching cycle. So, OCL is deactivated in the next switching cycle automatically and the normal operation is returned.

Figure 9.1 Description of OCL function

### 9.4 Battery missing detection

Battery missing detection avoids malfunction of charge caused by error of battery connection. It operates when the step-down DCDC converter drives in charge mode (CH\_DC="0"). BTMSD register sets ON and OFF of this detection. Trickle charge function is valid. And the battery missing detection starts monitoring when the voltage of AUXPWR terminal is 2.1V or less in charge start. Battery missing detection has two error detections. First detection is activated in charge start. The safety timer starts counting when charge starts. And it continues counting during trickle charge mode and judges it battery missing after a lapse of 36 minutes. Second detection is activated in transition from trickle charge mode to pre charge mode. The safety timer re-starts counting when the voltage of AUXPWR terminal rises over 3.6V within 87ms after the operation moves to taper charge mode. When battery missing is detected, the step-down DCDC converter is set off (EN\_DCDC="0") and outputs high level for STAT which corresponds to wait mode. The error flag which indicates battery missing is configured NBAT="1". Description of operation is shown in Figure 9.2. To re-start the step-down DCDC converter, the step-down DCDC converter is set on (EN\_DCDC="1") again. The error flag keeps the flag until the step-down DCDC converter is set on (EN\_DCDC="1") or POR starts operating.

#### 9.5 Watch-dog timer

The TB6860WBG includes watch-dog timer. It is configured on and off by WDTE register. It operates when the step-down DCDC converter is set on ( $EN_DCDC="1"$ ). Its monitoring time is 42s. And it is reset by ACK signal of I<sup>2</sup>C interface. When watch-dog timer is time out, the step-down DCDC converter is set off ( $EN_DCDC="0"$ ) and outputs high signal for STAT which corresponds to wait mode. The error flag which indicates watch-dog time out is set WDTD="1". The step-down DCDC converter should be set on ( $EN_DCDC="1"$ ) again to re-start the operation of the step-down DCDC converter. The error flag keeps the flag until the step-down DCDC converter is set on ( $EN_DCDC="1"$ ) or POR start operating.

Figure 9.2 Description of battery missing detection