## LT1711/LT1712

## FEATURES

- Ultrafast: 4.5ns at 20mV Overdrive 5.5ns at 5mV Overdrive

- Rail-to-Rail Inputs

- Rail-to-Rail Complementary Outputs (TTL/CMOS Compatible)

- Specified at 2.7V, 5V and ±5V Supplies

- Output Latch

- Inputs Can Exceed Supplies Without Phase Reversal

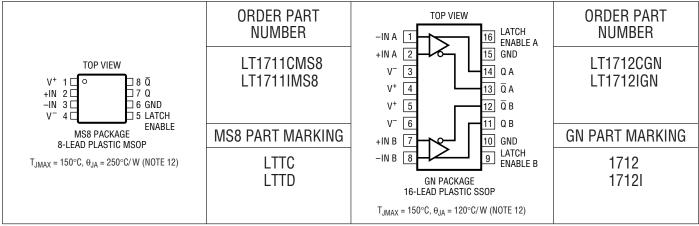

- LT1711: 8-Lead MSOP Package

- LT1712: 16-Lead Narrow SSOP Package

### **APPLICATIONS**

- High Speed Automatic Test Equipment

- Current Sense for Switching Regulators

- Crystal Oscillator Circuits

- High Speed Sampling Circuits

- High Speed A/D Converters

- Pulse Width Modulators

- Window Comparators

- Extended Range V/F Converters

- Fast Pulse Height/Width Discriminators

- Line Receivers

- High Speed Triggers

### Single/Dual 4.5ns, 3V/5V/±5V, Rail-to-Rail Comparators

### DESCRIPTION

The LT<sup>®</sup>1711/LT1712 are UltraFast<sup>TM</sup> 4.5ns comparators featuring rail-to-rail inputs, rail-to-rail complementary outputs and an output latch. Optimized for 3V and 5V power supplies, they operate over a single supply voltage range from 2.4V to 12V or from  $\pm 2.4V$  to  $\pm 6V$  dual supplies.

The LT1711/LT1712 are designed for ease of use in a variety of systems. In addition to wide supply voltage flexibility, rail-to-rail input common mode range extends 100mV beyond both supply rails, and the outputs are protected against phase reversal for inputs extending further beyond the rails. Also, the rail-to-rail inputs may be taken to opposite rails with no significant increase in input current. The rail-to-rail matched complementary outputs interface directly to TTL or CMOS logic and can sink 10mA to within 0.5V of GND or source 10mA to within 0.7V of V<sup>+</sup>.

The LT1711/LT1712 have internal TTL/CMOS compatible latches for retaining data at the outputs. Each latch holds data as long as the latch pin is held high. Latch pin hysteresis provides protection against slow moving or noisy latch signals. The LT1711 is available in the 8-pin MSOP package. The LT1712 is available in the 16-pin narrow SSOP package.

T, LTC and LT are registered trademarks of Linear Technology Corporation. UltraFast is a trademark of Linear Technology Corporation.

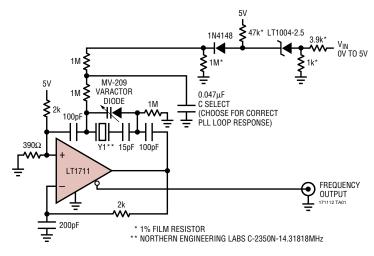

### TYPICAL APPLICATION

A 4× NTSC Subcarrier Voltage-Tunable Crystal Oscillator

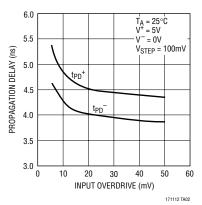

#### LT1711/LT1712 Propagation Delay vs Input Overdrive

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| V+ to V <sup>-</sup>       | 12.6V       |

|----------------------------|-------------|

| V <sup>+</sup> to GND      | 12.6V       |

| $V^-$ to GND               | 10V to 0.3V |

| Differential Input Voltage | ±12.6V      |

| Latch Pin Voltage          | 7V          |

| Input and Latch Current    | ±10mA       |

| Output Current (Continuous)              | ±20mA   |

|------------------------------------------|---------|

| Operating Temperature Range40°C          | to 85°C |

| Specified Temperature Range (Note 2)40°C | to 85°C |

| Junction Temperature                     | . 150°C |

| Storage Temperature Range65°C to         | ა 150°C |

| Lead Temperature (Soldering, 10 sec)     | 300°C   |

### PACKAGE/ORDER INFORMATION

Consult factory for parts specified with wider operating temperature ranges.

## **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 2.7V or V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, V<sub>CM</sub> = V<sup>+</sup>/2, V<sub>LATCH</sub> = 0.8V, C<sub>LOAD</sub> = 10pF, V<sub>OVERDRIVE</sub> = 20mV, unless otherwise specified.

| SYMBOL                     | PARAMETER                             | CONDITIONS                                                                                                                                                                                                                                                     |   | MIN                  | ТҮР             | MAX                  | UNITS                |

|----------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|-----------------|----------------------|----------------------|

| V+                         | Positive Supply Voltage Range         |                                                                                                                                                                                                                                                                | • | 2.4                  |                 | 7                    | V                    |

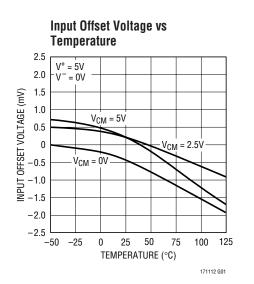

| V <sub>0S</sub>            | Input Offset Voltage (Note 4)         | $ \begin{array}{l} {\sf R}_{S} = 50\Omega,  {\sf V}_{CM} = {\sf V}^{+}\!/2 \\ {\sf R}_{S} = 50\Omega,  {\sf V}_{CM} = {\sf V}^{+}\!/2 \\ {\sf R}_{S} = 50\Omega,  {\sf V}_{CM} = 0{\sf V} \\ {\sf R}_{S} = 50\Omega,  {\sf V}_{CM} = {\sf V}^{+} \end{array} $ | • |                      | 0.5<br>0.7<br>1 | 5.0<br>6.0           | mV<br>mV<br>mV<br>mV |

| $\Delta V_{0S} / \Delta T$ | Input Offset Voltage Drift            |                                                                                                                                                                                                                                                                | • |                      | 10              |                      | μV/°C                |

| I <sub>OS</sub>            | Input Offset Current                  |                                                                                                                                                                                                                                                                | • |                      | 0.2             | 3<br>6               | μA<br>μA             |

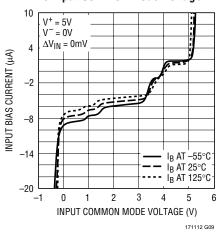

| I <sub>B</sub>             | Input Bias Current (Note 5)           |                                                                                                                                                                                                                                                                | • | -18<br>-35           | -5              | 5<br>10              | μΑ<br>μΑ             |

| V <sub>CM</sub>            | Input Voltage Range (Note 9)          |                                                                                                                                                                                                                                                                | • | -0.1                 |                 | V <sup>+</sup> + 0.1 | V                    |

| CMRR                       | Common Mode Rejection Ratio           | $\begin{array}{l} V^{+} = 5V,  0V \leq V_{CM} \leq 5V \\ V^{+} = 5V,  0V \leq V_{CM} \leq 5V \\ V^{+} = 2.7V,  0V \leq V_{CM} \leq 2.7V \\ V^{+} = 2.7V,  0V \leq V_{CM} \leq 2.7V \end{array}$                                                                | • | 56<br>53<br>54<br>50 | 65<br>65        |                      | dB<br>dB<br>dB<br>dB |

| PSRR+                      | Positive Power Supply Rejection Ratio | $2.4V \le V^+ \le 7V, V_{CM} = 0V$                                                                                                                                                                                                                             | • | 58<br>56             | 75              |                      | dB<br>dB             |

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 2.7V or V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, V<sub>CM</sub> = V<sup>+</sup>/2, V<sub>LATCH</sub> = 0.8V, C<sub>LOAD</sub> = 10pF, V<sub>OVERDRIVE</sub> = 20mV, unless otherwise specified.

| SYMBOL              | PARAMETER                                  | CONDITIONS                                                                                                         |   | MIN                                        | ТҮР                                        | MAX        | UNITS             |

|---------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------|--------------------------------------------|------------|-------------------|

| PSRR-               | Negative Power Supply Rejection Ratio      | $-7V \le V^- \le 0V, V^+ = 5V, V_{CM} = 5V$                                                                        | • | 60<br>58                                   | 80                                         |            | dB<br>dB          |

| A <sub>V</sub>      | Small-Signal Voltage Gain (Note 10)        |                                                                                                                    |   | 1                                          | 15                                         |            | V/mV              |

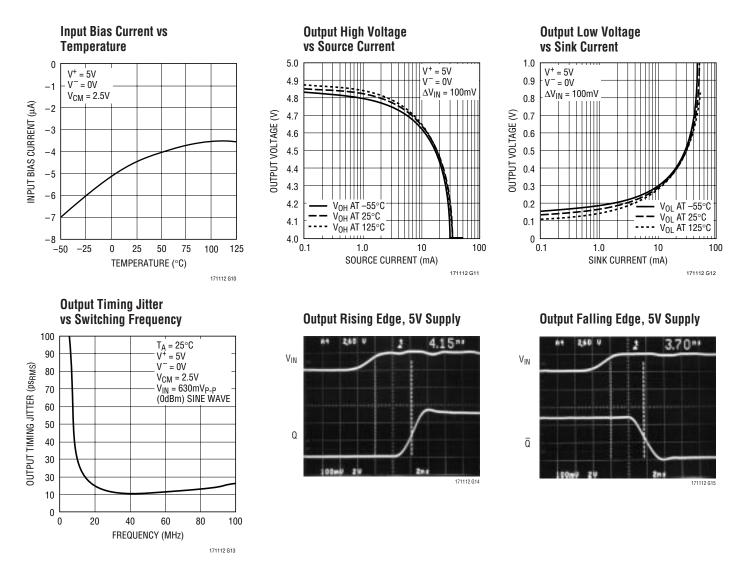

| V <sub>OH</sub>     | Output Voltage Swing HIGH                  | I <sub>OUT</sub> = 1mA, V <sub>OVERDRIVE</sub> = 50mV<br>I <sub>OUT</sub> = 10mA, V <sub>OVERDRIVE</sub> = 50mV    | • | V <sup>+</sup> -0.5<br>V <sup>+</sup> -0.7 | V <sup>+</sup> -0.2<br>V <sup>+</sup> -0.4 |            | V<br>V            |

| V <sub>OL</sub>     | Output Voltage Swing LOW                   | I <sub>OUT</sub> = – 1mA, V <sub>OVERDRIVE</sub> = 50mV<br>I <sub>OUT</sub> = –10mA, V <sub>OVERDRIVE</sub> = 50mV | • |                                            | 0.20<br>0.35                               | 0.4<br>0.5 | V<br>V            |

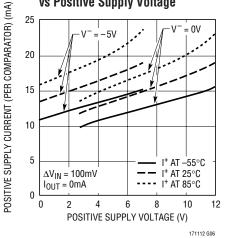

| +                   | Positive Supply Current (Per Comparator)   | V <sup>+</sup> = 5V, V <sub>OVERDRIVE</sub> = 1V                                                                   | • |                                            | 15                                         | 19<br>26   | mA<br>mA          |

| -                   | Negative Supply Current (Per Comparator)   | V <sup>+</sup> = 5V, V <sub>OVERDRIVE</sub> = 1V                                                                   | • |                                            | 8                                          | 10<br>13   | mA<br>mA          |

| V <sub>IH</sub>     | Latch Pin High Input Voltage               |                                                                                                                    |   | 2.4                                        |                                            |            | V                 |

| V <sub>IL</sub>     | Latch Pin Low Input Voltage                |                                                                                                                    |   |                                            |                                            | 0.8        | V                 |

| IIL                 | Latch Pin Current                          | $V_{LATCH} = V^+$                                                                                                  |   |                                            |                                            | 15         | μA                |

| t <sub>PD</sub>     | Propagation Delay (Note 6)                 |                                                                                                                    | • |                                            | 4.5<br>5.5                                 | 6.0<br>8.5 | ns<br>ns<br>ns    |

| $\Delta t_{PD}$     | Differential Propagation Delay (Note 6)    | $\Delta V_{IN} = 100 \text{mV}, V_{OVERDRIVE} = 20 \text{mV}$                                                      |   |                                            | 0.5                                        | 1.5        | ns                |

| t <sub>r</sub>      | Output Rise Time                           | 10% to 90%                                                                                                         |   |                                            | 2                                          |            | ns                |

| t <sub>f</sub>      | Output Fall Time                           | 90% to 10%                                                                                                         |   |                                            | 2                                          |            | ns                |

| t <sub>LPD</sub>    | Latch Propagation Delay (Note 7)           |                                                                                                                    |   |                                            | 5                                          |            | ns                |

| t <sub>SU</sub>     | Latch Setup Time (Note 7)                  |                                                                                                                    |   |                                            | 1                                          |            | ns                |

| t <sub>H</sub>      | Latch Hold Time (Note 7)                   |                                                                                                                    |   |                                            | 0                                          |            | ns                |

| t <sub>DPW</sub>    | Minimum Latch Disable Pulse Width (Note 7) |                                                                                                                    |   |                                            | 5                                          |            | ns                |

| f <sub>MAX</sub>    | Maximum Toggle Frequency                   | V <sub>IN</sub> = 100mV <sub>P-P</sub> Sine Wave                                                                   |   |                                            | 100                                        |            | MHz               |

| t <sub>JITTER</sub> | Output Timing Jitter                       | $V_{IN} = 630 m V_{P-P}$ (0dBm) Sine Wave, f = 30MHz                                                               |   |                                            | 11                                         |            | ps <sub>RMS</sub> |

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 5V, V<sup>-</sup> = -5V, V<sub>CM</sub> = 0V, V<sub>LATCH</sub> = 0.8V, C<sub>LOAD</sub> = 10pF, V<sub>OVERDRIVE</sub> = 20mV, unless otherwise specified.

| SYMBOL                   | PARAMETER                              | CONDITIONS                                                                                                                                                       |   | MIN        | ТҮР             | MAX        | UNITS                |

|--------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-----------------|------------|----------------------|

| V+                       | Positive Supply Voltage Range          |                                                                                                                                                                  | • | 2.4        |                 | 7          | V                    |

| V-                       | Negative Supply Voltage Range (Note 3) |                                                                                                                                                                  | • | -7         |                 | 0          | V                    |

| V <sub>0S</sub>          | Input Offset Voltage (Note 4)          | $\begin{array}{l} {R_S = 50\Omega ,V_{CM} = 0V} \\ {R_S = 50\Omega ,V_{CM} = 0V} \\ {R_S = 50\Omega ,V_{CM} = 5V} \\ {R_S = 50\Omega ,V_{CM} = -5V} \end{array}$ | • |            | 0.5<br>0.7<br>1 | 5.0<br>6.0 | mV<br>mV<br>mV<br>mV |

| $\Delta V_{0S}/\Delta T$ | Input Offset Voltage Drift             |                                                                                                                                                                  |   |            | 10              |            | μV/°C                |

| I <sub>OS</sub>          | Input Offset Current                   |                                                                                                                                                                  | • |            | 0.2             | 3<br>6     | μA<br>μA             |

| IB                       | Input Bias Current (Note 5)            |                                                                                                                                                                  | • | -18<br>-35 | -5              | 5<br>10    | μΑ<br>μΑ             |

| V <sub>CM</sub>          | Input Voltage Range                    |                                                                                                                                                                  | • | -5.1       |                 | 5.1        | V                    |

| CMRR                     | Common Mode Rejection Ratio            | $-5V \le V_{CM} \le 5V$                                                                                                                                          | • | 61<br>58   | 75              |            | dB<br>dB             |

| PSRR+                    | Positive Power Supply Rejection Ratio  | $2.4V \le V^+ \le 7V, V_{CM} = -5V$                                                                                                                              | • | 58<br>56   | 85              |            | dB<br>dB             |

| PSRR-                    | Negative Power Supply Rejection Ratio  | $-7V \le V^- \le 0V, V_{CM} = 5V$                                                                                                                                | • | 60<br>58   | 80              |            | dB<br>dB             |

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 5V, V<sup>-</sup> = -5V, V<sub>CM</sub> = 0V, V<sub>LATCH</sub> = 0.8V, C<sub>LOAD</sub> = 10pF, V<sub>OVERDRIVE</sub> = 20mV, unless otherwise specified.

| SYMBOL              | PARAMETER                                    | CONDITIONS                                                                                                      |   | MIN        | ТҮР          | MAX        | UNITS             |

|---------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|------------|--------------|------------|-------------------|

| A <sub>V</sub>      | Small-Signal Voltage Gain                    |                                                                                                                 |   | 1          | 15           |            | V/mV              |

| V <sub>OH</sub>     | Output Voltage Swing HIGH (Note 8)           | I <sub>OUT</sub> = 1mA, V <sub>OVERDRIVE</sub> = 50mV<br>I <sub>OUT</sub> = 10mA, V <sub>OVERDRIVE</sub> = 50mV | • | 4.5<br>4.3 | 4.8<br>4.6   |            | V<br>V            |

| V <sub>OL</sub>     | Output Voltage Swing LOW (Note 8)            | $I_{OUT} = -1mA$ , $V_{OVERDRIVE} = 50mV$<br>$I_{OUT} = -10mA$ , $V_{OVERDRIVE} = 50mV$                         | • |            | 0.20<br>0.30 | 0.4<br>0.5 | V<br>V            |

| +                   | Positive Supply Current (Per Comparator)     | V <sub>OVERDRIVE</sub> = 1V                                                                                     | • |            | 17           | 22<br>30   | mA<br>mA          |

| I-                  | Negative Supply Current (Per Comparator)     | V <sub>OVERDRIVE</sub> = 1V                                                                                     | • |            | 9            | 12<br>15   | mA<br>mA          |

| V <sub>IH</sub>     | Latch Pin High Input Voltage                 |                                                                                                                 |   | 2.4        |              |            | V                 |

| V <sub>IL</sub>     | Latch Pin Low Input Voltage                  |                                                                                                                 |   |            |              | 0.8        | V                 |

| IIL                 | Latch Pin Current                            | $V_{LATCH} = V^+$                                                                                               |   |            |              | 15         | μA                |

| t <sub>PD</sub>     | Propagation Delay (Notes 6, 11)              |                                                                                                                 | • |            | 4.5<br>5.5   | 6.0<br>8.5 | ns<br>ns<br>ns    |

| $\Delta t_{PD}$     | Differential Propagation Delay (Notes 6, 11) | $\Delta V_{IN} = 100 \text{mV}, V_{OVERDRIVE} = 20 \text{mV}$                                                   |   |            | 0.5          | 1.5        | ns                |

| t <sub>r</sub>      | Output Rise Time                             | 10% to 90%                                                                                                      |   |            | 2            |            | ns                |

| t <sub>f</sub>      | Output Fall Time                             | 90% to 10%                                                                                                      |   |            | 2            |            | ns                |

| t <sub>LPD</sub>    | Latch Propagation Delay (Note 7)             |                                                                                                                 |   |            | 5            |            | ns                |

| t <sub>SU</sub>     | Latch Setup Time (Note 7)                    |                                                                                                                 |   |            | 1            |            | ns                |

| t <sub>H</sub>      | Latch Hold Time (Note 7)                     |                                                                                                                 |   |            | 0            |            | ns                |

| t <sub>DPW</sub>    | Minimum Latch Disable Pulse Width (Note 7)   |                                                                                                                 |   |            | 5            |            | ns                |

| f <sub>MAX</sub>    | Maximum Toggle Frequency                     | $V_{IN} = 100 m V_{P-P}$ Sine Wave                                                                              |   |            | 100          |            | MHz               |

| t <sub>JITTER</sub> | Output Timing Jitter                         | $V_{IN} = 630mV_{P-P}$ (0dBm) Sine Wave, f = 30MHz                                                              |   |            | 11           |            | ps <sub>RMS</sub> |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LT1711C/LT1712C are guaranteed to meet specified performance from 0°C to 70°C. They are designed, characterized and expected to meet specified performance from -40°C to 85°C but are not tested or QA sampled at these temperatures. The LT1711I/LT1712I are guaranteed to meet specified performance from -40°C to 85°C.

**Note 3:** The negative supply should not be greater than the ground pin voltage and the maximum voltage across the positive and negative supplies should not be greater than 12V.

**Note 4:** Input offset voltage ( $V_{OS}$ ) is measured with the LT1711/LT1712 in a configuration that adds external hysteresis. It is defined as the average of the two hysteresis trip points.

Note 5: Input bias current  $\left(I_{B}\right)$  is defined as the average of the two input currents.

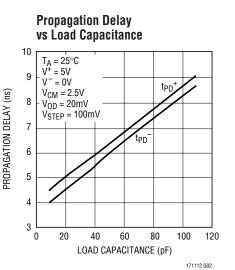

**Note 6:** Propagation delay  $(t_{PD})$  is measured with the overdrive added to the actual V<sub>OS</sub>. Differential propagation delay is defined as:

$\Delta t_{PD}$  =  $t_{PD}^+ - t_{PD}^-$ . Load capacitance is 10pF. Due to test system requirements, the LT1711/LT1712 propagation delay is specified with a 1k $\Omega$  load to ground for  $\pm 5V$  supplies, or to mid-supply for 2.7V or 5V single supplies.

**Note 7:** Latch propagation delay  $(t_{LPD})$  is the delay time for the output to respond when the latch pin is deasserted. Latch setup time  $(t_{SU})$  is the

interval in which the input signal must remain stable prior to asserting the latch signal. Latch hold time (t<sub>H</sub>) is the interval after the latch is asserted in which the input signal must remain stable. Latch disable pulse width (t<sub>DPW</sub>) is the width of the negative pulse on the latch enable pin that latches in new data on the data inputs.

**Note 8:** Output voltage swings are characterized and tested at  $V^+ = 5V$  and  $V^- = 0V$ . They are guaranteed by design and correlation to meet these specifications at  $V^- = -5V$ .

**Note 9:** The input voltage range is tested under the more demanding conditions of V<sup>+</sup> = 5V and V<sup>-</sup> = -5V. The LT1711/LT1712 are guaranteed by design and correlation to meet these specifications at V<sup>-</sup> = 0V.

**Note 10:** The LT1711/LT1712 voltage gain is tested at V<sup>+</sup> = 5V and V<sup>-</sup> = -5V only. Voltage gain at single supply V<sup>+</sup> = 5V and V<sup>+</sup> = 2.7V is guaranteed by design and correlation.

**Note 11:** The LT1711/LT1712  $t_{PD}$  is tested at V<sup>+</sup> = 5V and 2.7V with V<sup>-</sup> = 0V. Propagation delay at V<sup>+</sup> = 5V, V<sup>-</sup> = -5V is guaranteed by design and correlation.

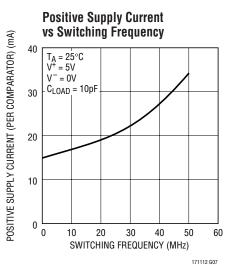

**Note 12:** Care must be taken to make sure that the LT1711/LT1712 do not exceed  $T_{JMAX}$  when operating with  $\pm 5V$  supplies over the industrial temperature range.  $T_{JMAX}$  is not exceeded for DC inputs, but supply current increases with switching frequency (see Typical Performance Characteristics).

### TYPICAL PERFORMANCE CHARACTERISTICS

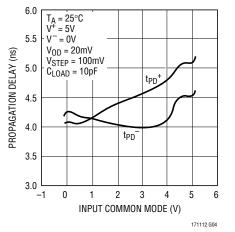

Propagation Delay vs Input Common Mode Voltage

**Propagation Delay**

T<sub>A</sub> = 25°C V<sup>-</sup> = 0V

$V_{CM} = 2.5V$

$V_{0D} = 20mV$  $V_{STEP} = 100mV$

$C_{LOAD} = 10 pF$

2

4

**Negative Supply Current**

vs Negative Supply Voltage

POSITIVE SUPPLY VOLTAGE (V)

6.0

5.5

5.0

4.5

4.0

3.5

3.0

14

12

10

8

6

4

2

0

0

-1

-2 -3 -4 -5 -6 -7

$V^{+}=5V$

$\Delta V_{IN} = 100 \text{mV}$

$I_{OUT} = 0mA$

0

PROPAGATION DELAY (ns)

VEGATIVE SUPPLY CURRENT (PER COMPARATOR) (mA)

vs Positive Supply Voltage

t<sub>PD</sub>

t<sub>PD</sub>

6

8

10

171112 G05

AT -55°C

AT 25°C

AT 85°C

171112 G08

L

- -

NEGATIVE SUPPLY VOLTAGE (V)

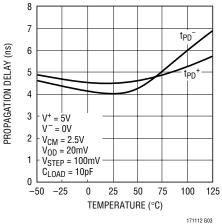

Propagation Delay vs Temperature

Positive Supply Current vs Positive Supply Voltage

Input Bias Current vs Input Common Mode Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

### LT1711

V<sup>+</sup> (Pins 1): Positive Supply Voltage, Usually 5V.

+IN (Pin 2): Noninverting Input.

-IN (Pin 3): Inverting Input.

V<sup>-</sup> (Pins 4): Negative Supply Voltage, Usually 0V or - 5V.

**LATCH ENABLE (Pin 5):** Latch Enable Input. With a logic high, the output is latched.

**GND (Pin 6):** Ground Supply Voltage, Usually OV. **Q (Pin 7):** Noninverting Output.  $\overline{\mathbf{Q}}$  (**Pin 8):** Inverting Output.

### PIN FUNCTIONS

#### LT1712

-IN A (Pin 1): Inverting Input of A Channel Comparator.

**+IN A (Pin 2):** Noninverting Input of A Channel Comparator.

**V**<sup>-</sup>(**Pins 3, 6**): Negative Supply Voltage, Usually – 5V. Pins 3 and 6 should be connected together externally.

**V**<sup>+</sup> (**Pins 4, 5**): Positive Supply Voltage, Usually 5V. Pins 4 and 5 should be connected together externally.

**+IN B (Pin 7):** Noninverting Input of B Channel Comparator.

-IN B (Pin 8): Inverting Input of B Channel Comparator.

**LATCH ENABLE B (Pin 9):** Latch Enable Input of B Channel Comparator. With a logic high, the B output is latched.

**GND (Pin 10):** Ground Supply Voltage of B Channel Comparator, Usually OV.

**Q B (Pin 11):** Noninverting Output of B Channel Comparator.

**Q B** (**Pin 12**): Inverting Output of B Channel Comparator.

**Q** A (Pin 13): Inverting Output of A Channel Comparator.

**Q A (Pin 14):** Noninverting Output of A Channel Comparator.

**GND (Pin 15):** Ground Supply Voltage of A Channel Comparator, Usually OV

**LATCH ENABLE A (Pin 16):** Latch Enable Input of A Channel Comparator. With a logic high, the A output is latched.

### **APPLICATIONS INFORMATION**

#### **Common Mode Considerations**

The LT1711/LT1712 are specified for a common mode range of -5.1V to 5.1V on a  $\pm 5V$  supply, or a common mode range of -0.1V to 5.1V on a single 5V supply. A more general consideration is that the common mode range is from 100mV below the negative supply to 100mV above the positive supply, independent of the actual supply voltage. The criteria for common mode limit is that the output still responds correctly to a small differential input signal.

When either input signal falls outside the common mode limit, the internal PN diode formed with the substrate can turn on resulting in significant current flow through the die. Schottky clamp diodes between the inputs and the supply rails speed up recovery from excessive overdrive conditions by preventing these substrate diodes from turning on.

#### Input Bias Current

Input bias current is measured with the outputs held at 2.5V with a 5V supply voltage. As with any rail-to-rail

differential input stage, the LT1711/LT1712 bias current flows into or out of the device depending upon the common mode level. The input circuit consists of an NPN pair and a PNP pair. For inputs near the negative rail, the NPN pair is inactive, and the input bias current flows out of the device; for inputs near the positive rail, the PNP pair is inactive, and these currents flow into the device. For inputs far enough away from the supply rails, the input bias current will be some combination of the NPN and PNP bias currents. As the differential input voltage increases, the input current of each pair will increase for one of the inputs and decrease for the other input. Large differential input voltages result in different input currents as the input stage enters various regions of operation. To reduce the influence of these changing input currents on system operation, use a low source resistance.

#### Latch Pin Dynamics

The internal latches of the LT1711/LT1712 comparators retain the input data (output latched) when their respective latch pin goes high. The latch pin will float to a low state when disconnected, but it is better to ground the

### APPLICATIONS INFORMATION

latch when a flow-through condition is desired. The latch pin is designed to be driven with either a TTL or CMOS output. It has built-in hysteresis of approximately 100mV, so that slow moving or noisy input signals do not impact latch performance.

For the LT1712, if only one of the comparators is being used at a given time, it is best to latch the second comparator to avoid any possibility of interactions between the two comparators in the same package.

#### High Speed Design Techniques

The extremely fast speed of the LT1711/LT1712 necessitates careful attention to proper PC board layout and circuit design in order to prevent oscillations, as with most high speed comparators. The most common problem involves power supply bypassing which is necessary to maintain low supply impedance. Resistance and inductance in supply wires and PC traces can quickly build up to unacceptable levels, thereby allowing the supply voltages to move as the supply current changes. This movement of the supply voltages will often result in improper operation. In addition, adjacent devices connected through an unbypassed supply can interact with each other through the finite supply impedances.

Bypass capacitors furnish a simple solution to this problem by providing a local reservoir of energy at the device, thus keeping supply impedance low. Bypass capacitors should be as close as possible to the LT1711/LT1712 supply pins. A good high frequency capacitor, such as a 1000pF ceramic, is recommended in parallel with larger capacitors, such as a  $0.1\mu$ F ceramic and a  $4.7\mu$ F tantalum in parallel. These bypass capacitors should be soldered to the output ground plane such that the return currents do not pass through the ground plane under the input circuitry. The common tie point for these two ground planes should be at the board ground connection. Such stargrounding and ground plane separation is extremely important for the proper operation of ultra high speed circuits.

Poor trace routes and high source impedances are also common sources of problems. Keep trace lengths as short as possible and avoid running any output trace adjacent to an input trace to prevent unnecessary coupling. If output traces are longer than a few inches, provide proper termination impedances (typically  $100\Omega$  to  $400\Omega$ ) to eliminate any reflections that may occur. Also keep source impedances as low as possible, preferably much less than  $1k\Omega$ .

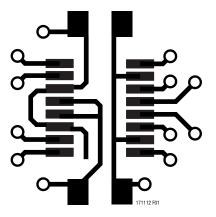

The input and output traces should also be isolated from one another. Power supply traces can be used to achieve this isolation as shown in Figure 1, a typical topside layout of the LT1712 on a multilayer PC board. Shown is the topside metal etch including traces, pin escape vias and the land pads for a GN16 LT1712 and its adjacent X7R 0805 bypass capacitors. The V<sup>+</sup>, V<sup>-</sup> and GND traces all shield the inputs from the outputs. Although the two V<sup>-</sup> pins are connected internally, they should be shorted together externally as well in order for both to function as shields. The same is true for the two V<sup>+</sup> pins. The two GND pins are not connected internally, but in most applications they are both connected directly to the ground plane.

Figure 1. Typical LT1712 Topside Metal for Multilayer PCB Layout

#### Hysteresis

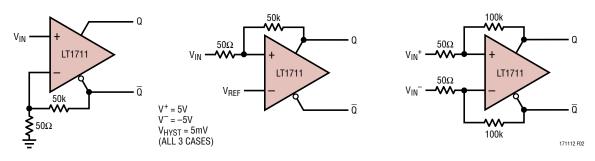

Another important technique to avoid oscillations is to provide positive feedback, also known as hysteresis, from the output to the input. Increased levels of hysteresis, however, reduce the sensitivity of the device to input voltage levels, so the amount of positive feedback should be tailored to particular system requirements. The LT1711/LT1712 are completely flexible regarding the application of hysteresis, due to rail-to-rail inputs and the complementary outputs. Specifically, feedback resistors can be connected from one of the outputs to its corresponding input without regard to common mode considerations. Figure 2 shows several configurations.

### **APPLICATIONS INFORMATION**

Figure 2. Various Configurations for Introducing Hysteresis

### TYPICAL APPLICATIONS

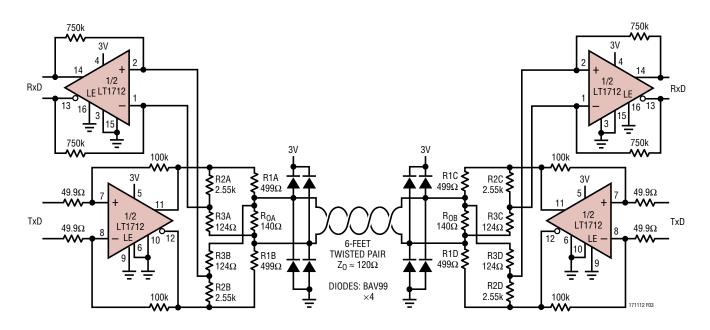

# Simultaneous Full Duplex 75Mbaud Interface with Only Two Wires

The circuit of Figure 3 shows a simple, fully bidirectional, differential 2-wire interface that gives good results to 75Mbaud, using the LT1712. Eye diagrams under conditions of unidirectional and bidirectional communication are shown in Figures 4 and 5. Although not as pristine as the unidirectional performance of Figure 4, the performance under simultaneous bidirectional operation is still excellent. Because the LT1712 input voltage range extends 100mV beyond both supply rails, the circuit works

with a full  $\pm 3V$  (one whole  $V_S$  up or down) of ground potential difference.

The circuit works well with the resistor values shown, but other sets of values can be used. The starting point is the characteristic impedance,  $Z_0$ , of the twisted-pair cable. The input impedance of the resistive network should match the characteristic impedance and is given by:

$$R_{IN} = 2 \bullet R_0 \bullet \frac{R1||(R2 + R3)}{R_0 + 2 \bullet [R1||(R2 + R3)]}$$

### TYPICAL APPLICATIONS

Figure 4. Performance of Figure 3's Circuit When Operated Unidirectionally. Eye is Wide Open

This comes out to  $120\Omega$  for the values shown. The Thevenin equivalent source voltage is given by:

$$V_{TH} = V_{S} \bullet \frac{(R2 + R3 - R1)}{(R2 + R3 + R1)} \\ \bullet \frac{R_{0}}{R_{0} + 2 \bullet [R1||(R2 + R3)]}$$

This amounts to an attenuation factor of 0.0978 with the values shown. (The actual voltage on the lines will be cut in half again due to the  $120\Omega Z_0$ .) The reason this attenuation factor is important is that it is the key to deciding the ratio between the R2-R3 resistor divider in the receiver path. This divider allows the receiver to reject the large signal of the local transmitter and instead sense the attenuated signal of the remote transmitter. Note that in the above equations, R2 and R3 are not yet fully determined because they only appear as a sum. This allows the designer to now place an additional constraint on their values. The R2-R3 divide ratio should be set to equal half the attenuation factor mentioned above or:

$$R3/R2 = 1/2 \bullet 0.0976^1$$

.

Having already designed R2 + R3 to be 2.653k (by allocating input impedance across R<sub>0</sub>, R1 and R2 + R3 to get the requisite 120 $\Omega$ ), R2 and R3 then become 2529 $\Omega$  and 123.5 $\Omega$  respectively. The nearest 1% value for R2 is 2.55k and that for R3 is 124 $\Omega$ .

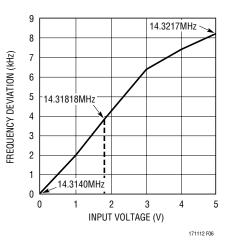

### Voltage-Tunable Crystal Oscillator

The front page application is a variant of a basic crystal oscillator that permits voltage tuning of the output frequency. Such voltage-controlled crystal oscillators (VCXO)

Figure 5. Performance When Operated Simultaneous Bidirectionally (Full Duplex). Crosstalk Appears as Noise. Eye is Slightly Shut But Performance is Still Excellent

are often employed where slight variation of a stable carrier is required. This example is specifically intended to provide a  $4 \times NTSC$  sub-carrier tunable oscillator suitable for phase locking.

The LT1711 is set up as a crystal oscillator. The varactor diode is biased from the tuning input. The tuning network is arranged so a 0V to 5V drive provides a reasonably symmetric, broad tuning range around the 14.31818MHz center frequency. The indicated selected capacitor sets tuning bandwidth. It should be picked to complement loop response in phase locking applications. Figure 6 is a plot of tuning input voltage versus frequency deviation. Tuning deviation from the  $4 \times$  NTSC 14.31818MHz center frequency exceeds ±240ppm for a 0V to 5V input.

$^{1}$  Using the design value of R2 + R3 = 2.653k rather than the implementation value of 2.55k + 124 $\Omega$  = 2.674k.

Figure 6. Control Voltage vs Output Frequency for the Front Page Application Circuit. Tuning Deviation from Center Frequency Exceeds  $\pm 240 \text{ppm}$

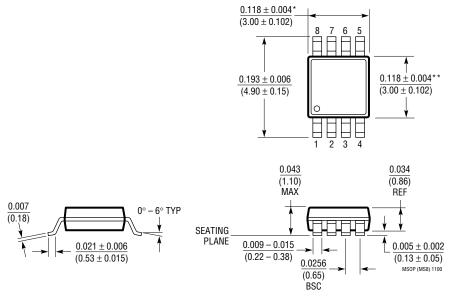

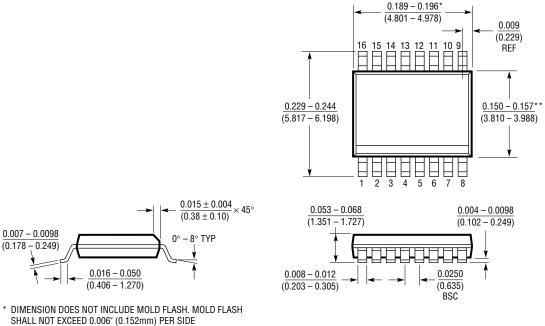

#### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

MS8 Package 8-Lead Plastic MSOP (LTC DWG # 05-08-1660)

DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

**GN Package** 16-Lead Plastic SSOP (Narrow 0.150)

(LTC DWG # 05-08-1641)

\*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

GN16 (SSOP) 1098

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

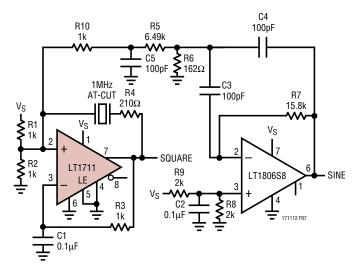

### TYPICAL APPLICATION

# 1MHz Series Resonant Crystal Oscillator with Square and Sinusoid Outputs

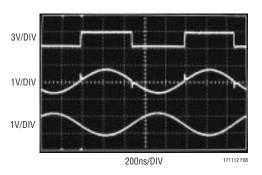

Figure 7 shows a classic 1MHz series resonant crystal oscillator. At series resonance, the crystal is a low impedance and the positive feedback connection is what brings about oscillation at the series resonant frequency. The RC feedback around the other path ensures that the circuit does not find a stable DC operating point and refuse to oscillate. The comparator output is a 1MHz square wave (top trace of Figure 8) with jitter measured at better than  $28p_{RMS}$  on a 5V supply and  $40p_{RMS}$  on a 3V supply. At Pin 2 of the comparator, on the other side of the crystal, is a clean sine wave except for the presence of the small high

Figure 7. LT1711 Comparator is Configured as a Series Resonant Xtal Oscillator. LT1806 Op Amp is Configured in a Q = 5 Bandpass with  $f_C$  = 1MHz

frequency glitch (middle trace of Figure 8). This glitch is caused by the fast edge of the comparator output feeding back through crystal capacitance. Amplitude stability of the sine wave is maintained by the fact that the sine wave is basically a filtered version of the square wave. Hence, the usual amplitude control loops associated with sinusoidal oscillators are not necessary.<sup>2</sup> The sine wave is filtered and buffered by the fast, low noise LT1806 op amp. To remove the glitch, the LT1806 is configured as a bandpass filter with a Q of 5 and unity-gain center frequency of 1MHz, with its output shown as the bottom trace of Figure 8. Distortion was measured at -70dBc and -60dBc on the second and third harmonics, respectively.

<sup>2</sup> Amplitude will be a linear function of comparator output swing, which is supply dependent and therefore adjustable. The important difference here is that any added amplitude stabilization or control loop will not be faced with the classical task of avoiding regions of nonoscillation versus clipping.

Figure 8. Oscillator Waveforms with  $V_S = 3V$ . Top is Comparator Output. Middle is Xtal Feedback to Pin 2 at LT1711 (Note the Glitches). Bottom is Buffered, Inverted and Bandpass Filtered with a Q = 5 by LT1806

## RELATED PARTS

| PART NUMBER                                                         | DESCRIPTION                                  | COMMENTS                                                    |

|---------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|

| LT1016                                                              | UltraFast Precision Comparator               | Industry Standard 10ns Comparator                           |

| LT1116                                                              | 12ns Single Supply Ground Sensing Comparator | Single Supply Version of the LT1016                         |

| LT1394                                                              | 7ns, UltraFast Single Supply Comparator      | 6mA Single Supply Comparator                                |

| LT1671                                                              | 60ns, Low Power, Single Supply Comparator    | 450µA Single Supply Comparator                              |

| LT1713/LT1714 Single/Dual 7ns, Low Power, 3V/5V/±5V, R-R Comparator |                                              | 7ns/5mA versions of the LT1711/LT1712                       |

| LT1719 4.5ns, Single Supply 3V/5V/±5V Comparator                    |                                              | 4mA Comparator with Rail-to-Rail Outputs and Level Shifting |

| LT1720/LT1721                                                       | Dual/Quad, 4.5ns, Single Supply Comparator   | Dual/Quad Version of the LT1719                             |

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург, Промышленная ул, дом № 19, литера Н, помещение 100-Н Офис 331