# OCTAL E1 SHORT HAUL LINE INTERFACE UNIT

# FEATURES

- Fully integrated octal E1 short haul line interface which supports 120W E1 twisted pair and 75W E1 coaxial applications

- Selectable single rail or dual rail mode and AMI or HDB3 line encoder/decoder

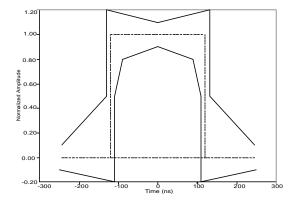

- Built-in transmit pre-equalization meets G.703

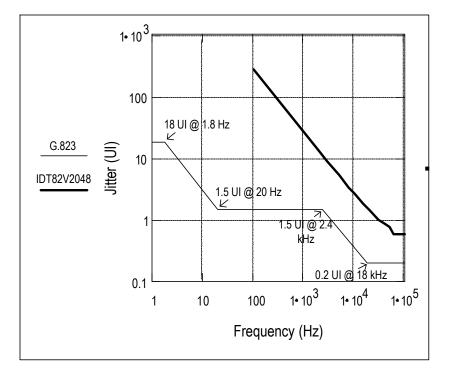

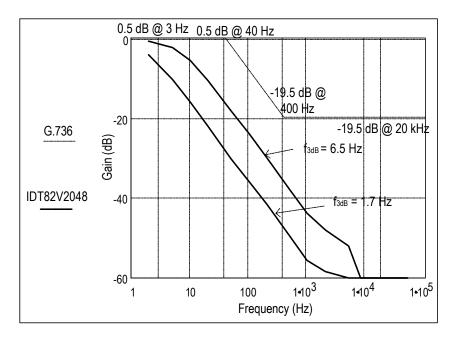

- Selectable transmit/receive jitter attenuator meets ETSI CTR12/13, ITU G.736, G.742 and G.823 specifications

- SONET/SDH optimized jitter attenuator meets ITU G.783 mapping jitter specification

- Digital/analog LOS detector meets ITU G.775 and ETS 300 233

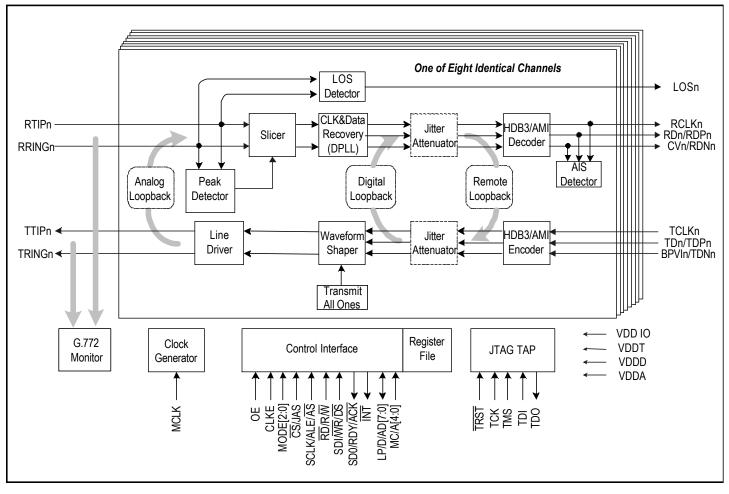

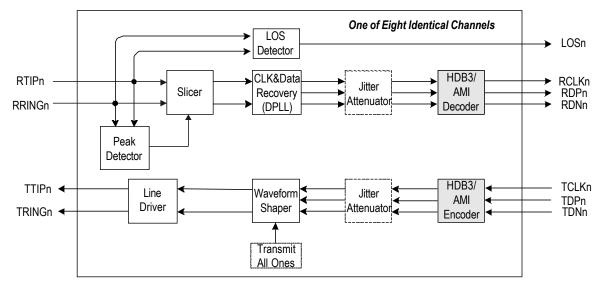

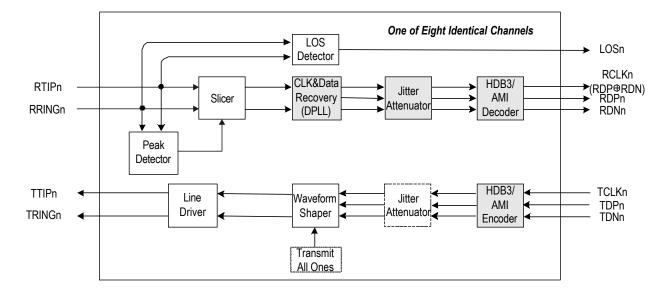

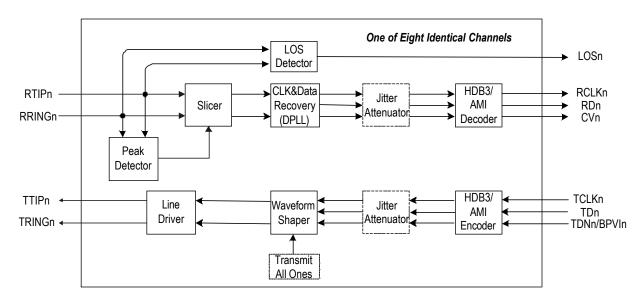

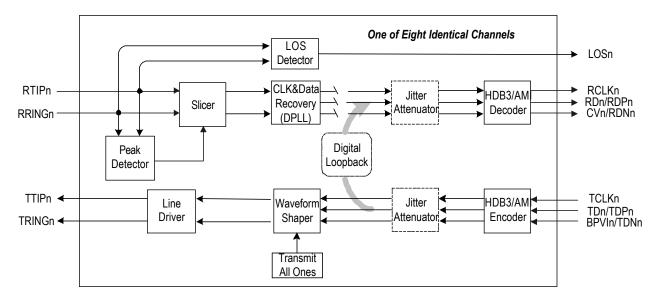

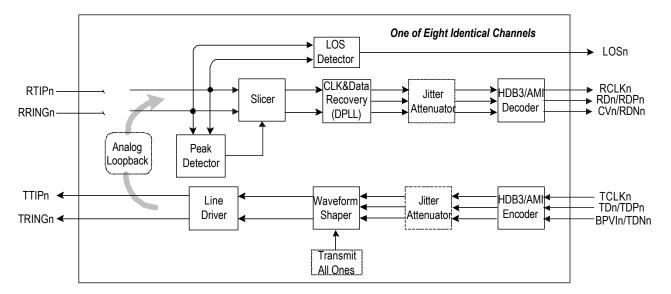

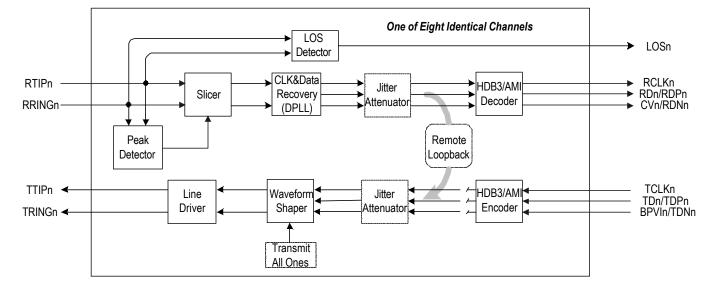

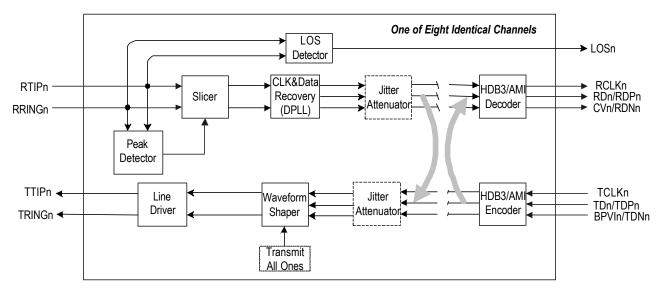

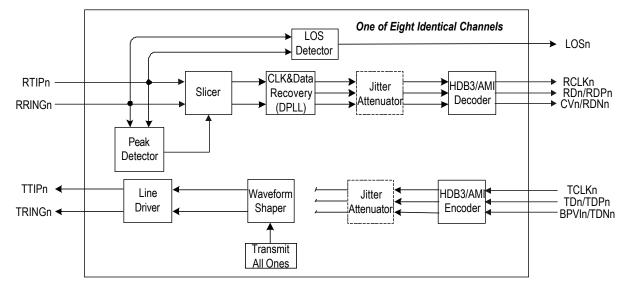

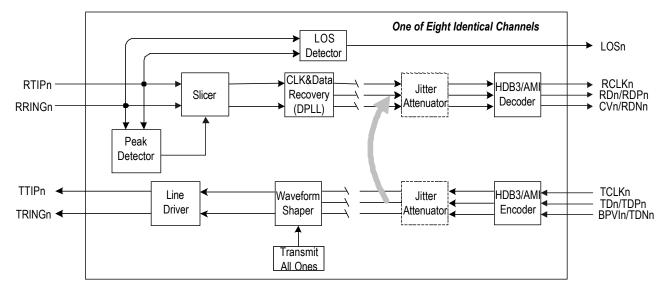

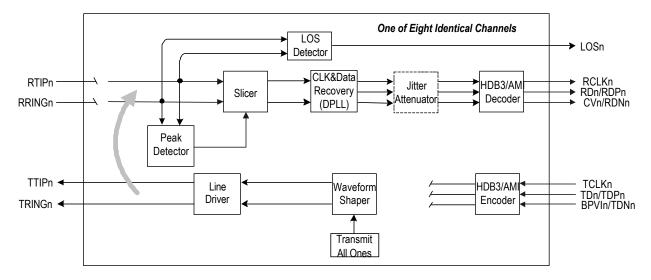

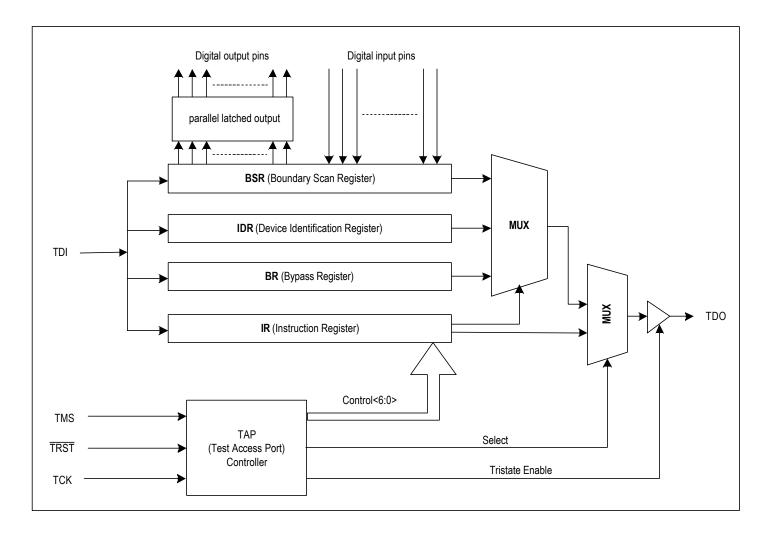

FUNCTIONAL BLOCK DIAGRAM

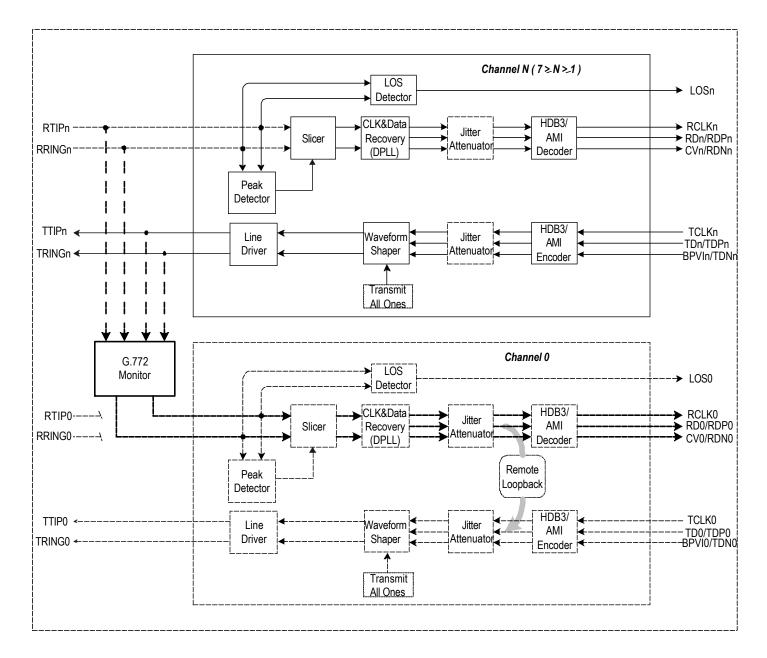

- ITU G.772 non-intrusive monitoring for in-service testing for any one of channel1 to channel7

- Low impedance transmit drivers with tri-state

- Selectable hardware and parallel/serial host interface

- Local and remote loopback test functions

- Hitless Protection Switching (HPS) for 1 to 1 protection without relays

- JTAG boundary scan for board test

- ♦ 3.3V supply with 5V tolerant I/O

- Low power consumption

- Operating temperature range: -40°C to +85°C

- Available in 144-pin Thin Quad Flat Pack (TQFP\_144\_DA) and 160-pin Plastic Ball Grid Array (PBGA) packages

# Figure - 1. Block Diagram

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### **INDUSTRIAL TEMPERATURE RANGES**

# **JANUARY 2003**

# **DESCRIPTION:**

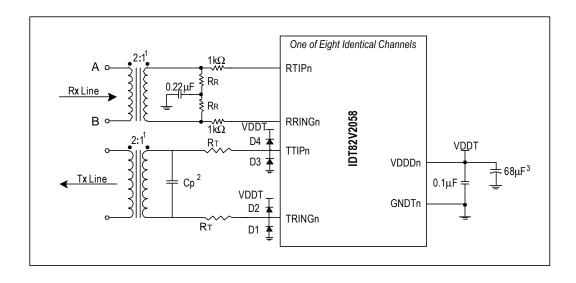

The IDT82V2058 is a single chip, 8-channel E1 short haul PCM transceiver with a reference clock of 2.048MHz. It contains 8 transmitters and 8 receivers.

Both receivers and transmitters can be programmed to work either in single rail mode or dual rail mode. AMI or HDB3 encoder/decoder is selectable in single rail mode. Pre-encoded transmit data in NRZ format can be accepted when the device is configured in dual rail mode. The receivers perform clock and data recovery by using integrated digital phase-locked loop. As an option, the raw sliced data (no retiming) can be output on the receive data pins. Transmit equalization is implemented with low-impedance output drivers that provide shaped waveforms to the transformer, guaranteeing template conformance.

A jitter attenuator is integrated in the IDT82V2058 and can be switched into either the transmit path or the receive path. The jitter attenuation performance meets ETSI CTR12/13, ITU G.736, G.742, and G.823 specifications.

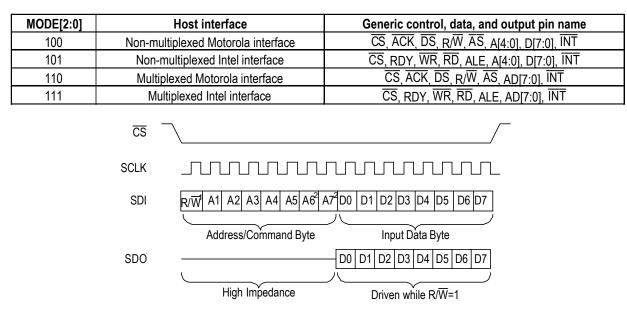

The IDT82V2058 offers hardware control mode and software control mode. Software control mode works with either serial host interface or parallel host interface. The latter works via an Intel/Motorola compatible 8-bit parallel interface for both multiplexed or nonmultiplexed applications. Hardware control mode uses multiplexed pins to select different operation mode when host interface is not available to the device.

The IDT82V2058 also provides loopback testing functions and JTAG boundary scan testing functions. As the monitoring function is integrated, IDT82V2058 can be configured as a 7-channel transceiver with non-intrusive protected monitoring points.

The IDT82V2058 can be used for SDH/SONET multiplexers, central office or PBX, digital access cross connects, digital radio base stations, remote wireless modules and microwave transmission systems.

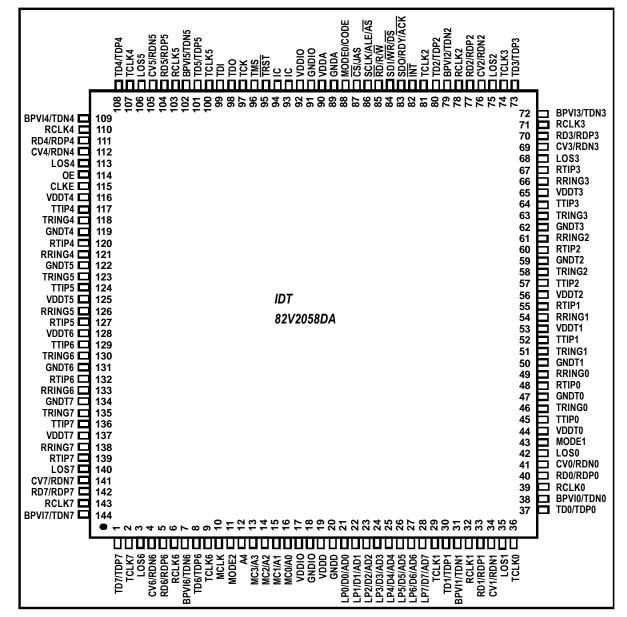

#### Figure - 2. TQFP144 Package Pin Assignment

# PIN CONFIGURATIONS

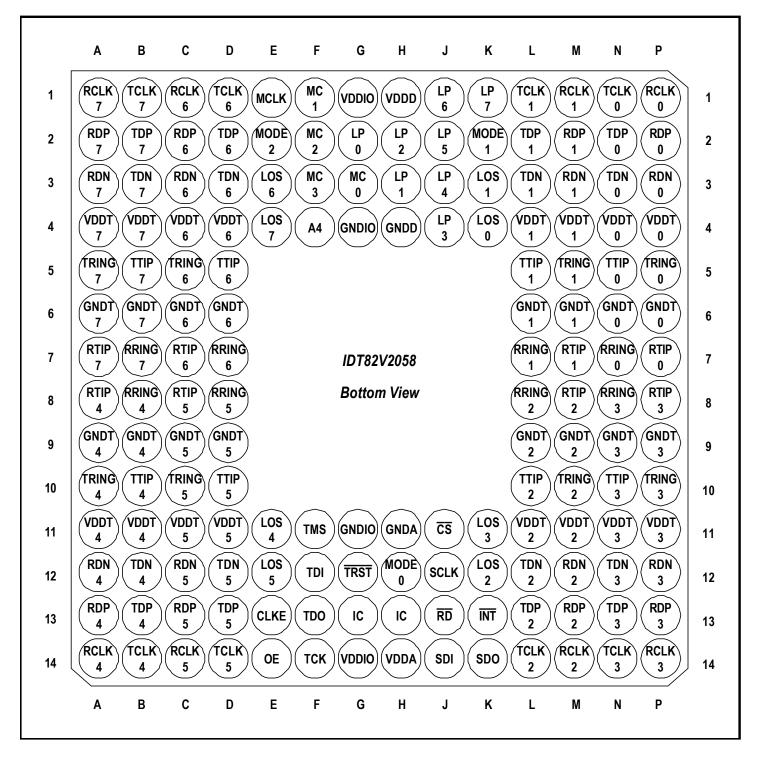

# **PIN CONFIGURATIONS (CONTINUED)**

Figure - 2b. PBGA160 Package Pin Assignment

# **PIN DESCRIPTION**

|        | Name Type       |        | No.    |                                                                                                     |

|--------|-----------------|--------|--------|-----------------------------------------------------------------------------------------------------|

| Name   | Туре            | QFP144 | BGA160 | Description                                                                                         |

|        | •               |        |        | Transmit and Receive Line Interface                                                                 |

| TTIP0  |                 | 45     | N5     | TTIPn/TRINGn: Transmit Bipolar Tip/Ring for Channel 0~7                                             |

| TTIP1  |                 | 52     | L5     | These pins are the differential line driver outputs. They will be in high impedance state if pin OE |

| TTIP2  |                 | 57     | L10    | is low or the corresponding pin TCLKn is low (pin OE is globe control, while pin TCLKn is per-      |

| TTIP3  |                 | 64     | N10    | channel control). In host mode, each pin can be in high impedance state by programming a "1" to     |

| TTIP4  |                 | 117    | B10    | the corresponding bit in Register <b>OE</b> <sup>1</sup> .                                          |

| TTIP5  |                 | 124    | D10    |                                                                                                     |

| TTIP6  |                 | 129    | D5     |                                                                                                     |

| TTIP7  | Analog          | 136    | B5     |                                                                                                     |

| TRING0 | Output          | 46     | P5     |                                                                                                     |

| TRING1 |                 | 51     | M5     |                                                                                                     |

| TRING2 |                 | 58     | M10    |                                                                                                     |

| TRING2 |                 | 63     | P10    |                                                                                                     |

| TRING4 |                 | 118    | A10    |                                                                                                     |

| TRING5 |                 | 123    | C10    |                                                                                                     |

| TRING6 |                 | 130    | C5     |                                                                                                     |

| TRING7 |                 | 135    | A5     |                                                                                                     |

| RTIP0  |                 | 48     | P7     | RTIPn/RRINGn: Receive Bipolar Tip/Ring for Channel 0~7                                              |

| RTIP1  |                 | 55     | M7     | These pins are the differential line receiver inputs.                                               |

| RTIP2  |                 | 60     | M8     | F                                                                                                   |

| RTIP3  |                 | 67     | P8     |                                                                                                     |

| RTIP4  |                 | 120    | A8     |                                                                                                     |

| RTIP5  |                 | 127    | C8     |                                                                                                     |

| RTIP6  | Analaa          | 132    | C7     |                                                                                                     |

| RTIP7  | Analog<br>Input | 139    | A7     |                                                                                                     |

| RRING0 |                 | 49     | N7     |                                                                                                     |

| RRING1 |                 | 54     | L7     |                                                                                                     |

| RRING2 |                 | 61     | L8     |                                                                                                     |

| RRING3 |                 | 66     | N8     |                                                                                                     |

| RRING4 |                 | 121    | B8     |                                                                                                     |

| RRING5 |                 | 126    | D8     |                                                                                                     |

| RRING6 |                 | 133    | D7     |                                                                                                     |

| RRING7 |                 | 138    | B7     |                                                                                                     |

<sup>1</sup> Register name is indicated by bold capital letter. **OE**: Output Enable Register.

| Name       | <b>T</b> | Pin    | No.    | Description                                                                                                                                                                      |                                                                     |                                                                       |  |  |  |

|------------|----------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Name       | Туре     | QFP144 | BGA160 |                                                                                                                                                                                  |                                                                     | Description                                                           |  |  |  |

| TD0/TDP0   |          | 37     | N2     | TDn: Transmi                                                                                                                                                                     | it Data for Channe                                                  | 0~7                                                                   |  |  |  |

| TD1/TDP1   |          | 30     | L2     |                                                                                                                                                                                  |                                                                     | mode, the NRZ data to be transmitted is input on this pin. Data       |  |  |  |

| TD2/TDP2   |          | 80     | L13    |                                                                                                                                                                                  |                                                                     | e on falling edges of TCLKn, and encoded by AMI or HDB3 line          |  |  |  |

| TD3/TDP3   |          | 73     | N13    | code rules bef                                                                                                                                                                   | ore being transmitte                                                | d to the line.                                                        |  |  |  |

| TD4/TDP4   |          | 108    | B13    |                                                                                                                                                                                  |                                                                     |                                                                       |  |  |  |

| TD5/TDP5   |          | 101    | D13    |                                                                                                                                                                                  |                                                                     | on for Channel 0~7                                                    |  |  |  |

| TD6/TDP6   |          | 8      | D2     |                                                                                                                                                                                  |                                                                     | ble in Signal Rail mode 2 (see table-1) with AMI enabled. A low-      |  |  |  |

| TD7/TDP7   | I        | 1      | B2     | to-high transition on this pin will make the next logic one to be transmitted on TDn pin the same polarity as the previous pulse, and violate the AMI rule. This is for testing. |                                                                     |                                                                       |  |  |  |

| BPVI0/TDN0 |          | 38     | N3     |                                                                                                                                                                                  |                                                                     |                                                                       |  |  |  |

| BPVI1/TDN1 |          | 31     | L3     |                                                                                                                                                                                  | TDPn/TDNn: Positive/Negative Transmit Data for Channel 0~7          |                                                                       |  |  |  |

| BPVI2/TDN2 |          | 79     | L12    |                                                                                                                                                                                  |                                                                     | node, the NRZ data to be transmitted for positive/negative pulse      |  |  |  |

| BPVI3/TDN3 |          | 72     | N12    |                                                                                                                                                                                  |                                                                     | n/TDNn are active high and sampled into the device on falling         |  |  |  |

| BPVI4/TDN4 |          | 109    | B12    |                                                                                                                                                                                  | edges of TCLKn. The line code in Dual Rail mode is as the follows : |                                                                       |  |  |  |

| BPVI5/TDN5 |          | 102    | D12    |                                                                                                                                                                                  |                                                                     | Output Pulse                                                          |  |  |  |

| BPVI6/TDN6 |          | 7      | D3     |                                                                                                                                                                                  |                                                                     | Space                                                                 |  |  |  |

| BPVI7/TDN7 |          | 144    | B3     |                                                                                                                                                                                  |                                                                     | Negative Pulse                                                        |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | Positive Pulse                                                        |  |  |  |

|            |          |        |        |                                                                                                                                                                                  | 1                                                                   | Space                                                                 |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     |                                                                       |  |  |  |

|            |          |        |        | Pulling pin TDNn high for more than 16 consecutive TCLK clock cycles will configure the corresponding channel into Single Rail mode 1 (see <i>table-1 on Page13</i> ).           |                                                                     |                                                                       |  |  |  |

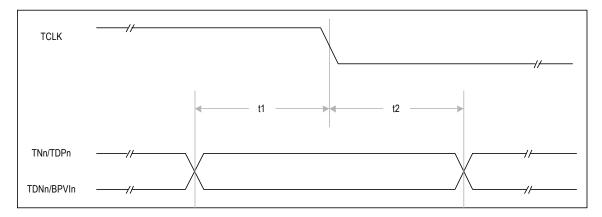

| TCLK0      | 1        | 36     | N1     |                                                                                                                                                                                  | smit Clock for Cha                                                  |                                                                       |  |  |  |

| TCLK0      | 1        | 29     | L1     |                                                                                                                                                                                  |                                                                     | nsmitted is input on this pin. The transmit data at TDn/TDPn or       |  |  |  |

| TCLK2      |          | 81     | L14    |                                                                                                                                                                                  |                                                                     | n falling edges of TCLKn.                                             |  |  |  |

| TCLK3      |          | 74     | N14    |                                                                                                                                                                                  |                                                                     | an 16 MCLK cycles, the corresponding transmitter is set in            |  |  |  |

| TCLK4      |          | 107    | B14    |                                                                                                                                                                                  |                                                                     | en MCLK is clocked). In TAO state, the TAO generator adopts           |  |  |  |

| TCLK5      |          | 100    | D14    | MCLK as the t                                                                                                                                                                    |                                                                     |                                                                       |  |  |  |

| TCLK6      |          | 9      | D1     |                                                                                                                                                                                  |                                                                     | ing transmit channel is set into power down state, while driver       |  |  |  |

| TCLK7      |          | 2      | B1     |                                                                                                                                                                                  | ecome high impeda                                                   |                                                                       |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | TCLKn are summarized as follows:                                      |  |  |  |

|            |          |        |        | MCLK                                                                                                                                                                             | TCLKn                                                               | Transmitter Mode                                                      |  |  |  |

|            |          |        |        | Clocked                                                                                                                                                                          | Clocked                                                             | Normal operation                                                      |  |  |  |

|            |          |        |        | Clocked                                                                                                                                                                          | High (≥ 16 MCLK                                                     |                                                                       |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | corresponding transmit channel.                                       |  |  |  |

|            |          |        |        | Clocked                                                                                                                                                                          | Low (≥ 64 MCLK)                                                     | Corresponding transmit channel is set into power down state.          |  |  |  |

|            |          |        |        | High/Low                                                                                                                                                                         | TCLK1 is clocked                                                    |                                                                       |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | TCLKn is high Transmit All One (TAO) signals to the line              |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | $(\geq 16 \text{ TCLK1})$ side in the corresponding transmit channel. |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | TCLKn is low Corresponding transmit channel is set into               |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | (≥ 64 TCLK1) power down state.                                        |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | The receive path is not affected by the status of TCLK1.              |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | When MCLK is high, all receive paths just slice the incoming          |  |  |  |

|            |          |        |        |                                                                                                                                                                                  |                                                                     | data stream. When MCLK is low, all the receive paths are              |  |  |  |

|            |          |        |        |                                                                                                                                                                                  | <b>TOLIK</b>                                                        | powered down.                                                         |  |  |  |

|            |          |        |        | High/Low                                                                                                                                                                         | TCLK1 is not                                                        | All eight transmitters (TTIPn & TRINGn) will be in high               |  |  |  |

|            |          |        |        |                                                                                                                                                                                  | available                                                           | impedance state.                                                      |  |  |  |

|            |          |        |        |                                                                                                                                                                                  | (High/Low)                                                          |                                                                       |  |  |  |

| Name           | <b>.</b>  | Pin No.  |          | Description                                                                                                    |  |  |  |

|----------------|-----------|----------|----------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| Name           | Туре      | QFP144   | BGA160   | Description                                                                                                    |  |  |  |

| RD0/RDP0       | 0         | 40       | P2       | RDn: Receive Data for Channel 0~7                                                                              |  |  |  |

| RD1/RDP1       |           | 33       | M2       | In Single Rail mode, the received NRZ data is output on this pin. The data is decoded by AMI or HDB3           |  |  |  |

| RD2/RDP2       | Tri-state | 77       | M13      | line code rule.                                                                                                |  |  |  |

| RD3/RDP3       |           | 70       | P13      |                                                                                                                |  |  |  |

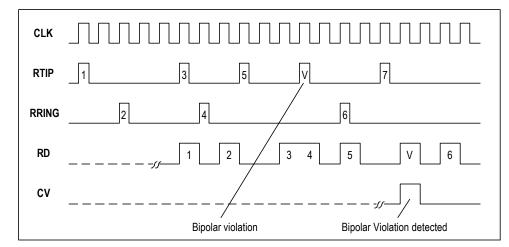

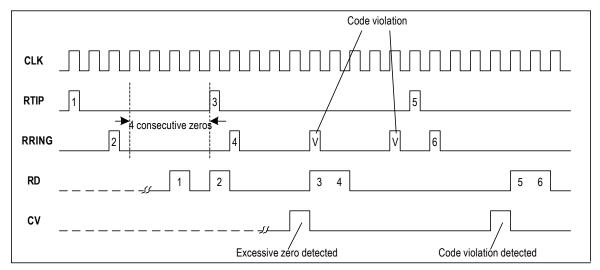

| RD4/RDP4       |           | 111      | A13      | CVn: Code Violation for Channel 0~7                                                                            |  |  |  |

| RD5/RDP5       |           | 104      | C13      | In Single Rail mode, the bipolar violation, code violation and excessive zeros will be reported by driving     |  |  |  |

| RD6/RDP6       |           | 5        | C2       | pin CVn to high level for a full clock cycle. However, only bipolar violation is indicated when AMI            |  |  |  |

| RD7/RDP7       |           | 142      | A2       | decoder is selected.                                                                                           |  |  |  |

| CV0/RDN0       |           | 41       | P3       | RDPn/RDNn: Positive/Negative Receive Data for Channel 0~7                                                      |  |  |  |

| CV1/RDN1       |           | 34       | M3       | In Dual Rail mode with clock recovery, these pins output the NRZ data. A high signal on RDPn                   |  |  |  |

| CV2/RDN2       |           | 76       | M12      | indicates the receipt of a positive pulse on RTIPn/RRINGn while a high signal on RDNn indicates the            |  |  |  |

| CV3/RDN3       |           | 69       | P12      | receipt of a negative pulse on RTIPn/RRINGn.                                                                   |  |  |  |

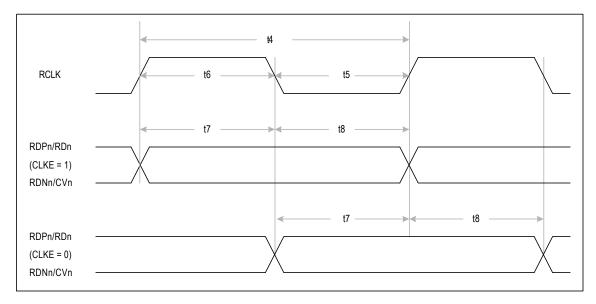

| CV4/RDN4       |           | 112      | A12      | The output data at RDn or RDPn/RDNn are valid on the falling edges of RCLK when the CLKE input is              |  |  |  |

| CV5/RDN5       |           | 105      | C12      | in High level, or valid on the rising edges of RCLK when CLKE is Low.                                          |  |  |  |

| CV6/RDN6       |           | 4        | C3       | In Dual Rail mode without clock recovery, these pins output the raw RZ sliced data. In this data               |  |  |  |

| CV7/RDN7       |           | 141      | A3       | recovery mode, the active polarity of RDPn/RDNn is determined by pin CLKE. When pin CLKE is Low,               |  |  |  |

|                |           |          |          | RDPn/RDNn is active low. When pin CLKE is High, RDPn/RDNn is active high.                                      |  |  |  |

|                |           |          |          | In hardware mode, RDn or RDPn/RDNn will remain active during LOS. In host mode, these pins will                |  |  |  |

|                |           |          |          | either remain active or insert alarm indication signal (AIS) into the receive path, determined by bit AISE     |  |  |  |

|                |           |          |          | in register <b>GCF</b> (Global Configuration register).                                                        |  |  |  |

|                | -         |          |          | RDn or RDPn/RDNn is set into high impedance when the corresponding receiver is power down.                     |  |  |  |

| RCLK0          | 0         | 39       | P1       | RCLKn: Receive Clock for Channel 0~7                                                                           |  |  |  |

| RCLK1          |           | 32       | M1       | In clock recovery mode, this pin outputs the recovered clock from signal received on RTIPn/RRINGn.             |  |  |  |

| RCLK2          | Tri-state | 78       | M14      | The received data are clocked out of the device on rising edges of RCLKn if pin CLKE is low, or on             |  |  |  |

| RCLK3          |           | 71       | P14      | falling edges of RCLKn if pin CLKE is high.                                                                    |  |  |  |

| RCLK4          |           | 110      | A14      | In data recovery mode, RCLKn is the output of an internal exclusive OR (XOR) which is connected with           |  |  |  |

| RCLK5          |           | 103      | C14      | RDPn and RDNn. The clock is recovered from the signal on RCLKn externally.                                     |  |  |  |

| RCLK6<br>RCLK7 |           | 6<br>143 | C1<br>A1 | If receiver n is power down, the corresponding RCLKn is in high impedance.                                     |  |  |  |

| MCLK/          | 1         | 143      | E1       | MCLK: Master Clock                                                                                             |  |  |  |

| MOLIN          | I         | 10       |          | This is the independent, free running reference clock. A clock of 2.048 MHz is supplied to this pin as         |  |  |  |

|                |           |          |          | the clock reference of the device for normal operation.                                                        |  |  |  |

|                |           |          |          | In receive path, when MCLK is high, the device slices the incoming bipolar line signal into RZ pulse           |  |  |  |

|                |           |          |          | (Data Recovery mode). When MCLK is low, all the receivers are power down, and the output pins                  |  |  |  |

|                |           |          |          | RCLKn, RDPn and RDNn are switched to high impedance.                                                           |  |  |  |

|                |           |          |          | In transmit path, the operation mode is decided by the combination of MCLK and TCLKn (see TCLKn                |  |  |  |

|                |           |          |          | pin description for detail).                                                                                   |  |  |  |

|                |           |          |          | Note that wait state generation via RDY/ACK is not available if MCLK is not provided.                          |  |  |  |

| LOS0           | 0         | 42       | K4       | LOSn: Loss of Signal Output for Channel 0~7                                                                    |  |  |  |

| LOS1           |           | 35       | K3       | A high level on this pin indicates the loss of signal when there is no transition over a specified period of   |  |  |  |

| LOS2           |           | 75       | K12      | time or hasn't enough ones density in the received signal. The transition will return to low automa            |  |  |  |

| LOS3           |           | 68       | K11      | when there is enough transitions over a specified period of time with a certain ones density in the            |  |  |  |

| LOS4           |           | 113      | E11      | received signal. The LOS assertion and desertion criteria are described in the <i>Functional Description</i> . |  |  |  |

| LOS5           |           | 106      | E12      |                                                                                                                |  |  |  |

| LOS6           |           | 3        | E3       |                                                                                                                |  |  |  |

| LOS7           |           | 140      | E4       |                                                                                                                |  |  |  |

| Nama   | <b>T</b>     | Pin    | No.    | Description                                                                                                             |                   |                                                                                                                                                                                       |  |  |  |  |

|--------|--------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name   | Туре         | QFP144 | BGA160 |                                                                                                                         |                   | Description                                                                                                                                                                           |  |  |  |  |

|        |              |        |        | -                                                                                                                       |                   | re/Host Control Mode                                                                                                                                                                  |  |  |  |  |

| MODE2  | I            | 11     | E2     |                                                                                                                         | ontrol Mode S     |                                                                                                                                                                                       |  |  |  |  |

|        | / <b>D</b>   |        |        | The signal                                                                                                              |                   | ermines which control mode is selected to control the device:                                                                                                                         |  |  |  |  |

|        | (Pulled      |        |        |                                                                                                                         | MODE2             | Control Interface                                                                                                                                                                     |  |  |  |  |

|        | to<br>VDDIO  |        |        |                                                                                                                         | Low               | Control by Hardware mode                                                                                                                                                              |  |  |  |  |

|        | /2)          |        |        |                                                                                                                         | VDDIO/2           | Control by Serial Host Interface                                                                                                                                                      |  |  |  |  |

|        | , _ ,        |        |        |                                                                                                                         | High              | Control by Parallel Host Interface                                                                                                                                                    |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | lude MODE[2:0], TS[2:0], LOOP[7:0], CODE, CLKE, JAS and OE.                                                                                                                           |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | include CS, SCLK, SDI, SDO and INT.                                                                                                                                                   |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | is include $\overline{CS}$ , A[4:0], D[7:0], $\overline{WR}/\overline{DS}$ , $\overline{RD}/R/\overline{W}$ , ALE/ $\overline{AS}$ , $\overline{INT}$ and RDY/ $\overline{ACK}$ . The |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | parallel host interface as follows (refer to MODE1 and MODE0 pin descriptions                                                                                                         |  |  |  |  |

|        |              |        |        | below for details):                                                                                                     |                   |                                                                                                                                                                                       |  |  |  |  |

|        |              |        |        | -                                                                                                                       | MODE[2:0]         | Host Interface                                                                                                                                                                        |  |  |  |  |

|        |              | r -    |        | 100 Non-multiplexed Motorola mode interface.                                                                            |                   |                                                                                                                                                                                       |  |  |  |  |

|        |              |        |        | -                                                                                                                       | 101               | Non-multiplexed Intel mode interface.                                                                                                                                                 |  |  |  |  |

|        |              |        |        | -                                                                                                                       | <u>110</u><br>111 | Multiplexed Motorola mode interface.                                                                                                                                                  |  |  |  |  |

| MODE1  |              | 43     | K2     |                                                                                                                         | ontrol Mode S     | Multiplexed Intel mode interface.                                                                                                                                                     |  |  |  |  |

| NUDET  | I            | 43     | r\2    |                                                                                                                         |                   | e parallel interface operates with separate address bus and data bus when this                                                                                                        |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | with multiplexed address and data bus when this pin is High.                                                                                                                          |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | ardware mode, this pin should be grounded.                                                                                                                                            |  |  |  |  |

| MODE0  | I            | 88     | H12    | MODE0: C                                                                                                                | ontrol Mode S     | Select 0                                                                                                                                                                              |  |  |  |  |

| /CODE  |              |        |        | In host mo                                                                                                              | de, the paralle   | I host interface is configured for Motorola compatible hosts when this pin is Low,                                                                                                    |  |  |  |  |

|        |              |        |        | or for Intel                                                                                                            | compatible hos    | sts when this pin is High.                                                                                                                                                            |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | 0-14                                                                                                                                                                                  |  |  |  |  |

|        |              |        |        |                                                                                                                         | e Code Rule       | de, the HDB3 encoder/decoder is enabled when this pin is Low, and AMI                                                                                                                 |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | ed when this pin is High. The selections affect all the channels.                                                                                                                     |  |  |  |  |

|        |              |        |        | 011000001/00                                                                                                            |                   |                                                                                                                                                                                       |  |  |  |  |

|        |              |        |        | In serial ho                                                                                                            | st mode, this p   | pin should be grounded.                                                                                                                                                               |  |  |  |  |

| CS/JAS | -            | 87     | J11    | CS: Chip S                                                                                                              | Select (Active    | Low)                                                                                                                                                                                  |  |  |  |  |

|        |              |        |        |                                                                                                                         |                   | asserted low by the host to enable host interface. A transition from High to Low                                                                                                      |  |  |  |  |

|        | (Pulled      |        |        |                                                                                                                         |                   | or each Read/Write operation and the level must not return to High until the                                                                                                          |  |  |  |  |

|        | to           |        |        | operation is                                                                                                            | s over.           |                                                                                                                                                                                       |  |  |  |  |

|        | VDDIO<br>/2) |        |        | IAS: litto                                                                                                              | · Attonuator S    | calact                                                                                                                                                                                |  |  |  |  |

|        | 12)          |        |        | JAS: Jitter Attenuator Select<br>In hardware control mode, this pin globally determines the Jitter Attenuator position: |                   |                                                                                                                                                                                       |  |  |  |  |

|        |              |        |        | JAS Jitter Attenuator (JA) Configuration                                                                                |                   |                                                                                                                                                                                       |  |  |  |  |

|        | ŀ            |        |        |                                                                                                                         | Low               | JA in transmit path                                                                                                                                                                   |  |  |  |  |

|        |              |        |        | V                                                                                                                       | DDIO/2            | JA not used                                                                                                                                                                           |  |  |  |  |

|        |              |        |        |                                                                                                                         | High              | JA in receive path                                                                                                                                                                    |  |  |  |  |

|                     |      | Pin | No.    | <b>-</b> <i>1.4</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------|------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                | Туре |     | BGA160 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

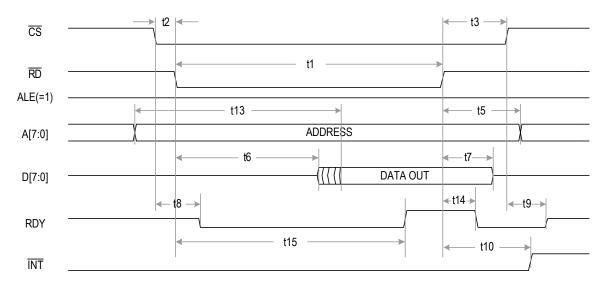

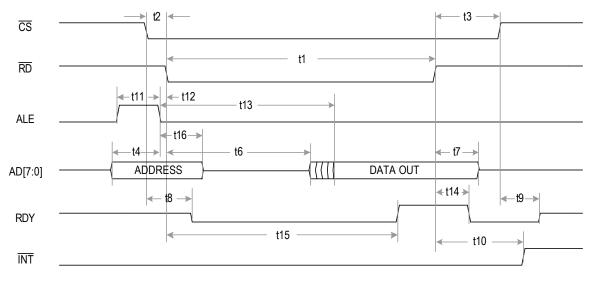

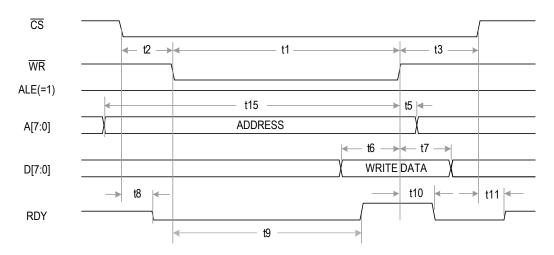

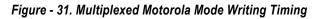

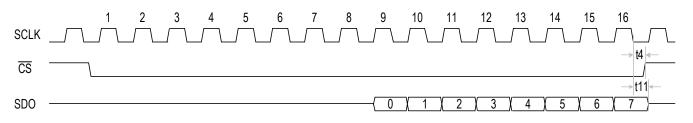

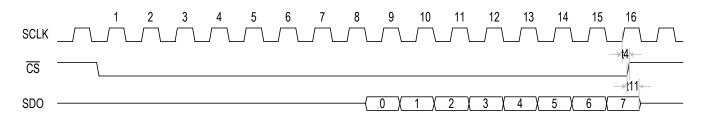

| SCLK<br>/ALE<br>/AS | I    | 86  |        | SCLK: Shift Clock<br>In serial host mode, the signal on this pin is the shift clock for the serial interface. Data on pin SDO is<br>clocked out on falling edges of SCLK if pin CLKE is Low, or on rising edges of SCLK if pin CLKE is<br>High. Data on pin SDI is always sampled on rising edges of SCLK.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

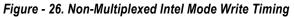

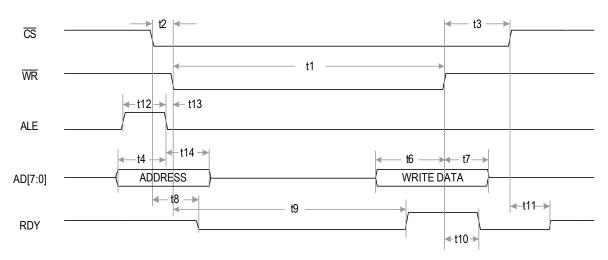

|                     |      |     |        | ALE: Address Latch Enable<br>In parallel Intel multiplexed host mode, the address on AD[4:0] is sampled into the device on falling<br>edges of ALE (Signals on AD[7:5] are ignored). In non-multiplexed host mode, ALE should be pulled<br>High.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

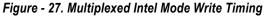

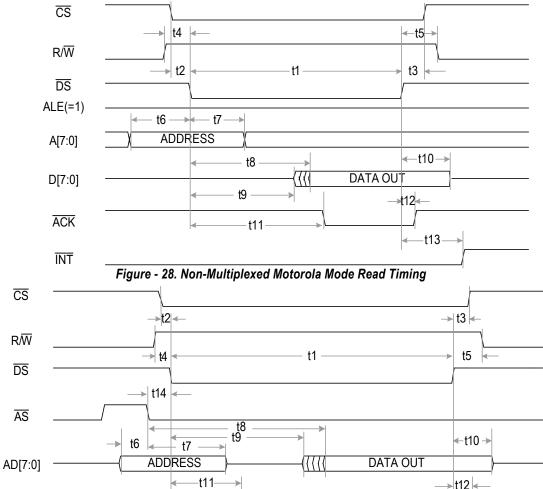

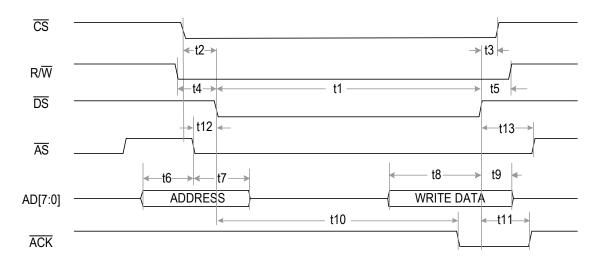

|                     |      |     |        | $\overline{\text{AS}}$ : Address Strobe (Active Low)<br>In parallel Motorola multiplexed host mode, the address on AD[4:0] is latched into the device on falling<br>edges of $\overline{\text{AS}}$ (Signals on AD[7:5] are ignored). In non-multiplexed host mode, $\overline{\text{AS}}$ should be pulled<br>High.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                     |      |     |        | (Note: This pin is ignored in hardware control mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RD/R/W              | I    | 85  | J13    | <b>RD: Read Strobe (Active Low)</b><br>In parallel Intel multiplexed or non-multiplexed host mode, this pin is active low for read operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                     |      |     |        | <b>R</b> <i>W</i> <b>: Read/Write Select</b><br>In parallel Motorola multiplexed or non-multiplexed host mode, the pin is active low for write operation<br>and high for read operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                     |      |     |        | (Note: This pin is ignored in hardware control mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SDI<br>/WR<br>/DS   |      | 84  | J14    | SDI: Serial Data Input<br>In serial host mode, this pin input the data to the serial interface. Data on this pin is sampled on rising<br>edges of SCLK.<br>WR: Write Strobe (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                     |      |     |        | In parallel Intel host mode, this pin is active low during write operation. The data on D[7:0] (in non-<br>multiplexed mode) or AD[7:0] (in multiplexed mode) is sampled into the device on rising edges of $\overline{WR}$ .                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

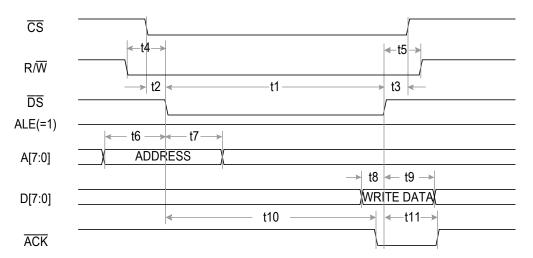

|                     |      |     |        | $\overline{\text{DS}}$ : Data Strobe (Active Low)<br>In parallel Motorola host mode, this pin is active low. During a write operation (R/ $\overline{W}$ = 0), the data on D[7:0] (in non-multiplexed mode) or AD[7:0] (in multiplexed mode) is sampled into the device on rising edges of DS. During a read operation (R/ $\overline{W}$ =1), the data is driven to D[7:0] (in non-multiplexed mode) by the device on rising edges of $\overline{\text{DS}}$ .<br>In parallel Motorola non-multiplexed host mode, the address information on the 5 bits of address bus A[4:0] are latched into the device on the falling edge of $\overline{\text{DS}}$ . |  |  |  |

|                     |      |     |        | (Note: This pin is ignored in hardware control mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SDO<br>/RDY<br>/ACK | 0    | 83  | K14    | SDO: Serial Data Output<br>In serial host mode, the data is output on this pin. In serial write operation, SDO is always in High<br>impedance. In serial read operation, SDO is in High impedance only when SDI is in<br>address/command byte. Data on pin SDO is clocked out of the device on falling edges of SCLK if pin<br>CLKE is Low, or on rising edges of SCLK if pin CLKE is High.                                                                                                                                                                                                                                                                |  |  |  |

|                     |      |     |        | <b>RDY: Ready Output</b><br>In parallel Intel host mode, the high level of this pin reports to the host that bus cycle can be<br>completed, while low reports the host must insert wait states.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                     |      |     |        | <b>ACK:</b> Acknowledge Output (Active Low)<br>In parallel Motorola host mode, the low level of this pin indicates that valid information on the data bus<br>is ready for a read operation or acknowledges the acceptance of the written data during a write<br>operation.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Name             | Туре      | Pin No. |        | Description                          |                                                                                                                           |  |  |

|------------------|-----------|---------|--------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

|                  |           | QFP144  | BGA160 |                                      |                                                                                                                           |  |  |

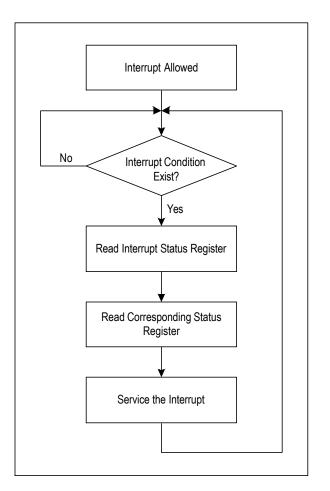

| ĪNT              | 0         | 82      | K13    | INT: Interrupt (Active Low)          |                                                                                                                           |  |  |

|                  | Open      |         |        | This is the open drain, active low   | r interrupt output. Four sources may cause the interrupt (refer                                                           |  |  |

|                  | Drain     |         |        | to Interrupt Handling of Function    |                                                                                                                           |  |  |

| LP7/D7/AD7       | I/O       | 28      | K1     | LPn: Loopback Select 7~0             |                                                                                                                           |  |  |

| LP6/D6/AD6       | ., 0      | 27      | J1     | •                                    | Pn configures the corresponding channel in different loopback                                                             |  |  |

| LP5/D5/AD5       | Tri-State | 26      | J2     | mode, as follows:                    |                                                                                                                           |  |  |

| LP4/D4/AD4       | in olato  | 25      | J3     | LPn                                  | Loopback Configuration                                                                                                    |  |  |

| LP3/D3/AD3       |           | 24      | J4     | Low                                  | Remote Loopback                                                                                                           |  |  |

| LP2/D2/AD2       |           | 23      | H2     | VDDIO/2                              | No Loopback                                                                                                               |  |  |

| LP1/D1/AD1       |           | 22      | H3     | High                                 | Analog Loopback                                                                                                           |  |  |

| LP0/D0/AD0       |           | 21      | G2     |                                      | n of Functional Description for details.                                                                                  |  |  |

|                  |           |         |        | Dn: Data Bus 7~0                     |                                                                                                                           |  |  |

|                  |           |         |        |                                      | ese pins are the bi-directional data bus.                                                                                 |  |  |

|                  |           |         |        | ADn: Address/Data Bus 7~0            |                                                                                                                           |  |  |

|                  |           |         |        | In multiplexed host mode, these      | pins are the multiplexed bi-directional address/data bus.                                                                 |  |  |

|                  |           |         |        | In serial host mode, these pins s    | hould be arounded.                                                                                                        |  |  |

| A4               |           | 12      | F4     | MCn: Performance Monitor Co          |                                                                                                                           |  |  |

| MC3/A3           | -         | 13      | F3     |                                      | ust be connected to GND. MC[3:0] are used to select one                                                                   |  |  |

| MC2/A2           |           | 14      | F2     |                                      | nnel 1 to 7 for non-intrusive monitoring. Channel 0 is used as                                                            |  |  |

| MC1/A1           |           | 15      | F1     |                                      | mitter is monitored, signals on the corresponding pins TTIPn                                                              |  |  |

| MC1/A1<br>MC0/A0 |           | 15      | G3     | -                                    |                                                                                                                           |  |  |

| MC0/A0           |           | 10      | 63     | -                                    | nitted to RTIP0 and RRING0. If a receiver is monitored, signals                                                           |  |  |

|                  |           |         |        |                                      | and RRINGn are internally transmitted to RTIP0 and RRING0.                                                                |  |  |

|                  |           |         |        |                                      | uit in receiver 0 can then output the monitored clock to pin<br>data to RDP0 and RDN0 pins. The signals monitored by cha- |  |  |

|                  |           |         |        |                                      | RING0 by activating the remote loopback in this channel.                                                                  |  |  |

|                  |           |         |        |                                      | on determined by MC[3:0] is shown below. Note that if MC[2:0]                                                             |  |  |

|                  |           |         |        | = 000, the device is in normal op    |                                                                                                                           |  |  |

|                  |           |         |        | MC[3:0]                              | Monitoring Configuration                                                                                                  |  |  |

|                  |           |         |        | 0000                                 | Normal operation without monitoring                                                                                       |  |  |

|                  |           |         |        | 0000                                 | Monitoring receiver 1                                                                                                     |  |  |

|                  |           |         |        | 0010                                 | Monitoring receiver 1                                                                                                     |  |  |

|                  |           |         |        | 0010                                 | Monitoring receiver 2                                                                                                     |  |  |

|                  |           |         |        | 0100                                 | Monitoring receiver 4                                                                                                     |  |  |

|                  |           |         |        | 0101                                 | Monitoring receiver 5                                                                                                     |  |  |

|                  |           |         |        | 0110                                 | Monitoring receiver 6                                                                                                     |  |  |

|                  |           |         |        | 0111                                 | Monitoring receiver 7                                                                                                     |  |  |

|                  |           |         |        | 1000                                 | Normal operation without monitoring                                                                                       |  |  |

|                  |           |         |        | 1001                                 | Monitoring transmitter 1                                                                                                  |  |  |

|                  |           |         |        | 1010 Monitoring transmitter 2        |                                                                                                                           |  |  |

|                  |           |         |        | 1011 Monitoring transmitter 3        |                                                                                                                           |  |  |

|                  |           |         |        | 1100                                 | Monitoring transmitter 4                                                                                                  |  |  |

|                  |           |         |        | 1101                                 | Monitoring transmitter 5                                                                                                  |  |  |

|                  |           |         |        | 1110                                 | Monitoring transmitter 6                                                                                                  |  |  |

|                  |           |         |        | 1111                                 | Monitoring transmitter 7                                                                                                  |  |  |

|                  |           |         |        | •                                    |                                                                                                                           |  |  |

|                  |           |         |        | An: Address Bus 4~0                  |                                                                                                                           |  |  |

|                  |           |         |        |                                      | allel host interface operates with separate address and data                                                              |  |  |

|                  |           |         |        | bus. In this mode, the signal on the | his pin is the address bus of the host interface.                                                                         |  |  |

|                  | -         |         |        |                                      |                                                                                                                           |  |  |

| Nama           | Pin No.      |            | No.              | Description                                                                                                 |  |  |  |  |

|----------------|--------------|------------|------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name           | Туре         | QFP144     | BGA160           | Description                                                                                                 |  |  |  |  |

| OE             | I            | 114        | E14              | OE: Output Driver Enable                                                                                    |  |  |  |  |

|                |              |            |                  | Pulling this pin to low can make all driver output into high impedance state immediately for redundancy     |  |  |  |  |

|                |              |            |                  | application without external mechanical relays. In this condition, all the other internal circuits remain   |  |  |  |  |

|                |              |            |                  | active.                                                                                                     |  |  |  |  |

| CLKE           | I            | 115        | E13              | CLKE: Clock Edge Select                                                                                     |  |  |  |  |

|                |              |            |                  | The signal on this pin determins the active edge of RCLKn and SCLK in clock recovery mode, or               |  |  |  |  |

|                |              |            |                  | determines the active level of RDPn and RDNn in the data recovery mode. (Refer to Functional                |  |  |  |  |

|                |              |            |                  | Description and Table-2).                                                                                   |  |  |  |  |

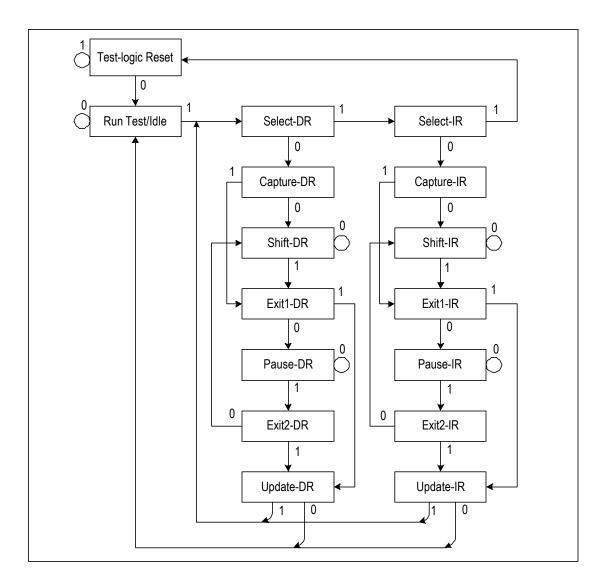

| TRST           | 1            | 95         | G12              | JTAG Signals<br>TRST: JTAG Test Port Reset (Active Low)                                                     |  |  |  |  |

| IROI           | ı<br>Pull up | 90         | GIZ              | This is the active low asynchronous reset to the JTAG Test Port. This pin has an internal pullup resistor   |  |  |  |  |

|                | i uli up     |            |                  | and it can be left disconnected.                                                                            |  |  |  |  |

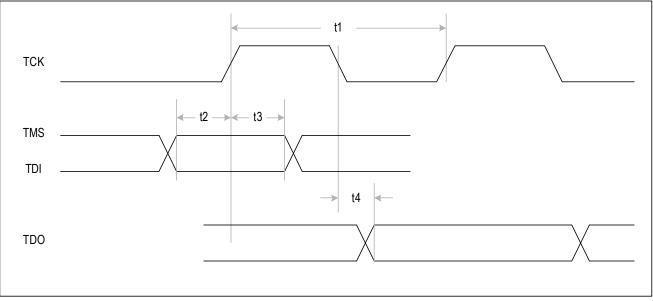

| TMS            |              | 96         | F11              | TMS: JTAG Test Mode Select                                                                                  |  |  |  |  |

|                | Pull up      |            |                  | The signal on this pin controls the JTAG test performance and is clocked into the device on rising edges    |  |  |  |  |

|                |              |            |                  | of TCK. This pin has an internal pullup resistor and it can be left disconnected.                           |  |  |  |  |

| TCK            |              | 97         | F14              | TCK: JTAG Test Clock                                                                                        |  |  |  |  |

|                |              |            |                  | This pin input the clock of the JTAG Test. The data on TDI and TMS are clocked into the device on rising    |  |  |  |  |

|                |              |            |                  | edges of TCK, while the data on TDO is clocked out of the device on falling edges of TCK.                   |  |  |  |  |